ICGOO在线商城 > 集成电路(IC) > 嵌入式 - FPGA(现场可编程门阵列) > XC7K160T-2FBG484C

- 型号: XC7K160T-2FBG484C

- 制造商: Xilinx

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

XC7K160T-2FBG484C产品简介:

ICGOO电子元器件商城为您提供XC7K160T-2FBG484C由Xilinx设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 XC7K160T-2FBG484C价格参考。XilinxXC7K160T-2FBG484C封装/规格:嵌入式 - FPGA(现场可编程门阵列), 。您可以下载XC7K160T-2FBG484C参考资料、Datasheet数据手册功能说明书,资料中有XC7K160T-2FBG484C 详细功能的应用电路图电压和使用方法及教程。

Xilinx Inc.的XC7K160T-2FBG484C是一款嵌入式FPGA(现场可编程门阵列),属于其7系列Kintex FPGA产品线。这款器件具有高性能、低功耗和丰富的逻辑资源,适用于多种应用场景,尤其是在通信、工业控制、医疗成像、广播视频处理和数据中心加速等领域。 1. 通信领域 在通信系统中,XC7K160T-2FBG484C可用于实现复杂的信号处理任务,如基带处理、前向纠错(FEC)、数据包处理等。它支持高速串行接口(如GTX收发器),能够满足10Gbps及以上速率的通信需求。此外,它还可以用于无线基站、路由器、交换机等设备中的协议转换和流量管理。 2. 工业控制 在工业自动化和控制系统中,XC7K160T-2FBG484C可以作为核心控制器,负责实时数据采集、运动控制、电机驱动等功能。它可以通过配置不同的IP核来适应各种工业协议(如EtherCAT、Profinet等),并支持多通道模拟和数字信号处理,确保系统的高可靠性和灵活性。 3. 医疗成像 医疗设备如CT扫描仪、超声波设备等需要高效的图像处理能力。XC7K160T-2FBG484C凭借其强大的并行处理能力和丰富的DSP Slice资源,能够加速图像重建、滤波和增强等操作,提升诊断效率和准确性。同时,它的低功耗特性有助于减少设备的散热压力,延长使用寿命。 4. 广播视频处理 广播行业对视频质量要求极高,XC7K160T-2FBG484C可以用于视频编码/解码、帧同步、色彩校正等任务。它支持多种视频格式和分辨率,并且可以通过硬件加速实现高效的数据传输和处理,确保视频流的稳定性和流畅性。 5. 数据中心加速 在数据中心中,XC7K160T-2FBG484C可以用作计算加速器,帮助分担CPU的任务,特别是在机器学习推理、大数据分析等计算密集型应用中。它能够通过定制化的硬件逻辑显著提升性能,降低延迟,提高能效比。 总之,XC7K160T-2FBG484C凭借其灵活的架构和卓越的性能,在多个领域展现出了广泛的应用潜力。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC) |

| 描述 | IC FPGA 185 I/O 484FCBGA |

| 产品分类 | |

| I/O数 | 185 |

| LAB/CLB数 | 12675 |

| 品牌 | Xilinx Inc |

| 数据手册 | |

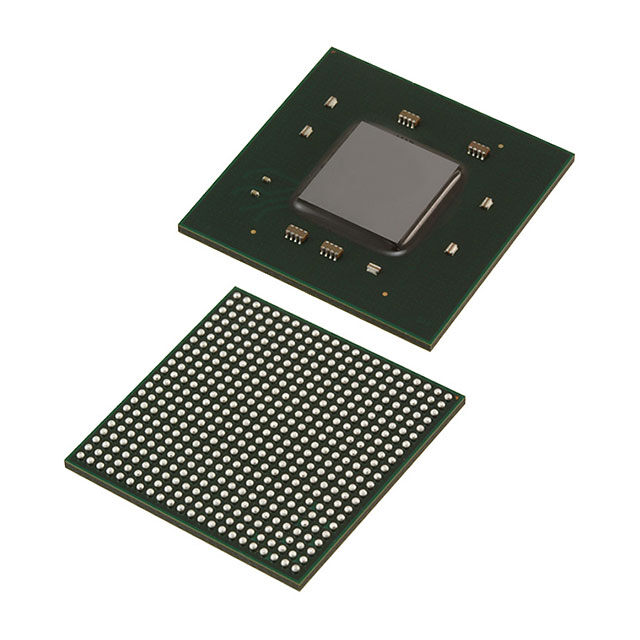

| 产品图片 | |

| 产品型号 | XC7K160T-2FBG484C |

| PCN组件/产地 | |

| PCN设计/规格 | |

| rohs | 无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | Kintex-7 |

| 产品培训模块 | http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=30320 |

| 供应商器件封装 | 484-FCBGA(23x23) |

| 其它名称 | 122-1842 |

| 安装类型 | 表面贴装 |

| 封装/外壳 | 484-BBGA,FCBGA |

| 工作温度 | 0°C ~ 85°C |

| 总RAM位数 | 11980800 |

| 栅极数 | - |

| 标准包装 | 1 |

| 电压-电源 | 0.97 V ~ 1.03 V |

| 逻辑元件/单元数 | 162240 |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics DS182 (v2.16.1) August 7, 2018 Product Specification Introduction Kintex®-7 FPGAs are available in -3, -2, -1, -1L, and -2L unless otherwise noted, all the DC and AC electrical speed grades, with -3 having the highest performance. The parameters are the same for a particular speed grade (that -2L devices are screened for lower maximum static power is, the timing characteristics of a -1 speed grade military and can operate at lower core voltages for lower dynamic temperature device are the same as for a -1 speed grade power than the -2 devices. The -2L industrial (I) temperature commercial temperature device). However, only selected devices operate only at V =0.95V. The -2L extended (E) speed grades and/or devices are available in each CCINT temperature devices can operate at either V =0.9V or temperature range. CCINT 1.0V. The -2LE devices when operated at V =1.0V, and CCINT All supply voltage and junction temperature specifications the -2LI devices when operated at V =0.95V, have the CCINT are representative of worst-case conditions. The parameters same speed specifications as the -2 speed grade, except included are common to popular designs and typical where noted. When the -2LE devices are operated at applications. V =0.9V, the speed specifications, static power, and CCINT dynamic power are reduced. The -1L military (M) Available device and package combinations can be found in: temperature devices have the same speed specifications as • 7Series FPGAs Overview (DS180) the -1 military temperature devices and are screened for lower maximum static power. • Defense-Grade 7Series FPGAs Overview (DS185) Kintex-7 FPGA DC and AC characteristics are specified in This Kintex-7 FPGA data sheet, part of an overall set of commercial, extended, industrial, and military temperature documentation on the 7series FPGAs, is available on the ranges. Except for the operating temperature range or Xilinx website at www.xilinx.com/documentation. DC Characteristics Table 1: Absolute Maximum Ratings(1) Symbol Description Min Max Units FPGA Logic V Internal supply voltage –0.5 1.1 V CCINT V Auxiliary supply voltage –0.5 2.0 V CCAUX V Supply voltage for the block RAM memories –0.5 1.1 V CCBRAM Output drivers supply voltage for HR I/O banks –0.5 3.6 V V CCO Output drivers supply voltage for HP I/O banks –0.5 2.0 V V Auxiliary supply voltage –0.5 2.06 V CCAUX_IO V Input reference voltage –0.5 2.0 V REF I/O input voltage for HR I/O banks –0.40 V +0.55 V CCO I/O input voltage for HP I/O banks –0.55 V +0.55 V V (2)(3)(4) CCO IN I/O input voltage (when V =3.3V) for V and differential I/O standards except –0.40 2.625 V CCO REF TMDS_33(5) V Key memory battery backup supply –0.5 2.0 V CCBATT © 2011–2018 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Kintex, Artix, Zynq, Spartan, ISE, Vivado and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners. DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 1

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics Table 1: Absolute Maximum Ratings(1) (Cont’d) Symbol Description Min Max Units GTX Transceiver V Analog supply voltage for the GTX transmitter and receiver circuits –0.5 1.1 V MGTAVCC V Analog supply voltage for the GTX transmitter and receiver termination circuits –0.5 1.32 V MGTAVTT V Auxiliary analog Quad PLL (QPLL) voltage supply for the GTX transceivers –0.5 1.935 V MGTVCCAUX V GTX transceiver reference clock absolute input voltage –0.5 1.32 V MGTREFCLK Analog supply voltage for the resistor calibration circuit of the GTX transceiver –0.5 1.32 V V MGTAVTTRCAL column V Receiver (RXP/RXN) and Transmitter (TXP/TXN) absolute input voltage –0.5 1.26 V IN I DC input current for receiver input pins DC coupled RX termination=floating – 14 mA DCIN-FLOAT I DC input current for receiver input pins DC coupled RX termination=V – 12 mA DCIN-MGTAVTT MGTAVTT I DC input current for receiver input pins DC coupled RX termination=GND – 6.5 mA DCIN-GND I DC output current for transmitter pins DC coupled RX termination=floating – 14 mA DCOUT-FLOAT I DC output current for transmitter pins DC coupled RX termination=V – 12 mA DCOUT-MGTAVTT MGTAVTT XADC V XADC supply relative to GNDADC –0.5 2.0 V CCADC V XADC reference input relative to GNDADC –0.5 2.0 V REFP Temperature T Storage temperature (ambient) –65 150 °C STG Maximum soldering temperature for Pb/Sn component bodies (6) – +220 °C T SOL Maximum soldering temperature for Pb-free component bodies (6) – +260 °C T Maximum junction temperature(6) – +125 °C j Notes: 1. Stresses beyond those listed under Absolute Maximum Ratings might cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time might affect device reliability. 2. The lower absolute voltage specification always applies. 3. For I/O operation, refer to the 7Series FPGAs SelectIO Resources User Guide (UG471). 4. The maximum limit applies to DC signals. For maximum undershoot and overshoot AC specifications, see Table4 and Table5. 5. See Table10 for TMDS_33 specifications. 6. For soldering guidelines and thermal considerations, see the 7Series FPGA Packaging and Pinout Specification (UG475). Table 2: Recommended Operating Conditions(1)(2) Symbol Description Min Typ Max Units FPGA Logic For -3, -2, -2LE (1.0V), -1, -1M, -1LM devices: internal supply voltage 0.97 1.00 1.03 V V (3) For -2LE (0.9V) devices: internal supply voltage 0.87 0.90 0.93 V CCINT For -2LI (0.95V) devices: internal supply voltage 0.93 0.95 0.97 V For -3, -2, -2LE (1.0V), -1, -1M, -1LM devices: block RAM supply voltage 0.97 1.00 1.03 V V (3) For -2LE (0.9V) devices: block RAM supply voltage 0.87 0.90 1.03 V CCBRAM For -2LI (0.95V) devices: block RAM supply voltage 0.93 0.95 0.97 V V Auxiliary supply voltage 1.71 1.80 1.89 V CCAUX Supply voltage for HR I/O banks 1.14 – 3.465 V V (4)(5) CCO Supply voltage for HP I/O banks 1.14 – 1.89 V DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 2

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics Table 2: Recommended Operating Conditions(1)(2) (Cont’d) Symbol Description Min Typ Max Units Auxiliary supply voltage when set to 1.8V 1.71 1.80 1.89 V V (6) CCAUX_IO Auxiliary supply voltage when set to 2.0V 1.94 2.00 2.06 V I/O input voltage –0.20 – V +0.2 V CCO VIN(7) I/O input voltage (when VCCO=3.3V) for VREF and differential I/O –0.20 – 2.625 V standards except TMDS_33(8) Maximum current through any pin in a powered or unpowered bank when – – 10 mA I (9) IN forward biasing the clamp diode. V (10) Battery voltage 1.0 – 1.89 V CCBATT GTX Transceiver Analog supply voltage for the GTX transceiver QPLL frequency range 0.97 1.0 1.08 V ≤10.3125GHz(12)(13) V (11) MGTAVCC Analog supply voltage for the GTX transceiver QPLL frequency range 1.02 1.05 1.08 V >10.3125GHz Analog supply voltage for the GTX transmitter and receiver termination V (11) 1.17 1.2 1.23 V MGTAVTT circuits V (11) Auxiliary analog QPLL voltage supply for the transceivers 1.75 1.80 1.85 V MGTVCCAUX Analog supply voltage for the resistor calibration circuit of the GTX V (11) 1.17 1.2 1.23 V MGTAVTTRCAL transceiver column XADC V XADC supply relative to GNDADC 1.71 1.80 1.89 V CCADC V Externally supplied reference voltage 1.20 1.25 1.30 V REFP Temperature Junction temperature operating range for commercial (C) temperature 0 – 85 °C devices Junction temperature operating range for extended (E) temperature 0 – 100 °C Tj devices Junction temperature operating range for industrial (I) temperature devices –40 – 100 °C Junction temperature operating range for military (M) temperature devices –55 – 125 °C Notes: 1. All voltages are relative to ground. 2. For the design of the power distribution system, consult the 7 Series FPGAs PCB Design and Pin Planning Guide (UG483). 3. V and V should be connected to the same supply. CCINT CCBRAM 4. Configuration data is retained even if V drops to 0V. CCO 5. Includes V of 1.2V, 1.35V, 1.5V, 1.8V, 2.5V (HR I/O only), and 3.3V (HR I/O only) at ±5%. CCO 6. For more information, refer to the V section of 7Series FPGAs SelectIO Resources User Guide (UG471). CCAUX_IO 7. The lower absolute voltage specification always applies. 8. See Table10 for TMDS_33 specifications. 9. A total of 200mA per bank should not be exceeded. 10. V is required only when using bitstream encryption. If battery is not used, connect V to either ground or V . CCBATT CCBATT CCAUX 11. Each voltage listed requires the filter circuit described in the 7Series FPGAs GTX/GTH Transceivers User Guide (UG476). 12. For data rates ≤10.3125Gb/s, V should be 1.0V ±3% for lower power consumption. MGTAVCC 13. For lower power consumption, V should be 1.0V ±3% over the entire CPLL frequency range. MGTAVCC DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 3

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics Table 3: DC Characteristics Over Recommended Operating Conditions Symbol Description Min Typ(1) Max Units V Data retention V voltage (below which configuration data might be lost) 0.75 – – V DRINT CCINT V Data retention V voltage (below which configuration data might be lost) 1.5 – – V DRI CCAUX I V leakage current per pin – – 15 µA REF REF I Input or output leakage current per pin (sample-tested) – – 15 µA L C (2) Die input capacitance at the pad – – 8 pF IN Pad pull-up (when selected) @ V =0V, V =3.3V 90 – 330 µA IN CCO Pad pull-up (when selected) @ V =0V, V =2.5V 68 – 250 µA IN CCO I Pad pull-up (when selected) @ V =0V, V =1.8V 34 – 220 µA RPU IN CCO Pad pull-up (when selected) @ V =0V, V =1.5V 23 – 150 µA IN CCO Pad pull-up (when selected) @ V =0V, V =1.2V 12 – 120 µA IN CCO Pad pull-down (when selected) @ V =3.3V 68 – 330 µA IN I RPD Pad pull-down (when selected) @ V =1.8V 45 – 180 µA IN I Analog supply current, analog circuits in powered up state – – 25 mA CCADC I (3) Battery supply current – – 150 nA BATT Thevenin equivalent resistance of programmable input termination to V /2 28 40 55 Ω CCO (UNTUNED_SPLIT_40) Thevenin equivalent resistance of programmable input termination to V /2 35 50 65 Ω R (4) CCO IN_TERM (UNTUNED_SPLIT_50) Thevenin equivalent resistance of programmable input termination to V /2 44 60 83 Ω CCO (UNTUNED_SPLIT_60) n Temperature diode ideality factor – 1.010 – – r Temperature diode series resistance – 2 – Ω Notes: 1. Typical values are specified at nominal voltage, 25°C. 2. This measurement represents the die capacitance at the pad, not including the package. 3. Maximum value specified for worst case process at 25°C. 4. Termination resistance to a V /2 level. CCO Table 4: V Maximum Allowed AC Voltage Overshoot and Undershoot for HR I/O Banks(1)(2) IN AC Voltage Overshoot % of UI at –55°C to 125°C AC Voltage Undershoot % of UI at –55°C to 125°C –0.40 100 –0.45 61.7 V +0.55 100 CCO –0.50 25.8 –0.55 11.0 V +0.60 46.6 –0.60 4.77 CCO V +0.65 21.2 –0.65 2.10 CCO V +0.70 9.75 –0.70 0.94 CCO V +0.75 4.55 –0.75 0.43 CCO V +0.80 2.15 –0.80 0.20 CCO V +0.85 1.02 –0.85 0.09 CCO V +0.90 0.49 –0.90 0.04 CCO DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 4

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics Table 4: V Maximum Allowed AC Voltage Overshoot and Undershoot for HR I/O Banks(1)(2) (Cont’d) IN AC Voltage Overshoot % of UI at –55°C to 125°C AC Voltage Undershoot % of UI at –55°C to 125°C V +0.95 0.24 –0.95 0.02 CCO Notes: 1. A total of 200mA per bank should not be exceeded. 2. The peak voltage of the overshoot or undershoot, and the duration above V +0.20V or below GND–0.20V, must not exceed the values CCO in this table. Table 5: V Maximum Allowed AC Voltage Overshoot and Undershoot for HP I/O Banks(1)(2) IN AC Voltage Overshoot % of UI at –55°C to 125°C AC Voltage Undershoot % of UI at –55°C to 125°C V +0.55 100 –0.55 100 CCO V +0.60 50.0(3) –0.60 50.0(3) CCO V +0.65 50.0(3) –0.65 50.0(3) CCO V +0.70 47.0 –0.70 50.0(3) CCO V +0.75 21.2 –0.75 50.0(3) CCO V +0.80 9.71 –0.80 50.0(3) CCO V +0.85 4.51 –0.85 28.4 CCO V +0.90 2.12 –0.90 12.7 CCO V +0.95 1.01 –0.95 5.79 CCO Notes: 1. A total of 200mA per bank should not be exceeded. 2. The peak voltage of the overshoot or undershoot, and the duration above V +0.20V or below GND–0.20V, must not exceed the values CCO in this table. 3. For UI lasting less than 20µs. Table 6: Typical Quiescent Supply Current Speed Grade Symbol Description Device 1.0V 0.95V 0.9V Units -3 -2/-2LE -1 -1LM -1M -2LI -2LE I Quiescent V supply XC7K70T 241 241 241 N/A N/A N/A 187 mA CCINTQ CCINT current XC7K160T 474 474 474 N/A N/A 271 368 mA XC7K325T 810 810 810 N/A N/A 463 629 mA XC7K355T 993 993 993 N/A N/A 568 771 mA XC7K410T 1080 1080 1080 N/A N/A 618 838 mA XC7K420T 1313 1313 1313 N/A N/A 751 1019 mA XC7K480T 1313 1313 1313 N/A N/A 751 1019 mA XQ7K325T N/A 810 810 810 810 463 629 mA XQ7K410T N/A 1080 1080 N/A 1080 618 838 mA DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 5

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics Table 6: Typical Quiescent Supply Current (Cont’d) Speed Grade Symbol Description Device 1.0V 0.95V 0.9V Units -3 -2/-2LE -1 -1LM -1M -2LI -2LE I Quiescent V supply XC7K70T 1 1 1 N/A N/A N/A 1 mA CCOQ CCO current XC7K160T 1 1 1 N/A N/A 1 1 mA XC7K325T 1 1 1 N/A N/A 1 1 mA XC7K355T 1 1 1 N/A N/A 1 1 mA XC7K410T 1 1 1 N/A N/A 1 1 mA XC7K420T 1 1 1 N/A N/A 1 1 mA XC7K480T 1 1 1 N/A N/A 1 1 mA XQ7K325T N/A 1 1 1 1 1 1 mA XQ7K410T N/A 1 1 N/A 1 1 1 mA I Quiescent V supply XC7K70T 21 21 21 N/A N/A N/A 21 mA CCAUXQ CCAUX current XC7K160T 40 40 40 N/A N/A 36 40 mA XC7K325T 68 68 68 N/A N/A 61 68 mA XC7K355T 75 75 75 N/A N/A 67 75 mA XC7K410T 85 85 85 N/A N/A 76 85 mA XC7K420T 99 99 99 N/A N/A 89 99 mA XC7K480T 99 99 99 N/A N/A 89 99 mA XQ7K325T N/A 68 68 68 68 68 68 mA XQ7K410T N/A 85 85 N/A 85 85 85 mA I Quiescent V supply XC7K70T N/A N/A N/A N/A N/A N/A N/A mA CCAUX_IOQ CCAUX_IO current XC7K160T 2 2 2 N/A N/A 1 2 mA XC7K325T 2 2 2 N/A N/A 1 2 mA XC7K355T N/A N/A N/A N/A N/A N/A N/A mA XC7K410T 2 2 2 N/A N/A 1 2 mA XC7K420T N/A N/A N/A N/A N/A N/A N/A mA XC7K480T N/A N/A N/A N/A N/A N/A N/A mA XQ7K325T N/A 2 2 2 2 2 2 mA XQ7K410T N/A 2 2 N/A 2 2 2 mA DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 6

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics Table 6: Typical Quiescent Supply Current (Cont’d) Speed Grade Symbol Description Device 1.0V 0.95V 0.9V Units -3 -2/-2LE -1 -1LM -1M -2LI -2LE I Quiescent V supply XC7K70T 6 6 6 N/A N/A N/A 6 mA CCBRAMQ CCBRAM current XC7K160T 14 14 14 N/A N/A 8 14 mA XC7K325T 19 19 19 N/A N/A 10 19 mA XC7K355T 31 31 31 N/A N/A 17 31 mA XC7K410T 34 34 34 N/A N/A 19 34 mA XC7K420T 41 41 41 N/A N/A 23 41 mA XC7K480T 41 41 41 N/A N/A 23 41 mA XQ7K325T N/A 19 19 19 19 19 19 mA XQ7K410T N/A 34 34 N/A 34 34 34 mA Notes: 1. Typical values are specified at nominal voltage, 85°C junction temperatures (T) with single-ended SelectIO resources. j 2. Typical values are for blank configured devices with no output current loads, no active input pull-up resistors, all I/O pins are 3-state and floating. 3. Use the Xilinx Power Estimator (XPE) spreadsheet tool (download at www.xilinx.com/power) to estimate static power consumption for conditions other than those specified. Power-On/Off Power Supply Sequencing The recommended power-on sequence is V , V , V , V , and V to achieve minimum current draw CCINT CCBRAM CCAUX CCAUX_IO CCO and ensure that the I/Os are 3-stated at power-on. The recommended power-off sequence is the reverse of the power-on sequence. If V and V have the same recommended voltage levels then both can be powered by the same supply CCINT CCBRAM and ramped simultaneously. If V , V , and V have the same recommended voltage levels then they can be CCAUX CCAUX_IO CCO powered by the same supply and ramped simultaneously. For V voltages of 3.3V in HR I/O banks and configuration bank 0: CCO • The voltage difference between V and V must not exceed 2.625V for longer than T for each CCO CCAUX VCCO2VCCAUX power-on/off cycle to maintain device reliability levels. • The T time can be allocated in any percentage between the power-on and power-off ramps. VCCO2VCCAUX The recommended power-on sequence to achieve minimum current draw for the GTX transceivers is V , V , CCINT MGTAVCC V OR V , V , V . There is no recommended sequencing for V . Both V and V MGTAVTT MGTAVCC CCINT MGTAVTT MGTVCCAUX MGTAVCC CCINT can be ramped simultaneously. The recommended power-off sequence is the reverse of the power-on sequence to achieve minimum current draw. If these recommended sequences are not met, current drawn from V can be higher than specifications during power- MGTAVTT up and power-down. • When V is powered before V and V –V >150 mV and V <0.7V, the V MGTAVTT MGTAVCC MGTAVTT MGTAVCC MGTAVCC MGTAVTT current draw can increase by 460mA per transceiver during V ramp up. The duration of the current draw can be MGTAVCC up to 0.3xT (ramp time from GND to 90% of V ). The reverse is true for power-down. MGTAVCC MGTAVCC • When V is powered before V and V –V >150 mV and V <0.7V, the V current MGTAVTT CCINT MGTAVTT CCINT CCINT MGTAVTT draw can increase by 50mA per transceiver during V ramp up. The duration of the current draw can be up to CCINT 0.3xT (ramp time from GND to 90% of V ). The reverse is true for power-down. VCCINT CCINT There is no recommended sequence for supplies not shown. Table7 shows the minimum current, in addition to I , that are required by Kintex-7 devices for proper power-on and CCQ configuration. If the current minimums shown in Table6 and Table7 are met, the device powers on after all five supplies have passed through their power-on reset threshold voltages. The FPGA must not be configured until after V is applied. CCINT DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 7

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics Once initialized and configured, use the Xilinx Power Estimator (XPE) spreadsheet tool (download at www.xilinx.com/power) to estimate current drain on these supplies. Table 7: Power-On Current for Kintex-7 Devices Device I I I I I Units CCINTMIN CCAUXMIN CCOMIN CCAUX_IOMIN CCBRAMMIN XC7K70T I +450 I +40 I +40mA per bank I +40mA per bank I +40 mA CCINTQ CCAUXQ CCOQ CCOAUXIOQ CCBRAMQ XC7K160T I +550 I +50 I +40mA per bank I +40mA per bank I +40 mA CCINTQ CCAUXQ CCOQ CCOAUXIOQ CCBRAMQ XC7K325T I +600 I +80 I +40mA per bank I +40mA per bank I +40 mA CCINTQ CCAUXQ CCOQ CCOAUXIOQ CCBRAMQ XC7K355T I +1450 I +109 I +40mA per bank I +40mA per bank I +81 mA CCINTQ CCAUXQ CCOQ CCOAUXIOQ CCBRAMQ XC7K410T I +1500 I +125 I +40mA per bank I +40mA per bank I +90 mA CCINTQ CCAUXQ CCOQ CCOAUXIOQ CCBRAMQ XC7K420T I +2200 I +180 I +40mA per bank I +40mA per bank I +108 mA CCINTQ CCAUXQ CCOQ CCOAUXIOQ CCBRAMQ XC7K480T I +2200 I +180 I +40mA per bank I +40mA per bank I +108 mA CCINTQ CCAUXQ CCOQ CCOAUXIOQ CCBRAMQ XQ7K325T I +600 I +80 I +40mA per bank I +40mA per bank I +40 mA CCINTQ CCAUXQ CCOQ CCOAUXIOQ CCBRAMQ XQ7K410T I +1500 I +125 I +40mA per bank I +40mA per bank I +90 mA CCINTQ CCAUXQ CCOQ CCOAUXIOQ CCBRAMQ Table 8: Power Supply Ramp Time Symbol Description Conditions Min Max Units T Ramp time from GND to 90% of V 0.2 50 ms VCCINT CCINT T Ramp time from GND to 90% of V 0.2 50 ms VCCO CCO T Ramp time from GND to 90% of V 0.2 50 ms VCCAUX CCAUX T Ramp time from GND to 90% of V 0.2 50 ms VCCAUX_IO CCAUX_IO T Ramp time from GND to 90% of V 0.2 50 ms VCCBRAM CCBRAM T = 125°C(1) – 300 J T Allowed time per power cycle for V – V > 2.625V T = 100°C(1) – 500 ms VCCO2VCCAUX CCO CCAUX J T = 85°C(1) – 800 J T Ramp time from GND to 90% of V 0.2 50 ms MGTAVCC MGTAVCC T Ramp time from GND to 90% of V 0.2 50 ms MGTAVTT MGTAVTT T Ramp time from GND to 90% of V 0.2 50 ms MGTVCCAUX MGTVCCAUX Notes: 1. Based on 240,000 power cycles with nominal V of 3.3V or 36,500 power cycles with a worst case V of 3.465V. CCO CCO DC Input and Output Levels Values for V and V are recommended input voltages. Values for I and I are guaranteed over the recommended IL IH OL OH operating conditions at the V and V test points. Only selected standards are tested. These are chosen to ensure that all OL OH standards meet their specifications. The selected standards are tested at a minimum V with the respective V and V CCO OL OH voltage levels shown. Other standards are sample tested. Table 9: SelectIO DC Input and Output Levels(1)(2) V V V V I I IL IH OL OH OL OH I/O Standard V, Min V, Max V, Min V, Max V, Max V, Min mA mA HSTL_I –0.300 V –0.100 V +0.100 V +0.300 0.400 V –0.400 8 –8 REF REF CCO CCO HSTL_I_12 –0.300 V –0.080 V +0.080 V +0.300 25%V 75%V 6.3 –6.3 REF REF CCO CCO CCO HSTL_I_18 –0.300 V –0.100 V +0.100 V +0.300 0.400 V –0.400 8 –8 REF REF CCO CCO HSTL_II –0.300 V –0.100 V +0.100 V +0.300 0.400 V –0.400 16 –16 REF REF CCO CCO HSTL_II_18 –0.300 V –0.100 V +0.100 V +0.300 0.400 V –0.400 16 –16 REF REF CCO CCO DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 8

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics Table 9: SelectIO DC Input and Output Levels(1)(2) (Cont’d) V V V V I I IL IH OL OH OL OH I/O Standard V, Min V, Max V, Min V, Max V, Max V, Min mA mA HSUL_12 –0.300 V –0.130 V +0.130 V +0.300 20%V 80%V 0.1 –0.1 REF REF CCO CCO CCO LVCMOS12 –0.300 35% V 65% V V +0.300 0.400 V –0.400 Note3 Note3 CCO CCO CCO CCO LVCMOS15, –0.300 35% V 65% V V +0.300 25%V 75%V Note4 Note4 CCO CCO CCO CCO CCO LVDCI_15 LVCMOS18, –0.300 35% V 65% V V +0.300 0.450 V –0.450 Note5 Note5 CCO CCO CCO CCO LVDCI_18 LVCMOS25 –0.300 0.700 1.700 V +0.300 0.400 V –0.400 Note6 Note6 CCO CCO LVCMOS33 –0.300 0.800 2.000 3.450 0.400 V –0.400 Note6 Note6 CCO LVTTL –0.300 0.800 2.000 3.450 0.400 2.400 Note7 Note7 MOBILE_DDR –0.300 20% V 80% V V +0.300 10%V 90%V 0.1 –0.1 CCO CCO CCO CCO CCO PCI33_3 –0.400 30% V 50% V V +0.500 10%V 90%V 1.5 –0.5 CCO CCO CCO CCO CCO SSTL12 –0.300 V –0.100 V +0.100 V +0.300 V /2–0.150 V /2+0.150 14.25 –14.25 REF REF CCO CCO CCO SSTL135 –0.300 V –0.090 V +0.090 V +0.300 V /2–0.150 V /2+0.150 13.0 –13.0 REF REF CCO CCO CCO SSTL135_R –0.300 V –0.090 V +0.090 V +0.300 V /2–0.150 V /2+0.150 8.9 –8.9 REF REF CCO CCO CCO SSTL15 –0.300 V –0.100 V +0.100 V +0.300 V /2–0.175 V /2+0.175 13.0 –13.0 REF REF CCO CCO CCO SSTL15_R –0.300 V –0.100 V +0.100 V +0.300 V /2–0.175 V /2+0.175 8.9 –8.9 REF REF CCO CCO CCO SSTL18_I –0.300 V –0.125 V +0.125 V +0.300 V /2–0.470 V /2+0.470 8 –8 REF REF CCO CCO CCO SSTL18_II –0.300 V –0.125 V +0.125 V +0.300 V /2–0.600 V /2+0.600 13.4 –13.4 REF REF CCO CCO CCO Notes: 1. Tested according to relevant specifications. 2. 3.3V and 2.5V standards are only supported in HR I/O banks. 3. Supported drive strengths of 2, 4, 6, or 8mA in HP I/O banks and 4, 8, or 12mA in HR I/O banks. 4. Supported drive strengths of 2, 4, 6, 8, 12, or 16mA in HP I/O banks and 4, 8, 12, or 16mA in HR I/O banks. 5. Supported drive strengths of 2, 4, 6, 8, 12, or 16mA in HP I/O banks and 4, 8, 12, 16, or 24mA in HR I/O banks. 6. Supported drive strengths of 4, 8, 12, or 16mA 7. Supported drive strengths of 4, 8, 12, 16, or 24mA 8. For detailed interface specific DC voltage levels, see the 7Series FPGAs SelectIO Resources User Guide (UG471). DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 9

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics Table 10: Differential SelectIO DC Input and Output Levels V (1) V (2) V (3) V (4) ICM ID OCM OD I/O Standard V, Min V, Typ V, Max V, Min V, Typ V, Max V, Min V, Typ V, Max V, Min V, Typ V, Max BLVDS_25 0.300 1.200 1.425 0.100 – – – 1.250 – Note5 MINI_LVDS_25 0.300 1.200 V 0.200 0.400 0.600 1.000 1.200 1.400 0.300 0.450 0.600 CCAUX PPDS_25 0.200 0.900 V 0.100 0.250 0.400 0.500 0.950 1.400 0.100 0.250 0.400 CCAUX RSDS_25 0.300 0.900 1.500 0.100 0.350 0.600 1.000 1.200 1.400 0.100 0.350 0.600 TMDS_33 2.700 2.965 3.230 0.150 0.675 1.200 V –0.405 V –0.300 V –0.190 0.400 0.600 0.800 CCO CCO CCO Notes: 1. V is the input common mode voltage. ICM 2. V is the input differential voltage (Q–Q). ID 3. V is the output common mode voltage. OCM 4. V is the output differential voltage (Q–Q). OD 5. V for BLVDS will vary significantly depending on topology and loading. OD 6. LVDS_25 is specified in Table12. 7. LVDS is specified in Table13. Table 11: Complementary Differential SelectIO DC Input and Output Levels V (1) V (2) V (3) V (4) I I ICM ID OL OH OL OH I/O Standard V, Min V, Typ V, Max V, Min V, Max V, Max V, Min mA, Max mA, Min DIFF_HSTL_I 0.300 0.750 1.125 0.100 – 0.400 V –0.400 8.00 –8.00 CCO DIFF_HSTL_I_18 0.300 0.900 1.425 0.100 – 0.400 V –0.400 8.00 –8.00 CCO DIFF_HSTL_II 0.300 0.750 1.125 0.100 – 0.400 V –0.400 16.00 –16.00 CCO DIFF_HSTL_II_18 0.300 0.900 1.425 0.100 – 0.400 V –0.400 16.00 –16.00 CCO DIFF_HSUL_12 0.300 0.600 0.850 0.100 – 20% V 80% V 0.100 –0.100 CCO CCO DIFF_MOBILE_DDR 0.300 0.900 1.425 0.100 – 10% V 90% V 0.100 –0.100 CCO CCO DIFF_SSTL12 0.300 0.600 0.850 0.100 – (V /2)–0.150 (V /2)+0.150 14.25 –14.25 CCO CCO DIFF_SSTL135 0.300 0.675 1.000 0.100 – (V /2)–0.150 (V /2)+0.150 13.0 –13.0 CCO CCO DIFF_SSTL135_R 0.300 0.675 1.000 0.100 – (V /2)–0.150 (V /2)+0.150 8.9 –8.9 CCO CCO DIFF_SSTL15 0.300 0.750 1.125 0.100 – (V /2)–0.175 (V /2)+0.175 13.0 –13.0 CCO CCO DIFF_SSTL15_R 0.300 0.750 1.125 0.100 – (V /2)–0.175 (V /2)+0.175 8.9 –8.9 CCO CCO DIFF_SSTL18_I 0.300 0.900 1.425 0.100 – (V /2)–0.470 (V /2)+0.470 8.00 –8.00 CCO CCO DIFF_SSTL18_II 0.300 0.900 1.425 0.100 – (V /2)–0.600 (V /2)+0.600 13.4 –13.4 CCO CCO Notes: 1. V is the input common mode voltage. ICM 2. V is the input differential voltage (Q–Q). ID 3. V is the single-ended low-output voltage. OL 4. V is the single-ended high-output voltage. OH DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 10

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics LVDS DC Specifications (LVDS_25) The LVDS_25 standard is available in the HR I/O banks. See the 7Series FPGAs SelectIO Resources User Guide (UG471) for more information. Table 12: LVDS_25 DC Specifications Symbol DC Parameter Conditions Min Typ Max Units V Supply Voltage 2.375 2.500 2.625 V CCO V Output High Voltage for Q and Q R = 100Ω across Q and Q signals – – 1.675 V OH T V Output Low Voltage for Q and Q R = 100Ω across Q and Q signals 0.700 – – V OL T Differential Output Voltage: R = 100Ω across Q and Q signals 247 350 600 mV T V (Q–Q), Q = High ODIFF (Q–Q), Q=High V Output Common-Mode Voltage R = 100Ω across Q and Q signals 1.000 1.250 1.425 V OCM T Differential Input Voltage: 100 350 600 mV V (Q–Q), Q = High IDIFF (Q–Q), Q=High V Input Common-Mode Voltage 0.300 1.200 1.500 V ICM Notes: 1. Differential inputs for LVDS_25 can be placed in banks with V levels that are different from the required level for outputs. Refer to the CCO 7Series FPGAs SelectIO Resources User Guide (UG471) for more information. LVDS DC Specifications (LVDS) The LVDS standard is available in the HP I/O banks. See the 7Series FPGAs SelectIO Resources User Guide (UG471) for more information. Table 13: LVDS DC Specifications Symbol DC Parameter Conditions Min Typ Max Units V Supply Voltage 1.710 1.800 1.890 V CCO V Output High Voltage for Q and Q R = 100Ω across Q and Q signals – – 1.675 V OH T V Output Low Voltage for Q and Q R = 100Ω across Q and Q signals 0.825 – – V OL T Differential Output Voltage: R = 100Ω across Q and Q signals 247 350 600 mV T V (Q–Q), Q = High ODIFF (Q–Q), Q=High V Output Common-Mode Voltage R = 100Ω across Q and Q signals 1.000 1.250 1.425 V OCM T Differential Input Voltage: Common-mode input voltage=1.25V 100 350 600 mV V (Q–Q), Q = High IDIFF (Q–Q), Q=High V Input Common-Mode Voltage Differential input voltage=±350mV 0.300 1.200 1.425 V ICM Notes: 1. Differential inputs for LVDS can be placed in banks with V levels that are different from the required level for outputs. Refer to the 7Series CCO FPGAs SelectIO Resources User Guide (UG471) for more information. DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 11

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics AC Switching Characteristics All values represented in this data sheet are based on the speed specifications in the Vivado® Design Suite 2015.4 and ISE®software 14.7 as outlined in Table14. Table 14: Kintex-7 FPGA Speed Specification Version By Device Version In: Typical V CCINT Device ISE 14.7 Vivado 2015.4 (Table2) 1.10 1.12 1.0V XC7K70T(1), XC7K160T(1), XC7K325T, XC7K355T, XC7K410T, XC7K420T, XC7K480T N/A 1.12 0.95V XC7K160T(1), XC7K325T, XC7K355T, XC7K410T, XC7K420T, XC7K480T 1.09 1.09 0.9V XC7K70T, XC7K160T, XC7K325T, XC7K355T, XC7K410T, XC7K420T, XC7K480T 1.05 1.09 1.0V XQ7K325T, XQ7K410T 1.05 1.09 0.9V XQ7K325T, XQ7K410T Notes: 1. GTX data rates greater than 6.6Gb/s in the FBG484 package in the -3 and -2 speed grades require Vivado Design Suite 2017.1 or later. Switching characteristics are specified on a per-speed-grade basis and can be designated as Advance, Preliminary, or Production. Each designation is defined as follows: Advance Product Specification These specifications are based on simulations only and are typically available soon after device design specifications are frozen. Although speed grades with this designation are considered relatively stable and conservative, some under-reporting might still occur. Preliminary Product Specification These specifications are based on complete ES (engineering sample) silicon characterization. Devices and speed grades with this designation are intended to give a better indication of the expected performance of production silicon. The probability of under-reporting delays is greatly reduced as compared to Advance data. Product Specification These specifications are released once enough production silicon of a particular device family member has been characterized to provide full correlation between specifications and devices over numerous production lots. There is no under-reporting of delays, and customers receive formal notification of any subsequent changes. Typically, the slowest speed grades transition to production before faster speed grades. Testing of AC Switching Characteristics Internal timing parameters are derived from measuring internal test patterns. All AC switching characteristics are representative of worst-case supply voltage and junction temperature conditions. For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer and back-annotate to the simulation net list. Unless otherwise noted, values apply to all Kintex-7 FPGAs. DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 12

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics Speed Grade Designations Since individual family members are produced at different times, the migration from one category to another depends completely on the status of the fabrication process for each device. Table15 correlates the current status of each Kintex-7 device on a per speed grade basis. Table 15: Kintex-7 Device Speed Grade Designations Speed Grade Designations Device Advance Preliminary Production XC7K70T -3, -2, -2LE(1.0V), -1, and -2LE (0.9V) XC7K160T -3, -2, -2LE(1.0V), -2LI (0.95V), -1, and -2LE (0.9V) XC7K325T -3, -2, -2LE(1.0V), -2LI (0.95V), -1, and -2LE (0.9V) XC7K355T -3, -2, -2LE(1.0V), -2LI (0.95V), -1, and -2LE (0.9V) XC7K410T -3, -2, -2LE(1.0V), -2LI (0.95V), -1, and -2LE (0.9V) XC7K420T -3, -2, -2LE(1.0V), -2LI (0.95V), -1, and -2LE (0.9V) XC7K480T -3, -2, -2LE(1.0V), -2LI (0.95V), -1, and -2LE (0.9V) XQ7K325T -2I, -2LE(1.0V), -1I, -2LE(0.9V), -2LI (0.95V), -1LM, and -1M XQ7K410T -2I, -2LE(1.0V), -1I, -2LE(0.9V), -2LI (0.95V), and -1M Production Silicon and Software Status In some cases, a particular family member (and speed grade) is released to production before a speed specification is released with the correct label (Advance, Preliminary, Production). Any labeling discrepancies are corrected in subsequent speed specification releases. Table16 lists the production released Kintex-7 device, speed grade, and the minimum corresponding supported speed specification version and software revisions. The software and speed specifications listed are the minimum releases required for production. All subsequent releases of software and speed specifications are valid. Table 16: Kintex-7 Device Production Software and Speed Specification Release Speed Grade Designations Device 1.0V 0.95V 0.9V -3 -2/-2LE -1 -1M -1LM -2LI -2LE XC7K70T Vivado tools 2012.4 v1.08 N/A N/A N/A Vivado tools 2012.4 v1.07 or ISE tools 14.2 v1.06 or ISE tools 14.3 v1.06 XC7K160T Vivado tools 2012.4 v1.08 N/A N/A Vivado tools 2014.4 v1.12 Vivado tools 2012.4 v1.07 or ISE tools 14.2 v1.06 or ISE tools 14.3 v1.06 XC7K325T Vivado tools 2012.4 v1.08 N/A N/A Vivado tools 2014.4 v1.12 Vivado tools 2012.4 v1.07 or ISE tools 14.2 v1.06 or ISE tools 14.3 v1.06 XC7K355T Vivado tools 2012.4 v1.08 N/A N/A Vivado tools 2014.4 v1.12 Vivado tools 2012.4 v1.07 or ISE tools 14.2 v1.06 or ISE tools 14.3 v1.06 XC7K410T Vivado tools 2012.4 v1.08 N/A N/A Vivado tools 2014.4 v1.12 Vivado tools 2012.4 v1.07 or ISE tools 14.2 v1.06 or ISE tools 14.3 v1.06 XC7K420T Vivado tools 2012.4 v1.08 N/A N/A Vivado tools 2014.4 v1.12 Vivado tools 2012.4 v1.07 or ISE tools 14.2 v1.06 or ISE tools 14.3 v1.06 XC7K480T Vivado tools 2012.4 v1.08 N/A N/A Vivado tools 2014.4 v1.12 Vivado tools 2012.4 v1.07 or ISE tools 14.2 v1.06 or ISE tools 14.3 v1.06 XQ7K325T N/A Vivado tools 2013.1 v1.04 Vivado tools Vivado tools 2015.4 v1.07 Vivado tools 2013.1 v1.04 or ISE tools 14.5 v1.04 2015.4 v1.09 or ISE tools 14.5 v1.04 XQ7K410T N/A Vivado tools 2013.1 v1.04 N/A Vivado tools 2015.4 v1.07 Vivado tools 2013.1 v1.04 or ISE tools 14.5 v1.04 or ISE tools 14.5 v1.04 DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 13

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics Selecting the Correct Speed Grade and Voltage in the Vivado Tools It is important to select the correct device speed grade and voltage in the Vivado tools for the device that you are selecting. To select the 1.0V speed specifications in the Vivado tools, select the Kintex-7 or Defense Grade Kintex-7Q sub-family, and then select the part name that is the device name followed by the package name followed by the speed grade. For example, select the xc7k325tffg900-3 part name for the XC7K325T device in the FFG900 package and -3 (1.0V) speed grade or select the xc7k325tffg900-2L part name for the XC7K325T device in the FFG900 package and -2LE (1.0V) speed grade. To select the -2LI (0.95V) speed specifications in the Vivado tools, select the Kintex-7 sub-family and then select the part name that is the device name followed by an i followed by the package name followed by the speed grade. For example, select the xc7k325tiffg900-2L part name for the XC7K325T device in the FFG900 package and -2LI (0.95V) speed grade. The -2LI (0.95V) speed specifications are not supported in the ISE tools. To select the -2LE (0.9V) speed specifications in the Vivado tools, select the Kintex-7 Low Voltage or Defense Grade Kintex-7Q Low Voltage sub-family, and then select the part name that is the device name followed by an l followed by the package name followed by the speed grade. For example, select the xc7k325tlffg900-2L part name for the XC7K325T device in the FFG900 package and -2LE (0.9V) speed grade. A similar part naming convention applies to the speed specifications selection in the ISE tools for supported devices. See Table16 for the subset of 7 series FPGAs supported in the ISE tools. Performance Characteristics This section provides the performance characteristics of some common functions and designs implemented in Kintex-7 devices. The numbers reported here are worst-case values; they have all been fully characterized. These values are subject to the same guidelines as the AC Switching Characteristics, page12. In each table, the I/O bank type is either High Performance (HP) or High Range (HR). Table 17: Networking Applications Interface Performances Speed Grade I/O Description Bank 1.0V 0.95V 0.9V Units Type -3 -2/-2LE -1/-1M/-1LM -2LI -2LE SDR LVDS transmitter (using OSERDES; HR 710 710 625 710 625 Mb/s DATA_WIDTH=4 to 8) HP 710 710 625 710 625 Mb/s DDR LVDS transmitter (using OSERDES; HR 1250 1250 950 1250 950 Mb/s DATA_WIDTH=4 to 14) HP 1600 1400 1250 1400 1250 Mb/s SDR LVDS receiver (SFI-4.1)(1) HR 710 710 625 710 625 Mb/s HP 710 710 625 710 625 Mb/s DDR LVDS receiver (SPI-4.2)(1) HR 1250 1250 950 1250 950 Mb/s HP 1600 1400 1250 1400 1250 Mb/s Notes: 1. LVDS receivers are typically bounded with certain applications where specific dynamic phase-alignment (DPA) algorithms dominate deterministic performance. Table18 and Table19 provide the maximum data rates for applicable memory standards using the Kintex-7 FPGAs memory PHY. The final performance of the memory interface is determined through a complete design implemented in the Vivado or ISE Design Suite, following guidelines in the Zynq-7000 SoC and 7Series Devices Memory Interface Solutions User Guide (UG586), electrical analysis, and characterization of the system. DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 14

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics Table 18: Maximum Physical Interface (PHY) Rate for Memory Interfaces IP available with the Memory Interface Generator (FF and RF Packages)(1)(2) Speed Grade Memory I/O Bank V 1.0V 0.95V 0.9V Units Standard Type CCAUX_IO -3 -2/-2LE -1 -1M/-1LM -2LI -2LE 4:1 Memory Controllers HP 2.0V 1866(3) 1866(3) 1600 1066 1600 1333 Mb/s DDR3 HP 1.8V 1600 1333 1066 800 1333 1066 Mb/s HR N/A 1066 1066 800 800 1066 800 Mb/s HP 2.0V 1600 1600 1333 1066 1600 1066 Mb/s DDR3L HP 1.8V 1333 1066 800 800 1066 800 Mb/s HR N/A 800 800 667 N/A 800 667 Mb/s HP 2.0V 800 800 800 667 800 800 Mb/s DDR2 HP 1.8V 800 800 800 667 800 800 Mb/s HR N/A 800 800 800 533 800 800 Mb/s HP 2.0V 800 667 667 550 667 533 MHz RLDRAM III HP 1.8V 550 500 450 400 500 450 MHz HR N/A N/A 2:1 Memory Controllers HP 2.0V 1066 1066 800 667 1066 800 Mb/s DDR3 HP 1.8V 1066 1066 800 667 1066 800 Mb/s HR N/A 1066 1066 800 667 1066 800 Mb/s HP 2.0V 1066 1066 800 667 1066 800 Mb/s DDR3L HP 1.8V 1066 1066 800 667 1066 800 Mb/s HR N/A 800 800 667 N/A 800 667 Mb/s HP 2.0V 667 DDR2 HP 1.8V 800 800 800 667 800 800 Mb/s HR N/A 533 HP 2.0V 550 500 450 300 500 450 MHz QDR II+(4) HP 1.8V HR N/A 500 450 400 300 450 400 MHz HP 2.0V RLDRAM II HP 1.8V 533 500 450 400 500 450 MHz HR N/A HP 2.0V 667 667 667 533 667 667 Mb/s LPDDR2 HP 1.8V 667 667 667 533 667 667 Mb/s HR N/A 667 667 667 533 667 667 Mb/s Notes: 1. V tracking is required. For more information, see the Zynq-7000 SoC and 7Series Devices Memory Interface Solutions User Guide REF (UG586). 2. When using the internal V , the maximum data rate is 800Mb/s (400MHz). REF 3. For designs using 1866Mb/s components, contact Xilinx Technical Support. 4. The maximum QDRII+ performance specifications are for burst-length 4 (BL=4) implementations. Burst length 2 (BL=2) implementations are limited to 333MHz for all speed grades and I/O bank types. DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 15

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics Table 19: Maximum Physical Interface (PHY) Rate for Memory Interfaces IP available with the Memory Interface Generator (FB Packages)(1)(2) Speed Grade Memory I/O Bank V (3) 1.0V 0.95V 0.9V Units Standard Type CCAUX_IO -3 -2/-2LE -1 -1M/-1LM -2LI -2LE 4:1 Memory Controllers HP N/A 1333 1066 800 800 1066 800 Mb/s DDR3 HR N/A 1066 800 800 800 800 800 Mb/s HP N/A 1066 800 667 667 800 667 Mb/s DDR3L HR N/A 800 800 667 N/A 800 667 Mb/s HP N/A 800 800 800 667 800 800 Mb/s DDR2 HR N/A 800 667 667 533 667 667 Mb/s HP N/A 550 500 450 350 500 450 MHz RLDRAM III HR N/A N/A 2:1 Memory Controllers HP N/A 1066 1066 800 667 1066 800 Mb/s DDR3 HR N/A 1066 800 800 667 800 800 Mb/s HP N/A 1066 800 667 667 800 667 Mb/s DDR3L HR N/A 800 800 667 N/A 800 667 Mb/s HP N/A 800 800 800 667 800 800 Mb/s DDR2 HR N/A 800 667 667 533 667 667 Mb/s HP N/A 550 500 450 300 500 450 MHz QDR II+(4) HR N/A 450 400 350 300 400 350 MHz HP N/A RLDRAM II 533 500 450 400 500 450 MHz HR N/A HP N/A 667 667 667 400 667 667 Mb/s LPDDR2 HR N/A 667 667 533 400 667 533 Mb/s Notes: 1. V tracking is required. For more information, see the Zynq-7000 SoC and 7Series Devices Memory Interface Solutions User Guide REF (UG586). 2. When using the internal V , the maximum data rate is 800Mb/s (400MHz). REF 3. FB packages do not have separate V supply pins to adjust the pre-driver voltage of the HP I/O banks. CCAUX_IO 4. The maximum QDRII+ performance specifications are for burst-length 4 (BL=4) implementations. Burst length 2 (BL=2) implementations are limited to 333MHz for all speed grades and I/O bank types. DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 16

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics IOB Pad Input/Output/3-State Table20 (high-range IOB (HR)) and Table21 (high-performance IOB (HP)) summarizes the values of standard-specific data input delay adjustments, output delays terminating at pads (based on standard) and 3-state delays. • T is described as the delay from IOB pad through the input buffer to the I-pin of an IOB pad. The delay varies IOPI depending on the capability of the SelectIO input buffer. • T is described as the delay from the O pin to the IOB pad through the output buffer of an IOB pad. The delay varies IOOP depending on the capability of the SelectIO output buffer. • T is described as the delay from the T pin to the IOB pad through the output buffer of an IOB pad, when 3-state is IOTP disabled. The delay varies depending on the SelectIO capability of the output buffer. In HP I/O banks, the internal DCI termination turn-on time is always faster than T when the DCITERMDISABLE pin is used. In HR I/O banks, the IOTP IN_TERM termination turn-on time is always faster than T when the INTERMDISABLE pin is used. IOTP Table 20: IOB High Range (HR) Switching Characteristics T T T IOPI IOOP IOTP Speed Grade Speed Grade Speed Grade I/OStandard Units 1.0V 0.95V 0.9V 1.0V 0.95V 0.9V 1.0V 0.95V 0.9V -2/ -1M/ -2/ -1M/ -2/ -1M/ -3 -1 -2LI -2LE -3 -1 -2LI -2LE -3 -1 -2LI -2LE -2LE -1LM -2LE -1LM -2LE -1LM LVTTL_S4 1.31 1.42 1.64 1.64 1.42 1.51 3.77 3.90 4.00 4.00 3.90 4.13 3.52 3.67 3.86 3.86 3.67 3.85 ns LVTTL_S8 1.31 1.42 1.64 1.64 1.42 1.51 3.50 3.64 3.73 3.73 3.64 3.86 3.26 3.40 3.60 3.60 3.40 3.58 ns LVTTL_S12 1.31 1.42 1.64 1.64 1.42 1.51 3.49 3.62 3.72 3.72 3.62 3.84 3.24 3.39 3.58 3.58 3.39 3.56 ns LVTTL_S16 1.31 1.42 1.64 1.64 1.42 1.51 3.03 3.17 3.26 3.26 3.17 3.39 2.79 2.93 3.13 3.13 2.93 3.11 ns LVTTL_S24 1.31 1.42 1.64 1.64 1.42 1.51 3.25 3.39 3.48 3.48 3.39 3.61 3.01 3.15 3.35 3.35 3.15 3.33 ns LVTTL_F4 1.31 1.42 1.64 1.64 1.42 1.51 3.22 3.36 3.45 3.45 3.36 3.58 2.98 3.12 3.32 3.32 3.12 3.30 ns LVTTL_F8 1.31 1.42 1.64 1.64 1.42 1.51 2.71 2.84 2.93 2.93 2.84 3.06 2.46 2.61 2.80 2.80 2.61 2.78 ns LVTTL_F12 1.31 1.42 1.64 1.64 1.42 1.51 2.69 2.82 2.92 2.92 2.82 3.05 2.44 2.59 2.79 2.79 2.59 2.77 ns LVTTL_F16 1.31 1.42 1.64 1.64 1.42 1.51 2.57 2.85 3.15 3.15 2.85 2.88 2.33 2.61 3.02 3.02 2.61 2.60 ns LVTTL_F24 1.31 1.42 1.64 1.64 1.42 1.51 2.41 2.64 2.89 3.04 2.64 2.94 2.16 2.41 2.76 2.91 2.41 2.66 ns LVDS_25 0.64 0.68 0.80 0.87 0.68 0.83 1.36 1.47 1.55 1.55 1.47 1.58 1.11 1.24 1.41 1.41 1.24 1.30 ns MINI_LVDS_25 0.68 0.70 0.79 0.87 0.70 0.83 1.36 1.47 1.55 1.55 1.47 1.59 1.11 1.24 1.41 1.41 1.24 1.31 ns BLVDS_25 0.65 0.69 0.80 0.85 0.69 0.83 1.83 2.02 2.20 2.57 2.02 2.16 1.59 1.79 2.07 2.44 1.79 1.88 ns RSDS_25 0.63 0.68 0.79 0.87 0.68 0.83 1.36 1.48 1.55 1.55 1.48 1.59 1.11 1.24 1.41 1.41 1.24 1.31 ns (point to point) PPDS_25 0.65 0.69 0.80 0.87 0.69 0.83 1.36 1.49 1.58 1.58 1.49 1.59 1.11 1.25 1.45 1.45 1.25 1.31 ns TMDS_33 0.72 0.76 0.86 0.90 0.76 0.83 1.43 1.54 1.60 1.60 1.54 1.70 1.18 1.31 1.47 1.47 1.31 1.42 ns PCI33_3 1.28 1.41 1.65 1.65 1.41 1.50 2.71 3.08 3.52 3.52 3.08 3.42 2.46 2.84 3.39 3.39 2.84 3.14 ns HSUL_12_S 0.63 0.64 0.71 0.85 0.64 0.79 1.77 1.90 2.00 2.00 1.90 2.13 1.52 1.67 1.86 1.86 1.67 1.85 ns HSUL_12_F 0.63 0.64 0.71 0.85 0.64 0.79 1.26 1.40 1.50 1.50 1.40 1.61 1.01 1.16 1.37 1.37 1.16 1.33 ns DIFF_HSUL_ 0.58 0.61 0.70 0.84 0.61 0.81 1.55 1.68 1.78 1.78 1.68 1.92 1.30 1.45 1.65 1.65 1.45 1.64 ns 12_S DIFF_HSUL_ 0.58 0.61 0.70 0.84 0.61 0.81 1.16 1.28 1.35 1.35 1.28 1.50 0.92 1.04 1.21 1.21 1.04 1.22 ns 12_F MOBILE_DDR_S 0.64 0.66 0.74 0.74 0.66 0.89 2.58 2.91 3.31 3.31 2.91 1.95 2.33 2.68 3.17 3.17 2.68 1.67 ns MOBILE_DDR_F 0.64 0.66 0.74 0.74 0.66 0.89 1.91 2.13 2.36 2.36 2.13 1.69 1.66 1.89 2.23 2.23 1.89 1.41 ns DIFF_MOBILE_ 0.63 0.66 0.75 0.75 0.66 0.79 2.51 2.84 3.24 3.24 2.84 1.95 2.26 2.61 3.10 3.10 2.61 1.67 ns DDR_S DIFF_MOBILE_ 0.63 0.66 0.75 0.75 0.66 0.79 1.89 2.11 2.34 2.34 2.11 1.72 1.64 1.88 2.21 2.21 1.88 1.44 ns DDR_F DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 17

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics Table 20: IOB High Range (HR) Switching Characteristics (Cont’d) T T T IOPI IOOP IOTP Speed Grade Speed Grade Speed Grade I/OStandard Units 1.0V 0.95V 0.9V 1.0V 0.95V 0.9V 1.0V 0.95V 0.9V -2/ -1M/ -2/ -1M/ -2/ -1M/ -3 -1 -2LI -2LE -3 -1 -2LI -2LE -3 -1 -2LI -2LE -2LE -1LM -2LE -1LM -2LE -1LM HSTL_I_S 0.61 0.64 0.73 0.84 0.64 0.79 1.55 1.69 1.80 1.80 1.69 1.91 1.30 1.46 1.67 1.67 1.46 1.63 ns HSTL_II_S 0.61 0.64 0.73 0.84 0.64 0.78 1.21 1.34 1.43 1.61 1.34 1.70 0.96 1.11 1.30 1.47 1.11 1.42 ns HSTL_I_18_S 0.64 0.67 0.76 0.85 0.67 0.79 1.28 1.39 1.45 1.45 1.39 1.58 1.04 1.16 1.31 1.32 1.16 1.30 ns HSTL_II_18_S 0.64 0.67 0.76 0.85 0.67 0.79 1.18 1.31 1.40 1.57 1.31 1.69 0.93 1.08 1.27 1.44 1.08 1.41 ns DIFF_HSTL_I_S 0.63 0.67 0.77 0.84 0.67 0.78 1.42 1.54 1.61 1.78 1.54 1.84 1.17 1.31 1.48 1.65 1.31 1.56 ns DIFF_HSTL_II_S 0.63 0.67 0.77 0.84 0.67 0.79 1.15 1.24 1.27 1.61 1.24 1.78 0.91 1.01 1.14 1.47 1.01 1.50 ns DIFF_HSTL_I_ 0.65 0.69 0.78 0.84 0.69 0.79 1.27 1.38 1.43 1.45 1.38 1.67 1.03 1.14 1.30 1.32 1.14 1.39 ns 18_S DIFF_HSTL_II_ 0.65 0.69 0.78 0.85 0.69 0.81 1.14 1.23 1.26 1.57 1.23 1.72 0.90 1.00 1.13 1.44 1.00 1.44 ns 18_S HSTL_I_F 0.61 0.64 0.73 0.84 0.64 0.79 1.10 1.19 1.23 1.31 1.19 1.41 0.85 0.96 1.10 1.18 0.96 1.13 ns HSTL_II_F 0.61 0.64 0.73 0.84 0.64 0.78 1.05 1.18 1.28 1.31 1.18 1.42 0.80 0.95 1.15 1.18 0.95 1.14 ns HSTL_I_18_F 0.64 0.67 0.76 0.85 0.67 0.79 1.05 1.18 1.28 1.36 1.18 1.44 0.80 0.95 1.15 1.22 0.95 1.16 ns HSTL_II_18_F 0.64 0.67 0.76 0.85 0.67 0.79 1.03 1.14 1.23 1.32 1.14 1.42 0.78 0.90 1.10 1.19 0.90 1.14 ns DIFF_HSTL_I_F 0.63 0.67 0.77 0.84 0.67 0.78 1.09 1.18 1.22 1.31 1.18 1.48 0.84 0.95 1.09 1.18 0.95 1.20 ns DIFF_HSTL_II_F 0.63 0.67 0.77 0.84 0.67 0.79 1.02 1.11 1.14 1.31 1.11 1.48 0.77 0.88 1.01 1.18 0.88 1.20 ns DIFF_HSTL_I_ 0.65 0.69 0.78 0.84 0.69 0.79 1.08 1.17 1.21 1.36 1.17 1.48 0.83 0.94 1.07 1.22 0.94 1.20 ns 18_F DIFF_HSTL_II_ 0.65 0.69 0.78 0.85 0.69 0.81 1.01 1.10 1.13 1.32 1.10 1.48 0.76 0.87 1.00 1.19 0.87 1.20 ns 18_F LVCMOS33_S4 1.31 1.40 1.60 1.60 1.40 1.54 3.77 3.90 4.00 4.00 3.90 4.13 3.52 3.67 3.86 3.86 3.67 3.85 ns LVCMOS33_S8 1.31 1.40 1.60 1.60 1.40 1.54 3.49 3.62 3.72 3.72 3.62 3.84 3.24 3.39 3.58 3.58 3.39 3.56 ns LVCMOS33_S12 1.31 1.40 1.60 1.60 1.40 1.54 3.05 3.18 3.28 3.28 3.18 3.41 2.80 2.95 3.15 3.15 2.95 3.13 ns LVCMOS33_S16 1.31 1.40 1.60 1.60 1.40 1.54 3.06 3.43 3.88 3.88 3.43 3.72 2.81 3.20 3.75 3.75 3.20 3.44 ns LVCMOS33_F4 1.31 1.40 1.60 1.60 1.40 1.54 3.22 3.36 3.45 3.45 3.36 3.58 2.98 3.12 3.32 3.32 3.12 3.30 ns LVCMOS33_F8 1.31 1.40 1.60 1.60 1.40 1.54 2.71 2.84 2.93 2.93 2.84 3.06 2.46 2.61 2.80 2.80 2.61 2.78 ns LVCMOS33_F12 1.31 1.40 1.60 1.60 1.40 1.54 2.57 2.85 3.15 3.15 2.85 2.88 2.33 2.61 3.02 3.02 2.61 2.60 ns LVCMOS33_F16 1.31 1.40 1.60 1.60 1.40 1.54 2.44 2.69 2.96 2.96 2.69 2.88 2.19 2.45 2.82 2.82 2.45 2.60 ns LVCMOS25_S4 1.08 1.16 1.32 1.35 1.16 1.36 3.08 3.22 3.31 3.31 3.22 3.44 2.84 2.98 3.18 3.18 2.98 3.16 ns LVCMOS25_S8 1.08 1.16 1.32 1.35 1.16 1.36 2.85 2.98 3.07 3.08 2.98 3.20 2.60 2.75 2.94 2.94 2.75 2.92 ns LVCMOS25_S12 1.08 1.16 1.32 1.35 1.16 1.36 2.44 2.57 2.67 2.67 2.57 2.80 2.19 2.34 2.54 2.54 2.34 2.52 ns LVCMOS25_S16 1.08 1.16 1.32 1.35 1.16 1.36 2.79 2.92 3.01 3.01 2.92 3.14 2.54 2.68 2.88 2.88 2.68 2.86 ns LVCMOS25_F4 1.08 1.16 1.32 1.35 1.16 1.36 2.71 2.84 2.93 2.93 2.84 3.06 2.46 2.61 2.80 2.80 2.61 2.78 ns LVCMOS25_F8 1.08 1.16 1.32 1.35 1.16 1.36 2.14 2.28 2.37 2.37 2.28 2.50 1.90 2.04 2.24 2.24 2.04 2.22 ns LVCMOS25_F12 1.08 1.16 1.32 1.35 1.16 1.36 2.15 2.29 2.52 2.52 2.29 2.48 1.91 2.05 2.38 2.38 2.05 2.20 ns LVCMOS25_F16 1.08 1.16 1.32 1.35 1.16 1.36 1.92 2.17 2.45 2.45 2.17 2.33 1.67 1.94 2.32 2.32 1.94 2.05 ns LVCMOS18_S4 0.64 0.66 0.74 0.95 0.66 0.87 1.55 1.68 1.78 1.78 1.68 1.91 1.30 1.45 1.65 1.65 1.45 1.63 ns LVCMOS18_S8 0.64 0.66 0.74 0.95 0.66 0.87 2.14 2.28 2.37 2.37 2.28 2.50 1.90 2.04 2.24 2.24 2.04 2.22 ns LVCMOS18_S12 0.64 0.66 0.74 0.95 0.66 0.87 2.14 2.28 2.37 2.37 2.28 2.50 1.90 2.04 2.24 2.24 2.04 2.22 ns LVCMOS18_S16 0.64 0.66 0.74 0.95 0.66 0.87 1.49 1.62 1.72 1.72 1.62 1.84 1.24 1.39 1.58 1.58 1.39 1.56 ns DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 18

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics Table 20: IOB High Range (HR) Switching Characteristics (Cont’d) T T T IOPI IOOP IOTP Speed Grade Speed Grade Speed Grade I/OStandard Units 1.0V 0.95V 0.9V 1.0V 0.95V 0.9V 1.0V 0.95V 0.9V -2/ -1M/ -2/ -1M/ -2/ -1M/ -3 -1 -2LI -2LE -3 -1 -2LI -2LE -3 -1 -2LI -2LE -2LE -1LM -2LE -1LM -2LE -1LM LVCMOS18_S24 0.64 0.66 0.74 0.95 0.66 0.87 1.74 1.92 2.08 2.22 1.92 1.92 1.50 1.69 1.95 2.08 1.69 1.64 ns LVCMOS18_F4 0.64 0.66 0.74 0.95 0.66 0.87 1.38 1.51 1.61 1.64 1.51 1.77 1.13 1.28 1.47 1.50 1.28 1.49 ns LVCMOS18_F8 0.64 0.66 0.74 0.95 0.66 0.87 1.64 1.78 1.87 1.87 1.78 2.00 1.40 1.54 1.74 1.74 1.54 1.72 ns LVCMOS18_F12 0.64 0.66 0.74 0.95 0.66 0.87 1.64 1.78 1.87 1.87 1.78 2.00 1.40 1.54 1.74 1.74 1.54 1.72 ns LVCMOS18_F16 0.64 0.66 0.74 0.95 0.66 0.87 1.52 1.68 1.81 1.81 1.68 1.72 1.28 1.45 1.68 1.68 1.45 1.44 ns LVCMOS18_F24 0.64 0.66 0.74 0.95 0.66 0.87 1.34 1.46 1.55 2.09 1.46 1.66 1.09 1.23 1.42 1.96 1.23 1.38 ns LVCMOS15_S4 0.66 0.69 0.81 0.93 0.69 0.90 1.86 2.00 2.09 2.09 2.00 2.22 1.62 1.76 1.96 1.96 1.76 1.94 ns LVCMOS15_S8 0.66 0.69 0.81 0.93 0.69 0.90 2.05 2.18 2.28 2.28 2.18 2.41 1.80 1.95 2.14 2.15 1.95 2.13 ns LVCMOS15_S12 0.66 0.69 0.81 0.93 0.69 0.90 1.83 2.03 2.23 2.23 2.03 1.91 1.59 1.80 2.10 2.10 1.80 1.63 ns LVCMOS15_S16 0.66 0.69 0.81 0.93 0.69 0.90 1.76 1.95 2.13 2.13 1.95 1.91 1.52 1.72 1.99 1.99 1.72 1.63 ns LVCMOS15_F4 0.66 0.69 0.81 0.93 0.69 0.90 1.63 1.76 1.86 1.86 1.76 1.98 1.38 1.53 1.72 1.72 1.53 1.70 ns LVCMOS15_F8 0.66 0.69 0.81 0.93 0.69 0.90 1.79 1.99 2.18 2.18 1.99 1.92 1.55 1.76 2.05 2.05 1.76 1.64 ns LVCMOS15_F12 0.66 0.69 0.81 0.93 0.69 0.90 1.40 1.54 1.65 1.65 1.54 1.67 1.15 1.31 1.52 1.52 1.31 1.39 ns LVCMOS15_F16 0.66 0.69 0.81 0.93 0.69 0.90 1.37 1.51 1.61 1.89 1.51 1.66 1.13 1.27 1.48 1.75 1.27 1.38 ns LVCMOS12_S4 0.88 0.91 1.00 1.17 0.91 1.01 2.53 2.67 2.76 2.76 2.67 2.89 2.29 2.43 2.63 2.63 2.43 2.61 ns LVCMOS12_S8 0.88 0.91 1.00 1.17 0.91 1.01 2.05 2.18 2.28 2.28 2.18 2.41 1.80 1.95 2.14 2.15 1.95 2.13 ns LVCMOS12_S12 0.88 0.91 1.00 1.17 0.91 1.01 1.75 1.89 1.98 1.98 1.89 2.11 1.51 1.65 1.85 1.85 1.65 1.83 ns LVCMOS12_F4 0.88 0.91 1.00 1.17 0.91 1.01 1.94 2.07 2.17 2.17 2.07 2.30 1.69 1.84 2.04 2.04 1.84 2.02 ns LVCMOS12_F8 0.88 0.91 1.00 1.17 0.91 1.01 1.50 1.64 1.73 1.73 1.64 1.86 1.26 1.40 1.60 1.60 1.40 1.58 ns LVCMOS12_F12 0.88 0.91 1.00 1.17 0.91 1.01 1.54 1.71 1.87 1.87 1.71 1.69 1.29 1.48 1.74 1.74 1.48 1.41 ns SSTL135_S 0.61 0.64 0.73 0.85 0.64 0.79 1.27 1.40 1.50 1.53 1.40 1.64 1.02 1.17 1.36 1.40 1.17 1.36 ns SSTL15_S 0.61 0.64 0.73 0.73 0.64 0.73 1.24 1.37 1.47 1.53 1.37 1.59 0.99 1.14 1.33 1.40 1.14 1.31 ns SSTL18_I_S 0.64 0.67 0.76 0.84 0.67 0.79 1.59 1.74 1.85 1.85 1.74 1.95 1.34 1.50 1.72 1.72 1.50 1.67 ns SSTL18_II_S 0.64 0.67 0.76 0.85 0.67 0.78 1.27 1.40 1.50 1.50 1.40 1.63 1.02 1.17 1.36 1.36 1.17 1.35 ns DIFF_SSTL135_ 0.59 0.61 0.73 0.85 0.61 0.79 1.27 1.40 1.50 1.53 1.40 1.64 1.02 1.17 1.36 1.40 1.17 1.36 ns S DIFF_SSTL15_S 0.63 0.67 0.77 0.85 0.67 0.79 1.24 1.37 1.47 1.53 1.37 1.59 0.99 1.14 1.33 1.40 1.14 1.31 ns DIFF_SSTL18_ 0.65 0.69 0.78 0.85 0.69 0.79 1.50 1.63 1.72 1.82 1.63 1.95 1.26 1.40 1.59 1.69 1.40 1.67 ns I_S DIFF_SSTL18_ 0.65 0.69 0.78 0.85 0.69 0.79 1.13 1.22 1.25 1.50 1.22 1.66 0.88 0.99 1.12 1.36 0.99 1.38 ns II_S DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 19

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics Table 20: IOB High Range (HR) Switching Characteristics (Cont’d) T T T IOPI IOOP IOTP Speed Grade Speed Grade Speed Grade I/OStandard Units 1.0V 0.95V 0.9V 1.0V 0.95V 0.9V 1.0V 0.95V 0.9V -2/ -1M/ -2/ -1M/ -2/ -1M/ -3 -1 -2LI -2LE -3 -1 -2LI -2LE -3 -1 -2LI -2LE -2LE -1LM -2LE -1LM -2LE -1LM SSTL135_F 0.61 0.64 0.73 0.85 0.64 0.79 1.04 1.17 1.26 1.31 1.17 1.42 0.79 0.93 1.13 1.18 0.93 1.14 ns SSTL15_F 0.61 0.64 0.73 0.73 0.64 0.73 1.04 1.17 1.26 1.26 1.17 1.39 0.79 0.93 1.13 1.13 0.93 1.11 ns SSTL18_I_F 0.64 0.67 0.76 0.84 0.67 0.79 1.12 1.22 1.26 1.34 1.22 1.44 0.88 0.99 1.13 1.21 0.99 1.16 ns SSTL18_II_F 0.64 0.67 0.76 0.85 0.67 0.78 1.05 1.18 1.28 1.32 1.18 1.42 0.80 0.95 1.15 1.19 0.95 1.14 ns DIFF_SSTL135_ ns 0.59 0.61 0.73 0.85 0.61 0.79 1.04 1.17 1.26 1.31 1.17 1.42 0.79 0.93 1.13 1.18 0.93 1.14 F DIFF_SSTL15_F 0.63 0.67 0.77 0.85 0.67 0.79 1.04 1.17 1.26 1.26 1.17 1.39 0.79 0.93 1.13 1.13 0.93 1.11 ns DIFF_SSTL18_I_ ns 0.65 0.69 0.78 0.85 0.69 0.79 1.10 1.19 1.23 1.34 1.19 1.52 0.85 0.96 1.10 1.21 0.96 1.24 F DIFF_SSTL18_II ns 0.65 0.69 0.78 0.85 0.69 0.79 1.02 1.10 1.14 1.32 1.10 1.50 0.77 0.87 1.00 1.19 0.87 1.22 _F DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 20

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics Table 21: IOB High Performance (HP) Switching Characteristics T T T IOPI IOOP IOTP Speed Grade Speed Grade Speed Grade I/OStandard Units 1.0V 0.95V 0.9V 1.0V 0.95V 0.9V 1.0V 0.95V 0.9V -2/ -1M/ -2/ -1M/ -2/ -1M/ -3 -1 -2LI -2LE -3 -1 -2LI -2LE -3 -1 -2LI -2LE -2LE -1LM -2LE -1LM -2LE -1LM LVDS 0.75 0.79 0.92 0.96 0.79 0.89 1.05 1.17 1.24 1.26 1.17 1.43 0.88 1.01 1.08 1.10 1.01 1.32 ns HSUL_12_S 0.69 0.72 0.82 0.98 0.72 0.95 1.65 1.84 2.05 2.05 1.84 1.80 1.48 1.68 1.89 1.89 1.68 1.70 ns HSUL_12_F 0.69 0.72 0.82 0.98 0.72 0.95 1.39 1.54 1.68 1.68 1.54 1.49 1.22 1.38 1.52 1.52 1.38 1.39 ns DIFF_HSUL_12_ 0.69 0.72 0.82 0.98 0.72 0.92 1.65 1.84 2.05 2.05 1.84 1.47 1.48 1.68 1.89 1.89 1.68 1.37 ns S DIFF_HSUL_12_F 0.69 0.72 0.82 0.98 0.72 0.92 1.39 1.54 1.68 1.68 1.54 1.35 1.22 1.38 1.52 1.52 1.38 1.24 ns DIFF_HSUL_12_ 0.69 0.72 0.82 0.82 0.72 0.92 1.78 1.91 2.05 2.05 1.91 1.46 1.61 1.76 1.89 1.89 1.76 1.35 ns DCI_S DIFF_HSUL_12_ 0.69 0.72 0.82 0.82 0.72 0.92 1.56 1.67 1.76 1.76 1.67 1.35 1.39 1.51 1.60 1.60 1.51 1.24 ns DCI_F HSTL_I_S 0.68 0.72 0.82 0.90 0.72 0.84 1.15 1.28 1.38 1.38 1.28 1.46 0.98 1.12 1.22 1.22 1.12 1.35 ns HSTL_II_S 0.68 0.72 0.82 0.90 0.72 0.84 1.05 1.17 1.26 1.27 1.17 1.44 0.88 1.01 1.10 1.11 1.01 1.34 ns HSTL_I_18_S 0.70 0.72 0.82 0.95 0.72 0.86 1.12 1.24 1.34 1.34 1.24 1.41 0.95 1.08 1.18 1.18 1.08 1.31 ns HSTL_II_18_S 0.70 0.72 0.82 0.90 0.72 0.86 1.06 1.18 1.26 1.27 1.18 1.44 0.89 1.02 1.10 1.11 1.02 1.34 ns HSTL_I_12_S 0.68 0.72 0.82 0.96 0.72 0.94 1.14 1.27 1.37 1.37 1.27 1.43 0.97 1.11 1.21 1.21 1.11 1.32 ns HSTL_I_DCI_S 0.68 0.72 0.82 0.90 0.72 0.78 1.11 1.23 1.33 1.33 1.23 1.36 0.94 1.07 1.17 1.17 1.07 1.26 ns HSTL_II_DCI_S 0.68 0.72 0.82 0.85 0.72 0.78 1.05 1.17 1.26 1.26 1.17 1.33 0.88 1.01 1.10 1.10 1.01 1.23 ns HSTL_II_T_DCI_ 0.70 0.72 0.82 0.82 0.72 0.76 1.15 1.28 1.38 1.38 1.28 1.40 0.98 1.12 1.22 1.22 1.12 1.29 ns S HSTL_I_DCI_18_ 0.70 0.72 0.82 0.90 0.72 0.76 1.11 1.23 1.33 1.33 1.23 1.36 0.94 1.07 1.17 1.17 1.07 1.26 ns S HSTL_II_DCI_18_ 0.70 0.72 0.82 0.82 0.72 0.76 1.05 1.16 1.24 1.24 1.16 1.32 0.88 1.00 1.08 1.08 1.00 1.21 ns S HSTL_II 0.70 0.72 0.82 0.84 0.72 0.76 1.11 1.23 1.33 1.34 1.23 1.36 0.94 1.07 1.17 1.18 1.07 1.26 ns _T_DCI_18_S DIFF_HSTL_I_S 0.75 0.79 0.92 1.02 0.79 0.89 1.15 1.28 1.38 1.38 1.28 1.47 0.98 1.12 1.22 1.22 1.12 1.37 ns DIFF_HSTL_II_S 0.75 0.79 0.92 1.02 0.79 0.89 1.05 1.17 1.26 1.32 1.17 1.47 0.88 1.01 1.10 1.16 1.01 1.37 ns DIFF_HSTL_I_ 0.75 0.79 0.92 0.92 0.79 0.76 1.15 1.28 1.38 1.38 1.28 1.47 0.98 1.12 1.22 1.22 1.12 1.37 ns DCI_S DIFF_HSTL_II_ 0.75 0.79 0.92 0.92 0.79 0.76 1.05 1.17 1.26 1.26 1.17 1.40 0.88 1.01 1.10 1.10 1.01 1.29 ns DCI_S DIFF_HSTL_I_ 0.75 0.79 0.92 0.98 0.79 0.89 1.12 1.24 1.34 1.34 1.24 1.46 0.95 1.08 1.18 1.18 1.08 1.35 ns 18_S DIFF_HSTL_II_ 0.75 0.79 0.92 0.99 0.79 0.89 1.06 1.18 1.26 1.32 1.18 1.47 0.89 1.02 1.10 1.16 1.02 1.37 ns 18_S DIFF_HSTL_I_ 0.75 0.79 0.92 0.92 0.79 0.75 1.11 1.23 1.33 1.33 1.23 1.46 0.94 1.07 1.17 1.17 1.07 1.35 ns DCI_18_S DIFF_HSTL_II_ 0.75 0.79 0.92 0.93 0.79 0.75 1.05 1.16 1.24 1.26 1.16 1.41 0.88 1.00 1.08 1.10 1.00 1.31 ns DCI_18_S DIFF_HSTL_II 0.75 0.79 0.92 0.92 0.79 0.76 1.11 1.23 1.33 1.33 1.23 1.46 0.94 1.07 1.17 1.17 1.07 1.35 ns _T_DCI_18_S HSTL_I_F 0.68 0.72 0.82 0.90 0.72 0.84 1.02 1.14 1.22 1.22 1.14 1.26 0.85 0.98 1.06 1.06 0.98 1.15 ns HSTL_II_F 0.68 0.72 0.82 0.90 0.72 0.84 0.97 1.08 1.15 1.15 1.08 1.29 0.80 0.92 0.99 0.99 0.92 1.18 ns HSTL_I_18_F 0.70 0.72 0.82 0.95 0.72 0.86 1.04 1.16 1.24 1.24 1.16 1.32 0.87 1.00 1.08 1.08 1.00 1.21 ns DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 21

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics Table 21: IOB High Performance (HP) Switching Characteristics (Cont’d) T T T IOPI IOOP IOTP Speed Grade Speed Grade Speed Grade I/OStandard Units 1.0V 0.95V 0.9V 1.0V 0.95V 0.9V 1.0V 0.95V 0.9V -2/ -1M/ -2/ -1M/ -2/ -1M/ -3 -1 -2LI -2LE -3 -1 -2LI -2LE -3 -1 -2LI -2LE -2LE -1LM -2LE -1LM -2LE -1LM HSTL_II_18_F 0.70 0.72 0.82 0.90 0.72 0.86 0.98 1.09 1.16 1.20 1.09 1.35 0.81 0.94 1.00 1.03 0.94 1.24 ns HSTL_I_12_F 0.68 0.72 0.82 0.96 0.72 0.94 1.02 1.13 1.21 1.21 1.13 1.26 0.85 0.97 1.05 1.05 0.97 1.15 ns HSTL_I_DCI_F 0.68 0.72 0.82 0.90 0.72 0.78 1.04 1.16 1.24 1.24 1.16 1.30 0.87 1.00 1.08 1.08 1.00 1.20 ns HSTL_II_DCI_F 0.68 0.72 0.82 0.85 0.72 0.78 0.97 1.08 1.15 1.15 1.08 1.22 0.80 0.92 0.99 0.99 0.92 1.12 ns HSTL_II_T_DCI_F 0.70 0.72 0.82 0.82 0.72 0.76 1.02 1.14 1.22 1.22 1.14 1.26 0.85 0.98 1.06 1.06 0.98 1.15 ns HSTL_I_DCI_ 0.70 0.72 0.82 0.90 0.72 0.76 1.04 1.16 1.24 1.24 1.16 1.30 0.87 1.00 1.08 1.08 1.00 1.20 ns 18_F HSTL_II_DCI_ 0.70 0.72 0.82 0.82 0.72 0.76 0.98 1.09 1.16 1.16 1.09 1.27 0.81 0.93 1.00 1.00 0.93 1.17 ns 18_F HSTL_II 0.70 0.72 0.82 0.84 0.72 0.76 1.04 1.16 1.24 1.24 1.16 1.30 0.87 1.00 1.08 1.08 1.00 1.20 ns _T_DCI_18_F DIFF_HSTL_I_F 0.75 0.79 0.92 1.02 0.79 0.89 1.02 1.14 1.22 1.22 1.14 1.35 0.85 0.98 1.06 1.06 0.98 1.24 ns DIFF_HSTL_II_F 0.75 0.79 0.92 1.02 0.79 0.89 0.97 1.08 1.15 1.20 1.08 1.35 0.80 0.92 0.99 1.03 0.92 1.24 ns DIFF_HSTL_I_ 0.75 0.79 0.92 0.92 0.79 0.76 1.02 1.14 1.22 1.22 1.14 1.35 0.85 0.98 1.06 1.06 0.98 1.24 ns DCI_F DIFF_HSTL_II_ 0.75 0.79 0.92 0.92 0.79 0.76 0.97 1.08 1.15 1.15 1.08 1.30 0.80 0.92 0.99 0.99 0.92 1.20 ns DCI_F DIFF_HSTL_I_ 0.75 0.79 0.92 0.98 0.79 0.89 1.04 1.16 1.24 1.24 1.16 1.38 0.87 1.00 1.08 1.08 1.00 1.28 ns 18_F DIFF_HSTL_II_ 0.75 0.79 0.92 0.99 0.79 0.89 0.98 1.09 1.16 1.24 1.09 1.40 0.81 0.94 1.00 1.08 0.94 1.29 ns 18_F DIFF_HSTL_I_ 0.75 0.79 0.92 0.92 0.79 0.75 1.04 1.16 1.24 1.24 1.16 1.38 0.87 1.00 1.08 1.08 1.00 1.28 ns DCI_18_F DIFF_HSTL_II_ 0.75 0.79 0.92 0.93 0.79 0.75 0.98 1.09 1.16 1.18 1.09 1.33 0.81 0.93 1.00 1.02 0.93 1.23 ns DCI_18_F DIFF_HSTL_II 0.75 0.79 0.92 0.92 0.79 0.76 1.04 1.16 1.24 1.24 1.16 1.38 0.87 1.00 1.08 1.08 1.00 1.28 ns _T_DCI_18_F LVCMOS18_S2 0.47 0.50 0.60 0.90 0.50 0.87 3.95 4.28 4.85 4.85 4.28 3.40 3.78 4.13 4.69 4.69 4.13 3.29 ns LVCMOS18_S4 0.47 0.50 0.60 0.90 0.50 0.87 2.67 2.98 3.43 3.43 2.98 2.69 2.50 2.82 3.27 3.27 2.82 2.59 ns LVCMOS18_S6 0.47 0.50 0.60 0.90 0.50 0.87 2.14 2.38 2.72 2.72 2.38 2.18 1.97 2.22 2.56 2.56 2.22 2.07 ns LVCMOS18_S8 0.47 0.50 0.60 0.90 0.50 0.87 1.98 2.21 2.52 2.52 2.21 2.02 1.81 2.05 2.36 2.36 2.05 1.92 ns LVCMOS18_S12 0.47 0.50 0.60 0.90 0.50 0.87 1.70 1.91 2.17 2.17 1.91 1.85 1.53 1.75 2.01 2.01 1.75 1.74 ns LVCMOS18_S16 0.47 0.50 0.60 0.90 0.50 0.87 1.57 1.75 1.97 1.97 1.75 1.76 1.40 1.59 1.81 1.81 1.59 1.65 ns LVCMOS18_F2 0.47 0.50 0.60 0.90 0.50 0.87 3.50 3.87 4.48 4.48 3.87 2.85 3.33 3.71 4.32 4.32 3.71 2.74 ns LVCMOS18_F4 0.47 0.50 0.60 0.90 0.50 0.87 2.23 2.50 2.87 2.87 2.50 2.26 2.06 2.34 2.71 2.71 2.34 2.15 ns LVCMOS18_F6 0.47 0.50 0.60 0.90 0.50 0.87 1.80 2.00 2.26 2.26 2.00 1.52 1.63 1.84 2.09 2.09 1.84 1.42 ns LVCMOS18_F8 0.47 0.50 0.60 0.90 0.50 0.87 1.46 1.72 2.04 2.04 1.72 1.51 1.29 1.56 1.88 1.88 1.56 1.40 ns LVCMOS18_F12 0.47 0.50 0.60 0.90 0.50 0.87 1.26 1.40 1.53 1.53 1.40 1.46 1.09 1.24 1.37 1.37 1.24 1.35 ns LVCMOS18_F16 0.47 0.50 0.60 0.90 0.50 0.87 1.19 1.33 1.44 1.66 1.33 1.46 1.02 1.17 1.28 1.50 1.17 1.35 ns LVCMOS15_S2 0.59 0.62 0.73 0.88 0.62 0.86 3.55 3.89 4.45 4.45 3.89 3.11 3.38 3.73 4.29 4.29 3.73 3.01 ns LVCMOS15_S4 0.59 0.62 0.73 0.88 0.62 0.86 2.45 2.70 3.06 3.06 2.70 2.46 2.28 2.54 2.90 2.90 2.54 2.35 ns LVCMOS15_S6 0.59 0.62 0.73 0.88 0.62 0.86 2.24 2.51 2.88 2.88 2.51 2.33 2.07 2.35 2.72 2.72 2.35 2.23 ns DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 22

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics Table 21: IOB High Performance (HP) Switching Characteristics (Cont’d) T T T IOPI IOOP IOTP Speed Grade Speed Grade Speed Grade I/OStandard Units 1.0V 0.95V 0.9V 1.0V 0.95V 0.9V 1.0V 0.95V 0.9V -2/ -1M/ -2/ -1M/ -2/ -1M/ -3 -1 -2LI -2LE -3 -1 -2LI -2LE -3 -1 -2LI -2LE -2LE -1LM -2LE -1LM -2LE -1LM LVCMOS15_S8 0.59 0.62 0.73 0.88 0.62 0.86 1.91 2.16 2.49 2.49 2.16 2.05 1.74 2.00 2.32 2.32 2.00 1.95 ns LVCMOS15_S12 0.59 0.62 0.73 0.88 0.62 0.86 1.77 1.98 2.23 2.23 1.98 1.97 1.60 1.82 2.07 2.07 1.82 1.87 ns LVCMOS15_S16 0.59 0.62 0.73 0.88 0.62 0.86 1.62 1.81 2.02 2.02 1.81 1.85 1.45 1.65 1.86 1.86 1.65 1.74 ns LVCMOS15_F2 0.59 0.62 0.73 0.88 0.62 0.86 3.38 3.69 4.18 4.18 3.69 2.74 3.21 3.53 4.02 4.02 3.53 2.64 ns LVCMOS15_F4 0.59 0.62 0.73 0.88 0.62 0.86 2.04 2.21 2.44 2.44 2.21 1.72 1.87 2.06 2.27 2.27 2.06 1.62 ns LVCMOS15_F6 0.59 0.62 0.73 0.88 0.62 0.86 1.47 1.74 2.09 2.09 1.74 1.49 1.30 1.58 1.93 1.93 1.58 1.39 ns LVCMOS15_F8 0.59 0.62 0.73 0.88 0.62 0.86 1.31 1.46 1.61 1.61 1.46 1.47 1.14 1.30 1.45 1.45 1.30 1.37 ns LVCMOS15_F12 0.59 0.62 0.73 0.88 0.62 0.86 1.21 1.34 1.45 1.45 1.34 1.44 1.04 1.18 1.29 1.29 1.18 1.34 ns LVCMOS15_F16 0.59 0.62 0.73 0.88 0.62 0.86 1.18 1.31 1.41 1.68 1.31 1.41 1.01 1.15 1.25 1.52 1.15 1.31 ns LVCMOS12_S2 0.64 0.67 0.78 1.04 0.67 0.95 3.38 3.80 4.48 4.48 3.80 3.27 3.21 3.64 4.31 4.31 3.64 3.17 ns LVCMOS12_S4 0.64 0.67 0.78 1.04 0.67 0.95 2.62 2.94 3.43 3.43 2.94 2.76 2.45 2.78 3.27 3.27 2.78 2.65 ns LVCMOS12_S6 0.64 0.67 0.78 1.04 0.67 0.95 2.05 2.33 2.72 2.72 2.33 2.24 1.88 2.17 2.56 2.56 2.17 2.14 ns LVCMOS12_S8 0.64 0.67 0.78 1.04 0.67 0.95 1.94 2.18 2.51 2.51 2.18 2.16 1.77 2.02 2.34 2.34 2.02 2.06 ns LVCMOS12_F2 0.64 0.67 0.78 1.04 0.67 0.95 2.84 3.15 3.62 3.62 3.15 2.47 2.67 2.99 3.46 3.46 2.99 2.37 ns LVCMOS12_F4 0.64 0.67 0.78 1.04 0.67 0.95 1.97 2.18 2.44 2.44 2.18 1.69 1.80 2.02 2.28 2.28 2.02 1.59 ns LVCMOS12_F6 0.64 0.67 0.78 1.04 0.67 0.95 1.33 1.51 1.70 1.70 1.51 1.43 1.16 1.35 1.54 1.54 1.35 1.32 ns LVCMOS12_F8 0.64 0.67 0.78 1.04 0.67 0.95 1.27 1.42 1.55 1.55 1.42 1.41 1.10 1.26 1.39 1.39 1.26 1.31 ns LVDCI_18 0.47 0.50 0.60 0.87 0.50 0.86 1.99 2.15 2.35 2.35 2.15 2.44 1.82 1.99 2.19 2.19 1.99 2.34 ns LVDCI_15 0.59 0.62 0.73 0.92 0.62 0.87 1.98 2.23 2.58 2.58 2.23 2.40 1.81 2.07 2.41 2.41 2.07 2.29 ns LVDCI_DV2_18 0.47 0.50 0.60 0.88 0.50 0.87 1.99 2.15 2.34 2.34 2.15 1.86 1.82 1.99 2.18 2.18 1.99 1.76 ns LVDCI_DV2_15 0.59 0.62 0.73 0.88 0.62 0.87 1.98 2.23 2.58 2.58 2.23 1.83 1.81 2.07 2.41 2.41 2.07 1.73 ns HSLVDCI_18 0.68 0.72 0.82 0.90 0.72 0.86 1.99 2.15 2.35 2.35 2.15 2.43 1.82 1.99 2.19 2.19 1.99 2.32 ns HSLVDCI_15 0.68 0.72 0.82 0.93 0.72 0.84 1.98 2.23 2.58 2.58 2.23 2.27 1.81 2.07 2.41 2.41 2.07 2.17 ns SSTL18_I_S 0.68 0.72 0.82 0.95 0.72 0.86 1.02 1.15 1.24 1.24 1.15 1.41 0.85 0.99 1.08 1.08 0.99 1.31 ns SSTL18_II_S 0.68 0.72 0.82 1.01 0.72 0.87 1.17 1.29 1.37 1.38 1.29 1.55 1.00 1.13 1.21 1.22 1.13 1.45 ns SSTL18_I_DCI_S 0.68 0.72 0.82 0.87 0.72 0.76 0.92 1.06 1.17 1.18 1.06 1.32 0.75 0.90 1.01 1.02 0.90 1.21 ns SSTL18_II_DCI_S 0.68 0.72 0.82 0.82 0.72 0.78 0.88 0.98 1.08 1.12 0.98 1.26 0.71 0.83 0.92 0.96 0.83 1.15 ns SSTL18_II_T_ 0.68 0.72 0.82 0.98 0.72 0.78 0.92 1.06 1.17 1.18 1.06 1.32 0.75 0.90 1.01 1.02 0.90 1.21 ns DCI_S SSTL15_S 0.68 0.72 0.82 0.82 0.72 0.81 0.94 1.06 1.15 1.16 1.06 1.32 0.77 0.91 0.99 1.00 0.91 1.21 ns SSTL15_DCI_S 0.68 0.72 0.82 0.90 0.72 0.78 0.94 1.06 1.15 1.16 1.06 1.30 0.77 0.90 0.99 1.00 0.90 1.20 ns SSTL15_T_DCI_S 0.68 0.72 0.82 0.87 0.72 0.80 0.94 1.06 1.15 1.15 1.06 1.30 0.77 0.90 0.99 0.99 0.90 1.20 ns SSTL135_S 0.69 0.72 0.82 0.93 0.72 0.89 0.97 1.10 1.19 1.20 1.10 1.35 0.80 0.94 1.03 1.03 0.94 1.24 ns SSTL135_DCI_S 0.69 0.72 0.82 0.85 0.72 0.84 0.97 1.09 1.19 1.20 1.09 1.33 0.80 0.93 1.03 1.03 0.93 1.23 ns SSTL135_T_ 0.69 0.72 0.82 0.93 0.72 0.84 0.97 1.09 1.19 1.20 1.09 1.33 0.80 0.93 1.03 1.03 0.93 1.23 ns DCI_S SSTL12_S 0.69 0.72 0.82 1.02 0.72 0.95 0.96 1.09 1.18 1.18 1.09 1.33 0.79 0.93 1.02 1.02 0.93 1.23 ns SSTL12_DCI_S 0.69 0.72 0.82 0.90 0.72 0.91 1.03 1.17 1.27 1.27 1.17 1.33 0.86 1.01 1.11 1.11 1.01 1.23 ns SSTL12_T_DCI_S 0.69 0.72 0.82 0.88 0.72 0.91 1.03 1.17 1.27 1.27 1.17 1.33 0.86 1.01 1.11 1.11 1.01 1.23 ns DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 23

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics Table 21: IOB High Performance (HP) Switching Characteristics (Cont’d) T T T IOPI IOOP IOTP Speed Grade Speed Grade Speed Grade I/OStandard Units 1.0V 0.95V 0.9V 1.0V 0.95V 0.9V 1.0V 0.95V 0.9V -2/ -1M/ -2/ -1M/ -2/ -1M/ -3 -1 -2LI -2LE -3 -1 -2LI -2LE -3 -1 -2LI -2LE -2LE -1LM -2LE -1LM -2LE -1LM DIFF_SSTL18_ 0.75 0.79 0.92 0.99 0.79 0.89 1.02 1.15 1.24 1.29 1.15 1.43 0.85 0.99 1.08 1.13 0.99 1.32 ns I_S DIFF_SSTL18_ 0.75 0.79 0.92 0.93 0.79 0.89 1.17 1.29 1.37 1.40 1.29 1.55 1.00 1.13 1.21 1.24 1.13 1.45 ns II_S DIFF_SSTL18_ 0.75 0.79 0.92 0.92 0.79 0.76 0.92 1.06 1.17 1.24 1.06 1.40 0.75 0.90 1.01 1.08 0.90 1.29 ns I_DCI_S DIFF_SSTL18_ 0.75 0.79 0.92 0.96 0.79 0.75 0.88 0.98 1.08 1.18 0.98 1.33 0.71 0.83 0.92 1.02 0.83 1.23 ns II_DCI_S DIFF_SSTL18_ 0.75 0.79 0.92 0.92 0.79 0.76 0.92 1.06 1.17 1.24 1.06 1.40 0.75 0.90 1.01 1.08 0.90 1.29 ns II_T_DCI_S DIFF_SSTL15_S 0.68 0.72 0.82 0.99 0.72 0.89 0.94 1.06 1.15 1.16 1.06 1.32 0.77 0.91 0.99 1.00 0.91 1.21 ns DIFF_SSTL15_ 0.68 0.72 0.82 0.96 0.72 0.75 0.94 1.06 1.15 1.16 1.06 1.30 0.77 0.90 0.99 1.00 0.90 1.20 ns DCI_S DIFF_SSTL15_T_ 0.68 0.72 0.82 0.88 0.72 0.76 0.94 1.06 1.15 1.23 1.06 1.38 0.77 0.90 0.99 1.07 0.90 1.28 ns DCI_S DIFF_SSTL135_S 0.69 0.72 0.82 1.09 0.72 0.91 0.97 1.10 1.19 1.20 1.10 1.35 0.80 0.94 1.03 1.03 0.94 1.24 ns DIFF_SSTL135_D 0.69 0.72 0.82 0.90 0.72 0.76 0.97 1.09 1.19 1.20 1.09 1.33 0.80 0.93 1.03 1.03 0.93 1.23 ns CI_S DIFF_SSTL135_ 0.69 0.72 0.82 0.84 0.72 0.76 0.97 1.09 1.19 1.27 1.09 1.43 0.80 0.93 1.03 1.11 0.93 1.32 ns T_DCI_S DIFF_SSTL12_S 0.69 0.72 0.82 0.96 0.72 0.91 0.96 1.09 1.18 1.18 1.09 1.33 0.79 0.93 1.02 1.02 0.93 1.23 ns DIFF_SSTL12_ 0.69 0.72 0.82 0.87 0.72 0.78 1.03 1.17 1.27 1.27 1.17 1.33 0.86 1.01 1.11 1.11 1.01 1.23 ns DCI_S DIFF_SSTL12_ 0.69 0.72 0.82 0.96 0.72 0.80 1.03 1.17 1.27 1.27 1.17 1.41 0.86 1.01 1.11 1.11 1.01 1.31 ns T_DCI_S SSTL18_I_F 0.68 0.72 0.82 0.95 0.72 0.86 0.94 1.06 1.15 1.15 1.06 1.32 0.77 0.91 0.99 0.99 0.91 1.21 ns SSTL18_II_F 0.68 0.72 0.82 1.01 0.72 0.87 0.97 1.09 1.16 1.21 1.09 1.36 0.80 0.93 1.00 1.05 0.93 1.26 ns SSTL18_I_DCI_F 0.68 0.72 0.82 0.87 0.72 0.76 0.89 1.02 1.10 1.15 1.02 1.30 0.72 0.86 0.94 0.99 0.86 1.20 ns SSTL18_II_DCI_F 0.68 0.72 0.82 0.82 0.72 0.78 0.89 1.02 1.10 1.10 1.02 1.24 0.72 0.86 0.94 0.94 0.86 1.14 ns SSTL18_II_T_ 0.68 0.72 0.82 0.98 0.72 0.78 0.89 1.02 1.10 1.15 1.02 1.27 0.72 0.86 0.94 0.99 0.86 1.17 ns DCI_F SSTL15_F 0.68 0.72 0.82 0.82 0.72 0.81 0.89 1.01 1.09 1.09 1.01 1.24 0.72 0.85 0.93 0.93 0.85 1.14 ns SSTL15_DCI_F 0.68 0.72 0.82 0.90 0.72 0.78 0.89 1.01 1.09 1.12 1.01 1.27 0.72 0.85 0.93 0.96 0.85 1.17 ns SSTL15_T_DCI_F 0.68 0.72 0.82 0.87 0.72 0.80 0.89 1.01 1.09 1.12 1.01 1.27 0.72 0.85 0.93 0.96 0.85 1.17 ns SSTL135_F 0.69 0.72 0.82 0.93 0.72 0.89 0.88 1.00 1.08 1.12 1.00 1.27 0.71 0.85 0.92 0.96 0.85 1.17 ns SSTL135_DCI_F 0.69 0.72 0.82 0.85 0.72 0.84 0.89 1.00 1.08 1.12 1.00 1.27 0.72 0.85 0.92 0.96 0.85 1.17 ns SSTL135_T_ 0.69 0.72 0.82 0.93 0.72 0.84 0.89 1.00 1.08 1.12 1.00 1.27 0.72 0.85 0.92 0.96 0.85 1.17 ns DCI_F SSTL12_F 0.69 0.72 0.82 1.02 0.72 0.95 0.88 1.00 1.08 1.12 1.00 1.26 0.71 0.84 0.92 0.96 0.84 1.15 ns SSTL12_DCI_F 0.69 0.72 0.82 0.90 0.72 0.91 0.91 1.03 1.11 1.11 1.03 1.24 0.74 0.88 0.95 0.95 0.88 1.14 ns SSTL12_T_DCI_F 0.69 0.72 0.82 0.88 0.72 0.91 0.91 1.03 1.11 1.12 1.03 1.26 0.74 0.88 0.95 0.96 0.88 1.15 ns DIFF_SSTL18_ 0.75 0.79 0.92 0.99 0.79 0.89 0.94 1.06 1.15 1.23 1.06 1.38 0.77 0.91 0.99 1.07 0.91 1.28 ns I_F DIFF_SSTL18_ 0.75 0.79 0.92 0.93 0.79 0.89 0.97 1.09 1.16 1.24 1.09 1.40 0.80 0.93 1.00 1.08 0.93 1.29 ns II_F DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 24

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics Table 21: IOB High Performance (HP) Switching Characteristics (Cont’d) T T T IOPI IOOP IOTP Speed Grade Speed Grade Speed Grade I/OStandard Units 1.0V 0.95V 0.9V 1.0V 0.95V 0.9V 1.0V 0.95V 0.9V -2/ -1M/ -2/ -1M/ -2/ -1M/ -3 -1 -2LI -2LE -3 -1 -2LI -2LE -3 -1 -2LI -2LE -2LE -1LM -2LE -1LM -2LE -1LM DIFF_SSTL18_I_ 0.75 0.79 0.92 0.92 0.79 0.76 0.89 1.02 1.10 1.23 1.02 1.36 0.72 0.86 0.94 1.07 0.86 1.26 ns DCI_F DIFF_SSTL18_II_ 0.75 0.79 0.92 0.96 0.79 0.75 0.89 1.02 1.10 1.16 1.02 1.32 0.72 0.86 0.94 1.00 0.86 1.21 ns DCI_F DIFF_SSTL18_II_ 0.75 0.79 0.92 0.92 0.79 0.76 0.89 1.02 1.10 1.24 1.02 1.38 0.72 0.86 0.94 1.08 0.86 1.28 ns T_DCI_F DIFF_SSTL15_F 0.68 0.72 0.82 0.99 0.72 0.89 0.89 1.01 1.09 1.09 1.01 1.24 0.72 0.85 0.93 0.93 0.85 1.14 ns DIFF_SSTL15_D 0.68 0.72 0.82 0.96 0.72 0.75 0.89 1.01 1.09 1.12 1.01 1.27 0.72 0.85 0.93 0.96 0.85 1.17 ns CI_F DIFF_SSTL15_T_ 0.68 0.72 0.82 0.88 0.72 0.76 0.89 1.01 1.09 1.20 1.01 1.35 0.72 0.85 0.93 1.03 0.85 1.24 ns DCI_F DIFF_SSTL135_F 0.69 0.72 0.82 1.09 0.72 0.91 0.88 1.00 1.08 1.12 1.00 1.27 0.71 0.85 0.92 0.96 0.85 1.17 ns DIFF_SSTL135_ 0.69 0.72 0.82 0.90 0.72 0.76 0.89 1.00 1.08 1.12 1.00 1.27 0.72 0.85 0.92 0.96 0.85 1.17 ns DCI_F DIFF_SSTL135_ 0.69 0.72 0.82 0.84 0.72 0.76 0.89 1.00 1.08 1.20 1.00 1.35 0.72 0.85 0.92 1.03 0.85 1.24 ns T_DCI_F DIFF_SSTL12_F 0.69 0.72 0.82 0.96 0.72 0.91 0.88 1.00 1.08 1.12 1.00 1.26 0.71 0.84 0.92 0.96 0.84 1.15 ns DIFF_SSTL12_ 0.69 0.72 0.82 0.87 0.72 0.78 0.91 1.03 1.11 1.11 1.03 1.24 0.74 0.88 0.95 0.95 0.88 1.14 ns DCI_F DIFF_SSTL12_T_ 0.69 0.72 0.82 0.96 0.72 0.80 0.91 1.03 1.11 1.18 1.03 1.33 0.74 0.88 0.95 1.02 0.88 1.23 ns DCI_F Table22 specifies the values of T and T . T is described as the delay from the T pin to the IOB pad IOTPHZ IOIBUFDISABLE IOTPHZ through the output buffer of an IOB pad, when 3-state is enabled (i.e., a high impedance state). T is described as IOIBUFDISABLE the IOB delay from IBUFDISABLE to O output. In HP I/O banks, the internal DCI termination turn-off time is always faster than T when the DCITERMDISABLE pin is used. In HR I/O banks, the internal IN_TERM termination turn-off time is always IOTPHZ faster than T when the INTERMDISABLE pin is used. IOTPHZ Table 22: IOB 3-state Output Switching Characteristics Speed Grade Symbol Description 1.0V 0.95V 0.9V Units -3 -2/-2LE -1 -1M/-1LM -2LI -2LE T T input to pad high-impedance 0.76 0.86 0.99 0.99 0.86 0.62 ns IOTPHZ T IBUF turn-on time from IBUFDISABLE to 1.72 1.89 2.14 2.14 1.89 2.17 ns IOIBUFDISABLE_HR Ooutput for HR I/O banks T IBUF turn-on time from IBUFDISABLE to 1.31 1.46 1.76 1.76 1.46 1.86 ns IOIBUFDISABLE_HP Ooutput for HP I/O banks DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 25

Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics I/O Standard Adjustment Measurement Methodology Input Delay Measurements Table23 shows the test setup parameters used for measuring input delay. Table 23: Input Delay Measurement Methodology V V MEAS REF Description I/O Standard Attribute V (1)(2) V (1)(2) L H (1)(4)(6) (1)(3)(5) LVCMOS, 1.2V LVCMOS12 0.1 1.1 0.6 – LVCMOS, 1.5V LVCMOS15 0.1 1.4 0.75 – LVCMOS, 1.8V LVCMOS18 0.1 1.7 0.9 – LVCMOS, 2.5V LVCMOS25 0.1 2.4 1.25 – LVCMOS, 3.3V LVCMOS33 0.1 3.2 1.65 – LVTTL, 3.3V LVTTL 0.1 3.2 1.65 – MOBILE_DDR, 1.8V MOBILE_DDR 0.1 1.7 0.9 – PCI33, 3.3V PCI33_3 0.1 3.2 1.65 – HSTL (High-Speed Transceiver Logic), Class I, 1.2V HSTL_I_12 V –0.5 V +0.5 V 0.60 REF REF REF HSTL, Class I & II, 1.5V HSTL_I, HSTL_II V –0.65 V +0.65 V 0.75 REF REF REF HSTL, Class I & II, 1.8V HSTL_I_18, HSTL_II_18 V –0.8 V +0.8 V 0.90 REF REF REF HSUL (High-Speed Unterminated Logic), 1.2V HSUL_12 V –0.5 V +0.5 V 0.60 REF REF REF SSTL (Stub Terminated Transceiver Logic), 1.2V SSTL12 V –0.5 V +0.5 V 0.60 REF REF REF SSTL, 1.35V SSTL135, SSTL135_R V –0.575 V +0.575 V 0.675 REF REF REF SSTL, 1.5V SSTL15, SSTL15_R V –0.65 V +0.65 V 0.75 REF REF REF SSTL, Class I & II, 1.8V SSTL18_I, SSTL18_II V –0.8 V +0.8 V 0.90 REF REF REF DIFF_MOBILE_DDR, 1.8V DIFF_MOBILE_DDR 0.9–0.125 0.9+0.125 0(6) – DIFF_HSTL, Class I, 1.2V DIFF_HSTL_I_12 0.6–0.125 0.6+0.125 0(6) – DIFF_HSTL, Class I & II,1.5V DIFF_HSTL_I, 0.75–0.125 0.75+0.125 0(6) – DIFF_HSTL_II DIFF_HSTL, Class I & II, 1.8V DIFF_HSTL_I_18, 0.9–0.125 0.9+0.125 0(6) – DIFF_HSTL_II_18 DIFF_HSUL, 1.2V DIFF_HSUL_12 0.6–0.125 0.6+0.125 0(6) – DIFF_SSTL, 1.2V DIFF_SSTL12 0.6–0.125 0.6+0.125 0(6) – DIFF_SSTL135/DIFF_SSTL135_R, 1.35V DIFF_SSTL135, 0.675–0.125 0.675+0.125 0(6) – DIFF_SSTL135_R DIFF_SSTL15/DIFF_SSTL15_R, 1.5V DIFF_SSTL15, 0.75–0.125 0.75+0.125 0(6) – DIFF_SSTL15_R DIFF_SSTL18_I/DIFF_SSTL18_II, 1.8V DIFF_SSTL18_I, 0.9–0.125 0.9+0.125 0(6) – DIFF_SSTL18_II LVDS (Low-Voltage Differential Signaling), 1.8V LVDS 0.9–0.125 0.9+0.125 0(6) – LVDS_25, 2.5V LVDS_25 1.2–0.125 1.2+0.125 0(6) – BLVDS_25, 2.5V BLVDS_25 1.25–0.125 1.25+0.125 0(6) – MINI_LVDS_25, 2.5V MINI_LVDS_25 1.25–0.125 1.25+0.125 0(6) – PPDS_25 PPDS_25 1.25–0.125 1.25+0.125 0(6) – RSDS_25 RSDS_25 1.25–0.125 1.25+0.125 0(6) – DS182 (v2.16.1) August 7, 2018 www.xilinx.com Send Feedback Product Specification 26