ICGOO在线商城 > 集成电路(IC) > PMIC - PFC(功率因数修正) > UCC28070APW

- 型号: UCC28070APW

- 制造商: Texas Instruments

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

UCC28070APW产品简介:

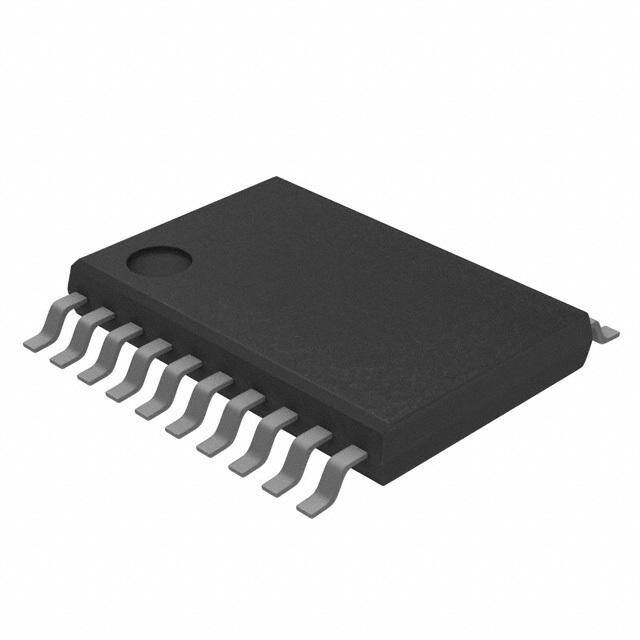

ICGOO电子元器件商城为您提供UCC28070APW由Texas Instruments设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 UCC28070APW价格参考¥12.21-¥22.80。Texas InstrumentsUCC28070APW封装/规格:PMIC - PFC(功率因数修正), PFC IC Continuous Conduction (CCM) Adjustable 20-TSSOP。您可以下载UCC28070APW参考资料、Datasheet数据手册功能说明书,资料中有UCC28070APW 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC)半导体 |

| 描述 | IC PFC CTRLR CCM 20TSSOP功率因数校正 - PFC 2-Phase Interleaved CCM PFC Controller |

| 产品分类 | |

| 品牌 | Texas Instruments |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 电源管理 IC,功率因数校正 - PFC,Texas Instruments UCC28070APW- |

| 数据手册 | |

| 产品型号 | UCC28070APW |

| PCN设计/规格 | |

| 产品培训模块 | http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=25886 |

| 产品种类 | 功率因数校正 - PFC |

| 供应商器件封装 | 20-TSSOP |

| 其它名称 | 296-30341-5 |

| 制造商产品页 | http://www.ti.com/general/docs/suppproductinfo.tsp?distId=10&orderablePartNumber=UCC28070APW |

| 包装 | 管件 |

| 商标 | Texas Instruments |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装 | Tube |

| 封装/外壳 | 20-TSSOP(0.173",4.40mm 宽) |

| 封装/箱体 | TSSOP-20 |

| 工作温度 | -40°C ~ 125°C |

| 工厂包装数量 | 70 |

| 开关频率 | 10 kHz to 300 kHz |

| 最大功率耗散 | 800 mW |

| 最大工作温度 | + 125 C |

| 最小工作温度 | - 40 C |

| 标准包装 | 70 |

| 模式 | 连续导电(CCM) |

| 电压-电源 | 11.2 V ~ 21 V |

| 电流-启动 | 20mA |

| 系列 | UCC28070A |

| 频率-开关 | 可调式 |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

Product Sample & Technical Tools & Support & Folder Buy Documents Software Community UCC28070A SLUSAW0A–MARCH2012–REVISEDMAY2016 UCC28070A Extended Frequency Range (10 kHz to 300 kHz), Interleaving Continuous Conduction Mode PFC Controller 1 Features The UCC28070A device is capable of operating at frequencies from 10 kHz to 300 kHz, thus extending • InterleavedAverageCurrent-ModePWMControl 1 the range of operation compared to the UCC28070 WithInherentCurrentMatching device whose minimum operating frequency was • AdvancedCurrentSynthesizerCurrentSensing limited to 30 kHz. All the other features and benefits forSuperiorEfficiency of the UCC28070 device are also available in the UCC28070A device. The 180° out-of-phase • Highly-LinearMultiplierOutputWithInternal interleaved operation generates substantial reduction QuantizedVoltageFeed-ForwardCorrectionfor in input and output ripple currents and conducted EMI Near-UnityPF filteringbecomeseasierandlessexpensive. • ExtendedRangeProgrammableFrequency Like the UCC28070 device, the UCC28070A device (10kHzto300kHz) also features multiple innovations including current • ProgrammableMaximumDuty-CycleClamp synthesis and quantized voltage feedforward to • ProgrammableFrequencyDitheringRateand promote performance enhancements in PF, MagnitudeforEnhancedEMIReduction efficiency, THD, and transient response. Features including frequency dithering, clock synchronization, – Magnitude:3kHzto30kHz and slew rate enhancement further expand the – Rate:Upto30kHz potential performance enhancements. All protection • ExternalClockSynchronizationCapability features in the UCC28070 device such as output • EnhancedLoadandLineTransientResponse overvoltage detection, programmable peak-current limit, undervoltage lockout, and open-loop protection throughVoltageAmplifierOutputSlew-Rate areavailableintheUCC28070Adeviceaswell. Correction • ProgrammablePeakCurrentLimiting DeviceInformation(1) • Bias-SupplyUVLO,OvervoltageProtection, PARTNUMBER PACKAGE BODYSIZE(NOM) Open‑LoopDetection,andPFC-EnableMonitoring UCC28070A TSSOP(20) 6.50mm×4.40mm • ExternalPFC-DisableInterface (1) For all available packages, see the orderable addendum at • Open-CircuitProtectiononVSENSEand theendofthedatasheet. VINACpins SimplifiedApplicationDiagram • ProgrammableSoftStart VIN L1 D1 VOUT 2 Applications + COUT • AirConditionersandWhiteGoods – 12Vto21V ToCSB •• PHFigCh-AEpffpicliiceantcioynSseWrviethraIGndBTDePsokwtoeprSPwowitcehres RA CRCRDDRM 1234RVCVSDADEOMRNSEDMGRSADSTXB21110987RRDRCMTSXS RS TM11 5VINAC GND16 Supplies RB RRISMYON 678RCIMSSOYBNTHVGVRCDECAF111543 L2 D2 • TelecomRectifiers 9CSA CAOA12 10PKLMT CAOB11 ToCSA • IndustrialEquipment FromIxfrms CZV RPK1 CREF CZC CZC RS T2 RA 3 Description CPV RZV RPK2 CPC RZC CPC RZC M2 RB The UCC28070A device is an extended frequency Copyright © 2016,Texas Instruments Incorporated range derivative of the UCC28070 device, capable of operating at low switching frequencies desired for IGBT power-switch based PFC converters in high- powerapplications. 1 An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectualpropertymattersandotherimportantdisclaimers.PRODUCTIONDATA.

UCC28070A SLUSAW0A–MARCH2012–REVISEDMAY2016 www.ti.com Table of Contents 1 Features.................................................................. 1 7.4 DeviceFunctionalModes........................................28 2 Applications........................................................... 1 8 ApplicationandImplementation........................ 29 3 Description............................................................. 1 8.1 ApplicationInformation............................................29 4 RevisionHistory..................................................... 2 8.2 TypicalApplication..................................................29 5 PinConfigurationandFunctions......................... 3 9 PowerSupplyRecommendations...................... 37 6 Specifications......................................................... 4 10 Layout................................................................... 38 6.1 AbsoluteMaximumRatings......................................4 10.1 LayoutGuidelines.................................................38 6.2 ESDRatings..............................................................4 10.2 LayoutExample....................................................38 6.3 RecommendedOperatingConditions.......................5 11 DeviceandDocumentationSupport................. 39 6.4 ThermalInformation..................................................5 11.1 DocumentationSupport........................................39 6.5 ElectricalCharacteristics...........................................5 11.2 CommunityResources..........................................39 6.6 TypicalCharacteristics..............................................9 11.3 Trademarks...........................................................39 7 DetailedDescription............................................ 12 11.4 ElectrostaticDischargeCaution............................39 7.1 Overview.................................................................12 11.5 Glossary................................................................39 7.2 FunctionalBlockDiagram.......................................13 12 Mechanical,Packaging,andOrderable Information........................................................... 39 7.3 FeatureDescription.................................................14 4 Revision History NOTE:Pagenumbersforpreviousrevisionsmaydifferfrompagenumbersinthecurrentversion. ChangesfromOriginal(May2015)toRevisionA Page • AddedDeviceInformationtable,RevisionHistorysection,PinConfigurationandFunctionssection,Specifications section,DetailedDescriptionsection,ApplicationandImplementationsection,PowerSupplyRecommendations section,Layoutsection,DeviceandDocumentationSupportsection,andMechanical,Packaging,andOrderable Informationsection................................................................................................................................................................. 1 2 SubmitDocumentationFeedback Copyright©2012–2016,TexasInstrumentsIncorporated ProductFolderLinks:UCC28070A

UCC28070A www.ti.com SLUSAW0A–MARCH2012–REVISEDMAY2016 5 Pin Configuration and Functions PWPackages 20-PinTSSOP TopView CDR 1 20 DMAX RDM 2 19 RT VAO 3 18 SS VSENSE 4 17 GDB VINAC 5 16 GND IMO 6 15 VCC RSYNTH 7 14 GDA CSB 8 13 VREF CSA 9 12 CAOA PKLMT 10 11 CAOB PinFunctions PIN I/O DESCRIPTION NO. NAME DitherRateCapacitor.Frequency-ditheringtimingpin.AnexternalcapacitortoGNDprogramstherateof 1 CDR I oscillatordither.ConnecttheCDRpintotheVREFpintodisabledithering. DitherMagnitudeResistor.Frequency-ditheringmagnitudeandexternalsynchronizationpin.Anexternal RDM resistortoGNDprogramsthemagnitudeofoscillatorfrequencydither.Whenfrequencyditheringisdisabled 2 I (SYNC) (CDR>5V),theinternalmasterclocksynchronizestopositiveedgespresentedontheRDMpin.Connect RDMtoGNDwhenditheringisdisabledandsynchronizationisnotdesired. VoltageAmplifierOutput.Outputoftransconductancevoltageerroramplifier.Internallyconnectedtothe 3 VAO O multiplierinputandthezero-powercomparator.Connectthevoltageregulationloopcompensationcomponents betweenthispinandGND. OutputVoltageSense.Internallyconnectedtotheinvertinginputofthetransconductancevoltageerror 4 VSENSE I amplifierinadditiontothepositiveterminalofthecurrentsynthesisdifferenceamplifier.Alsoconnectedtothe OVP,PFCenable,andslew-ratecomparators.ConnecttoPFCoutputwitharesistor-dividernetwork. ScaledACLineInputVoltage.Internallyconnectedtothemultiplierandnegativeterminalofthecurrent 5 VINAC I synthesisdifferenceamplifier.Connectaresistor-dividernetworkbetweenV ,VINAC,andGNDidenticalto IN thePFCoutputdividernetworkconnectedatVSENSE. 6 IMO O MultiplierCurrentOutput.ConnectaresistorbetweenthispinandGNDtosetthemultipliergain. CurrentSynthesisDown-SlopeProgramming.ConnectaresistorbetweenthispinandGNDtosetthe 7 RSYNTH I magnitudeofthecurrentsynthesizerdown-slope.ConnectingRSYNTHtoVREFdisablescurrentsynthesisand connectCSAandCSBdirectlytotheirrespectivecurrentamplifiers. PhaseBCurrentSenseInput.DuringtheON-timeofGDB,CSBisinternallyconnectedtotheinvertinginputof 8 CSB I phaseBcurrentamplifierthroughthecurrentsynthesisstage. PhaseACurrentSenseInput.DuringtheON-timeofGDA,CSAisinternallyconnectedtotheinvertinginputof 9 CSA I phaseAcurrentamplifierthroughthecurrentsynthesisstage. PeakCurrentLimitProgramming.Connectaresistor-dividernetworkbetweenVREFandthispintosetthe 10 PKLMT I voltagethresholdofthecycle-by-cyclepeakcurrentlimitingcomparators.AllowsadjustmentfordesiredΔI . LB PhaseBCurrentAmplifierOutput.OutputofphaseBtransconductancecurrentamplifier.Internallyconnected 11 CAOB O totheinvertinginputofphaseBPWMcomparatorfortrailing-edgemodulation.Connectthecurrentregulation loopcompensationcomponentsbetweenthispinandGND. Copyright©2012–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 3 ProductFolderLinks:UCC28070A

UCC28070A SLUSAW0A–MARCH2012–REVISEDMAY2016 www.ti.com PinFunctions(continued) PIN I/O DESCRIPTION NO. NAME PhaseACurrentAmplifierOutput.OutputofphaseAtransconductancecurrentamplifier.Internallyconnected 12 CAOA O totheinvertinginputofphaseAPWMcomparatorfortrailing-edgemodulation.Connectthecurrentregulation loopcompensationcomponentsbetweenthispinandGND. 6-VReferenceVoltageandInternalBiasVoltage.Connecta0.1-μFceramicbypasscapacitorascloseas 13 VREF O possibletothispinandGND. PhaseAGateDrive.Thislimited-currentoutputisintendedtoconnecttoaseparategate-drivedevicesuitable 14 GDA O fordrivingthephaseAswitchingcomponent(s).Theoutputvoltageistypicallyclampedto13.5V. 15 VCC I BiasVoltageInput.Connecta0.1-μFceramicbypasscapacitorascloseaspossibletothispinandGND. DeviceGroundReference.Connectallcompensationandprogrammingresistorandcapacitornetworkstothis 16 GND I/O pin.Connectthispintothesystemthroughaseparatetraceforhigh-currentnoiseisolation. PhaseBGateDrive.Thislimited-currentoutputisintendedtoconnecttoaseparategate-drivedevicesuitable 17 GDB O fordrivingthephaseBswitchingcomponent(s).Theoutputvoltageistypicallyclampedto13.5V. Soft-StartandExternalFaultInterface.ConnectacapacitortoGNDonthispintosetthesoft-startslewrate basedonaninternally-fixed,10-μAcurrentsource.TheregulationreferencevoltageforVSENSEisclampedto 18 SS I V untilV exceeds3V.Uponrecoveryfromcertainfaultconditions,a1-mAcurrentsourceispresentatthe SS SS SSpinuntiltheSSvoltageequalstheVSENSEvoltage.PullingtheSSpinbelow0.6Vimmediatelydisables bothGDAandGDBoutputs. TimingResistor.Oscillatorfrequencyprogrammingpin.AresistortoGNDsetstherunningfrequencyofthe 19 RT I internaloscillator. MaximumDuty-CycleResistor.MaximumPWMduty-cycleprogrammingpin.AresistortoGNDsetsthePWM 20 DMAX I maximumduty-cyclebasedontheratioofR /R . DMX RT 6 Specifications 6.1 Absolute Maximum Ratings overoperatingfree-airtemperaturerange(unlessotherwisenoted) (1)(2)(3)(4) MIN MAX UNIT Supplyvoltage VCC 22 V Supplycurrent,I 20 mA VCC Gatedrivecurrent–continuous GDA,GDB ±0.25 A Gatedrivecurrent–pulsed GDA,GDB ±0.75 A GDA,GDB –0.5 V +0.3 CC Voltage DMAX,RDM,RT,CDR,VINAC,VSENSE,SS,VAO,IMO,CSA, V –0.5 7 CSB,CAOA,CAOB,PKLMT,VREF RT,DMAX,RDM,RSYNTH –0.5 Current mA VREF,VAO,CAOA,CAOB,IMO 10 Leadtemperature(10seconds) 260 °C Operatingjunctiontemperature,T –40 125 °C J Storagetemperature,T –65 150 °C stg (1) StressesbeyondthoselistedunderAbsoluteMaximumRatingsmaycausepermanentdamagetothedevice.Thesearestressratings only,whichdonotimplyfunctionaloperationofthedeviceattheseoranyotherconditionsbeyondthoseindicatedunderRecommended OperatingConditions.Exposuretoabsolute-maximum-ratedconditionsforextendedperiodsmayaffectdevicereliability. (2) AllvoltagesarewithrespecttoGND. (3) Allcurrentsarepositiveintotheterminal,negativeoutoftheterminal. (4) Innormaluse,terminalsGDAandGDBareconnectedtoanexternalgatedriverandareinternallylimitedinoutputcurrent. 6.2 ESD Ratings VALUE UNIT Human-bodymodel(HBM),perANSI/ESDA/JEDECJS-001(1) 2000 V Electrostaticdischarge V (ESD) Charged-devicemodel(CDM),perJEDECspecificationJESD22-C101(2) 500 (1) JEDECdocumentJEP155statesthat500-VHBMallowssafemanufacturingwithastandardESDcontrolprocess. (2) JEDECdocumentJEP157statesthat250-VCDMallowssafemanufacturingwithastandardESDcontrolprocess. 4 SubmitDocumentationFeedback Copyright©2012–2016,TexasInstrumentsIncorporated ProductFolderLinks:UCC28070A

UCC28070A www.ti.com SLUSAW0A–MARCH2012–REVISEDMAY2016 6.3 Recommended Operating Conditions overoperatingfree-airtemperaturerange(unlessotherwisenoted) MIN MAX UNIT Inputvoltage(fromalow-impedancesource)toVCC V +1 21 V UVLO LoadcurrenttoVREF 2 mA InputvoltagetoVINAC 0 3 V VoltagetoIMO 0 3.3 V VoltagetoCSA,CSB,PKLMT 0 3.6 V R RSYNTHresistance 15 750 kΩ SYN R RDMresistance 30 330 kΩ RDM 6.4 Thermal Information UCC28070A THERMALMETRIC(1) PW(TSSOP) UNIT 20PINS R Junction-to-ambientthermalresistance 99.9 °C/W θJA R Junction-to-case(top)thermalresistance 34.1 °C/W θJC(top) R Junction-to-boardthermalresistance 50.8 °C/W θJB ψ Junction-to-topcharacterizationparameter 1.9 °C/W JT ψ Junction-to-boardcharacterizationparameter 50.3 °C/W JB (1) Formoreinformationabouttraditionalandnewthermalmetrics,seetheSemiconductorandICPackageThermalMetricsapplication report,SPRA953. 6.5 Electrical Characteristics T =T =–40°Cto125°C,V =12V,GND=0V,R =75kΩ,R =68.1kΩ,R =R =100kΩ,C =2.2nF, J A CC RT DMX RDM SYN CDR C =C =0.1μF,C =1μF,I =0mA(unlessotherwisenoted) SS VREF VCC VREF PARAMETER TESTCONDITIONS MIN TYP MAX UNIT BIASSUPPLY V V shuntvoltage(1) I =10mA 23 25 27 V CC(SHUNT) CC VCC Disabled V =0V 7 VSENSE mA Enabled V =3V(switching) 9 12 VSENSE I Supplycurrent VCC V =7V 200 µA CC UVLO V =9V 4 6 mA CC UVLOturnonthreshold MeasuredatVCC(rising) 9.8 10.2 10.6 V V UVLO UVLOhysteresis MeasuredatVCC(falling) 1 VREFenablethreshold MeasuredatVCC(rising) 7.5 8 8.5 V LINEARREGULATOR Noload I =0mA 5.82 6 6.18 V VREF MeasuredasthechangeinV Loadrejection VREF –12 12 V Referencevoltage (I =0mAand–2mA) VREF VREF mV MeasuredasthechangeinV Linerejection VREF –12 12 (V =11Vand20V,I =0μA) CC VREF (1) ExcessiveVCCinputvoltageorcurrentdamagesthedevice.Thisclampdoesnotprotectthedevicefromanunregulatedsupply.Ifan unregulatedsupplyisused,TIrecommendsaseries-connectedfixedpositivevoltageregulatorsuchasaUA78L15A.SeeAbsolute MaximumRatingsforthelimitsonVCCvoltageandcurrent. Copyright©2012–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 5 ProductFolderLinks:UCC28070A

UCC28070A SLUSAW0A–MARCH2012–REVISEDMAY2016 www.ti.com Electrical Characteristics (continued) T =T =–40°Cto125°C,V =12V,GND=0V,R =75kΩ,R =68.1kΩ,R =R =100kΩ,C =2.2nF, J A CC RT DMX RDM SYN CDR C =C =0.1μF,C =1μF,I =0mA(unlessotherwisenoted) SS VREF VCC VREF PARAMETER TESTCONDITIONS MIN TYP MAX UNIT PFCENABLE Enablethreshold MeasuredatVSENSE(rising) 0.65 0.75 0.85 V V EN Enablehysteresis 0.15 EXTERNALPFCDISABLE Disablethreshold MeasuredatSS(falling) 0.5 0.6 V Hysteresis V >0.85V 0.15 V VSENSE OSCILLATOR Outputphaseshift MeasuredbetweenGDAandGDB 179 180 181 ° V ,V , DMAX RT Timingregulationvoltages MeasuredatDMAX,RT,andRDM 2.91 3 3.09 V V RDM R =750kΩ,R =681kΩ,V =0V, RT DMX RDM 9.75 10.25 10.75 V =6V CDR R =75kΩ,R =68.1kΩ, f PWMswitchingfrequency RT DMX 95 100 105 kHz PWM V =0V,V =6V RDM CDR R =24.9kΩ,R =22.6kΩ, RT DMX 270 290 330 V =0V,V =6V RDM CDR R =75kΩ,R =68.1kΩ, D Duty-cycleclamp RT DMX 92% 95% 98% MAX V =0V,V =6V RDM CDR R =24.9kΩ,R =22.6kΩ, MinimumprogrammableOFF-time RT DMX 50 150 250 ns V =0V,V =6V RDM CDR Frequencyditheringmagnitudechange RRDM=316kΩ,RRT=75kΩ 2 3 4 f kHz DM infPWM RRDM=31.6kΩ,RRT=24.9kΩ 24 30 36 Frequencyditheringrateofchangein CCDR=2.2nF,RRDM=100kΩ 3 f kHz DR fPWM CCDR=0.3nF,RRDM=100kΩ 20 I Ditherratecurrent MeasuredatCDR(sinkandsource) ±10 μA CDR Ditherdisablethreshold MeasuredatCDR(rising) 5 5.25 V CLOCKSYNCHRONIZATION V SYNCenablethreshold MeasuredatCDR(rising) 5 5.25 V CDR V =6V,measuredfromRDM(rising)to SYNCpropagationdelay CDR 50 100 ns GDx(rising) SYNCthreshold(rising) V =6V,measuredatRDM 1.2 1.5 V CDR SYNCthreshold(falling) V =6V,measuredatRDM 0.4 0.7 V CDR SYNCpulses Positivepulsewidth 0.2 μs Maximumdutycycle(2) 50% VOLTAGEAMPLIFIER VSENSEvoltage Inregulation,T =25°C 2.97 3 3.03 V A VSENSEvoltage Inregulation 2.94 3 3.06 V VSENSEinputbiascurrent Inregulation 250 500 nA VAOhighvoltage V =2.9V 4.8 5 5.2 V VSENSE VAOlowvoltage V =3.1V 0.05 0.5 V VSENSE g VAOtransconductance V =2.8Vto3.2V,V =3V 70 μS MV VSENSE VAO VAOsinkcurrent,overdrivenlimit V =3.5V,V =3V 30 μA VSENSE VAO VAOsourcecurrent,overdriven V =2.5V,V =3V,SS=3V –30 μA VSENSE VAO VAOsourcecurrent, V =2.5V,V =3V –130 μA overdrivenlimit+I VSENSE VAO SRC (2) DuetotheinfluenceofthesynchronizationpulsewidthontheprogrammabilityofthemaximumPWMswitchingdutycycle(D ),TI MAX recommendsminimizingthedutycycleofthesynchronizationsignal. 6 SubmitDocumentationFeedback Copyright©2012–2016,TexasInstrumentsIncorporated ProductFolderLinks:UCC28070A

UCC28070A www.ti.com SLUSAW0A–MARCH2012–REVISEDMAY2016 Electrical Characteristics (continued) T =T =–40°Cto125°C,V =12V,GND=0V,R =75kΩ,R =68.1kΩ,R =R =100kΩ,C =2.2nF, J A CC RT DMX RDM SYN CDR C =C =0.1μF,C =1μF,I =0mA(unlessotherwisenoted) SS VREF VCC VREF PARAMETER TESTCONDITIONS MIN TYP MAX UNIT Measuredas Slew-ratecorrectionthreshold 92% 93% 95% V (falling)/V (regulation) VSENSE VSENSE Slew-ratecorrectionhysteresis MeasuredatVSENSE(rising) 3 9 mV MeasuredatVAO,inadditionto I Slew-ratecorrectioncurrent –100 μA SRC VAOsourcecurrent Slew-ratecorrectionenablethreshold MeasuredatSS(rising) 4 V VAOdischargecurrent V =0.5V,V =1V 10 μA VSENSE VAO SOFTSTART I SSsourcecurrent V =0.9V,V =1V –10 μA SS VSENSE SS Adaptivesourcecurrent V =2V,V =1V –1.5 –2.5 mA VSENSE SS AdaptiveSSdisable MeasuredasV –V –30 0 30 mV VSENSE SS SSsinkcurrent V =0.5V,V =0.2V 0.5 0.9 mA VSENSE SS OVERVOLTAGE Measuredas V OVPthreshold 104% 106% 108% OVP V (rising)/V (regulation) VSENSE VSENSE OVPhysteresis MeasuredatVSENSE(falling) 100 mV MeasuredbetweenVSENSE(rising)and OVPpropagationdelay 0.2 0.3 μs GDx(falling) ZERO-POWER V Zero-powerdetectthreshold MeasuredatVAO(falling) 0.65 0.75 V ZPWR Zero-powerhysteresis 0.15 V MULTIPLIER V ≥1.5V,T =25°C 16 17 18 VAO A V =1.2V,T =25°C 14.5 17 19.5 VAO A k Gainconstant μA MULT V ≥1.5V 15 17 19 VAO V =1.2V 13 17 21 VAO V =0.9V ,V =0.8V –0.2 0 0.2 VINAC PK VAO I Outputcurrent:zero μA IMO V =0V,V =5V –0.2 0 0.2 VINAC VAO QUANTIZEDVOLTAGEFEEDFORWARD V Level1threshold(3) MeasuredatVINAC(rising) 0.6 0.7 0.8 V LVL1 V Level2threshold 1 V LVL2 V Level3threshold 1.2 V LVL3 V Level4threshold 1.4 V LVL4 V Level5threshold 1.65 V LVL5 V Level6threshold 1.95 V LVL6 V Level7threshold 2.25 V LVL7 V Level8threshold 2.6 V LVL8 CURRENTAMPLIFIERS CAOxhighvoltage 5.75 6 V CAOxlowvoltage 0.1 V g CAOxtransconductance 100 μS MC CAOxsinkcurrent,overdriven 50 μA CAOxsourcecurrent,overdriven –50 μA Inputcommonmoderange 0 3.6 V (3) TheLevel1thresholdrepresentsthezero-crossingdetectionthresholdabovewhichVINACmustrisetoinitiateanewinputhalf-cycle, andbelowwhichVINACmustfalltoterminatethathalf-cycle. Copyright©2012–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 7 ProductFolderLinks:UCC28070A

UCC28070A SLUSAW0A–MARCH2012–REVISEDMAY2016 www.ti.com Electrical Characteristics (continued) T =T =–40°Cto125°C,V =12V,GND=0V,R =75kΩ,R =68.1kΩ,R =R =100kΩ,C =2.2nF, J A CC RT DMX RDM SYN CDR C =C =0.1μF,C =1μF,I =0mA(unlessotherwisenoted) SS VREF VCC VREF PARAMETER TESTCONDITIONS MIN TYP MAX UNIT V =6V,T =25°C –4 –8 –13 RSYNTH A Inputoffsetvoltage mV V =6V 0 –8 –20 RSYNTH Inputoffsetvoltage 0 –8 –20 mV MeasuredasphaseAinputoffsetminus Phasemismatch –12 0 12 mV phaseBinputoffset CAOxpulldowncurrent V =0.5V,V =0.2V 0.5 0.9 mA VSENSE CAOx CURRENTSYNTHESIZER V =3V,V =0V 2.91 3 3.09 VSENSE VINAC V Regulationvoltage V RSYNTH V =3V,V =2.85V 0.1 0.15 0.2 VSENSE VINAC Synthesizerdisablethreshold MeasuredatRSYNTH(rising) 5 5.25 V VINACinputbiascurrent 0.25 0.5 μA PEAKCURRENTLIMIT Peakcurrentlimitthreshold V =3.3V,measuredatCSx(rising) 3.27 3.3 3.33 V PKLMT MeasuredbetweenCSx(rising)and Peakcurrentlimitpropagationdelay 60 100 ns GDx(falling)edges PWMRAMP V PWMrampamplitude 3.8 4 4.2 V RMP PWMrampoffsetvoltage T =25°C,R =75kΩ 0.65 0.7 V A RT PWMrampoffsettemperature –2 mV/°C coefficient GATEDRIVE GDA,GDBoutputvoltage,high, V =20V,C =1nF 11.5 13 15 V clamped CC LOAD GDA,GDBoutputvoltage,high C =1nF 10 10.5 V LOAD GDA,GDBoutputvoltage,low C =1nF 0.2 0.3 V LOAD RisetimeGDx 1Vto9V,C =1nF 18 30 ns LOAD FalltimeGDx 9Vto1V,C =1nF 12 25 ns LOAD GDA,GDBoutputvoltage,UVLO V =0V,I ,I =2.5mA 0.7 2 V CC GDA GDB THERMALSHUTDOWN Thermalshutdownthreshold 160 °C Thermalshutdownrecovery 140 °C 8 SubmitDocumentationFeedback Copyright©2012–2016,TexasInstrumentsIncorporated ProductFolderLinks:UCC28070A

UCC28070A www.ti.com SLUSAW0A–MARCH2012–REVISEDMAY2016 6.6 Typical Characteristics 12 6.18 10 IVCC, VCC= 12 V, enabled 6.12 mA) 8 e (V) 6.06 Supply Current ( 64 IVCC, VCC= 12 V, disabled Reference Voltag 65..0904 2 5.88 0 5.82 –60 –40 –20 0 20 40 60 80 100 120 140 –60 –10 40 90 140 Temperature (°C) Temperature (°C) V =0mA VREF Figure1.VCCSupplyCurrentvsJunctionTemperature Figure2.V vsJunctionTemperature VREF 3.06 0.50 0.45 3.04 0.40 Regulation (V) 33..0002 urrent (mA) 000...233550 ENSE Bias C 0.20 S 2.98 V 0.15 0.10 2.96 0.05 2.94 0 –60 –40 –20 0 20 40 60 80 100 120 140 –60 –10 40 90 140 Temperature (°C) Temperature (°C) Figure3.V RegulationvsJunctionTemperature Figure4.I BiasCurrentvsJunctionTemperature VSENSE VSENSE 180 20 QVFF Level 160 Level 1 Level 2 19 140 A) Level 3 Output Current (m 11208000 LLLLeeeevvvveeeellll 7654 er Constant (mA) 1187 ultiplier 60 Level 8 Multipli 16 M 40 VAO 15 1.2 V 1.5 V 20 3 V 5 V 0 14 0 1 2 3 4 5 6 –60 –40 –20 0 20 40 60 80 100 120 140 VoltageAmplifier Output (V) Temperature (°C) Figure5.IMO,MultiplierOutputCurrentvsV Figure6.MultiplierConstantvsJunctionTemperature VAO Copyright©2012–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 9 ProductFolderLinks:UCC28070A

UCC28070A SLUSAW0A–MARCH2012–REVISEDMAY2016 www.ti.com Typical Characteristics (continued) 0.50 1 Typical fPWM= 290 kHz, RT= 24.9 kΩ 00..4450 ncy (%) 00..86 TTyyppiiccaall ffPPWWMM== 11000.2 k5H kzH, zR, TRT= =7 57 5kΩ0 kΩ e u 0.35 eq 0.4 Current (mA) 00..2350 n Switching Fr 0.02 Bias 0.20 ange i −0.2 h 0.15 VINAC d C −0.4 0.10 01. 2V V malize −0.6 2 V or 0.05 2.5 V N −0.8 2.85 V 0.00 −1 –60 –10 40 90 140 –60 –40 –20 0 20 40 60 80 100 120 140 Temperature (°C) Temperature (°C) Figure7.I BiasCurrentvsJunctionTemperature Figure8.SwitchingFrequencyvsTemperature VINAC 80 40 20 mplifierTransconductance (nS) 67675500 Amplifier Output Current (mA) ––––842600000 A e Voltage 55 Voltag –100 –120 50 –140 –60 –40 –20 0 20 40 60 80 100 120 140 2.5 2.6 2.7 2.8 2.9 3.0 3.1 3.2 3.3 3.4 3.5 Temperature (°C) VSENSE (V) Figure9.VAO,VoltageAmplifierTransconductancevs Figure10.VoltageAmplifierTransferFunctionvsV VSENSE JunctionTemperature 110 5 105 0 S) nce (n 100 mV) CAx + 3σ OxTranjsconducta 9950 CAx Input Offset ( ––150 CAxAVG A CAx - 3σ C –15 85 80 –20 –60 –40 –20 0 20 40 60 80 100 120 140 –60 –40 –20 0 20 40 60 80 100 120 140 Temperature (°C) Temperature (°C) 0.8-VCommonMode Figure11.CurrentAmplifierTransconductancevs Figure12.CAxInputOffsetVoltagevs JunctionTemperature JunctionTemperature 10 SubmitDocumentationFeedback Copyright©2012–2016,TexasInstrumentsIncorporated ProductFolderLinks:UCC28070A

UCC28070A www.ti.com SLUSAW0A–MARCH2012–REVISEDMAY2016 Typical Characteristics (continued) 15 5 mV) 10 0 Voltage ( 5 A- B + 3σ mV) CAx + 3σ A2 Relative Offset –50 A- BAVG CAx Input Offset ( ––150 CAxAVG C A1 to A- B - 3σ –15 CAx - 3σ C –10 –15 –20 –60 –40 –20 0 20 40 60 80 100 120 140 –60 –40 –20 0 20 40 60 80 100 120 140 Tempterature (°C) Temperature (°C) 0.8-VCommonMode 2-VCommonMode Figure13.CA1toCA2RelativeOffsetvs Figure14.CAxInputOffsetVoltagevs JunctionTemperature JunctionTemperature 15 5 mV) 10 0 ge ( A- B + 3σ Volta 5 mV) CAx + 3σ A2 Relative Offset –50 A- BAVG CAx Input Offset ( ––150 CAxAVG CA1 to C –10 A- B - 3σ –15 CAx - 3σ –15 –20 –60 –40 –20 0 20 40 60 80 100 120 140 –60 –40 –20 0 20 40 60 80 100 120 140 Temperature (°C) Temperature (°C) 2-VCommonMode 3.6-VCommonMode Figure15.CA1toCA2RelativeOffsetvs Figure16.CAxInputOffsetVoltagevs JunctionTemperature JunctionTemperature 15 V) 10 m ge ( A- B + 3σ a Volt 5 et Offs e 0 ativ A- BAVG el R A2 –5 C o A- B - 3σ 1 t A C –10 –15 –60 –40 –20 0 20 40 60 80 100 120 140 Temperature (°C) 3.6-VCommonMode Figure17.CA1toCA2RelativeOffsetvsJunctionTemperature Copyright©2012–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 11 ProductFolderLinks:UCC28070A

UCC28070A SLUSAW0A–MARCH2012–REVISEDMAY2016 www.ti.com 7 Detailed Description 7.1 Overview The UCC28070A power factor corrector IC controls two CCM (Continuous Conduction Mode) Boost PFC power stages operating 180° out of phase with each other. This interleaving action reduces the input and output ripple currents so that less EMI filtering is needed and allows operation at higher power levels than a non-interleaved solution. The UCC28070A can operate over a wide range of frequencies, making it suitable for use with both MOSFET and IGBT power switches. Multiple UCC28070A controllers can be synchronized for use in higher-power applicationswheremorethantwointerleavedpowerstagesareneeded. This device is especially suited to high-performance, high-power, PFC applications where the use of Average CurrentModePWMcontrolgiveslowTHD. 12 SubmitDocumentationFeedback Copyright©2012–2016,TexasInstrumentsIncorporated ProductFolderLinks:UCC28070A

UCC28070A www.ti.com SLUSAW0A–MARCH2012–REVISEDMAY2016 7.2 Functional Block Diagram + VSENSE OVP VCC 15 Fault 3.18V 3.08V 25V 0.75V 160On oC ThermSD ReStart Ext.Disable + 0.60V VREF 13 6V Linear EN + 140Off SS Regulator 8V S Q 0.75V + 0.60V VSENSE R Q GND 16 + 0.90V UVLO ZeroPwr 0.75V 10.2V + VAO 9.2V 6 IMO 5 VINAC DMAX 20 Voltage 250nA Feed- CLKA RT 19 OFrsecqil.laDtoitrhwer/ CLKB IIMO=VVINACK∗VF(FVVAO–1)∗17uA FoKrwVFaFrd OffA x OffB Mult. / x 3 VAO RDM/ 2 SYNC ReStart + SS SYNC Logic 100uA 4V 5V SlewRate SYNC Dither Correction + 2.8V CDR 1 + Enable Disable 10uA 5V GmAmp - 4 VSENSE VA+ 3V + 250nA AdaptiveSS PKLMT 10 IpeakA ReStart 1mA + ISS + 10uA Control ReStart Logic Ext.Disable CSA 9 IpeakB + + PWM1 18 SS CA1 VCC GmAmp + S Q (Clampedat13.5V) OutA CSB 8 OutB OffA CLKA R Q Driver 14 GDA Current IpeakA Synthesizer Fault GND RSYNTH 7 Disable + PWM2 CA2 + VINAC VCC 5V VSENSE GmAmp + S Q (Clampedat13.5V) CAOA 12 IpeOafkfBB CLKB R Q Driver 17 GDB Fault GND CAOB 11 Copyright © 2016,Texas Instruments Incorporated Copyright©2012–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 13 ProductFolderLinks:UCC28070A

UCC28070A SLUSAW0A–MARCH2012–REVISEDMAY2016 www.ti.com 7.3 Feature Description 7.3.1 Interleaving One of the main benefits from the 180° interleaving of phases is significant reductions in the high-frequency ripple components of both the input current and the current into the output capacitor of the PFC preregulator. Compared to that of a single-phase PFC stage of equal power, the reduced ripple on the input current eases the burden of filtering conducted-EMI noise and helps reduce the EMI filter and C sizes. Additionally, reduced high- IN frequency ripple current into the PFC output capacitor, C , helps to reduce its size and cost. Furthermore, with OUT reduced ripple and average current in each phase, the boost inductor size can be smaller than in a single-phase design[1]. Ripple current reduction due to interleaving is often referred to as ripple cancellation, but strictly speaking, the peak-to-peak ripple is completely cancelled only at 50% duty-cycle in a 2-phase system. At duty-cycles other than 50%, ripple reduction occurs in the form of partial cancellation due to the superposition of the individual phase currents. Nevertheless, compared to the ripple currents of an equivalent single-phase PFC preregulator, those of a 2-phase interleaved design are extraordinarily smaller [1]. Independent of ripple cancellation, the frequencyoftheinterleavedripple,atboththeinputandoutput,is2 ×f . PWM On the input, 180° interleaving reduces the peak-to-peak ripple amplitude to ½ or less of the ripple amplitude of theequivalentsingle-phasecurrent. On the output, 180° interleaving reduces the rms value of the PFC-generated ripple current in the output capacitorbyafactorofslightlymorethan √2,forPWMduty-cycles>50%. Thiscanbeseeninthefollowingderivations,adaptingthemethodbyErickson[2]. In a single-phase PFC preregulator, the total rms capacitor current contributed by the PFC stage at all duty- cyclescanbeshowntobeapproximatedby: æI ö ææ16´V ö ö iCRMS1j =çè hO ÷ø ççèçè3p´VOM ÷ø-h2÷÷ø where • I istheaveragePFCoutputloadcurrent O • V istheaveragePFCoutputvoltage O • V isthepeakoftheinputAC-linevoltage M • ηistheefficiencyofthePFCstageattheseconditions (1) In a dual-phase interleaved PFC preregulator, the total rms capacitor current contributed by the PFC stage for D>50%canbeshowntobeapproximatedby: æI ö ææ16´V ö ö iCRMS2j =çè hO ÷ø ççèçè6p´VOM ÷ø-h2÷÷ø (2) It can be seen that the quantity under the radical for i is slightly smaller than ½ of that under the radical for CRMS2φ i . The rms currents shown contain both the low-frequency and the high-frequency components of the PFC CRMS1φ outputcurrent.Interleavingreducesthehigh-frequencycomponent,butnotthelow-frequencycomponent. 14 SubmitDocumentationFeedback Copyright©2012–2016,TexasInstrumentsIncorporated ProductFolderLinks:UCC28070A

UCC28070A www.ti.com SLUSAW0A–MARCH2012–REVISEDMAY2016 Feature Description (continued) 7.3.2 ProgrammingthePWMFrequencyandMaximumDuty-CycleClamp The PWM frequency and maximum duty-cycle clamps for both GDx outputs of the UCC28070A are set through the selection of the resistors connected to the RT and DMAX pins, respectively. The selection of the RT resistor (R )directlysetsthePWMfrequency(f ). RT PWM 7500 R (kW)= RT f (kHz) PWM (3) OnceR hasbeendetermined,theD resistor(R )maybederived. RT MAX DMX R =R ´(2´D -1) DMX RT MAX where • D isthedesiredmaximumPWMduty-cycle (4) MAX 7.3.3 FrequencyDithering(MagnitudeandRate) Frequency dithering refers to modulating the switching frequency to achieve a reduction in conducted-EMI noise beyond the capability of the line filter alone. The UCC28070A implements a triangular modulation method which results in equal time spent at every point along the switching frequency range. This total range from minimum to maximum frequency is defined as the dither magnitude, and is centered around the nominal switching frequency f set with R . For example, a dither magnitude of 20 kHz on a nominal f of 100 kHz results in a PWM RT PWM frequency range of 100 kHz ±10 kHz. Furthermore, the programmed duty-cycle clamp set by R remains DMX constantattheprogrammedvalueacrosstheentirerangeofthefrequencydithering. The rate at which f traverses from one extreme to the other and back again is defined as the dither rate. For PWM example, a dither rate of 1 kHz would linearly modulate the nominal frequency from 110 kHz to 90 kHz to 110 kHz once every millisecond. A good initial design target for dither magnitude is ±10% of f . Most boost PWM components can tolerate such a spread in f . The designer can then iterate around there to find the best PWM compromisebetweenEMIreduction,componenttolerances,andloopstability. ThedesireddithermagnitudeissetbyaresistorfromtheRDMpintoGND,ofvaluecalculatedwithEquation5: 937.5 R (kW)= RDM f (kHz) DM (5) Once the value of R is determined, the desired dither rate may be set by a capacitor from the CDR pin to RDM GND,ofvaluecalculatedwithEquation6: æR (kW)ö C (pF)= 66.7´ç RDM ÷ CDR f (kHz) è ø DR (6) Frequency dithering may be fully disabled by forcing the CDR pin > 5 V or by connecting it to VREF (6 V) and connecting the RDM pin directly to GND. (If populated, the relatively high impedance of the RDM resistor may allow system switching noise to couple in and interfere with the controller timing functions if not bypassed with a lowimpedancepathwhenditheringisdisabled.) If an external frequency source is used to synchronize f and frequency dithering is desired, the external PWM frequency source must provide the dither magnitude and rate functions as the internal dither circuitry is disabled topreventundesiredperformanceduringsynchronization.(SeeExternalClockSynchronizationformoredetails.) 7.3.4 ExternalClockSynchronization The UCC28070A has also been designed to be easily synchronized to almost any external frequency source. By disabling frequency dithering (pulling CDR > 5 V), the SYNC circuitry is enabled permitting the internal oscillator to be synchronized with pulses presented on the RDM pin. To ensure a precise 180° phase shift is maintained between the GDA and GDB outputs, the frequency (f ) of the pulses presented at the RDM pin must be at SYNC twicethedesiredf .Forexample,ifa100-kHzswitchingfrequencyisdesired,thef mustbe200kHz. PWM SYNC Copyright©2012–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 15 ProductFolderLinks:UCC28070A

UCC28070A SLUSAW0A–MARCH2012–REVISEDMAY2016 www.ti.com Feature Description (continued) f f = SYNC PWM 2 (7) To ensure the internal oscillator does not interfere with the SYNC function, R must be sized to set the internal RT oscillatorfrequencyatleast10%belowf . SYNC 15000 R (kW)= ´1.1 RT f (kHz) SYNC (8) It must be noted that the PWM modulator gain is reduced by a factor equivalent to the scaled R due to a direct RT correlation between the PWM ramp current and R . Adjustments to the current loop gains must be made RT accordingly. It must also be noted that the maximum duty-cycle clamp programmability is affected during external synchronization. The internal timing circuitry responsible for setting the maximum duty cycle is initiated on the falling edge of the synchronization pulse. Therefore, the selection of R becomes dependent on the DMX synchronizationpulsewidth(t ). SYNC D = t ´f SYNC SYNC SYNCForuseinR equationimmediatelybelow. (9) DMX æ 15000 ö R (kW)=ç ÷´(2´D -1-D ) DMX f (kHz) MAX SYNC è ø SYNC (10) Consequently to minimize the impact of the t it is clearly advantageous to use the smallest synchronization SYNC pulsewidthfeasible. NOTE When external synchronization is used, a propagation delay of approximately 50 ns to 100 ns exists between internal timing circuits and the falling edge of the SYNC signal, which may result in reduced OFF-time at the highest of switching frequencies. Therefore, R DMX must be adjusted downward slightly by (t – 0.1 μs) / t to compensate. At lower SYNC SYNC SYNC frequencies, this delay becomes an insignificant fraction of the PWM period, and canbeneglected. 16 SubmitDocumentationFeedback Copyright©2012–2016,TexasInstrumentsIncorporated ProductFolderLinks:UCC28070A

UCC28070A www.ti.com SLUSAW0A–MARCH2012–REVISEDMAY2016 Feature Description (continued) 7.3.5 Multi-phaseOperation External synchronization also facilitates using more than 2 phases for interleaving. Multiple UCC28070A devices can easily be paralleled to add an even number of additional phases for higher-power applications. With appropriate phase-shifting of the synchronization signals, even more input and output ripple current cancellation can be obtained. (An odd number of phases can be accommodated if desired, but the ripple cancellation would not be optimal.) For 4-, 6-, or any 2 × n-phases (where n = the number of UCC28070A controllers), each controller must receive a SYNC signal which is 360/n degrees out of phase with each other. For a 4-phase application interleaving with two controllers, SYNC1 must be 180° out of phase with SYNC2 for optimal ripple cancellation. Similarly for a 6-phase system, SYNC1, SYNC2, and SYNC3 must be 120° out of phase with each otherforoptimalripplecancellation. In a multi-phase interleaved system, each current loop is independent and treated separately; however, there is only one common voltage loop. To maintain a single control loop, all VSENSE, VINAC, SS, IMO, and VAO signals are paralleled, respectively between the n controllers. Where current-source outputs are combined (SS, IMO, VAO), the calculated load impedances must be adjusted by 1/n to maintain the same performance as with asinglecontroller. Figure18illustratestheparallelingoftwocontrollersfora4-phase,90-degree-interleavedPFCsystem. 7.3.6 VSENSEandVINACResistorConfiguration The primary purpose of the VSENSE input is to provide the voltage feedback from the output to the voltage control loop. Thus, a traditional resistor-divider network must be sized and connected between the output capacitor and the VSENSE pin to set the desired output voltage based on the 3-V regulation voltage on VSENSE. A unique aspect of the UCC28070A is the need to place the same resistor-divider network on the V side of the IN inductor to the VINAC pin. This provides the scaled input voltage monitoring needed for the linear multiplier and current synthesizer circuitry. It is not required that the actual resistance of the VINAC network be identical to the VSENSE network, but it is necessary that the attenuation (k ) of the two divider networks be equivalent for R properPFCoperation. R k = B R (R +R ) A B (11) In noisy environments, it may be beneficial for small filter capacitors to be applied to the VSENSE and VINAC inputs to avoid the destabilizing effects of excessive noise on these inputs. If applied, the RC time-constant must not exceed 100 μs on the VSENSE input to avoid significant delay in the output transient response. The RC time-constant must also not exceed 100 μs on the VINAC input to avoid degrading of the wave-shape zero- crossings. Usually, a time constant of 3 / f is adequate to filter out typical noise on VSENSE and VINAC. PWM Some design and test iteration may be required to find the optimal amount of filtering required in a particular application. 7.3.7 VSENSEandVINACOpen-CircuitProtection BoththeVSENSEandVINACpinshavebeendesignedwithaninternal250-nAcurrentsinktoensurethatinthe event of an open circuit at either pin, the voltage is not left undefined, and the UCC28070A remains in a safe operatingmode. Copyright©2012–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 17 ProductFolderLinks:UCC28070A

UCC28070A SLUSAW0A–MARCH2012–REVISEDMAY2016 www.ti.com Feature Description (continued) V IN L1 D1 – + ToCSB1 VREF1 1 CDR DMAX20 RDMX1 RS1 T1 2 RDM RT 19 3 VAO SS 18 RRT1 RA 4 VSENSE GDB17 M1 5 VINAC GND16 6 IMO VCC15 12Vto21V RB 7 RSYNTH GDA14 CSB1 8 CSB VREF13 VREF1 L2 D2 FromIxfrms 9 CSA CAOA12 CSA1 ToCSA1 10 PKLMT CAOB11 RS2 T2 1N RSY M2 CZV RPK1 CZC CZC MO CREF CPV RI CPC CPC RPK2 CSS RZV RZC RZC VOUT RZC RZC RA COUT CPC CPC CREF RB CZC CZC Vin L3 D3 ToCSA2 2N RSY 10 PKLMT CAOB11 RS3 T3 CSA2 9 CSA CAOA12 FromIxfrms 8 CSB VREF13 VREF2 CSB2 M3 7 RSYNTH GDA14 6 IMO VCC15 12Vto21V 5 VINAC GND16 4 VSENSE GDB17 L4 3 VAO SS 18 D4 RRT2 2 RDM RT 19 ToCSB2 1 CDR DMAX20 Synchronized RDMX2 RS4 T4 Clocks with 180° PhaseShift M4 Copyright © 2016,Texas Instruments Incorporated Figure18. SimplifiedFour-PhaseApplicationDiagramUsingTwoUCC28070ADevices 18 SubmitDocumentationFeedback Copyright©2012–2016,TexasInstrumentsIncorporated ProductFolderLinks:UCC28070A

UCC28070A www.ti.com SLUSAW0A–MARCH2012–REVISEDMAY2016 Feature Description (continued) 7.3.8 CurrentSynthesizer One of the most prominent innovations in the UCC28070A design is the current synthesizer circuitry that synchronouslymonitorstheinstantaneousinductorcurrentthroughacombinationofON-timesamplingandOFF- timedown-slopeemulation. During the ON-time of the GDA and GDB outputs, the inductor current is recorded at the CSA and CSB pins, respectively, through the current transformer network in each output phase. Meanwhile, the continuous monitoring of the input and output voltages through the VINAC and VSENSE pins permits the UCC28070A to internallyrecreatethedown-slopeoftheinductorcurrentduringtherespectiveOFF-timeofeachoutput.Through the selection of the RSYNTH resistor (R ), based on Equation 12, the internal response may be adjusted to SYN accommodatethewiderangeofinductancesexpectedacrossthewidearrayofapplications. During inrush surge events at power up and AC drop-out recovery, V < V , the synthesized downslope VSENSE VINAC becomes zero. In this case, the synthesized inductor current remains above the IMO reference and the current loop drives the duty cycle to zero. This avoids excessive stress on the MOSFETs during the surge event. Once V fallsbelowV ,thedutycycleincreasesuntilsteady-stateoperationresumes. VINAC VSENSE Waveformat Synthesized CSx input down-slope CurrentSynthesizer outputtoCA Figure19. DownslopeoftheInductorCurrent (10´N ´L (mH)´k ) R (kW)= CT B R SYN R (W) S where: • L =NominalZero-BiasBoostInductance(μH) B • R =SenseResistor(Ω) S • N =Current-senseTransformerturnsratio CT • k =R /(R +R )=theresistor-dividerattenuationattheVSENSEandVINACpins (12) R B A B Copyright©2012–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 19 ProductFolderLinks:UCC28070A

UCC28070A SLUSAW0A–MARCH2012–REVISEDMAY2016 www.ti.com Feature Description (continued) 7.3.9 ProgrammablePeakCurrentLimit The UCC28070A has been designed with a programmable cycle-by-cycle peak current limit dedicated to disabling either the GDA or GDB output whenever the corresponding current-sense input (CSA or CSB, respectively) rises above the voltage established on the PKLMT pin. Once an output has been disabled through the detection of peak current limit, the output remains disabled until the next clock cycle initiates a new PWM period. The programming range of the PKLMT voltage extends to upwards of 4 V to permit the full use of the 3-V average current sense signal range; however, note that the linearity of the current amplifiers begins to compress above3.6V. A resistor-divider network from VREF to GND can easily program the peak current limit voltage on PKLMT, provided the total current out of VREF is less than 2 mA to avoid drooping of the 6-V VREF voltage. TI recommends a load of less than 0.5 mA, but if the resistance on PKLMT is very high, TI recommends a small filtercapacitoronPKLMTtoavoidoperationalproblemsinhigh-noiseenvironments. PKLMT ExternallyProgrammablePeak 10 CurrentLimitlevel(PKLMT) IPEAKx + ToGate-Drive Shut-down CSx DI Current ToCurrent Synthesizer Amplifier 3VAverageCurrent-sense SignalRange,plusRipple Figure20. ExternallyProgrammablePeakCurrentLimit 7.3.10 LinearMultiplierandQuantizedVoltageFeedForward The UCC28070A multiplier generates a reference current which represents the desired wave shape and proportionalamplitudeoftheACinputcurrent.ThiscurrentisconvertedtoareferencevoltagesignalbytheR IMO resistor which is scaled in value to match the voltage of the current-sense signals. The instantaneous multiplier current is dependent upon the rectified, scaled input voltage V and the voltage-error amplifier output V . VINAC VAO V conveysthreepiecesofinformationtothemultiplier: VINAC • Theoverallwave-shapeoftheinputvoltage(typicallysinusoidal) • Theinstantaneousinputvoltagemagnitudeatanypointinthelinecycle • Thermsleveloftheinputvoltage. V representsthetotaloutputpowerofthePFCpreregulator. VAO A major innovation in the UCC28070A multiplier architecture is the internal quantized V feed-forward (Q ) RMS VFF circuitry, which eliminates the requirement for external filtering of the VINAC signal and the subsequent slow response to transient line variations. A unique circuit algorithm detects the transition of the peak of V VINAC through seven thresholds and generates an equivalent VFF level centered within the 8-Q ranges. The VFF boundaries of the ranges expand with increasing V to maintain an approximately equal-percentage delta IN betweenlevels.These8-Q levelsarespacedtoaccommodatethefulluniversallinerangeof85to265V . VFF RMS 20 SubmitDocumentationFeedback Copyright©2012–2016,TexasInstrumentsIncorporated ProductFolderLinks:UCC28070A

UCC28070A www.ti.com SLUSAW0A–MARCH2012–REVISEDMAY2016 Feature Description (continued) A great benefit of the Q architecture is that the fixed k factors eliminate any contribution to distortion of the VFF VFF multiplier output, unlike an externally-filtered VINAC signal which unavoidably contains 2nd-harmonic distortion components. Furthermore, the Q algorithm allows for rapid response to both increasing and decreasing VFF changes in input rms voltage so that disturbances transmitted to the PFC output are minimized. 5% hysteresis in the level thresholds help avoid chattering between Q levels for V voltage peaks near a particular VFF VINAC threshold or containing mild ringing or distortion. The Q architecture requires that the input voltage be largely VFF sinusoidal, and relies on detecting zero-crossings to adjust Q downward on decreasing input voltage. Zero- VFF crossingsaredefinedasV fallingbelow0.7Vforatleast50μs,typically. VINAC Table 1 shows the relationship between the various V peak voltages and the corresponding k terms for VINAC VFF themultiplierequation. Table1.V PeakVoltages VINAC LEVEL V PEAKVOLTAGE k (V2) V PEAKVOLTAGE (1) VINAC VFF IN 8 2.6V≤V 3.857 >345V VINAC(pk) 7 2.25V≤V <2.6V 2.922 300Vto345V VINAC(pk) 6 1.95V≤V <2.25V 2.199 260Vto300V VINAC(pk) 5 1.65V≤V <1.95V 1.604 220Vto260V VINAC(pk) 4 1.4V≤V <1.65V 1.156 187Vto220V VINAC(pk) 3 1.2V≤V <1.4V 0.839 160Vto187V VINAC(pk) 2 1V≤V <1.2V 0.6 133Vto160V VINAC(pk) 1 V ≤1V 0.398 <133V VINAC(pk) (1) TheV peakvoltageboundaryvalueslistedabovearecalculatedbasedona400-VPFCoutputvoltageandtheuseofamatched IN resistor-dividernetwork(k =3V/400V=0.0075)onVINACandVSENSE(asrequiredforcurrentsynthesis).WhenV isdesigned R OUT tobehigherorlowerthan400V,k =3V/V ,andtheV peakvoltageboundaryvaluesforeachQ leveladjustto R OUT IN VFF V /k . VINAC(pk) R ThemultiplieroutputcurrentI foranylineandloadconditioncanthusbedeterminedusingEquation13: IMO 17mA´(V )´(V -1) I = VINAC VAO IMO k VFF (13) Because the k value represents the scaled (V )2 at the center of a level, V adjusts slightly upwards or VFF RMS VAO downwards when V is either lower or higher than the center of the Q voltage range to compensate for VINAC(pk) VFF the difference. This is automatically accomplished by the voltage loop control when V varies, both within a level IN andafteratransitionbetweenlevels. The output of the voltage-error amplifier (V ) is clamped at 5 V, which represents the maximum PFC output VAO power. This value is used to calculate the maximum reference current at the IMO pin, and sets a limit for the maximuminputpowerallowed(and,asaconsequence,limitsmaximumoutputpower). Unlike a continuous V situation, where maximum input power is a fixed power at any V input, the discrete FF RMS Q levels permit a variation in maximum input power within limited boundaries as the input V varies within VFF RMS eachlevel. The lowest maximum power limit occurs at the V voltage of 0.76 V, while the highest maximum power limit VINAC occurs at the increasing threshold from level-1 to level-2. This pattern repeats at every level transition threshold, considering that decreasing thresholds are 95% of the increasing threshold values. Below V = 0.76 V, P is VINAC IN alwayslessthanP ,fallinglinearlytozerowithdecreasinginputvoltage. IN(max) Forexample,todesignforthelowestmaximumpowerallowable,determinethemaximumsteady-state(average) output power required of the PFC preregulator and add some additional percentage to account for line drop-out recovery power (to recharge C while full load power is drawn) such as 10% or 20% of P . Then apply OUT OUT(max) theexpectedefficiencyfactortofindthelowestmaximuminputpowerallowable: 1.1´P P = OUT(max) IN(max) h (14) Copyright©2012–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 21 ProductFolderLinks:UCC28070A

UCC28070A SLUSAW0A–MARCH2012–REVISEDMAY2016 www.ti.com At the P design threshold, V = 0.76 V, hence Q = 0.398 and input V = 73 V (accounting for IN(max) VINAC VFF AC RMS 2‑Vbridge-rectifierdrop)foranominal400-Voutputsystem. P I = IN(max) IN(rms) 73 V RMS (15) I =1.414´I IN(pk) IN(rms) (16) This I value represents the combined average current through the boost inductors at the peak of the line IN(pk) voltage. Each inductor current is detected and scaled by a current-sense transformer (CT). Assuming equal currents through each interleaved phase, the signal voltage at each current sense input pin (CSA and CSB) is developed across a sense resistor selected to generate approximately 3 V based on ½ I × R / N , where IN(pk) S CT R isthecurrentsenseresistorandN istheCTturns-ratio. S CT I isthencalculatedatthatsamelowestmaximum-powerpoint,as: IMO (0.76 V)(5 V-1V) I =17mA´ =130mA IMO(max) 0.398 (17) R isselectedsuchthat: IMO R R ´I = 1´I ´ S IMO IMO(max) 2 IN(pk) N CT (18) Therefore: ( ) 1´I ´R R = 2 IN(pk) S IMO ( ) N ´I CT IMO(max) (19) At the increasing side of the level-1 to level-2 threshold, note that the IMO current would allow higher input currentsatlow-line: (1V)(5 V-1V) I =17mA´ =171mA IMO(L1-L2) 0.398 (20) However, this current may easily be limited by the programmable peak current limiting (PKLMT) feature of the UCC28070Aifrequiredbythepowerstagedesign. The same procedure can be used to find the lowest and highest input power limits at each of the Q level VFF transition thresholds. At higher line voltages, where the average current with inductor ripple is traditionally below the PKLMT threshold, the full variation of maximum input power is seen, but the input currents are inherently belowthemaximumacceptablecurrentlevelsofthepowerstage. The performance of the multiplier in the UCC28070A has been significantly enhanced when compared to previous generation PFC controllers, with high linearity and accuracy over most of the input ranges. The accuracy is at its worst as V approaches 1 V because the error of the (V – 1) subtraction increases and VAO VAO beginstodistorttheIMOreferencecurrenttoagreaterdegree. 7.3.11 EnhancedTransientResponse(VASlew-RateCorrection) Due to the low-voltage loop bandwidth required to maintain proper PFC and ignore the slight ripple at twice line frequency on the output, the response of ordinary controllers to input voltage and load transients are also slow. However, the Q function effectively handles the line transient response with the exception of any minor VFF adjustments needed within a Q level. Load transients on the other hand can only be handled by the voltage VFF loop; therefore, the UCC28070A has been designed to improve its transient response by pulling up on the output of the voltage amplifier (V ) with an additional 100 μA of current in the event the voltage on VSENSE drops VAO below 93% of regulation (2.79 V). During a soft-start cycle, when V is ramping up from the 0.75-V PFC VSENSE Enable threshold, the 100-μA correction current source is disabled to ensure the gradual and controlled ramping ofoutputvoltageandcurrentduringasoftstart. 22 SubmitDocumentationFeedback Copyright©2012–2016,TexasInstrumentsIncorporated ProductFolderLinks:UCC28070A

UCC28070A www.ti.com SLUSAW0A–MARCH2012–REVISEDMAY2016 7.3.12 VoltageBiasing(V andV ) CC VREF The UCC28070A operates within a V bias supply range of 10 V to 21 V. An undervoltage lockout (UVLO) CC threshold prevents the PFC from activating until V > 10.2 V, and 1 V of hysteresis assures reliable start-up CC from a possibly low-compliance bias source. An internal 25-V Zener-like clamp on the VCC pin is intended only to protect the device from brief energy-limited surges from the bias supply, and must not be used as a regulator withacurrent-limitedsource. At minimum, a 0.1-μF ceramic bypass capacitor must be applied from VCC to GND close to the device pins to provide local filtering of the bias supply. Larger values may be required depending on I peak current CC magnitudesanddurationstominimizeripplevoltageonVCC. To provide a smooth transition out of UVLO and to make the 6-V voltage reference available as early as possible,theoutputfromVREFisenabledwhenV exceeds8Vtypically. CC The VREF circuitry is designed to provide the biasing of all internal control circuits and for limited use externally. At minimum, a 22-nF ceramic bypass capacitor must be applied from VREF to GND close to the device pins to ensure stability of the circuit. External load current on the VREF pin must be limited to less than 2 mA, or degradedregulationmayresult. 7.3.13 PFCEnableandDisable The UCC28070A contains two independent circuits dedicated to disabling the GDx outputs based on the biasing conditions of the VSENSE or SS pins. The first is a PFC Enable which monitors V and holds off soft start VSENSE and the overall PFC function until the output has precharged to approximately 25%. Before V reaching VSENSE 0.75 V, almost all of the internal circuitry is disabled. Once V reaches 0.75 V and V < 0.75 V, the VSENSE VAO oscillator, multiplier, and current synthesizer are enabled and the SS circuitry begins to ramp up the voltage on the SS pin. The second circuit provides an external interface to emulate an internal fault condition to disable the GDx output without fully disabling the voltage loop and multiplier. By externally pulling the SS pin below 0.6 V, the GDx outputs are immediately disabled and held low. Assuming no other fault conditions are present, normal PWM operation resumes when the external SS pulldown is released. The external pulldown must be sized large enough to override the internal 1.5-mA adaptive SS pullup once the SS voltage falls below the disable threshold. TI recommends using a MOSFET with less than 100-Ω R resistance to ensure the SS pin is held DS(on) adequatelybelowthedisablethreshold. 7.3.14 AdaptiveSoftStart To maintain a controlled power up, the UCC28070A has been designed with an adaptive soft-start function that overridestheinternalreferencevoltagewithacontrolledvoltagerampduringpowerup.Oninitialpowerup,once V exceeds the 0.75-V enable threshold (V ), the internal pulldown on the SS pin is released, and the VSENSE EN 1.5‑mA adaptive soft-start current source is activated. This 1.5-mA pullup almost immediately pulls the SS pin to 0.75V(V )tobypasstheinitial25%ofdeadtimeduringatraditional0VtoV SSramp.Oncethe VSENSE REGULATION SS pin has reached the voltage on VSENSE, the 10-μA soft-start current (I ) takes over. Thus, through the SS selection of the soft-start capacitor (C ), the effective soft-start time (t ) may be easily programmed based on SS SS Equation21. æ2.25 Vö t =C ´ SS SS çè 10mA ÷ø (21) Often, a system restart is desired following a brief shutdown. In such a case, VSENSE may still have substantial voltage if V has not fully discharged or if high line has peak charged C . To eliminate the delay caused by OUT OUT chargingC from0VuptotheprechargedV withonlythe10-μAcurrentsourceandminimizeanyfurther SS VSENSE output voltage sag, the adaptive soft start uses a 1.5-mA current source to rapidly charge C to V , after SS VSENSE which time the 10-μA source controls the V rise at the desired soft-start ramp rate. In such a case, t is SS SS estimatedasfollows: æ3 V-V ö t =C ´ VSENSE0 SS SS çè 10mA ÷ø where • V isthevoltageatVSENSEatthemomentasoftstartorrestartisinitiated (22) VSENSE0 Copyright©2012–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 23 ProductFolderLinks:UCC28070A

UCC28070A SLUSAW0A–MARCH2012–REVISEDMAY2016 www.ti.com NOTE For soft start to be effective and avoid overshoot on V , the SS ramp must be slower OUT thanthevoltage-loopcontrolresponse.ChooseC ≥C toensurethis. SS VZ (V) V SS V VSENSE VSSifnoadaptivecurrent Time(s) PFCexternally Reduceddelaytoregulation disableddueto AC-Linerecovers AC-linedrop-out andSSpinreleased Figure21. Soft-StartRampRate 7.3.15 PFCStart-UpHoldOff An additional feature designed into the UCC28070A is the Start-Up Hold Off logic that prevents the device from initiating a soft-start cycle until the VAO pin is below the zero-power threshold (0.75 V). This feature ensures that theSScycleinitiatesfromzero-powerandzeroduty-cyclewhilepreventingthepotentialforanysignificantinrush currentsduetostoredchargeintheVAOcompensationnetwork. 7.3.16 OutputOvervoltageProtection(OVP) Because of the high voltage output and a limited design margin on the output capacitor, output overvoltage protection is essential for PFC circuits. The UCC28070A implements OVP through the continuous monitoring of V . In the event V rises above 106% of regulation (3.18 V), the GDx outputs are immediately VSENSE VSENSE disabled to prevent the output voltage from reaching excessive levels. Meanwhile the CAOx outputs are pulled low to ensure a controlled recovery starting from 0% duty-cycle after an OVP fault is released. Once V has VSENSE droppedbelow3.08V,thePWMoperationresumesnormaloperation. 7.3.17 Zero-PowerDetection To prevent undesired performance under no-load and near no-load conditions, the UCC28070A zero-power detection comparator is designed to disable both GDA and GDB outputs in the event V voltage falls below VAO 0.75 V. The 150 mV of hysteresis ensures that the outputs remain disabled until V has nearly risen back into VAO thelinearrangeofthemultiplier(V ≥0.9V). VAO 7.3.18 ThermalShutdown To protect the power supplies from silicon failures at excessive temperatures, the UCC28070A has an internal temperature-sensing comparator that shuts down nearly all of the internal circuitry, and disables the GDA and GDB outputs, if the die temperature rises above 160°C. Once the die temperature falls below 140°C, the device bringstheoutputsupthroughatypicalsoftstart. 24 SubmitDocumentationFeedback Copyright©2012–2016,TexasInstrumentsIncorporated ProductFolderLinks:UCC28070A

UCC28070A www.ti.com SLUSAW0A–MARCH2012–REVISEDMAY2016 7.3.19 CurrentLoopCompensation The UCC28070A incorporates two identical and independent transconductance-type current-error amplifiers (one for each phase) with which to control the shaping of the PFC input current waveform. The current-error amplifier (CA) forms the heart of the embedded current control loop of the boost PFC preregulator, and is compensated for loop stability using familiar principles [4, 5]. The output of the CA for phase-A is CAOA, and that for phase-B is CAOB. Because the design considerations are the same for both, they are collectively referred to as CAOx, wherexisAorB. In a boost PFC preregulator, the current control loop comprises the boost power plant stage, the current sensing circuitry, the wave-shape reference, the PWM stage, and the CA with compensation components. The CA compares the average boost inductor current sensed with the wave-shape reference from the multiplier stage andgeneratesanoutputcurrentproportionaltothedifference. This CA output current flows through the impedance of the compensation network generating an output voltage, V , which is then compared with a periodic voltage ramp to generate the PWM signal necessary to achieve CAO PFC. IMO CAOx + CAx CSx – C Current g = 100 µs ZC CPC Synthesizer mC R ZC Copyright © 2016,Texas Instruments Incorporated Figure22. CurrentErrorAmplifierWithTypeIICompensation For frequencies above boost LC resonance and below f , the small-signal model of the boost stage, which PWM includescurrentsensing,canbesimplifiedto: v V ´ RS RS = OUT NCT v DV ´k ´s´L CA RMP SYNC B where: • L =mid-valueboostinductance B • R =CTsenseresistor S • N =CTturnsratio CT • V =averageoutputvoltage OUT • ∆V =4V amplitudeofthePWMvoltageramp RMP pk-pk • k =rampreductionfactor(ifPWMfrequencyissynchronizedtoanexternaloscillator;k =1,otherwise) SYNC SYNC • s=Laplacecomplexvariable (23) An R C network is introduced on CAOx to obtain high gain for the low-frequency content of the inductor ZC ZC current signal, but reduced flat gain above the zero frequency out to f to attenuate the high-frequency PWM switchingripplecontentofthesignal(thusaveragingit). The switching ripple voltage must be attenuated to less than 1/10 of the ΔV amplitude so as to be considered RMP negligibleripple. Thus,CAOxgainatf is: PWM DV ´k RMP SYNC g ´Rzc £ 10 mc DI ´ RS LB N CT where: • ∆I isthemaximumpeak-to-peakripplecurrentintheboostinductor LB • g isthetransconductanceoftheCA,100μS (24) mc Copyright©2012–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 25 ProductFolderLinks:UCC28070A

UCC28070A SLUSAW0A–MARCH2012–REVISEDMAY2016 www.ti.com 4 V´N Rzc £ CT 10´100ms´DI ´R LB S (25) Thecurrent-loopcross-overfrequencyisthenfoundbyequatingtheopenloopgainto1andsolvingforf : CXO V ´ RS f = OUT NCT ´g ´Rzc CXO DV ´k ´2p´L mc RMP SYNC B (26) C is then determined by setting f = f = 1 / (2πR × C ) and solving for C . At f = f , a phase CZ ZC CXO ZC ZC ZC ZC CXO marginof45° isobtainedatf .Greaterphasemarginmaybehadbyplacingf <f . CXO ZC CXO An additional high-frequency pole is generally added at f to further attenuate ripple and noise at f and PWM PWM higher.Thisisdonebyaddingasmall-valuecapacitor,C ,acrosstheR C network. pc zc zc 1 Cpc = 2p´f ´Rzc PWM (27) Theprocedureaboveisvalidforfixed-valueinductors. NOTE If a swinging-choke boost inductor (inductance decreases with increasing current) is used, f varieswithinductance,soC mustbedeterminedatmaximuminductance. CXO ZC 7.3.20 VoltageLoopCompensation The outer voltage control loop of the dual-phase PFC controller functions the same as with a single-phase controller, and compensation techniques for loop stability are standard [4]. The bandwidth of the voltage-loop must be considerably lower than the twice-line ripple frequency (f ) on the output capacitor to avoid distortion- 2LF causing correction to the output voltage. The output of the voltage-error amplifier (V ) is an input to the VAO multiplier to adjust the input current amplitude relative to the required output power. Variations on VAO within the bandwidth of the current loops influences the wave-shape of the input current. Because the low-frequency ripple on C is a function of input power only, its peak-to-peak amplitude is the same at high-line as at low-line. Any OUT response of the voltage-loop to this ripple has a greater distorting effect on high-line current than on low-line current. Therefore, the allowable percentage of 3rd-harmonic distortion on the input current contributed by VAO mustbedeterminedusinghigh-lineconditions. Because the voltage-error amplifier (VA) is a transconductance type of amplifier, the impedance on its input has no bearing on the amplifier gain, which is determined solely by the product of its transconductance (g ) with its mv output impedance (Z ). Thus, the VSENSE input divider-network values are determined separately based on OV criteriadiscussedinVSENSEandVINACOpen-CircuitProtection.ItsoutputistheVAOpin. VAO 3 V + VA – C ZV C VSENSE gmv= 70 µs PV R ZV Copyright © 2016,Texas Instruments Incorporated Figure23. VoltageErrorAmplifierWithTypeIICompensation The twice-line ripple voltage component of V must be sufficiently attenuated and phase-shifted at VAO to VSENSE achieve the desired level of 3rd-harmonic distortion of the input current wave-shape [4]. For every 1% of 3rd- harmonic input distortion allowable, the small-signal gain G = V / v = g × Z at the twice-line VEA VAOpk SENSEpk mv OV frequency must allow no more than 2% ripple over the full V voltage range. In the UCC28070A, V can VAO VAO range from 1 V at zero load power to approximately 4.2 V at full load power for a ΔV = 3.2 V, so 2% of 3.2 V VAO is64-mVpeakripple. 26 SubmitDocumentationFeedback Copyright©2012–2016,TexasInstrumentsIncorporated ProductFolderLinks:UCC28070A

UCC28070A www.ti.com SLUSAW0A–MARCH2012–REVISEDMAY2016 NOTE Although the maximum V is clamped at 5 V, at full load V may vary around an VAO VAO approximate center point of 4.2 V to compensate for the effects of the quantized feed- forward voltage in the multiplier stage (see Linear Multiplier and Quantized Voltage Feed Forward for details). Therefore, 4.2 V is the proper voltage to use to represent maximum outputpowerwhenperformingvoltage-loopgaincalculations. Theoutputcapacitormaximumlow-frequency,zero-to-peak,ripplevoltageiscloselyapproximatedby: P ´X P v = IN(avg) Cout = IN(avg) 0pk V V ´2p´f ´C OUT(avg) OUT(avg) 2LF OUT where: • P isthetotalmaximuminputpoweroftheinterleaved-PFCpreregulator IN(avg) • V istheaverageoutputvoltage OUT(avg) • C istheoutputcapacitance (28) OUT V =v ×k SENSEpk opk R where • k isthegainoftheresistor-dividernetworkonVSENSE (29) R Thus, for k , the percentage of allowable 3rd-harmonic distortion on the input current attributable to the VAO 3rd ripple, k ´64mV´V ´2p´f ´C Z = 3rd OUT(avg) 2LF OUT OV(f2LF) g ´k ´P mv R IN(avg) (30) ThisimpedanceonVAOissetbyacapacitor(C ),whereC =1/(2πf × Z (f ));therefore: PV PV 2LF OV 2LF g ´k ´P Cpv = mv R IN(avg) k ´64mV´V ´(2p´f )2´C 3rd OUT(avg) 2LF OUT (31) The voltage-loop unity-gain cross-over frequency (f ) may now be solved by setting the open-loop gain equal VXO to1: æ P ´X ö Tv(f )=G ´G ´k =ç IN(avg) Cout ÷´(g ´X )´k =1 VXO BST VEA R çDV ´V ÷ mv Cpv R è VAO OUT(avg) ø (32) g ´k ´P f 2 = mv R IN(avg) VXO DV ´V ´(2p)2´Cpv´C so, VAO OUT(avg) OUT (33) The zero-resistor (R ) from the zero-placement network of the compensation may now be calculated. Together ZV withC ,R setsapolerightatf toobtain45° phasemarginatthecross-over. PV ZV VXO 1 Rzv = 2p´f ´Cpv Thus, VXO (34) Finally, a zero is placed at or below f / 6 with capacitor C to provide high gain at DC but with a breakpoint VXO ZV far enough below f so as not to significantly reduce the phase margin. Choosing f / 10 allows one to VXO VXO approximatetheparallelcombinationvalueofC andC asC ,andsolveforC simplyas: ZV PV ZV ZV 10 Czv = »10´Cpv 2p´f ´Rzv VXO (35) By using a spreadsheet or math program, C , R , and C may be manipulated to observe their effects on f ZV ZV PV VXO and phase margin and the percentage contribution to 3rd-harmonic distortion. Also, phase margin may be checkedasP levelandsystemparametertolerancesvary. IN(avg) Copyright©2012–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 27 ProductFolderLinks:UCC28070A

UCC28070A SLUSAW0A–MARCH2012–REVISEDMAY2016 www.ti.com NOTE The percent of 3rd-harmonic distortion calculated in this section represents the contribution from the f voltage ripple on C only. Other sources of distortion, such as 2LF OUT the current-sense transformer, the current synthesizer stage, even distorted V , and so IN on,cancontributeadditional3rdandhigherorderharmonicdistortion. 7.4 Device Functional Modes The UCC28070A operates in Average Current Mode. This eliminates the peak-to-average current error inherent inthepeakcurrentmodecontrolmethodandgiveslowerTHDandharmonicsonthecurrentdrawnfromtheline. Itdoesnotrequireslopecompensationandhasbetternoiseimmunitythanthepeakcurrentcontrolmethod. 28 SubmitDocumentationFeedback Copyright©2012–2016,TexasInstrumentsIncorporated ProductFolderLinks:UCC28070A

UCC28070A www.ti.com SLUSAW0A–MARCH2012–REVISEDMAY2016 8 Application and Implementation NOTE Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validateandtesttheirdesignimplementationtoconfirmsystemfunctionality. 8.1 Application Information The UCC28070A is a switch-mode controller used in interleaved boost converters for power factor correction. The UCC28070A requires few external components to operate as an active PFC preregulator. It operates at a fixed frequency in continuous conduction mode. The operating switching frequency can be programmed from 30 kHz to 300 kHz by a single resistor from the RT pin to ground. The magnitude and rate of optional frequency dithering may also be controlled easily. The internal 5-V reference voltage provides for accurate output voltage regulation over the typical world-wide 85-V to 265-V mains input range from zero to full output load. The AC AC reference may also be used to set a peak current limit. Regulation is accomplished in two loops. The inner current loop shapes the average input current to match the sinusoidal input voltage under continuous inductor current conditions. A single multiplier output is shared between the two current amplifiers to ensure close matching of the currents in the two phases. A Zero-Power detector disables both the GDA and GDB outputs underlight-loadconditions. 8.2 Typical Application VIN L1 D1 V OUT + C OUT 12Vto21V – ToCSB CCDR 1 CDR DMAX 20 R T1 R S RRDM 2 RDM RT 19 DMX R R RT A 3 VAO SS 18 CSS M1 4 VSENSE GDB17 5 VINAC GND16 RIMO 6 IMO VCC15 RB RSYN 7 RSYNTH GDA14 L2 8 CSB VREF13 D2 9 CSA CAOA 12 ToCSA 10 PKLMT CAOB 11 R T2 FromIxfrms S CZV RPK1 C CZC CZC RA REF CPV CPC CPC M2 R PK2 R R R R B ZV ZC ZC Copyright © 2016,Texas Instruments Incorporated Figure24. TypicalApplicationDiagram Copyright©2012–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 29 ProductFolderLinks:UCC28070A

UCC28070A SLUSAW0A–MARCH2012–REVISEDMAY2016 www.ti.com Typical Application (continued) 8.2.1 DesignRequirements Forthisdesignexample,usetheparameterslistedinTable2astheinputparameters. Table2.DesignParameters DESIGNPARAMETER MIN TYP MAX UNIT V Inputvoltage 85 265 V AC V Outputvoltage 390 V OUT f Linefrequency 47 63 Hz LINE f Switchingfrequency 200 kHz SW P Outputpower 300 W OUT η Fullloadefficiency 90% 8.2.2 DetailedDesignProcedure 8.2.2.1 OutputCurrentCalculation Thefirststepistodeterminethemaximumloadcurrentontheoutput. P 300W I = o = =0.78A o V 385V o (36) 8.2.2.2 BridgeRectifier ThemaximumRMSinput-linecurrentisgivenbyEquation37: P 300W I = o = =3.6Arms line_max hV 98%(85V) AC_min (37) ThepeakinputcurrentisgivenbyEquation38: I = 2´I = 2´3.6A =5.1A in_pk line_max (38) ThemaximumaveragerectifiedlinecurrentisgivenbyEquation39: 2 2 2 2 I = ´I = ´3.6A =3.25A in_avg_max p line_max p (39) A typical bridge rectifier has a forward voltage drop V of 0.95 V. The power loss in the rectifier bridge can be F calculatedbyEquation40: P =2´V ´I =2´0.95V´3.25A =6.2W BR_max F in_avg_max (40) The bridge rectifier must be rated to carry the full line current. The voltage rating of the bridge must be at least 600 V. The bridge rectifier also carries the full inrush current as the bulk capacitor C charges when line is OUT connected. 30 SubmitDocumentationFeedback Copyright©2012–2016,TexasInstrumentsIncorporated ProductFolderLinks:UCC28070A

UCC28070A www.ti.com SLUSAW0A–MARCH2012–REVISEDMAY2016 8.2.2.3 PFCInductor(L andL ) 1 2 The selection of the PFC inductor value may be based on a number of different considerations. Cost, core size, EMI filter, and inductor ripple current are some of the factors that have an influence. For this design we choose the inductor so that at the minimum input voltage the peak to peak ripple (ΔI ) has the same amplitude as the L peak of line current in each phase. The line current flows equally in the two phases so ΔI is half I calculated I in_pk inEquation38.TheinductoriscalculatedbyEquation41. V ´D(1-D) 385V´0.7(1-0.7) L = OUT = »160µH 1 f ´DI 5.1A sw L 200kHz´ 2 where • V isthePFCstageoutputvoltage OUT • f istheswitchingfrequency SW • ΔI istheallowedpeak-to-peakripplecurrent. (41) L DisthePFCstagedutycycleat120V (peakof85Vrmsline)andisgivenbyEquation42: IN V D=1- IN V OUT (42) Thepeakcurrentineachboostinductoristhen: I =Iin_pk + DIL = 5.1A +5.1A =3.8A L_pk 2 2 2 4 (43) Theinductorspecificationsare: • Inductance:160µH • Current:4A 8.2.2.4 PFCMOSFETs(M andM ) 1 2 ThemainspecificationsforthePFCMOSFETsare: • B ,drainsourcebreakdownvoltage:≥650V VDSS • R ,ON-statedrainsourceresistance:520mΩ at25°C,estimate1Ω at125°C DS(on) • C ,outputcapacitance:32pF DSS • tr,deviserisetime:12ns • tf,devicefalltime:16ns The losses in the device are calculated by Equation 44 and Equation 45. These calculations are approximations because the losses are dependent on parameters which are not well controlled. For example, the R of a DS(on) MOSFET can vary by a factor of 2 from 25°C to 125°C. Therefore several iterations may be needed to choose anoptimumdeviceforanapplicationdifferentthantheonediscussed. Eachphasecarrieshalftheloadpowersotheconductionlossesareestimatedby: P =æç 0.5´Po ´ 2-16´ 2´VIN(min) ÷ö2´R =æç 150W ´ 2-16´ 2´85V ö÷2´1.0=2.25W M_cond ç 2´V 3p V ÷ DS(on) ç 2´85V 3p 385V ÷ è IN(min) OUT ø è ø (44) TheswitchinglossesineachMOSFETareestimatedby: PM_sw = 21´fSWççèæVo´Iline_2max ´(tr +tf)+Coss´Vo2÷÷øö= 21´200kHzçèæ385V´3.26A´(12ns+16ns)+32pF´385V2ö÷ø=2.4W (45) ThetotallossesineachMOSFETarethen: P =P +P =2.25W+2.4W =4.9W M M_cond M_sw (46) Copyright©2012–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 31 ProductFolderLinks:UCC28070A

UCC28070A SLUSAW0A–MARCH2012–REVISEDMAY2016 www.ti.com 8.2.2.5 PFCDiode Reverse recovery losses can be significant in a CCM boost converter. A silicon-carbide diode is chosen here becauseithasnoreverserecoverycharge(Q )andthereforezeroreverserecoverylosses. RR I 0.78A P = V ´ OUT =1.5V´ =580mW D f 2 2 (47) 8.2.2.6 PFCOutputCapacitor Thevalueoftheoutputcapacitorisgovernedbytherequiredhold-uptimeandtheallowablerippleontheoutput. Thehold-uptimedependsontheloadcurrentandtheminimumacceptablevoltageattheoutput. The value of the output capacitor must be large enough to provide the required hold-up time and keep the ripple voltage at twice line frequency within acceptable limits. Normally a capacitance value of about 0.6 μF per Watt of output power is a reasonable compromise where hold-up time is not significant. At 300 W this would indicate a capacitanceofabout200 μF. Thelowfrequency(attwicelinefrequency)rmsvoltagerippleonV isgivenbyEquation48: OUT 1 I 1 0.78A V = ´ o = ´ =4.4Vrms o_ripple 2 2 2p´fline´Co 2 2 2p´50Hz´200µF (48) Theresultinglowfrequencycurrentinthecapacitoris: I =2p´f ´C ´V =4p´100Hz´200µF´4.4V =1.1Arms o_ripple lf o o_ripple (49) 8.2.2.7 CurrentLoopFeedbackConfiguration (SizingoftheCurrentTransformerTurnsRatioandSenseResistor(R ) S A current-sense transformer (CT) is typically used in high-power applications to sense inductor current and avoid the losses inherent in the use of a current sensing resistor. For average current-mode control, the entire inductor current waveform is required; however low-frequency CTs are obviously impracticable. Normally, two high- frequency CTs are used, one in the switching leg to obtain the up-slope current and one in the diode leg to obtain the down-slope current. These two current signals are summed together to form the entire inductor current,butthisisnotnecessarywiththeUCC28070A. A major advantage of the UCC28070A design is the current synthesis function, which internally recreates the inductor current down-slope during the switching period OFF-time. This eliminates the need for the diode-leg CT in each phase, significantly reducing space, cost and complexity. A single resistor programs the synthesizer downslope,aspreviouslydiscussedintheCurrentSynthesizersection. A number of trade-offs must be made in the selection of the CT. Various internal and external factors influence thesize,cost,performance,anddistortioncontributionoftheCT. Thesefactorsinclude,butarenotlimitedto: • Turns-ratio(N ) CT • Magnetizinginductance(L ) M • Leakageinductance(L ) LK • Volt-microsecondproduct(Vμs) • Distributedcapacitance(C ) d • Seriesresistance(R ) SER • Externaldiodedrop(V ) D • Externalcurrentsenseresistor(R ) S • Externalresetnetwork Traditionally, the turns-ratio and the current sense resistor are selected first. Some iterations may be needed to refinetheselectiononcetheotherconsiderationsareincluded. In general, 50 ≤ N ≤ 200 is a reasonable range from which to choose. If N is too low, there may be high CT CT power loss in R and insufficient L . If too high, there could be excessive L and C . (A one-turn primary S M LK d windingisassumed.) 32 SubmitDocumentationFeedback Copyright©2012–2016,TexasInstrumentsIncorporated ProductFolderLinks:UCC28070A