ICGOO在线商城 > 集成电路(IC) > 线性 - 音頻放大器 > TPA751DGN

- 型号: TPA751DGN

- 制造商: Texas Instruments

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

TPA751DGN产品简介:

ICGOO电子元器件商城为您提供TPA751DGN由Texas Instruments设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 TPA751DGN价格参考¥6.35-¥14.29。Texas InstrumentsTPA751DGN封装/规格:线性 - 音頻放大器, Amplifier IC 1-Channel (Mono) Class AB 8-MSOP-PowerPad。您可以下载TPA751DGN参考资料、Datasheet数据手册功能说明书,资料中有TPA751DGN 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC)半导体 |

| 描述 | IC AMP AUDIO PWR .7W MONO 8MSOP音频放大器 Mono Diff Input Class-AB |

| DevelopmentKit | TPA751EVM |

| 产品分类 | |

| 品牌 | Texas Instruments |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 音频 IC,音频放大器,Texas Instruments TPA751DGN- |

| 数据手册 | |

| 产品型号 | TPA751DGN |

| THD+噪声 | 0.55 % |

| 不同负载时的最大输出功率x通道数 | 700mW x 1 @ 8 欧姆 |

| 产品 | Class-AB |

| 产品种类 | 音频放大器 |

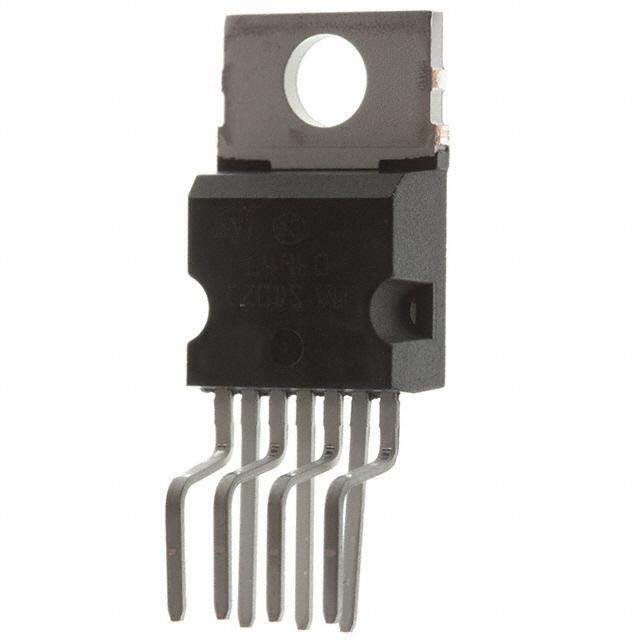

| 供应商器件封装 | 8-MSOP-PowerPad |

| 其它名称 | 296-34565-5 |

| 包装 | 管件 |

| 单位重量 | 19 mg |

| 商标 | Texas Instruments |

| 增益带宽生成 | 1.4 MHz |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装 | Tube |

| 封装/外壳 | 8-TSSOP,8-MSOP(0.118",3.00mm 宽)裸焊盘 |

| 封装/箱体 | HVSSOP-8 |

| 工作温度 | -40°C ~ 85°C (TA) |

| 工作电源电压 | 2.5 V to 5.5 V |

| 工厂包装数量 | 80 |

| 最大功率耗散 | 2140 mW |

| 最大工作温度 | + 85 C |

| 最小工作温度 | - 40 C |

| 标准包装 | 80 |

| 特性 | 差分输入,短路保护和热保护,关机 |

| 电压-电源 | 2.5 V ~ 5.5 V |

| 电源电压-最大 | 5.5 V |

| 电源电压-最小 | 2.5 V |

| 电源电流 | 1.45 mA |

| 电源类型 | Single |

| 类型 | AB 类 |

| 系列 | TPA751 |

| 输入信号类型 | Differential |

| 输出信号类型 | Differential |

| 输出功率 | 0.7 W |

| 输出类型 | 1-通道(单声道) |

| 配用 | /product-detail/zh/TPA751EVM/296-13570-ND/486529 |

| 音频负载电阻 | 8 Ohms |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

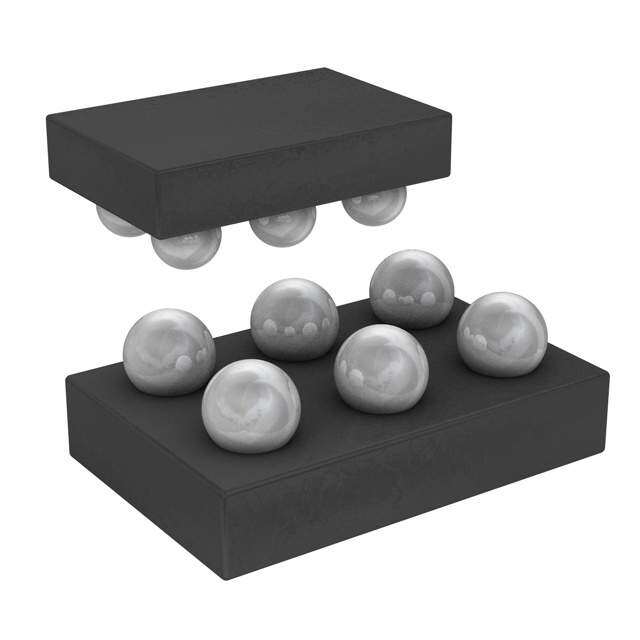

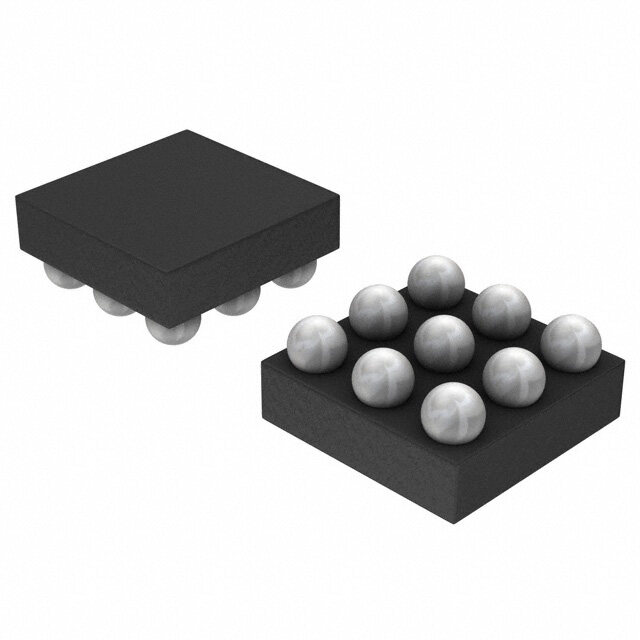

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6) (cid:4)(cid:7)(cid:7)(cid:8)(cid:9)(cid:10) (cid:11)(cid:12)(cid:13)(cid:12) (cid:14)(cid:12)(cid:10)(cid:8)(cid:15)(cid:12)(cid:14)(cid:1)(cid:3)(cid:16)(cid:17) (cid:3)(cid:18)(cid:19)(cid:20)(cid:12) (cid:2)(cid:12)(cid:10)(cid:17)(cid:21) (cid:3)(cid:11)(cid:2)(cid:14)(cid:20)(cid:22)(cid:20)(cid:17)(cid:21) (cid:10)(cid:20)(cid:1)(cid:23) (cid:19)(cid:20)(cid:22)(cid:22)(cid:17)(cid:21)(cid:17)(cid:13)(cid:1)(cid:20)(cid:3)(cid:14) (cid:20)(cid:13)(cid:2)(cid:18)(cid:1)(cid:24) SLOS336C − DECEMBER 2000 − REVISED OCTOBER 2002 (cid:1) Fully Specified for 3.3-V and 5-V Operation D OR DGN PACKAGE (cid:1) (TOP VIEW) Wide Power Supply Compatibility 2.5 V − 5.5 V (cid:1) SHUTDOWN 1 8 VO− Power Supply Rejection at 217 Hz BYPASS 2 7 GND − 84 dB at VDD = 5 V IN+ 3 6 VDD − 81 dB at VDD = 3.3 V IN− 4 5 VO+ (cid:1) Output Power for R = 8 Ω L − 700 mW at VDD = 5 V MicroStar Junior(cid:2) (GQS) Package − 250 mW at VDD = 3.3 V (TOP VIEW) (cid:1) Ultralow Supply Current in Shutdown (E2) (A2) Mode...1.5 nA SHUTDOWN VO− (E3) (A3) (cid:1) BYPASS GND Thermal and Short-Circuit Protection IN+ (E4) (A4) VDD (cid:1) Surface-Mount Packaging IN− (E5) (A5) VO+ − SOIC − PowerPAD MSOP (SIDE VIEW) − MicroStar Junior (BGA) NOTE: The shaded terminals are used for thermal description connections to the ground plane. The TPA751 is a bridge-tied load (BTL) audio power amplifier developed especially for low-voltage applications where internal speakers are required. Operating with a 3.3-V supply, the TPA751 can deliver 250-mW of continuous power into a BTL 8-Ω load at less than 0.6% THD+N throughout voice band frequencies. Although this device is characterized out to 20 kHz, its operation is optimized for narrower band applications such as wireless communications. The BTL configuration eliminates the need for external coupling capacitors on the output in most applications, which is particularly important for small battery-powered equipment. This device features a shutdown mode for power-sensitive applications with a supply current of 1.5 nA during shutdown. The TPA751 is available in a 3.0 × 3.0 mm MicroStar Junior (BGA), 8-pin SOIC surface-mount package and a surface-mount PowerPAD MSOP. VDD 6 RF VDD Audio VDD/2 CS Input RI 4 IN− − VO+ 5 CI 3 IN+ + 2 BYPASS CB − VO− 8 700 mW + 7 GND 1 SHUTDOWN Bias From System Control Control Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet. PowerPAD and MicroStar Junior are trademarks of Texas Instruments. (cid:2)(cid:21)(cid:12)(cid:19)(cid:18)(cid:25)(cid:1)(cid:20)(cid:12)(cid:13) (cid:19)(cid:3)(cid:1)(cid:3) (cid:26)(cid:27)(cid:28)(cid:29)(cid:30)(cid:9)(cid:31)!(cid:26)(cid:29)(cid:27) (cid:26)" #$(cid:30)(cid:30)%(cid:27)! (cid:31)" (cid:29)(cid:28) &$’((cid:26)#(cid:31)!(cid:26)(cid:29)(cid:27) )(cid:31)!%* Copyright 2002, Texas Instruments Incorporated (cid:2)(cid:30)(cid:29))$#!" #(cid:29)(cid:27)(cid:28)(cid:29)(cid:30)(cid:9) !(cid:29) "&%#(cid:26)(cid:28)(cid:26)#(cid:31)!(cid:26)(cid:29)(cid:27)" &%(cid:30) !+% !%(cid:30)(cid:9)" (cid:29)(cid:28) (cid:1)%,(cid:31)" (cid:20)(cid:27)"!(cid:30)$(cid:9)%(cid:27)!" "!(cid:31)(cid:27))(cid:31)(cid:30)) -(cid:31)(cid:30)(cid:30)(cid:31)(cid:27)!.* (cid:2)(cid:30)(cid:29))$#!(cid:26)(cid:29)(cid:27) &(cid:30)(cid:29)#%""(cid:26)(cid:27)/ )(cid:29)%" (cid:27)(cid:29)! (cid:27)%#%""(cid:31)(cid:30)(cid:26)(. (cid:26)(cid:27)#($)% !%"!(cid:26)(cid:27)/ (cid:29)(cid:28) (cid:31)(( &(cid:31)(cid:30)(cid:31)(cid:9)%!%(cid:30)"* POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 1

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6) (cid:4)(cid:7)(cid:7)(cid:8)(cid:9)(cid:10) (cid:11)(cid:12)(cid:13)(cid:12) (cid:14)(cid:12)(cid:10)(cid:8)(cid:15)(cid:12)(cid:14)(cid:1)(cid:3)(cid:16)(cid:17) (cid:3)(cid:18)(cid:19)(cid:20)(cid:12) (cid:2)(cid:12)(cid:10)(cid:17)(cid:21) (cid:3)(cid:11)(cid:2)(cid:14)(cid:20)(cid:22)(cid:20)(cid:17)(cid:21) (cid:10)(cid:20)(cid:1)(cid:23) (cid:19)(cid:20)(cid:22)(cid:22)(cid:17)(cid:21)(cid:17)(cid:13)(cid:1)(cid:20)(cid:3)(cid:14) (cid:20)(cid:13)(cid:2)(cid:18)(cid:1)(cid:24) SLOS336C − DECEMBER 2000 − REVISED OCTOBER 2002 AVAILABLE OPTIONS PACKAGED DEVICES MicroStar-Junior (BGA)‡ SMALL OUTLINE† MSOP‡ (GQS) (D) (DGN) Device TPA751GQS TPA751D TPA751DGN Package symbolization TPA751 TPA751 ATC †In the SOIC package, the maximum RMS output power is thermally limited to 350 mW; 700 mW peaks can be driven, as long as the RMS value is less than 350 mW. ‡The D, DGN, and GQS packages are available taped and reeled. To order a taped and reeled part, add the suffix R to the part number (e.g., TPA751DR). Terminal Functions TERMINAL NO. II//OO DDEESSCCRRIIPPTTIIOONN NNAAMMEE GQS D, DGN BYPASS is the tap to the voltage divider for internal mid-supply bias. This terminal should be BYPASS E3 2 I connected to a 0.1-µF to 2.2-µF capacitor when used as an audio amplifier. GND § 7 GND is the ground connection. IN− E5 4 I IN− is the inverting input. IN− is typically used as the audio input terminal. IN+ E4 3 I IN+ is the noninverting input. IN+ is typically tied to the BYPASS terminal for SE input. SHUTDOWN E2 1 I SHUTDOWN places the entire device in shutdown mode when held low (IDD = 1.5 nA). VDD A4 6 VDD is the supply voltage terminal. VO+ A5 5 O VO+ is the positive BTL output. VO− A2 8 O VO− is the negative BTL output. §A1, A3, A5, B1−B5, C1−C5, D1−D5 are electrical and thermal connections to the ground plane. absolute maximum ratings over operating free-air temperature range (unless otherwise noted)¶ Supply voltage, V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 V DD Input voltage, V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −0.3 V to V +0.3 V I DD Continuous total power dissipation . . . . . . . . . . . . . . . . . . . . . Internally limited (see Dissipation Rating Table) Operating free-air temperature range, T . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −40°C to 85°C A Operating junction temperature range, T . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −40°C to 150°C J Storage temperature range, T . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −65°C to 150°C stg Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260°C ¶Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. DISSIPATION RATING TABLE PACKAGE TA = 25°C DERATING FACTOR TA = 70°C TA = 85°C GQS|| 1.66 W|| 13.3 mW/°C 1.06 W 866 mW D 725 mW 5.8 mW/°C 464 mW 377 mW DGN 2.14 W# 17.1 mW/°C 1.37 W 1.11 W #See the Texas Instruments document, PowerPAD Thermally Enhanced Package Application Report (SLMA002), for more information on the PowerPAD package. The thermal data was measured on a PCB layout based on the information in the section entitled Texas Instruments Recommended Board for PowerPAD on page 33 of that document. ||See the Texas Instruments document, MicroStar Junior Made Easy Application Brief (SSYA009A) for board layout information on the MicroStar Junior package. 2 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6) (cid:4)(cid:7)(cid:7)(cid:8)(cid:9)(cid:10) (cid:11)(cid:12)(cid:13)(cid:12) (cid:14)(cid:12)(cid:10)(cid:8)(cid:15)(cid:12)(cid:14)(cid:1)(cid:3)(cid:16)(cid:17) (cid:3)(cid:18)(cid:19)(cid:20)(cid:12) (cid:2)(cid:12)(cid:10)(cid:17)(cid:21) (cid:3)(cid:11)(cid:2)(cid:14)(cid:20)(cid:22)(cid:20)(cid:17)(cid:21) (cid:10)(cid:20)(cid:1)(cid:23) (cid:19)(cid:20)(cid:22)(cid:22)(cid:17)(cid:21)(cid:17)(cid:13)(cid:1)(cid:20)(cid:3)(cid:14) (cid:20)(cid:13)(cid:2)(cid:18)(cid:1)(cid:24) SLOS336C − DECEMBER 2000 − REVISED OCTOBER 2002 recommended operating conditions ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ MIN MAX UNIT ÁÁSuÁÁpplyÁÁ voltÁÁage,ÁÁ VDDÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ2.ÁÁÁÁ5 ÁÁÁÁ5.ÁÁÁÁ5 ÁÁVÁÁ ÁÁHiÁÁgh-leÁÁvel iÁÁnputÁÁ voltÁÁage,ÁÁ VIHÁÁ, (SHÁÁUTDÁÁOWÁÁN) ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ0.ÁÁ9VDÁÁÁÁD ÁÁÁÁÁÁÁÁÁÁVÁÁ ÁÁLoÁÁw-leÁÁvel inÁÁput ÁÁvoltaÁÁge, ÁÁVIL,ÁÁ (SHÁÁUTDÁÁOWÁÁN) ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ0.1ÁÁVDDÁÁÁÁÁÁVÁÁ Operating free-air temperature, TA −40 85 °C ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ electrical characteristics at specified free-air temperature, V = 3.3 V, T = 25°C (unless otherwise DD A noted) ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ PARAMETER TEST CONDITIONS MIN TYP MAX UNIT ÁÁ|VÁÁOS|ÁÁÁÁÁÁOutÁÁput oÁÁffseÁÁt volÁÁtageÁÁ (meÁÁasurÁÁed dÁÁiffereÁÁntiaÁÁlly) ÁÁÁÁSÁÁHUTÁÁDOWÁÁN =ÁÁ VDÁÁD, RÁÁL = 8ÁÁ Ω, ÁÁRF =ÁÁ 10 ÁÁkΩ ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ2ÁÁÁÁ0 ÁÁmVÁÁ ÁÁPSÁÁRRÁÁÁÁÁÁPowÁÁer sÁÁupplÁÁy rejÁÁectioÁÁn raÁÁtio ÁÁÁÁÁÁÁÁÁÁÁÁVÁÁDD =ÁÁ 3.2ÁÁ V toÁÁ 3.4ÁÁ V ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ8ÁÁÁÁ5 ÁÁÁÁÁÁÁÁdBÁÁ ÁÁIDÁÁD ÁÁÁÁÁÁSupÁÁply cÁÁurreÁÁnt ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁSÁÁHUTÁÁDOWÁÁN =ÁÁ VDÁÁD, RÁÁF = ÁÁ10 kΩÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ1.2ÁÁÁÁ5 ÁÁ2.ÁÁÁÁ5 ÁÁmAÁÁ IDD(SD) Supply current, shutdown mode (see Figure 4) SHUTDOWN = 0 V, RF = 10 kΩ 1.5 1000 nA ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ |IIH| SHUTDOWN, VDD = 3.3 V, Vi = VDD 1 µA ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ |IIL| SHUTDOWN, VDD = 3.3 V, Vi = 0 V 1 µA ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ operating characteristics, VDD = 3.3 V, TA = 25°C, RL = 8 Ω ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ PARAMETER TEST CONDITIONS MIN TYP MAX UNIT ÁÁPOÁÁÁÁÁÁÁÁOutÁÁput pÁÁoweÁÁr, SeÁÁe NÁÁote 1ÁÁÁÁÁÁÁÁÁÁTHDÁÁ = 0ÁÁ.2%,ÁÁÁÁÁÁSee ÁÁFiguÁÁre 9ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ25ÁÁÁÁ0 ÁÁÁÁÁÁÁÁmWÁÁ ÁÁTHÁÁD +ÁÁ N ÁÁÁÁTotaÁÁl haÁÁrmonÁÁic dÁÁistorÁÁtion ÁÁplus ÁÁnoisÁÁÁÁe ÁÁPO =ÁÁ 250ÁÁ mWÁÁÁÁ, ÁÁf = 2ÁÁ00 HÁÁz toÁÁ 4 kHÁÁÁÁz, ÁÁSeeÁÁ FiguÁÁre 7ÁÁÁÁÁÁÁÁÁÁ0ÁÁ.55%ÁÁÁÁÁÁÁÁÁÁÁÁÁÁ ÁÁBOÁÁM ÁÁÁÁÁÁMaxÁÁimuÁÁm ouÁÁtputÁÁ powÁÁer bÁÁandwÁÁidthÁÁÁÁÁÁAV =ÁÁ −2 ÁÁV/V,ÁÁÁÁÁÁTHDÁÁ = 2%ÁÁ, ÁÁÁÁÁÁÁÁSeeÁÁ FiguÁÁre 7ÁÁÁÁÁÁÁÁÁÁÁÁ2ÁÁÁÁ0 ÁÁÁÁÁÁÁÁkHzÁÁ B1 Unity-gain bandwidth Open loop, See Figure 15 1.4 MHz ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ Supply ripple rejection ratio f = 1 kHz, CB = 1 µF, See Figure 2 79 dB ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ Vn Noise output voltage AV = −1V/V, CB = 0.1 µF, See Figure 19 17 µV(rms) ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ NOTE 1: Output power is measured at the output terminals of the device at f = 1 kHz. electrical characteristics at specified free-air temperature, V = 5 V, T = 25°C (unless otherwise DD A noted) PARAMETER TEST CONDITIONS MIN TYP MAX UNIT ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ |VOS| Output offset voltage (measured differentially) SHUTDOWN = VDD, RL = 8 Ω, RF = 10 kΩ 20 mV ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ PSRR Power supply rejection ratio VDD = 4.9 V to 5.1 V 78 dB ÁÁIDÁÁD ÁÁÁÁÁÁSupÁÁply cÁÁurreÁÁnt ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁSHÁÁUTDÁÁOWÁÁN =ÁÁ VDDÁÁ, RFÁÁ = 1ÁÁ0 kΩÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ1.4ÁÁÁÁ5 ÁÁ2.ÁÁÁÁ5 ÁÁmAÁÁ ÁÁIDÁÁD(SDÁÁ) ÁÁÁÁSupÁÁply cÁÁurreÁÁnt, sÁÁhutdÁÁownÁÁ modÁÁe (sÁÁee FÁÁigurÁÁe 4)ÁÁÁÁSHÁÁUTDÁÁOWÁÁN =ÁÁ 0 V,ÁÁ RF ÁÁ= 10ÁÁ kΩÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ5 ÁÁ150ÁÁÁÁ0 ÁÁnAÁÁ ÁÁ|IIHÁÁ| ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁSHÁÁUTDÁÁOWÁÁN, VÁÁDD ÁÁ= 5.5ÁÁ V, VÁÁi = ÁÁVDDÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ1 ÁÁµAÁÁ Á|IILÁ| ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁSHÁUTDÁOWÁN, VÁDD Á= 5.5Á V, VÁi = Á0 VÁÁÁÁÁÁÁÁÁÁÁÁ1 ÁµAÁ operating characteristics, VDD = 5 V, TA = 25°C, RL = 8 Ω PARAMETER TEST CONDITIONS MIN TYP MAX UNIT ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ PO Output power THD = 0.5%, See Figure 13 700† mW ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ THD + N Total harmonic distortion plus noise PO = 250 mW, f = 200 Hz to 4 kHz, See Figure 11 0.5% ÁÁBOÁÁM ÁÁÁÁÁÁMaxÁÁimuÁÁm ouÁÁtputÁÁ powÁÁer bÁÁandwÁÁidthÁÁÁÁÁÁAV ÁÁ= −2ÁÁ V/VÁÁÁÁ, ÁÁTHDÁÁ = 2ÁÁ%, ÁÁÁÁÁÁÁÁSeÁÁe FigÁÁure ÁÁÁÁ11 ÁÁÁÁÁÁÁÁ2ÁÁÁÁ0 ÁÁÁÁÁÁÁÁkHzÁÁ ÁÁB1ÁÁÁÁÁÁÁÁUniÁÁty-gaÁÁin bÁÁandwÁÁidthÁÁÁÁÁÁÁÁÁÁÁÁOpeÁÁn loÁÁop,ÁÁÁÁÁÁSeeÁÁ FigÁÁure 1ÁÁ6 ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ1ÁÁÁÁ.4 ÁÁÁÁÁÁÁÁMHzÁÁ ÁÁÁÁÁÁÁÁÁÁSupÁÁply rÁÁippleÁÁ rejeÁÁctioÁÁn ratÁÁio ÁÁÁÁÁÁÁÁf = ÁÁ1 kHÁÁz, ÁÁÁÁÁÁCB ÁÁ= 1 µÁÁF, ÁÁÁÁÁÁÁÁSeÁÁe FigÁÁure ÁÁÁÁ2 ÁÁÁÁÁÁÁÁ8ÁÁÁÁ0 ÁÁÁÁÁÁÁÁdBÁÁ ÁVnÁÁÁÁNoiÁse oÁutpuÁt voltÁageÁÁÁÁÁÁAV Á= −1Á V/VÁÁ, ÁCB Á= 0.1Á µF,ÁÁÁÁSeÁe FigÁure ÁÁ20 ÁÁÁÁ1ÁÁ7 ÁÁÁµÁV(rmÁs) †The GQS and DGN packages, properly mounted, can conduct 700 mW RMS power continuously. The D package, can only conduct 350 mW RMS power continuously, with peaks to 700 mW. POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 3

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6) (cid:4)(cid:7)(cid:7)(cid:8)(cid:9)(cid:10) (cid:11)(cid:12)(cid:13)(cid:12) (cid:14)(cid:12)(cid:10)(cid:8)(cid:15)(cid:12)(cid:14)(cid:1)(cid:3)(cid:16)(cid:17) (cid:3)(cid:18)(cid:19)(cid:20)(cid:12) (cid:2)(cid:12)(cid:10)(cid:17)(cid:21) (cid:3)(cid:11)(cid:2)(cid:14)(cid:20)(cid:22)(cid:20)(cid:17)(cid:21) (cid:10)(cid:20)(cid:1)(cid:23) (cid:19)(cid:20)(cid:22)(cid:22)(cid:17)(cid:21)(cid:17)(cid:13)(cid:1)(cid:20)(cid:3)(cid:14) (cid:20)(cid:13)(cid:2)(cid:18)(cid:1)(cid:24) SLOS336C − DECEMBER 2000 − REVISED OCTOBER 2002 PARAMETER MEASUREMENT INFORMATION VDD 6 VDD RF Audio VDD/2 CS Input RI 4 IN− − VO+ 5 CI 3 IN+ + 2 BYPASS RL = 8 Ω CB − VO− 8 + 7 GND 1 SHUTDOWN Bias VDD Control Figure 1. BTL Mode Test Circuit TYPICAL CHARACTERISTICS Table of Graphs FIGURE kSVR Supply ripple rejection ratio vs Frequency 2 IDD Supply current vs Supply voltage 3, 4 vs Supply voltage 5 PPOO OOuuttppuutt ppoowweerr vs Load resistance 6 vs Frequency 7, 8, 11, 12 TTHHDD++NN TToottaall hhaarrmmoonniicc ddiissttoorrttiioonn pplluuss nnooiissee vs Output power 9, 10, 13, 14 Open loop gain and phase vs Frequency 15, 16 Closed loop gain and phase vs Frequency 17, 18 Vn Output noise voltage vs Frequency 19, 20 PD Power dissipation vs Output power 21, 22 4 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6) (cid:4)(cid:7)(cid:7)(cid:8)(cid:9)(cid:10) (cid:11)(cid:12)(cid:13)(cid:12) (cid:14)(cid:12)(cid:10)(cid:8)(cid:15)(cid:12)(cid:14)(cid:1)(cid:3)(cid:16)(cid:17) (cid:3)(cid:18)(cid:19)(cid:20)(cid:12) (cid:2)(cid:12)(cid:10)(cid:17)(cid:21) (cid:3)(cid:11)(cid:2)(cid:14)(cid:20)(cid:22)(cid:20)(cid:17)(cid:21) (cid:10)(cid:20)(cid:1)(cid:23) (cid:19)(cid:20)(cid:22)(cid:22)(cid:17)(cid:21)(cid:17)(cid:13)(cid:1)(cid:20)(cid:3)(cid:14) (cid:20)(cid:13)(cid:2)(cid:18)(cid:1)(cid:24) SLOS336C − DECEMBER 2000 − REVISED OCTOBER 2002 TYPICAL CHARACTERISTICS SUPPLY RIPPLE REJECTION RATIO SUPPLY CURRENT vs vs FREQUENCY SUPPLY VOLTAGE 0 1.8 − dB −10 CRLB == 81 ΩµF SRHF U=T 1D0O kWΩN = VDD atio −20 Inputs Floating 1.6 R n −30 A o m cti − 1.4 eje −40 nt R e ple −50 Curr 1.2 Rip −60 ply y p uppl −70 − Su 1 − S −80 VDD = 3.3 V DD R I kSV −90 VDD = 5 V 0.8 −100 0.6 20 100 1k 10k 20k 2.5 3 3.5 4 4.5 5 5.5 f − Frequency − Hz VDD − Supply Voltage − V Figure 2 Figure 3 SUPPLY CURRENT vs SUPPLY VOLTAGE 10 SHUTDOWN = 0 V 9 RF = 10 kΩ 8 A − n 7 ent 6 r r u C 5 y pl p 4 u S − D 3 D I 2 1 0 2.5 3 3.5 4 4.5 5 5.5 VDD − Supply Voltage − V Figure 4 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 5

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6) (cid:4)(cid:7)(cid:7)(cid:8)(cid:9)(cid:10) (cid:11)(cid:12)(cid:13)(cid:12) (cid:14)(cid:12)(cid:10)(cid:8)(cid:15)(cid:12)(cid:14)(cid:1)(cid:3)(cid:16)(cid:17) (cid:3)(cid:18)(cid:19)(cid:20)(cid:12) (cid:2)(cid:12)(cid:10)(cid:17)(cid:21) (cid:3)(cid:11)(cid:2)(cid:14)(cid:20)(cid:22)(cid:20)(cid:17)(cid:21) (cid:10)(cid:20)(cid:1)(cid:23) (cid:19)(cid:20)(cid:22)(cid:22)(cid:17)(cid:21)(cid:17)(cid:13)(cid:1)(cid:20)(cid:3)(cid:14) (cid:20)(cid:13)(cid:2)(cid:18)(cid:1)(cid:24) SLOS336C − DECEMBER 2000 − REVISED OCTOBER 2002 TYPICAL CHARACTERISTICS OUTPUT POWER vs SUPPLY VOLTAGE 1000 THD+N 1% f = 1 kHz 800 W m − r e 600 w Po RL = 8 Ω ut p Out 400 RL = 32 Ω − O P 200 0 2.5 3 3.5 4 4.5 5 5.5 VDD − Supply Voltage − V Figure 5 OUTPUT POWER vs LOAD RESISTANCE 800 THD+N = 1% f = 1 kHz 700 W 600 − m VDD = 5 V er 500 w o P ut 400 p ut − O 300 VDD = 3.3 V O P 200 100 0 8 16 24 32 40 48 56 64 RL − Load Resistance − Ω Figure 6 6 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6) (cid:4)(cid:7)(cid:7)(cid:8)(cid:9)(cid:10) (cid:11)(cid:12)(cid:13)(cid:12) (cid:14)(cid:12)(cid:10)(cid:8)(cid:15)(cid:12)(cid:14)(cid:1)(cid:3)(cid:16)(cid:17) (cid:3)(cid:18)(cid:19)(cid:20)(cid:12) (cid:2)(cid:12)(cid:10)(cid:17)(cid:21) (cid:3)(cid:11)(cid:2)(cid:14)(cid:20)(cid:22)(cid:20)(cid:17)(cid:21) (cid:10)(cid:20)(cid:1)(cid:23) (cid:19)(cid:20)(cid:22)(cid:22)(cid:17)(cid:21)(cid:17)(cid:13)(cid:1)(cid:20)(cid:3)(cid:14) (cid:20)(cid:13)(cid:2)(cid:18)(cid:1)(cid:24) SLOS336C − DECEMBER 2000 − REVISED OCTOBER 2002 TYPICAL CHARACTERISTICS TOTAL HARMONIC DISTORTION PLUS NOISE TOTAL HARMONIC DISTORTION PLUS NOISE vs vs FREQUENCY FREQUENCY 10 10 Noise − % RVPDOL D == =82 53Ω0.3 m VW Noise − % VRAVDL D== =−8 23Ω .V3/ VV Distortion + 1 AV =− 1A0 VV /=V −20 V/V Distortion + 1 PO = 50 mW monic monic Har 0.1 AV = −2 V/V Har 0.1 N −Total N −Total PO = 125 mW D+ D+ TH TH PO = 250 mW 0.01 0.01 20 100 1k 10k 20k 20 100 1k 10k 20k f − Frequency − Hz f − Frequency − Hz Figure 7 Figure 8 TOTAL HARMONIC DISTORTION PLUS NOISE TOTAL HARMONIC DISTORTION PLUS NOISE vs vs OUTPUT POWER OUTPUT POWER 10 10 % VDD = 3.3 V % Noise − fA =V 1= k−H2 zV/V Noise − f = 20 kHz Distortion + 1 Distortion + 1 f = 10 kHz monic RL = 8 Ω monic f = 1 kHz Har 0.1 Har 0.1 N −Total N −Total f = 20 Hz VRCDBL D == =81 3Ωµ.F3 V D+ D+ AV = −2 V/V H H T T 0.01 0.01 0 0.05 0.1 0.15 0.2 0.25 0.3 0.35 0.4 0.01 0.1 1 PO − Output Power − W PO − Output Power − W Figure 9 Figure 10 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 7

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6) (cid:4)(cid:7)(cid:7)(cid:8)(cid:9)(cid:10) (cid:11)(cid:12)(cid:13)(cid:12) (cid:14)(cid:12)(cid:10)(cid:8)(cid:15)(cid:12)(cid:14)(cid:1)(cid:3)(cid:16)(cid:17) (cid:3)(cid:18)(cid:19)(cid:20)(cid:12) (cid:2)(cid:12)(cid:10)(cid:17)(cid:21) (cid:3)(cid:11)(cid:2)(cid:14)(cid:20)(cid:22)(cid:20)(cid:17)(cid:21) (cid:10)(cid:20)(cid:1)(cid:23) (cid:19)(cid:20)(cid:22)(cid:22)(cid:17)(cid:21)(cid:17)(cid:13)(cid:1)(cid:20)(cid:3)(cid:14) (cid:20)(cid:13)(cid:2)(cid:18)(cid:1)(cid:24) SLOS336C − DECEMBER 2000 − REVISED OCTOBER 2002 TYPICAL CHARACTERISTICS TOTAL HARMONIC DISTORTION PLUS NOISE TOTAL HARMONIC DISTORTION PLUS NOISE vs vs FREQUENCY FREQUENCY 10 10 Distortion + Noise − % 1 RVPDOL D == =87 05Ω0 V mW AV = −20 V/V Distortion + Noise − % 1 VRAVDL D== =−8 25Ω VV/V PO = 50 mW monic AV = −10 V/V monic Har 0.1 AV = −2 V/V Har 0.1 PO = 700 mW N −Total N −Total PO = 350 mW D+ D+ H H T T 0.01 0.01 20 100 1k 10k 20k 20 100 1k 10k 20k f − Frequency − Hz f − Frequency − Hz Figure 11 Figure 12 TOTAL HARMONIC DISTORTION PLUS NOISE TOTAL HARMONIC DISTORTION PLUS NOISE vs vs OUTPUT POWER OUTPUT POWER 10 10 Noise − % VfA =VD D1= k=−H 25 z VV/V Noise − % Distortion + 1 Distortion + 1 f = 10 kHzf = 20 kHz Harmonic 0.1 RL = 8 Ω Harmonic 0.1 f = 20 fH =z 1 kHz HD+N −Total HD+N −Total ACVRVDBL D === =−81 2 5Ωµ VFV/V T T 0.01 0.01 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1 0.01 0.1 1 PO − Output Power − W PO − Output Power − W Figure 13 Figure 14 8 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6) (cid:4)(cid:7)(cid:7)(cid:8)(cid:9)(cid:10) (cid:11)(cid:12)(cid:13)(cid:12) (cid:14)(cid:12)(cid:10)(cid:8)(cid:15)(cid:12)(cid:14)(cid:1)(cid:3)(cid:16)(cid:17) (cid:3)(cid:18)(cid:19)(cid:20)(cid:12) (cid:2)(cid:12)(cid:10)(cid:17)(cid:21) (cid:3)(cid:11)(cid:2)(cid:14)(cid:20)(cid:22)(cid:20)(cid:17)(cid:21) (cid:10)(cid:20)(cid:1)(cid:23) (cid:19)(cid:20)(cid:22)(cid:22)(cid:17)(cid:21)(cid:17)(cid:13)(cid:1)(cid:20)(cid:3)(cid:14) (cid:20)(cid:13)(cid:2)(cid:18)(cid:1)(cid:24) SLOS336C − DECEMBER 2000 − REVISED OCTOBER 2002 TYPICAL CHARACTERISTICS OPEN-LOOP GAIN AND PHASE vs FREQUENCY 80 180° VDD = 3.3 V 70 RL = Open 140° 60 Phase 100° B 50 − d 40 60° n Gai 30 20° e p Gain as o h o 20 −20°P L n- e 10 p −60° O 0 −100° −10 −140° −20 −30 −180° 1 101 102 103 104 f − Frequency − kHz Figure 15 OPEN-LOOP GAIN AND PHASE vs FREQUENCY 80 180° VDD = 5 V 70 RL = Open 140° 60 Phase 100° 50 B − d 40 60° n Gai 30 20° e p as oo 20 Gain −20°Ph L n- e 10 p −60° O 0 −100° −10 −140° −20 −30 −180° 1 101 102 103 104 f − Frequency − kHz Figure 16 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 9

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6) (cid:4)(cid:7)(cid:7)(cid:8)(cid:9)(cid:10) (cid:11)(cid:12)(cid:13)(cid:12) (cid:14)(cid:12)(cid:10)(cid:8)(cid:15)(cid:12)(cid:14)(cid:1)(cid:3)(cid:16)(cid:17) (cid:3)(cid:18)(cid:19)(cid:20)(cid:12) (cid:2)(cid:12)(cid:10)(cid:17)(cid:21) (cid:3)(cid:11)(cid:2)(cid:14)(cid:20)(cid:22)(cid:20)(cid:17)(cid:21) (cid:10)(cid:20)(cid:1)(cid:23) (cid:19)(cid:20)(cid:22)(cid:22)(cid:17)(cid:21)(cid:17)(cid:13)(cid:1)(cid:20)(cid:3)(cid:14) (cid:20)(cid:13)(cid:2)(cid:18)(cid:1)(cid:24) SLOS336C − DECEMBER 2000 − REVISED OCTOBER 2002 TYPICAL CHARACTERISTICS CLOSED-LOOP GAIN AND PHASE vs FREQUENCY 1 180° Phase 0.75 0.5 170° B 0.25 d − 0 160° n ai −0.25 Gain G oop −0.5 150° hase L P d- −0.75 e s o −1 140° Cl VDD = 3.3 V −1.25 RL = 8 Ω −1.5 PO = 250 mW 130° −1.75 −2 120° 101 102 103 104 105 106 f − Frequency − Hz Figure 17 CLOSED-LOOP GAIN AND PHASE vs FREQUENCY 1 180° Phase 0.75 0.5 170° B 0.25 d − 0 160° ain −0.25 Gain G oop −0.5 150° hase L P d- −0.75 e s o −1 140° Cl −1.25 VDD = 5 V RL = 8 Ω −1.5 PO = 700 m W 130° −1.75 −2 120° 101 102 103 104 105 106 f − Frequency − Hz Figure 18 10 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6) (cid:4)(cid:7)(cid:7)(cid:8)(cid:9)(cid:10) (cid:11)(cid:12)(cid:13)(cid:12) (cid:14)(cid:12)(cid:10)(cid:8)(cid:15)(cid:12)(cid:14)(cid:1)(cid:3)(cid:16)(cid:17) (cid:3)(cid:18)(cid:19)(cid:20)(cid:12) (cid:2)(cid:12)(cid:10)(cid:17)(cid:21) (cid:3)(cid:11)(cid:2)(cid:14)(cid:20)(cid:22)(cid:20)(cid:17)(cid:21) (cid:10)(cid:20)(cid:1)(cid:23) (cid:19)(cid:20)(cid:22)(cid:22)(cid:17)(cid:21)(cid:17)(cid:13)(cid:1)(cid:20)(cid:3)(cid:14) (cid:20)(cid:13)(cid:2)(cid:18)(cid:1)(cid:24) SLOS336C − DECEMBER 2000 − REVISED OCTOBER 2002 TYPICAL CHARACTERISTICS OUTPUT NOISE VOLTAGE OUTPUT NOISE VOLTAGE vs vs FREQUENCY FREQUENCY 100 VDD = 3.3 V 100 VDD = 5 V BW = 22 Hz to 22 kHz BW = 22 Hz to 22 kHz V(rms) RAVL == −8 1Ω V o/Vr 32 Ω ms) RAVL == −8 1Ω V o/Vr 32 Ω µ V(r age − VO BTL µe − VO BTL olt ag e V VO+ Volt VO+ ut Nois 10 Noise 10 utp put − O Out n − V n V 1 1 20 100 1k 10k 20k 20 100 1k 10k 20k f − Frequency − Hz f − Frequency − Hz Figure 19 Figure 20 POWER DISSIPATION POWER DISSIPATION vs vs OUTPUT POWER OUTPUT POWER 350 800 VDD = 3.3 V VDD = 5 V 300 RL = 8 Ω 700 RL = 8 Ω W W m 250 m 600 wer Dissipation − 125000 wer Dissipation − 435000000 Po Po P− D 100 RL = 32 Ω P− D 200 RL = 32 Ω 50 100 0 0 0 200 400 600 0 200 400 600 800 1000 PD − Output Power − mW PD − Output Power − mW Figure 21 Figure 22 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 11

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6) (cid:4)(cid:7)(cid:7)(cid:8)(cid:9)(cid:10) (cid:11)(cid:12)(cid:13)(cid:12) (cid:14)(cid:12)(cid:10)(cid:8)(cid:15)(cid:12)(cid:14)(cid:1)(cid:3)(cid:16)(cid:17) (cid:3)(cid:18)(cid:19)(cid:20)(cid:12) (cid:2)(cid:12)(cid:10)(cid:17)(cid:21) (cid:3)(cid:11)(cid:2)(cid:14)(cid:20)(cid:22)(cid:20)(cid:17)(cid:21) (cid:10)(cid:20)(cid:1)(cid:23) (cid:19)(cid:20)(cid:22)(cid:22)(cid:17)(cid:21)(cid:17)(cid:13)(cid:1)(cid:20)(cid:3)(cid:14) (cid:20)(cid:13)(cid:2)(cid:18)(cid:1)(cid:24) SLOS336C − DECEMBER 2000 − REVISED OCTOBER 2002 APPLICATION INFORMATION bridged-tied load Figure 23 shows a linear audio power amplifier (APA) in a BTL configuration. The TPA751 BTL amplifier consists of two linear amplifiers driving both ends of the load. There are several potential benefits to this differential drive configuration, but initially consider power to the load. The differential drive to the speaker means that as one side is slewing up, the other side is slewing down, and vice versa. This, in effect, doubles the voltage swing on the load as compared to a ground referenced load. Plugging 2 × V into the power equation, where voltage O(PP) is squared, yields 4× the output power from the same supply rail and load impedance (see equation 1). V O(PP) V (cid:1) (rms) (cid:2) 2 2 2 V (1) (rms) Power (cid:1) R L VDD VO(PP) RL 2x VO(PP) VDD −VO(PP) Figure 23. Bridge-Tied Load Configuration In a typical portable handheld equipment sound channel operating at 3.3 V, bridging raises the power into an 8-Ω speaker from a singled-ended (SE, ground reference) limit of 62.5 mW to 250 mW. In sound power that is a 6-dB improvement, which is loudness that can be heard. In addition to increased power, there are frequency response concerns. Consider the single-supply SE configuration shown in Figure 24. A coupling capacitor is required to block the dc offset voltage from reaching the load. These capacitors can be quite large (approximately 33 µF to 1000 µF), so they tend to be expensive, heavy, occupy valuable PCB area, and have the additional drawback of limiting low-frequency performance of the system. This frequency-limiting effect, due to the high pass filter network created with the speaker impedance and the coupling capacitance, is calculated with equation 2. f (cid:1) 1 (2) c 2(cid:1)R C L C 12 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6) (cid:4)(cid:7)(cid:7)(cid:8)(cid:9)(cid:10) (cid:11)(cid:12)(cid:13)(cid:12) (cid:14)(cid:12)(cid:10)(cid:8)(cid:15)(cid:12)(cid:14)(cid:1)(cid:3)(cid:16)(cid:17) (cid:3)(cid:18)(cid:19)(cid:20)(cid:12) (cid:2)(cid:12)(cid:10)(cid:17)(cid:21) (cid:3)(cid:11)(cid:2)(cid:14)(cid:20)(cid:22)(cid:20)(cid:17)(cid:21) (cid:10)(cid:20)(cid:1)(cid:23) (cid:19)(cid:20)(cid:22)(cid:22)(cid:17)(cid:21)(cid:17)(cid:13)(cid:1)(cid:20)(cid:3)(cid:14) (cid:20)(cid:13)(cid:2)(cid:18)(cid:1)(cid:24) SLOS336C − DECEMBER 2000 − REVISED OCTOBER 2002 APPLICATION INFORMATION bridged-tied load (continued) For example, a 68-µF capacitor with an 8-Ω speaker would attenuate low frequencies below 293 Hz. The BTL configuration cancels the dc offsets, which eliminates the need for the blocking capacitors. Low-frequency performance is then limited only by the input network and speaker response. Cost and PCB space are also minimized by eliminating the bulky coupling capacitor. VDD −3 dB VO(PP) CC VO(PP) RL fc Figure 24. Single-Ended Configuration and Frequency Response Increasing power to the load does carry a penalty of increased internal power dissipation. The increased dissipation is understandable considering that the BTL configuration produces 4× the output power of a SE configuration. Internal dissipation versus output power is discussed further in the thermal considerations section. BTL amplifier efficiency The primary cause of linear amplifier inefficiencies is voltage drop across the output stage transistors. There are two components of the internal voltage drop. One is the headroom or dc voltage drop that varies inversely to output power. The second component is due to the sinewave nature of the output. The total voltage drop, can be calculated by subtracting the RMS value of the output voltage from V . The internal voltage drop multiplied DD by the RMS value of the supply current, I rms, determines the internal power dissipation of the amplifier. DD An easy-to-use equation to calculate efficiency starts out being equal to the ratio of power from the power supply to the power delivered to the load. To accurately calculate the RMS values of power in the load and in the amplifier, the current and voltage waveform shapes must first be understood (see Figure 25). VO IDD V(LRMS) IDD(RMS) Figure 25. Voltage and Current Waveforms for BTL Amplifiers POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 13

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6) (cid:4)(cid:7)(cid:7)(cid:8)(cid:9)(cid:10) (cid:11)(cid:12)(cid:13)(cid:12) (cid:14)(cid:12)(cid:10)(cid:8)(cid:15)(cid:12)(cid:14)(cid:1)(cid:3)(cid:16)(cid:17) (cid:3)(cid:18)(cid:19)(cid:20)(cid:12) (cid:2)(cid:12)(cid:10)(cid:17)(cid:21) (cid:3)(cid:11)(cid:2)(cid:14)(cid:20)(cid:22)(cid:20)(cid:17)(cid:21) (cid:10)(cid:20)(cid:1)(cid:23) (cid:19)(cid:20)(cid:22)(cid:22)(cid:17)(cid:21)(cid:17)(cid:13)(cid:1)(cid:20)(cid:3)(cid:14) (cid:20)(cid:13)(cid:2)(cid:18)(cid:1)(cid:24) SLOS336C − DECEMBER 2000 − REVISED OCTOBER 2002 APPLICATION INFORMATION BTL amplifier efficiency (continued) Although the voltages and currents for SE and BTL are sinusoidal in the load, currents from the supply are very different between SE and BTL configurations. In an SE application, the current waveform is a half-wave rectified shape, whereas in BTL it is a full-wave rectified waveform. This means RMS conversion factors are different. Keep in mind that for most of the waveform both the push and pull transistors are not on at the same time, which supports the fact that each amplifier in the BTL device only draws current from the supply for half the waveform. The following equations are the basis for calculating amplifier efficiency. P EfficiencyofaBTLamplifier(cid:1) L P (3) SUP where 2 V rms2 V V P (cid:1) L , andV (cid:1) P, therefore, P (cid:1) P L RL LRMS (cid:2)2 L 2RL (cid:3)(cid:1) V V (cid:1) 2V and PSUP (cid:1) VDDIDDavg and IDDavg (cid:1) 1(cid:1) RP sin(t)dt (cid:1) 1(cid:1) (cid:4) RP [cos(t)] 0 (cid:1) (cid:1)RP 0 L L L therefore, 2V V P (cid:1) DD P SUP (cid:1)R L substituting P and P into equation 7, P = Power delivered to load L SUP L V 2 PSUP = Power drawn from power supply P VLRMS = RMS voltage on BTL load EfficiencyofaBTLamplifier (cid:1) 2RL (cid:1) (cid:1)VP RVL == LPoeaadk rveosltisatgaen coen BTL load P 2VDDVP 4VDD IDDavg = Average current drawn from the (cid:1)R power supply where L V = Power supply voltage DD (cid:2) ηBTL = Efficiency of a BTL amplifier V (cid:1) 2P R P L L therefore, (cid:2) (cid:1) 2P R L L (cid:2) (cid:1) BTL 4V (4) DD 14 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6) (cid:4)(cid:7)(cid:7)(cid:8)(cid:9)(cid:10) (cid:11)(cid:12)(cid:13)(cid:12) (cid:14)(cid:12)(cid:10)(cid:8)(cid:15)(cid:12)(cid:14)(cid:1)(cid:3)(cid:16)(cid:17) (cid:3)(cid:18)(cid:19)(cid:20)(cid:12) (cid:2)(cid:12)(cid:10)(cid:17)(cid:21) (cid:3)(cid:11)(cid:2)(cid:14)(cid:20)(cid:22)(cid:20)(cid:17)(cid:21) (cid:10)(cid:20)(cid:1)(cid:23) (cid:19)(cid:20)(cid:22)(cid:22)(cid:17)(cid:21)(cid:17)(cid:13)(cid:1)(cid:20)(cid:3)(cid:14) (cid:20)(cid:13)(cid:2)(cid:18)(cid:1)(cid:24) SLOS336C − DECEMBER 2000 − REVISED OCTOBER 2002 APPLICATION INFORMATION application schematics Figure 26 is a schematic diagram of a typical handheld audio application circuit, configured for a gain of −10 V/V. VDD 6 50R kFΩ VDD Audio VDD/2 CS Input RI 1 µF 10 kΩ 4 IN− − VO+ 5 CI 3 IN+ + 2 BYPASS CB 2.2 µF − VO− 8 700 mW + 7 GND 1 SHUTDOWN Bias From System Control Control Figure 26. TPA751 Application Circuit Figure 27 is a schematic diagram of a typical handheld audio application circuit, configured for a gain of −10 V/V with a differential input. VDD 6 50R kFΩ VDD Audio VDD/2 CS Input− RI 1 µF 10 kΩ 4 IN− − VO+ 5 CI 3 IN+ + RI RF Audio 10 kΩ 50 kΩ Input+ 2 BYPASS CB CI 2.2 µF − VO− 8 700 mW + 7 GND 1 SHUTDOWN Bias From System Control Control Figure 27. TPA751 Application Circuit With Differential Input POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 15

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6) (cid:4)(cid:7)(cid:7)(cid:8)(cid:9)(cid:10) (cid:11)(cid:12)(cid:13)(cid:12) (cid:14)(cid:12)(cid:10)(cid:8)(cid:15)(cid:12)(cid:14)(cid:1)(cid:3)(cid:16)(cid:17) (cid:3)(cid:18)(cid:19)(cid:20)(cid:12) (cid:2)(cid:12)(cid:10)(cid:17)(cid:21) (cid:3)(cid:11)(cid:2)(cid:14)(cid:20)(cid:22)(cid:20)(cid:17)(cid:21) (cid:10)(cid:20)(cid:1)(cid:23) (cid:19)(cid:20)(cid:22)(cid:22)(cid:17)(cid:21)(cid:17)(cid:13)(cid:1)(cid:20)(cid:3)(cid:14) (cid:20)(cid:13)(cid:2)(cid:18)(cid:1)(cid:24) SLOS336C − DECEMBER 2000 − REVISED OCTOBER 2002 APPLICATION INFORMATION application schematics (continued) It is important to note that using the additional R resistor connected between IN+ and BYPASS causes V /2 F DD to shift slightly, which could influence the THD+N performance of the amplifier. Although an additional external operational amplifier could be used to buffer BYPASS from R , tests in the lab have shown that the THD+N F performance is only minimally affected by operating in the fully differential mode as shown in Figure 27. The following sections discuss the selection of the components used in Figures 26 and 27. component selection gain setting resistors, R and R F I The gain for each audio input of the TPA751 is set by resistors R and R according to equation 5 for BTL mode. F I (cid:6) (cid:7) R BTLgain (cid:1) (cid:5)2 F (5) R I BTL mode operation brings about the factor 2 in the gain equation due to the inverting amplifier mirroring the voltage swing across the load. Given that the TPA751 is a MOS amplifier, the input impedance is very high; consequently input leakage currents are not generally a concern, although noise in the circuit increases as the value of R increases. In addition, a certain range of R values is required for proper start-up operation of the F F amplifier. Taken together it is recommended that the effective impedance seen by the inverting node of the amplifier be set between 5 kΩ and 20 kΩ. The effective impedance is calculated in equation 6. R R Effectiveimpedance (cid:1) F I (6) R (cid:8)R F I As an example, consider an input resistance of 10 kΩ and a feedback resistor of 50 kΩ. The BTL gain of the amplifier would be −10 V/V and the effective impedance at the inverting terminal would be 8.3 kΩ, which is well within the recommended range. For high performance applications, metal film resistors are recommended because they tend to have lower noise levels than carbon resistors. For values of R above 50 kΩ, the amplifier tends to become unstable due F to a pole formed from R and the inherent input capacitance of the MOS input structure. For this reason, a small F compensation capacitor of approximately 5 pF should be placed in parallel with R when R is greater than F F 50 kΩ. This, in effect, creates a low-pass filter network with the cutoff frequency defined in equation 7. −3 dB f (cid:1) 1 (7) c 2(cid:1)R C F F fc For example, if R is 100 kΩ and C is 5 pF, then f is 318 kHz, which is well outside of the audio range. F F c 16 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6) (cid:4)(cid:7)(cid:7)(cid:8)(cid:9)(cid:10) (cid:11)(cid:12)(cid:13)(cid:12) (cid:14)(cid:12)(cid:10)(cid:8)(cid:15)(cid:12)(cid:14)(cid:1)(cid:3)(cid:16)(cid:17) (cid:3)(cid:18)(cid:19)(cid:20)(cid:12) (cid:2)(cid:12)(cid:10)(cid:17)(cid:21) (cid:3)(cid:11)(cid:2)(cid:14)(cid:20)(cid:22)(cid:20)(cid:17)(cid:21) (cid:10)(cid:20)(cid:1)(cid:23) (cid:19)(cid:20)(cid:22)(cid:22)(cid:17)(cid:21)(cid:17)(cid:13)(cid:1)(cid:20)(cid:3)(cid:14) (cid:20)(cid:13)(cid:2)(cid:18)(cid:1)(cid:24) SLOS336C − DECEMBER 2000 − REVISED OCTOBER 2002 APPLICATION INFORMATION input capacitor, C I In the typical application an input capacitor, C, is required to allow the amplifier to bias the input signal to the I proper dc level for optimum operation. In this case, C and R form a high-pass filter with the corner frequency I I determined in equation 8. −3 dB fc (cid:1) 2(cid:1)R1 C (8) I I fc The value of C is important to consider, as it directly affects the bass (low frequency) performance of the circuit. I Consider the example where R is 10 kΩ and the specification calls for a flat bass response down to 40 Hz. I Equation 8 is reconfigured as equation 9. C (cid:1) 1 I 2(cid:1)R f (9) I c In this example, C is 0.40 µF, so one would likely choose a value in the range of 0.47 µF to 1 µF. A further I consideration for this capacitor is the leakage path from the input source through the input network (R, C) and I I the feedback resistor (R ) to the load. This leakage current creates a dc offset voltage at the input to the amplifier F that reduces useful headroom, especially in high gain applications. For this reason a low-leakage tantalum or ceramic capacitor is the best choice. When polarized capacitors are used, the positive side of the capacitor should face the amplifier input in most applications, as the dc level there is held at V /2, which is likely higher DD than the source dc level. It is important to confirm the capacitor polarity in the application. power supply decoupling, C S The TPA751 is a high-performance CMOS audio amplifier that requires adequate power supply decoupling to ensure the output total harmonic distortion (THD) is as low as possible. Power supply decoupling also prevents oscillations for long lead lengths between the amplifier and the speaker. The optimum decoupling is achieved by using two capacitors of different types that target different types of noise on the power supply leads. For higher frequency transients, spikes, or digital hash on the line, a good low equivalent-series-resistance (ESR) ceramic capacitor, typically 0.1 µF, placed as close as possible to the device V lead, works best. For filtering DD lower-frequency noise signals, a larger aluminum electrolytic capacitor of 10 µF or greater placed near the audio power amplifier is recommended. POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 17

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6) (cid:4)(cid:7)(cid:7)(cid:8)(cid:9)(cid:10) (cid:11)(cid:12)(cid:13)(cid:12) (cid:14)(cid:12)(cid:10)(cid:8)(cid:15)(cid:12)(cid:14)(cid:1)(cid:3)(cid:16)(cid:17) (cid:3)(cid:18)(cid:19)(cid:20)(cid:12) (cid:2)(cid:12)(cid:10)(cid:17)(cid:21) (cid:3)(cid:11)(cid:2)(cid:14)(cid:20)(cid:22)(cid:20)(cid:17)(cid:21) (cid:10)(cid:20)(cid:1)(cid:23) (cid:19)(cid:20)(cid:22)(cid:22)(cid:17)(cid:21)(cid:17)(cid:13)(cid:1)(cid:20)(cid:3)(cid:14) (cid:20)(cid:13)(cid:2)(cid:18)(cid:1)(cid:24) SLOS336C − DECEMBER 2000 − REVISED OCTOBER 2002 APPLICATION INFORMATION midrail bypass capacitor, C B The midrail bypass capacitor, C , is the most critical capacitor and serves several important functions. During B start-up or recovery from shutdown mode, C determines the rate at which the amplifier starts up. The second B function is to reduce noise produced by the power supply caused by coupling into the output drive signal. This noise is from the midrail generation circuit internal to the amplifier, which appears as degraded PSRR and THD + N. The capacitor is fed from a 250-kΩ source inside the amplifier. To keep the start-up pop as low as possible, the relationship shown in equation 10 should be maintained. This insures the input capacitor is fully charged before the bypass capacitor is fully charged and the amplifier starts up. 10 (cid:9) 1 (cid:6) (cid:7) (cid:6) (cid:7) (10) C (cid:4)250kΩ R (cid:8)R C B F I I As an example, consider a circuit where C is 2.2 µF, C is 0.47 µF, R is 50 kΩ, and R is 10 kΩ. Inserting these B I F I values into the equation 10 we get: 18.2(cid:9)35.5 which satisfies the rule. Bypass capacitor, C , values of 0.1 µF to 2.2 µF ceramic or tantalum low-ESR capacitors B are recommended for the best THD and noise performance. using low-ESR capacitors Low-ESR capacitors are recommended throughout this applications section. A real (as opposed to ideal) capacitor can be modeled simply as a resistor in series with an ideal capacitor. The voltage drop across this resistor minimizes the beneficial effects of the capacitor in the circuit. The lower the equivalent value of this resistance, the more the real capacitor behaves like an ideal capacitor. 5-V versus 3.3-V operation The TPA751 operates over a supply range of 2.5 V to 5.5 V. This data sheet provides full specifications for 5-V and 3.3-V operation, as these are considered to be the two most common standard voltages. There are no special considerations for 3.3-V versus 5-V operation with respect to supply bypassing, gain setting, or stability. The most important consideration is that of output power. Each amplifier in TPA751 can produce a maximum voltage swing of V − 1 V. This means, for 3.3-V operation, clipping starts to occur when V = 2.3 V as DD O(PP) opposed to V = 4 V at 5 V. The reduced voltage swing subsequently reduces maximum output power into O(PP) an 8-Ω load before distortion becomes significant. Operation from 3.3-V supplies, as can be shown from the efficiency formula in equation 4, consumes approximately two-thirds the supply power of operation from 5-V supplies for a given output-power level. 18 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6) (cid:4)(cid:7)(cid:7)(cid:8)(cid:9)(cid:10) (cid:11)(cid:12)(cid:13)(cid:12) (cid:14)(cid:12)(cid:10)(cid:8)(cid:15)(cid:12)(cid:14)(cid:1)(cid:3)(cid:16)(cid:17) (cid:3)(cid:18)(cid:19)(cid:20)(cid:12) (cid:2)(cid:12)(cid:10)(cid:17)(cid:21) (cid:3)(cid:11)(cid:2)(cid:14)(cid:20)(cid:22)(cid:20)(cid:17)(cid:21) (cid:10)(cid:20)(cid:1)(cid:23) (cid:19)(cid:20)(cid:22)(cid:22)(cid:17)(cid:21)(cid:17)(cid:13)(cid:1)(cid:20)(cid:3)(cid:14) (cid:20)(cid:13)(cid:2)(cid:18)(cid:1)(cid:24) SLOS336C − DECEMBER 2000 − REVISED OCTOBER 2002 APPLICATION INFORMATION headroom and thermal considerations Linear power amplifiers dissipate a significant amount of heat in the package under normal operating conditions. A typical music CD requires 12 dB to 15 dB of dynamic headroom to pass the loudest portions without distortion as compared with the average power output. From the TPA751 data sheet, one can see that when the TPA751 is operating from a 5-V supply into an 8-Ω speaker that 700 mW peaks are available. Converting watts to dB: P P (cid:1) 10Log W (cid:1)10Log 700mW(cid:1)–1.5dB dB P 1W ref Subtracting the headroom restriction to obtain the average listening level without distortion yields: −1.5 dB − 15 dB = −16.5 (15 dB headroom) −1.5 dB − 12 dB = −13.5 (12 dB headroom) −1.5 dB − 9 dB = −10.5 (9 dB headroom) −1.5 dB − 6 dB = −7.5 (6 dB headroom) −1.5 dB − 3 dB = −4.5 (3 dB headroom) Converting dB back into watts: P (cid:1) 10PdB(cid:10)10 xP W ref = 22 mW (15 dB headroom) = 44 mW (12 dB headroom) = 88 mW (9 dB headroom) = 175 mW (6 dB headroom) = 350 mW (3 dB headroom) This is valuable information to consider when attempting to estimate the heat dissipation requirements for the amplifier system. Comparing the absolute worst case, which is 700 mW of continuous power output with 0 dB of headroom, against 12 dB and 15 dB applications drastically affects maximum ambient temperature ratings for the system. Using the power dissipation curves for a 5-V, 8-Ω system, the internal dissipation in the TPA751 and maximum ambient temperatures is shown in Table 1. Table 1. TPA751 Power Rating, 5-V, 8-Ω, BTL D PACKAGE DGN PACKAGE GQS PACKAGE PEAK OUTPUT POWER (SOIC) (MSOP) (MicroStar Junior) AAVVEERRAAGGEE PPOOWWEERR DDIISSSSIIPPAATTIIOONN OUTPUT POWER MAXIMUM AMBIENT MAXIMUM AMBIENT MAXIMUM AMBIENT (mW) (mW) TEMPERATURE TEMPERATURE TEMPERATURE 700 700 mW 675 34°C 110°C 99°C 700 350 mW (3 dB) 595 47°C 115°C 105°C 700 176 mW (6 dB) 475 68°C 122°C 114°C 700 88 mW (9 dB) 350 89°C 125°C 123°C 700 44 mW (12 dB) 225 111°C 125°C 125°C Table 1 shows that the TPA751 can be used to its full 700-mW rating without any heat sinking in still air up to 110°C, 34°C, and 99°C for the DGN package (MSOP), D package (SOIC), and GQS (MicroStar Junior) package, respectively. POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 19

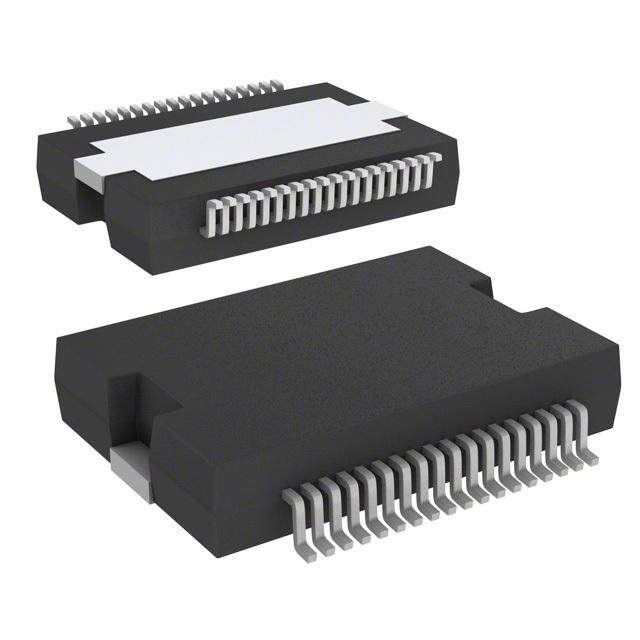

PACKAGE OPTION ADDENDUM www.ti.com 6-Feb-2020 PACKAGING INFORMATION Orderable Device Status Package Type Package Pins Package Eco Plan Lead/Ball Finish MSL Peak Temp Op Temp (°C) Device Marking Samples (1) Drawing Qty (2) (6) (3) (4/5) TPA751D ACTIVE SOIC D 8 75 Green (RoHS NIPDAU Level-1-260C-UNLIM -40 to 85 TPA751 & no Sb/Br) TPA751DGN ACTIVE HVSSOP DGN 8 80 Green (RoHS NIPDAU Level-1-260C-UNLIM -40 to 85 ATC & no Sb/Br) TPA751DGNR ACTIVE HVSSOP DGN 8 2500 Green (RoHS NIPDAU Level-1-260C-UNLIM -40 to 85 ATC & no Sb/Br) TPA751DR ACTIVE SOIC D 8 2500 Green (RoHS NIPDAU Level-1-260C-UNLIM -40 to 85 TPA751 & no Sb/Br) (1) The marketing status values are defined as follows: ACTIVE: Product device recommended for new designs. LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect. NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design. PREVIEW: Device has been announced but is not in production. Samples may or may not be available. OBSOLETE: TI has discontinued the production of the device. (2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free". RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption. Green: TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement. (3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature. (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device. (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device. (6) Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width. Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and Addendum-Page 1

PACKAGE OPTION ADDENDUM www.ti.com 6-Feb-2020 continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release. In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis. Addendum-Page 2

PACKAGE MATERIALS INFORMATION www.ti.com 6-Sep-2019 TAPE AND REEL INFORMATION *Alldimensionsarenominal Device Package Package Pins SPQ Reel Reel A0 B0 K0 P1 W Pin1 Type Drawing Diameter Width (mm) (mm) (mm) (mm) (mm) Quadrant (mm) W1(mm) TPA751DGNR HVSSOP DGN 8 2500 330.0 12.4 5.3 3.4 1.4 8.0 12.0 Q1 TPA751DR SOIC D 8 2500 330.0 12.4 6.4 5.2 2.1 8.0 12.0 Q1 PackMaterials-Page1

PACKAGE MATERIALS INFORMATION www.ti.com 6-Sep-2019 *Alldimensionsarenominal Device PackageType PackageDrawing Pins SPQ Length(mm) Width(mm) Height(mm) TPA751DGNR HVSSOP DGN 8 2500 358.0 335.0 35.0 TPA751DR SOIC D 8 2500 340.5 338.1 20.6 PackMaterials-Page2

PACKAGE OUTLINE D0008A SOIC - 1.75 mm max height SCALE 2.800 SMALL OUTLINE INTEGRATED CIRCUIT C SEATING PLANE .228-.244 TYP [5.80-6.19] .004 [0.1] C A PIN 1 ID AREA 6X .050 [1.27] 8 1 2X .189-.197 [4.81-5.00] .150 NOTE 3 [3.81] 4X (0 -15 ) 4 5 8X .012-.020 B .150-.157 [0.31-0.51] .069 MAX [3.81-3.98] .010 [0.25] C A B [1.75] NOTE 4 .005-.010 TYP [0.13-0.25] 4X (0 -15 ) SEE DETAIL A .010 [0.25] .004-.010 0 - 8 [0.11-0.25] .016-.050 [0.41-1.27] DETAIL A (.041) TYPICAL [1.04] 4214825/C 02/2019 NOTES: 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side. 4. This dimension does not include interlead flash. 5. Reference JEDEC registration MS-012, variation AA. www.ti.com

EXAMPLE BOARD LAYOUT D0008A SOIC - 1.75 mm max height SMALL OUTLINE INTEGRATED CIRCUIT 8X (.061 ) [1.55] SYMM SEE DETAILS 1 8 8X (.024) [0.6] SYMM (R.002 ) TYP [0.05] 5 4 6X (.050 ) [1.27] (.213) [5.4] LAND PATTERN EXAMPLE EXPOSED METAL SHOWN SCALE:8X SOLDER MASK SOLDER MASK METAL OPENING OPENING METAL UNDER SOLDER MASK EXPOSED METAL EXPOSED METAL .0028 MAX .0028 MIN [0.07] [0.07] ALL AROUND ALL AROUND NON SOLDER MASK SOLDER MASK DEFINED DEFINED SOLDER MASK DETAILS 4214825/C 02/2019 NOTES: (continued) 6. Publication IPC-7351 may have alternate designs. 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site. www.ti.com

EXAMPLE STENCIL DESIGN D0008A SOIC - 1.75 mm max height SMALL OUTLINE INTEGRATED CIRCUIT 8X (.061 ) [1.55] SYMM 1 8 8X (.024) [0.6] SYMM (R.002 ) TYP [0.05] 5 4 6X (.050 ) [1.27] (.213) [5.4] SOLDER PASTE EXAMPLE BASED ON .005 INCH [0.125 MM] THICK STENCIL SCALE:8X 4214825/C 02/2019 NOTES: (continued) 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations. 9. Board assembly site may have different recommendations for stencil design. www.ti.com

None

PACKAGE OUTLINE DGN0008D PowerPAD TM VSSOP - 1.1 mm max height SCALE 4.000 SMALL OUTLINE PACKAGE C 5.05 A 4.75 TYP 0.1 C PIN 1 INDEX AREA SEATING PLANE 6X 0.65 8 1 2X 3.1 1.95 2.9 NOTE 3 4 5 0.38 8X 0.25 B 3.1 0.13 C A B 2.9 NOTE 4 0.23 0.13 SEE DETAIL A EXPOSED THERMAL PAD 4 5 0.25 GAGE PLANE 1.89 1.63 9 1.1 MAX 8 1 0.7 0.15 0 -8 0.05 0.4 DETA 20AIL A 1.57 TYPICAL 1.28 4225481/A 11/2019 PowerPAD is a trademark of Texas Instruments. NOTES: 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side. 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side. 5. Reference JEDEC registration MO-187. www.ti.com

EXAMPLE BOARD LAYOUT DGN0008D PowerPAD TM VSSOP - 1.1 mm max height SMALL OUTLINE PACKAGE (2) NOTE 9 METAL COVERED BY SOLDER MASK (1.57) SYMM SOLDER MASK DEFINED PAD 8X (1.4) (R0.05) TYP 8 8X (0.45) 1 (3) 9 SYMM NOTE 9 (1.89) 6X (0.65) (1.22) 5 4 ( 0.2) TYP VIA (0.55) SEE DETAILS (4.4) LAND PATTERN EXAMPLE EXPOSED METAL SHOWN SCALE: 15X SOLDER MASK METAL METAL UNDER SOLDER MASK OPENING SOLDER MASK OPENING EXPOSED METAL EXPOSED METAL 0.05 MAX 0.05 MIN ALL AROUND ALL AROUND NON-SOLDER MASK SOLDER MASK DEFINED DEFINED (PREFERRED) SOLDE15.000R MASK DETAILS 4225481/A 11/2019 NOTES: (continued) 6. Publication IPC-7351 may have alternate designs. 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site. 8. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented. 9. Size of metal pad may vary due to creepage requirement. www.ti.com

EXAMPLE STENCIL DESIGN DGN0008D PowerPAD TM VSSOP - 1.1 mm max height SMALL OUTLINE PACKAGE (1.57) BASED ON 0.125 THICK STENCIL SYMM 8X (1.4) (R0.05) TYP 8 8X (0.45) 1 (1.89) SYMM BASED ON 0.125 THICK STENCIL 6X (0.65) 4 5 METAL COVERED SEE TABLE FOR BY SOLDER MASK DIFFERENT OPENINGS (4.4) FOR OTHER STENCIL THICKNESSES SOLDER PASTE EXAMPLE EXPOSED PAD 9: 100% PRINTED SOLDER COVERAGE BY AREA SCALE: 15X STENCIL SOLDER STENCIL THICKNESS OPENING 0.1 1.76 X 2.11 0.125 1.57 X 1.89 (SHOWN) 0.15 1.43 X 1.73 0.175 1.33 X 1.60 4225481/A 11/2019 NOTES: (continued) 10. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations. 11. Board assembly site may have different recommendations for stencil design. www.ti.com

IMPORTANTNOTICEANDDISCLAIMER TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS. These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources. TI’s products are provided subject to TI’s Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI’s provision of these resources does not expand or otherwise alter TI’s applicable warranties or warranty disclaimers for TI products. Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated

Datasheet下载

Datasheet下载