ICGOO在线商城 > TMS320DM647ZUT7

- 型号: TMS320DM647ZUT7

- 制造商: Texas Instruments

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

TMS320DM647ZUT7产品简介:

ICGOO电子元器件商城为您提供TMS320DM647ZUT7由Texas Instruments设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 提供TMS320DM647ZUT7价格参考¥251.07-¥385.93以及Texas InstrumentsTMS320DM647ZUT7封装/规格参数等产品信息。 你可以下载TMS320DM647ZUT7参考资料、Datasheet数据手册功能说明书, 资料中有TMS320DM647ZUT7详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC)半导体 |

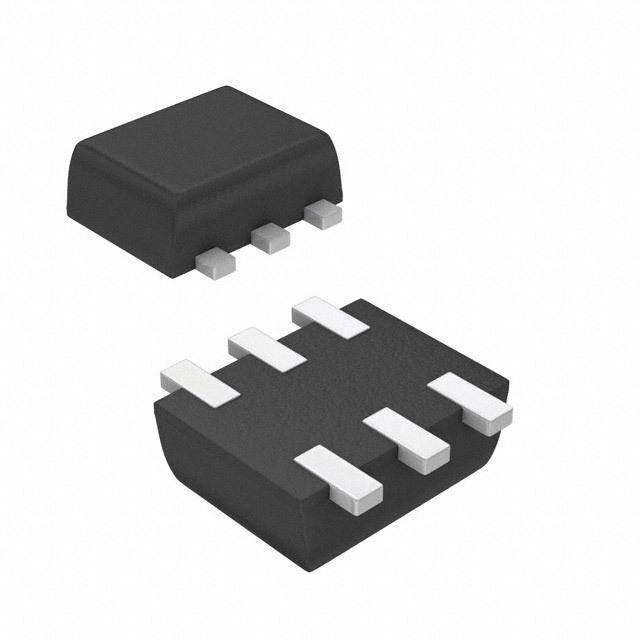

| 描述 | IC DGTL MEDIA PROC 529-FCBGA数字信号处理器和控制器 - DSP, DSC Dig Media Proc |

| 产品分类 | |

| 品牌 | Texas Instruments |

| MIPS | 5760 MIPs |

| 产品手册 | http://www.ti.com/lit/gpn/tms320dm647 |

| 产品图片 |

|

| rohs | RoHS 合规性豁免含铅 / 不符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 嵌入式处理器和控制器,数字信号处理器和控制器 - DSP, DSC,Texas Instruments TMS320DM647ZUT7TMS320DM64x, DaVinci™ |

| 数据手册 | |

| 产品型号 | TMS320DM647ZUT7 |

| 产品 | DSPs |

| 产品种类 | 数字信号处理器和控制器 - DSP, DSC |

| 供应商器件封装 | 529-FCBGA(19x19) |

| 其它名称 | 296-34539-5 |

| 包装 | 托盘 |

| 单位重量 | 2.220 g |

| 商标 | Texas Instruments |

| 处理器系列 | DaVinci DM6x |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装/外壳 | 529-BFBGA,FCBGA |

| 封装/箱体 | FCBGA-529 |

| 工作温度 | 0°C ~ 90°C |

| 工作电源电压 | 1.2 V, 1.8 V, 3.3 V |

| 工厂包装数量 | 84 |

| 接口 | 主机接口,I²C,McASP,PCI,SPI,UART |

| 数据总线宽度 | 32 bit |

| 时钟速率 | 720MHz |

| 最大工作温度 | + 90 C |

| 最大时钟频率 | 720 MHz |

| 最小工作温度 | 0 C |

| 标准包装 | 84 |

| 核心 | TMS320 |

| 片载RAM | 320kB |

| 电压-I/O | 1.8V,3.3V |

| 电压-内核 | 1.20V |

| 类型 | 定点 |

| 系列 | TMS320DM647 |

| 说明书类型 | Fixed Point |

| 非易失性存储器 | ROM(64 kB) |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

TMS320DM647 TMS320DM648 www.ti.com SPRS372H–MAY2007–REVISEDAPRIL2012 TMS320DM647/TMS320DM648 Digital Media Processor CheckforSamples:TMS320DM647,TMS320DM648 1 Features 1 • High-PerformanceDigitalMediaProcessor • C64x+L1/L2MemoryArchitecture – 720-MHz,800-MHz,900-MHz,1.1-GHz – 256K-bit(32K-byte)L1PProgramRAM/Cache C64x+™ClockRates [DirectMapped] – 1.39ns(-720),1.25ns(-800),1.11ns(-900), – 256K-bit(32K-byte)L1DDataRAM/Cache 0.91ns(-1100)InstructionCycleTime [2-WaySet-Associative] – 5760,6400,7200,8800MIPS – 2M-bit/256K-byte(DM647)or4M-Bit/512K- – Eight32-BitC64x+Instructions/Cycle byte)(DM648)L2UnifiedMapped RAM/Cache[FlexibleAllocation] – FullySoftware-CompatibleWithC64x/Debug – CommercialTemperatureRanges(-720,-900, • SupportsLittleEndianModeOnly and-1100only) • FiveConfigurableVideoPorts – ExtendedTemperatureRanges(-800only) – ProvidingaGluelessI/FtoCommonVideo – IndustrialTemperatureRanges(-720,-900, DecoderandEncoderDevices and-1100only) – SupportsMultipleResolutions/Video • VelociTI.2™ExtensionstoVelociTI™ Standards AdvancedVery-Long-Instruction-Word(VLIW) • VCXOInterpolatedControlPort(VIC) TMS320C64x+™DSPCore – SupportsAudio/VideoSynchronization – EightHighlyIndependentFunctionalUnits • ExternalMemoryInterfaces(EMIFs) WithVelociTI.2Extensions: – 32-BitDDR2SDRAMMemoryControllerWith • SixALUs(32-/40-Bit),EachSupports 512M-ByteAddressSpace(1.8-VI/O) Single32-bit,Dual16-bit,orQuad8-bit – Asynchronous16-BitWideEMIF(EMIFA) ArithmeticperClockCycle • Upto128M-ByteTotalAddressReach • TwoMultipliersSupportFour16x16-bit Multiplies(32-bitResults)perClockCycle • 64M-ByteAddressReachperCESpace orEight8x8-bitMultiplies(16-Bit – GluelessInterfacetoAsynchronous Results)perClockCycle Memories(SRAM,Flash,andEEPROM) – Load-StoreArchitectureWithNon-Aligned – SynchronousMemories(SBSRAMandZBT Support SRAM) – 6432-bitGeneral-PurposeRegisters – SupportsInterfacetoStandardSyncDevices – InstructionPackingReducesCodeSize andCustomLogic(FPGA,CPLD,ASICs, etc.) – AllInstructionsConditional • EnhancedDirect-Memory-Access(EDMA) – AdditionalC64x+™Enhancements Controller(64IndependentChannels) • ProtectedModeOperation • 3-PortGigabitEthernetSwitchSubsystem • ExceptionsSupportforErrorDetection • Four64-BitGeneral-PurposeTimers(Each andProgramRedirection ConfigurableasTwo32-BitTimers) • HardwareSupportforModuloLoopAuto- • OneUART(WithRTSandCTSFlowControl) FocusModuleOperation • One4-wireSerialPortInterface(SPI)WithTwo • C64x+InstructionSetFeatures Chip-Selects – Byte-Addressable(8-/16-/32-/64-bitData) • Master/SlaveInter-IntegratedCircuit(I2C – 8-bitOverflowProtection Bus™) – Bit-FieldExtract,Set,Clear • MultichannelAudioSerialPort(McASP) – Normalization,Saturation,Bit-Counting – TenSerializersandSPDIF(DIT)Mode – VelociTI.2IncreasedOrthogonality • 16/32-BitHost-PortInterface(HPI) – C64x+Extensions • AdvancedEventTriggering(AET)Compatible • Compact16-bitInstructions • 32-Bit33-/66-MHz,3.3-VPeripheralComponent • AdditionalInstructionstoSupport Interconnect(PCI)Master/SlaveInterface ComplexMultiplies ConformstoPCISpecification2.3 1 Pleasebeawarethatanimportantnoticeconcerningavailability,standardwarranty,anduseincriticalapplicationsof TexasInstrumentssemiconductorproductsanddisclaimerstheretoappearsattheendofthisdatasheet. PRODUCTIONDATAinformationiscurrentasofpublicationdate.Productsconformto Copyright©2007–2012,TexasInstrumentsIncorporated specifications per the terms of the Texas Instruments standard warranty. Production processingdoesnotnecessarilyincludetestingofallparameters.

TMS320DM647 TMS320DM648 SPRS372H–MAY2007–REVISEDAPRIL2012 www.ti.com • VLYNQ™Interface(FPGAInterface) (MultiplexedWithOtherDeviceFunctions) • On-ChipROMBootloader • Package: • IndividualPower-SavingModes – 529-pinnFBGA(ZUTsuffix) • FlexiblePLLClockGenerators – 19x19mm0.8mmpitchBGA • IEEE-1149.1(JTAG™)Boundary-Scan- – 0.09-μm/6-LevelCuMetalProcess(CMOS) Compatible • 3.3-Vand1.8-VI/O,1.2-VInternal(-720,-800,- • 32General-PurposeI/O(GPIO)Pins 900,-1100) 1.1 Applications • DigitalVideoRecording 1.2 Trademarks TMS320C64x+, C64x, C64x+, VelociTI, VelociTI.2, VLYNQ, TMS320C6000, C6000, TI, and TMS320 are trademarksofTexasInstruments. I2CBusisaregisteredtrademarkofKoninklijkePhilipsElectronicsN.V. WindowsisaregisteredtrademarkofMicrosoftCorporationintheUnitedStatesand/orothercountries. Alltrademarksarethepropertyoftheirrespectiveowners. 1.3 Description The TMS320C64x+™ DSPs (including the TMS320DM647/TMS320DM648 devices) are the highest- performance fixed-point DSP generation in the TMS320C6000™ DSP platform. The DM647, DM648 devices are based on the third-generation high-performance, advanced VelociTI™ very-long-instruction- word (VLIW) architecture developed by Texas Instruments (TI), making these DSPs an excellent choice for digital media applications. The C64x+™ devices are upward code-compatible from previous devices that are part of the C6000™ DSP platform. The C64x™ DSPs support added functionality and have an expandedinstructionsetfrompreviousdevices. AnyreferencetotheC64xDSPorC64xCPUalsoapplies,unlessotherwisenoted,totheC64x+DSPand C64x+CPU,respectively. With performance of up to 8800 million instructions per second (MIPS) at a clock rate of 1.1 GHz, the C64x+ core offers solutions to high-performance DSP programming challenges. The DSP core possesses the operational flexibility of high-speed controllers and the numerical capability of array processors. The C64x+ DSP core processor has 64 general-purpose registers of 32-bit word length and eight highly independent functional units—two multipliers for a 32-bit result and six arithmetic logic units (ALUs). The eight functional units include instructions to accelerate the performance in video and imaging applications. TheDSPcorecanproducefour16-bitmultiply-accumulates(MACs)percycleforupto4400millionMACs per second (MMACS), or eight 8-bit MACs per cycle for up tp 8800 MMACS. For more details on the C64x+ DSP, see the TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide (literature numberSPRU732). The devices also have application-specific hardware logic, on-chip memory, and additional on-chip peripherals similar to the other C6000 DSP platform devices. The core uses a two-level cache-based architecture. The Level 1 program cache (L1P) is a 256K-bit direct mapped cache and the Level 1 data cache (L1D) is a 256K-bit 2-way set-associative cache. The Level 2 memory/cache (L2) consists of a 4M- bit (DM648) or 2M-bit (DM647) memory space that is shared between program and data space. L2 memorycanbeconfiguredasmappedmemory,cache,orcombinationsofthetwo. The peripheral set includes five configurable 16-bit video port peripherals (VP0, VP1, VP2, VP3, and VP4). These video port peripherals provide a glueless interface to common video decoder and encoder devices. The video port peripherals support multiple resolutions and video standards (e.g., CCIR601, ITU- BT.656,BT.1120,SMPTE125M,260M,274M,and296M),aVCXOinterpolatedcontrolport(VIC);a1000 Mbps Ethernet Switch Subsystem with a management data input/output (MDIO) module and two SGMII 2 Features Copyright©2007–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 www.ti.com SPRS372H–MAY2007–REVISEDAPRIL2012 ports (DM648) or one SGMII port (only DM647); a 4-bit transmit, 4-bit receive VLYNQ interface; an inter- integratedcircuit(I2C)businterface;amultichannelaudioserialport(McASP)withtenserializers;four64- bit general-purpose timers each configurable as two independent 32-bit timers; a user-configurable 16-bit or 32-bit host-port interface (HPI); 32 pins for general-purpose input/output (GPIO) with programmable interrupt/event generation modes, multiplexed with other peripherals; one UART; and two glueless external memory interfaces: a synchronous and asynchronous external memory interface (EMIFA) for slowermemories/peripherals,andahigherDDR2SDRAMinterface. The video port peripherals provide a glueless interface to common video decoder and encoder devices. The video port peripherals support multiple resolutions and video standards (e.g., CCIR601, ITU-BT.656, BT.1120,SMPTE125M,260M,274M,and296M). The video port peripherals are configurable and can support either video capture and/or video display modes. Each video port consists of two channels (A and B) with a 5120-byte capture/display buffer that is splittablebetweenthetwochannels. For more details on the video port peripherals, see the TMS320DM647/DM648 Video Port User's Guide (literaturenumberSPRUEM1). The management data input/output (MDIO) module continuously polls all 32 MDIO addresses to enumerateallPHYdevicesinthesystem. The I2C and VLYNQ ports allow the device to easily control peripheral modules and/or communicate with hostprocessors. The rich peripheral set provides the ability to control external peripheral devices and communicate with external processors. For details on each of the peripherals, see the related sections later in this document andtheassociatedperipheralreferenceguides. The devices have a complete set of development tools. These include C compilers, a DSP assembly optimizer to simplify programming and scheduling, and a Windows™ debugger interface for visibility into sourcecodeexecution. Copyright©2007–2012,TexasInstrumentsIncorporated Features 3 SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 SPRS372H–MAY2007–REVISEDAPRIL2012 www.ti.com 1.4 Functional Block Diagram Figure1-1showsthefunctionalblockdiagramofthedevice. Timers (4 64-bit or 8 32-bit) PCI66 PLL or EDMA3.0 UHPI CC JTAG 3-port Ethernet Switch Subsystem TC TC TC TC GPIO x32 SGMII (x2, DM648) VIC (x1, DM647) VLYNQ Switched Central Resource DDR2 EMIFA16-bit Video Ports (5) L2 RAM L1D32KB 256KB McASP (DM647) C64x+ 512KB UART Mega (DM648) SPI L1P32KB L2 ROM I2C 64KB Imaging Coprocessor Figure1-1.FunctionalBlockDiagram 4 Features Copyright©2007–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 www.ti.com SPRS372H–MAY2007–REVISEDAPRIL2012 1 Features ................................................... 1 6.2 RecommendedClockandControlSignalTransition ............................................ .......................................... Behavior 59 1.1 Applications 2 ..................................... .......................................... 6.3 PowerSupplies 59 1.2 Trademarks 2 ..................................... ........................................... 6.4 PLL1Controller 65 1.3 Description 2 ..................................... ........................... 6.5 PLL2Controller 69 1.4 FunctionalBlockDiagram 4 RevisionHistory .............................................. 6 6.6 EnhancedDirectMemoryAccess(EDMA3) ........................................... Controller 71 2 DeviceOverview ........................................ 7 .................................... 6.7 ResetController 84 ............................... 2.1 DeviceCharacteristics 7 ........................................... 6.8 Interrupts 96 ........................ 2.2 CPU(DSPCore)Description 8 ......................... 6.9 DDR2MemoryController 100 ......................................... 2.3 C64x+CPU 11 ............ 6.10 ExternalMemoryInterfaceA(EMIFA) 111 ............................ 2.4 MemoryMapSummary 12 ......................................... 6.11 VideoPort 118 .................................... 2.5 PinAssignments 16 ................. 6.12 VCXOInterpolatedControl(VIC) 126 ................................. 2.6 TerminalFunctions 20 6.13 UniversalAsynchronousReceiver/Transmitter 2.7 DeviceSupport ..................................... 34 (UART) ............................................ 128 3 DeviceConfiguration ................................. 38 6.14 SerialPeripheralInterfacePort(SPI) ............. 130 3.1 SystemModuleRegisters .......................... 38 6.15 Inter-IntegratedCircuit(I2C) ...................... 134 3.2 BootmodeRegisters ................................ 39 6.16 Host-PortInterface(HPI)Peripheral .............. 138 3.3 Pullup/PulldownResistors .......................... 49 6.17 PeripheralComponentInterconnect(PCI) ........ 149 4 SystemInterconnect .................................. 50 6.18 MultichannelAudioSerialPort(McASP).......... 154 4.1 InternalBuses,Bridges,andSwitchFabrics ....... 50 6.19 3-PortEthernetSwitchSubsystem(3PSW)....... 162 4.2 DataSwitchFabricConnections ................... 50 6.20 ManagementDataInput/Output(MDIO) .......... 172 4.3 ConfigurationSwitchFabric ........................ 52 6.21 Timers ............................................. 173 5 DeviceOperatingConditions ....................... 54 6.22 VLYNQPeripheral................................. 175 5.1 AbsoluteMaximumRatings ........................ 54 6.23 General-PurposeInput/Output(GPIO) ............ 178 5.2 RecommendedOperatingConditions .............. 55 6.24 EmulationFeaturesandCapability ............... 180 5.3 ElectricalCharacteristics ........................... 56 6.25 IEEE1149.1JTAG ................................ 181 6 PeripheralInformationandElectrical 7 MechanicalData ...................................... 183 Specifications .......................................... 57 ............................. 7.1 ThermalDataforZUT 183 .............................. 6.1 ParameterInformation 57 ............................ 7.2 PackagingInformation 184 Copyright©2007–2012,TexasInstrumentsIncorporated Contents 5 SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 SPRS372H–MAY2007–REVISEDAPRIL2012 www.ti.com Revision History NOTE:Pagenumbersforpreviousrevisionsmaydifferfrompagenumbersinthecurrentversion. This data manual revision history highlights the technical changes made to the SPRS372G device-specific data manual to make it an SPRS372H revision. Applicable updates to the TMS320DM64x Digital Media Processors device family , specifically relating to the TMS320DM647, TMS320DM648 devices which are nowintheproductiondata(PD)stageofdevelopment,havebeenincorporated. DM647/DM648RevisionHistory SEE ADDITIONS,DELETIONS,MODIFICATIONS ExternalMemoryInterfaces(EMIFs): Section1 • Deletedthefootnotereference(1)from"512M-ByteAddressSpace(1.8-VI/O)"subbullet • Deletedassociatedfootnote[devicesarePD;SR1.0wasTMX] Section1.1 AddedseparateApplicationssection(newformatstructure) TerminalFunctions,PowerPins: Table2-4 • Added"orleftunconnected"totheV (L19)pinDESCRIPTIONcolumn[FortheAdvisory,seethe CCMON Device-SpecificSiliconErrata.] Figure6-5 CorrectedCLKDIRtoVLYNQtoshow0isVLYNQ,external PLL1ControllerDevice-SpecificInformation • Added"[WhenSYSCLK4isusedastheEMIFinputclocksource,theactualclockgoesthrougha Section6.4.1 dividerandthefrequencywouldbeSYSCLK4divide-by-2(seeFigure6-5,PLLInputClock).]"tothe SYSCLK4isusedastheEMIFAAECLKOUTbullet[ClearedDocFeedback] TimingRequirementsforAsynchronousMemoryCyclesforEMIFAModule: Table6-44 • Changed3nsto0nsfort (AOEH-EDV) h Figure6-21 Updatedtoshowtimes3and4arereferredtorisingedgeAAOE/ASOE. Table6-49 Changed5.4nsto4.2nsfort andt . w(VKIH) w(VKIL) Section7.2 DeletedduplicatedOrderableAddendumtable 6 Contents Copyright©2007–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 www.ti.com SPRS372H–MAY2007–REVISEDAPRIL2012 2 Device Overview 2.1 Device Characteristics Table 2-1, provides an overview of the DSP. The tables show significant features of the devices, including thecapacityofon-chipRAM,theperipherals,theCPUfrequency,andthepackagetypewithpincount. Table2-1.CharacteristicsoftheProcessor HARDWAREFEATURES DM647 DM648 DDR2memorycontroller(32-bit 1 1 buswidth)[1.8VI/O] 16-bitbuswidth synchronous/asynchronous 1 1 EMIF[EMIFA] EDMA3(64independent 1 1 channels,8QDMAchannels) 464-bitGeneralPurpose 464-bitGeneralPurpose Timers (eachconfigurableas164-bitor232- (eachconfigurableas164-bitor232-bit) bit) UART (withRTSandCTSflowcontrol) (withRTSandCTSflowcontrol) I2C 1(Master/Slave) 1(Master/Slave) Peripherals Notallperipheral SPI 1(4-wire,2chipselect) 1(4-wire,2chipselect) pinsareavailable McASP 1(10serializers) 1(10serializers) atthesametime (Formoredetail, 3-portEthernetSwitch seeSection3.) Subsystemsupporting 10/100/1000Base-T 1SGMIIportavailable 2SGMIIportsavailable Managementdatainput/output (MDIO) VLYNQ 1 1 General-purposeinput/output Upto32pins Upto32pins port(GPIO) HPI(16/32-bit) 1 1 PCI(32bit)(33MHzor66 1(PCI33orPCI66) 1(PCI33orPCI66) MHz) VIC 1 1 Configurablevideoports 5 5 Size(bytes) 320KBRAM,64KBROM 576KBRAM,64KBROM 32KBL1program(L1P)/cache(upto 32KB) 32KBL1program(L1P)/cache(upto32KB) On-ChipMemory 32KBL1data(L1D)/cache(upto 32KBL1data(L1D)/cache(upto32KB) Organization 32KB) 512KBunifiedmappedRAM/Cache(L2) 256KBunifiedmappedRAM/Cache 64KBBootROM (L2) 64KBBootROM RevisionIDRegister MegaModule (MM_REVID[15:0]) 0x0003 0x0003 RevID (addresslocation0x01812000) CPUID+CPU ControlStatusRegister 0x1000 0x1000 RevID (CSR.[31:16]) JTAGIDregister JTAGBSDL_ID 0x1B77A02F 0x1B77A02F (addresslocation:0x02049018) CPUFrequency MHz 720,900,1100 720,800,900,1100 1.39ns(-720) 1.39ns(-720) 1.25ns(-800) CycleTime ns 1.11ns(-900) 1.11ns(-900) 0.91ns(-1100) 0.91ns(-1100) Core(V) 1.2V(-720,-900,-1100) 1.2V(-720,-800,-900,-1100) Voltage I/O(V) 1.8V,3.3V 1.8V,3.3V Copyright©2007–2012,TexasInstrumentsIncorporated DeviceOverview 7 SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 SPRS372H–MAY2007–REVISEDAPRIL2012 www.ti.com Table2-1.CharacteristicsoftheProcessor(continued) HARDWAREFEATURES DM647 DM648 x1(Bypass), x1(Bypass), PLLOptions CLKIN1frequencymultiplier PLLM=15,16,…,31 PLLM=15,16,…,31 (x16,x17,…,x32)(1) (x16,x17,…,x32)(1) BGAPackage 529-PinFlipChipPlasticBGA(ZUT) 529-PinFlipChipPlasticBGA(ZUT) Process 0.09-μm/6-LevelCuMetal 0.09μm 0.09μm Technology Process(CMOS) ProductStatus(2) ProductionData(PD) PD PD (1) ThemaximumCPUfrequencymustnotbeviolated. (2) SeeSection2.7foradescriptionofeachstageofdevelopment. 2.2 CPU (DSP Core) Description The C64x+ central processing unit (CPU) consists of eight functional units, two register files, and two data paths as shown in Figure 2-1. The two general-purpose register files (A and B) each contain 32 32-bit registers for a total of 64 registers. The general-purpose registers can be used for data or can be data address pointers. The data types supported include packed 8-bit data, packed 16-bit data, 32-bit data, 40- bit data, and 64-bit data. Values larger than 32 bits, such as 40-bit-long or 64-bit-long values are stored in register pairs, with the 32 LSBs of data placed in an even register and the remaining 8 or 32 MSBs in the nextupperregister(whichisalwaysanodd-numberedregister). The eight functional units (.M1, .L1, .D1, .S1, .M2, .L2, .D2, and .S2) are each capable of executing one instruction every clock cycle. The .M functional units perform all multiply operations. The .S and .L units perform a general set of arithmetic, logical, and branch functions. The .D units primarily load data from memorytotheregisterfileandstoreresultsfromtheregisterfileintomemory. TheC64x+CPUextendstheperformanceoftheC64xcorethroughenhancementsandnewfeatures. Each C64x+ .M unit can perform one of the following each clock cycle: one 32 x 32 bit multiply, one 16 x 32 bit multiply, two 16 x 16 bit multiplies, two 16 x 32 bit multiplies, two 16 x 16 bit multiplies with add/subtract capabilities, four 8 x 8 bit multiplies, four 8 x 8 bit multiplies with add operations, and four 16 x 16 multiplies with add/subtract capabilities (including a complex multiply). There is also support for Galois field multiplication for 8-bit and 32-bit data. Many communications algorithms such as FFTs and modems require complex multiplication. The complex multiply (CMPY) instruction takes for 16-bit inputs and produces a 32-bit real and a 32-bit imaginary output. There are also complex multiplies with rounding capability that produces one 32-bit packed output that contain 16-bit real and 16-bit imaginary values. The 32 x 32 bit multiply instructions provide the extended precision necessary for audio and other high- precisionalgorithmsonavarietyofsignedandunsigned32-bitdatatypes. The .L or (Arithmetic Logic Unit) now incorporates the ability to do parallel add/subtract operations on a pair of common inputs. Versions of this instruction exist to work on 32-bit data or on pairs of 16-bit data performingdual16-bitaddandsubtractsinparallel.Therearealsosaturatedformsoftheseinstructions. The C64x+ core enhances the .S unit in several ways. In the C64x core, dual 16-bit MIN2 and MAX2 comparisons were available only on the .L units. On the C64x+ core they are also available on the .S unit, which increases the performance of algorithms that do searching and sorting. Finally, to increase data packing and unpacking throughput, the .S unit allows sustained high performance for the quad 8-bit/16-bit and dual 16-bit instructions. Unpack instructions prepare 8-bit data for parallel 16-bit operations. Pack instructionsreturnparallelresultstooutputprecisionincludingsaturationsupport. Othernewfeaturesinclude: • SPLOOP-AsmallinstructionbufferintheCPUthataidsincreationofsoftwarepipeliningloopswhere multiple iterations of a loop are executed in parallel. The SPLOOP buffer reduces the code size associatedwithsoftwarepipelining.Furthermore,loopsintheSPLOOPbufferarefullyinterruptible. 8 DeviceOverview Copyright©2007–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 www.ti.com SPRS372H–MAY2007–REVISEDAPRIL2012 • Compact Instructions - The native instruction size for the C6000 devices is 32 bits. Many common instructions such as MPY, AND, OR, ADD, and SUB can be expressed as 16 bits if the C64x+ compiler can restrict the code to use certain registers in the register file. This compression is performedbythecodegenerationtools. • Instruction Set Enhancement - As noted above, there are new instructions such as 32-bit multiplications, complex multiplications, packing, sorting, bit manipulation, and 32-bit Galois field multiplication. • Exceptions Handling - Intended to aid the programmer in isolating bugs. The C64x+ CPU is able to detectandrespondtoexceptions,bothfrominternallydetectedsources(suchasillegalopcodes). • Privilege - Defines user and supervisor modes of operation, allowing the operating system to give a basic level of protection to sensitive resources. Local memory is divided into multiple pages, each with read,write,andexecutepermissions. • Time-Stamp Counter - Primarily targeted for real-time operating system (RTOS) robustness, a free- runningtime-stampcounterthatisnotsensitivetosystemstallsisimplementedintheCPU. For more details on the C64x+ CPU and its enhancements over the C64x architecture, see the following documents: • TMS320C64x/C64x+DSPCPUandInstructionSetReferenceGuide(literaturenumberSPRU732) • TMS320C64x+DSPMegamoduleReferenceGuide(literaturenumberSPRU871) • TMS320C64xtoTMS320C64x+CPUMigrationGuideApplicationReport(literaturenumberSPRAA84) • TMS320C64x+DSPCacheUser'sGuide(literaturenumberSPRU862) Copyright©2007–2012,TexasInstrumentsIncorporated DeviceOverview 9 SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 SPRS372H–MAY2007–REVISEDAPRIL2012 www.ti.com Even src1 Odd register register fileA fileA (A0,A2, .L1 src2 (A1,A3, A4...A30) A5...A31) odd dst (D) even dst long src 8 ST1b 32 MSB 32 LSB ST1a 8 long src even dst DatapathA odd dst (D) .S1 src1 src2 32 dst2 (A) dst1 32 (B) .M1 src1 src2 (C) 32 MSB LD1b 32 LSB LD1a dst .D1 src1 DA1 src2 2x 1x Even Odd register DA2 src2 register file B .D2 src1 file B (B0, B2, dst (B1, B3, B4...B30) LD2a 32 LSB B5...B31) LD2b 32 MSB src2 (C) .M2 src1 dst2 32 (B) dst1 32 (A) src2 src1 .S2 odd dst Datapath B (D) even dst 8 long src 32 MSB ST2a 32 LSB ST2b 8 long src even dst (D) odd dst .L2 src2 src1 ControlRegister A. On.M unit,dst2is 32 MSB. B. On .M unit,dst1is 32 LSB. C. On C64x CPU .M unit,src2is 32 bits; on C64x+ CPU .M unit,src2is 64 bits. D. On .Land .S units,odd dstconnects to odd register files andeven dstconnects to even register files. Figure2-1.TMS320C64x+™CPU(DSPCore)DataPaths 10 DeviceOverview Copyright©2007–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 www.ti.com SPRS372H–MAY2007–REVISEDAPRIL2012 2.3 C64x+ CPU The C64x+ core uses a two-level cache-based architecture. The Level 1 program memory/cache (L1P) consists of 32KB memory space that can be configured as mapped memory or direct mapped cache. The Level 1 data memory/cache (L1D) consists of 32KB that can be configured as mapped memory or 2-way associated cache. The Level 2 memory/cache (L2) consists of a 256KB (DM647)/512 KB (DM648) memoryspacethatissharedbetweenprogramanddataspace.L2memorycanbeconfiguredasmapped memory,cache,oracombinationofboth. Table2-2showsamemorymapoftheC64x+CPUcacheregistersforthedevice. Table2-2.C64x+CacheRegisters HEXADDRESSRANGE REGISTERACRONYM DESCRIPTION 0x01840000 L2CFG L2cacheconfigurationregister 0x01840020 L1PCFG L1Psizecacheconfigurationregister 0x01840024 L1PCC L1Pfreezemodecacheconfigurationregister 0x01840040 L1DCFG L1Dsizecacheconfigurationregister 0x01840044 L1DCC L1Dfreezemodecacheconfigurationregister 0x01840048-0x01840FFC - Reserved 0x01841000 - Reserved 0x01841004-0x01841FFC - Reserved 0x01842000 L2ALLOC0 L2allocationregister0 0x01842004 L2ALLOC1 L2allocationregister1 0x01842008 L2ALLOC2 L2allocationregister2 0x0184200C L2ALLOC3 L2allocationregister3 0x01842010-0x01843FFF - Reserved 0x01844000 L2WBAR L2writebackbaseaddressregister 0x01844004 L2WWC L2writebackwordcountregister 0x01844010 L2WIBAR L2writebackinvalidatebaseaddressregister 0x01844014 L2WIWC L2writebackinvalidatewordcountregister 0x01844018 L2IBAR L2invalidatebaseaddressregister 0x0184401C L2IWC L2invalidatewordcountregister 0x01844020 L1PIBAR L1Pinvalidatebaseaddressregister 0x01844024 L1PIWC L1Pinvalidatewordcountregister 0x01844030 L1DWIBAR L1Dwritebackinvalidatebaseaddressregister 0x01844034 L1DWIWC L1Dwritebackinvalidatewordcountregister 0x01844038 - Reserved 0x01844040 L1DWBAR L1Dblockwriteback 0x01844044 L1DWWC L1Dblockwriteback 0x01844048 L1DIBAR L1Dinvalidatebaseaddressregister 0x0184404C L1DIWC L1Dinvalidatewordcountregister 0x01844050-0x01844FFF - Reserved 0x01845000 L2WB L2writebackallregister 0x01845004 L2WBINV L2writebackinvalidateallregister 0x01845008 L2INV L2globalinvalidatewithoutwriteback 0x0184500C-0x01845027 - Reserved 0x01845028 L1PINV L1Pglobalinvalidate 0x0184502C-0x01845039 - Reserved 0x01845040 L1DWB L1Dglobalwriteback 0x01845044 L1DWBINV L1Dglobalwritebackwithinvalidate 0x01845048 L1DINV L1Dglobalinvalidatewithoutwriteback Copyright©2007–2012,TexasInstrumentsIncorporated DeviceOverview 11 SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 SPRS372H–MAY2007–REVISEDAPRIL2012 www.ti.com Table2-2.C64x+CacheRegisters(continued) HEXADDRESSRANGE REGISTERACRONYM DESCRIPTION 0x01848000-0x018480FC MAR0-MAR63 Reserved0x00000000-0x3FFFFFFF 0x018480C0-0x018480FC MAR48-MAR63 Reserved0x30000000-0x3FFFFFFF 0x01848100-0x0184813C MAR64-MAR79 MemoryattributeregistersforPCIData0x40000000-0x4FFFFFFF 0x01848140-0x0184827C MAR80-MAR159 Reserved0x50000000-0x9FFFFFFF 0x01848280-0x018482BC MAR160-MAR175 MemoryattributeregistersforEMIFACE20xA0000000-0xA3FFFFFF 0x018482C0-0x018482FC MAR176-MAR191 MemoryattributeregistersforEMIFACE30xB0000000-0xB3FFFFFF 0x01848130-0x0184813C MAR76-MAR79 MemoryAttributeRegistersforVLYNQ0x4C000000-0x4FFFFFFF 0x01848300-0x0184837C MAR192-MAR223 Reserved0xC0000000-0xDFFFFFFF 0x01848380-0x018483BC MAR224-MAR239 MemoryattributeregistersforDDR20xE0000000-0xEFFFFFFF 0x018483C0-0x018483FC MAR240-MAR255 MemoryattributeregistersforDDR20xF0000000-0xFFFFFFFF 2.4 Memory Map Summary Table 2-3 shows the memory map address ranges of the device. The device has multiple on-chip memories associated with its processor and various subsystems. To help simplify software development, a unified memory map is used where possible to maintain a consistent view of device resources across all busmasters. Table2-3.MemoryMapSummary START END SIZE C64x+ ADDRESS ADDRESS (Bytes) MEMORYMAP 0x00000000 0x000FFFFF 1M Reserved 0x00100000 0x0011FFFF 128K VICP 0x00200000 0x007FFFFF 6M Reserved 0x00800000 0x008BFFFF 768K InternalROM 0x008C0000 0x009FFFFF 2M-768K Reserved 0x00A00000 0x00A3FFFF 256K L2SRAM(forbothDM647andDM648) 0x00A40000 0x00A7FFFF 256K L2SRAM(forDM648only) 0x00A80000 0x00DFFFFF 4M-512K Reserved 0x00E00000 0x00E07FFF 32K L1PSRAM 0x00E08000 0x00EFFFFF 1M–32K Reserved 0x00F00000 0x00F07FFF 32K L1DSRAM 0x00F08000 0x00FFFFFF 1M–32K Reserved 0x01000000 0x017FFFFF 8M Reserved 0x01800000 0x0180FFFF 64K C64x+InterruptController 0x01810000 0x01810FFF 4K C64x+Power-downControl 0x01811000 0x01811FFF 4K C64x+SecurityID 0x01812000 0x01812FFF 4K C64x+RevisionID 0x01813000 0x0181FFFF 52K Reserved 0x01820000 0x0182040F 1040B C64x+EMC 0x01820410 0x0182FFFF 64K–16 Reserved 0x01830000 0x0183FFFF 64K Reserved 0x01840000 0x0184FFFF 64K C64x+Memorycontrol 0x01850000 0x01BBFFFF 3,520K Reserved 0x01BC0000 0x01BCFFFF 64K Emulation 0x01BD0000 0x01BDFFFF 64K Reserved 0x01BE0000 0x01BFFFFF 128K Reserved 0x01BE0000 0x01FFFFFF 4.125M Reserved 0x02000000 0x0200007F 128B HPIControl 0x02000080 0x0203FFFF 256K–128 Reserved 0x02040000 0x02043FFF 16K McASPControl 12 DeviceOverview Copyright©2007–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 www.ti.com SPRS372H–MAY2007–REVISEDAPRIL2012 Table2-3.MemoryMapSummary(continued) START END SIZE C64x+ ADDRESS ADDRESS (Bytes) MEMORYMAP 0x02044000 0x020443FF 1K McASPData 0x02044400 0x020447FF 1K Timer0 0x02044800 0x02044BFF 1K Timer1 0x02044C00 0x02044FFF 1K Timer2 0x02045000 0x020453FF 1K Timer3 0x02045400 0x02045FFF 3K Reserved 0x02046000 0x02046FFF 4K PSC 0x02047000 0x020473FF 1K UART 0x02047400 0x020477FF 1K VICControl 0x02047800 0x02047BFF 1K SPI 0x02047C00 0x02047FFF 1K I2CDataandControl 0x02048000 0x020483FF 1K GPIO 0x02048400 0x020487FF 1K PCIControl 0x02048800 0x02048FFF 2K Reserved 0x02049000 0x02049FFF 4K Chip-LevelRegisters 0x0204A000 0x0207FFFF 216K Reserved 0x02080000 0x0209FFFF 128K VICPConfiguration 0x020A0000 0x020DFFFF 256K Reserved 0x020E0000 0x020E01FF 512 PLLController1 0x020E0200 0x0211FFFF 256K–512 Reserved 0x02120000 0x021201FF 512 PLLController2 0x02120200 0x0215FFFF 256K–512 Reserved 0x02160000 0x029CFFFF 9M-576K Reserved 0x02A00000 0x02A07FFF 32K EDMA3CC 0x02A08000 0x02A1FFFF 96K Reserved 0x02A20000 0x02A27FFF 32K EDMA3TC0 0x02A28000 0x02A2FFFF 32K EDMA3TC1 0x02A30000 0x02A37FFF 32K EDMA3TC2 0x02A38000 0x02A3FFFF 32K EDMA3TC3 0x02A40000 0x02A7FFFF 256K Reserved 0x02A80000 0x02A804FF 1.25K Reserved 0x02A80500 0x02ABFFFF 256K–1.25K Reserved 0x02AC0000 0x02ADFFFF 128K Reserved 0x02AE0000 0x02AFFFFF 128K Reserved 0x02B00000 0x02B000FF 256 Reserved 0x02B00100 0x02B03FFF 16K–256 Reserved 0x02B04000 0x02B0407F 128 Reserved 0x02B04080 0x02B3FFFF 256K–128 Reserved 0x02B40000 0x02B401FF 512 Reserved 0x02B40200 0x02B7FFFF 256K–512 Reserved 0x02B80000 0x02B9FFFF 128K Reserved 0x02BA0000 0x02BBFFFF 128K Reserved 0x02BC0000 0x02BFFFFF 256K Reserved 0x02C00000 0x02C03FFF 16K VP0Control 0x02C04000 0x02C07FFF 16K VP1Control 0x02C08000 0x02C0BFFF 16K VP2Control 0x02C0C000 0x02C0FFFF 16K VP3Control 0x02C10000 0x02C13FFF 16K VP4Control 0x02C14000 0x02C3FFFF 176K Reserved 0x02C40000 0x02C7FFFF 256K Reserved 0x02C80000 0x02CBFFFF 256K Reserved Copyright©2007–2012,TexasInstrumentsIncorporated DeviceOverview 13 SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 SPRS372H–MAY2007–REVISEDAPRIL2012 www.ti.com Table2-3.MemoryMapSummary(continued) START END SIZE C64x+ ADDRESS ADDRESS (Bytes) MEMORYMAP 0x02CC0000 0x02CFFFFF 256K Reserved 0x02D00000 0x02D01FFF 8K EthernetSubsystemCPPIRAM(1) 0x02D02000 0x02D02FFF 4K EthernetSubsystemControl 0x02D03000 0x02D03FFF 4K EthernetSubsystem3PSW 0x02D04000 0x02D047FF 2K EthernetSubsystemMDIO 0x02D04800 0x02D04BFF 1K EthernetSubsystemSGMII0 0x02D04C00 0x02D04FFF 1K EthernetSubsystemSGMII1(DM648only) 0x02D05000 0x02D057FF 2K Reserved 0x02D05800 0x02DBFFFF 746K Reserved 0x02DC0000 0x02DFFFFF 256K Reserved 0x02E00000 0x02E03FFF 16K Reserved 0x02E04000 0x02FFFFFF 2M–16K Reserved 0x03000000 0x03FFFFFF 16M Reserved 0x04000000 0x0FFFFFFF 192M Reserved 0x10000000 0x1FFFFFFF 256M Reserved 0x20000000 0x2FFFFFFF 256M Reserved 0x30000000 0x300000FF 256 Reserved 0x30000100 0x33FFFFFF 64M–256 Reserved 0x34000000 0x340000FF 256 Reserved 0x34000100 0x37FFFFFF 64M–256 Reserved 0x38000000 0x3BFFFFFF 64M VLYNQ 0x3C000000 0x3CFFFFFF 16M Reserved 0x3D000000 0x3DFFFFFF 16M Reserved 0x3E000000 0x3FFFFFFF 32M Reserved 0x40000000 0x4FFFFFFF 256M PCIData 0x50000000 0x51FFFFFF 32M VP0ChannelAData 0x52000000 0x53FFFFFF 32M VP0ChannelBData 0x54000000 0x55FFFFFF 32M VP1ChannelAData 0x56000000 0x57FFFFFF 32M VP1ChannelBData 0x58000000 0x59FFFFFF 32M VP2ChannelAData 0x5A000000 0x5BFFFFFF 32M VP2ChannelBData 0x5C000000 0x5DFFFFFF 32M Reserved 0x5E000000 0x5FFFFFFF 32M Reserved 0x60000000 0x61FFFFFF 32M VP3ChannelAData 0x62000000 0x63FFFFFF 32M VP3ChannelBData 0x64000000 0x65FFFFFF 32M VP4ChannelAData 0x66000000 0x67FFFFFF 32M VP4ChannelBData 0x68000000 0x6FFFFFFF 128M Reserved 0x70000000 0x77FFFFFF 128M EMIFAConfiguration 0x78000000 0x7FFFFFFF 128M DDR2EMIFConfiguration 0x80000000 0x8FFFFFFF 256M Reserved 0x90000000 0x9FFFFFFF 256M Reserved 0xA0000000 0xA3FFFFFF 64M EMIFACE2(2) 0xA4000000 0xAFFFFFFF 256-64M Reserved 0xB0000000 0xB3FFFFFF 64M EMIFACE3(2) 0xB4000000 0xBFFFFFFF 256-64M Reserved 0xC0000000 0xCFFFFFFF 256M Reserved (1) The8KCPPIDescriptormemoryismappedtoanaddressrange0x02C82000-0x02C83FFF,fromtheperspectiveoftheEthernet subsystem3PSW.Thebufferdescriptors,whenaccessedfromtheC64x+,areaddressedfrom0x02D00000.However,withinthese bufferdescriptors,whenthepointertothenextbufferdescriptorisprogrammed,theEthernetsubsystem3PSWisinterpretingthisvalue. Thus,thisprogrammedvalueshouldbeintheaddressrangestartingfrom0x02C82000. (2) TheEMIFACS0andCS1arenotfunctionallysupported;therefore,theyarenotpinnedout. 14 DeviceOverview Copyright©2007–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 www.ti.com SPRS372H–MAY2007–REVISEDAPRIL2012 Table2-3.MemoryMapSummary(continued) START END SIZE C64x+ ADDRESS ADDRESS (Bytes) MEMORYMAP 0xD0000000 0xDFFFFFFF 256M Reserved 0xE0000000 0xEFFFFFFF 256M DDR2SDRAM 0xF0000000 0xFFFFFFFF 256M DDR2SDRAM Copyright©2007–2012,TexasInstrumentsIncorporated DeviceOverview 15 SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 SPRS372H–MAY2007–REVISEDAPRIL2012 www.ti.com 2.5 Pin Assignments Extensive use of pin multiplexing is used to accommodate the largest number of peripheral functions in the smallest possible package. Pin multiplexing is controlled using a combination of hardware configuration at device reset and software programmable register settings. For more information on pin muxing,seeSection3.2.6,PINMUXRegister. 2.5.1 Pin Map (Bottom View) Figure 2-2 through Figure 2-5 show the bottom view of the ZUT package pin assignments in four quadrants(A,B,C,andD). 1 2 3 4 5 6 7 8 9 10 11 12 AC VSS DVDD33 AHCLKX AHCLKR DVDD33 ACLKR ACLKX VSS SGMII1RXN VSS REFCLKN VSS AB VP2CLK0 VP2CTL1 AMUTEIN AXR3 VSS AXR0 DVDD33 AVDDT SGMII1RXP AVDDR REFCLKP DVDD33 AA VP2CTL0 VP2D03 VSS AXR6 VADXARC9/ AXR2 AFSX VSS SGMII0RXP SGMII0RXN VSS PGRPE0Q3/ Y VVPS2CCRTULN2/ VP2D06 VP2D04 DVDD33 AXR4 AXR1 SATXCRL8K/ DVDD33 VSS VSS SGMII0TXP RSV21 W VPV2CCLLKK1/ VVPR2XDD102/ VP2D07 VP2D09 VP2D02 AFSR VSS SGMII1TXP SGMII1TXN AVDDA SGMII0TXN RSV22 V VSS DVDD33 V/VPR2XDD113 VVPR2XDD124/ VP2D08 AXR7 AXR5 CVDD VSS RSV17 AVDDA PGINPT0A2/ U VVPR2XDD135/ VVPT2XDD117/ VVPT2XDD106/ VVPT2XDD139/ VVPT2XDD128/ VP2D05 AMUTE MDIO MDCLK DVDDD AVDDT PGRPS0T1/ T VAPE3CCLLKKIN0/ AAVWP3EC/ ATSLW0/E VAPE3DD0035/ VAPE3DD0024/ VAPE3DD0013/ VAPE3DD0002/ VSS DVDD33 VSS DVDDD VSS DVDD33 R VPA3RC/TWL1/ VAPE3DD0182/ VAPE3DD0079/ VAPE3DD0068/ VAPE3DD0057/ VAPE3DD0046/ DVDD33 CVDD CVDDESS VSS CVDDESS VSS P AVEPC3LCKLOKU1/T AVAPO3EC/ ATSL2O/E VAPE3DD1126/ VAPE3DD1115/ VAPE3DD1104/ VAPE3DD0193/ VSS DVDD33 VSS CVDD VSS CVDD N VSS DVDD33 PLLV1 VAPE3DD1137/ VAPE3DD1159/ VAPE3DD1148/ DVDD33 VSS CVDD VSS CVDD VSS M CLKIN1 RSV9 SYSCLK5 VAPB4ED0013/ VAPE4AD1004/ VP4D05 VSS DVDD33 VSS CVDD VSS CVDD Figure2-2.ZUTPinMap[TopLeftQuadrant] 16 DeviceOverview Copyright©2007–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 www.ti.com SPRS372H–MAY2007–REVISEDAPRIL2012 13 14 15 16 17 18 19 20 21 22 23 AHDD2266/ AHDD2222/ HPHCWLKIL/ VSS PHCDBSE21/ AHDD1144/ DVDD33 PGCPB0E40/ AHDD0022/ AHDD0044/ DVDD33 AC AHDD2277/ AHDD2233/ AHDD1177/ DVDD33 PHIRRDDYY/ AHDD1122/ VSS AHDD0088/ AHDD0055/ AHDD0011/ VSS AB AD28/ PIDSEL/ AD18/ PFRAME/ PTRDY/ AD15/ AD13/ AD09/ AD06/ AD00/ AD03/ AA HD28 GP06 HD18 HINT GP05 HD15 HD13 HD09 HD06 HD00 HD03 AD29/ PCBE3/ AD19/ AD16/ PDEVSEL/ PSTOP/ AD11/ AD10/ AD07/ VP0CTL0 VP0CLK0 Y HD29 GP07 HD19 HD16 HCNTL1 HCNTL0 HD11 HD10 HD07 AHDD3300/ AHDD2244/ AHDD2200/ PHCRB/EW2/ PPHECRSR/ PHSDESR1R/ PHPAASR/ VP0D02 VP0D06 VSS DVDD33 W AD31/ Ad25/ AD21/ VP0D12/ HD31 HD25 HD21 DVDD33 VSS VP0D03 VP0D05 VP0D09 GP12 VP0CTL1 VP0CLK1 V PGGPN0T0/ VSS DVDD33 VSS DVDD33 VP0D04 VP0D08 VP0D16 VP0D18 VP0D17 VP0CTL2 U VSS DVDD33 VSS CVDD VSS VP0D07 VPG0PD1133/ VPG0PD1144/ VPG0PD1155/ VSS DVDD33 T CVDD VSS CVDD VSS DVDD33 VP0D19 VPG1PD1062/ VPG1PD2017/ VPG1PD2006/ VPG1PD1095/ VP1CTL0 R VP1D04/ VP1D03/ VP1D14/ VP1D13/ VSS CVDD VSS DVDD33 VSS GP18 GP17 GP26 GP25 VP1CTL1 VP1CLK0 P VP1D17/ VP1D12/ VP1D09/ VP1D08/ CVDD VSS CVDD VSS DVDD33 GP29 GP24 GP23 GP22 VP1CTL2 VP1CLK1 N VP1D16/ VP1D19/ VP1D15/ VP1D18/ VSS CVDD VSS DVDD33 VSS GP28 GP31 GP27 GP30 VSS DVDD33 M Figure2-3.ZUTPinMap[TopRightQuadrant] Copyright©2007–2012,TexasInstrumentsIncorporated DeviceOverview 17 SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 SPRS372H–MAY2007–REVISEDAPRIL2012 www.ti.com L VAPA4CRLDKY0/ VAPB4ED0002/ VPA4CDE026/ VPA4CDE037/ VAPE4AD0008/ VAPE4AD0133/ DVDD33 VSS CVDD VSS CVDD VSS K VP4CLK1 ASVAPD4SC/ TALS2R/E VAPE4AD0019/ VAPE4AD0122/ VAPE4AD0144/ VAPE4AD0199/ VSS DVDD33 VSS CVDD VSS CVDD J VPA4BCAT1L1/ VPA4BCAT0L0/ VAPE4AD0155/ VAPE4AD0166/ VAPE4AD0177/ VAPE4AD0188/ DVDD33 VSS CVDD VSS CVDD VSS H VSS UHPIEN HPAIWEAID1T6H/ AEA23 AEA19 RSAVE_BAO15OT/ RSV7 RSV8 CVDD1 DVDD18 VSS DVDD18 EMIFA AECLKIN BOOT G DVDD33 FA/SATEBAO21OT WIDTH/ SEL/ APECAI6168/ MODE3/ PLLV2 VSS DVDD18 VSS DVDD18 VSS AEA22 AEA17 AEA14 DEVICE BOOT BOOT BOOT F CLKIN2 ENABLE0/ MODE0/ MODE1/ MODE2/ RSV18 VSS DVDD18 DDR_CS DDR_A13 DDR_A06 DDR_A08 AEA20 AEA11 AEA12 AEA13 E RSV12 RSV11 RSV14 RSV13 DVDD18 VSS DDR_D07 DDR_D04 DDR_D00 DDR_RAS DDR_BA[2] DDR_A12 D RSV4 RSV3 RSV6 RSV5 DDQDMR[_1] DDR_D10 DQDGDART_E0 DDR_D05 VSS DDR_CAS DDR_WE VSS C RSV20 RSV19 DVDD18 VSS DDR_D15 DDR_D08 DDR_D06 DDR_D03 DDR_D01 DVDD18 DVRDERF_ DDR_BA[0] B DVDD18 VDD18MON DDR_D12 DDR_D14 DVDD18 DQDGDART_E1 DDR_D09 DDQDMR[_0] DDR_D02 AVDLL1 DDR_CKE DDR_BA[1] A VSS RSV10 DDR_D11 DDR_D13 VSS DDQDSR[_1] DDQDSR[_1] DDQDSR[_0] DDQDSR[_0] RSV15 DDR_CLK DDR_CLK 1 2 3 4 5 6 7 8 9 10 11 12 Figure2-4.ZUTPinMap[BottomLeftQuadrant] 18 DeviceOverview Copyright©2007–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 www.ti.com SPRS372H–MAY2007–REVISEDAPRIL2012 CVDD VSS CVDD VSS DVDD33 EMU4 VCCMON RSV1 RSV2 TMS TRST L VSS CVDD VSS DVDD33 VSS EMU11 EMU6 EMU3 EMU2 EMU1 EMU0 K CVDD1 VSS CVDD VSS DVDD33 NMI EMU10 EMU8 EMU5 TDI TDO J VSS DVDD18 VSS DVDD33 VSS POR RESETSTAT EMU9 EMU7 DVDD33 TCLK H DVDD18 VSS DVDD18 VSS DVDD18 VSS DVDD33 RESET VDD33MON VSS UASRPTIDRIT/S G DDR_A02 DVDD18 VSS DVDD18 VSS DVDD18 VSS DVDD33 USAPRITDCOT/S SPICLK USAPRICTSR2X/ F DDR_ODT0 DDR_A03 DDQDMR[_2] DDR_D19 DDR_D23 DQDGDART_E2 DDR_D31 T0GINPP0182/ T1GINPP1102/ DVDD33 VSS E T0OUT12/ SPICS1/ D DDR_A09 DDR_A04 DDR_A00 DDR_D18 DDR_D22 DDR_D25 DDR_D29 VSS GP09 SCL UARTTX T1OUT12/ C DVDD18 DDR_A05 DDR_A01 DDR_D17 DDR_D21 DDR_D24 DDR_D27 DDR_D30 DVDD18 GP11 SDA DDR_ B DDR_A11 DDR_A07 DVDD18 DDR_D16 DDR_D20 DVDD18 DDR_D26 DDR_D28 DQM[3] AVDLL2 DVDD18 DDR_A10 DDR_ODT1 VSS DDQDSR[_2] DDQDSR[_2] VSS DDQDSR[_3] DDQDSR[_3] DQDGDART_E3 RSV16 VSS A 13 14 15 16 17 18 19 20 21 22 23 Figure2-5.ZUTPinMap[BottomRightQuadrant] Copyright©2007–2012,TexasInstrumentsIncorporated DeviceOverview 19 SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 SPRS372H–MAY2007–REVISEDAPRIL2012 www.ti.com 2.6 Terminal Functions The terminal functions tables (Table 2-4 through Table 2-5) identify the external signal names, the associatedpin(ball)numbersalongwiththemechanicalpackagedesignator,thepintype,whetherthepin has any internal pullup or pulldown resistors, and a functional pin description. For more detailed information on device configuration, peripheral selection, multiplexed/shared pin, and debugging considerations,seeSection3. All device boot and configuration pins are multiplexed with functional pins. These pins function as device boot and configuration pins only during device reset. When both the reset pin (RESET) and the power-on reset pin (POR) are deasserted, the input states of these multiplexed device boot and configuration pins are sampled and latched into the BOOTCFG register. For proper device operation, these pins must be pulledup/downtothedesiredvalueviaanexternalresistor. Table2-4.TerminalFunctions TERMINALNAME NO TYPE( INTERNAL OPER DESCRIPTION 1) PULLUP/ VOLT PULLDOWN Clock/PLLConfiguration CLKIN1 M1 I IPD 3.3V ClockInputforPLL1 CLKIN2 F1 I IPD 3.3V ClockInputforPLL2 REFCLKN(2) AC11 I DifferentialReferenceClockinput(negative)forSGMII REFCLKP(2) AB11 I DifferentialReferenceClockinput(positive)forSGMII PLLV1 N3 A 1.8V 1.8-VI/OSupplyVoltageforPLL1 PLLV2 G7 A 1.8V 1.8-VI/OSupplyVoltageforPLL2 SYSCLK5 M3 I/O/Z IPD 3.3V Clockoutofdevicespeed/4 JTAG TCLK H23 I IPU 3.3V JTAGTestPortClock TDI J22 I IPU 3.3V JTAGTestPortDataIn TDO J23 OZ IPU 3.3V JTAGTestPortDataOut TMS L22 I IPU 3.3V JTAGTestPortModeSelect TRST L23 I IPD 3.3V JTAGTestPortReset EMU0 K23 I/O/Z IPU 3.3V JTAGTestPortEmulation0 EMU1 K22 I/O/Z IPU 3.3V JTAGTestPortEmulation1 EMU2 K21 I/O/Z IPU 3.3V JTAGTestPortEmulation2 EMU3 K20 I/O/Z IPU 3.3V JTAGTestPortEmulation3 EMU4 L18 I/O/Z IPU 3.3V JTAGTestPortEmulation4 EMU5 J21 I/O/Z IPU 3.3V JTAGTestPortEmulation5 EMU6 K19 I/O/Z IPU 3.3V JTAGTestPortEmulation6 EMU7 H21 I/O/Z IPU 3.3V JTAGTestPortEmulation7 EMU8 J20 I/O/Z IPU 3.3V JTAGTestPortEmulation8 EMU9 H20 I/O/Z IPU 3.3V JTAGTestPortEmulation9 EMU10 J19 I/O/Z IPU 3.3V JTAGTestPortEmulation10 EMU11 K18 I/O/Z IPU 3.3V JTAGTestPortEmulation11 RESET/INTERRUPTS NMI J18 I IPD 3.3V NonmaskableInterrupt RESETSTAT H19 O 3.3V ResetStatusPin RESET G20 I 3.3V DeviceReset POR H18 I 3.3V PowerOnReset (1) I=Input,O=Output,Z=Highimpedance,S=Supplyvoltage,GND=Ground,A=Analogsignal (2) TheclockinputbuffersontheREFCLKP/NpinsarecompatiblewithLVDSandLVPECLclocksources.Theseinputbuffersincludea 100-Ωtermination(PtoN)andacommon-modebiasing.Becausethecommon-modebiasingisincluded,theclocksourcemustbeAC coupled. 20 DeviceOverview Copyright©2007–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 www.ti.com SPRS372H–MAY2007–REVISEDAPRIL2012 Table2-4.TerminalFunctions(continued) TERMINALNAME NO TYPE( INTERNAL OPER DESCRIPTION 1) PULLUP/ VOLT PULLDOWN HOST-PORTINTERFACE(HPI)orPERIPHERALCOMPONENTINTERCONNECT(PCI)orGPIO[0:7] AD00/HD00 AA22 I/O/Z 3.3V HostPortdata[15:00]pinorPCIdata-addressbus[15:00] [default] AD01/HD01 AB22 I/O/Z 3.3V AD02/HD02 AC21 I/O/Z 3.3V AD03/HD03 AA23 I/O/Z 3.3V AD04/HD04 AC22 I/O/Z 3.3V AD05/HD05 AB21 I/O/Z 3.3V AD06/HD06 AA21 I/O/Z 3.3V AD07/HD07 Y21 I/O/Z 3.3V AD08/HD08 AB20 I/O/Z 3.3V AD09/HD09 AA20 I/O/Z 3.3V AD10/HD10 Y20 I/O/Z 3.3V AD11/HD11 Y19 I/O/Z 3.3V AD12/HD12 AB18 I/O/Z 3.3V AD13/HD13 AA19 I/O/Z 3.3V AD14/HD14 AC18 I/O/Z 3.3V AD15/HD15 AA18 I/O/Z 3.3V AD16/HD16 Y16 I/O/Z 3.3V HostPortdata[31:16]pinorPCIdata-addressbus[31:16] [default] AD17/HD17 AB15 I/O/Z 3.3V AD18/HD18 AA15 I/O/Z 3.3V AD19/HD19 Y15 I/O/Z 3.3V AD20/HD20 W15 I/O/Z 3.3V AD21/HD21 V15 I/O/Z 3.3V AD22/HD22 AC14 I/O/Z 3.3V AD23/HD23 AB14 I/O/Z 3.3V AD24/HD24 W14 I/O/Z 3.3V AD25/HD25 V14 I/O/Z 3.3V AD26/HD26 AC13 I/O/Z 3.3V AD27/HD27 AB13 I/O/Z 3.3V AD28/HD28 AA13 I/O/Z 3.3V AD29/HD29 Y13 I/O/Z 3.3V AD30/HD30 W13 I/O/Z 3.3V AD31/HD31 V13 I/O/Z 3.3V PPAR/HAS W19 I/O/Z 3.3V HostAddressStrobe(I)orPCIparity[default] PSTOP/HCNTL0 Y18 I/O/Z 3.3V HostControlselectsbetweencontrol,address,ordataregisters(I) orPCIStop[default] PDEVSEL/HCNTL1 Y17 I/O/Z 3.3V HostControlselectsbetweencontrol,address,ordataregisters(I) orPCIDeviceSelect[default] PPERR/HCS W17 I/O/Z 3.3V HostChipSelect(I)orPCIParityError[default] PSERR/HDS1 W18 I/O/Z 3.3V HostDataStrobe1(I)orPCISystemError[default] PCBE0/GP04 AC20 I/O/Z 3.3V PCICommand/ByteEnable0orGP[4][default PCBE1/HDS2 AC17 I 3.3V PCICommand/ByteEnable1orhostdatastrobe2 PCBE2/HR/W W16 I/O/Z 3.3V PCICommand/ByteEnable2orhostreadorwriteselect(I) PCBE3/GP07 Y14 I/O/Z 3.3V PCICommand/ByteEnable3orGPIO[7] PCLK/HHWIL AC15 I/O/Z 3.3V PCIClock(I)[default]orhostHalf-wordSelect-firstorsecond half-word(notnecessarilyhighorloworder)[ForHPI16buswidth selectiononly](I) Copyright©2007–2012,TexasInstrumentsIncorporated DeviceOverview 21 SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 SPRS372H–MAY2007–REVISEDAPRIL2012 www.ti.com Table2-4.TerminalFunctions(continued) TERMINALNAME NO TYPE( INTERNAL OPER DESCRIPTION 1) PULLUP/ VOLT PULLDOWN PFRAME/HINT AA16 I/O/Z 3.3V PCIFrameorhostinterruptfromDSPtohost(O/Z) PIRDY/HRDY AB17 I/O/Z 3.3V PCIInitiatorReady[default]orHostReadyfromDSPtohost(O/Z) PGNT/GP00 U13 I/O/Z 3.3V PCIBusGrant(I)orGPIO[0] PRST/GP01 U12 I/O/Z 3.3V PCIReset(I)orGPIO[1] PINTA/GP02 V12 I/O/Z 3.3V PCIInterruptA(O/Z)orGPIO[2] PREQ/GP03 AA12 I/O/Z 3.3V PCIBusRequest(O/Z)orGPIO[3] PTRDY/GP05 AA17 I/O/Z 3.3V PCITargetReadyorGPIO[5] PIDSEL/GP06 AA14 I/O/Z 3.3V PCIInitializationDeviceSelect(I)orGPIO[6] DDR2MEMORYCONTROLLER DDR_BA[0] C12 I/O/Z 1.8V DDR2MemoryControllerBankAddressControl DDR_BA[1] B12 I/O/Z 1.8V DDR_BA[2] E11 I/O/Z 1.8V DDR_CS F9 I/O/Z 1.8V DDR2MemoryControllerMemorySpaceEnable DDR_A00 D15 I/O/Z 1.8V DDR2MemoryControllerExternalAddress DDR_A01 C15 I/O/Z 1.8V DDR_A02 F13 I/O/Z 1.8V DDR_A03 E14 I/O/Z 1.8V DDR_A04 D14 I/O/Z 1.8V DDR_A05 C14 I/O/Z 1.8V DDR_A06 F11 I/O/Z 1.8V DDR_A07 B14 I/O/Z 1.8V DDR_A08 F12 I/O/Z 1.8V DDR_A09 D13 I/O/Z 1.8V DDR_A10 A13 I/O/Z 1.8V DDR_A11 B13 I/O/Z 1.8V DDR_A12 E12 I/O/Z 1.8V DDR_A13 F10 I/O/Z 1.8V DDR_CLK A12 I/O/Z 1.8V NegativeDDR2MemoryControllerOutputClock(CLKIN2 frequencyx10) DDR_CLK A11 I/O/Z 1.8V DDR2MemoryControllerOutputClock(CLKIN2frequencyx10) DDR_D00 E9 I/O/Z 1.8V DDR2MemoryControllerExternalData DDR_D01 C9 I/O/Z 1.8V DDR_D02 B9 I/O/Z 1.8V DDR_D03 C8 I/O/Z 1.8V DDR_D04 E8 I/O/Z 1.8V DDR_D05 D8 I/O/Z 1.8V DDR_D06 C7 I/O/Z 1.8V DDR_D07 E7 I/O/Z 1.8V DDR_D08 C6 I/O/Z 1.8V DDR_D09 B7 I/O/Z 1.8V DDR_D10 D6 I/O/Z 1.8V DDR_D11 A3 I/O/Z 1.8V DDR_D12 B3 I/O/Z 1.8V DDR_D13 A4 I/O/Z 1.8V DDR_D14 B4 I/O/Z 1.8V DDR_D15 C5 I/O/Z 1.8V 22 DeviceOverview Copyright©2007–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 www.ti.com SPRS372H–MAY2007–REVISEDAPRIL2012 Table2-4.TerminalFunctions(continued) TERMINALNAME NO TYPE( INTERNAL OPER DESCRIPTION 1) PULLUP/ VOLT PULLDOWN DDR_D16 B16 I/O/Z 1.8V DDR2MemoryControllerExternalData(continued) DDR_D17 C16 I/O/Z 1.8V DDR_D18 D16 I/O/Z 1.8V DDR_D19 E16 I/O/Z 1.8V DDR_D20 B17 I/O/Z 1.8V DDR_D21 C17 I/O/Z 1.8V DDR_D22 D17 I/O/Z 1.8V DDR_D23 E17 I/O/Z 1.8V DDR_D24 C18 I/O/Z 1.8V DDR_D25 D18 I/O/Z 1.8V DDR_D26 B19 I/O/Z 1.8V DDR_D27 C19 I/O/Z 1.8V DDR_D28 B20 I/O/Z 1.8V DDR_D29 D19 I/O/Z 1.8V DDR_D30 C20 I/O/Z 1.8V DDR_D31 E19 I/O/Z 1.8V DDR_ODT0 E13 I/O/Z 1.8V On-dieterminationsignalstoexternalDDR2SDRAM.Thesepins arereservedforfutureuseandshouldnotbeconnectedtothe DDR_ODT1 A14 I/O/Z 1.8V DDR2SDRAM. Note:Therearenoon-dieterminationresistorsimplementedon theDM647/DM648DSPdie. DDR_CAS D10 I/O/Z 1.8V DDR2MemoryControllerSDRAMcolumnaddressstrobe DDR_CKE B11 I/O/Z 1.8V DDR2MemoryControllerSDRAMclock-enable DDR_DQGATE0 D7 I/O/Z 1.8V DDR2MemoryControllerDataStrobeGate DDR_DQGATE1 B6 I/O/Z 1.8V DDR_DQGATE2 E18 I/O/Z 1.8V DDR_DQGATE3 A21 I/O/Z 1.8V DDR_DQM[0] B8 I/O/Z 1.8V DDR2MemoryControllerByte-enableControls.Decodedfromthe low-orderaddressbits.Thenumberofaddressbitsorbyte DDR_DQM[1] D5 I/O/Z 1.8V enablesuseddependsonthewidthofexternalmemory.Byte-write DDR_DQM[2] E15 I/O/Z 1.8V enablesformosttypesofmemory.Canbedirectlyconnectedto SDRAMreadandwritemasksignal(SDQM). DDR_DQM[3] B21 I/O/Z 1.8V DDR_DQS[0] A9 I/O/Z 1.8V DDR2MemoryControllerDataStrobe[3:0] DDR_DQS[1] A7 I/O/Z 1.8V DDR_DQS[2] A17 I/O/Z 1.8V DDR_DQS[3] A20 I/O/Z 1.8V DDR_DQS[0] A8 I/O/Z 1.8V DDR2MemoryControllerDataStrobe[3:0]Negative DDR_DQS[1] A6 I/O/Z 1.8V DDR_DQS[2] A16 I/O/Z 1.8V DDR_DQS[3] A19 I/O/Z 1.8V DDR_RAS E10 I/O/Z 1.8V DDR2MemoryControllerSDRAMRowAddressStrobe DDR_WE D11 I/O/Z 1.8V DDR2MemoryControllerSDRAMWriteEnable Copyright©2007–2012,TexasInstrumentsIncorporated DeviceOverview 23 SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 SPRS372H–MAY2007–REVISEDAPRIL2012 www.ti.com Table2-4.TerminalFunctions(continued) TERMINALNAME NO TYPE( INTERNAL OPER DESCRIPTION 1) PULLUP/ VOLT PULLDOWN CONFIGURATIONANDEMIFA DEVICEENABLE0/ F2 I/O/Z IPD 3.3V EMIFAExternalAddress20(wordaddress).(O/Z)Forproper AEA20 deviceoperation,thispinmustbeexternallypulledupwitha1-kΩ resistoratdevicereset EMIFAWIDTH/ G3 I/O/Z IPD 3.3V EMIFAExternalAddress22(wordaddress).(O/Z)EMIFAdata AEA22 buswidthselectionpinstatecapturedattherisingedgeof RESET. 0-setsEMIFACS2to8-bitdatabuswidth 1-setsEMIFACS2to16bitdatabuswidth.Fordetails,see Section3. FASTBOOT/ G2 I/O/Z IPD 3.3V EMIFAExternalAddress22(wordaddress).(O/Z)EnablesFAST AEA21 BOOTofthedevice.Fordetails,seeSection3. UHPIEN H2 I IPD 3.3V UHPIEnablePin.Thispincontrolstheselection(enable/disable) oftheHPIandGPIO[0:7]muxedwithPCI.Fordetails,see Section3. HPIWIDTH/ H3 I/O/Z IPD 3.3V EMIFAExternalAddress16(wordaddress)(O/Z)HPIperipheral AEA16 buswidth(HPI_WIDTH)select(AppliesonlywhenHPIisenabled; UHPIENpin=1) RSV_BOOT/ H6 I/O/Z IPU 3.3V EMIFAExternalAddress15(wordaddress)(O/Z)Forproper AEA15 deviceoperation,thispinmustbeexternallypulledupwitha1-kΩ resistoratdevicereset. PCI66/AEA18 G5 I/O/Z IPD 3.3V PCIFrequencySelection(PCI66).ThePCIperipheralmustbe enabled(UHPIEN=0)tousethisfunction.PCI66_AEA18selects thePCIoperatingfrequencyof66MHzor33MHz.PCIoperating frequencyisselectedatresetviathepullup/pulldownresistoron thePCI66pinAEA18: 0-PCIoperatesat33MHz(default) 1-PCIoperatesat66MHz. BOOTMODE0/AEA11 F3 I/O/Z IPD 3.3V TheBOOTMODE[3:0]defineswhatbootcodeisexecutedon BOOTMODE1/AEA12 F4 devicereset.SeeSection3.2.1formoredetails. BOOTMODE2/AEA13 F5 BOOTMODE3/AEA14 G6 INTER-INTEGRATEDCIRCUIT(I2C) SCL D22 I/O/Z 3.3V I2Cclock.WhentheI2Cmoduleisused,useanexternalpullup resistor. SDA C23 I/O/Z 3.3V I2Cdata.WhenI2Cisused,makecertainthereisanexternal pullupresistor. SGMII0/1andMDIO(1)(2) SGMII0RXN AA10 I 1.2V DifferentialSGMIIPort0RXinput(negative) SGMII0RXP AA9 I 1.2V DifferentialSGMIIPort0RXinput(positive) SGMII0TXN W11 O 1.2V DifferentialSGMIIPort0TXoutput(negative) SGMII0TXP Y11 O 1.2V DifferentialSGMIIPort0TXoutput(positive) SGMII1RXN AC9 I 1.2V DifferentialSGMIIPort1RXinput(negative) SGMII1RXP AB9 I 1.2V DifferentialSGMIIPort1RXinput(positive) SGMII1TXN W9 O 1.2V DifferentialSGMIIPort1TXoutput(negative) SGMII1TXP W8 O 1.2V DifferentialSGMIIPort1TXoutput(positive) MDCLK U9 OZ IPD 3.3V MDIOSerialClock(MDCLK) (1) ForDM647:LeavetheSGMII1RXP/NandSGMII1TXP/Npinsdisconnected.DisableENTX/ENRXbitsinCFGTX1/CFGRX1forSGMII1 andstillconfiguretheCFGPLLbecausetheSerDesTXBCLK0isusedastheinternalVBUSclock.ForDM648:ifoneoftheSGMIIpair isnotused,thesameapproachmustbeused. (2) IftheEthernetSubsystemisnotusedatall,theseconnectionsmustbefollowed: • DisconnectAA10,AA9,W11,Y11,AC9,AB9,W9,W8,andU9 • ConnectAC11toCV DD • ConnectAB11toV SS • DirectlyconnectV11(V ),W10(V ),T10(V ),U10(V ),AB8(V ),U11(V ),R9(ESScorepower),R11(ESScore DDA DDA DDD DDD DDT DDT power)toCV DD • DirectlyconnectAB10,(V )toDV DDR DD18 24 DeviceOverview Copyright©2007–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 www.ti.com SPRS372H–MAY2007–REVISEDAPRIL2012 Table2-4.TerminalFunctions(continued) TERMINALNAME NO TYPE( INTERNAL OPER DESCRIPTION 1) PULLUP/ VOLT PULLDOWN MDIO U8 I/O/Z IPU 3.3V MDIOSerialData(MDIO) SPIorUART SPICLK F22 I/O/Z IPU 3.3V SPIClockOutput SPICS1/UARTTX D23 I/O/Z IPU 3.3V SPIChipSelect1orUARTTransmit(O/Z) SPICS2/UARTRX F23 I/O/Z IPU 3.3V SPIChipSelect2orUARTReceive SPIDI/UARTRTS G23 I/O/Z IPU 3.3V SPIDatainputorUARTReadytosend(O/Z) SPIDO/UARTCTS F21 I/O/Z IPU 3.3V SPIDataOutputorUARTCleartosend TIMER0/1orGPIO[8:11] T0INP12/GP08 E20 I/O/Z IPD 3.3V Timer0inputpinforlower32-bitcounter(I)orGPIO8 T0OUT12/GP09 D21 I/O/Z IPD 3.3V Timer0outputpinforlower32-bitcounter(O/Z)orGPIO9 T1INPL/GP10 E21 I/O/Z IPD 3.3V Timer1inputpinforlower32-bitcounter(I)orGPIO10 T1OUT12/GP11 C22 I/O/Z IPD 3.3V Timer1outputpinforlower32-bitcounter(O/Z)orGPIO11 McASPORVIDEOPORTORVIC AHCLKR AC4 I/O/Z IPD 3.3V McASPReceivehigh-frequencymasterclock AHCLKX AC3 I/O/Z IPD 3.3V McASPTransmithigh-frequencymasterclock ACLKR AC6 I/O/Z IPD 3.3V McASPReceivemasterclock ACLKX AC7 I/O/Z IPD 3.3V McASPTransmitmasterclock AFSR W6 I/O/Z IPD 3.3V McASPReceiveFramesyncorleft/rightclock(LRCLK) AFSX AA7 I/O/Z IPD 3.3V McASPTransmitFramesyncorleft/rightclock(LRCLK) AXR0 AB6 I/O/Z IPD 3.3V McASPDataPin[0:7] AXR1 Y6 IPD 3.3V AXR2 AA6 IPD 3.3V AXR3 AB4 IPD 3.3V AXR4 Y5 IPD 3.3V AXR5 V7 IPD 3.3V AXR6 AA4 IPD 3.3V AXR7 V6 IPD 3.3V STCLK/AXR8 Y7 I/O/Z IPD 3.3V TheSTCLKsignaldrivesthehardwarecounterforusebythe videoports(I)orMcASPdatapin8. VDAC/AXR9 AA5 I/O/Z IPD 3.3V VCXOInterpolatedControlPort(VIC)single-bitdigital-to-analog converter(VDAC)output(O)orMcASPdatapin9 AMUTEIN AB3 I/O/Z IPD 3.3V McASPMuteInput AMUTE U7 I/O/Z IPD 3.3V McASPMuteOutput VIDEOPORT0ORGPIO[12:15] VP0CLK0 Y23 I IPU 3.3V VideoPort0Clock0(I) VP0CLK1 V23 I/O/Z IPU 3.3V VideoPort0Clock1 VP0CTL0 Y22 I/O/Z IPU 3.3V VideoPort0Control0 VP0CTL1 V22 I/O/Z IPU 3.3V VideoPort0Control1 VP0CTL2 U23 I/O/Z IPU 3.3V VideoPort0Control2 VP0D02 W20 I/O/Z IPD 3.3V VideoPort0Data2 VP0D03 V18 I/O/Z IPD 3.3V VideoPort0Data3 VP0D04 U18 I/O/Z IPD 3.3V VideoPort0Data4 VP0D05 V19 I/O/Z IPD 3.3V VideoPort0Data5 VP0D06 W21 I/O/Z IPD 3.3V VideoPort0Data6 VP0D07 T18 I/O/Z IPD 3.3V VideoPort0Data7 VP0D08 U19 I/O/Z IPD 3.3V VideoPort0Data8 Copyright©2007–2012,TexasInstrumentsIncorporated DeviceOverview 25 SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 SPRS372H–MAY2007–REVISEDAPRIL2012 www.ti.com Table2-4.TerminalFunctions(continued) TERMINALNAME NO TYPE( INTERNAL OPER DESCRIPTION 1) PULLUP/ VOLT PULLDOWN VP0D09 V20 I/O/Z IPD 3.3V VideoPort0Data9 VP0D12/GP12 V21 I/O/Z IPD 3.3V VideoPort0Data12orGPIO12 VP0D13/GP13 T19 I/O/Z IPD 3.3V VideoPort0Data13orGPIO13 VP0D14/GP14 T20 I/O/Z IPD 3.3V VideoPort0Data14orGPIO14 VP0D15/GP15 T21 I/O/Z IPD 3.3V VideoPort0Data15orGPIO15 VP0D16 U20 I/O/Z IPD 3.3V VideoPort0Data16 VP0D17 U22 I/O/Z IPD 3.3V VideoPort0Data17 VP0D18 U21 I/O/Z IPD 3.3V VideoPort0Data18 VP0D19 R18 I/O/Z IPD 3.3V VideoPort0Data19 VIDEOPORT1ORGPIO[16:31] VP1CLK0 P23 I IPU 3.3V VideoPort1Clock0 VP1CLK1 N23 I/O/Z IPU 3.3V VideoPort1Clock1 VP1CTL0 R23 I/O/Z IPU 3.3V VideoPort1Control0 VP1CTL1 P22 I/O/Z IPU 3.3V VideoPort1Control1 VP1CTL2 N22 I/O/Z IPU 3.3V VideoPort1Control2 VP1D02/GP16 R19 I/O/Z IPD 3.3V VideoPort1Data2orGPIO16 VP1D03/GP17 P19 I/O/Z IPD 3.3V VideoPort1Data3orGPIO17 VP1D04/GP18 P18 I/O/Z IPD 3.3V VideoPort1Data4orGPIO18 VP1D05/GP19 R22 I/O/Z IPD 3.3V VideoPort1Data5orGPIO19 VP1D06/GP20 R21 I/O/Z IPD 3.3V VideoPort1Data6orGPIO20 VP1D07/GP21 R20 I/O/Z IPD 3.3V VideoPort1Data7orGPIO21 VP1D08/GP22 N21 I/O/Z IPD 3.3V VideoPort1Data8orGPIO22 VP1D09/GP23 N20 I/O/Z IPD 3.3V VideoPort1Data9orGPIO23 VP1D12/GP24 N19 I/O/Z IPD 3.3V VideoPort1Data12orGPIO24 VP1D13/GP25 P21 I/O/Z IPD 3.3V VideoPort1Data13orGPIO25 VP1D14/GP26 P20 I/O/Z IPD 3.3V VideoPort1Data14orGPIO26 VP1D15/GP27 M20 I/O/Z IPD 3.3V VideoPort1Data15orGPIO27 VP1D16/GP28 M18 I/O/Z IPD 3.3V VideoPort1Data16orGPIO28 VP1D17/GP29 N18 I/O/Z IPD 3.3V VideoPort1Data17orGPIO29 VP1D18/GP30 M21 I/O/Z IPD 3.3V VideoPort1Data18orGPIO30 VP1D19/GP31 M19 I/O/Z IPD 3.3V VideoPort1Data19orGPIO31 VIDEOPORT2ORVLYNQ VP2CLK0 AB1 I IPU 3.3V VideoPort2Clock0(I) VP2CLK1/VCLK W1 I/O/Z IPU 3.3V VideoPort2Clock1orVLYNQClock(I/O) VP2CTL0 AA1 I/O/Z IPU 3.3V VideoPort2Control0 VP2CTL1 AB2 I/O/Z IPU 3.3V VideoPort2Control1 VP2CTL2/VSCRUN Y1 I/O/Z IPU 3.3V VideoPort2Control2orVLYNQserialclockrunrequest(I/O) VP2D02 W5 I/O/Z IPD 3.3V VideoPort2Data2 VP2D03 AA2 I/O/Z IPD 3.3V VideoPort2Data3 VP2D04 Y3 I/O/Z IPD 3.3V VideoPort2Data4 VP2D05 U6 I/O/Z IPD 3.3V VideoPort2Data5 VP2D06 Y2 I/O/Z IPD 3.3V VideoPort2Data6 VP2D07 W3 I/O/Z IPD 3.3V VideoPort2Data7 VP2D08 V5 I/O/Z IPD 3.3V VideoPort2Data8 VP2D09 W4 I/O/Z IPD 3.3V VideoPort2Data9 VP2D12/VRXD0 W2 I/O/Z IPD 3.3V VideoPort2Data12orVLYNQreceivedatapin[0](I) 26 DeviceOverview Copyright©2007–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 www.ti.com SPRS372H–MAY2007–REVISEDAPRIL2012 Table2-4.TerminalFunctions(continued) TERMINALNAME NO TYPE( INTERNAL OPER DESCRIPTION 1) PULLUP/ VOLT PULLDOWN VP2D13/VRXD1 V3 I/O/Z IPD 3.3V VideoPort2Data13orVLYNQreceivedatapin[1](I) VP2D14/VRXD2 V4 I/O/Z IPD 3.3V VideoPort2Data14orVLYNQreceivedatapin[2](I) VP2D15/VRXD3 U1 I/O/Z IPD 3.3V VideoPort2Data15orVLYNQreceivedatapin[3](I) VP2D16/VTXD0 U3 I/O/Z IPD 3.3V VideoPort2Data16orVLYNQtransmitdatapin[0](O) VP2D17/VTXD1 U2 I/O/Z IPD 3.3V VideoPort2Data17orVLYNQtransmitdatapin[1](O) VP2D18/VTXD2 U5 I/O/Z IPD 3.3V VideoPort2Data18orVLYNQtransmitdatapin[2](O) VP2D19/VTXD3 U4 I/O/Z IPD 3.3V VideoPort2Data19orVLYNQtransmitdatapin[3](O) VIDEOPORT3OREMIFA VP3CLK0/AECLKIN T1 I IPD 3.3V VideoPort3Clock0(I)orEMIFAexternalinputclock(I) VP3CLK1/ P1 I/O/Z IPD 3.3V VideoPort3Clock1orEMIFAoutputclock(O/Z) AECLKOUT VP3CTL0/ T2 I/O/Z IPU 3.3V VideoPort3Control0orAsynchronousmemorywrite AAWE/ASWE enable/Programmablesynchronousinterfacewrite-enable VP3CTL1/AR/W R1 I/O/Z IPU 3.3V VideoPort3Control1orAsynchronousmemoryread/write(O/Z) VP3CTL2/ P2 I/O/Z IPU 3.3V VideoPort3Control2orAsynchronous/Programmable AAOE/ASOE synchronousmemoryoutput-enable(O/Z) VP3D02/AED00 T6 I/O/Z IPU 3.3V VideoPort3Data2orEMIFAExternalData0 VP3D03/AED01 T5 I/O/Z IPU 3.3V VideoPort3Data3orEMIFAExternalData1 VP3D04/AED02 T4 I/O/Z IPU 3.3V VideoPort3Data4orEMIFAExternalData2 VP3D05/AED03 T3 I/O/Z IPU 3.3V VideoPort3Data5orEMIFAExternalData3 VP3D06/AED04 R6 I/O/Z IPU 3.3V VideoPort3Data6orEMIFAExternalData4 VP3D07/AED05 R5 I/O/Z IPU 3.3V VideoPort3Data7orEMIFAExternalData5 VP3D08/AED06 R4 I/O/Z IPU 3.3V VideoPort3Data8orEMIFAExternalData6 VP3D09/AED07 R3 I/O/Z IPU 3.3V VideoPort3Data9orEMIFAExternalData7 VP3D12/AED08 R2 I/O/Z IPU 3.3V VideoPort3Data12orEMIFAExternalData8 VP3D13/AED09 P6 I/O/Z IPU 3.3V VideoPort3Data13orEMIFAExternalData9 VP3D14/AED10 P5 I/O/Z IPU 3.3V VideoPort3Data14orEMIFAExternalData10 VP3D15/AED11 P4 I/O/Z IPU 3.3V VideoPort3Data15orEMIFAExternalData11 VP3D16/AED12 P3 I/O/Z IPU 3.3V VideoPort3Data16orEMIFAExternalData12 VP3D17/AED13 N4 I/O/Z IPU 3.3V VideoPort3Data17orEMIFAExternalData13 VP3D18/AED14 N6 I/O/Z IPU 3.3V VideoPort3Data18orEMIFAExternalData14 VP3D19/AED15 N5 I/O/Z IPU 3.3V VideoPort3Data19orEMIFAExternalData15 VIDEOPORT4OREMIFA VP4CLK0/AARDY L1 I IPU 3.3V VideoPort4Clock0(I)orAsynchronousmemoryreadyinput(I) VP4CLK1 K1 I/O/Z IPD 3.3V VideoPort4Clock1 VP4CTL0/ABA0 J2 I/O/Z IPD 3.3V VideoPort4Control0orEMIFAbankaddresscontrol(ABA[1:0]) (O/Z).Active-lowbankselectsforthe16-bitEMIFA.When interfacingto16-bitasynchronousdevices,ABA1carriesbit1of thebyteaddress.Foran8-bitasynchronousinterface,ABA[1:0] areusedtocarrybits1and0ofthebyteaddress. VP4CTL1/ABA1 J1 I/O/Z IPD 3.3V VideoPort4Control1orEMIFAbankaddresscontrol(ABA[1:0]) (O/Z).Active-lowbankselectsforthe16-bitEMIFA.WHEN interfacingto16-bitasynchronousdevices,ABA1carriesbit1of thebyteaddress.Foran8-bitasynchronousinterface,ABA[1:0] areusedtocarrybits1and0ofthebyteaddress. Copyright©2007–2012,TexasInstrumentsIncorporated DeviceOverview 27 SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 SPRS372H–MAY2007–REVISEDAPRIL2012 www.ti.com Table2-4.TerminalFunctions(continued) TERMINALNAME NO TYPE( INTERNAL OPER DESCRIPTION 1) PULLUP/ VOLT PULLDOWN VP4CTL2/ASADS/ K2 I/O/Z IPD 3.3V VideoPort4Control2orProgrammablesynchronousaddress ASRE strobeorread-enable.Forprogrammablesynchronousinterface, ther_enablefieldintheChipSelectxConfigurationRegister selectsbetweenASADSandASRE: –Ifr_enable=0,thentheASADS/ASREsignalfunctionsasthe ASADSsignal. –Ifr_enable=1,thentheASADS/ASREsignalfunctionsasthe ASREsignal. VP4D02/ABE00 L2 I/O/Z IPU 3.3V VideoPort4Data2orEMIFAbyte-enablecontrol0.Decoded fromthelow-orderaddressbits.Thenumberofaddressbitsor byteenablesuseddependsonthewidthofexternalmemory. Byte-writeenablesformosttypesofmemory. VP4D03/ABE01 M4 I/O/Z IPU 3.3V VideoPort4Data3orEMIFAbyte-enablecontrol1.Numberof addressbitsorbyteenablesuseddependsonthewidthof externalmemory.Byte-writeenablesformosttypesofmemory. VP4D04/AEA10 M5 I/O/Z IPU 3.3V VideoPort4Data4orEMIFAExternalAddress10(wordaddress) (O/Z) VP4D05 M6 I/O/Z IPU 3.3V VideoPort4Data5 VP4D06/ACE2 L3 I/O/Z IPU 3.3V VideoPort4Data6orEMIFAmemoryspaceenable2 VP4D07/ACE3 L4 I/O/Z IPU 3.3V VideoPort4Data7orEMIFAmemoryspaceenable3 VP4D08/AEA00 L5 I/O/Z IPD 3.3V VideoPort4Data8orEMIFAExternalAddress0(wordaddress) (O/Z) VP4D09/AEA01 K3 I/O/Z IPD 3.3V VideoPort4Data9orEMIFAExternalAddress1(wordaddress) (O/Z) VP4D12/AEA02 K4 I/O/Z IPD 3.3V VideoPort4Data12orEMIFAExternalAddress2(wordaddress) (O/Z) VP4D13/AEA03 L6 I/O/Z IPD 3.3V VideoPort4Data13orEMIFAExternalAddress3(wordaddress) (O/Z) VP4D14/AEA04 K5 I/O/Z IPD 3.3V VideoPort4Data14orEMIFAExternalAddress4(wordaddress) (O/Z) VP4D15/AEA05 J3 I/O/Z IPD 3.3V VideoPort4Data15orEMIFAExternalAddress5(wordaddress) (O/Z) VP4D16/AEA06 J4 I/O/Z IPD 3.3V VideoPort4Data16orEMIFAExternalAddress6(wordaddress) (O/Z) VP4D17/AEA07 J5 I/O/Z IPD 3.3V VideoPort4Data17orEMIFAExternalAddress7(wordaddress) (O/Z) VP4D18/AEA08 J6 I/O/Z IPD 3.3V VideoPort4Data18orEMIFAExternalAddress8(wordaddress) (O/Z) VP4D19/AEA09 K6 I/O/Z IPD 3.3V VideoPort4Data19orEMIFAExternalAddress9(wordaddress) (O/Z) EMIFA AEA23 H4 OZ IPD 3.3V EMIFAExternalAddress23(wordaddress)(O/Z) AEA19 H5 O/Z IPU 3.3V EMIFAExternalAddress19(wordaddress)(O/Z) AECLKINSEL/AEA17 G4 I/O/Z IPD 3.3V SelectEMIFAexternalclock(I)(TheEMIFAinputclockAECLKIN orSYSCLK4isselectedatresetviathepullup/pulldownresistor onthispin.Note:AECLKINisthedefaultfortheEMIFAinput clock.) orEMIFAexternaladdress17(wordaddress)(O/Z) 28 DeviceOverview Copyright©2007–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 www.ti.com SPRS372H–MAY2007–REVISEDAPRIL2012 Table2-5. TerminalFunctions(GroundandPowerSupply) TERMINAL NO TYPE(1) INTERNAL OPER DESCRIPTION NAME PULLUP/ VOLT PULLDOWN V A1 Ground SS V A5 Ground SS V A15 Ground SS V A18 Ground SS V A23 Ground SS V C4 Ground SS V D9 Ground SS V D12 Ground SS V D20 Ground SS V E6 Ground SS V E23 Ground SS V F7 Ground SS V F15 Ground SS V F17 Ground SS V F19 Ground SS V G8 Ground SS V G10 Ground SS V G12 Ground SS V G14 Ground SS V G16 Ground SS V G18 Ground SS V G22 Ground SS V H1 Ground SS V H11 Ground SS V H13 Ground SS V H15 Ground SS V H17 Ground SS V J8 Ground SS V J10 Ground SS V J12 Ground SS V J14 Ground SS V J16 Ground SS V K7 Ground SS V K9 Ground SS V K11 Ground SS V K13 Ground SS V K15 Ground SS V K17 Ground SS V L8 Ground SS V L10 Ground SS V L12 Ground SS V L14 Ground SS V L16 Ground SS V M7 Ground SS V M9 Ground SS (1) I=Input,O=Output,Z=Highimpedance,S=Supplyvoltage,GND=Ground,A=Analogsignal Copyright©2007–2012,TexasInstrumentsIncorporated DeviceOverview 29 SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 SPRS372H–MAY2007–REVISEDAPRIL2012 www.ti.com Table2-5. TerminalFunctions(GroundandPowerSupply)(continued) TERMINAL NO TYPE(1) INTERNAL OPER DESCRIPTION NAME PULLUP/ VOLT PULLDOWN V M11 Ground SS V M13 Ground SS V M15 Ground SS V M17 Ground SS V M22 Ground SS V N1 Ground SS V N8 Ground SS V N10 Ground SS V N12 Ground SS V N14 Ground SS V N16 Ground SS V P7 Ground SS V P9 Ground SS V P11 Ground SS V P13 Ground SS V P15 Ground SS V P17 Ground SS V R10 Ground SS V R12 Ground SS V R14 Ground SS V R16 Ground SS V T7 Ground SS V T9 Ground SS V T11 Ground SS V T13 Ground SS V T15 Ground SS V T17 Ground SS V T22 Ground SS V U14 Ground SS V U16 Ground SS V V1 Ground SS V V9 Ground SS V V17 Ground SS V W7 Ground SS V W22 Ground SS V Y9 Ground SS V Y10 Ground SS V AA3 Ground SS V AA8 Ground SS V AA11 Ground SS V AB5 Ground SS V AB19 Ground SS V AB23 Ground SS V AC1 Ground SS V AC8 Ground SS V AC10 Ground SS 30 DeviceOverview Copyright©2007–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 www.ti.com SPRS372H–MAY2007–REVISEDAPRIL2012 Table2-5. TerminalFunctions(GroundandPowerSupply)(continued) TERMINAL NO TYPE(1) INTERNAL OPER DESCRIPTION NAME PULLUP/ VOLT PULLDOWN V AC12 Ground SS V AC16 Ground SS POWERPINS CV J9 1.2-VCorePowerSupply DD CV J11 1.2-VCorePowerSupply DD CV J15 1.2-VCorePowerSupply DD CV K10 1.2-VCorePowerSupply DD CV K12 1.2-VCorePowerSupply DD CV K14 1.2-VCorePowerSupply DD CV L9 1.2-VCorePowerSupply DD CV L11 1.2-VCorePowerSupply DD CV L13 1.2-VCorePowerSupply DD CV L15 1.2-VCorePowerSupply DD CV M10 1.2-VCorePowerSupply DD CV M12 1.2-VCorePowerSupply DD CV M14 1.2-VCorePowerSupply DD CV N11 1.2-VCorePowerSupply DD CV N13 1.2-VCorePowerSupply DD CV N15 1.2-VCorePowerSupply DD CV P10 1.2-VCorePowerSupply DD CV P12 1.2-VCorePowerSupply DD CV P14 1.2-VCorePowerSupply DD CV R13 1.2-VCorePowerSupply DD CV N9 1.2-VCorePowerSupply DD CV T16 1.2-VCorePowerSupply DD CV R8 1.2-VCorePowerSupply DD CV R15 1.2-VCorePowerSupply DD CV V8 1.2-VCorePowerSupply DD CV R11 1.2-VCorePowerSupplyforEthernetSubsystem DDESS CV R9 1.2-VCorePowerSupplyforEthernetSubsystem DDESS AV B10 1.8-VI/Osupply DLL1 AV B22 1.8-VI/Osupply DLL2 CV H9 1.2-VPowersupplyforDDR,DDRI/Os,EMIF-DDR DD1 Subsystem CV J13 1.2-VPowersupplyforDDR,DDRI/Os,EMIF-DDR DD1 Subsystem AV V11 1.2-VSerDesAnalogsupply DDA AV W10 1.2-VSerDesAnalogsupply DDA DV T10 1.2-VSerDesDigitalSupply DDD DV U10 1.2-VSerDesDigitalSupply DDD AV AB10 1.8-VSerDesAnalogSupply(Regulator) DDR AV AB8 1.2-VSerDesAnalogSupply DDT AV U11 1.2-VSerDesAnalogSupply DDT DV E22 3.3-VI/Osupplyvoltage DD33 DV F20 3.3-VI/Osupplyvoltage DD33 DV G1 3.3-VI/Osupplyvoltage DD33 Copyright©2007–2012,TexasInstrumentsIncorporated DeviceOverview 31 SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 SPRS372H–MAY2007–REVISEDAPRIL2012 www.ti.com Table2-5. TerminalFunctions(GroundandPowerSupply)(continued) TERMINAL NO TYPE(1) INTERNAL OPER DESCRIPTION NAME PULLUP/ VOLT PULLDOWN DV G19 3.3-VI/Osupplyvoltage DD33 DV J7 3.3-VI/Osupplyvoltage DD33 DV H16 3.3-VI/Osupplyvoltage DD33 DV H22 3.3-VI/Osupplyvoltage DD33 DV J17 3.3-VI/Osupplyvoltage DD33 DV K8 3.3-VI/Osupplyvoltage DD33 DV K16 3.3-VI/Osupplyvoltage DD33 DV L7 3.3-VI/Osupplyvoltage DD33 DV L17 3.3-VI/Osupplyvoltage DD33 DV M8 3.3-VI/Osupplyvoltage DD33 DV M16 3.3-VI/Osupplyvoltage DD33 DV M23 3.3-VI/Osupplyvoltage DD33 DV N2 3.3-VI/Osupplyvoltage DD33 DV N7 3.3-VI/Osupplyvoltage DD33 DV N17 3.3-VI/Osupplyvoltage DD33 DV P8 3.3-VI/Osupplyvoltage DD33 DV P16 3.3-VI/Osupplyvoltage DD33 DV R7 3.3-VI/Osupplyvoltage DD33 DV R17 3.3-VI/Osupplyvoltage DD33 DV T8 3.3-VI/Osupplyvoltage DD33 DV T12 3.3-VI/Osupplyvoltage DD33 DV T14 3.3-VI/Osupplyvoltage DD33 DV T23 3.3-VI/Osupplyvoltage DD33 DV AB7 3.3-VI/Osupplyvoltage DD33 DV U15 3.3-VI/Osupplyvoltage DD33 DV U17 3.3-VI/Osupplyvoltage DD33 DV V2 3.3-VI/Osupplyvoltage DD33 DV V16 3.3-VI/Osupplyvoltage DD33 DV W23 3.3-VI/Osupplyvoltage DD33 DV Y4 3.3-VI/Osupplyvoltage DD33 DV Y8 3.3-VI/Osupplyvoltage DD33 DV AB16 3.3-VI/Osupplyvoltage DD33 DV AC2 3.3-VI/Osupplyvoltage DD33 DV AC5 3.3-VI/Osupplyvoltage DD33 DV AB12 3.3-VI/Osupplyvoltage DD33 DV AC19 3.3-VI/Osupplyvoltage DD33 DV AC23 3.3-VI/Osupplyvoltage DD33 DV B1 1.8-VI/Osupplyvoltage(DDR2MemoryController) DD18 DV B5 1.8-VI/Osupplyvoltage(DDR2MemoryController) DD18 DV B15 1.8-VI/Osupplyvoltage(DDR2MemoryController) DD18 DV B18 1.8-VI/Osupplyvoltage(DDR2MemoryController) DD18 DV B23 1.8-VI/Osupplyvoltage(DDR2MemoryController) DD18 DV C3 1.8-VI/Osupplyvoltage(DDR2MemoryController) DD18 DV C10 1.8-VI/Osupplyvoltage(DDR2MemoryController) DD18 DV C13 1.8-VI/Osupplyvoltage(DDR2MemoryController) DD18 DV C21 1.8-VI/Osupplyvoltage(DDR2MemoryController) DD18 32 DeviceOverview Copyright©2007–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 www.ti.com SPRS372H–MAY2007–REVISEDAPRIL2012 Table2-5. TerminalFunctions(GroundandPowerSupply)(continued) TERMINAL NO TYPE(1) INTERNAL OPER DESCRIPTION NAME PULLUP/ VOLT PULLDOWN DV E5 1.8-VI/Osupplyvoltage(DDR2MemoryController) DD18 DV F8 1.8-VI/Osupplyvoltage(DDR2MemoryController) DD18 DV F14 1.8-VI/Osupplyvoltage(DDR2MemoryController) DD18 DV F16 1.8-VI/Osupplyvoltage(DDR2MemoryController) DD18 DV F18 1.8-VI/Osupplyvoltage(DDR2MemoryController) DD18 DV G9 1.8-VI/Osupplyvoltage(DDR2MemoryController) DD18 DV G11 1.8-VI/Osupplyvoltage(DDR2MemoryController) DD18 DV G13 1.8-VI/Osupplyvoltage(DDR2MemoryController) DD18 DV G15 1.8-VI/Osupplyvoltage(DDR2MemoryController) DD18 DV G17 1.8-VI/Osupplyvoltage(DDR2MemoryController) DD18 DV H10 1.8-VI/Osupplyvoltage(DDR2MemoryController) DD18 DV H12 1.8-VI/Osupplyvoltage(DDR2MemoryController) DD18 DV H14 1.8-VI/Osupplyvoltage(DDR2MemoryController) DD18 DDR_VREF C11 (DV /2)-VreferenceforSSTLbuffer(DDR2Memory DD18 Controller0.Thisinputvoltagecnbegenerateddirectlyfrom DV usingtwo1-KΩresistorstoformaresisterdivider DD18 circuit. V L19 Die-side1.2-Vcoresupplyvoltagemonitorpin.Themonitor CCMON pinsindicatethevoltageonthedie,and,therefore,providethe bestprobepointforvoltagemonitoringpurposes.IftheV CCMON pinisnotused,itshouldbeconnecteddirectlytothe1.2-V coresupplyorleftunconnected. V B2 Die-side1.8-VI/Osupplyvoltagemonitorpin.Themonitorpins DD18MON indicatethevoltageonthedieand,therefore,providethebest probepointforvoltagemonitoringpurposes.IftheV DD18MON pinisnotused,itshouldbeconnecteddirectlytothe1.8-VI/O supply(DV ). DD18 V G21 Die-side3.3-VI/Osupplyvoltagemonitorpin.Themonitorpins DD33MON indicatethevoltageonthedieand,therefore,providethebest probepointforvoltagemonitoringpurposes.IftheV DD33MON pinisnotused,itshouldbeconnecteddirectlytothe3.3-VI/O supply(DV ). DD33 Reserved RSV1 L20 A Reserved.Unconnected RSV2 L21 A Reserved.Unconnected RSV3 D2 O Reserved.Unconnected RSV4 D1 O Reserved.Unconnected RSV5 D4 O Reserved.Unconnected RSV6 D3 O Reserved.Unconnected RSV7 H7 A Reserved.ThesepinsmustbeconnecteddirectlytoV for SS properdeviceoperation. RSV8 H8 A Reserved.ThesepinsmustbeconnecteddirectlytoV for SS properdeviceoperation. RSV9 M2 A Reserved.Unconnected RSV10 A2 A Reserved.Unconnected RSV11 E2 ReservedThispinmustbeconnecteddirectlytoV forproper SS deviceoperation. RSV12 E1 Reserved.Thispinmustbeconnecteddirectlyto1.8-VI/O supply RSV13 E4 ReservedThispinmustbeconnecteddirectlytoV forproper SS deviceoperation. RSV14 E3 Reserved.Thispinmustbeconnecteddirectlyto1.8-VI/O supply Copyright©2007–2012,TexasInstrumentsIncorporated DeviceOverview 33 SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648

TMS320DM647 TMS320DM648 SPRS372H–MAY2007–REVISEDAPRIL2012 www.ti.com Table2-5. TerminalFunctions(GroundandPowerSupply)(continued) TERMINAL NO TYPE(1) INTERNAL OPER DESCRIPTION NAME PULLUP/ VOLT PULLDOWN RSV15 A10 A Reserved.Unconnected RSV16 A22 A Reserved.Unconnected RSV17 V10 A Reserved.Unconnected RSV18 F6 I Reserved.Thesepinsmustbeconnecteddirectlyto1.8-VI/O supply(DV )forproperdeviceoperation. DD18 RSV19 C2 Reserved.Thispinmustbeconnectedtothe1.8-VI/Osupply (DV )viaa200-Ωresistorforproperdeviceoperation. DD18 NOTE:IftheDDR2MemoryControllerisnotused,the DDR_VREF,RSV19,andRSV20pinscanbedirectly connectedtoground(V )tosavepower.However, SS connectingthesepinsdirectlytogroundwillpreventboundary scanfromfunctioningontheDDR2MemoryControllerpins.To preserveboundary-scanfunctionalityontheDDR2Memory Controllerpins,seeSection6.3.6. RSV20 C1 Reserved.Thispinmustbeconnectedtoground(V )viaa SS 200-Ωresistorforproperdeviceoperation. NOTE:IftheDDR2MemoryControllerisnotused,theRSV19 andRSV20pinscanbedirectlyconnectedtoground(V )to SS savepower.However,connectingthesepinsdirectlytoground willpreventboundaryscanfromfunctioningontheDDR2 MemoryControllerpins.Topreserveboundary-scan functionalityontheDDR2MemoryControllerpins,see Section6.3.6. RSV21 Y12 Reserved.Thispinmustbeconnectedviaa20-Ωresistor directlyto3.3-VI/OSupply(DV )forproperdevice DD33 operation.Theresistorusedshouldhaveaminimalratingof 250mW. RSV22 W12 Reserved.Thispinmustbeconnectedviaa40-Ωresistor directlytoground(V )forproperdeviceoperation.The SS resistorusedshouldhaveaminimalratingof100mW. 2.7 Device Support 2.7.1 Development Support TI offers an extensive line of development tools for the TMS320DM64x DMP platform, including tools to evaluate the performance of the processors, generate code, develop algorithm implementations, and fully integrate and debug software and hardware modules. The tools support documentation is electronically availablewithintheCodeComposerStudio™IntegratedDevelopmentEnvironment(IDE). ThefollowingproductssupportdevelopmentofTMS320DM64xxDMP-basedapplications: SoftwareDevelopmentTools: CodeComposerStudio™IntegratedDevelopmentEnvironment(IDE):includingEditor C/C++/AssemblyCodeGeneration,andDebugplusadditionaldevelopmenttools Scalable, Real-Time Foundation Software (DSP/BIOS™), which provides the basic run-time target softwareneededtosupportanySoCapplication. HardwareDevelopmentTools: Extended Development System (XDS™) Emulator (supports TMS320DM64x multiprocessor system debug)EVM(EvaluationModule) For a complete listing of development-support tools for the TMS320DM64x platform, visit the Texas Instruments website at www.ti.com. For information on pricing and availability, contact the nearest TI fieldsalesofficeorauthorizeddistributor. 34 DeviceOverview Copyright©2007–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):TMS320DM647TMS320DM648