- 型号: TLV320AIC3106IRGZR

- 制造商: Texas Instruments

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

TLV320AIC3106IRGZR产品简介:

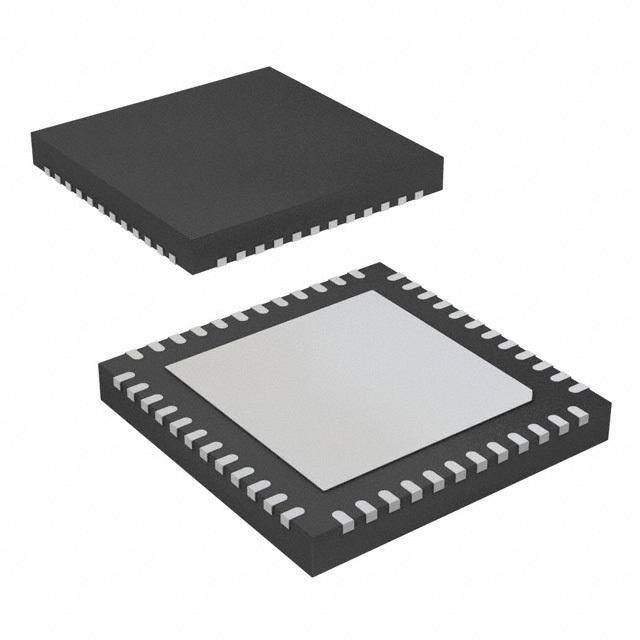

ICGOO电子元器件商城为您提供TLV320AIC3106IRGZR由Texas Instruments设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 TLV320AIC3106IRGZR价格参考。Texas InstrumentsTLV320AIC3106IRGZR封装/规格:接口 - 编解码器, Stereo Audio Interface 24 b PCM Audio Interface 48-VQFN (7x7)。您可以下载TLV320AIC3106IRGZR参考资料、Datasheet数据手册功能说明书,资料中有TLV320AIC3106IRGZR 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| ADC/DAC数 | 2 / 2 |

| 产品目录 | 集成电路 (IC) |

| 描述 | IC STER AUD CODEC 32 BIT 48-VQFN |

| 产品分类 | |

| 品牌 | Texas Instruments |

| 数据手册 | |

| 产品图片 |

|

| 产品型号 | TLV320AIC3106IRGZR |

| PCN设计/规格 | |

| rohs | 无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | - |

| 三角积分 | 是 |

| 产品目录页面 | |

| 供应商器件封装 | 48-VQFN(7x7) |

| 信噪比,ADC/DAC(db)(典型值) | 92 / 102 |

| 其它名称 | 296-22705-1 |

| 分辨率(位) | 24 b |

| 动态范围,ADC/DAC(db)(典型值) | 91 / 92 |

| 包装 | 剪切带 (CT) |

| 安装类型 | 表面贴装 |

| 封装/外壳 | 48-VFQFN 裸露焊盘 |

| 工作温度 | -40°C ~ 85°C |

| 数据接口 | PCM 音频接口 |

| 标准包装 | 1 |

| 电压-电源,数字 | 1.65 V ~ 1.95 V |

| 电压-电源,模拟 | 2.7 V ~ 3.6 V |

| 类型 | 立体声音频 |

| 配用 | /product-detail/zh/TLV320AIC3106EVM-K/296-31035-ND/1906858 |

_renders/CS4265-CNZR.jpg)

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

Product Sample & Technical Tools & Support & Folder Buy Documents Software Community TLV320AIC3106 SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 TLV320AIC3106 Low-Power Stereo Audio CODEC for Portable Audio/Telephony 1 Features • ConcurrentDigitalMicrophoneandAnalog MicrophoneSupportAvailable • StereoAudioDAC 1 • ExtensiveModularPowerControl – 102-dBASignal-to-NoiseRatio • PowerSupplies: – 16/20/24/32-BitData – Analog:2.7V–3.6V. – SupportsRatesFrom8kHzto96kHz – DigitalCore:1.65V–1.95V – 3D/Bass/Treble/EQ/De-EmphasisEffects – DigitalI/O:1.1V–3.6V – FlexiblePowerSavingModesand Packages:5.00mm ×5.00mm80-pinVFBGA; PerformanceareAvailable 7.00mm×7.00mm48-pinQFN • StereoAudioADC – 92-dBASignal-to-NoiseRatio 2 Applications – SupportsRatesFrom8kHzto96kHz • DigitalCameras – DigitalSignalProcessingandNoiseFiltering • SmartCellularPhones AvailableDuringRecord • TenAudioInputPins 3 Description – ProgrammableinSingle-EndedorFully The TLV320AIC3106 is a low-power stereo audio DifferentialConfigurations codec with stereo headphone amplifier, as well as multiple inputs and outputs programmable in single- – 3-StateCapabilityforFloatingInput ended or fully differential configurations. Extensive Configurations register-based power control is included, enabling • SevenAudioOutputDrivers stereo 48-kHz DAC playback as low as 15 mW from – StereoFullyDifferentialorSingle-Ended a 3.3-V analog supply, making it ideal for portable HeadphoneDrivers battery-poweredaudioandtelephonyapplications. – FullyDifferentialStereoLineOutputs The record path of the TLV320AIC3106 contains – FullyDifferentialMonoOutput integrated microphone bias, digitally controlled stereo microphone preamplifier, and automatic gain control • LowPower:15-mWStereo48-kHzPlaybackWith (AGC), with mix/mux capability among the multiple 3.3-VAnalogSupply analog inputs. Programmable filters are available • Ultralow-PowerModewithPassiveAnalogBypass during record which can remove audible noise that • ProgrammableInput/OutputAnalogGains canoccurduringopticalzoomingindigitalcameras. • AutomaticGainControl(AGC)forRecord DeviceInformation(1) • ProgrammableMicrophoneBiasLevel PARTNUMBER PACKAGE BODYSIZE(NOM) • ProgrammablePLLforFlexibleClockGeneration BGAMICROSTAR • ControlBusSelectableSPIorI2C TLV320AIC3106 JUNIOR(80) 5.00mmx5.00mm • AudioSerialDataBusSupportsI2S,Left/Right- VQFN(48) 7.00mmx7.00mm Justified,DSP,andTDMModes (1) For all available packages, see the orderable addendum at • AlternateSerialPCM/I2SDataBusforEasy theendofthedatasheet. ConnectiontoBluetooth™Module 4 Simplified Diagram 1 An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectualpropertymattersandotherimportantdisclaimers.PRODUCTIONDATA.

TLV320AIC3106 SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 www.ti.com Table of Contents 1 Features.................................................................. 1 11.2 FunctionalBlockDiagram.....................................16 2 Applications........................................................... 1 11.3 FeatureDescription...............................................16 3 Description............................................................. 1 11.4 DeviceFunctionalModes......................................39 11.5 Programming.........................................................42 4 SimplifiedDiagram................................................ 1 11.6 RegisterMaps.......................................................46 5 RevisionHistory..................................................... 2 11.7 OutputStageVolumeControls.............................64 6 Description(continued)......................................... 3 12 ApplicationandImplementation........................ 91 7 DeviceComparisonTable..................................... 3 12.1 ApplicationInformation..........................................91 8 PinConfigurationandFunctions......................... 4 12.2 TypicalApplication ...............................................91 9 Specifications......................................................... 6 13 PowerSupplyRecommendations..................... 93 9.1 AbsoluteMaximumRatings......................................6 14 Layout................................................................... 94 9.2 ESDRatings..............................................................6 14.1 LayoutGuidelines.................................................94 9.3 RecommendedOperatingConditions.......................6 14.2 LayoutExample....................................................94 9.4 ThermalInformation..................................................7 15 DeviceandDocumentationSupport................. 96 9.5 ElectricalCharacteristics...........................................7 15.1 Trademarks...........................................................96 9.6 TimingRequirements:AudioDataSerialInterface.10 15.2 ElectrostaticDischargeCaution............................96 9.7 TypicalCharacteristics............................................13 15.3 Glossary................................................................96 10 ParameterMeasurementInformation................14 16 Mechanical,Packaging,andOrderable 11 DetailedDescription........................................... 15 Information........................................................... 96 11.1 Overview...............................................................15 5 Revision History ChangesfromRevisionE(December2008)toRevisionF Page • AddedESDRatingstable,FeatureDescriptionsection,DeviceFunctionalModes,ApplicationandImplementation section,PowerSupplyRecommendationssection,Layoutsection,andDeviceandDocumentationSupport ....................1 2 SubmitDocumentationFeedback Copyright©2006–2014,TexasInstrumentsIncorporated ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 www.ti.com SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 6 Description (continued) The playback path includes mix/mux capability from the stereo DAC and selected inputs, through programmable volumecontrols,tothevariousoutputs. The TLV320AIC3106 contains four high-power output drivers as well as three fully differential output drivers. The high-power output drivers are capable of driving a variety of load configurations, including up to four channels of single-ended 16-Ω headphones using ac-coupling capacitors, or stereo 16-Ω headphones in a capacitorless outputconfiguration. The stereo audio DAC supports sampling rates from 8 kHz to 96 kHz and includes programmable digital filtering in the DAC path for 3D, bass, treble, midrange effects, speaker equalization, and de-emphasis for 32-kHz, 44.1- kHz, and 48-kHz rates. The stereo audio ADC supports sampling rates from 8 kHz to 96 kHz and is preceded by programmable gain amplifiers or AGC that can provide up to 59.5-dB analog gain for low-level microphone inputs. The TLV320AIC3106 provides an extremely high range of programmability for both attack (8 ms–1,408 ms) and for decay (0.05 s–22.4 s). This extended AGC range allows the AGC to be tuned for many types of applications. For battery saving applications where neither analog nor digital signal processing are required, the device can be putinaspecialanalogsignalpassthrumode.Thismodesignificantlyreducespowerconsumption,asmostofthe deviceispowereddownduringthispassthroughoperation. The serial control bus supports SPI or I2C protocols, while the serial audio data bus is programmable for I2S, left/right-justified, DSP, or TDM modes. A highly programmable PLL is included for flexible clock generation and supportforallstandardaudioratesfromawiderangeofavailableMCLKs,varyingfrom512kHzto50MHz,with special attention paid to the most popular cases of 12-MHz, 13-MHz, 16-MHz, 19.2-MHz, and 19.68-MHz system clocks. The TLV320AIC3106 operates from an analog supply of 2.7 V–3.6 V, a digital core supply of 1.65 V–1.95 V, and a digital I/O supply of 1.1 V–3.6 V. The device is available in the 5-mm × 5-mm, 80-ball MicroStar Junior™ BGA packageanda7-mm× 7-mm,48-leadQFNpackage. 7 Device Comparison Table DEVICENAME DESCRIPTION TLV320AIC3106 Low-PowerStereoCODECwith10Inputs,7Outputs,Speaker/HPAmpandEnhancedDigitalEffects. TLV320AIC3101 SameasTLV320AIC3106,butwith6inputs,6outputsandSpeaker/HPAmp. TLV320AIC3104 SameasTLV320AIC3106,butwith6inputsand6outputs. TLV320AIC3105 SameasTLV320AIC3106,butwith6Single-endedinputsand6outputs. TLV320AIC3107 SameasTLV320AIC3106,butwith7Inputs,6OutputsandIntegratedMonoClass-DAmplifier. Copyright©2006–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 3 ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 www.ti.com 8 Pin Configuration and Functions RGZ48-PinPackage (BottomView) ZQE80-BallPackage (BottomView) 1 1 2 J 4 8 1 3 H G F E D C B A 3 7 2 4 1 2 3 4 5 6 7 8 9 3 6 2 5 Theshadedballsarenotconnectedtothe SoldertheQFNthermalpadtotheground die,butareelectricallyconnectedtoeach plane(DRVSS). other.Isrecommendedtosolderthemto analoggroundinordertoenhancethe thermalperformanceofthedevice. PinFunctions PIN I/O DESCRIPTION NAME QFN BGABALL MICBIAS 13 A2 O Microphonebiasvoltageoutput MIC3R 14 A1 I MIC3input(rightormultifunction) AVSS_ADC 15 C2,D2 – AnalogADCgroundsupply,0V DRVDD 16,17 B1,C1 – ADCanalogandoutputdrivervoltagesupply,2.7V–3.6V HPLOUT 18 D1 O High-poweroutputdriver(left+) HPLCOM 19 E1 O High-poweroutputdriver(left–ormultifunctional) DRVSS 20,21 E2,F2 – Analogoutputdrivergroundsupply,0V HPRCOM 22 F1 O High-poweroutputdriver(right–ormultifunctional) HPROUT 23 G1 O High-poweroutputdriver(right+) DRVDD 24 H1 – ADCanalogandoutputdrivervoltagesupply,2.7V–3.6V AVDD_DAC 25 J1 – AnalogDACvoltagesupply,2.7V–3.6V AVSS_DAC 26 G2,H2 – AnalogDACgroundsupply,0V MONO_LOP 27 J2 O Monolineoutput(+) MONO_LOM 28 J3 O Monolineoutput(–) LEFT_LOP 29 J4 O Leftlineoutput(+) LEFT_LOM 30 J5 O Leftlineoutput(–) RIGHT_LOP 31 J6 O Rightlineoutput(+) RIGHT_LOM 32 J7 O Rightlineoutput(–) RESET 33 H8 I Reset General-purposeinput/output#2(input/output)/digitalmicrophonedatainput/PLLclock GPIO2 34 J8 I/O input/audioserialdatabusbitclockinput/output 4 SubmitDocumentationFeedback Copyright©2006–2014,TexasInstrumentsIncorporated ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 www.ti.com SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 PinFunctions(continued) PIN I/O DESCRIPTION NAME QFN BGABALL General-purposeinput/output#1(input/output)/PLL/clockmuxoutput/shortcircuit GPIO1 35 J9 I/O interrupt/AGCnoiseflag/digitalmicrophoneclockaudioserialdatabuswordclock input/output DVDD 36 H9 – Digitalcorevoltagesupply,1.65V–1.95V MCLK 37 G8 I Masterclockinput BCLK 38 G9 I Audioserialdatabusbitclock(input/output) WCLK 39 F9 I Audioserialdatabuswordclock(input/output) DIN 40 E9 I Audioserialdatabusdatainput(input) DOUT 41 F8 O Audioserialdatabusdataoutput(output) DVSS 42 D9 – Digitalcore/I/Ogroundsupply,0V SELECT 43 E8 I Controlmodeselectpin(1=SPI,0=I2C) IOVDD 44 C9 – I/Ovoltagesupply,1.1V–3.6V MFP0 45 B8 I Multifunctionpin#0–SPIchipselect/GPI/I2Caddresspin#0 MFP1 46 B9 I Multifunctionpin#1–SPIserialclock/GPI/I2Caddresspin#1S MFP2 47 A8 I Multifunctionpin#2–SPIMISOslaveserialdataoutput/GPOI Multifunctionpin#3–SPIMOSIslaveserialdatainput/GPI/audioserialdatabusdata MFP3 48 A9 I input SCL 1 C8 I/O I2Cserialclock/GPIO SDA 2 D8 I/O I2Cserialdatainput/output/GPIO NC – A7 – Notconnected LINE1LP 3 A6 I MIC1orLine1analoginput(left+ormultifunction) LINE1LM 4 A5 I MIC1orLine1analoginput(left–ormultifunction) LINE1RP 5 B7 I MIC1orLine1analoginput(right+ormultifunction) LINE1RM 6 B6 I MIC1orLine1analoginput(right–ormultifunction) LINE2LP 7 A4 I MIC2orLine2analoginput(left+ormultifunction) LINE2LM 8 B5 I MIC2orLine2analoginput(left–ormultifunction) LINE2RP 9 B4 I MIC2orLine2analoginput(right+ormultifunction) LINE2RM 10 A3 I MIC2orLine2analoginput(right–ormultifunction) MIC3L 11 B3 I MIC3input(leftormultifunction) MICDET 12 B2 I Microphonedetect C4-C7, D3-D7, E3-E7, NC – – Notconnected F3-F7, G3-G7, H3-H7 Copyright©2006–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 5 ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 www.ti.com 9 Specifications 9.1 Absolute Maximum Ratings overoperatingfree-airtemperaturerange(unlessotherwisenoted)(1) (2) MIN MAX. UNIT AVDD_DACtoAVSS_DAC,DRVDDtoDRVSS, –0.3 3.9 V AVSS_ADC AVDDtoDRVSS –0.3 3.9 V Inputvoltage IOVDDtoDVSS –0.3 3.9 V DVDDtoDVSS –0.3 2.5 V AVDD_DACtoDRVDD –0.1 0.1 V Digitalinputvoltage toDVSS –0.3 IOVDD+0.3 V Analoginputvoltage toAVSS_ADC –0.3 AVDD+0.3 V Operatingtemperature –40 t85 °C Junctiontemperature,T 105 °C J Storagetemperature,T –65 105 °C stg Powerdissipation (T Max–T )/θ J A JA (1) Stressesbeyondthoselistedunderabsolutemaximumratingsmaycausepermanentdamagetothedevice.Thesearestressratings only,andfunctionaloperationofthedeviceattheseoranyotherconditionsbeyondthoseindicatedunderrecommendedoperating conditionsisnotimplied.Exposuretoabsolute-maximum-ratedconditionsforextendedperiodsmayaffectdevicereliability. (2) ESDcomplicancetestedtoEIA/JESD22-A114-Bandpassed. 9.2 ESD Ratings VALUE UNIT Human-bodymodel(HBM),perANSI/ESDA/JEDECJS-001(1) ±1900 V(ESD) Electrostaticdischarge Charged-devicemodel(CDM),perJEDECspecificationJESD22- V C101(2) ±1500 (1) JEDECdocumentJEP155statesthat500-VHBMallowssafemanufacturingwithastandardESDcontrolprocess. (2) JEDECdocumentJEP157statesthat250-VCDMallowssafemanufacturingwithastandardESDcontrolprocess. 9.3 Recommended Operating Conditions overoperatingfree-airtemperaturerange(unlessotherwisenoted) MIN NOM MAX UNIT AVDD_DAC,DRVDD(1) Analogsupplyvoltage 2.7 3.3 3.6 V DVDD(1) Digitalcoresupplyvoltage 1.65 1.8 1.95 V IOVDD(1) DigitalI/Osupplyvoltage 1.1 1.8 3.6 V V Analogfull-scale0-dBinputvoltage(DRVDD1=3.3V) 0.707 V I RMS Stereolineoutputloadresistance 10 kΩ Stereoheadphoneoutputloadresistance 16 Ω Digitaloutputloadcapacitance 10 pF T Operatingfree-airtemperature –40 85 °C A (1) AnalogvoltagevaluesarewithrespecttoAVSS_ADC,AVSS_DAC,DRVSS;digitalvoltagevaluesarewithrespecttoDVSS. 6 SubmitDocumentationFeedback Copyright©2006–2014,TexasInstrumentsIncorporated ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 www.ti.com SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 9.4 Thermal Information RGZ ZQE THERMALMETRIC(1) UNIT 48PINS 80PINS R Junction-to-ambientthermalresistance 26.1 54.3 θJA R Junction-to-case(top)thermalresistance 12.7 25.7 θJC(top) R Junction-to-boardthermalresistance 3.9 31.8 θJB °C/W ψ Junction-to-topcharacterizationparameter 0.2 0.5 JT ψ Junction-to-boardcharacterizationparameter 3.4 31.8 JB R Junction-to-case(bottom)thermalresistance 0.4 N/A θJC(bot) (1) Formoreinformationabouttraditionalandnewthermalmetrics,seetheICPackageThermalMetricsapplicationreport,SPRA953. 9.5 Electrical Characteristics At25°C,AVDD_DAC,DRVDD,IOVDD=3.3V,DVDD=1.8V,f =48-kHz,16-bitaudiodata(unlessotherwisenoted) S PARAMETER TESTCONDITIONS MIN TYP MAX UNIT AUDIOADC Inputsignallevel(0-dB) Single-endedinput 0.707 VRMS Signal-to-noiseratio,A-weighted(1)(2) fS=48ksps,0-dBPGAgain,inputsac-shortedtoground 80 92 dB Dynamicrange(2) fS=48ksps,0-dBPGAgain,–60dBfull-scaleinputsignal 91 dB THD Totalharmonicdistortion fS=48ksps,0-dBPGAgain,–2dBfull-scale,1-kHzinputsignal –88 –70 dB 217-HzsignalappliedtoDRVDD 49 PSRR Powersupplyrejectionratio dB 1-kHzsignalappliedtoDRVDD 46 Gainerror fS=48ksps,0-dBPGAgain,–2dBfull-scale,1-kHzinputsignal 0.84 dB 1-kHz,–2-dBfull-scalesignal,MIC3LtoMIC3R –86 Inputchannelseparation 1-kHz,–2-dBfull-scalesignal,MIC2LtoMIC2R –98 dB 1-kHz,–2-dBfull-scalesignal,MIC1LtoMIC1R –75 ADCprogrammablegainamplifier 1-kHzinputtone 59.5 dB maximumgain ADCprogrammablegainamplifierstep 0.5 dB size MIC1L/MIC1RinputsroutedtosingleADC 20 Inputmixattenuation=0dB MIC1L/MIC1RinputsroutedtosingleADC,inputmixattenuation=12dB 80 MIC2L/MIC2RinputsroutedtosingleADC 20 Inputresistance Inputmixattenuation=0dB kΩ MIC2L/MIC2RinputsroutedtosingleADC,inputmixattenuation=12dB 80 MIC3L/MIC3RinputsroutedtosingleADC 20 Inputmixattenuation=0dB MIC3L/MIC3RinputsroutedtosingleADC,inputmixattenuation=12dB 80 Inputlevelcontrolminimumattenuation 0 dB setting Inputlevelcontrolmaximumattenuation 12 dB setting Inputsignallevel DifferentialInput 1.414 VRMS Signal-to-noiseratio,A-weighted(1)(2) fS=48ksps,0-dBPGAgain,inputsac-shortedtoground, 92 dB differentialmode THD Totalharmonicdistortion fS=48ksps,0-dBPGAgain,–2-dBfull-scale1-kHzinputsignal,differential –91 dB mode (1) Ratioofoutputlevelwith1-kHzfull-scalesine-waveinput,totheoutputlevelwiththeinputsshortcircuited,measuredA-weightedovera 20-Hzto20-kHzbandwidthusinganaudioanalyzer. (2) Allperformancemeasurementsdonewith20-kHzlow-passfilterand,wherenoted,A-weightedfilter.Failuretousesuchafiltermay resultinhigherTHD+NandlowerSNRanddynamicrangereadingsthanshownintheElectricalCharacteristics.Thelow-passfilter removesout-of-bandnoise,which,althoughnotaudible,mayaffectdynamicspecificationvalues. Copyright©2006–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 7 ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 www.ti.com Electrical Characteristics (continued) At25°C,AVDD_DAC,DRVDD,IOVDD=3.3V,DVDD=1.8V,f =48-kHz,16-bitaudiodata(unlessotherwisenoted) S PARAMETER TESTCONDITIONS MIN TYP MAX UNIT ANALOGPASSTHROUGHMODE MIC1/LINE1toLINE_OUT 330 Inputtooutputswitchresistance,(rdsON) MIC2/LINE2toLINE_OUT 330 Ω ADCDIGITALDECIMATIONFILTER,fS=48kHz Filtergainfrom0to0.39fS ±0.1 dB Filtergainat0.4125fS –0.25 dB Filtergainat0.45fS –3 dB Filtergainat0.5fS –17.5 dB Filtergainfrom0.55fSto64fS –75 dB Filtergroupdelay 17/fS s MICROPHONEBIAS Programmablesetting=2.0 2.0 Biasvoltage Programmablesetting=2.5 2.3 2.5 2.7 V Programmablesetting=DRVDD DRVDD Currentsourcing Programmablesetting=2.5V 4 mA AUDIODAC–DifferentialLineoutput,load=10kΩ 0-dBinputfull-scalesignal,outputvolumecontrol=0dB,outputcommon- Full-scaleoutputvoltage modesetting=1.35V 1.414 VRMS SNR Signal-to-noiseratio,A-weighted(3) Noinputsignal,outputvolumecontrol=0dB,outputcommonmode 90 102 dB setting=1.35V,fS=48kHz –60dB1-kHzinputfull-scalesignal,outputvolumecontrol=0dB,output Dynamicrange,A-weighted 99 dB common-modesetting=1.35V,fS=48kHz 0-dB1-kHzinputfull-scalesignal,outputvolumecontrol=0dB,output THD Totalharmonicdistortion –94 –75 dB common-modesetting=1.35V,fS=48kHz 217-HzsignalappliedtoDRVDD,AVDD_DAC 77 Power-supplyrejectionratio dB 1-kHzsignalappliedtoDRVDD,AVDD_DAC 73 DACchannelseparation 0-dBfull-scaleinputsignalbetweenleftandrightLineout 123 dB 0-dB1-kHzinputfull-scalesignal,outputvolumecontrol=0dB,output DACgainerror –0.4 dB common-modesetting=1.35V,fS=48kHz AUDIODAC–SINGLEENDEDLINEOUTPUT,Load=10kΩ 0-dBinputfull-scalesignal,outputvolumecontrol=0dB,outputcommon- Full-scaleoutputvoltage modesetting=1.35V 0.707 VRMS Noinputsignal,outputvolumecontrol=0dB,outputcommon-mode SNR Signal-to-noiseratio,A-weighted 97 dB setting=1.35V,fS=48kHz 0-dB1-kHzinputfull-scalesignal,outputvolumecontrol=0dB,output THD Totalharmonicdistortion 84 dB common-modesetting=1.35V,fS=48kHz 0-dB1-kHzinputfull-scalesignal,outputvolumecontrol=0dB,output DACgainerror 0.55 dB common-modesetting=1.35V,fS=48kHz AUDIODAC–SINGLEENDEDHEADPHONEOUTPUT,Load=16Ω 0-dBinputfull-scalesignal,outputvolumecontrol=0dB,outputcommon- Full-scaleoutputvoltage modesetting=1.35V 0.707 VRMS Noinputsignal,outputvolumecontrol=0dB,outputcommon-mode 95 dB SNR Signal-to-noiseratio,A-weighted setting=1.35V,fS=48kHz Noinputsignal,outputvolumecontrol=0dB,outputcommon-mode 96 dB setting=1.35V,fS=48kHz,50%DACcurrentboostmode –60-dB1-kHzinputfull-scalesignal,outputvolumecontrol=0dB,output Dynamicrange,A-weighted 92 dB common-modesetting=1.35V,fS=48kHz 0-dB1-kHzinputfull-scalesignal,outputvolumecontrol=0dB,output THD Totalharmonicdistortion –80 –65 dB common-modesetting=1.35V,fS=48kHz 217-HzsignalappliedtoDRVDD,AVDD_DAC 41 PSRR Power-supplyrejectionratio dB 1-kHzsignalappliedtoDRVDD,AVDD_DAC 44 DACchannelseparation 0-dBfull-scaleinputsignalbetweenleftandrightLineout 84 dB 0-dB1-kHzinputfull-scalesignal,outputvolumecontrol=0dB,output DACgainerror –0.5 dB common-modesetting=1.35V,fS=48kHz (3) Unlessotherwisenoted,allmeasurementsuseoutputcommon-modevoltagesettingof1.35V,0-dBoutputlevelcontrolgain,16-Ω single-endedload. 8 SubmitDocumentationFeedback Copyright©2006–2014,TexasInstrumentsIncorporated ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 www.ti.com SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 Electrical Characteristics (continued) At25°C,AVDD_DAC,DRVDD,IOVDD=3.3V,DVDD=1.8V,f =48-kHz,16-bitaudiodata(unlessotherwisenoted) S PARAMETER TESTCONDITIONS MIN TYP MAX UNIT AUDIODAC–LINEOUTANDHEADPHONEOUTDRIVERS Firstoption 1.35 Secondoption 1.5 Outputcommonmode V Thirdoption 1.65 Fourthoption 1.8 Outputvolumecontrolmaxsetting 9 dB Outputvolumecontrolstepsize 1 dB DACDIGITALINTERPOLATION–FILTERfS=48ksps Passband 0 0.45fS Hz Pass-bandripple ±0.06 dB Transitionband 0.45fS 0.55fS Hz Stopband 0.55fS 7.5fS Hz Stop-bandattenuation 65 dB Groupdelay 21/fS s DIGITALI/O VIL Inputlowlevel –0.3 0.3×IOVDD V 0.7× IOVDD>1.6V VIH Inputhighlevel(4) IOVDD V IOVDD<1.6V 1.1 VOL Outputlowlevel 0.1×IOVDD V 0.8× VOH Outputhighlevel IOVDD V POWERCONSUMPTION,DRVDD,AVDD_DAC=3.3V,DVDD=1.8V,IOVDD=3.3V IDRVDD+IAVDD_DAC 0.1 RESETheldlow μA IDVDD 0.2 IDRVDD+IAVDD_DAC 2.1 mA IDVDD MonoADCrecord,fS=8ksps,I2Sslave,AGC 0.5 IDRVDD+IAVDD_DAC off,nosignal 4.1 mA IDVDD 0.6 IDRVDD+IAVDD_DAC StereoADCrecord,fS=48ksps,I2Sslave, 4.3 mA IDVDD AGCoff,nosignal 2.5 IDRVDD+IAVDD_DAC StereoDACplaybacktoLineout,analogmixer 3.5 mA IDVDD bypassed,fS=48ksps,I2Sslave 2.3 IDRVDD+IAVDD_DAC StereoDACplaybacktoLineout,fS=48ksps, 4.9 mA IDVDD I2Sslave,nosignal 2.3 IDRVDD+IAVDD_DAC StereoDACplaybacktostereosingle-ended 6.7 mA IDVDD headphone,fS=48ksps,I2Sslave,nosignal 2.3 IDRVDD+IAVDD_DAC 3.1 StereoLineintostereoLineout,nosignal mA IDVDD 0 IDRVDD+IAVDD_DAC 1.4 ExtrapowerwhenPLLenabled mA IDVDD 0.9 IDRVDD+IAVDD_DAC Allblockspowereddown,headsetdetedtion 28 μA IDVDD enabled 2 (4) WhenIOVDD<1.6V,minimumV is1.1V. IH Copyright©2006–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 9 ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 www.ti.com 9.6 Timing Requirements: Audio Data Serial Interface(1) IOVDD=1.1V IOVDD=3.3V PARAMETER UNIT MIN MAX MIN MAX I2S/LJF/RJFTiminginMasterMode t (WS) ADWS/WCLKdelaytime 50 15 ns d t (DO-WS) ADWS/WCLKtoDOUTdelaytime 50 20 ns d t (DO-BCLK) BCLKtoDOUTdelaytime 50 15 ns d t(DI) DINsetuptime 10 6 ns s t (DI) DINholdtime 10 6 ns h t Risetime 30 10 ns r t Falltime 30 10 ns f DSPTiminginMasterMode t (WS) ADWS/WCLKdelaytime 50 15 ns d t (DO-BCLK) BCLKtoDOUTdelaytime 50 15 ns d t(DI) DINsetuptime 10 6 ns s t (DI) DINholdtime 10 6 ns h t Risetime 30 10 ns r t Falltime 30 10 ns f I2S/LJF/RJFTiminginSlaveMode t (BCLK) BCLKhighperiod 70 35 ns H t (BCLK) BCLKlowperiod 70 35 ns L t(WS) ADWS/WCLKsetuptime 10 6 ns s t (WS) ADWS/WCLKholdtime 10 6 ns h t (DO-WS) ADWS/WCLKtoDOUTdelaytime(forLJFModeonly) 50 35 ns d t (DO-BCLK) BCLKtoDOUTdelaytime 50 20 ns d t(DI) DINsetuptime 10 6 ns s t (DI) DINholdtime 10 6 ns h t Risetime 8 4 ns r t Falltime 8 4 ns f DSPTiminginSlaveMode t (BCLK) BCLKhighperiod 70 35 ns H t (BCLK) BCLKlowperiod 70 35 ns L t(WS) ADWS/WCLKsetuptime 10 8 ns s t (WS) ADWS/WCLKholdtime 10 8 ns h t (DO-BCLK) BCLKtoDOUTdelaytime 50 20 ns d t(DI) DINsetuptime 10 6 ns s t (DI) DINholdtime 10 6 ns h t Risetime 8 4 ns r t Falltime 8 4 ns f (1) Alltimingspecificationsaremeasuredatcharacterizationbutnottestedatfinaltest. 10 SubmitDocumentationFeedback Copyright©2006–2014,TexasInstrumentsIncorporated ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 www.ti.com SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 WCLK t(WS) d BCLK t(DO-WS) t(DO-BCLK) d d SDOUT t (DI) t(DI) S h SDIN T0145-01 Allspecificationsat25°C,DVDD=1.8V. Figure1. I2S/LJF/RJFTiminginMasterMode WCLK t(WS) t(WS) d d BCLK t(DO-BCLK) d SDOUT t (DI) t(DI) S h SDIN T0146-01 Figure2. DSPTiminginMasterMode Copyright©2006–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 11 ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 www.ti.com WCLK t (WS) S t(WS) h t (BCLK) H BCLK t(BCLK) t(DO-WS) L d t(DO-BCLK) d SDOUT t (DI) t(DI) S h SDIN T0145-02 Figure3. I2S/LJF/RJFTiminginSlaveMode WCLK t (WS) t (WS) S S t(WS) t(WS) h h t(BCLK) L BCLK t (BCLK) t(DO-BCLK) H d SDOUT t (DI) t(DI) S h SDIN T0146-02 Figure4. DSPTiminginSlaveMode 12 SubmitDocumentationFeedback Copyright©2006–2014,TexasInstrumentsIncorporated ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 www.ti.com SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 9.7 Typical Characteristics 0 45 2.7 VDD_CM 1.35_LDAC -10 40 B 3.6 VDD_CM 1.8_LDAC stortion - d --3200 23.7.3 V DVDD_DC_MCM 11.3.655__RLDDAACC Noise - dB 3305 c Di -40 To- 25 moni -50 3.3 VDD_CM 1.65_RDAC gnal- 20 ar Si al H -60 R - 15 Tot SN HD - -70 10 LINEIR Routed to RADC in Differential Mode, T 48 KSPS, Normal Supply and Temperature, -80 3.6 VDD_CM 1.8_RDAC 5 Input Signal at -65 dB -90 0 0 20 40 60 80 100 0 10 20 30 40 50 60 70 Headphone Out Power - mW ADC, PGA- Setting - dB Figure5.TotalHarmonicDistortionvsHeadphoneOut Figure6.Signal-To-NoiseRatiovsADCPGASetting Power 4 4 AVDD= 3.3 V, No Load No Load V 3.5 PGM = VDD 3.5 PGM = VDD - V GE E - OLTA 3 OLTAG 3 SV PGM = 2.5 V S V PGM = 2.5 V BIA 2.5 BIA 2.5 C C MI MI PGM = 2 V PGM = 2 V 2 2 1.5 1.5 2.7 2.9 3.1 3.3 3.5 -60 -40 -20 0 20 40 60 80 100 VDD- Supply Voltage - V TA- Free-Air Temperature - °C Figure7.MICBIASVoltagevsSupplyVoltage Figure8.MICBIASVoltagevsFree-AirTemperature 0 0 Load = 10 kW, Load = 10 kW, -20 F40S9 =6 4S8a mkHpzle, sfs,= 64 kHz, -20 FS = 48 kHz, fs= 64 kHz, AVDD= DRVDD= 3.3 V, AVDD= DRVDD= 3.3 V, -40 -40 B B d -60 d -60 e - e - d d u -80 u -80 plit plit m m A-100 A-100 -120 -120 -140 -140 -160 -160 0 2 4 6 8 10 12 14 16 18 20 0 2 4 6 8 10 12 14 16 18 20 f - Frequency - kHz f - Frequency - kHz Figure9.LeftDACFFT Figure10.RightDACFFT Copyright©2006–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 13 ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 www.ti.com Typical Characteristics (continued) 0 0 Load = 10 kW, Load = 10 kW, -20 F20S4 =8 4S8a mkHpzle, sfs,= 64 kHz, -20 F20S4 =8 4S8a mkHpzle, sfs,= 64 kHz, AVDD= DRVDD= 3.3 V, AVDD= DRVDD= 3.3 V, -40 -40 B B d -60 d -60 e - e - d d u -80 u -80 plit plit m m A-100 A-100 -120 -120 -140 -140 -160 -160 0 2 4 6 8 10 12 14 16 18 20 0 2 4 6 8 10 12 14 16 18 20 f - Frequency - kHz f - Frequency - kHz Figure11.LeftADCFFT Figure12.RightADCFFT 10 Parameter Measurement Information AllparametersaremeasuredaccordingtotheconditionsdescribedintheSpecificationssection. 14 SubmitDocumentationFeedback Copyright©2006–2014,TexasInstrumentsIncorporated ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 www.ti.com SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 11 Detailed Description 11.1 Overview The TLV320AIC3106 is a highly flexible, low power, stereo audio codec with extensive feature integration, intended for applications in smartphones, PDAs, and portable computing, communication, and entertainment applications. Available in a 5x5mm 80-ball BGA (with 51 balls actually used) and 7x7mm 48-lead QFN, the product integrates a host of features to reduce cost, board space, and power consumption in space-constrained, battery-powered,portableapplications. TheTLV320AIC3106consistsofthefollowingblocks: • Stereoaudiomulti-bitdelta-sigmaDAC(8kHz–96kHz) • Stereoaudiomulti-bitdelta-sigmaADC(8kHz–96kHz) • Programmabledigitalaudioeffectsprocessing(3-D,bass,treble,mid-range,EQ,notchfilter,de-emphasis) • Sixaudioinputs • Fourhigh-poweraudiooutputdrivers(headphonedrivecapability) • Threefullydifferentiallineoutputdrivers • FullyprogrammablePLL • Headphone/headsetjackdetectionwithinterrupt Communication to the TLV320AIC3106 for control is pin-selectable (using the SELECT pin) as either SPI or I2C. The SPI interface requires that the Slave Select signal (MFP0) be driven low to communicate with the TLV320AIC3106. Data is then shifted into or out of the TLV320AIC3106 under control of the host microprocessor, which also provides the serial data clock. The I2C interface supports both standard and fast communication modes, and also enables cascading of up to four multiple codecs on the same I2C bus through theuseoftwopinsforaddressing(MFP0,MFP1). Copyright©2006–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 15 ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 www.ti.com 11.2 Functional Block Diagram DINDOUT BCLKWCLK LINE2LP MMICI2CL2MLP / /L LININEE22LLMP + HPLOUT LINE2LM Audio Serial Bus Interface MIC3L/ LINE3L AGC DOUTL DOUTR DINRDINL VCM HPLCOM + SW-D2 LINE1LP MMICIC1L1MLP // LLIINNEE11LLMP + 00.5/+dP5BG9 s.A5tedpBs ADC Effects VCoolunmtroel DALC SW-D1 + LINE1LM HPRCOM VCM + HPROUT AGC SW-D4 LINE1RP LINE2LP SW-L2 MMICIC1R1RMP // LLIINNEE11RRMP LINE1RM + 00.5/+dP5BG9 s.A5tedpBs ADC SW-D3 Effects VCoolnutmroel DACR + LINE1LP SSSWWW---LLL310 LEFT_LOP LEFT_LOM SW-L4 LINE1LM SW-L5 LINE2LM MIC3R / LINE3R SW-R2 LINE2RP SW-R1 LINE1RP SW-R0 LINE2RP + RIGHT_LOP SW-R3 MIC2RP/ LINE2RP RIGHT_LOM MIC2RM / LINE2RM LINE1RM SW-R4 SW-R5 LINE2RM LINE2RM Voltage Supplies ReBfeiraesn/ce AGuednioe rCaltoiocnk SPI / I2C Serial Control Bus + MONO_LOP MONO_LOM CDA_DDVACDA_SSVACAD_DDVACAD_SSVA DDVRDDDVRDSSVRDSSVRD DDVDDDVOISSVD TEDICM SAIBCIM KLCM 1_OIPG2_IOPG TESER TCELES 0RDA_C2/ILESC1RDA_CI2/KLCS OIP/GISOMOIPG/OSIMIOPG/LCSOIPG/ADS 11.3 Feature Description 11.3.1 HardwareReset The TLV320AIC3106 requires a hardware reset after power-up for proper operation. After all power supplies are at their specified values, the RESET pin must be driven low for at least 10 ns. If this reset sequence is not performed,theTLV320AIC3106maynotrespondproperlytoregisterreads/writes. 11.3.2 DigitalAudioDataSerialInterface Audio data is transferred between the host processor and the TLV320AIC3106 via the digital audio data serial interface, or audio bus. The audio bus on this device is very flexible, including left or right justified data options, support for I2S or PCM protocols, programmable data length options, a TDM mode for multichannel operation, very flexible master/slave configurability for each bus clock line, and the ability to communicate with multiple deviceswithinasystemdirectly. The data serial interface uses two sets of pins for communication between external devices, with the particular pinusedcontrolledthroughregisterprogramming.ThisconfigurationisshowninFigure13below. 16 SubmitDocumentationFeedback Copyright©2006–2014,TexasInstrumentsIncorporated ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 www.ti.com SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 Feature Description (continued) WCLK BCLK DIN DOUT GPIO1 GPIO2 MFP3 Audio Serial Data Bus Figure13. AlternateAudioBusMulitplexingFunction In cases where MFP3 is needed for a secondary device digital input, the TLV320AIC3106 must be used in I2C mode (when in SPI mode, MFP3 is used as the SPI bus MOSI pin and thus cannot be used here as an alternate digitalinputsource). This mux capability allows the TLV320AIC3106 to communicate with two separate devices with independent I2S/PCM buses. An example of such an application is a cellphone containing a Bluetooth transceiver with PCM/I2S interface, as shown in Figure 14. The applications processor can be connected to the WCLK, BCLK, DIN, DOUT pins on the TLV320AIC3106, while a Bluetooth device with PCM interface can be connected to the GPIO1, GPIO2, MFP3, and DOUT pins on the TLV320AIC3106. By programming the registers via I2C control, the applications processor can determine which device is communicating with the TLV320AIC3106. This is attractive in cases where the TLV320AIC3106 can be configured to communicate data with the Bluetooth device, then the applications processor can be put into a low power sleep mode, while voice/audio transmission still occursbetweentheBluetoothdeviceandtheTLV320AIC3106. Processor Processor 1 2 K K N T 3 1 2 WCL BCL DI DOU MFP GPIO GPIO AIC3106 Possible ProcessorTypes: Application Processor, Multimedia Processor, CompressedAudio Decoder, Wireless Modem, Bluetooth Module,AdditionalAudio/Voice Codec Figure14. TLV320AIC3106ConnectedtoMultipleAudioDevices Copyright©2006–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 17 ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 www.ti.com Feature Description (continued) The audio bus of the TLV320AIC3106 can be configured for left or right justified, I2S, DSP, or TDM modes of operation, where communication with standard telephony PCM interfaces is supported within the TDM mode. These modes are all MSB-first, with data width programmable as 16, 20, 24, or 32 bits. In addition, the word clock (WCLK or GPIO1) and bit clock (BCLK or GPIO2) can be independently configured in either Master or Slavemode,forflexibleconnectivitytoawidevarietyofprocessors The word clock (WCLK or GPIO1) is used to define the beginning of a frame, and may be programmed as either a pulse or a square-wave signal. The frequency of this clock corresponds to the maximum of the selected ADC andDACsamplingfrequencies. The bit clock (BCLK or GPIO2) is used to clock in and out the digital audio data across the serial bus. When in Master mode, this signal can be programmed in two further modes: continuous transfer mode, and 256-clock mode. In continuous transfer mode, only the minimal number of bit clocks needed to transfer the audio data are generated, so in general the number of bit clocks per frame will be two times the data width. For example, if data width is chosen as 16 bits, then 32 bit clocks will be generated per frame. If the bit clock signal in master mode will be used by a PLL in another device, it is recommended that the 16-bit or 32-bit data width selections be used. These cases result in a low jitter bit clock signal being generated, having frequencies of 32 × f or 64 × f . S S In the cases of 20-bit and 24-bt data width in master mode, the bit clocks generated in each frame will not all be of equal period, due to the device not having a clean 40 × f or 48 × f clock signal readily available. The S S average frequency of the bit clock signal is still accurate in these cases (being 40 × f or 48 × f ), but the S S resultingclocksignalhashigherjitterthaninthe16-bitand32-bitcases. In 256-clock mode, a constant 256 bit clocks per frame are generated, independent of the data width chosen. The TLV320AIC3106 further includes programmability to 3-state the DOUT line during all bit clocks when valid data is not being sent. By combining this capability with the ability to program at what bit clock in a frame the audio data will begin, time-division multiplexing (TDM) can be accomplished, resulting in multiple codecs able to useasingleaudioserialdatabus. When the audio serial data bus is powered down while configured in master mode, the pins associated with the interfacewillbeputintoa3-stateoutputcondition. 11.3.2.1 Right-JustifiedMode In right-justified mode, the LSB of the left channel is valid on the rising edge of the bit clock preceding the falling edge of word clock. Similarly, the LSB of the right channel is valid on the rising edge of the bit clock preceding therisingedgeofthewordclock. 1/fs WCLK BCLK Left Channel Right Channel SDIN/ 0 n−1n−2n−3 2 1 0 n−1n−2n−3 2 1 0 SDOUT MSB LSB Figure15. Right-JustifiedSerialBusModeOperation 18 SubmitDocumentationFeedback Copyright©2006–2014,TexasInstrumentsIncorporated ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 www.ti.com SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 Feature Description (continued) 11.3.2.2 Left-JustifiedMode In left-justified mode, the MSB of the right channel is valid on the rising edge of the bit clock following the falling edge of the word clock. Similarly the MSB of the left channel is valid on the rising edge of the bit clock following therisingedgeofthewordclock. n-1 n-2 n-3 n-1 n-2 n-3 Figure16. Left-JustifiedSerialDataBusModeOperation 11.3.2.3 I2SMode In I2S mode, the MSB of the left channel is valid on the second rising edge of the bit clock after the falling edge of the word clock. Similarly the MSB of the right channel is valid on the second rising edge of the bit clock after therisingedgeofthewordclock. n-1 n-2 n-3 n-1 n-2 n-3 Figure17. I2SSerialDataBusModeOperation Copyright©2006–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 19 ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 www.ti.com Feature Description (continued) 11.3.2.4 DSPMode In DSP mode, the rising edge of the word clock starts the data transfer with the left channel data first and immediatelyfollowedbytherightchanneldata.Eachdatabitisvalidonthefallingedgeofthebitclock. 1/fs WCLK BCLK Left Channel Right Channel SDIN/SDOUT n–1 n–2 n–3 n–4 2 1 0 n–1 n–2 n–3 2 1 0 n–1 LSB MSB LSB MSB LSB T0152-01 Figure18. DSPSerialBusModeOperation 11.3.2.5 TDMDataTransfer Time-division multiplexed data transfer can be realized in any of the above transfer modes if the 256-clock bit clock mode is selected, although it is recommended to be used in either left-justified mode or DSP mode. By changing the programmable offset, the bit clock in each frame where the data begins can be changed, and the serial data output driver (DOUT) can also be programmed to 3-state during all bit clocks except when valid data is being put onto the bus. This allows other codecs to be programmed with different offsets and to drive their data onto the same DOUT line, just in a different slot. For incoming data, the codec simply ignores data on the busexceptwhereitisexpectedbasedontheprogrammedoffset. Note that the location of the data when an offset is programmed is different, depending on what transfer mode is selected. In DSP mode, both left and right channels of data are transferred immediately adjacent to each other in the frame. This differs from left-justified mode, where the left and right channel data will always be a half-frame apart in each frame. In this case, as the offset is programmed from zero to some higher value, both the left and right channel data move across the frame, but still stay a full half-frame apart from each other. This is depicted in Figure19forthetwocases. 20 SubmitDocumentationFeedback Copyright©2006–2014,TexasInstrumentsIncorporated ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 www.ti.com SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 Feature Description (continued) DSPMode word clock bitclock data in/out N-1 N-2 1 0 N-1 N-2 1 0 offset Left Channel Data Right Channel Data Left Justified Mode word clock bitclock data in/out N-1 N-2 1 0 N-1 N-2 1 0 Left Channel Data Right Channel Data offset offset Figure19. DSPModeandLeftJustifiedModes,Showingthe EffectofaProgrammedDataWordOffset 11.3.3 AudioDataConverters The TLV320AIC3106 supports the following standard audio sampling rates: 8 kHz, 11.025 kHz, 12 kHz, 16 kHz, 22.05 kHz, 24 kHz, 32 kHz, 44.1 kHz, 48 kHz, 88.2 kHz, and 96 kHz. The converters can also operate at differentsamplingratesinvariouscombinations,whicharedescribedfurtherbelow. The data converters are based on the concept of an f rate that is used internal to the part, and it is related to S(ref) the actual sampling rates of the converters through a series of ratios. For typical sampling rates, f will be S(ref) either 44.1 kHz or 48 kHz, although it can realistically be set over a wider range of rates up to 53 kHz, with additional restrictions applying if the PLL is used. This concept is used to set the sampling rates of the ADC and DAC, and also to enable high quality playback of low sampling rate data, without high frequency audible noise beinggenerated. The sampling rate of the ADC and DAC can be set to f /NDAC or 2×f /NDAC, with NDAC being 1, 1.5, 2, S(ref) S(ref) 2.5,3,3.5,4,4.5,5,5.5,or6. While only one f can be used at a time in the part, the ADC and DAC sampling rates can differ from each S(ref) other by using different NADC and NDAC divider ratios for each. For example, with f =44.1-kHz, the DAC S(ref) samplingratecanbesetto44.1-kHzbyusingNDAC=1,whiletheADCsamplingratecanbesetto8.018-kHzby usingNADC=5.5. When the ADCs and DACs are operating at different sampling rates, an additional word clock is required, to provideinformationregardingwheredatabeginsfortheADCversustheDAC.Inthiscase,thestandardbitclock signal (which can be supplied through the BCLK pin or through GPIO2) is used to transfer both ADC and DAC data,thestandardwordclocksignalisusedtoidentifythestartoftheDACdata,andaseparateADCwordclock signal (denoted ADWK) is used. This clock can be supplied or generated from GPIO1 at the same time the DAC wordclockissuppliedorgeneratedfromWCLK. Copyright©2006–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 21 ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 www.ti.com Feature Description (continued) 11.3.3.1 AudioClockGeneration The audio converters in the TLV320AIC3106 need an internal audio master clock at a frequency of 256 × f , S(ref) whichcanbeobtainedinavarietyofmannersfromanexternalclocksignalappliedtothedevice. AmoredetaileddiagramoftheaudioclocksectionoftheTLV320AIC3106isshowninFigure20. MCLK BCLK GPIO2 CLKDIV_CLKIN PLL_CLKIN CLKDIV_IN PLL_IN K = J.D J = 1,2,3,…..,62,63 Q=2,3,…..,16,17 2/Q K*R/P D= 0000,0001,….,9998,9999 R= 1,2,3,4,….,15,16 P= 1,2,….,7,8 PLL_OUT CLKDIV_OUT 1/8 PLLDIV_OUT CLKMUX _OUT CODEC_CLKIN CLKOUT_IN CODEC_CLK=256*Fsref M =1,2,4,8 2/(N*M) CODEC N = 2,3,……,16,17 CLKOUT DAC_FS ADC_FS GPIO1 WCLK = Fsref/ Ndac GPIO1 = Fsref/ Nadc Ndac=1,1.5,2,…..,5.5,6 Nadc=1,1.5,2,…..,5.5,6 DAC DRA=> Ndac = 0.5 ADC DRA => Nadc = 0.5 Figure20. AudioClockGenerationProcessing The part can accept an MCLK input from 512 kHz to 50 MHz, which can then be passed through either a programmable divider or a PLL, to get the proper internal audio master clock needed by the part. The BCLK or GPIO2inputscanalsobeusedtogeneratetheinternalaudiomasterclock. ThisdesignalsoallowsthePLLtobeusedforanentirelyseparatepurposeinasystem,iftheaudiocodecisnot poweredup.TheusercansupplyaseparateclocktoGPIO2,routethisthroughthePLL,withtheresultingoutput clockdrivenoutGPIO1,forusebyotherdevicesinthesystem A primary concern is proper operation of the codec at various sample rates with the limited MCLK frequencies available in the system. This device includes a highly programmable PLL to accommodate such situations easily. The integrated PLL can generate audio clocks from a wide variety of possible MCLK inputs, with particular focus paidtothestandardMCLKratesalreadywidelyused. WhenthePLLisdisabled, f =CLKDIV_IN/(128 ×Q) S(ref) 22 SubmitDocumentationFeedback Copyright©2006–2014,TexasInstrumentsIncorporated ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 www.ti.com SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 Feature Description (continued) WhereQ=2,3,…,17 CLKDIV_INcanbeMCLK,BCLK,orGPIO2,selectedbyregister102,bitsD7-D6. NOTE – when NDAC = 1.5, 2.5, 3.5, 4.5, or 5.5, odd values of Q are not allowed. In this mode, MCLK can be as highas50MHz,andf shouldfallwithin39kHzto53kHz. S(ref) WhenthePLLisenabled, f =(PLLCLK_IN× K× R)/(2048 ×P),where S(ref) P=1,2,3,…,8 R=1,2,…,16 K=J.D J=1,2,3,…,63 D=0000,0001,0002,0003, …,9998,9999 PLLCLK_INcanbeMCLKorBCLK,selectedbyPage0,register102,bitsD5-D4 P, R, J, and D are register programmable. J is the integer portion of K (the numbers to the left of the decimal point), while D is the fractional portion of K (the numbers to the right of the decimal point, assuming four digits of precision). Examples: IfK=8.5,thenJ=8,D=5000 IfK=7.12,thenJ=7,D=1200 IfK=14.03,thenJ=14,D=0300 IfK=6.0004,thenJ=6,D=0004 When the PLL is enabled and D = 0000, the following conditions must be satisfied to meet specified performance: 2MHz≤ (PLLCLK_IN/P) ≤ 20MHz 80MHz≤ (PLLCLK_IN× K ×R/P) ≤ 110MHz 4≤ J≤ 55 WhenthePLLisenabledandD≠0000,thefollowingconditionsmustbesatisfiedtomeetspecifiedperformance: 10MHz≤ PLLCLK_IN/P ≤ 20MHz 80MHz≤ PLLCLK_IN × K× R/P≤ 110MHz 4≤ J≤ 11 R=1 Example: MCLK=12MHzandf =44.1kHz S(ref) SelectP=1,R=1,K=7.5264,whichresultsinJ=7,D=5264 Example: MCLK=12MHzandf =48kHz S(ref) SelectP=1,R=1,K=8.192,whichresultsinJ=8,D=1920 Table 1 lists several example cases of typical MCLK rates and how to program the PLL to achieve f = 44.1 S(ref) kHzor48kHz. Copyright©2006–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 23 ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 www.ti.com Feature Description (continued) Table1.TypicalMCLKRates f =44.1kHz S(ref) MCLK(MHz) P R J D ACHIEVEDf %ERROR S(ref) 2.8224 1 1 32 0 44100.00 0.0000 5.6448 1 1 16 0 44100.00 0.0000 12.0 1 1 7 5264 44100.00 0.0000 13.0 1 1 6 9474 44099.71 –0.0007 16.0 1 1 5 6448 44100.00 0.0000 19.2 1 1 4 7040 44100.00 0.0000 19.68 1 1 4 5893 44100.30 0.0007 48.0 4 1 7 5264 44100.00 0.0000 f =48kHz S(ref) MCLK(MHz) P R J D ACHIEVEDf %ERROR S(ref) 2.048 1 1 48 0 48000.00 0.0000 3.072 1 1 32 0 48000.00 0.0000 4.096 1 1 24 0 48000.00 0.0000 6.144 1 1 16 0 48000.00 0.0000 8.192 1 1 12 0 48000.00 0.0000 12.0 1 1 8 1920 48000.00 0.0000 13.0 1 1 7 5618 47999.71 –0.0006 16.0 1 1 6 1440 48000.00 0.0000 19.2 1 1 5 1200 48000.00 0.0000 19.68 1 1 4 9951 47999.79 –0.0004 48.0 4 1 8 1920 48000.00 0.0000 The TLV320AIC3106 can also output a separate clock on the GPIO1 pin. If the PLL is being used for the audio data converter clock, the M and N settings can be used to provide a divided version of the PLL output. If the PLL is not being used for the audio data converter clock, the PLL can still be enabled to provide a completely independent clock output on GPIO1. The formula for the GPIO1 clock output when PLL is enabled and CLKMUX_OUTis0is: GPIO1=(PLLCLK_IN×2 ×K ×R)/(M × N×P) When CLKMUX_OUT is 1, regardless of whether PLL is enabled or disabled, the input to the clock output divider canbeselectedasMCLK,BCLK,orGPIO2.Isthiscase,theformulafortheGPIO1clockis: GPIO1=(CLKDIV_IN ×2)/(M× N),where M=1,2,4,8 N=2,3,…,17 CLKDIV_INcanbeBCLK,MCLK,orGPIO2,selectedbypage0,register102,bitsD7-D6 11.3.3.2 StereoAudioADC The TLV320AIC3106 includes a stereo audio ADC, which uses a delta-sigma modulator with 128-times oversamplinginsingle-ratemode,followedbyadigitaldecimationfilter.TheADCsupportssamplingratesfrom8 kHz to 48 kHz in single-rate mode, and up to 96 kHz in dual-rate mode. Whenever the ADC or DAC is in operation, the device requires that an audio master clock be provided and appropriate audio clock generation be setupwithinthedevice. In order to provide optimal system power dissipation, the stereo ADC can be powered one channel at a time, to support the case where only mono record capability is required. In addition, both channels can be fully powered orentirelypowereddown. 24 SubmitDocumentationFeedback Copyright©2006–2014,TexasInstrumentsIncorporated ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 www.ti.com SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 The integrated digital decimation filter removes high-frequency content and downsamples the audio data from an initial sampling rate of 128 f to the final output sampling rate of f . The decimation filter provides a linear phase S S output response with a group delay of 17/f . The –3-dB bandwidth of the decimation filter extends to 0.45 f and S S scales with the sample rate (f ). The filter has minimum 75-dB attenuation over the stop band from 0.55 f to 64 S S f . Independent digital high-pass filters are also included with each ADC channel, with a corner frequency that S canbeindependentlyset. Because of the oversampling nature of the audio ADC and the integrated digital decimation filtering, requirements for analog antialiasing filtering are very relaxed. The TLV320AIC3106 integrates a second-order analog antialiasing filter with 20-dB attenuation at 1 MHz. This filter, combined with the digital decimation filter, providessufficientantialiasingfilteringwithoutrequiringadditionalexternalcomponents. The ADC is preceded by a programmable gain amplifier (PGA), which allows analog gain control from 0 dB to 59.5 dB in steps of 0.5 dB. The PGA gain changes are implemented with an internal soft-stepping algorithm that only changes the actual volume level by one 0.5-dB step every one or two ADC output samples, depending on the register programming (see page 0, registers 19 and 22). This soft-stepping ensures that volume control changes occur smoothly with no audible artifacts. On reset, the PGA gain defaults to a mute condition, and on power down, the PGA soft-steps the volume to mute before shutting down. A read-only flag is set whenever the gain applied by PGA equals the desired value set by the register. The soft-stepping control can also be disabled by programming a register bit. When soft stepping is enabled, the audio master clock must be applied to the part after the ADC power-down register is written to ensure the soft-stepping to mute has completed. When the ADC power-downflagisnolongerset,theaudiomasterclockcanbeshutdown. 11.3.3.2.1 StereoAudioADCHigh-PassFilter Often in audio applications it is desirable to remove the dc offset from the converted audio data stream. The TLV320AIC3106 has a programmable first-order high-pass filter which can be used for this purpose. The digital filter coefficients are in 16-bit format and therefore use two 8-bit registers for each of the three coefficients, N0, N1,andD1.Thetransferfunctionofthedigitalhigh-passfilterisoftheform: H(z)(cid:4) N0(cid:2)N1(cid:1)z(cid:3)1 32,768(cid:3)D1(cid:1)z(cid:3)1 (1) Programming the left channel is done by writing to page 1, registers 65–70, and the right channel is programmed by writing to page 1, registers 71–76. After the coefficients have been loaded, these ADC high-pass filter coefficients can be selected by writing to page 0, register 107, bits D7–D6, and the high-pass filter can be enabledbywritingtopage0,register12,bitsD7–D4. 11.3.3.2.2 AutomaticGainControl(AGC) An automatic gain control (AGC) circuit is included with the ADC and can be used to maintain nominally constant output signal amplitude when recording speech signals (it can be fully disabled if not desired). This circuitry automatically adjusts the PGA gain as the input signal becomes overly loud or very weak, such as when a personspeakingintoamicrophonemovescloserorfartherfromthemicrophone.TheAGCalgorithmhasseveral programmable settings, including target gain, attack and decay time constants, noise threshold, and maximum PGA gain applicable that allow the algorithm to be fine tuned for any particular application. The algorithm uses the absolute average of the signal (which is the average of the absolute value of the signal) as a measure of the nominalamplitudeoftheoutputsignal. Note that completely independent AGC circuitry is included with each ADC channel with entirely independent control over the algorithm from one channel to the next. This is attractive in cases where two microphones are used in a system, but may have different placement in the end equipment and require different dynamic performanceforoptimalsystemoperation. 11.3.3.2.2.1 TargetLevel The target level represents the nominal output level at which the AGC attempts to hold the ADC output signal level. The TLV320AIC3106 allows programming of eight different target levels, which can be programmed from –5.5dBto –24dBrelativetoafull-scalesignal.Sincethedevicereactstothesignalabsoluteaverageandnotto peaklevels,itisrecommendedthatthetargetlevelbesetwithenoughmargintoavoidclippingattheoccurrence ofloudsounds. Copyright©2006–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 25 ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 www.ti.com 11.3.3.2.2.2 AttackTime The Attack time determines how quickly the AGC circuitry reduces the PGA gain when the input signal is too loud. It can be varied from 7 ms to 1,408 ms. The extended Right Channel Attack time can be programmed by writingtoPage0,Registers103,andLeftChannelisprogrammedbywritingtoPage0,Register105. 11.3.3.2.2.3 DecayTime The decay time determines how quickly the PGA gain is increased when the input signal is too low. It can be varied in the range from 0.05 s to 22.4 s. The extended Right Channel Decay time can be programmed by writingtoPage0,Registers104,andLeftChannelisprogrammedbywritingtoPage0,Register106. The actual AGC decay time maximum is based on a counter length, so the maximum decay time will scale with theclocksetupthatisused.Table2showstherelationshipoftheNADCratiotothemaximumtimeavailablefor the AGC decay. In practice, these maximum times are extremely long for audio applications and should not limit anypracticalAGCdecaytimethatisneededbythesystem. Table2.AGCDecayTimeRestriction NADCRATIO MAXIMUMDECAYTIME(seconds) 1.0 4.0 1.5 5.6 2.0 8.0 2.5 9.6 3.0 11.2 3.5 11.2 4.0 16.0 4.5 16.0 5.0 19.2 5.5 22.4 6.0 22.4 11.3.3.2.2.4 NoiseGateThreshold The noise gate threshold determines the level below which if the input speech average value falls, AGC considers it as a silence and hence brings down the gain to 0 dB in steps of 0.5 dB every FS and sets the noise threshold flag. The gain stays at 0 dB unless the input speech signal average rises above the noise threshold setting. This ensures that noise does not get gained up in the absence of speech. Noise threshold level in the AGC algorithm is programmable from –30 dB to –90 dB relative to full scale. A disable noise gate feature is also available. This operation includes programmable debounce and hysteresis functionality to avoid the AGC gain from cycling between high gain and 0 dB when signals are near the noise threshold level. When the noise thresholdflagisset,thestatusofgainappliedbytheAGCandthesaturationflagshouldbeignored. 11.3.3.2.2.5 MaximumPGAGainApplicable Maximum PGA gain applicable allows the user to restrict the maximum PGA gain that can be applied by the AGC algorithm. This can be used for limiting PGA gain in situations where environmental noise is greater than programmednoisethreshold.Itcanbeprogrammedfrom0dBto59.5dBinstepsof0.5dB. 26 SubmitDocumentationFeedback Copyright©2006–2014,TexasInstrumentsIncorporated ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 www.ti.com SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 Input Signal Output Target Signal Level AGC Gain Decay Time Attack Time Figure21. TypicalOperationoftheAGCAlgorithmDuringSpeechRecording Note that the time constants here are correct when the ADC is not in double-rate audio mode. The time constants are achieved using the f value programmed in the control registers. However, if the f is set in S(ref) S(ref) theregistersto,forexample,48kHz,buttheactualaudioclockorPLLprogrammingactuallyresultsinadifferent f inpractice,thenthetimeconstantswouldnotbecorrect. S(ref) The actual AGC decay time maximum is based on a counter length, so the maximum decay time scales with the clocksetupthatisused.Table2showstherelationshipoftheNADCratiotothemaximumtimeavailableforthe AGC decay. In practice, these maximum times are extremely long for audio applications and should not limit any practicalAGCdecaytimethatisneededbythesystem. 11.3.3.3 StereoAudioDAC The TLV320AIC3106 includes a stereo audio DAC supporting sampling rates from 8 kHz to 96 kHz. Each channel of the stereo audio DAC consists of a digital audio processing block, a digital interpolation filter, multi-bit digital delta-sigma modulator, and an analog reconstruction filter. The DAC is designed to provide enhanced performance at low sampling rates through increased oversampling and image filtering, thereby keeping quantization noise generated within the delta-sigma modulator and signal images strongly suppressed within the audio band to beyond 20 kHz. This is realized by keeping the upsampled rate constant at 128 × f and S(ref) changing the oversampling ratio as the input sample rate is changed. For an f of 48 kHz, the digital delta- S(ref) sigma modulator always operates at a rate of 6.144 MHz. This ensures that quantization noise generated within the delta-sigma modulator stays low within the frequency band below 20 kHz at all sample rates. Similarly, for an f rateof44.1kHz,thedigitaldelta-sigmamodulatoralwaysoperatesatarateof5.6448MHz. S(ref) The following restrictions apply in the case when the PLL is powered down and double-rate audio mode is enabledintheDAC. AllowedQvalues=4,8,9,12,16 Qvalueswhereequivalentf canbeachievedbyturningonPLL S(ref) Q=5,6,7(setP=5/6/7andK=16.0andPLLenabled) Q=10,14(setP=5,7andK=8.0andPLLenabled) Copyright©2006–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 27 ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 www.ti.com 11.3.3.3.1 DigitalAudioProcessingforPlayback The DAC channel consists of optional filters for de-emphasis and bass, treble, midrange level adjustment, speaker equalization, and 3-D effects processing. The de-emphasis function is implemented by a programmable digital filter block with fully programmable coefficients (see Page-1/Reg-21-26 for left channel, Page-1/Reg-47-52 for right channel). If de-emphasis is not required in a particular application, this programmable filter block can be usedforsomeotherpurpose.Thede-emphasisfiltertransferfunctionisgivenby: N0+N1x z-1 H(z)= 32768-D1x z-1 (2) where the N0, N1, and D1 coefficients are fully programmable individually for each channel. The coefficients that shouldbeloadedtoimplementstandardde-emphasisfiltersaregiveninTable3. Table3.De-EmphasisCoefficientsforCommonAudioSamplingRates SAMPLINGFREQUENCY N0 N1 D1 32-kHz 16950 –1220 17037 44.1-kHz 15091 –2877 20555 48-kHz(1) 14677 –3283 21374 (1) The48-kHzcoefficientslistedinTable3areusedasdefaults. In addition to the de-emphasis filter block, the DAC digital effects processing includes a fourth order digital IIR filter with programmable coefficients (one set per channel). This filter is implemented as cascade of two biquad sectionswithfrequencyresponsegivenby: (cid:4) N0(cid:2)2(cid:1)N1(cid:1)z(cid:3)1(cid:2)N2(cid:1)z(cid:3)2 (cid:5)(cid:4) N3(cid:2)2(cid:1)N4(cid:1)z(cid:3)1(cid:2)N5(cid:1)z(cid:3)2 (cid:5) 32768(cid:3)2(cid:1)D1(cid:1)z(cid:3)1(cid:3)D2(cid:1)z(cid:3)2 32768(cid:3)2(cid:1)D4(cid:1)z(cid:3)1(cid:3)D5(cid:1)z(cid:3)2 (3) The N and D coefficients are fully programmable, and the entire filter can be enabled or bypassed. The structure of the filtering when configured for independent channel processing is shown below in Figure 22, with LB1 corresponding to the first left-channel biquad filter using coefficients N0, N1, N2, D1, and D2. LB2 similarly corresponds to the second left-channel biquad filter using coefficients N3, N4, N5, D4, and D5. The RB1 and RB2filtersrefertothefirstandsecondright-channelbiquadfilters,respectively. LB1 LB2 RB1 RB2 Figure22. StructureoftheDigitalEffectsProcessingforIndependentChannelProcessing 28 SubmitDocumentationFeedback Copyright©2006–2014,TexasInstrumentsIncorporated ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 www.ti.com SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 The coefficients for this filter implement a variety of sound effects, with bass-boost or treble boost being the most commonly used in portable audio applications. The default N and D coefficients in the part are given in Table 4 and implement a shelving filter with 0-dB gain from DC to approximately 150 Hz, at which point it rolls off to a 3- dB attenuation for higher frequency signals, thus giving a 3-dB boost to signals below 150 Hz. The N and D coefficientsarerepresentedby16-bittwo’scomplementnumberswithvaluesrangingfrom –32768to32767. Table4.DefaultDigitalEffectsProcessingFilterCoefficients, WheninIndependentChannelProcessingConfiguration Coefficients N0=N3 D1=D4 N1=N4 D2=D5 N2=N5 27,619 32,131 –27,034 –31,506 26,461 The digital processing also includes capability to implement 3-D processing algorithms by providing means to process the mono mix of the stereo input, and then combine this with the individual channel signals for stereo output playback. The architecture of this processing mode, and the programmable filters available for use in the system, is shown in Figure 23. Note that the programmable attenuation block provides a method of adjusting the levelof3-Deffectintroducedintothefinalstereooutput.Thiscombinedwiththefullyprogrammablebiquadfilters in the system enables the user to fully optimize the audio effects for a particular system and provide extensive differentiationfromothersystemsusingthesamedevice. + + L LB2 To Left Channel + + + LB1 Atten – – To Right Channel + R RB2 + B0155-01 Figure23. ArchitectureoftheDigitalAudioProcessingWhen3-DEffectsareEnabled It is recommended that the digital effects filters should be disabled while the filter coefficients are being modified. While new coefficients are being written to the device over the control port, it is possible that a filter using partially updated coefficients may actually implement an unstable system and lead to oscillation or objectionable audio output. By disabling the filters, changing the coefficients, and then re-enabling the filters, these types of effectscanbeentirelyavoided. 11.3.3.3.2 DigitalInterpolationFilter The digital interpolation filter upsamples the output of the digital audio processing block by the required oversampling ratio before data is provided to the digital delta-sigma modulator and analog reconstruction filter stages. The filter provides a linear phase output with a group delay of 21/f . In addition, programmable digital S interpolation filtering is included to provide enhanced image filtering and reduce signal images caused by the upsampling process that are below 20 kHz. For example, upsampling an 8-kHz signal produces signal images at multiples of 8-kHz (i.e., 8 kHz, 16 kHz, 24 kHz, etc.). The images at 8 kHz and 16 kHz are below 20 kHz and still audible to the listener; therefore, they must be filtered heavily to maintain a good quality output. The interpolation Copyright©2006–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 29 ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 www.ti.com filter is designed to maintain at least 65-dB rejection of images that land below 7.455 f . In order to utilize the S programmable interpolation capability, the f should be programmed to a higher rate (restricted to be in the S(ref) rangeof39kHzto53kHzwhenthePLLisinuse),andtheactualf issetusingtheNDACdivider.Forexample, S if f = 8 kHz is required, then f can be set to 48 kHz, and the DAC f set to f /6. This ensures that all S S(ref) S S(ref) imagesofthe8-kHzdataaresufficientlyattenuatedwellbeyonda20-kHzaudiblefrequencyrange. 11.3.3.3.3 Delta-SigmaAudioDAC The stereo audio DAC incorporates a third order multi-bit delta-sigma modulator followed by an analog reconstruction filter. The DAC provides high-resolution, low-noise performance, using oversampling and noise shaping techniques. The analog reconstruction filter design consists of a 6-tap analog FIR filter followed by a continuous time RC filter. The analog FIR operates at a rate of 128 × f (6.144 MHz when f = 48 kHz, S(ref) S(ref) 5.6448 MHz when f = 44.1 kHz). Note that the DAC analog performance may be degraded by excessive S(ref) clockjitterontheMCLKinput.Therefore,caremustbetakentokeepjitteronthisclocktoaminimum. 11.3.3.3.4 AudioDACDigitalVolumeControl The audio DAC includes a digital volume control block which implements a programmable digital gain. The volume level can be varied from 0 dB to –63.5 dB in 0.5-dB steps, in addition to a mute bit, independently for each channel. The volume level of both channels can also be changed simultaneously by the master volume control. Gain changes are implemented with a soft-stepping algorithm, which only changes the actual volume by one step per input sample, either up or down, until the desired volume is reached. The rate of soft-stepping can beslowedtoonesteppertwoinputsamplesthrougharegisterbit. Because of soft-stepping, the host does not know when the DAC has been actually muted. This may be important if the host wishes to mute the DAC before making a significant change, such as changing sample rates. In order to help with this situation, the device provides a flag back to the host via a read-only register bit that alerts the host when the part has completed the soft-stepping and the actual volume has reached the desired volume level. The soft-stepping feature can be disabled through register programming. If soft-stepping is enabled, the MCLK signal should be kept applied to the device until the DAC power-down flag is set. When this flag is set, the internal soft-stepping process and power down sequence is complete, and the MCLK can then be stoppedifdesired. The TLV320AIC3106 also includes functionality to detect when the user switches on or off the de-emphasis or digital audio processing functions, to first (1) soft-mute the DAC volume control, (2) change the operation of the digital effects processing, and (3) soft-unmute the part. This avoids any possible pop/clicks in the audio output due to instantaneous changes in the filtering. A similar algorithm is used when first powering up or down the DAC. The circuit begins operation at power up with the volume control muted, then soft-steps it up to the desired volume level. At power down, the logic first soft-steps the volume down to a mute level, then powers down the circuitry. 11.3.3.3.5 IncreasingDACDynamicRange The TLV320AIC3106 allows trading off dynamic range with power consumption. The DAC dynamic range can be increased by writing to Page 0, Register 109 bits D7-D6. The lowest DAC current setting is the default, and the dynamic range is displayed in the datasheet table. Increasing the current can increase the DAC dynamic range byupto1.5dB. 11.3.3.3.6 AnalogOutputCommon-ModeAdjustment The output common-mode voltage and output range of the analog output are determined by an internal bandgap reference, in contrast to other codecs that may use a divided version of the supply. This scheme is used to reduce the coupling of noise that may be on the supply (such as 217-Hz noise in a GSM cellphone) into the audiosignalpath. However, due to the possible wide variation in analog supply range (2.7 V – 3.6 V), an output common-mode voltagesettingof1.35V,whichwouldbeusedfora2.7Vsupplycase,willbeoverlyconservativeifthesupplyis actually much larger, such as 3.3 V or 3.6 V. In order to optimize device operation, the TLV320AIC3106 includes a programmable output common-mode level, which can be set by register programming to a level most appropriate to the actual supply range used by a particular customer. The output common-mode level can be varied among four different values, ranging from 1.35 V (most appropriate for low supply ranges, near 2.7 V) to 1.8 V (most appropriate for high supply ranges, near 3.6 V). Note that there is also some limitation on the range ofDVDDvoltageaswellindeterminingwhichsettingismostappropriate. 30 SubmitDocumentationFeedback Copyright©2006–2014,TexasInstrumentsIncorporated ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 www.ti.com SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 Table5.AppropriateSettings CMSETTING RECOMMENDEDAVDD_DAC, RECOMMENDEDDVDD DRVDD 1.35 2.7V–3.6V 1.65V–1.95V 1.50 3.0V–3.6V 1.65V–1.95V 1.65V 3.3V–3.6V 1.8V–1.95V 1.8V 3.6V 1.95V 11.3.3.3.7 AudioDACPowerControl The stereo DAC can be fully powered up or down, and in addition, the analog circuitry in each DAC channel can be powered up or down independently. This provides power savings when only a mono playback stream is needed. 11.3.4 AudioAnalogInputs The TLV320AIC3106 includes ten analog audio input pins, which can be configured as up to four fully-differential pair plus one single-ended pair of audio inputs, or up to six single-ended audio inputs. . These pins connect through series resistors and switches to the virtual ground terminals of two fully differential opamps (one per ADC/PGA channel). By selecting to turn on only one set of switches per opamp at a time, the inputs can be effectivelymuxedtoeachADCPGAchannel. By selecting to turn on multiple sets of switches per opamp at a time, mixing can also be achieved. Mixing of multiple inputs can easily lead to PGA outputs that exceed the range of the internal opamps, resulting in saturation and clipping of the mixed output signal. Whenever mixing is being implemented, the user should take adequate precautions to avoid such a saturation case from occurring. In general, the mixed signal should not exceed2V (single-ended)or4V (differential). pp pp In most mixing applications, there is also a general need to adjust the levels of the individual signals being mixed. For example, if a soft signal and a large signal are to be mixed and played together, the soft signal generally should be amplified to a level comparable to the large signal before mixing. In order to accommodate this need, the TLV320AIC3106 includes input level control on each of the individual inputs before they are mixed or muxed into the ADC PGAs, with gain programmable from 0 dB to –12 dB in 1.5 dB steps. Note that this input level control is not intended to be a volume control, but instead used occasionally for level setting. Soft-stepping of the input level control settings is implemented in this device, with the speed and functionality following the settingsusedbytheADCPGAforsoft-stepping. The TLV320AIC3106 supports the ability to mix up to three fully-differential analog inputs into each ADC PGA channel. Figure 24 shows the mixing configuration for the left channel, which can mix the signals LINE1LP- LINE1LM,LINE2LP-LINE2LM,andLINE1RP-LINE1RM GAIN=0,−1.5,−3,..,−12dB,MUTE LINE1LP LINE1LM GAIN=0,−1.5,−3,..,−12dB, MUTE LINE2LP TO LEFT ADC LINE2LM PGA GAIN=0,−1.5,−3,..,−12dB,MUTE LINE1RP LINE1RM Figure24. LeftChannelFully-DifferentialAnalogInputMixingConfiguration Copyright©2006–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 31 ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 www.ti.com Three fully-differential analog inputs can similarly be mixed into the right ADC PGA as well, consisting of LINE1RP-LINE1RM, LINE2RP-LINE2RM, and LINE1LP-LINE1LM. Note that it is not necessary to mix all three fully-differential signals if this is not desired – unnecessary inputs can simply be muted using the input level controlregisters. Inputscanalsobeselectedassingle-endedinsteadoffully-differential,andmixingormuxingintotheADCPGAs is also possible in this mode. It is not possible, however, for an input pair to be selected as fully-differential for connection to one ADC PGA and simultaneously selected as single-ended for connection to the other ADC PGA channel. However, it is possible for an input to be selected or mixed into both left and right channel PGAs, as longasithasthesameconfigurationforbothchannels(eitherbothsingle-endedorbothfully-differential). Figure 25 shows the single-ended mixing configuration for the left channel ADC PGA, which enables mixing of the signals LINE1LP, LINE2LP, LINE1RP, MIC3L, and MIC3R. The right channel ADC PGA mix is similar, enablingmixingofthesignalsLINE1RP,LINE2RP,LINE1LP,MIC3L,andMIC3R. GAIN=0,-1.5,-3,..,-12dB,MUTE LINE1LP/MIC1LP GAIN=0,-1.5,-3,..,-12dB,MUTE LINE2LP/MIC2LP GAIN=0,-1.5,-3,..,-12dB,MUTE LINE1RP/MIC1RP TO LEFTADC PGA GAIN=0,-1.5,-3,..,-12dB,MUTE LINE3L/MIC3L GAIN=0,-1.5,-3,..,-12dB,MUTE LINE3R/MIC3R Figure25. LeftChannelSingle-EndedAnalogInputMixingConfiguration 32 SubmitDocumentationFeedback Copyright©2006–2014,TexasInstrumentsIncorporated ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 www.ti.com SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 11.3.5 AnalogFullyDifferentialLineOutputDrivers The TLV320AIC3106 has two fully differential line output drivers, each capable of driving a 10-kΩ differential load. The output stage design leading to the fully differential line output drivers is shown in Figure 26 and Figure 27. This design includes extensive capability to adjust signal levels independently before any mixing occurs,beyondthatalreadyprovidedbythePGAgainandtheDACdigitalvolumecontrol. DAC_L1 DAC_L DAC_L2 STEREO DAC_L3 AUDIO DAC_R1 DAC DAC_R DAC_R2 DAC_R3 LINE2L LINE2R VOLUME PGA_L CONTROLS, PGA_R LEFT_LOP MIXING DAC_L1 LEFT_LOM DAC_R1 Gain = 0dB to +9dB, Mute DAC_L3 LINE2L LINE2R VOLUME PGA_L CONTROLS, RIGHT_LOP PGA_R MIXING DAC_L1 RIGHT_LOM DAC_R1 Gain = 0dB to +9dB, Mute DAC_R3 LINE2L LINE2R PGA_L VOLUME MONO_LOP CONTROLS, PGA_R MIXING MONO_LOM DAC_L1 Gain = 0dB to +9dB, DAC_R1 Mute Figure26. ArchitectureoftheOutputStageLeadingtotheFullyDifferentialLineOutputDrivers The LINE2L/R signals refer to the signals that travel through the analog input bypass path to the output stage. The PGA_L/R signals refer to the outputs of the ADC PGA stages that are similarly passed around the ADC to the output stage. Note that since both left and right channel signals are routed to all output drivers, a mono mix of any of the stereo signals can easily be obtained by setting the volume controls of both left and right channel signals to –6 dB and mixing them. Undesired signals can also be disconnected from the mix as well through registercontrol. Copyright©2006–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 33 ProductFolderLinks:TLV320AIC3106

TLV320AIC3106 SLAS509F–DECEMBER2006–REVISEDDECEMBER2014 www.ti.com LINE2L/MIC2L 0dB to -78dB LINE2R/MIC2R 0dB to -78dB PGA_L 0dB to -78dB + PGA_R 0dB to -78dB DAC_L1 0dB to -78dB DAC_R1 0dB to -78dB Figure27. DetailoftheVolumeControlandMixingFunctionShowninFigure22 andFigure37 The DAC_L/R signals are the outputs of the stereo audio DAC, which can be steered by register control based on the requirements of the system. If mixing of the DAC audio with other signals is not required, and the DAC output is only needed at the stereo line outputs, then it is recommended to use the routing through path DAC_L3/R3 to the fully differential stereo line outputs. This results not only in higher quality output performance, but also in lower power operation, since the analog volume controls and mixing blocks ahead of these drivers canbepowereddown. If instead the DAC analog output must be routed to multiple output drivers simultaneously (such as to LEFT_LOP/M, RIGHT_LOP/M, and MONO_LOP/M) or must be mixed with other analog signals, then the DAC outputs should be switched through the DAC_L1/R1 path. This option provides the maximum flexibility for routing oftheDACanalogsignalstotheoutputdrivers The TLV320AIC3106 includes an output level control on each output driver with limited gain adjustment from 0 dB to 9 dB. The output driver circuitry in this device are designed to provide a low distortion output while playing fullscale stereo DAC signals at a 0dB gain setting. However, a higher amplitude output can be obtained at the cost of increased signal distortion at the output. This output level control allows the user to make this tradeoff based on the requirements of the end equipment. Note that this output level control is not intended to be used as a standard output volume control. It is expected to be used only sparingly for level setting, that is, adjustment of thefullscaleoutputrangeofthedevice. The PGA_L/R signals refer to the outputs of the ADC PGA stages that are similarly passed around the ADC to the output stage. Note that because both left- and right-channel signals are routed to all output drivers, a mono mix of any of the stereo signals can easily be obtained by setting the volume controls of both left- and right- channel signals to –6 dB and mixing them. Undesired signals can also be disconnected from the mix as well throughregistercontrol. 11.3.6 AnalogHighPowerOutputDrivers The TLV320AIC3106 includes four high power output drivers with extensive flexibility in their usage. These output drivers are individually capable of driving 30 mW each into a 16-Ω load in single-ended configuration, and theycanbeusedinpairsconnectedinbridge-terminatedload(BTL)configurationbetweentwodriveroutputs. Thehighpoweroutputdriverscanbeconfiguredinavarietyofways,including: 1. drivinguptotwofullydifferentialoutputsignals 2. drivinguptofoursingle-endedoutputsignals 3. driving two single-ended output signals, with one or two of the remaining drivers driving a fixed VCM level, forapseudo-differentialstereooutput 34 SubmitDocumentationFeedback Copyright©2006–2014,TexasInstrumentsIncorporated ProductFolderLinks:TLV320AIC3106