ICGOO在线商城 > TLC5943PWPR

- 型号: TLC5943PWPR

- 制造商: Texas Instruments

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

TLC5943PWPR产品简介:

ICGOO电子元器件商城为您提供TLC5943PWPR由Texas Instruments设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 提供TLC5943PWPR价格参考¥7.93-¥16.18以及Texas InstrumentsTLC5943PWPR封装/规格参数等产品信息。 你可以下载TLC5943PWPR参考资料、Datasheet数据手册功能说明书, 资料中有TLC5943PWPR详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC) |

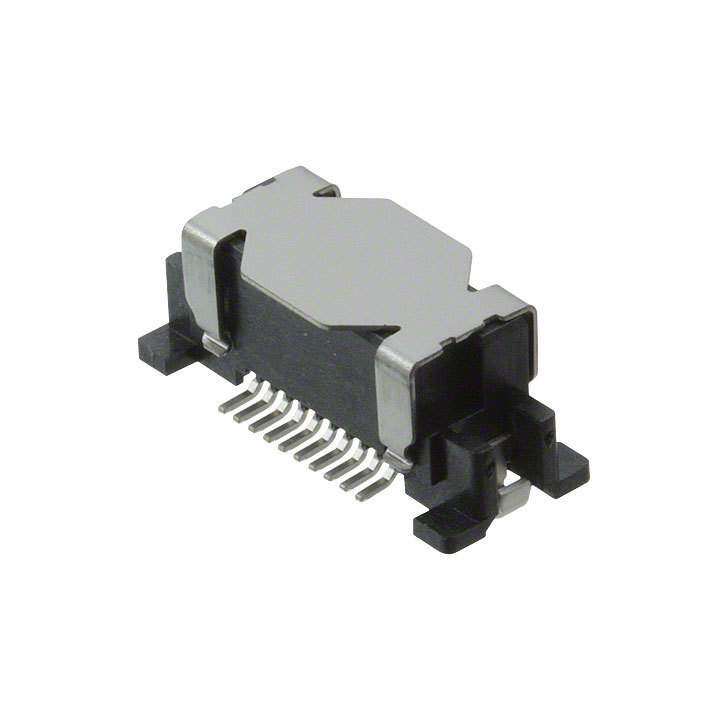

| 描述 | IC LED DRIVER LINEAR 28-TSSOP |

| 产品分类 | |

| 品牌 | Texas Instruments |

| 数据手册 | |

| 产品图片 |

|

| 产品型号 | TLC5943PWPR |

| rohs | 无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | - |

| 产品目录页面 | |

| 供应商器件封装 | 28-HTSSOP |

| 其它名称 | 296-22974-6 |

| 内部驱动器 | 是 |

| 包装 | Digi-Reel® |

| 安装类型 | 表面贴装 |

| 封装/外壳 | 28-SOIC(0.173",4.40mm 宽)裸露焊盘 |

| 工作温度 | -40°C ~ 85°C |

| 恒压 | - |

| 恒流 | 是 |

| 拓扑 | PWM |

| 标准包装 | 1 |

| 电压-电源 | 3 V ~ 5.5 V |

| 电压-输出 | 17V |

| 类型-初级 | 背光 |

| 类型-次级 | 颜色 |

| 输出数 | 16 |

| 频率 | 30MHz |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

TLC5943 www.ti.com SBVS101–DECEMBER2007 16-Channel, 16-Bit PWM LED Driver with 7-Bit Global Brightness Control FEATURES • ReadableErrorInformation: 1 • 16Channels,ConstantCurrentSinkOutput – LEDOpenDetection(LOD) 23 • 50-mACapability(ConstantCurrentSink) – ThermalErrorFlag(TEF) • 16-Bit(65,536Steps)GrayscaleControlwith • NoiseReduction: EnhancedSpectrum(ES)PWM – 4-channelgroupeddelaytopreventinrush • 7-Bit(128Steps)GlobalBrightnessControlfor current AllChannelswithSinkCurrent • OperatingTemperature:–40(cid:176) Cto+85(cid:176) C • LEDPower-SupplyVoltageupto17V • V =3.0Vto5.5V APPLICATIONS CC • ConstantCurrentAccuracy: • Monochrome,Multicolor,Full-ColorLED Displays – Channel-to-Channel=±1.5% • LEDSignboards – Device-to-Device=±3% • DisplayBacklighting • CMOSLevelI/O • 30-MHzDataTransferRate DESCRIPTION • 33-MHzGrayscaleControlClock The TLC5943 is a 16-channel, constant current sink • AutoDisplayRepeat driver. Each channel is individually adjustable with • AutoDataRefresh 65,536 enhanced spectrum pulse-width modulated (PWM) steps controlled by grayscale (GS) data. All • ContinuousBaseLEDOpenDetection(LOD): output drivers are adjustable with 128 constant sink – DetectLEDopeningandLEDshorttoGND current steps at same value controlled by brightness duringdisplay control (BC) data. Both GS data and BC data are • ThermalShutdown(TSD): writable via a serial interface port. The maximum current value of all 16 channels can be set by a – Automaticshutdownathightemperature singleexternalresistor. conditions – Restartundernormaltemperature VLED VLED VLED VLED ¼ ¼ ¼ ¼ ¼ ¼ ¼ ¼ OUT0 OUT15 OUT0 OUT15 DATA SIN SOUT SIN SOUT SCLK SCLK XERR SCLK XERR BCSEL BCSEL BCSEL XLAT XLAT VCC VCC XLAT VCC Controller BLANK BLANK VCC BLANK VCC GFLSACGLSK GSCLK XTEST GSCLK XTEST READ IREF IREF XREERARD RIREF TLCIC51943 GND RIREF TLCIC5n943 GND 5 XTEST pin must be connected to VCC or GND. TypicalApplicationCircuit(MultipleDaisy-ChainedTLC5943s) 1 Pleasebeawarethatanimportantnoticeconcerningavailability,standardwarranty,anduseincriticalapplicationsof TexasInstrumentssemiconductorproductsanddisclaimerstheretoappearsattheendofthisdatasheet. PowerPADisatrademarkofTexasInstruments,Inc. 2 Allothertrademarksarethepropertyoftheirrespectiveowners. 3 PRODUCTIONDATAinformationiscurrentasofpublicationdate. Copyright©2007,TexasInstrumentsIncorporated Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarilyincludetestingofallparameters.

TLC5943 www.ti.com SBVS101–DECEMBER2007 DESCRIPTION, CONTINUED The TLC5943 has two error detection circuits for LED open detection (LOD) and a thermal error flag (TEF). LOD detects a broken or disconnected LED and shorted LED to GND during the display period. TEF indicates an over-temperature condition; when a TEF is set, all output drivers are turned off. When the TEF is cleared, all outputdriversarerestarted. blank This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriateprecautions.Failuretoobserveproperhandlingandinstallationprocedurescancausedamage. ESDdamagecanrangefromsubtleperformancedegradationtocompletedevicefailure.Precisionintegratedcircuitsmaybemore susceptibletodamagebecauseverysmallparametricchangescouldcausethedevicenottomeetitspublishedspecifications. PACKAGE/ORDERINGINFORMATION(1) TRANSPORTMEDIA, PRODUCT PACKAGE-LEAD ORDERINGNUMBER QUANTITY TLC5943PWPR TapeandReel,2000 TLC5943 HTSSOP-28PowerPAD™ TLC5943PWP Tube,50 TLC5943RHBR TapeandReel,3000 TLC5943 5mm· 5mmQFN-32 TLC5943RHBT TapeandReel,250 (1) ForthemostcurrentpackageandorderinginformationseethePackageOptionAddendumattheendofthisdocument,orseetheTI websiteatwww.ti.com. ABSOLUTE MAXIMUM RATINGS(1)(2) Overoperatingfree-airtemperaturerange,unlessotherwisenoted. PARAMETER TLC5943 UNIT V Supplyvoltage,V –0.3to+6.0 V CC CC I Outputcurrent(dc):OUT0toOUT15 60 mA OUT Inputvoltagerange: V –0.3toV +0.3 V IN SIN,SCLK,XLAT,BLANK,GSCLK,BCSEL,IREF CC SOUT,XERR –0.3toV +0.3 V CC V Outputvoltagerange OUT OUT0toOUT15 –0.3to+18 V T Maximumoperatingjunctiontemperature +150 (cid:176) C J(max) T Storagetemperaturerange –55to+150 (cid:176) C STG Humanbodymodel(HBM) 2 kV ESDrating Chargeddevicemodel(CDM) 500 V (1) Stressesabovetheseratingsmaycausepermanentdamage.Exposuretoabsolutemaximumconditionsforextendedperiodsmay degradedevicereliability.Thesearestressratingsonly,andfunctionaloperationofthedeviceattheseoranyotherconditionsbeyond thosespecifiedisnotsupported. (2) Allvoltagevaluesarewithrespecttonetworkgroundterminal. 2 SubmitDocumentationFeedback Copyright©2007,TexasInstrumentsIncorporated ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 RECOMMENDED OPERATING CONDITIONS AtT =–40(cid:176) Cto+85(cid:176) C,unlessotherwisenoted. A TLC5943 PARAMETER TESTCONDITIONS MIN NOM MAX UNIT DCCharacteristics:V =3Vto5.5V CC V Supplyvoltage 3.0 5.5 V CC V Voltageappliedtooutput OUT0toOUT15 17 V O V High-levelinputvoltage 0.7· V V V IH CC CC V Low-levelinputvoltage GND 0.3· V V IL CC I High-leveloutputcurrent SOUT –1 mA OH SOUT 1 mA I Low-leveloutputcurrent OL XERR 5 mA I Constantoutputsinkcurrent OUT0toOUT15 50 mA OLC T Operatingfree-airtemperature –40 +85 (cid:176) C A T Operatingjunction –40 +125 (cid:176) C J temperature ACCharacteristics:V =3Vto5.5V CC f Datashiftclockfrequency SCLK 30 MHz CLK(sclk) Grayscalecontrolclock f GSCLK 33 MHz CLK(gsclk) frequency T /T SCLK,GSCLK 10 ns WH0 WL0 Pulseduration T XLAT,BLANK 30 ns WH1 T SIN–SCLK↑ 6 ns SU0 T XLAT↑–SCLK↑ 100 ns SU1 T BLANK↓–GSCLK↑ 10 ns SU2 T Setuptime BCSEL–SCLK↑ 10 ns SU3 T BCSEL–XLAT↑ 30 ns SU4 T XLAT↓–SCLK↑ 15 ns SU5 T XLAT↑–BLANK↓ 20 ns SU6 T SIN–SCLK↑ 3 ns H0 T XLAT↑–SCLK↑ 30 ns H1 Holdtime T BCSEL–SCLK↓ 10 ns H2 T BCSEL–XLAT↑ 100 ns H3 DISSIPATION RATINGS OPERATINGFACTOR T <+25(cid:176) C T =+70(cid:176) C T =+85(cid:176) C A A A PACKAGE ABOVET =+25(cid:176) C POWERRATING POWERRATING POWERRATING A PoHwTerSPSAODPs-2o8ldewriethd(1) 31.67mW/(cid:176) C 3958mW 2533mW 2058mW PoweHrTPSASDOnPo-t2s8owldiethred(2) 16.21mW/(cid:176) C 2026mW 1296mW 1053mW QFN-32(3) 27.86mW/(cid:176) C 3482mW 2228mW 1811mW (1) WithPowerPADsolderedontocopperareaonprintedcircuitboard(PCB);2oz.copper.Formoreinformation,seeSLMA002(available fordownloadatwww.ti.com). (2) WithPowerPADnotsolderedontocopperareaonPCB. (3) ThepackagethermalimpedanceiscalculatedinaccordancewithJESD51-5. Copyright©2007,TexasInstrumentsIncorporated SubmitDocumentationFeedback 3 ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 ELECTRICAL CHARACTERISTICS AtV =3.0Vto5.5V,andT =–40(cid:176) Cto+85(cid:176) C.TypicalvaluesatV =3.3VandT =+25(cid:176) C,unlessotherwisenoted. CC A CC A TLC5943 PARAMETER TESTCONDITIONS MIN TYP MAX UNIT VOH High-leveloutputvoltage IOH=–1mAatSOUT VCC–0.4 VCC V IOL=1mAatSOUT 0 0.4 V VOL Low-leveloutputvoltage IOL=5mAatXERR 0.4 V IIN Inputcurrent VBILNA=NVKC,CBCorSGENLDatSIN,SCLK,GSCLK,XLAT, –1 1 m A SIN/SCLK/GSCLK/XLAT/BCSEL=low,BLANK=high, ICC1 GSn=FFFFh,BCn=7Fh,VOUTn=1V,RIREF=10kΩ 1 3 mA SIN/SCLK/GSCLK/XLAT/BCSEL=low,BLANK=high, ICC2 GSn=FFFFh,BCn=7Fh,VOUTn=1V,RIREF=2kΩ 4 8 mA SCLK/GSCLK=30MHz,SIN=15MHz, ICC3 Supplycurrent(VCC) XGLSAnT=/BFCFSFEFLh/,BBLCAnNK=7=Flohw,A,utoRepeaton, 14 30 mA VOUTn=1V,RIREF=2kΩ(1) SCLK/GSCLK=30MHz,SIN=15MHz, XLAT/BCSEL/BLANK=low, ICC4 GSn=FFFFh,BCn=7Fh,AutoRepeaton, 27 50 mA VOUTn=1V,RIREF=1kΩ(1) IO(LC) Constantoutputcurrent AVOllUOTfUixT=n1=VO,NR,IRBECFn==17kΩFh,VOUTn=1V, 43 49 55 mA IO(LKG1) Leakageoutputcurrent BALtAONUKT0=thoigOhU,TR1IR5EF=1kΩ,VOUTn=17V, 0.1 m A IO(LKG2) Leakageoutputcurrent Noerrorcondition,VXERR=5.5V,atXERR 1 m A ΔIO(LC) C(poinn-stota-pnitnc)u(1r)renterror AVOllUOTfUixT=n1=VO,NR,IRBECFn==17kΩFh,,aVtOOUUTnT0=t1oVO,UT15 ±1.5 ±4 % ΔIO(LC1) C(doenvsictaen-ttoc-duerrveicnet)e(2rr)or AVOllUOTfUixT=n1=VO,NR,IRBECFn==17kΩFh,VOUTn=1V, ±3 ±9 % ΔIO(LC2) Lineregulation(3) AVOllUOTfUixT=n1=VO,NR,IRBECFn==17kΩFh,,aVtOOUUTnT0=t1oVO,UT15 ±1 ±4 %/V ΔIO(LC3) Loadregulation(4) AVOllUOTfUixT=n1=VO,NR,IRDECFn==17kΩFh,,aVtOOUUTTn0=t1oVOUtoT315V, ±1 ±3 %/V T(TEF) Thermalerrorflagthreshold Junctiontemperature(5) +150 +162 +175 (cid:176)C T(HYS) Thermalerrorhysteresis Junctiontemperature(5) +5 +10 +20 (cid:176)C VLOD LEDopendetectionthreshold AllOUTn=ON 0.2 0.3 0.4 V VIREF Referencevoltageoutput RIREF=1kΩ 1.16 1.20 1.24 V (1) ThedeviationofeachoutputfromtheaverageofOUT0–OUT15constantcurrent.Deviationiscalculatedbytheformula: I D(%) = OUTn -1 ´100 (I + I + ... + I ) OUT0 OUT1 OUT15 16 . (2) ThedeviationoftheOUT0–OUT15constantcurrentaveragefromtheidealconstantcurrentvalue. Deviationiscalculatedbythefollowingformula: (I + I + ... I + I ) OUT0 OUT1 OUT14 OUT15 -(Ideal Output Current) 16 D(%) = ´100 Ideal Output Current Idealcurrentiscalculatedbytheformula: 1.20 I = 41´ OUT(IDEAL) R IREF (3) Lineregulationiscalculatedbythisequation: D(%/V) = (IOUTnat VCC= 5.5 V)-(IOUTnat VCC= 3.0 V) ´ 100 (IOUTnat VCC= 3.0 V) 5.5 V-3 V (4) Loadregulationiscalculatedbytheequation: D(%/V) = (IOUTnat VOUTn= 3 V)-(IOUTnat VOUTn= 1 V) ´ 100 (I at V = 1 V) 3 V-1 V OUTn OUTn (5) Nottested.Specifiedbydesign. 4 SubmitDocumentationFeedback Copyright©2007,TexasInstrumentsIncorporated ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 SWITCHING CHARACTERISTICS AtV =3.0Vto5.5V,T =–40(cid:176) Cto+85(cid:176) C,C =15pF,R =82Ω,R =1kΩ,andV =5.0V.Typicalvaluesat CC A L L IREF LED V =3.3VandT =+25(cid:176) C,unlessotherwisenoted. CC A TLC5943 PARAMETER TESTCONDITIONS MIN TYP MAX UNIT t SOUT 16 R0 Risetime ns t OUTn,BC=7Fh 10 30 R1 t SOUT 16 F0 ns t Falltime OUTn,BC=7Fh 10 30 F1 t XERR,C =100pF,R =1kΩ,V =5V 100 ns F2 L L XERR t SCLK↑toSOUT 25 ns D0 t BLANK↑toOUT0sinkcurrentoff 20 40 ns D1 t GSCLK↑toOUT0/4/8/12 5 18 40 ns D2 Propagationdelaytime t GSCLK↑toOUT1/5/9/13 20 42 73 ns D3 t GSCLK↑toOUT2/6/10/14 35 66 106 ns D4 t GSCLK↑toOUT3/7/11/15 50 90 140 ns D5 t Outputon-timeerror(1) GSn=0001h,GSCLK=33MHz –20 10 ns ON_ERR (1) Outputon-timeerroriscalculatedbythefollowingformula:T (ns)=t –T .t istheactualon-timeoftheconstant ON_ERR OUTON GSCLK OUTON currentdriver.T istheperiodofGSCLK. GSCLK Copyright©2007,TexasInstrumentsIncorporated SubmitDocumentationFeedback 5 ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 FUNCTIONAL BLOCK DIAGRAM VCC 16 LED Open Detection Data Latch gsclk33 (16 LOD) VCC 16 LSB MSB SIN Grayscale Shift Register (16 Bits x 16 Channels) SOUT SCLK 0 255 256 LSB MSB First Grayscale Data Latch (16 Bits x 16 Channels) 0 255 256 LSB MSB BCSEL Second Grayscale Data Latch (16 Bits x 16 Channels) 0 255 LSB MSB Brightness Control (7 Bits) / Auto Repeat Enable (1 Bit) Shift Register 0 8 7 XLAT LSB MSB 256 First Brightness Control (7 Bits) / Auto Repeat Enable (1 Bit) Data Latch err d xlatbuf 0 7 7 lo LSB MSB gsclk33 gslat2 bclat2 Second BrigDhatntae sLsa Ctcohntrol (7 Bits) rptena 0 1 6 GSCLK AGuSto C Roeupneteart// 16 16-Bit ES PWM Timing Control XERR XERR Refresh Control 16 7 BLANK Output Switching Delay blankbuf (4-Chann1e6l Unit) tderr xlatbuf ankbuf bl IREF Reference Constant Current Driver with 7-Bit Current (128 Steps) Global Current Control Control 16 XTEST LED Open Detection Thermal GND (LOD, 16 Channels) Detection GND ¼ OUT0 OUT1 OUT14 OUT15 6 SubmitDocumentationFeedback Copyright©2007,TexasInstrumentsIncorporated ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 DEVICE INFORMATION PWPPACKAGE RHBPACKAGE (TopView) (TopView) K 5 4 3 2 1 L T R 1 1 1 1 1 GND 1 28 VCC C U R T T T T T S O E U U U U U G S X O O O O O BLANK 2 27 IREF 4 3 2 1 0 9 8 7 XLAT 3 26 XTEST 2 2 2 2 2 1 1 1 SCLK 4 25 GSCLK XTEST 25 16 OUT10 SIN 5 24 SOUT IREF 26 15 OUT9 BCSEL 6 23 XERR VCC 27 14 OUT8 OUT0 7 Thermal 22 OUT15 NC 28 13 NC Thermal Pad OUT1 8 21 OUT14 NC 29 Pad 12 NC OUT2 9 20 OUT13 GND 30 11 OUT7 OUT3 10 19 OUT12 BLANK 31 10 OUT6 OUT4 11 18 OUT11 XLAT 32 9 OUT5 OUT5 12 17 OUT10 1 2 3 4 5 6 7 8 OUT6 13 16 OUT9 K N L 0 1 2 3 4 OUT7 14 15 OUT8 CL SI SE UT UT UT UT UT S C O O O O O B NC=Nointernalconnection. Copyright©2007,TexasInstrumentsIncorporated SubmitDocumentationFeedback 7 ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 TERMINALFUNCTIONS TERMINAL NAME PWP RHB I/O DESCRIPTION SIN 5 2 I Serialdatainputforgrayscaleandbrightnesscontroldata.Schmittbufferinput. SerialdatashiftclockforGSshiftregisterandBCshiftregister.Schmittbufferinput.Theshift registerisselectedbyBCSEL.DatapresentontheSINpinareshiftedintotheshiftregister SCLK 4 1 I selectedbyBCSELwiththerisingedgeoftheSCLKpin.Dataintheselectedshiftregisterare shiftedtotheMSBsideby1-bitsynchronizingtotherisingedgeofSCLK.TheMSBdataofthe selectedregisterappearsonSOUT. DataintheGrayscaleandBrightnessshiftregisteraremovedtotherespectivefirstdatalatch XLAT 3 32 I withalow-to-hightransitionofthispin. Shiftregisteranddatalatchselect.Schmittbufferinput.WhenBCSELislow,Grayscaleshift BCSEL 6 3 I registerandfirstdatalatchareselected.WhenBCSELishigh,BrightnessControlshiftregister andfirstdatalatchareselected.BCSELshouldnotbechangedwhileSCLKishigh. ReferenceclockforGrayscalePWMcontrol.Schmittbufferinput.IfBLANKislow,theneach GSCLK 25 24 I risingedgeofGSCLKincrementsthegrayscalecounterforPWMcontrol. Blank(allconstantcurrentoutputsoff).Schmittbufferinput.WhenBLANKishigh,allconstant currentoutputs(OUT0throughOUT15)areforcedoff,theGrayscalecounterisresetto'0',and BLANK 2 31 I theGrayscalePWMtimingcontrollerisinitialized.WhenBLANKislow,allconstantcurrent outputsarecontrolledbytheGrayscalePWMtimingcontroller. Constantcurrentvaluesetting.OUT0throughOUT15sinkconstantcurrentissettodesired IREF 27 26 I/O valuebyconnectinganexternalresistorbetweenIREFandGND. Serialdataoutput.ThisoutputisconnectedtoGrayscale/StatusInformationshiftregisteror SOUT 24 23 O BrightnessControlshiftregister.TheconnectedregisterisselectedbyBCSEL. XERR 23 22 O Erroroutput.Open-drainoutput.XERRgoeslowwhenLODorTEFisdetected. OUT0 7 4 O Constantcurrentoutput. OUT1 8 5 O Constantcurrentoutput OUT2 9 6 O Constantcurrentoutput OUT3 10 7 O Constantcurrentoutput OUT4 11 8 O Constantcurrentoutput OUT5 12 9 O Constantcurrentoutput OUT6 13 10 O Constantcurrentoutput OUT7 14 11 O Constantcurrentoutput OUT8 15 14 O Constantcurrentoutput OUT9 16 15 O Constantcurrentoutput OUT10 17 16 O Constantcurrentoutput OUT11 18 17 O Constantcurrentoutput OUT12 19 18 O Constantcurrentoutput OUT13 20 19 O Constantcurrentoutput OUT14 21 20 O Constantcurrentoutput OUT15 22 21 O Constantcurrentoutput VCC 28 27 — Power-supplyvoltage GND 1 30 — Powerground XTEST 26 25 I Factorytestpin.XTESTmustbeconnectedtoVCCorGND. 12,13, NC — — Nointernalconnection 28,29 8 SubmitDocumentationFeedback Copyright©2007,TexasInstrumentsIncorporated ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 PARAMETER MEASUREMENT INFORMATION PIN EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS VCC VCC INPUT SOUT GND GND Figure1.SIN,SCLK,XLAT,BCSEL,BLANK,GSCLK Figure2.SOUT XERR OUTn GND GND Figure3.XERR Figure4.OUT0ThroughOUT15 TEST CIRCUITS VCC R VCC L VCC IREF OUTn V VCC SOUT RIREF GND CL(1) LED GND CL(1) (1) C includes measurement probe and jig (1) C includes measurement probe and jig L L capacitance. capacitance. Figure5.RiseTimeandFallTimeTestCircuitforOUTn Figure6.RiseTimeandFallTimeTestCircuitforSOUT VCC R VCC OUT0 L VCC VCC ¼ XERR V IREF OUTn C(1) XERR ¼ GND L RIREF GND OUT15 VOUTn VOUT FIX Figure8.ConstantCurrentTestCircuitforOUTn (1) C includes measurement probe and jig L capacitance. Figure7.RiseTimeandFallTimeTestCircuitforXERR Copyright©2007,TexasInstrumentsIncorporated SubmitDocumentationFeedback 9 ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 TIMING DIAGRAMS T , T , T WH0 WH1 WL0 VCC INPUT(1) 50% GND T T WH WL T , T , T , T , T , T , T , T , T , T , T SU0 SU1 SU2 SU3 SU4 SU5 SU6 H0 H1 H2 H3 VCC CLOCK 50% INPUT(1) GND T T SU H VCC DATA/CONTROL 50% INPUT(1) GND (1) Inputpulseriseandfalltimeis1nsto3ns. Figure9.InputTiming t , t , t , t , t , t , t , t , t , t : R0 R1 F0 F1 D0 D1 D2 D3 D4 D5 VCC INPUT(1) 50% GND t D V or V H OH OUTn 90% OUTPUT(2) 50% 10% V or V L OL OUTn t or t R F (1) Inputpulseriseandfalltimeis1nsto3ns. (2) InputpulsehighlevelisV andlowlevelisGND. CC Figure10.OutputTiming 10 SubmitDocumentationFeedback Copyright©2007,TexasInstrumentsIncorporated ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 BCSEL T TSU4 TH3 SU3 SIN GS0 GS15 GS15 GS15 GS15 GS15 GS0 GS0 GS0 GS0 0A 15B 14B 13B 12B 11B 3B 2B 1B 0B T H0 TSU0 TWH0 TH1 T SU1 SCLK 1 2 3 4 5 253 254 255 256 TWH0 TWL0 TH2 GSCLK 65,53465,53565,53665,53765,538 TWL0 TWH1 TGSCLK XLAT T SU6 T WH1 BLANK T SU2 Latched Data for Grayscale Previous Data Latest Data (Internal) t D0 SOUT GS15 GS15 GS15 GS15 GS15 GS15 GS0 GS0 GS0 GS0 GS15 LOD LOD LOD LOD LOD LOD LOD 15A 14A 13A 12A 11A 10A 3A 2A 1A 0A 15B 15 14 13 12 11 10 9 t /t R0 F0 t D1 Turning off outputs with the BLANK signal (all GS data are greater than 0300h): (V H) OUTn OFF OUT (V L) 0, 4, 8, 12 ON OUTn t D2 OUT OFF 1, 5, 9, 13 ON If GS data = FFFFh (65535d) tD3 tF1 t R1 OFF OUT 2, 6, 10, 14 ON t D4 OUT OFF 3, 7, 11, 15 ON t D5 Turning off outputs with GSCLK (all GS data are set to 0001h): OFF OUT 0, 4, 8, 12 ON t D2 t OUTON OUT OFF 1, 5, 9, 13 ON t D3 t OUTON OFF OUT 2, 6, 10, 14 ON t D4 t OUTON OUT OFF 3, 7, 11, 15 ON t D5 tOUTON tON_ERR= tOUTON-TGSCLK Figure11.GrayscaleDataWriteandConstantCurrentOutputTiming Copyright©2007,TexasInstrumentsIncorporated SubmitDocumentationFeedback 11 ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 BCSEL T TSU3 SU4 TH3 SIN N/A BC BC BC BC BC BC BC BC BC BC BC BC BC BC BC BC 7B 6B 5B 4B 3B 2B 1B 0B 7C 6C 5C 4C 3C 2C 1C 0C T H0 T SU0 TWH0 TSU1 TH2 SCLK 1 2 3 4 5 6 7 8 1 2 3 4 5 6 7 8 T T WL0 H1 T WH1 XLAT Latched Data for Brightness Control Previous Data New BC Data (Internal) t D0 SOUT BC BC BC BC BC BC BC BC BC BC BC BC BC BC BC BC BC 7A 6A 5A 4A 3A 2A 1A 0A 7B 6B 5B 4B 3B 2B 1B 0B 7C t /t R0 F0 Figure12.BrightnessControlDataWriteTiming BCSEL Low('L')level The SCLK falling edge must be prior to the XLAT rising edge in case SID is read. SIN GS0 GS0 GS15 GS15 GS15 GS15 GS15 GS15 GS15 GS15 GS14 GS14 GS14 GS14 GS0 GS0 1A 0A 15B 14B 13B 12B 11B 2B 1B 0B 15B 14B 13B 12B 1B 0B 255 256 T 1 2 3 4 5 13 14 15 16 17 18 19 20 254 255 256 SU1 SCLK T T T H1 WH1 SU5 XLAT t D0 SOUT G0S0 G1S51A5 L1O5D L1O4D L1O3D L1O2D LO3D LO2D LO1D LO0D TEF G1S41A4 G1S31A4 G1SA0 G0SA0 G1S51B5 256 255 254 253 244 243 242 241 239 238 2 1 SID are entered in the GS shift register at the first rising edge of SCLK after XLAT goes low. The SID readout consists of the saved LOD result at the 33rd GSCLK rising edge in the previous display period and the TEF data after the previous TEF data readout. Figure13.StatusInformationDataReadTiming 12 SubmitDocumentationFeedback Copyright©2007,TexasInstrumentsIncorporated ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 TYPICAL CHARACTERISTICS AtV =3.3VandT =+25(cid:176) C,unlessotherwisenoted. CC A REFERENCERESISTORvs POWERDISSIPATIONRATE OUTPUTCURRENT vsFREE-AIRTEMPERATURE 10000 4000 9840 TLC5943PWP PowerPAD Soldered W) TLC5943RHB Wor () 4920 ate (m 3000 st R si n e o Reference R 3280 21496608 1640 wer Dissipati 21000000 PoweTrPLACD59 N4o3tP SWoPldered o P 1406 1093 1230 984 1000 0 0 10 20 30 40 50 -40 -20 0 20 40 60 80 100 Output Current (mA) Free-Air Temperature (°C) Figure14. Figure15. OUTPUTCURRENTvs OUTPUTCURRENTvs OUTPUTVOLTAGE OUTPUTVOLTAGE 60 55 T = +25°C I = 50 mA A O BC = 7Fh IO= 50 mA 54 BC = 7Fh 50 53 mA) 40 IO= 40 mA mA) 52 T = +85°C urrent ( 30 IO= 30 mA urrent ( 5510 A C C utput 20 IO= 20 mA utput 4498 TA=-40°C TA= +25°C O O I = 10 mA O 47 10 46 I = 5 mA 0 O 45 0 0.5 1.0 1.5 2.0 2.5 3.0 0 0.5 1.0 1.5 2.0 2.5 3.0 Output Voltage (V) Output Voltage (V) Figure16. Figure17. ΔI vs ΔI vs OLC OLC AMBIENTTEMPERATURE OUTPUTCURRENT 5 5 I = 50 mA T = +25°C O A 4 BC = 7Fh 4 BC = 7Fh 3 3 2 2 %) 1 %) 1 ( ( C 0 C 0 OL OL DI -1 DI -1 -2 -2 -3 -3 V = 3.3 V V = 3.3 V -4 CC -4 CC V = 5 V V = 5 V CC CC -5 -5 -40 -20 0 20 40 60 80 100 0 10 20 30 40 50 Ambient Temperature (°C) Output Current (mA) Figure18. Figure19. Copyright©2007,TexasInstrumentsIncorporated SubmitDocumentationFeedback 13 ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 TYPICAL CHARACTERISTICS (continued) AtV =3.3VandT =+25(cid:176) C,unlessotherwisenoted. CC A BRIGHTNESSCONTROLLINEARITY BRIGHTNESSCONTROLLINEARITY 60 60 T = +25°C I = 50 mA A OLCMax 50 50 I = 50 mA A) OLCMax A) m 40 m 40 nt ( nt ( e e urr 30 urr 30 C C ut ut Outp 20 IOLCMax= 30 mA Outp 20 T =-40°C A 10 I = 5 mA 10 TA= +25°C OLCMax T = +85°C A 0 0 0 20 40 60 80 100 120 140 0 20 40 60 80 100 120 140 Brightness Control Data (dec) Brightness Control Data (dec) Figure20. Figure21. CONSTANTCURRENTOUTPUT VOLTAGEWAVEFORM CH1-GSCLK CH1 (2 V/div) (30 MHz) CH2-OUT0 CH2 (2 V/div) (GSData = 0x001h) CH3-OUT15 CH3 (2 V/div) I = 50 mA, BC = 7Fh (GSData = 0x001h) OLCMax T = +25°C,R = 82W A L C = 15 pF, VLED = 5 V L Time (25 ns/div) Figure22. 14 SubmitDocumentationFeedback Copyright©2007,TexasInstrumentsIncorporated ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 DETAILED DESCRIPTION Setting for the Maximum Constant Sink Current Value On the TLC5943, the maximum constant current sink value for each channel, I , is determined by an OLCMax external resistor, R , placed between the IREF and GND pins. The R resistor value is calculated with IREF IREF Equation1: R (kW) = VIREF(V) ´41 IREF IOLCMax(mA) (1) Where: • V =theinternalreferencevoltageontheIREFpin(typically1.20V) IREF I is the largest current for all outputs. Each output sinks the I current when it is turned on and the OLCMax OLCMax brightness control data are set to the maximum value of 7Fh (127d). The sink current for each output can be reducedbyloweringthebrightnesscontroldata. R must be between 984 Ω (typ) and 9.84 kΩ (typ) in order to keep I between 5 mA and 50 mA. The IREF OLCMax output may become unstable when I is set lower than 5 mA. However, output currents lower than 5 mA OLCMax can be achieved by setting I to 5 mA or higher, and then using brightness control to lower the output OLCMax current. Figure 14 in the Typical Characteristics and Table 1 show the characteristics of the constant sink current versus theexternalresistor,R . IREF Table1.MaximumConstantCurrentOutputversus ExternalResistorValue I (mA,Typical) R (Ω) OLCMax IREF 50 984 45 1093 40 1230 35 1406 30 1640 25 1968 20 2460 15 3280 10 4920 5 9840 Copyright©2007,TexasInstrumentsIncorporated SubmitDocumentationFeedback 15 ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 Brightness Control (BC) Function The TLC5943 is able to adjust the output current of all channels (OUT0 to OUT15). This function is called brightness control (BC). The BC function allows users to adjust the global brightness of LEDs connected to the outputs OUT0 to OUT15. All channel output currents can be adjusted in 128 steps from 0% to 100% of the maximum output current, I . The brightness control data are entered into the TLC5943 via the serial OLCMax interface. Equation2determinesthesinkcurrentforeachoutput(OUTn): BCn I (mA) = I (mA)´( ) OUTn OLCMax 127d (2) Where: • I =themaximumchannelcurrentforeachchanneldeterminedbyR OLCMax IREF • BCn=theprogrammedbrightnesscontrolvalueforOUTn(BCn=0to127d) When the IC is powered on, the data in the Brightness Control Shift Register and data latch 1 and 2 are not set to any default values. Therefore, BC data must be written to the BC latch 1 and 2 before turning on the constant currentoutput. Table2summarizestheBCdataversuscurrentratioandsetcurrentvalue. Table2.BCDataversusCurrentRatioandSetCurrentValue SETCURRENT OUTPUTCURRENT OUTPUTCURRENT BCDATA BCDATA BCDATA RATIOTO (mA,Typical) (mA,Typical) (Binary) (Decimal) (Hex) MAXCURRENT(%) ATI =50mA ATI =5mA OLCMax OLCMax 0000000 0 00 0.0 0.0 0.00 0000001 1 01 0.8 0.4 0.04 0000010 2 02 1.6 0.8 0.08 ...... ...... ...... ...... ...... ...... 1111101 125 7D 98.4 49.2 4.92 1111110 126 7E 99.2 49.6 4.96 1111111 127 7F 100.0 50.0 5.00 16 SubmitDocumentationFeedback Copyright©2007,TexasInstrumentsIncorporated ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 Grayscale (GS) Function (Enhanced Spectrum PWM Operation) The TLC5943 has an enhanced spectrum pulse-width modulation (ES PWM) function. In this PWM control, the total display period is divided to 128 display segments. Total display period means the timing from the first grayscale clock (GSCLK) input to the 65,536th grayscale clock input after BLANK goes low. Each display period has 512 grayscale as a maximum. The driver (OUTn) on time changes depending on the 16-bit grayscale data. RefertoTable3forsequenceinformationandFigure23fortiminginformation. Table3.ESPWMDriveTurn-OnTimeLength GSDATA(Dec) GSDATA(Hex) OUTnDRIVEROPERATION 0 0000h Noturnon 1 0001h Turnsonduring1GSCLKperiodinfirstdisplayperiod 2 0002h Turnsonduring1GSCLKperiodinfirstand65thdisplayperiods 3 0003h Turnsonduring1GSCLKperiodinfirst,65th,and33rddisplayperiods 4 0004h Turnsonduring1GSCLKperiodinfirst,65th,33rd,and97thdisplayperiods 5 0005h Turnsonduring1GSCLKperiodinfirst,65th,33rd,97th,and17thdisplayperiods 6 0006h Turnsonduring1GSCLKperiodinfirst,65th,33rd,97th,17th,and81stdisplay periods --- --- ThenumberofdisplayperiodsinwhichOUTnturnsonduring1GSCLKis increasedbyGSdataincreasinginthefollowingorder. ThedisplayperiodorderinwhichOUTnturnson: 1>65>33>97>17>81>49>113>9>73>41>105>25>89>57>121>5>69>37>101>21> 85>53>117>13>77>45>109>29>93>61>125>3>67>35>99>19>83>51>115>11> 75>43>107>27>91>59>123>7>71>39>103>23>87>55>119>15>79>47>111>31> 95>63>127>2>66>34>98>18>82>50>114>10>74>42>106>26>90>58>122>6>70> 38>102>22>86>54>118>14>78>46>110>30>94>62>126>4>68>36>100>20>84> 52>116>12>76>44>108>28>92>60>124>8>72>40>104>24>88>56>120>16>80> 48>112>32>96>64>128. 127 007Fh Turnsonduring1GSCLKperiodinfirstthrough127thdisplayperiod.Noturnonin 128thdisplayperiodonly. 128 0080h Turnsonduring1GSCLKperiodinall(1through128th)displayperiods. 129 0081h Turnsonduring2GSCLKperiodsinfirstdisplayperiodand1GSCLKperiodin otherdisplayperiods. --- --- ThenumberofdisplayperiodsinwhichOUTnturnsonduring2GSCLKsincreases byGSdataaswhenGSis130through254. 255 00FFh Turnsonduring2GSCLKsperiodin1through127thdisplayperiodandturnson 1GSCLKperiodin128thdisplayperiodonly. 256 0100h Turnsonduring2GSCLKperiodsinall(1through128th)displayperiods. 257 0101h Turnsonduring3GSCLKperiodsinfirstdisplayperiodand2GSCLKperiodsin otherdisplayperiods. --- --- DisplayperiodinwhichOUTnturn-ontimeincreasesbyGSdata,increasingas doesaboveoperation 65478 FEFFh Turnsonduring511GSCLKperiodin1through127thdisplayperiodandturnson 510GSCLKperiodin128thdisplayperiodonly. 65279 FF00h Turnsonduring511GSCLKperiodinall(1through128th)displayperiods. 65280 FF01h Turnsonduring512GSCLKperiodinfirstdisplayperiod+511GSCLKperiodin secondthrough128thdisplayperiod. --- --- DisplayperiodinwhichOUTnturn-ontimeincreasesbyGSdata,increasingas doesaboveoperation 65534 FFFEh Turnsonduring512GSCLKperiodinfirstthrough63rdand65ththrough127th displayperiod,andturnson511GSCLKperiodin64thand128thdisplayperiods. 65535 FFFFh Turnsonduring512GSCLKperiodinfirstthrough127thdisplayperiods,andturns on511GSCLKperiodin128thdisplayperiodonly. Copyright©2007,TexasInstrumentsIncorporated SubmitDocumentationFeedback 17 ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 ConstantCurrentDriverON/OFFTminginES-PWM BLANK 512 514 16,38316,38516,387 32,76732,76932,771 49,15149,15349,155 65,02465,026 65,535 1 2 3 511 513 16,38216,38416,386 32,76632,76832,770 49,15049,15249,154 65,02365,025 65,53465,536 GSCLK 2nd 32nd 33rd 64th 65th 96th 97th 127th 1st Period 128th Period 1st Period Voltage level = High ('H') Period¼Period Period ¼ Period Period ¼ Period Period¼Period OFF OUTn ON Voltage level = Low ('L’) (GSDATA = 000h) T = GSCLK´1d OFF OUTn ON (GSDATA = 001h) If Auto Repeat T = GSCLK´1d T = GSCLK´1d is enabled OFF OUTn ON (GSDATA = 002h) T = GSCLK´1d T = GSCLK´1d T = GSCLK´1d OFF OUTn ON (GSDATA = 003h) T = GSCLK´1d T = GSCLK´1d T = GSCLK´1d T = GSCLK´1d OFF OUTn ON (GSDATA = 004h) ¼ ¼ T = GSCLK´1d T = GSCLK´1d T = GSCLK´1d T = GSCLK´1d T = GSCLK´1d OFF OUTn ON (GSDATA = 0041h) ¼ ¼ T = GSCLK´1d T = GSCLK´1d T = GSCLK´1d T = GSCLK´1d T = GSCLK´1d T = GSCLK ´1d OFF OUTn ON (GSDATA = 0080h) T = GSCLK T = GSCLK´1d T = GSCLK´1d T = GSCLK´1d T = GSCLK´1d T = GSCLK ´2d ´1d OFF OUTn ON (GSDATA = 0081h) T = GSCLK T = GSCLK´1d T = GSCLK´1d T = GSCLK T = GSCLK´1d T = GSCLK ´2d ´2d ´1d OFF OUTn ON (GSDATA = 0082h) ¼ ¼ T = GSCLK´511d T = GSCLK´511d in 2nd through 128th Periods OFF OUTn ON (GSDATA = FFC0h) T = GSCLK´512d in 2ndT t=h rGoSugChL K12´8t5h1 P1deriods OFF OUTn ON (GSDATA = FFC1h) ¼ ¼ T = GSCLK´512d in 2nd through 63rd and 65th through 127th Periods; T = GSCLK´512d T =GSCLK´511d in 64th Period T = GSCLK´511d OFF OUTn ON (GSDATA = FFFEh) T = GSCLK´512d T =GSCLK´512d in 2nd through 127th Periods T = GSCLK´511d OFF OUTn ON (GSDATA = FFFFh) Figure23.PWMOperationTiming 18 SubmitDocumentationFeedback Copyright©2007,TexasInstrumentsIncorporated ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 When the IC powers on, the data in the Grayscale Shift Register and latch 1/2 are not set to any default value. Therefore, grayscale data must be written to the Grayscale latch before turning on the constant current output. Additionally, BLANK should be high when the device turns on, to prevent the outputs from turning on before the proper grayscale and brightness control values can be written. All constant current outputs are always off when BLANKishigh.Equation3determineseachoutput(OUTn)totalontime(t ): OUTON t (ns) = T (ns)´GSn OUTON GSCLK (3) Where: • T =theperiodofGSCLK GSCLK • GSn=theprogrammedgrayscalevalueforOUTn(GSn=0to65,535d) Table4summarizestheGSdataversusOUTnondutyandontime. Table4.GSDataversusOUTnTotalOnDuty GSDATA(Decimal) GSDATA(Hex) ON-TIMEDUTY(%) GSDATA(Decimal) GSDATA(Hex) ON-TIMEDUTY(%) 0 0 0 32768 8000 50.001 1 1 0.002 32769 8001 50.002 2 2 0.003 32770 8002 50.004 3 3 0.005 32771 8003 50.005 --- --- --- --- --- --- 8191 1FFF 12.499 40959 9FFF 62.499 8192 2000 12.5 40960 A000 62.501 8193 2001 12.502 40961 A001 62.502 --- --- --- --- --- --- 16381 3FFD 24.996 49149 BFFD 74.997 16382 3FFE 24.997 49150 C000 74.998 16383 3FFF 24.999 49151 C001 75 16384 4000 25 49152 C002 75.001 16385 4001 25.002 49153 C003 75.003 16386 4002 25.003 49154 C004 75.004 16387 4003 25.005 49155 C005 75.006 --- --- --- --- --- --- 24575 5FFF 37.499 57343 DFFF 87.5 24576 6000 37.501 57344 E000 87.501 24577 6001 37.502 57345 E001 87.503 --- --- --- --- 32765 7FFD 49.996 65533 FFFD 99.997 32766 7FFE 49.998 65534 FFFE 99.998 32767 7FFF 49.999 65535 FFFF 100 Copyright©2007,TexasInstrumentsIncorporated SubmitDocumentationFeedback 19 ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 Auto Display Repeat Function This function can repeat the total display period without a BLANK signal as long as GSCLK is input as Figure 24 shows. This function can be switched on or off by the data of bit 7 in the first latch of the Brightness Control. When bit 7 is '1', Auto Repeat is enabled and the entire display period repeats without a BLANK signal. When bit 7 is '0', Auto Repeat is disabled and the entire display period executes only one time after the falling edge of BLANK. BLANK ¼ 65,534 65,536 ¼ 65,534 65,536 ¼65,534 65,536 1 2 3 4 5 65,533 65,535 1 2 3 4 5 65,533 65,535 1 2 3 4 5 6 7 8 9 10 1 2 65,535 1 2 GSCLK Bit 7 =‘1’ (Auto Repeat On) Bit 7 =‘0’ Brightness (Auto Repeat Off) 1st Latch Bit 7 1st of 128 2nd of 128 3rd of 128 display period display period display period 1st of 128 display period OUTn is not turned on until Display period repeated OUTn is forced off next BLANK OFF by Auto Refresh function when BLANK goes high falling edge OUTn ON (GSData = FFFFh) Figure24.AutoRepeatDisplayFunctionTiming 20 SubmitDocumentationFeedback Copyright©2007,TexasInstrumentsIncorporated ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 Auto Data Refresh Function This function allows users to input Grayscale (GS) data or Brightness Control (BC) data any time without synchronizing the input to the BLANK signal. If GS data or BC data are input during a display period, the input data are held in the first latch for each data register. Data are then transferred to the second latch when the 65,536th GSCLK occurs. The second latch data are used for the next display period. Figure 25 through Figure27showthetiming. However, when the high level signal of BLANK occurs before the 65,536th GSCLK, then the first latch data upload to the second latch immediately. Also, when the XLAT rising edge inputs while BLANK is at a high level, then the selected shift register data are transferred to the first and second latch at the same time. Bit 7 data of BCupdateimmediatelywheneverthedataarewrittenintothefirstlatch. SIN GS0 GS0 GS0 GS0 GS0 BC BC BC BC BC BC BC BC GS15 GS15 GS15 GS15 4A 3A 2A 1B 0A 7A 6A 5A 4A 3A 2A 1A 0A 15B 14B 13B 12B SCLK 251 252 253 254 255 256 1 2 3 4 5 6 7 8 1 2 3 4 BCSEL Low level ('L') = Grayscale Register is selected High level ('H') = Brightness Register is selected XLAT 65,536 65,535 1 2 3 4 5 6 7 8 GSCLK BLANK Low level ('L') GS Shift Register Latest Grayscale Data (Internal) GSData Previous Grayscale Data Latest Grayscale Data 1st Latch (Internal) GSData Previous Grayscale Data Latest Grayscale Data 2nd Latch (Internal) BC Shift Register Previous Brightness Data Latest Brightness Data (Internal) BCData Previous Brightness Data Latest Brightness Data 1st Latch (Internal) BCData Previous Brightness Data (Bit 0-Bit 6) Latest Brightness Data (Bit 0-Bit 6) 2nd Latch (Internal) OFF OUTn PWM/Brightness Controlled by Previous Data PWM/Brightness Controlled by Latest Data ON SOUT GS0 GS0 GS0 GS0 GS0 GS15 BC BC BC BC BC BC BC BC BC GS15 GS15 GS15 GS15 GS15 4 3 2 1 0 15A 7 6 5 4 3 2 1 0 7A 15A 14A 13A 12A 11A IfthereisnoBLANKinputwhenAutoRepeatisenabled. Figure25.AutoRefreshDataFunctionTiming1 Copyright©2007,TexasInstrumentsIncorporated SubmitDocumentationFeedback 21 ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 SIN GS0 GS0 GS0 GS0 GS0 BC BC BC BC BC BC BC BC GS15 GS15 GS15 GS15 4A 3A 2A 1B 0A 7A 6A 5A 4A 3A 2A 1A 0A 15B 14B 13B 12B SCLK 251 252 253 254 255 256 1 2 3 4 5 6 7 8 1 2 3 4 BCSEL Low level ('L') = Grayscale Register is selected High level ('H') = Brightness Register is selected XLAT 1 2 3 4 5 6 7 8 GSCLK BLANK Low level ('L') GS Shift Register Latest Grayscale Data (Internal) GSData Previous Grayscale Data Latest Grayscale Data 1st Latch (Internal) GSData Previous Grayscale Data Latest Grayscale Data 2nd Latch (Internal) BC Shift Register Previous Brightness Data Latest Brightness Data (Internal) BCData Previous Brightness Data Latest Brightness Data 1st Latch (Internal) BCData Previous Brightness Data (Bit 0-Bit 6) Latest Brightness Data (Bit 0-Bit 6) 2nd Latch (Internal) OFF OUTn PWM/Brightness Controlled by Previous Data PWM/Brightness Controlled by Latest Data ON SOUT GS0 GS0 GS0 GS0 GS0 GS15 BC BC BC BC BC BC BC BC BC GS15 GS15 GS15 GS15 GS15 4 3 2 1 0 15A 7 6 5 4 3 2 1 0 7A 15A 14A 13A 12A 11A WhentheBLANKinputoccursafterXLAT. Figure26.AutoRefreshDataFunctionTiming2 22 SubmitDocumentationFeedback Copyright©2007,TexasInstrumentsIncorporated ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 SIN GS0 GS0 GS0 GS0 GS0 BC BC BC BC BC BC BC BC GS15 GS15 GS15 GS15 4A 3A 2A 1B 0A 7A 6A 5A 4A 3A 2A 1A 0A 15B 14B 13B 12B SCLK 251 252 253 254 255 256 1 2 3 4 5 6 7 8 1 2 3 4 BCSEL Low level ('L') = Grayscale Register is selected High level ('H') = Brightness Register is selected XLAT 1 2 3 4 5 6 7 8 GSCLK BLANK Low level ('L') GS Shift Register Latest Grayscale Data (Internal) GSData Previous Grayscale Data Latest Grayscale Data 1st Latch (Internal) GSData Previous Grayscale Data Latest Grayscale Data 2nd Latch (Internal) BC Shift Register Previous Brightness Data Latest Brightness Data (Internal) BCData Previous Brightness Data Latest Brightness Data 1st Latch (Internal) BCData Previous Brightness Data (Bit 0-Bit 6) Latest Brightness Data (Bit 0-Bit 6) 2nd Latch (Internal) OFF OUTn PWM/Brightness Controlled by Previous Data PWM/Brightness Controlled by Latest Data ON SOUT GS0 GS0 GS0 GS0 GS0 GS15 BC BC BC BC BC BC BC BC BC GS15 BC GS15 GS15 GS15 GS15 GS15 4 3 2 1 0 15A 7 6 5 4 3 2 1 0 7A 15A 7A 15A 14A 13A 12A 11A WhentheBLANKinputoccurswithXLAT. Figure27.AutoRefreshDataFunctionTiming3 Copyright©2007,TexasInstrumentsIncorporated SubmitDocumentationFeedback 23 ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 Grayscale (GS) Shift Register and Data Latch The Grayscale (GS) Shift Register and data latch 1 and 2 are each 256 bits in length, and set the PWM timing for each constant current driver. See Table 4 for the ON time duty of each GS data bit. Figure 28 shows the shift register and latch configuration. Refer to Figure 11 for the timing diagram for writing data into the GS shift registerandlatch. The driver on time is controlled by the data in the GS second data latch. GS data can be set into the latch by the rising edge of XLAT with BCSEL = low after writing data into the GS shift register with SIN and GSCLK with BCSEL = low. A BCSEL level change occurs during SCLK = low, and after 100 ns from the rising edge of XLAT. When the device powers up, the data in the GS shift register and latches are not set to any default value. Therefore, GS data must be written to the GS latch before turning on the constant current output. Also, BLANK should be at a high level when powering on the device, because the constant current may be turned on as well. AllconstantcurrentoutputisoffwhenBLANKisatahighlevel. GS Data for OUT15 GS Data for OUT0 MSB LSB 255 240 239 16 15 0 SIN with GS Data ¼ GS Data GS Data ¼ GS Data GS Data ¼ GS Data BCSEL = low for Bit 15 for Bit 0 for Bit 15 for Bit 0 for Bit 15 for Bit 0 of OUT15 of OUT15 of OUT14 of OUT1 of OUT0 of OUT0 SCLK with BCSEL = low Grayscale Shift Register (16 Bits x 16 Channels) ¼ ¼ ¼ ¼ GS Data for OUT15 GS Data for OUT14 GS Data for OUT1 GS Data for OUT0 MSB LSB 255 240 239 16 15 0 GS Data ¼ GS Data GS Data ¼ GS Data GS Data ¼ GS Data XLAT with for Bit 15 for Bit 0 for Bit 15 for Bit 0 for Bit 15 for Bit 0 BCSEL = low of OUT15 of OUT15 of OUT14 of OUT1 of OUT0 of OUT0 Grayscale Data Latch 1 (16 Bits x 16 Channels) ¼ ¼ ¼ ¼ GS Data for OUT15 GS Data for OUT14 GS Data for OUT1 GS Data for OUT0 MSB LSB 255 240 239 16 15 0 65,536th GSCLK GS Data ¼ GS Data GS Data ¼ GS Data GS Data ¼ GS Data when Auto Repeat is for Bit 15 for Bit 0 for Bit 15 for Bit 0 for Bit 15 for Bit 0 enabled or Blank of OUT15 of OUT15 of OUT14 of OUT1 of OUT0 of OUT0 with BCSEL = low Grayscale Data Latch 2 (16 Bits x 16 Channels) 256 Bits To PWM Timing Control Block Figure28.GrayscaleShiftRegisterandDataLatchConfiguration 24 SubmitDocumentationFeedback Copyright©2007,TexasInstrumentsIncorporated ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 Brightness Control (BC) Shift Register and Data Latch The Brightness Control (BC) data shift register and the first latch are each 8 bits long; the second latch is 7 bits long. The lower 7 bits in the latch are used to adjust the constant current value for all channels of the constant current driver. The MSB of the first latch is used for the auto repeat mode setting. Table 5 shows the ratio of setting the current value against the maximum current value for each BC data point. Figure 29 shows the shift registerandlatchconfigurationforBCdata.Figure12showsthetimingforwritingdata. The driver constant current value is controlled by the data in the second BC data latch. BC data can be set into the latch at the rising edge of XLAT with BCSEL = high after writing the data into the BC Shift Register by SIN andSCLKwithBCSEL=high.ABCSELlevel change occurs during SCLK = low and after 100 ns from the rising edge of XLAT. When powered up, the data in the BC Shift Register and latches are not set to any default value. Therefore,brightnessdatamustbewrittentotheBClatchbeforeturningontheconstantcurrentoutput. Table5.BCDatavsCurrentRatio BCData(Dec) BCData(Lower7Bits;Hex) RatioofSettingCurrentValueAgainstMAXValue(%) 0 0 0 1 1 0.8 2 2 1.6 3 3 2.4 --- --- --- 125 7D 98.4 126 7E 99.2 127 7F 100 MSB LSB 7 6 5 4 3 2 1 0 Shift SIN with Data BCSEL = high SOUT Auto-Repeat BC Data BC Data BC Data BC Data BC Data BC Data BC Data 1 = Repeat for Bit 6 for Bit 5 for Bit 4 for Bit 3 for Bit 2 for Bit 1 for Bit 0 Shift SCLK with Clock BCSEL = high Brightness/Auto Repeat Control Shift Register (8 Bits) MSB LSB 7 6 5 4 3 2 1 0 Latch Auto-Repeat BC Data BC Data BC Data BC Data BC Data BC Data BC Data Signal XLAT rising edge with 1 = Repeat for Bit 6 for Bit 5 for Bit 4 for Bit 3 for Bit 2 for Bit 1 for Bit 0 BCSEL = high Brightness/Auto Repeat Control Data Latch 1 (8 Bits) MSB LSB 6 5 4 3 2 1 0 Latch BC Data BC Data BC Data BC Data BC Data BC Data BC Data Signal 6A5u,t5o3 R6ethp eGaSt CisL eKn wabhleend for Bit 6 for Bit 5 for Bit 4 for Bit 3 for Bit 2 for Bit 1 for Bit 0 or BLANK with BCSEL = high Brightness Control Data Latch 2 (7 Bits) 1 Bit 7 Bits To PWM Control Block To Constant Current Driver Figure29.BrightnessControlShiftRegisterandLatchConfiguration Copyright©2007,TexasInstrumentsIncorporated SubmitDocumentationFeedback 25 ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 Status Information Data (SID) Status information data (SID) are 17-bit, read-only data. Both the LED open detection (LOD) error and the thermal error flag (TEF) are shifted out onto the SOUT pin with each rising edge of the shift clock, SCLK. The 16 LOD bits for each channel and the TEF bit are written into the 17 most significant bits of the Grayscale Shift Register at the rising edge of the first SCLK after XLAT goes low. As a result, the previous data in the 17 most significant bits are lost at the same time. No data are loaded into the other 175 bits. Figure 30 shows the bit assignments.Figure13illustratesthereadtimingforthestatusinformationdata. Status Information Data (SID) Configuration LOD Data of OUT15 to OUT0 TEF (1 Bit) ¼ MSB LSB 16 15 2 1 0 ¼ OUT15 OUT14 OUT1 OUT0 TEF Data LOD Data LOD Data LOD Data LOD Data The 16 LOD bits for each channel and the TEF bit overwrite ¼ the most significant 17 bits of the Grayscale Shift Register at the rising edge of the firstSCLK after XLAT goes low. GS Data for OUT15 GS Data for OUT14-OUT1 GS Data for OUT0 MSB LSB 255 254 241 240 239 16 15 0 OUT15-Bit15 OUT15-Bit1 ¼ OUT15-Bit1 OUT15-Bit0 OUT14-Bit15 ¼ ¼ SIN SOUT OUT1-Bit0 OUT0-Bit15 OUT0-Bit0 (LOD-OUT15)(LOD-OUT14) (LOD-OUT1) (LOD-OUT0) (TEF) SCLK (BCSEL = low) Grayscale Shift Register (16 Bits´16 Channels) Figure30.StatusInformationDataConfiguration The LOD data update at the rising edge of the 33rd GSCLK pulse after BLANK goes low; the LOD data are retained until the next 33rd GSCLK. LOD data are only checked for outputs that are turned on during the rising edge of the 33rd GSCLK pulse. A '1' in an LOD bit indicates an open LED or short LED to GND condition for the corresponding channel. A '0' indicates normal operation. LOD shows a '0' even if the LED is open or shorted to GND when the grayscale data are less than 1000h (4096d). Therefore, grayscale data must be greater than 1001h(4097d)tocorrectlyreceiveLODdata. The TEF bit indicates that the IC temperature is too high. The flag also indicates that the IC has turned off all drivers to avoid damage by overheating the device. A '1' in the TEF bit means that the IC temperature has exceeded the detect temperature threshold (T ) and the driver is turned off. A '0' in the TEF bit indicates (TEF) normal operating temperature conditions. The IC automatically turns the drivers back on when the IC temperaturedecreasestolessthanT –T .WhentheICpowerson,LODdatadonotshowcorrect values. (TEF) (HYS) Therefore, LOD data must be read from the 33rd GSCLK pulse input after BLANK goes low. Table 6 shows a truthtableforbothLODandTEF. Table6.LODandTEFTruthTable CONDITION SIDDATA LEDOPENDETECTION(LODn) THERMALERRORFLAG(TEF) 0 LEDisconnected(V >V ) Devicetemperatureislow(temp≤T –T ) OUTn LOD (TEF) (HYS) 1 LEDisopenorshortedtoGND(V ≤V ) Devicetemperatureishigh(temp>T ) OUTn LOD (TEF) 26 SubmitDocumentationFeedback Copyright©2007,TexasInstrumentsIncorporated ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 Noise Reduction LargesurgecurrentsmayflowthroughtheICandtheprintedcircuitboard(PCB)onwhichthedeviceis mounted if all 16 LED channels turn on simultaneously at the start of each grayscale cycle. These large current surges could introduce detrimental noise and electromagnetic interference (EMI) into other circuits. The TLC5943 turns on the LED channels in a series delay to provide a circuit soft-start feature. The output current sinks are grouped into four groups of four channels each. The first group is OUT0,4,8,12; the second group is OUT1,5,9,13; the third group is OUT2,6,10,14; and the fourth group is OUT3,7,11,15. Each group is turns on sequentially with a smalldelaybetweengroups;seeFigure11.Bothturn-onandturn-offaredelayed. Continuous Base LED Open Detection When the 33rd GSCLK goes high in the first display period after a BLANK falling edge, the LED open detection (LOD) circuit checks the voltage of each constant current output (OUT0 through OUT15 = OUTn) that is turned on to detect open LEDs and short LEDs to GND. Then, if the voltage of OUTn is less than the LED open detection threshold (V = 0.3 V ), it sets '1' as the error flag to the LOD error bit that corresponds with the LOD TYP error channel in the Status Information Data (SID) register. Also, the XERR pin level moves from Hi-Z at the same time. As a result, GS data should be over 1001h (4097d) to get the LOD result. The OUTn channel that hasthedetectedLODerrorisforcedofftoavoidanincreasein the V supply current. OUTn turns on at the first CC GSCLK after a BLANK falling edge again. LOD data are kept until the next 33rd rising edge of GSCLK in the first display period after a BLANK falling edge. LOD is always '0' when grayscale data are less than 1001h (4097d). XERR is forced to a Hi-Z state while BLANK is high. When powered up, LOD data are not set to any default value. Therefore, SID data must be used after OUTn turns on with over 1001h GS data. Figure 31 shows the LEDOpenDetectiontiming. BLANK 65,53465,536 1 2 3 4 30 3132333435 65,53365,535 1 2 3 30 3132333435 GSCLK 1st GSCLK Period OUTn is turned off by Auto Off OFF function if LOD error is detected OUTn ON (Data = FFFFh) V If no LOD error is detected OUTn GND If the OUTn voltage (V ) is less than VLOD (0.3 V, typ) at the rising edge of the 33rd OUT GSCLK after the falling edge of BLANK, the LOD sets the SID bit corresponding to the output channel in which LED is open or shorted to GND equal to‘1. SID Register Value Old LED open detection data New LED open detection data (Internal) This LED Open Detection (LOD) data are kept until the next 33rd rising edge of GSCLK after BLANK goes low. 'Hi-Z’ If no LOD error is detected XERR Low Depends on LOD data Depends on previous ('L') If LOD error is detected LOD data Figure31.LEDOpenDetection(LOD)Timing Copyright©2007,TexasInstrumentsIncorporated SubmitDocumentationFeedback 27 ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 Auto Output Off If the active OUTn channel is not connected to an LED or if LED is shorted to GND, then V consumption CC current increases. In order to avoid this event, the device has an auto output off function. This function turns off channel OUTn with a detected LED opening or LED shorting to GND at the 33rd GSCLK after BLANK goes low automatically. V current can be saved by this function. OUTn is controlled normally again after BLANK goes CC low.Figure32illustratestheautooutputofffunction. VCC Dissipation Current BLANK 65,53465,536 1 2 3 4 303132333435 65,53365,535 1 2 3 303132333435 GSCLK OFF If LOD error is detected Voltage of ON OUTn V If no LOD error is detected OUTn GND SID Register Value Old LED open detection data New LED open detection data (Internal) Remain'On' (if no Remain'On' 'ON' LOD error detected) 'ON' (if no LOD error detected) ON Signal of OUTn (Internal) 'OFF' 'OFF' (GS data = FFFFh) Turn'Off' (OUTn is turned off Turn'Off' (OUTn is turned off by Auto Off function if LOD error by Auto Off function if LOD error is detected) is detected) Figure32.AutoOutputOffFunction 28 SubmitDocumentationFeedback Copyright©2007,TexasInstrumentsIncorporated ProductFolderLink(s):TLC5943

TLC5943 www.ti.com SBVS101–DECEMBER2007 Thermal Shutdown and Thermal Error Flag The Thermal Shutdown (TSD) function turns off all of the constant current outputs on the IC immediately when the junction temperature (T ) exceeds the threshold (T = +162(cid:176) C, typ) and sets the thermal error flag (TEF) J (TEF) to '1'. The XERR pin goes low at the same time. The XERR pin level and the TEF level are kept until the first SCLK falling edge after an XLAT falling edge of grayscale data. Then if T is still greater than T , TEF J (TEF) continues at '1' while XERR remains low. If T becomes less than T –T , TEF is set to '0' and XERR J (TEF) (HYS) becomes Hi-Z. XERR is not forced to a Hi-Z state while BLANK is high. Therefore, the error type TEF or LOD can be distinguished from the BLANK signal control. OUTn is turned on at the first GSCLK after the BLANK fallingedgeifT becomeslessthanT –T attheBLANKrisingedge. J (TEF) (HYS) When the IC powers on, TEF may be set and all output is forced off. Therefore, an XLAT pulse and a BLANK risingedgeshouldbeinputoncetoturnontheoutput.Figure33illustratestheTEF/TSD/XERRtimingsequence. BLANK XLAT SCLK 65,53465,536 1 2 3 4 65,53365,535 1 2 3 GSCLK TempeICra Jtuurnec (tiTon) TJ< T(TEF) TJ³T(TEF) TJ< T(TEF)-T(HYS) TJ³T(TEF) J '1' TEF '0' '0' (Internal) 'Hi-Z’ Low XERR ('L') OFF OFF OUTn ON Figure33.TEF/TSD/XERRtiming POWER DISSIPATION CALCULATION The device power dissipation must be below the power dissipation rate of the device package (illustrated in Figure15)toensurecorrectoperation.Equation4calculatesthepowerdissipationofthedevice: BCn P = (V ´I ) + V ´I ´N´ ´d D CC CC OUT MAX 127d PWM (4) Where: • V =devicesupplyvoltage CC • I =devicesupplycurrent CC • V =OUTnvoltagewhendrivingLEDcurrent OUT • I =LEDcurrentadjustedbyR resistor MAX (IREF) • BCn=maximumBCvalueforOUTn • N=numberofOUTndrivingLEDatthesametime • d =dutyratiodefinedbyBLANKpinorGSPWMvalue PWM Copyright©2007,TexasInstrumentsIncorporated SubmitDocumentationFeedback 29 ProductFolderLink(s):TLC5943

PACKAGE OPTION ADDENDUM www.ti.com 6-Feb-2020 PACKAGING INFORMATION Orderable Device Status Package Type Package Pins Package Eco Plan Lead/Ball Finish MSL Peak Temp Op Temp (°C) Device Marking Samples (1) Drawing Qty (2) (6) (3) (4/5) HPA00669PWPR ACTIVE HTSSOP PWP 28 2000 Green (RoHS NIPDAU Level-2-260C-1 YEAR -40 to 85 TLC5943 & no Sb/Br) TLC5943PWP ACTIVE HTSSOP PWP 28 50 Green (RoHS NIPDAU Level-2-260C-1 YEAR -40 to 85 TLC5943 & no Sb/Br) TLC5943PWPR ACTIVE HTSSOP PWP 28 2000 Green (RoHS NIPDAU Level-2-260C-1 YEAR -40 to 85 TLC5943 & no Sb/Br) TLC5943RHBR ACTIVE VQFN RHB 32 3000 Green (RoHS NIPDAU Level-2-260C-1 YEAR -40 to 85 TLC & no Sb/Br) 5943 TLC5943RHBT ACTIVE VQFN RHB 32 250 Green (RoHS NIPDAU Level-2-260C-1 YEAR -40 to 85 TLC & no Sb/Br) 5943 (1) The marketing status values are defined as follows: ACTIVE: Product device recommended for new designs. LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect. NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design. PREVIEW: Device has been announced but is not in production. Samples may or may not be available. OBSOLETE: TI has discontinued the production of the device. (2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free". RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption. Green: TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement. (3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature. (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device. (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device. (6) Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width. Addendum-Page 1

PACKAGE OPTION ADDENDUM www.ti.com 6-Feb-2020 Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release. In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis. Addendum-Page 2

PACKAGE MATERIALS INFORMATION www.ti.com 27-Jul-2013 TAPE AND REEL INFORMATION *Alldimensionsarenominal Device Package Package Pins SPQ Reel Reel A0 B0 K0 P1 W Pin1 Type Drawing Diameter Width (mm) (mm) (mm) (mm) (mm) Quadrant (mm) W1(mm) TLC5943PWPR HTSSOP PWP 28 2000 330.0 16.4 6.9 10.2 1.8 12.0 16.0 Q1 TLC5943RHBR VQFN RHB 32 3000 330.0 12.4 5.3 5.3 1.5 8.0 12.0 Q2 TLC5943RHBT VQFN RHB 32 250 180.0 12.4 5.3 5.3 1.5 8.0 12.0 Q2 PackMaterials-Page1

PACKAGE MATERIALS INFORMATION www.ti.com 27-Jul-2013 *Alldimensionsarenominal Device PackageType PackageDrawing Pins SPQ Length(mm) Width(mm) Height(mm) TLC5943PWPR HTSSOP PWP 28 2000 367.0 367.0 38.0 TLC5943RHBR VQFN RHB 32 3000 367.0 367.0 35.0 TLC5943RHBT VQFN RHB 32 250 210.0 185.0 35.0 PackMaterials-Page2

GENERIC PACKAGE VIEW RHB 32 VQFN - 1 mm max height 5 x 5, 0.5 mm pitch PLASTIC QUAD FLATPACK - NO LEAD Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details. 4224745/A www.ti.com

PACKAGE OUTLINE RHB0032E VQFN - 1 mm max height SCALE 3.000 PLASTIC QUAD FLATPACK - NO LEAD A 5.1 B 4.9 PIN 1 INDEX AREA 5.1 (0.1) 4.9 SIDE WALL DETAIL OPTIONAL ME20.000TAL THICKNESS C 1 MAX SEATING PLANE 0.05 0.00 0.08 C 2X 3.5 3.45 0.1 (0.2) TYP 9 16 EXPOSED THERMAL PAD 28X 0.5 8 17 SEE SIDE WALL DETAIL 2X 33 SYMM 3.5 0.3 32X 0.2 24 0.1 C A B 1 0.05 C 32 25 PIN 1 ID SYMM (OPTIONAL) 0.5 32X 0.3 4223442/B 08/2019 NOTES: 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance. www.ti.com

EXAMPLE BOARD LAYOUT RHB0032E VQFN - 1 mm max height PLASTIC QUAD FLATPACK - NO LEAD ( 3.45) SYMM 32 25 32X (0.6) 1 24 32X (0.25) (1.475) 28X (0.5) 33 SYMM (4.8) ( 0.2) TYP VIA 8 17 (R0.05) TYP 9 16 (1.475) (4.8) LAND PATTERN EXAMPLE SCALE:18X 0.07 MAX 0.07 MIN ALL AROUND ALL AROUND SOLDER MASK METAL OPENING SOLDER MASK METAL UNDER OPENING SOLDER MASK NON SOLDER MASK SOLDER MASK DEFINED DEFINED (PREFERRED) SOLDER MASK DETAILS 4223442/B 08/2019 NOTES: (continued) 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271). 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented. www.ti.com

EXAMPLE STENCIL DESIGN RHB0032E VQFN - 1 mm max height PLASTIC QUAD FLATPACK - NO LEAD 4X ( 1.49) (R0.05) TYP (0.845) 32 25 32X (0.6) 1 24 32X (0.25) 28X (0.5) (0.845) SYMM 33 (4.8) 8 17 METAL TYP 9 16 SYMM (4.8) SOLDER PASTE EXAMPLE BASED ON 0.125 mm THICK STENCIL EXPOSED PAD 33: 75% PRINTED SOLDER COVERAGE BY AREA UNDER PACKAGE SCALE:20X 4223442/B 08/2019 NOTES: (continued) 6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations. www.ti.com

GENERIC PACKAGE VIEW PWP 28 PowerPADTM TSSOP - 1.2 mm max height 4.4 x 9.7, 0.65 mm pitch SMALL OUTLINE PACKAGE Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details. 4224765/A www.ti.com

None

None

None

IMPORTANTNOTICEANDDISCLAIMER TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS. These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources. TI’s products are provided subject to TI’s Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI’s provision of these resources does not expand or otherwise alter TI’s applicable warranties or warranty disclaimers for TI products. Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated

Datasheet下载

Datasheet下载