- 型号: TLC3702MD

- 制造商: Texas Instruments

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

TLC3702MD产品简介:

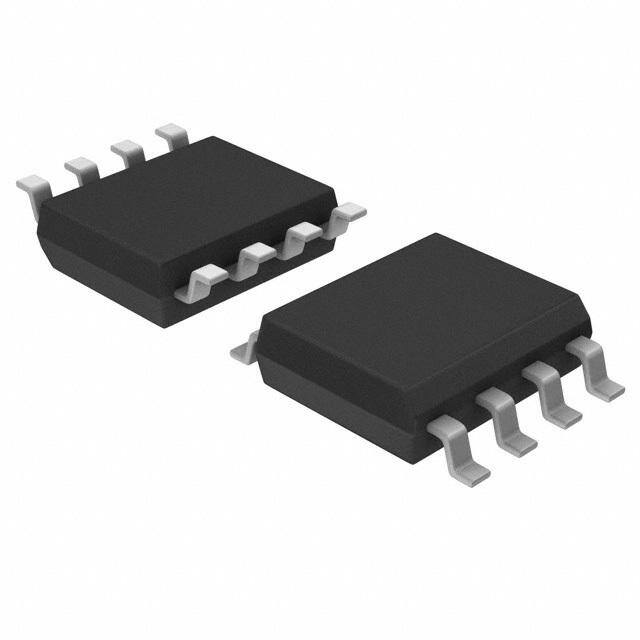

ICGOO电子元器件商城为您提供TLC3702MD由Texas Instruments设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 TLC3702MD价格参考。Texas InstrumentsTLC3702MD封装/规格:线性 - 比较器, 通用 比较器 CMOS,推挽式,TTL 8-SOIC。您可以下载TLC3702MD参考资料、Datasheet数据手册功能说明书,资料中有TLC3702MD 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC)半导体 |

| CMRR,PSRR(典型值) | 84dB CMRR |

| 描述 | IC DUAL MCPWR VOLT COMP 8-SOIC模拟比较器 Dual Voltage |

| 产品分类 | |

| 品牌 | Texas Instruments |

| 产品手册 | http://www.ti.com/litv/slcs013e |

| 产品图片 |

|

| rohs | 否含铅 / 不符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 校验器 IC,Texas Instruments TLC3702MDLinCMOS™ |

| 数据手册 | |

| 产品型号 | TLC3702MD |

| 产品 | Analog Comparators |

| 产品目录页面 | |

| 产品种类 | 模拟比较器 |

| 传播延迟(最大值) | 4.5µs |

| 供应商器件封装 | 8-SOIC |

| 偏转电压—最大值 | 5 mV |

| 元件数 | 2 |

| 其它名称 | 296-12188-5 |

| 包装 | 管件 |

| 单位重量 | 76 mg |

| 响应时间 | 2.7 us |

| 商标 | Texas Instruments |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装 | Tube |

| 封装/外壳 | 8-SOIC(0.154",3.90mm 宽) |

| 封装/箱体 | SOIC-8 |

| 工作温度 | -55°C ~ 125°C |

| 工厂包装数量 | 75 |

| 最大功率耗散 | 725 mW |

| 最大工作温度 | + 125 C |

| 最小工作温度 | - 55 C |

| 标准包装 | 75 |

| 滞后 | - |

| 电压-电源,单/双 (±) | 4 V ~ 16 V |

| 电压-输入失调(最大值) | 5mV @ 10V |

| 电流-输入偏置(最大值) | 5pA @ 5V |

| 电流-输出(典型值) | 20mA |

| 电流-静态(最大值) | 90µA |

| 电源电压-最大 | 16 V |

| 电源电压-最小 | 4 V |

| 电源电流 | 40 uA |

| 电源电流—最大值 | 40 uA |

| 类型 | 通用 |

| 系列 | TLC3702M |

| 输入偏压电流—最大 | 0.6 nA |

| 输出电流—典型值 | 8 mA |

| 输出类型 | CMOS,推挽式,TTL |

| 通道数量 | 2 Channel |

PDF Datasheet 数据手册内容提取

TLC3702 ™ DUAL MICROPOWER LinCMOS VOLTAGE COMPARATORS SLCS013E − NOVEMBER 1986 − REVISED MARCH 2012 (cid:2) Push-Pull CMOS Output Drives Capacitive D, JG, OR P PACKAGE (TOP VIEW) Loads Without Pullup Resistor, I = ± 8 mA O (cid:2) Very Low Power...100 μW Typ at 5 V 1OUT 1 8 VDD 1IN− 2 7 2OUT (cid:2) Fast Response Time...tPLH = 2.7 μs Typ 1IN+ 3 6 2IN− With 5-mV Overdrive GND 4 5 2IN+ (cid:2) Single-Supply Operation...3 V to 16 V TLC3702M...4 V to 16 V (cid:2) On-Chip ESD Protection FK PACKAGE (TOP VIEW) description T U D C O C DC The TLC3702 consists of two independent N 1 NV N micropower voltage comparators designed to 3 2 1 20 19 operate from a single supply and be compatible NC 4 18 NC with modern HCMOS logic systems. They are 1IN− 5 17 2OUT functionally similar to the LM339 but use one- NC 6 16 NC twentieth of the power for similar response times. 1IN+ 7 15 2IN− The push-pull CMOS output stage drives NC 8 14 NC 9 10 11 12 13 capacitive loads directly without a power- consuming pullup resistor to achieve the stated C D C +C response time. Eliminating the pullup resistor not N N N NN G 2I only reduces power dissipation, but also saves board space and component cost. The output NC − No internal connection stage is also fully compatible with TTL requirements. symbol (each comparator) Texas Instruments LinCMOS™ process offers superior analog performance to standard CMOS IN+ processes. Along with the standard CMOS OUT advantages of low power without sacrificing IN− speed, high input impedance, and low bias currents, the LinCMOS™ process offers extremely stable input offset voltages with large differential input voltages. This characteristic makes it possible to build reliable CMOS comparators. The TLC3702C is characterized for operation over the commercial temperature range of 0°C to 70°C. The TLC3702I is characterized for operation over the extended industrial temperature range of −40°C to 85°C. The TLC3702M is characterized for operation over the full military temperature range of −55°C to 125°C. Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet. LinCMOS is a trademark of Texas Instruments Incorporated. PRODUCTION DATA information is current as of publication date. Copyright © 1998, Texas Instruments Incorporated Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters. • POST OFFICE BOX 655303 DALLAS, TEXAS 75265 1

TLC3702 ™ DUAL MICROPOWER LinCMOS VOLTAGE COMPARATORS SLCS013E − NOVEMBER 1986 − REVISED MARCH 2012 AVAILABLE OPTIONS PACKAGES TA VVatIO 2mm5°aaCxx SMALL OUTLINE CERAMIC CERAMIC DIP PLASTIC DIP (D) (FK) (JG) (P) 0°C to 70°C 5 mV TLC3702CD — — TLC3702CP −40°C to 85°C 5 mV TLC3702ID — — TLC3702IP −55°C to 125°C 5 mV TLC3702MD TLC3702MFK TLC3702MJG — The D package is available taped and reeled. Add R suffix to the device type (e.g., TLC3702CDR). functional block diagram (each comparator) VDD IN+ Differential Input OUT Circuits IN− GND absolute maximum ratings over operating free-air temperature range (unless otherwise noted)† Supply voltage range, V (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −0.3 V to 18 V DD Differential input voltage, V (see Note 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±18 V ID Input voltage range, V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −0.3 V to V I DD Output voltage range, V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . − 0.3 V to V O DD Input current, I . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±5 mA I Output current, I (each output) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±20 mA O Total supply current into V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40 mA DD Total current out of GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40 mA Continuous total power dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . See Dissipation Rating Table Operating free-air temperature range, T : TLC3702C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0°C to 70°C A TLC3702I . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −40°C to 85°C TLC3702M . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −55°C to 125°C Storage temperature range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −65°C to 150°C Case temperature for 60 seconds: FK package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260°C Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: D or P package . . . . . . . . . . . . . . . . . 260°C Lead temperature 1,6 mm (1/16 inch) from case for 60 seconds: JG package . . . . . . . . . . . . . . . . . . . . 300°C †Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. NOTES: 1. All voltage values, except differential voltages, are with respect to network ground. 2. Differential voltages are at IN+ with respect to IN−. • 2 POST OFFICE BOX 655303 DALLAS, TEXAS 75265

TLC3702 ™ DUAL MICROPOWER LinCMOS VOLTAGE COMPARATORS SLCS013E − NOVEMBER 1986 − REVISED MARCH 2012 DISSIPATION RATING TABLE PACKAGE POWTAE R≤ 2R5A°CTING DAEBROATVIEN GTA F =A C25T°OCR POWTAE R= 7R0A°TCING POWTAE R= 8R5A°TCING POTWAE =R 1 R25A°TCING D 725 mW 5.8 mW/°C 464 mW 377 mW 145 mW FK 1375 mW 11.0 mW/°C 880 mW 715 mW 275 mW JG 1050 mW 8.4 mW/°C 672 mW 546 mW 210 mW P 1000 mW 8.0 mW/°C 640 mW 520 mW N/A recommended operating conditions TLC3702C UUNNIITT MIN NOM MAX Supply voltage, VDD 3 5 16 V Common-mode input voltage, VIC − 0.2 VDD − 1.5 V High-level output current, IOH −20 mA Low-level output current, IOL 20 mA Operating free-air temperature, TA 0 70 °C electrical characteristics at specified operating free-air temperature, V = 5 V (unless otherwise DD noted) TLC3702C PPAARRAAMMEETTEERR TTEESSTT CCOONNDDIITTIIOONNSS†† TTA MIN TYP MAX UUNNIITT VDD = 5 V to 10 V, 25°C 1.2 5 VVIO IInnppuutt ooffffsseett vvoollttaaggee VVSeICe = N VVoItCeR 3mmiinn, 0°C to 70°C 6.5 mmVV 25°C 1 pA IIIO IInnppuutt ooffffsseett ccuurrrreenntt VVIC = 22.55 VV 70°C 0.3 nA 25°C 5 pA IIIB IInnppuutt bbiiaass ccuurrrreenntt VVIC = 22.55 VV 70°C 0.6 nA 25°C 0 to VDD − 1 VVICR CCoommmmoonn-mmooddee iinnppuutt vvoollttaaggee rraannggee 0°C to 70°C 0 to VDD − 1.5 VV 25°C 84 CCMMRRRR CCoommmmoonn-mmooddee rreejjeeccttiioonn rraattiioo VVIICC = VVIICCRRmmiinn 70°C 84 ddBB 0°C 84 25°C 85 kkSSVVRR SSuuppppllyy-vvoollttaaggee rreejjeeccttiioonn rraattiioo VVDDDD = 55 VV ttoo 1100 VV 70°C 85 ddBB 0°C 85 VVOH HHiigghh-lleevveell oouuttppuutt vvoollttaaggee VVIOIIDDH === −11 4VV ,,mA 2750°°CC 44..53 4.7 VV VVOL LLooww-lleevveell oouuttppuutt vvoollttaaggee VVIOIIDDH === −411 m VVA,, 2750°°CC 210 330705 mmVV 25°C 18 40 IIDD SSuuppppllyy ccuurrrreenntt ((bbootthh ccoommppaarraattoorrss)) OOuuttppuuttss llooww, NNoo llooaadd 0°C to 70°C 50 μμAA †All characteristics are measured with zero common-mode voltage unless otherwise noted. NOTE 3: The offset voltage limits given are the maximum values required to drive the output up to 4.5 V or down to 0.3 V. • POST OFFICE BOX 655303 DALLAS, TEXAS 75265 3

TLC3702 ™ DUAL MICROPOWER LinCMOS VOLTAGE COMPARATORS SLCS013E − NOVEMBER 1986 − REVISED MARCH 2012 recommended operating conditions TLC3702I UUNNIITT MIN NOM MAX Supply voltage, VDD 3 5 16 V Common-mode input voltage, VIC −0.2 VDD − 1.5 V High-level output current, IOH −20 mA Low-level output current, IOL 20 mA Operating free-air temperature, TA −40 85 °C electrical characteristics at specified operating free-air temperature, V = 5 V (unless otherwise DD noted) TLC3702I PPAARRAAMMEETTEERR TTEESSTT CCOONNDDIITTIIOONNSS†† TTA MIN TYP MAX UUNNIITT VVIO IInnppuutt ooffffsseett vvoollttaaggee VVVDDICDD = == V 55IC VVR mttooi n11,00 SVVe,,e Note 3 −40°C25 t°oC 85°C 1.2 57 mmVV 25°C 1 pA IIIO IInnppuutt ooffffsseett ccuurrrreenntt VVIC = 22.55 VV 85°C 1 nA 25°C 5 pA IIIB IInnppuutt bbiiaass ccuurrrreenntt VVIC = 22.55 VV 85°C 2 nA 0 to 25°C VDD − 1 VVICR CCoommmmoonn-mmooddee iinnppuutt vvoollttaaggee rraannggee 0 to VV −40°C to 85°C VDD − 1.5 25°C 84 CCMMRRRR CCoommmmoonn-mmooddee rreejjeeccttiioonn rraattiioo VVIICC = VVIICCRRmmiinn 85°C 84 ddBB −40°C 83 25°C 85 kkSSVVRR SSuuppppllyy-vvoollttaaggee rreejjeeccttiioonn rraattiioo VVDDDD = 55 VV ttoo 1100 VV 85°C 85 ddBB −40°C 83 25°C 4.5 4.7 VVOH HHiigghh-lleevveell oouuttppuutt vvoollttaaggee VVID = 11 VV, IIOH = −44 mmAA 85°C 4.3 VV 25°C 210 300 VVOL LLooww-lleevveell oouuttppuutt vvoollttaaggee VVID = −11 VV, IIOH = −44 mmAA 85°C 400 mmVV 25°C 18 40 IIDD SSuuppppllyy ccuurrrreenntt ((bbootthh ccoommppaarraattoorrss)) OOuuttppuuttss llooww, NNoo llooaadd −40°C to 85°C 65 μμAA †All characteristics are measured with zero common-mode voltage unless otherwise noted. NOTE 3. The offset voltage limits given are the maximum values required to drive the output up to 4.5 V or down to 0.3 V. • 4 POST OFFICE BOX 655303 DALLAS, TEXAS 75265

TLC3702 ™ DUAL MICROPOWER LinCMOS VOLTAGE COMPARATORS SLCS013E − NOVEMBER 1986 − REVISED MARCH 2012 recommended operating conditions TLC3702M UUNNIITT MIN NOM MAX Supply voltage, VDD 4 5 16 V Common-mode input voltage, VIC 0 VDD − 1.5 V High-level output current, IOH − 20 mA Low-level output current, IOL 20 mA Operating free-air temperature, TA − 55 125 °C electrical characteristics at specified operating free-air temperature, V = 5 V (unless otherwise DD noted) TLC3702M PPAARRAAMMEETTEERR TTEESSTT CCOONNDDIITTIIOONNSS†† TTA MIN TYP MAX UUNNIITT VVIO IInnppuutt ooffffsseett vvoollttaaggee VVVDDICDD = == V 55IC VVR mttooi n11,00 SVVe,,e Note 3 −55°C2 t5o° 1C25°C 1.2 150 mmVV 25°C 1 pA IIIO IInnppuutt ooffffsseett ccuurrrreenntt VVIC = 22.55 VV 125°C 15 nA 25°C 5 pA IIIB IInnppuutt bbiiaass ccuurrrreenntt VVIC = 22.55 VV 125°C 30 nA 0 to 25°C VDD − 1 VVICR CCoommmmoonn-mmooddee iinnppuutt vvoollttaaggee rraannggee 0 to VV −55°C to 125°C VDD − 1.5 25°C 84 CCMMRRRR CCoommmmoonn-mmooddee rreejjeeccttiioonn rraattiioo VVIICC = VVIICCRRmmiinn 125°C 83 ddBB −55°C 82 25°C 85 kkSSVVRR SSuuppppllyy-vvoollttaaggee rreejjeeccttiioonn rraattiioo VVDDDD = 55 VV ttoo 1100 VV 125°C 85 ddBB − 55°C 82 25°C 4.5 4.7 VVOH HHiigghh-lleevveell oouuttppuutt vvoollttaaggee VVID = 11 VV, IIOH = −44 mmAA 125°C 4.2 VV 25°C 210 300 VVOL LLooww-lleevveell oouuttppuutt vvoollttaaggee VVID = −11 VV, IIOH = −44 mmAA 125°C 500 mmVV 25°C 18 40 IIDD SSuuppppllyy ccuurrrreenntt ((bbootthh ccoommppaarraattoorrss)) OOuuttppuuttss llooww, NNoo llooaadd −55°C to 125°C 90 μμAA †All characteristics are measured with zero common-mode voltage unless otherwise noted. NOTE 3. The offset voltage limits given are the maximum values required to drive the output up to 4.5 V or down to 0.3 V. • POST OFFICE BOX 655303 DALLAS, TEXAS 75265 5

TLC3702 ™ DUAL MICROPOWER LinCMOS VOLTAGE COMPARATORS SLCS013E − NOVEMBER 1986 − REVISED MARCH 2012 switching characteristics, V = 5 V, T = 25°C DD A TLC3702C, TLC3702I PPAARRAAMMEETTEERR TTEESSTT CCOONNDDIITTIIOONNSS TLC3702M UUNNIITT MIN TYP MAX Overdrive = 2 mV 4.5 Overdrive = 5 mV 2.7 ff = 1100 kkHHz, ttPPLLHH PPrrooppaaggaattiioonn ddeellaayy ttiimmee,, llooww-ttoo-hhiigghh-lleevveell oouuttppuutt† CCLL == 5500 ppFF Overdrive = 10 mV 1.9 μμss Overdrive = 20 mV 1.4 Overdrive = 40 mV 1.1 VI = 1.4 V step at IN+ 1.1 Overdrive = 2 mV 4 Overdrive = 5 mV 2.3 ff = 1100 kkHHz, ttPPHHLL PPrrooppaaggaattiioonn ddeellaayy ttiimmee,, hhiigghh-ttoo-llooww-lleevveell oouuttppuutt† CCLL == 5500 ppFF Overdrive = 10 mV 1.5 μμss Overdrive = 20 mV 0.95 Overdrive = 40 mV 0.65 VI = 1.4 V step at IN+ 0.15 f = 10 kHz, tf Fall time CL = 50 pF Overdrive = 50 mV 50 ns f = 10 kHz, tr Rise time CL = 50 pF Overdrive = 50 mV 125 ns †Simultaneous switching of inputs causes degradation in output response. • 6 POST OFFICE BOX 655303 DALLAS, TEXAS 75265

TLC3702 ™ DUAL MICROPOWER LinCMOS VOLTAGE COMPARATORS SLCS013E − NOVEMBER 1986 − REVISED MARCH 2012 PRINCIPLES OF OPERATION LinCMOS™process The LinCMOS™ process is a linear polysilicon-gate CMOS process. Primarily designed for single-supply applications, LinCMOS™ products facilitate the design of a wide range of high-performance analog functions from operational amplifiers to complex mixed-mode converters. While digital designers are experienced with CMOS, MOS technologies are relatively new for analog designers. This short guide is intended to answer the most frequently asked questions related to the quality and reliability of LinCMOS™ products. Further questions should be directed to the nearest TI field sales office. electrostatic discharge CMOS circuits are prone to gate oxide breakdown when exposed to high voltages even if the exposure is only for very short periods of time. Electrostatic discharge (ESD) is one of the most common causes of damage to CMOS devices. It can occur when a device is handled without proper consideration for environmental electrostatic charges, e.g., during board assembly. If a circuit in which one amplifier from a dual op amp is being used and the unused pins are left open, high voltages tend to develop. If there is no provision for ESD protection, these voltages may eventually punch through the gate oxide and cause the device to fail. To prevent voltage buildup, each pin is protected by internal circuitry. Standard ESD-protection circuits safely shunt the ESD current by providing a mechanism whereby one or more transistors break down at voltages higher than the normal operating voltages but lower than the breakdown voltage of the input gate. This type of protection scheme is limited by leakage currents which flow through the shunting transistors during normal operation after an ESD voltage has occurred. Although these currents are small, on the order of tens of nanoamps, CMOS amplifiers are often specified to draw input currents as low as tens of picoamps. To overcome this limitation, TI design engineers developed the patented ESD-protection circuit shown in Figure 1. This circuit can withstand several successive 2-kV ESD pulses, while reducing or eliminating leakage currents that may be drawn through the input pins. A more detailed discussion of the operation of the TI ESD-protection circuit is presented on the next page. All input and output pins on LinCMOS™ and Advanced LinCMOS™ products have associated ESD-protection circuitry that undergoes qualification testing to withstand 2000 V discharged from a 100-pF capacitor through a 1500-Ω resistor (human body model) and 200 V from a 100-pF capacitor with no current-limiting resistor (charged device model). These tests simulate both operator and machine handling of devices during normal test and assembly operations. VDD R1 Input To Protect Circuit R2 Q1 Q2 D1 D2 D3 GND Figure 1. LinCMOS™ ESD-Protection Schematic LinCMOS and Advanced LinCMOS are trademarks of Texas Instruments Incorporated. • POST OFFICE BOX 655303 DALLAS, TEXAS 75265 7

TLC3702 ™ DUAL MICROPOWER LinCMOS VOLTAGE COMPARATORS SLCS013E − NOVEMBER 1986 − REVISED MARCH 2012 PRINCIPLES OF OPERATION input protection circuit operation Texas Instruments patented protection circuitry allows for both positive- and negative-going ESD transients. These transients are characterized by extremely fast rise times and usually low energies, and can occur both when the device has all pins open and when it is installed in a circuit. positive ESD transients Initial positive charged energy is shunted through Q1 to V . Q1 turns on when the voltage at the input rises SS above the voltage on the V pin by a value equal to the V of Q1. The base current increases through R2 DD BE with input current as Q1 saturates. The base current through R2 forces the voltage at the drain and gate of Q2 to exceed its threshold level (V ∼ 22 to 26 V) and turn Q2 on. The shunted input current through Q1 to V is T SS now shunted through the n-channel enhancement-type MOSFET Q2 to V . If the voltage on the input pin SS continues to rise, the breakdown voltage of the zener diode D3 is exceeded and all remaining energy is dissipated in R1 and D3. The breakdown voltage of D3 is designed to be 24 V to 27 V, which is well below the gate-oxide voltage of the circuit to be protected. negative ESD transients The negative charged ESD transients are shunted directly through D1. Additional energy is dissipated in R1 and D2 as D2 becomes forward biased. The voltage seen by the protected circuit is −0.3 V to −1 V (the forward voltage of D1 and D2). circuit-design considerations LinCMOS™ products are being used in actual circuit environments that have input voltages that exceed the recommended common-mode input voltage range and activate the input protection circuit. Even under normal operation, these conditions occur during circuit power up or power down, and in many cases, when the device is being used for a signal conditioning function. The input voltages can exceed V and not damage the device ICR only if the inputs are current limited. The recommended current limit shown on most product data sheets is ±5 mA. Figure 2 and Figure 3 show typical characteristics for input voltage versus input current. Normal operation and correct output state can be expected even when the input voltage exceeds the positive supply voltage. Again, the input current should be externally limited even though internal positive current limiting is achieved in the input protection circuit by the action of Q1. When Q1 is on, it saturates and limits the current to approximately 5-mA collector current by design. When saturated, Q1 base current increases with input current. This base current is forced into the V pin and into the device I or the V supply through R2 DD DD DD producing the current limiting effects shown in Figure 2. This internal limiting lasts only as long as the input voltage is below the V of Q2. T When the input voltage exceeds the negative supply voltage, normal operation is affected and output voltage states may not be correct. Also, the isolation between channels of multiple devices (duals and quads) can be severely affected. External current limiting must be used since this current is directly shunted by D1 and D2 and no internal limiting is achieved. If normal output voltage states are required, an external input voltage clamp is required (see Figure 4). • 8 POST OFFICE BOX 655303 DALLAS, TEXAS 75265

TLC3702 ™ DUAL MICROPOWER LinCMOS VOLTAGE COMPARATORS SLCS013E − NOVEMBER 1986 − REVISED MARCH 2012 PRINCIPLES OF OPERATION circuit-design considerations (continued) INPUT CURRENT INPUT CURRENT vs vs POSITIVE INPUT VOLTAGE NEGATIVE INPUT VOLTAGE 8 −10 TA = 25° C TA = 25° C −9 7 −8 6 A A −7 m m − 5 − nt nt −6 e e r r ur 4 ur −5 C C ut ut −4 p 3 p n n − I − I −3 II 2 II −2 1 −1 0 −0 VDD VDD + 4 VDD + 8 VDD + 12 −0.3 −0.5 −0.7 −0.9 VI − Input Voltage − V VI − Input Voltage − V Figure 2 Figure 3 VDD RI PositiveVoltageInputCurrentLimit: VI + 1/2 V (cid:3)V (cid:3)0.3V TLC3702 R (cid:2) I DD I 5mA Vref − NegativeVoltageInputCurrentLimit: (cid:3)V (cid:3)V (cid:3)((cid:3)0.3V) R (cid:2) I DD I 5mA See Note A NOTE A: If the correct input state is required when the negative input exceeds GND, a Schottky clamp is required. Figure 4. Typical Input Current-Limiting Configuration for a LinCMOS™ Comparator • POST OFFICE BOX 655303 DALLAS, TEXAS 75265 9

TLC3702 ™ DUAL MICROPOWER LinCMOS VOLTAGE COMPARATORS SLCS013E − NOVEMBER 1986 − REVISED MARCH 2012 PARAMETER MEASUREMENT INFORMATION The TLC3702 contains a digital output stage which, if held in the linear region of the transfer curve, can cause damage to the device. Conventional operational amplifier/comparator testing incorporates the use of a servo loop which is designed to force the device output to a level within this linear region. Since the servo-loop method of testing cannot be used, we offer the following alternatives for measuring parameters such as input offset voltage, common-mode rejection, etc. To verify that the input offset voltage falls within the limits specified, the limit value is applied to the input as shown in Figure 5(a). With the noninverting input positive with respect to the inverting input, the output should be high. With the input polarity reversed, the output should be low. A similar test can be made to verify the input offset voltage at the common-mode extremes. The supply voltages can be slewed to provide greater accuracy, as shown in Figure 5(b) for the V test. This slewing is done instead ICR of changing the input voltages. A close approximation of the input offset voltage can be obtained by using a binary search method to vary the differential input voltage while monitoring the output state. When the applied input voltage differential is equal, but opposite in polarity, to the input offset voltage, the output changes states. Figure 6 illustrates a practical circuit for direct dc measurement of input offset voltage that does not bias the comparator in the linear region. The circuit consists of a switching mode servo loop in which IC1a generates a triangular waveform of approximately 20-mV amplitude. IC1b acts as a buffer, with C2 and R4 removing any residual dc offset. The signal is then applied to the inverting input of the comparator under test, while the noninverting input is driven by the output of the integrator formed by IC1c through the voltage divider formed by R8 and R9. The loop reaches a stable operating point when the output of the comparator under test has a duty cycle of exactly 50%, which can only occur when the incoming triangle wave is sliced symmetrically or when the voltage at the noninverting input exactly equals the input offset voltage. Voltage dividers R8 and R9 provide an increase in input offset voltage by a factor of 100 to make measurement easier. The values of R5, R7, R8, and R9 can significantly influence the accuracy of the reading; therefore, it is suggested that their tolerance level be one percent or lower. Measuring the extremely low values of input current requires isolation from all other sources of leakage current and compensation for the leakage of the test socket and board. With a good picoammeter, the socket and board leakage can be measured with no device in the socket. Subsequently, this open socket leakage value can be subtracted from the measurement obtained with a device in the socket to obtain the actual input current of the device. 5 V 1 V + + Applied VIO − Applied VIO − Limit VO Limit VO − 4 V (a) VIO WITH VIC = 0 V (b) VIO WITH VIC = 4 V Figure 5. Method for Verifying That Input Offset Voltage Is Within Specified Limits • 10 POST OFFICE BOX 655303 DALLAS, TEXAS 75265

TLC3702 ™ DUAL MICROPOWER LinCMOS VOLTAGE COMPARATORS SLCS013E − NOVEMBER 1986 − REVISED MARCH 2012 PARAMETER MEASUREMENT INFORMATION VDD C3 R5 0.68 μF IC1a 1.8 kΩ 1% 1/4 TLC274CN C2 + Buffer 1 μF 1/4 TLICC12c74CN R6 − 1 MΩ − DUT − R4 + VIO 47 kΩ (X100) + R7 Integrator R1 1.8 kΩ 1% 240 kΩ IC1b C4 1/4 TLC274CN 0.1 μF − C1 0.1 μF + Triangle Generator R8 R9 10 kΩ 1% 100 Ω 1% R2 10 kΩ R3 100 Ω Figure 6. Circuit for Input Offset Voltage Measurement Response time is defined as the interval between the application of an input step function and the instant when the output reaches 50% of its maximum value. Response time for the low-to-high-level output is measured from the leading edge of the input pulse, while response time for the high-to-low-level output is measured from the trailing edge of the input pulse. Response time measurement at low input signal levels can be greatly affected by the input offset voltage. The offset voltage should be balanced by the adjustment at the inverting input as shown in Figure 7, so that the circuit is just at the transition point. A low signal, for example 105-mV or 5-mV overdrive, causes the output to change state. • POST OFFICE BOX 655303 DALLAS, TEXAS 75265 11

TLC3702 ™ DUAL MICROPOWER LinCMOS VOLTAGE COMPARATORS SLCS013E − NOVEMBER 1986 − REVISED MARCH 2012 PARAMETER MEASUREMENT INFORMATION VDD Pulse 1 μF Generator 50 Ω + 1 V DUT 10 Ω 10-Turn − CL Potentiometer 1 kΩ (see Note A) 0.1 μF − 1 V TEST CIRCUIT Overdrive Overdrive Input 100 mV Input 100 mV 90% 90% Low-to-High High-to-Low Level Output 50% Level Output 50% 10% 10% tr tf tPLH tPHL VOLTAGE WAVEFORMS NOTE A: CL includes probe and jig capacitance. Figure 7. Response, Rise, and Fall Times Circuit and Voltage Waveforms • 12 POST OFFICE BOX 655303 DALLAS, TEXAS 75265

TLC3702 ™ DUAL MICROPOWER LinCMOS VOLTAGE COMPARATORS SLCS013E − NOVEMBER 1986 − REVISED MARCH 2012 TYPICAL CHARACTERISTICS† Table of Graphs FIGURE VIO Input offset voltage Distribution 8 IIB Input bias current vs Free-air temperature 9 CMRR Common-mode rejection ratio vs Free-air temperature 10 kSVR Supply-voltage rejection ratio vs Free-air temperature 11 vvss FFrreeee-aaiirr tteemmppeerraattuurree 1122 VVOH HHiigghh-lleevveell oouuttppuutt ccuurrrreenntt vs High-level output current 13 vvss LLooww-lleevveell oouuttppuutt ccuurrrreenntt 1144 VVOL LLooww-lleevveell oouuttppuutt vvoollttaaggee vs Free-air temperature 15 tt Transition time vs Load capacitance 16 Supply current response vs Time 17 Low-to-high-level output response Low-to-high level output propagation delay time 18 High-to-low level output response High-to-low level output propagation delay time 19 tPLH Low-to-high level output propagation delay time vs Supply voltage 20 tPHL High-to-low level output propagation delay time vs Supply voltage 21 vvss FFrreeqquueennccyy 2222 IIDDDD SSuuppppllyy ccuurrrreenntt vvss SSuuppppllyy vvoollttaaggee 2233 vs Free-air temperature 24 INPUT BIAS CURRENT DISTRIBUTION OF INPUT vs FREE-AIR TEMPERATURE OFFSET VOLTAGE 200 10 VDD = 5 V ÉÉ VDD = 5 V 180 VTAIC = = 2 25.°5 CV ÉÉ VIC = 2.5 V 160 6F9ro8m U n4i tWs aTfeesrt Ledots ÉÉÇ nA 1 − s 140 ÉÉÇ nt Unit 120 ÉÉÇ urre r of 100 ÉÉÇ as C 0.1 be ÉÇÉÇ Bi m 80 ut Nu ÉÇÉÇ np 60 − I ÇÇÉÉÇÉÇÉÉ B 0.01 II 40 ÇÇÉÉÇÉÇÉÇÉÉ 20 ÇÇÇÉÇÉÉÇÉÇÉÇÉÇÉÇ ÇÇÉÇÇÇÉÇÉÉÇÉÇÉÇÉÇÉÇÉÇÉÇ 0 0.001 −5 −4 −3 −2 −1 0 1 2 3 4 5 25 50 75 100 125 VIO − Input Offset Voltage − mV TA − Free-Air Temperature − °C Figure 8 Figure 9 †Data at high and low temperatures are applicable only within the rated operating free-air temperature ranges of the various devices. • POST OFFICE BOX 655303 DALLAS, TEXAS 75265 13

TLC3702 ™ DUAL MICROPOWER LinCMOS VOLTAGE COMPARATORS SLCS013E − NOVEMBER 1986 − REVISED MARCH 2012 TYPICAL CHARACTERISTICS† COMMON-MODE REJECTION RATIO SUPPLY VOLTAGE REJECTION RATIO vs vs FREE-AIR TEMPERATURE FREE-AIR TEMPERATURE 90 90 B d B Ratio − 8886 VDD = 5 V atio − d 8886 VDD = 5 V to 10 V ection 84 ction R 84 Rej 82 eje 82 ode 80 ge R 80 on-M 78 Volta 78 m y Com 76 Suppl 76 R − 74 − R 74 R V M 72 S 72 C k 70 70 −75 −50 −25 0 25 50 75 100 125 −75 −50 −25 0 25 50 75 100 125 TA − Free-Air Temperature − °C TA − Free-Air Temperature − °C Figure 10 Figure 11 HIGH-LEVEL OUTPUT VOLTAGE HIGH-LEVEL OUTPUT VOLTAGE vs vs FREE-AIR TEMPERATURE HIGH-LEVEL OUTPUT CURRENT 5 VDD VDD = 5 V V V 4.95 IOH = − 4 mA e − −0.25 VDD = 16 V − g ge 4.9 olta a V −0.5 Volt 4.85 put out 4.8 Out −0.75 10 V el Out 4.75 Level −1 h-Lev 4.7 nput −1.25 5 V Hig 4.65 gh-I − Hi −1.5 4 V OH 4.6 − H V 4.55 VO −1.75 TA = 25° C 3 V 4.5 −2 −75 −50 −25 0 25 50 75 100 125 0 −2.5 −5 −7.5 −10 −12.5 −15 −17.5 −20 TA − Free-Air Temperature − °C IOH − High-Level Output Current − mA Figure 12 Figure 13 †Data at high and low temperatures are applicable only within the rated operating free-air temperature ranges of the various devices. • 14 POST OFFICE BOX 655303 DALLAS, TEXAS 75265

TLC3702 ™ DUAL MICROPOWER LinCMOS VOLTAGE COMPARATORS SLCS013E − NOVEMBER 1986 − REVISED MARCH 2012 TYPICAL CHARACTERISTICS† LOW-LEVEL OUTPUT VOLTAGE LOW-LEVEL OUTPUT VOLTAGE vs vs LOW-LEVEL OUTPUT CURRENT FREE-AIR TEMPERATURE 1.5 400 TA = 25°C 3 V VDD = 5 V − V 1.25 4 V mV 350 IOL = 4 mA ge − a e olt ag 300 ut V 1 5 V Volt el Outp 0.75 Output 225000 ev el L 10 V v Low- 0.5 w-Le 150 − OL − Lo 100 V 0.25 VDD = 16 V OL V 50 0 0 0 2 4 6 8 10 12 14 16 18 20 −75 −50 −25 0 25 50 75 100 125 IOL − Low-Level Output Current − mA TA − Free-Air Temperature − °C Figure 14 Figure 15 OUTPUT TRANSITION TIME vs SUPPLY CURRENT RESPONSE LOAD CAPACITANCE TO AN OUTPUT VOLTAGE TRANSITION 250 225 VTAD D= =2 55° CV VCDL D= =5 05 pVF 10 f = 10 kHz 200 yA ns plm − 175 Rise Time up− me − Sent 5 Ti 150 Drr on IDCu siti 125 Fall Time 0 n a 100 Tr − 5 t 75 V t pute − 50 Outoltag 0 25 V 0 0 200 400 600 800 1000 t − Time CL − Load Capacitance − pF Figure 16 Figure 17 †Data at high and low temperatures are applicable only within the rated operating free-air temperature ranges of the various devices. • POST OFFICE BOX 655303 DALLAS, TEXAS 75265 15

TLC3702 ™ DUAL MICROPOWER LinCMOS VOLTAGE COMPARATORS SLCS013E − NOVEMBER 1986 − REVISED MARCH 2012 TYPICAL CHARACTERISTICS LOW-TO-HIGH-LEVEL OUTPUT RESPONSE HIGH-TO-LOW-LEVEL OUTPUT RESPONSE FOR VARIOUS INPUT OVERDRIVES FOR VARIOUS INPUT OVERDRIVES 5 5 40 mV put− V 20 mV put− V 40 mV ute 10 mV ute 20 mV V − OOVoltag 52 mmVV V − OOVoltag 1520 mmmVVV 0 0 VDD = 5 V 100 100 TA = 25° C DifferentialInputoltage − mV 0 VTCADL D== =25 505° pCVF DifferentialInputoltage − mV 0 CL = 50 pF V V 0 1 2 3 4 5 0 1 2 3 4 5 tPLH − Low-to-High-Level Output tPHL − High-to-Low-Level Output Response Time − μs Response Time − μs Figure 18 Figure 19 LOW-TO-HIGH-LEVEL HIGH-TO-LOW-LEVEL OUTPUT RESPONSE TIME OUTPUT RESPONSE TIME vs vs SUPPLY VOLTAGE SUPPLY VOLTAGE μonse −s 65 CTAL == 5205 °pCF μnse −s 65 CTAL == 5205 °pCF p Overdrive = 2 mV o s p e s R e put 4 ut R 4 Overdrive = 2 mV Out 5 mV utp O h-Level 3 10 mV Level 3 5 mV g w- ow-to-Hi 2 20 mV h-to-Lo 2 1200 mmVV − L 1 40 mV Hig 1 H − L L P H 40 mV t 0 P 0 2 4 6 8 10 12 14 16 t 0 0 2 4 6 8 10 12 14 16 VDD − Supply Voltage − V VDD − Supply Voltage − V Figure 20 Figure 21 • 16 POST OFFICE BOX 655303 DALLAS, TEXAS 75265

TLC3702 ™ DUAL MICROPOWER LinCMOS VOLTAGE COMPARATORS SLCS013E − NOVEMBER 1986 − REVISED MARCH 2012 TYPICAL CHARACTERISTICS† AVERAGE SUPPLY CURRENT (PER COMPARATOR) SUPPLY CURRENT vs vs SUPPLY VOLTAGE FREQUENCY 10000 40 TCAL == 5205 °pCF 35 ONou tLpouatsd sLow TA = −T 4A0 =°C − 55°C VDD = 16 V μV − Supply Current − ADD 1100000 4 V10 V5 V μV − Supply Current − ADD 3221105050 TA = 85°C TTA A= = − −1 2255°°CC 5 3 V 10 0 0.01 0.1 1 10 100 0 1 2 3 4 5 6 7 8 f − Frequency − kHz VDD − Supply Voltage − V Figure 22 Figure 23 SUPPLY CURRENT vs FREE-AIR TEMPERATURE 30 VDD = 5 V No Load 25 A μ − nt 20 e r ur Outputs Low C y 15 pl p u S − 10 D D I Outputs High 5 0 −75 −50 −25 0 25 50 75 100 125 TA − Free-Air Temperature − °C Figure 24 †Data at high and low temperatures are applicable only within the rated operating free-air temperature ranges of the various devices. • POST OFFICE BOX 655303 DALLAS, TEXAS 75265 17

TLC3702 ™ DUAL MICROPOWER LinCMOS VOLTAGE COMPARATORS SLCS013E − NOVEMBER 1986 − REVISED MARCH 2012 APPLICATION INFORMATION The inputs should always remain within the supply rails in order to avoid forward biasing the diodes in the electrostatic discharge (ESD) protection structure. If either input exceeds this range, the device is not damaged as long as the input is limited to less than 5 mA. To maintain the expected output state, the inputs must remain within the common-mode range. For example, at 25°C with V = 5 V, both inputs must remain between DD −0.2 V and 4 V to ensure proper device operation. To ensure reliable operation, the supply should be decoupled with a capacitor (0.1 μF) that is positioned as close to the device as possible. The TLC3702 has internal ESD-protection circuits that prevent functional failures at voltages up to 2000 V as tested under MIL-STD-883C, Method 3015.2; however, care should be exercised in handling these devices as exposure to ESD may result in the degradation of the device parametric performance. Table of Applications FIGURE Pulse-width-modulated motor speed controller 25 Enhanced supply supervisor 26 Two-phase nonoverlapping clock generator 27 Micropower switching regulator 28 12 V SN75603 DIR Half-H Driver 5 V EN 1/2 TLC3702 See Note A + 100 kΩ 10 kΩ + 5 V − 10 kΩ C1 Motor 0.01 μF − 1/2 TLC3704 12 V (see Note B) SN75604 DIR Half-H Driver 10 kΩ 5 V 10 kΩ EN Motor Speed Control Potentiometer 5 V Direction Control S1 SPDT NOTES: A. The recommended minimum capacitance is 10 μF to eliminate common ground switching noise. B. Adjust C1 for change in oscillator frequency. Figure 25. Pulse-Width-Modulated Motor Speed Controller • 18 POST OFFICE BOX 655303 DALLAS, TEXAS 75265

TLC3702 ™ DUAL MICROPOWER LinCMOS VOLTAGE COMPARATORS SLCS013E − NOVEMBER 1986 − REVISED MARCH 2012 APPLICATION INFORMATION 5 V 5 V 12 V VCC SENSE 12-V 3.3 kΩ 1/2 TLC3702 10 kΩ Sense + To μP RESIN TL7705A RESET Reset 1 kΩ − REF CT GND 2.5 V 1 μF CT (see Note B) 1/2 TLC3702 + To μP Interrupt R1 Early Power Fail V(UNREG) − (see Note A) R2 Monitors 5 VDC Rail Monitors 12 VDC Rail Early Power Fail Warning (R1 +R2) NOTES: A. V (cid:2) 2.5 (UNREG) R2 B. The value of CT determines the time delay of reset. Figure 26. Enhanced Supply Supervisor • POST OFFICE BOX 655303 DALLAS, TEXAS 75265 19

TLC3702 ™ DUAL MICROPOWER LinCMOS VOLTAGE COMPARATORS SLCS013E − NOVEMBER 1986 − REVISED MARCH 2012 APPLICATION INFORMATION 12 V R1 12 V 12 V 100 kΩ (see Note B) 1/2 TLC3702 − 1OUT R2 1/2 TLC3702 5 kΩ + − 100 kΩ (see Note C) + 1/2 TLC3702 22 kΩ − C1 0.01 μF 2OUT (see Note A) + 100 kΩ 100 kΩ R3 100 kΩ (see Note B) 12 V 1OUT 2OUT NOTES: A. Adjust C1 for a change in oscillator frequency where: 1/f = 1.85(100 kΩ)C1 B. Adjust R1 and R3 to change duty cycle C. Adjust R2 to change deadtime Figure 27. Two-Phase Nonoverlapping Clock Generator • 20 POST OFFICE BOX 655303 DALLAS, TEXAS 75265

TLC3702 ™ DUAL MICROPOWER LinCMOS VOLTAGE COMPARATORS SLCS013E − NOVEMBER 1986 − REVISED MARCH 2012 APPLICATION INFORMATION V (cid:2) 6Vto16V I I (cid:2) 0.01mAto0.25mA L V (cid:2) 2.5(R1 (cid:4) R2) O R2 1/2 TLC3702 1/2 TLC3702 VI SK9504 (see Note C) + 100 kΩ G S 100 kΩ − VI VI − + 47 μF 100 kΩ D Tantalum C1 + 180 μF IN5818 (see Note A) 100 kΩ R = 6 Ω L = 1 mH R1 (see Note D) VO 100 kΩ TLC271 (see Note B) VI RL 470 μF + R2 100 kΩ − C2 100 pF 100 kΩ 270 kΩ VI LM385 2.5 V NOTES: A. Adjust C1 for a change in oscillator frequency B. TLC271 − Tie pin 8 to pin 7 for low bias operation C. SK9504 − VDS = 40 V IDS = 1 A D. To achieve microampere current drive, the inductance of the circuit must be increased. Figure 28. Micropower Switching Regulator • POST OFFICE BOX 655303 DALLAS, TEXAS 75265 21

PACKAGE OPTION ADDENDUM www.ti.com 6-Feb-2020 PACKAGING INFORMATION Orderable Device Status Package Type Package Pins Package Eco Plan Lead/Ball Finish MSL Peak Temp Op Temp (°C) Device Marking Samples (1) Drawing Qty (2) (6) (3) (4/5) 5962-9153201Q2A ACTIVE LCCC FK 20 1 TBD POST-PLATE N / A for Pkg Type -55 to 125 5962- 9153201Q2A TLC3702 MFKB 5962-9153201QPA ACTIVE CDIP JG 8 1 TBD Call TI N / A for Pkg Type -55 to 125 9153201QPA TLC3702M 5962-9153202QPA ACTIVE CDIP JG 8 1 TBD Call TI N / A for Pkg Type -55 to 125 5962- 9153202QPA TLC3702CD ACTIVE SOIC D 8 75 Green (RoHS NIPDAU Level-1-260C-UNLIM 0 to 70 3702C & no Sb/Br) TLC3702CDR ACTIVE SOIC D 8 2500 Green (RoHS NIPDAU Level-1-260C-UNLIM 0 to 70 3702C & no Sb/Br) TLC3702CDRG4 ACTIVE SOIC D 8 2500 Green (RoHS NIPDAU Level-1-260C-UNLIM 0 to 70 3702C & no Sb/Br) TLC3702CP ACTIVE PDIP P 8 50 Green (RoHS NIPDAU N / A for Pkg Type 0 to 70 TLC3702CP & no Sb/Br) TLC3702CPSR ACTIVE SO PS 8 2000 Green (RoHS NIPDAU Level-1-260C-UNLIM 0 to 70 P3702 & no Sb/Br) TLC3702CPSRG4 ACTIVE SO PS 8 2000 Green (RoHS NIPDAU Level-1-260C-UNLIM 0 to 70 P3702 & no Sb/Br) TLC3702CPW ACTIVE TSSOP PW 8 150 Green (RoHS NIPDAU Level-1-260C-UNLIM 0 to 70 P3702 & no Sb/Br) TLC3702CPWR ACTIVE TSSOP PW 8 2000 Green (RoHS NIPDAU Level-1-260C-UNLIM 0 to 70 P3702 & no Sb/Br) TLC3702ID ACTIVE SOIC D 8 75 Green (RoHS NIPDAU Level-1-260C-UNLIM -40 to 85 3702I & no Sb/Br) TLC3702IDG4 ACTIVE SOIC D 8 75 Green (RoHS NIPDAU Level-1-260C-UNLIM -40 to 85 3702I & no Sb/Br) TLC3702IDR ACTIVE SOIC D 8 2500 Green (RoHS NIPDAU Level-1-260C-UNLIM -40 to 85 3702I & no Sb/Br) TLC3702IDRG4 ACTIVE SOIC D 8 2500 Green (RoHS NIPDAU Level-1-260C-UNLIM -40 to 85 3702I & no Sb/Br) TLC3702IP ACTIVE PDIP P 8 50 Green (RoHS NIPDAU N / A for Pkg Type -40 to 85 TLC3702IP & no Sb/Br) Addendum-Page 1

PACKAGE OPTION ADDENDUM www.ti.com 6-Feb-2020 Orderable Device Status Package Type Package Pins Package Eco Plan Lead/Ball Finish MSL Peak Temp Op Temp (°C) Device Marking Samples (1) Drawing Qty (2) (6) (3) (4/5) TLC3702IPE4 ACTIVE PDIP P 8 50 Green (RoHS NIPDAU N / A for Pkg Type -40 to 85 TLC3702IP & no Sb/Br) TLC3702IPW ACTIVE TSSOP PW 8 150 Green (RoHS NIPDAU Level-1-260C-UNLIM -40 to 85 P3702I & no Sb/Br) TLC3702IPWR ACTIVE TSSOP PW 8 2000 Green (RoHS NIPDAU Level-1-260C-UNLIM -40 to 85 P3702I & no Sb/Br) TLC3702IPWRG4 ACTIVE TSSOP PW 8 2000 Green (RoHS NIPDAU Level-1-260C-UNLIM -40 to 85 P3702I & no Sb/Br) TLC3702MD ACTIVE SOIC D 8 75 Green (RoHS NIPDAU Level-1-260C-UNLIM -55 to 125 3702M & no Sb/Br) TLC3702MDG4 ACTIVE SOIC D 8 75 Green (RoHS NIPDAU Level-1-260C-UNLIM -55 to 125 3702M & no Sb/Br) TLC3702MDR ACTIVE SOIC D 8 2500 Green (RoHS NIPDAU Level-1-260C-UNLIM -55 to 125 3702M & no Sb/Br) TLC3702MDRG4 ACTIVE SOIC D 8 2500 Green (RoHS NIPDAU Level-1-260C-UNLIM -55 to 125 3702M & no Sb/Br) TLC3702MFKB ACTIVE LCCC FK 20 1 TBD POST-PLATE N / A for Pkg Type -55 to 125 5962- 9153201Q2A TLC3702 MFKB TLC3702MJG ACTIVE CDIP JG 8 1 TBD Call TI N / A for Pkg Type -55 to 125 TLC3702MJG TLC3702MJGB ACTIVE CDIP JG 8 1 TBD Call TI N / A for Pkg Type -55 to 125 9153201QPA TLC3702M (1) The marketing status values are defined as follows: ACTIVE: Product device recommended for new designs. LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect. NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design. PREVIEW: Device has been announced but is not in production. Samples may or may not be available. OBSOLETE: TI has discontinued the production of the device. (2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free". RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption. Green: TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement. Addendum-Page 2

PACKAGE OPTION ADDENDUM www.ti.com 6-Feb-2020 (3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature. (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device. (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device. (6) Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width. Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release. In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis. OTHER QUALIFIED VERSIONS OF TLC3702, TLC3702M : •Catalog: TLC3702 •Automotive: TLC3702-Q1, TLC3702-Q1 •Enhanced Product: TLC3702-EP, TLC3702-EP •Military: TLC3702M NOTE: Qualified Version Definitions: •Catalog - TI's standard catalog product •Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects •Enhanced Product - Supports Defense, Aerospace and Medical Applications •Military - QML certified for Military and Defense Applications Addendum-Page 3

PACKAGE MATERIALS INFORMATION www.ti.com 25-Sep-2019 TAPE AND REEL INFORMATION *Alldimensionsarenominal Device Package Package Pins SPQ Reel Reel A0 B0 K0 P1 W Pin1 Type Drawing Diameter Width (mm) (mm) (mm) (mm) (mm) Quadrant (mm) W1(mm) TLC3702CDR SOIC D 8 2500 330.0 12.4 6.4 5.2 2.1 8.0 12.0 Q1 TLC3702CPSR SO PS 8 2000 330.0 16.4 8.35 6.6 2.5 12.0 16.0 Q1 TLC3702CPWR TSSOP PW 8 2000 330.0 12.4 7.0 3.6 1.6 8.0 12.0 Q1 TLC3702IDR SOIC D 8 2500 330.0 12.4 6.4 5.2 2.1 8.0 12.0 Q1 TLC3702IPWR TSSOP PW 8 2000 330.0 12.4 7.0 3.6 1.6 8.0 12.0 Q1 TLC3702MDR SOIC D 8 2500 330.0 12.4 6.4 5.2 2.1 8.0 12.0 Q1 TLC3702MDRG4 SOIC D 8 2500 330.0 12.4 6.4 5.2 2.1 8.0 12.0 Q1 PackMaterials-Page1

PACKAGE MATERIALS INFORMATION www.ti.com 25-Sep-2019 *Alldimensionsarenominal Device PackageType PackageDrawing Pins SPQ Length(mm) Width(mm) Height(mm) TLC3702CDR SOIC D 8 2500 340.5 338.1 20.6 TLC3702CPSR SO PS 8 2000 367.0 367.0 38.0 TLC3702CPWR TSSOP PW 8 2000 367.0 367.0 35.0 TLC3702IDR SOIC D 8 2500 340.5 338.1 20.6 TLC3702IPWR TSSOP PW 8 2000 367.0 367.0 35.0 TLC3702MDR SOIC D 8 2500 350.0 350.0 43.0 TLC3702MDRG4 SOIC D 8 2500 350.0 350.0 43.0 PackMaterials-Page2

None

PACKAGE OUTLINE D0008A SOIC - 1.75 mm max height SCALE 2.800 SMALL OUTLINE INTEGRATED CIRCUIT C SEATING PLANE .228-.244 TYP [5.80-6.19] .004 [0.1] C A PIN 1 ID AREA 6X .050 [1.27] 8 1 2X .189-.197 [4.81-5.00] .150 NOTE 3 [3.81] 4X (0 -15 ) 4 5 8X .012-.020 B .150-.157 [0.31-0.51] .069 MAX [3.81-3.98] .010 [0.25] C A B [1.75] NOTE 4 .005-.010 TYP [0.13-0.25] 4X (0 -15 ) SEE DETAIL A .010 [0.25] .004-.010 0 - 8 [0.11-0.25] .016-.050 [0.41-1.27] DETAIL A (.041) TYPICAL [1.04] 4214825/C 02/2019 NOTES: 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side. 4. This dimension does not include interlead flash. 5. Reference JEDEC registration MS-012, variation AA. www.ti.com

EXAMPLE BOARD LAYOUT D0008A SOIC - 1.75 mm max height SMALL OUTLINE INTEGRATED CIRCUIT 8X (.061 ) [1.55] SYMM SEE DETAILS 1 8 8X (.024) [0.6] SYMM (R.002 ) TYP [0.05] 5 4 6X (.050 ) [1.27] (.213) [5.4] LAND PATTERN EXAMPLE EXPOSED METAL SHOWN SCALE:8X SOLDER MASK SOLDER MASK METAL OPENING OPENING METAL UNDER SOLDER MASK EXPOSED METAL EXPOSED METAL .0028 MAX .0028 MIN [0.07] [0.07] ALL AROUND ALL AROUND NON SOLDER MASK SOLDER MASK DEFINED DEFINED SOLDER MASK DETAILS 4214825/C 02/2019 NOTES: (continued) 6. Publication IPC-7351 may have alternate designs. 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site. www.ti.com

EXAMPLE STENCIL DESIGN D0008A SOIC - 1.75 mm max height SMALL OUTLINE INTEGRATED CIRCUIT 8X (.061 ) [1.55] SYMM 1 8 8X (.024) [0.6] SYMM (R.002 ) TYP [0.05] 5 4 6X (.050 ) [1.27] (.213) [5.4] SOLDER PASTE EXAMPLE BASED ON .005 INCH [0.125 MM] THICK STENCIL SCALE:8X 4214825/C 02/2019 NOTES: (continued) 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations. 9. Board assembly site may have different recommendations for stencil design. www.ti.com

None

None

MECHANICAL DATA MCER001A – JANUARY 1995 – REVISED JANUARY 1997 JG (R-GDIP-T8) CERAMIC DUAL-IN-LINE 0.400 (10,16) 0.355 (9,00) 8 5 0.280 (7,11) 0.245 (6,22) 1 4 0.065 (1,65) 0.045 (1,14) 0.063 (1,60) 0.020 (0,51) MIN 0.310 (7,87) 0.015 (0,38) 0.290 (7,37) 0.200 (5,08) MAX Seating Plane 0.130 (3,30) MIN 0.023 (0,58) 0°–15° 0.015 (0,38) 0.100 (2,54) 0.014 (0,36) 0.008 (0,20) 4040107/C 08/96 NOTES: A. All linear dimensions are in inches (millimeters). B. This drawing is subject to change without notice. C. This package can be hermetically sealed with a ceramic lid using glass frit. D. Index point is provided on cap for terminal identification. E. Falls within MIL STD 1835 GDIP1-T8 • POST OFFICE BOX 655303 DALLAS, TEXAS 75265

None

PACKAGE OUTLINE PW0008A TSSOP - 1.2 mm max height SCALE 2.800 SMALL OUTLINE PACKAGE C 6.6 TYP SEATING PLANE 6.2 PIN 1 ID A 0.1 C AREA 6X 0.65 8 1 3.1 2X 2.9 NOTE 3 1.95 4 5 0.30 8X 0.19 4.5 1.2 MAX B 0.1 C A B 4.3 NOTE 4 (0.15) TYP SEE DETAIL A 0.25 GAGE PLANE 0.15 0.75 0 - 8 0.05 0.50 DETAIL A TYPICAL 4221848/A 02/2015 NOTES: 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side. 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side. 5. Reference JEDEC registration MO-153, variation AA. www.ti.com

EXAMPLE BOARD LAYOUT PW0008A TSSOP - 1.2 mm max height SMALL OUTLINE PACKAGE 8X (1.5) 8X (0.45) SYMM (R0.05) 1 TYP 8 SYMM 6X (0.65) 5 4 (5.8) LAND PATTERN EXAMPLE SCALE:10X SOOPLEDNEINRG MASK METAL MSOELTDAEL RU NMDAESRK SOOPLEDNEINRG MASK 0.05 MAX 0.05 MIN ALL AROUND ALL AROUND NON SOLDER MASK SOLDER MASK DEFINED DEFINED SOLDER MASK DETAILS NOT TO SCALE 4221848/A 02/2015 NOTES: (continued) 6. Publication IPC-7351 may have alternate designs. 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site. www.ti.com

EXAMPLE STENCIL DESIGN PW0008A TSSOP - 1.2 mm max height SMALL OUTLINE PACKAGE 8X (1.5) SYMM (R0.05) TYP 8X (0.45) 1 8 SYMM 6X (0.65) 5 4 (5.8) SOLDER PASTE EXAMPLE BASED ON 0.125 mm THICK STENCIL SCALE:10X 4221848/A 02/2015 NOTES: (continued) 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations. 9. Board assembly site may have different recommendations for stencil design. www.ti.com

IMPORTANTNOTICEANDDISCLAIMER TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS. These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources. TI’s products are provided subject to TI’s Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI’s provision of these resources does not expand or otherwise alter TI’s applicable warranties or warranty disclaimers for TI products. Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated

Datasheet下载

Datasheet下载