ICGOO在线商城 > 集成电路(IC) > PMIC - AC-DC 转换器,离线开关 > TFS761HG

- 型号: TFS761HG

- 制造商: Power Integrations

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

TFS761HG产品简介:

ICGOO电子元器件商城为您提供TFS761HG由Power Integrations设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 TFS761HG价格参考。Power IntegrationsTFS761HG封装/规格:PMIC - AC-DC 转换器,离线开关, Converter Offline Flyback, Forward Topology 66kHz 16-eSIPB。您可以下载TFS761HG参考资料、Datasheet数据手册功能说明书,资料中有TFS761HG 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC)半导体 |

| 描述 | IC PWR SUPPLY CTLR 326W ESIP-16开关控制器 2 Swt Fwd,Flybk Cntr 326 W Cont. @ 25 C |

| 产品分类 | |

| 品牌 | Power Integrations |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 电源管理 IC,开关控制器 ,Power Integrations TFS761HGHiperTFS® |

| 数据手册 | |

| 产品型号 | TFS761HG |

| 产品 | Voltage Converters |

| 产品种类 | 开关控制器 |

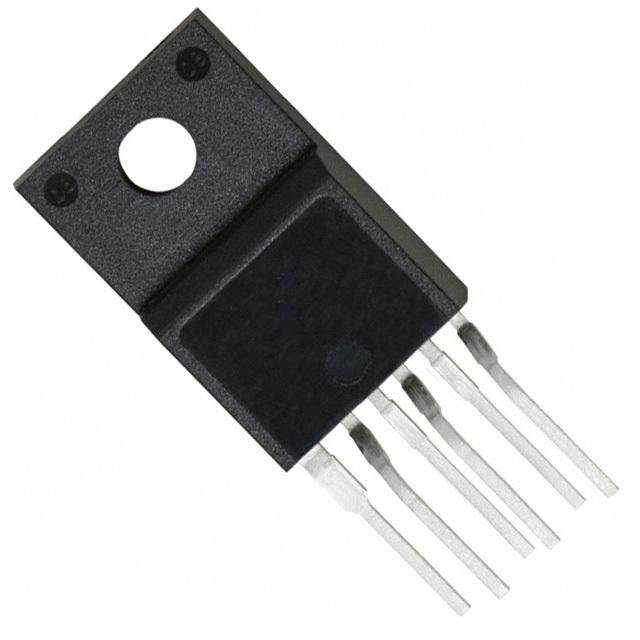

| 供应商器件封装 | 16-eSIPB |

| 其它名称 | 596-1404 |

| 功率(W) | 326W |

| 包装 | 管件 |

| 占空比-最大 | 73 % |

| 商标 | Power Integrations |

| 安装风格 | Through Hole |

| 封装 | Tube |

| 封装/外壳 | 16-SIP,12 引线,裸露焊盘,成形引线 |

| 封装/箱体 | eSIP-16B |

| 工作温度 | 0°C ~ 100°C |

| 工厂包装数量 | 30 |

| 开关频率 | 66 kHz |

| 标准包装 | 30 |

| 电压-击穿 | 725V |

| 电压-输入 | 10.3 V ~ 13.4 V |

| 电压-输出 | - |

| 输出功率 | 383 W |

| 输出电压 | 100 V to 400 V |

| 输出端数量 | 1 Output |

| 输出隔离 | 隔离 |

| 频率范围 | 62kHz ~ 70kHz |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

TFS757-764HG HiperTFS™ Family Combined Two-Switch Forward and Flyback Power Supply Controllers with Integrated High Voltage MOSFETs Key Benefits Applications • Single chip solution for two-switch forward main and flyback • PC standby • Printer • High integration allows smaller form factor and higher power • LCD TV density designs • Video game consoles • Incorporates control, gate drivers, and three power • High-power adapters MOSFETS • Industrial and appliance high-power adapters • Level shift technology eliminates need for pulse transformer • Protection features include: UV, OV, OTP, OCP, and SCP Output Power Table • Transformer reset control Two-Switched Forward Flyback • Prevents transformer saturation under all conditions 380 V 100 V - 400 V • Allows >50% duty cycle operation Product Continuous Continuous Peak • Reduces primary side RMS currents and conduction losses (25 °C) (50 °C) (50 °C) 50 °C • Standby supply provides built-in overload power compensation TFS757HG 193 W 163 W 228 W 20 W • Up to 434 W total output power in a highly compact package TFS758HG 236 W 200 W 278 W 20 W • Up to 550 W peak TFS759HG 280 W 235 W 309 W 20 W • High efficiency solution easily enables design to meet TFS760HG 305 W 258 W 358 W 20 W stringent efficiency specifications TFS761HG 326 W 276 W 383 W 20 W • >90% efficiency at full load TFS762HG 360 W 304 W 407 W 20 W • No-load regulation and low losses at light-load TFS763HG 388 W 327 W 455 W 20 W • Simple clip mounting to heat sink without need for insulation pad TFS764HG 414 W 344 W 530 W 20 W • Halogen free and RoHS compliant Table 1. Output Power Table (See Notes on page 13). Main Output HiperTFS VDDH HD HS L D Two-Switch Forward Transformer Auxiliary/Standby Output DC RTN Input Control, Gate Drivers, R FB Level Shift DSB EN FB Flyback Transformer FB BP EN EN G S PI-6200-102910 Figure 1. Simplified Schematic of Two-Switch Forward and Flyback Converter. www.power.com April 2015

TFS757-764HG Section List Description .................................................................................................................................................................. 3 Product Highlights ...................................................................................................................................................... 3 Pin Functional Description .........................................................................................................................................5 Pin Configuration ......................................................................................................................................................5 Functional Block Diagram .....................................................................................................................................6-7 Functional Description ...............................................................................................................................................8 Output Power Table ...............................................................................................................................................13 Design, Assembly, and Layout Considerations ....................................................................................................14 Application Example .................................................................................................................................................20 Absolute Maximum Ratings .....................................................................................................................................23 Parameter Table .....................................................................................................................................................23 Typical Performance Characteristics .................................................................................................................29-33 Package Details ........................................................................................................................................................34 Part Ordering Information.........................................................................................................................................35 Part Marking Information .........................................................................................................................................35 2 Rev. E 04/15 www.power.com

TFS757-764HG Description • Programmable line overvoltage (OV) detection; latching and The HiperTFS device family members incorporate both a non-latching high-power two-switch-forward converter and a mid-power • Accurate hysteretic thermal shutdown (OTP) flyback (standby) converter into a single, low-profile eSIP™ • Accurate selectable current limit (main and standby) power package. The single chip solution provides the controllers • Fully integrated soft-start for minimum start-up stress for the two-switch-forward and flyback converters, high- and • Simple fast AC reset low-side drivers, all three of the high-voltage power MOSFETs, • Reduced EMI and eliminates the converter’s need for costly external pulse • Synchronized 66 kHz forward and 132 kHz flyback transformers. The device is ideal for high power applications converters that require both a main power converter (two-switch forward) • Frequency jitter up to 414 W, and standby converter (flyback) up to 20 W. • Eliminates up to 30 discrete components for higher reliability HiperTFS includes Power Integrations’ standard set of comprehen- and lower cost sive protection features, such as integrated soft-start, fault and Asymmetrical Two-Switch Forward Reduces Losses over-load protection, and hysteretic thermal shutdown. • Allows >50% duty cycle operation HiperTFS utilizes advanced power packaging technology that • Reduces primary side RMS currents and conduction losses simplifies the complexity of two-switch forward layout, mounting • Minimizes the size and cost of the bulk capacitor and thermal management, while providing very high power • Allows reduced capacitance or longer hold-up time capabilities in a single compact package. The devices operate • Allows lower voltage output diodes over a wide input voltage range, and can be used following a • Transformer reset control power-factor correction stage such as HiperPFS. • Prevents transformer saturation under all conditions • Extends duty cycle to satisfy AC cycle drop out ride through Two-switch-forward power converters are often selected for • Duty cycle soft-start with 115% current limit boost applications demanding cost-effective efficiency, fast transient • Satisfies 2 ms ~ 20 ms start-up with large capacitance at response, and accurate tolerance to line voltage fluctuation. The output two-switch-forward controller incorporated into HiperTFS • Remote ON/OFF function devices improves on the classic topology by allowing operation • Voltage mode controller with current limit considerably above 60% duty cycle. This improvement reduces RMS currents conduction losses, minimizes the size and cost of 20 W Flyback with Selectable Power Limit the bulk capacitor, and minimizes output diode voltage ratings. • TinySwitch-III based converter The advanced design also includes transformer flux reset • Selectable power limit (10 W, 12.5 W, 15 W, or 20 W) control (saturation protection) and charge-recovery switching of • Built-in overload power compensation the high-side MOSFET, which reduces switching losses. This • Flat overload power vs. input voltage combination of innovations yields an extremely efficient power • Reduces component stress during overload conditions supply with smaller MOSFETs, fewer passives and discrete • Reduces required design margin for transformer and output components, and a lower-cost transformer. diode • Output overvoltage (OV) protection with fast AC reset HiperTFS’s flyback standby controller and MOSFET solution is • Latching, non-latching, or auto-restart based on the highly popular TinySwitch™ technology used in • Output short-circuit protection (SCP) with auto-restart billions of power converter ICs due to its simplicity of operation, • Output over-current protection (OCP) light load efficiency, and rugged, reliable, performance. This Advanced Package for High Power Applications flyback converter can provide up to 20 W of output power and • 434 W output power capability in a highly compact package the built in overload power compensation reduces component • Up to 550 W peak design margin. • Simple clip mounting to heat sink Product Highlights • Can be directly connected to heat sink without insulation pad • Provides thermal impedance equivalent to a TO-220 Protected Two-Switch Forward and • Heat slug connected to ground potential for low EMI Flyback Combination Solution • Staggered pin arrangement for simple routing of board traces • Incorporates three high-voltage power MOSFETs, main and and high-voltage creepage requirements standby controllers, and gate drivers • Single power package for two power converters reduces • Level shift technology eliminates need for pulse transformer assembly costs layout size • Programmable line undervoltage (UV) detection prevents turn-off glitches 3 www.power.com Rev. E 04/15

TFS757-764HG Typical Two-Switch Function Forward HiperTFS Advantages of HiperTFS Nominal Duty Cycle 33% 45% Wider duty cycle reduces RMS switch currents by 17%. Reduces R losses by 31% Maximum Duty Cycle <50% 63% DS(ON) Switch Current (RMS) 100% 83% Output Catch Diode V + V /D V + V /D Lower losses. Wider D lowers catch diode rating by O D MAX O D MAX MAX (1-(50%/63%)) = 21% reduction in catch diode voltage rating Clamp Voltage Reset diodes from zero Reset from zero to With fast/slow diode combination, allows charge to V (V + 130) recovery to limit high-side C loss IN IN OSS Thermal Shutdown --- 118 °C Shutdown / HiperTFS provides integrated OTP device protection 55 °C hysteresis Current Sense Resistor 0.5 V drop (0.33 W at Sense resistor not Improved efficiency. MOSFET R sense eliminated DS(ON) 300 W) required need for sense resistor High-Side Drive Requires gate-drive Built in high-side drive Lower cost; component elimination. Removes transformer (high cost) high-cost gate-drive transformer (EE10 or toroid) Component Count Higher Lower Saves up to 50 components, depending on specification. TinySwitch Overload Power --- Built-in compensation Safer design; easier to design power supply. Flattens Compensation vs. Input Voltage overload output power over line voltages Package Creepage TO-220 = 1.17 mm eSIP16/12 = 2.3 mm/ HiperTFS meets functional safety spacing at package 3.3 mm pins Package Assembly 2 × TO-220 package, 2 1 Package No SIL (insulation) pad required × SIL (insulation) Table 2. Summary of Differences Between HiperTFS and Other Typical High Power Supplies. 4 Rev. E 04/15 www.power.com

TFS757-764HG Pin Functional Description BYPASS (BP) Pin This is the decoupled operating voltage pin for the low-side MAIN DRAIN (D) Pin controller. At start-up the bypass capacitor is charged from an Drain of the low-side MOSFET transistor forward converter. internal device current source. During normal operation the capacitor voltage is maintained by drawing current from the STANDBY DRAIN (DSB) Pin low-side bias winding on the standby power supply. This pin is Drain of the MOSFET of standby power supply. also used to implement remote ON/OFF for the main controller. This is done by driving extra current into the BYPASS pin when GROUND (G) Pin we want to turn-on the Main controller. The BYPASS pin also This pin gives a signal current path to the substrate of the implements a latch-off function to disable standby and main low-side controller. This pin is provided to allow a separate when the BP pin current exceeds latching threshold. Latch is Kelvin connection to the substrate of the low-side controller to reset when LINE-SENSE pin falls below UV (off) standby eliminate inductive voltages that might be developed by high threshold. switching currents in the SOURCE pin. The GROUND pin is not intended to carrier high currents, instead it is intended as a HIGH-SIDE OPERATING VOLTAGE (VDDH) Pin voltage-reference connection only. This is the high-side bias (VDD) of approximately 11.5 V. This voltage is maintained with current from a high-side bias winding SOURCE (S) Pin on the main transformer and/or from a bootstrap diode from the SOURCE pin that is common to both the standby and main low-side standby bias supply. supplies. HIGH-SIDE SOURCE (HS) Pin RESET (R) Pin SOURCE pin of the high-side MOSFET. This pin provides information to limit the maximum duty cycle as a function of the current fed into the RESET pin during the off-time HIGH-SIDE DRAIN (HD) Pin of the main converter MOSFET. This pin can also be pulled up to DRAIN pin of the high-side MOSFET. This MOSFET is floating bypass to signal remote ON/OFF of the main converter only. with respect to low-side source and ground. ENABLE (EN) Pin This is the ENABLE pin for the standby controller. Prior to the H Package (eSIP-16/12) start-up a resistor connected from ENABLE to BYPASS, can be detected to select one of several internal current limits. LINE-SENSE (L) Pin This pin provides input bulk voltage line-sense function. This information is used by the undervoltage and overvoltage detection circuits for both main and standby. The pin can also Exposed Metal be pulled up to BYPASS or be pulled down to SOURCE to (On Edge) implement a remote ON/OFF of both standby and main Internally 1 3 5 67 891011 1314 16 Connected D D GSRELFB VH H supplies simultaneously. The LINE-SENSE pin works in S N BP DS D B D conjunction with the RESET pin to implement a duty-cycle limit H function. Also the LINE-SENSE pin compensates the value of standby current limit so as to flatten the output overload HDHDHSS S response as a function of input voltage. FEEDBACK (FB) Pin This pin provides feedback for the main two transistor forward Exposed Pad converter. An increase in current sink from FEEDBACK pin to (Backside) Internally ground, will lead to a reduction in operating duty cycle. This pin Connected to SOURCE Pin (see eSIP-16B also selects the main device current limit at start-up (in a similar Package Drawing) manner to ENABLE pin). PI-5290-110510 Figure 2. Pin Configuration. 5 www.power.com Rev. E 04/15

TFS757-764HG HIGH-SIDE OPERATING VOLTAGE (VDDH) HIGH-SIDE DRAIN (HD) VDDH UNDERVOLTAGE + HSD1 11.1 V 12 V 9.9 V HSD2 S Q DISCRIMINATOR R HIGH-SIDE SOURCE (HS) PI-5516-060410 BYPASS (BP) HSD1 HSD2 DRAIN (D) MAIN REMOTE-ON FAULT PRESENT GATE HS PWM INPUT REMOTE OFF VILIMIT SOFT-START DSS FEEDBACK (FB) and MAIN CURRENT 3 V+VT LIMIT SELECT POWER ON ILIMIT SELECT - + R DMAX RESET (R) REMOTE DUTY GATE CCUORMRPEANRTA LTIOMRIT OFF CLYIMCLITE CLK L ON LINE-SENSE (L) CONTROLLED VBG STOP GATTUER DNR-OIVNER LINE SENSE LV S Q LEADING - R BLEADNGKEING + PWM COMPARATOR LV D2MAX CLK2SAW IPNWPUMT THERMAL SD SOURCE (S) PI-5263-021511 Figure 3. Functional Block Diagram for Two-Switch Forward Converter. 6 Rev. E 04/15 www.power.com

TFS757-764HG LV (LINE VOLTAGE) BYPASS (BP) STANDBY DRAIN (DSB) REGULATOR 5.7 V 115 µA FAULT BYPASS PIN 6.0 V PRESENT + UNDER-VOLTAGE AUTO- ENABLE PULL RESTART UP RESISTOR - COURNESTEERT SLECIMLUIETRC RSTET AANTNTED 54..77 VV ILVIMINIT VILIMIT MACHINE ADJUST CURRENT LIMIT COMPARATOR ENABLE - + JITTER CLOCK CLK2 CaEUnNdRA RSBETLANEN L(DEIMBNIY)T 1.0 V + VT DDC2MMAAXX STHHUETRDMOAWLN SELECT SAW 1.0 V OSCILLATOR S Q R Q MAIN LEADING REMOTE EDGE ON/ BLANKING OVP LATCH OFF SOURCE (S) SAW D2MAX MAIN CLK2 FAULT THERMAL SD PI-5264-020510 REMOTE PRESENT ON Figure 4. Functional Block Diagram for Flyback/Standby Converter. 7 www.power.com Rev. E 04/15

TFS757-764HG FTcohunent HrcoiltpleieorrsTn FaaSnl d cD oanestssaocincrsiai tptwetdoi o lsonwwi-tcshid-em ModOeS pFoEwTe’sr asluopnpgl yw ith FSrweqitucehnincgy fOSC + PI-4530-041107 f - high-side driver and high-side MOSFET. OSC • The HiperTFS two-switch forward includes a controller along 4 ms with low-side power MOSFET, high-side power MOSFET and high-side driver. This device operates in voltage mode (linear V duty-cycle control) at fixed frequency (exactly half the operat- DRAIN ing frequency of the standby controller). The control converts a current input (FEEDBACK pin), to a duty-cycle at the open Time drain MOSFET MAIN DRAIN pin decreasing duty-cycle with increasing sourced current from the FEEDBACK pin. Figure 5. Switching Frequency Jitter (Idealized V Waveforms). DRAIN • The HiperTFS flyback includes a controller and power MOSFET Main Start-Up Operation which is based on TinySwitch-III. This device operates in Once the flyback (standby) converter is up and running, the multi-level ON/OFF current limit control mode. The open drain main converter can be enabled by two functions. The first MOSFET (STANDBY DRAIN pin) is turned on when the sourced condition is that the BYPASS pin remote-on current must current from the ENABLE pin is below the threshold and exceed the remote-on threshold (I ), provided by an external BP(ON) switching is disabled when the ENABLE pin current is above remote ON/OFF circuit. This current threshold has a hysteresis the threshold. to prevent noise interference. Once the BYPASS remote-on has been achieved, the HiperTFS also requires that the LINE- In addition to the basic features, such as the high-voltage SENSE pin current exceeds the UV Main-on (I ), which L(MA-UVON) start-up, the cycle-by-cycle current limiting, loop compensation corresponds to approximately 315 VDC input voltage when circuitry, auto-restart and thermal shutdown, the HiperTFS main using a 4 MW LINE-SENSE pin resistor. Once this LINE-SENSE controller incorporates many additional functions that reduce pin threshold has been achieved the HiperTFS will enter a 12 ms system cost, increase power supply performance and design pre-charge period (t ) to allow the PFC-boost stage to reach D(CH) flexibility. regulation before the main applies a load to the bulk-capacitor. Also during this pre-charge period the high-side driver is Main Converter General Introduction charged via the boot-strap diode from the low-side auxiliary The Main converter for the HiperTFS, is a two-switch forward voltage, and is charged when the main low-side MOSFET turns converter (although the HiperTFS could be used with other two-switch topologies). This topology involves a low-side and high-side power MOSFET, both of which are switched at the VIN same time. In the case of the HiperTFS, the low-side MOSFET 385 V is a 725 V MOSFET (with the substrate connected to the t SOURCE pin). The high-side MOSFET is a 530 V MOSFET (with the substrate connected to the HIGH-SIDE DRAIN (HD) Standby pin). As such the substrate of both low-side and high-side Output MOSFET’s are tied to quiet circuit nodes (0 V and V IN t respectively), meaning that both MOSFETs have electrically quiet substrates – good for EMI. Main Output The low-side MOSFET has a very low C capacitance and OSS thus can be hard-switched without performance penalty. Due to the external clamp configuration it is possible to substantially 12 ms t soft-switch the high-side MOSFET at high-loads (thus 32 ms eliminating a large proportion of high-side capacitive switching Main 12 ms 115% ILIM loss) and improving efficiency. The higher breakdown voltage Primary 100% ILIM Current on the low-side MOSFET allows the transformer reset voltage to exceed the input voltage, and thus allow operation at duty cycles greater than 50%. Higher duty cycle operation leads to t lower RMS switch currents and also lower output diode voltage-rating, both of which contribute to improved efficiency. Remote ON The HiperTFS also contains a high-side driver to control the t high-side MOSFET. This internal high-side driver eliminates the PI-5619a-102710 need for a gate-driver transformer, an expensive component that is required for many other two-switch forward circuits. Figure 6. Supply Start-Up Sequence by Remote ON. 8 Rev. E 04/15 www.power.com

TFS757-764HG on, while the main high-side MOSFET is held off. By the end of The HIGH-SIDE OPERATING VOLTAGE pin has an undervoltage the pre-charge period, the PFC-boost voltage should be at or lock-out threshold, to prevent gate-drive when the supply voltage above the nominal boost voltage. The HiperTFS begins drops below a safe threshold. At power-up the high-side driver switching, going through the soft-start period (t ). During the remains in the off-state, until the HIGH-SIDE OPERATING SS soft-start period the maximum duty cycle starts at 30% and is VOLTAGE pin is charged above 10.5 V, at which point the ramped during a 12 ms period to the maximum. The ramped high-side driver becomes active. The high-side driver is initially duty cycle controls the rise slew rate of the output during charged via a boot-strap diode connected via a diode to the start-up, allowing well controlled start-up and also facilitates a HIGH-SIDE OPERATING VOLTAGE pin from the low-side smooth transition when the control loop takes over regulation standby auxiliary supply (approximately 12 V). During start-up towards the end of soft-start. Also during a 32 ms period the high-side MOSFET remains off, but the low-side MOSFET is (starting at the beginning of soft-start), the main current limit is turned on for a period of 14 ms to allow pre-charge of the boosted to 115% of the nominal selected Main current. This high-side operating voltage to 12 V. After this period, the high- allows the main to start-up within the required period for the side operating voltage is supplied by a forward-winding coupled application (typically < 20 ms for PC main applications), when to the main transformer. This floating winding provides energy there is a substantial capacitive load on the output. After the every time the main converter switches one cycle. The soft-start period, the current limit returns to 100% of the operating power for high-side operating voltage can also be nominal selected current limit. provided from a floating winding on the standby supply. However this would continue delivering power even when the Main Converter Control FEEDBACK (FB) Pin Operation main converter is in remote-off, and thus is considered The FEEDBACK pin is the input for control loop feedback from undesirable from a standby light-load efficiency point of view. the main control loop. During normal operation the FEEDBACK pin is used to provide duty cycle control for the main converter. Once the high-side driver is operating it receives level-shifted The system output voltage is detected and converted into a drive commands from the low-side device. These drive feedback current. The main converter duty cycle will reduce as commands cause both turn-on and turn-off drive of the more current is sourced from the FEEDBACK pin, reaching zero high-side main MOSFET simultaneously with that of the duty cycle at approximately 2.1 mA. The nominal voltage of the low-side main MOSFET. FEEDBACK pin is maintained at approximately 3.5 V. An internal pole on the FEEDBACK pin is set to approximately The high-side driver also contains a thermal shutdown on-chip, 12 kHz, in order to facilitate optimal control loop response. but this is set to a temperature above the thermal shutdown temperature of the low-side device. Thus the low-side will The maximum duty cycle of the main converter is defined by the always shutdown first. LINE-SENSE pin and RESET pin behavior and is a dynamically calculated value according to cycle-by-cycle conditions on the Main Converter Maximum Duty Cycle LINE-SENSE pin and RESET pin. The LINE-SENSE pin resistor converts the input voltage into an LINE-SENSE pin current signal. The RESET pin resistor converts the reset voltage into an RESET pin current signal. Duty (D) The LINE-SENSE pin and RESET pin currents allow the 78% HiperTFS to determine a maximum duty cycle envelope on a IL = 60 µA Typical IL and IR cycle-by-cycle basis. This feature ensures sufficient time for 63% IR = 170 µA currents at VMIN transformer reset on a cycle-by-cycle basis and also protects Limited by L & R against single-cycle transformer saturation and at high-input pin duty limit voltage by limiting the maximum duty cycle to prevent the transformer from reaching an unsafe flux density during the FEEDBACK Pin on-time period. Both of these features allow the optimal Current I 0% FB performance to be obtained from the main transformer. The 1 mA 2.1 mA duty cycle limit is trimmed during production. PI-5885-082610 Figure 7. PWM Duty Cycle vs. Control Current. The LINE-SENSE pin and RESET pin are sampled just before the turn-on of the next main cycle. This is done to sample at a Main High-Side Driver point when there is minimal noise in the system. Due to the low The high-side driver is a device that is electrically floating at the current signal input to the LINE-SENSE pin and RESET pin, potential of the HIGH-SIDE MOSFET SOURCE (HS) pin. This care should be taken to prevent noise injection on these pins device provides gate-drive for the high-side Main MOSFET. The (see Applications section layout guidelines for details). low-side main and high-side main MOSFET’s switch simul- taneously. The high-side driver has a HIGH-SIDE OPERATING Main On-Chip Current Limit with External Selection VOLTAGE supply pin. External circuitry provides a current During start-up, the FEEDBACK pin and ENABLE pin are both source into this HIGH-SIDE OPERATING VOLTAGE pin. The used to select internal current limits for the main and standby high-side operating voltage has an internal 12 V shunt-regulator. converters respectively. The detection period occurs at the The device consumes approximately 2 mA when driving the initial start-up of the device, and before the main or standby high-side MOSFET. MOSFETs start switching. This is done to minimize noise interference. 9 www.power.com Rev. E 04/15

TFS757-764HG 0.7 0 1 0 1 6 IL = 60 µA 7-0 7 9 5 PI- I = 90 µA mit 0.6 L Li e cl I = 100 µA y L C y ut D 0.5 I = 115 µA L 0.4 0.5 1.0 1.5 2.0 2.5 3.0 I /I R L Figure 8. Duty Cycle Limit vs. Ratio of R Pin Current Over L Pin Current. A resistor R is connected from the BYPASS pin to the Main Line Undervoltage Detection (UV) FB FEEDBACK pin. This resistor feeds current into the FEEDBACK The LINE-SENSE pin resistor is connected to V and generates IN pin (who’s voltage is clamped to approximately 1 V during this a current signal proportional to V . The LINE-SENSE pin voltage IN detection period). The current into the FEEDBACK pin is is held by the device at 2.35 V. The LINE-SENSE pin current determined by the value of the resistor, and thus the input signal is used to trigger under/overvoltage thresholds for both the current (and indirectly the resistor value), select an internal standby and main converters. Assuming a LINE-SENSE pin current limit according to the following table. resistor of 4 MW, the standby will begin operating when the LINE-SENSE pin current exceeds the (I ) threshold, L(SB-UVON) nominally approximately 100 V. However the main is still held in I R (ThreFsBhold) ILIMIT F(B1(S%ELE)CT) the off-state, until the LINE-SENSE pin current exceeds the (I ) threshold, nominally 315 V for 4 MW. There is 0.0-5.1 mA L1 60% mA Open kW hLy(MsAte-UrVeOsNi)s for both main and standby undervoltage-off thresholds, to allow sufficient margin to avoid accidental 5.1-11.9 mA L2 80% mA 511.0 kW triggering, and to provide sufficient margin to meet hold-up time 11.9-23.8 mA L3 100% mA 232.0 kW requirements. Bear in mind that the main converter may start to loose regulation before it finally shuts down. This is because Table 3. FEEDBACK Pin Main Current Limit Selection. the dynamic duty cycle limit may clamp the duty cycle below that required for regulation at lower input voltages. Once the input voltage falls below the 215 V (I ) threshold, the UV(ON) , I = 25 µA L(MA_UVOFF) STANDBY (L) main will shutdown but standby will continue to operate. The standby will turn off when the input voltage drops below approximately 40 V (I ). L(SB-UVON) I(L) 4.7 V 6.0 V after standby 5.7 V acheives V(BP) regulation 1 V 2.7 V V (FB) V 2.2 V (EN) T - current limit selection occurs here during SELECT device start-up and before power supply switching PI-5975-102610 Figure 9. Current Limit Selection. 10 Rev. E 04/15 www.power.com

TFS757-764HG Standby Power General Introduction Supply Start-Up Sequence The standby is a wide range power supply, typically a flyback converter, operating over a wide input range (85-265 VAC) and VIN delivering up to 20 W continuous output power. The standby 385 V power supply provides two functions in most high-power 315 V applications. It provides a direct secondary output but also provide bias power to other primary-side devices (in particular typically a PFC boost converter). 100 V The HiperTFS standby retains most features of the TinySwitch-III, such as auto-restart, thermal shutdown, multi-level current limit 30 V ON/OFF control, etc. The HiperTFS standby controller has a few differences versus TinySwitch-III: Standby 1. There are 4 current limits that are selected via the ENABLE Output pin (rather than by using different BYPASS pin capacitors as in TinySwitch-III). There are 4 user selectable current limits 500, 550, 650, 750 mA design for secondary standby 12 ms 2-20 ms Main output power of 10, 12.5, 15 and 20 W. Output 2. Secondary OVP latching shutdown. This is triggered via a current in excess of the BYPASS pin latching shutdown threshold (I = 15 mA). BP(SD) 3. Dedicated LINE-SENSE pin for line-voltage detection providing absolute UV and OV ON/OFF thresholds (unlike TinySwitch-III 6.0 V VBP which detects input voltage only during restart). 4. Current limit is compensated as a function of input voltage 5.7 V 4.7 V to maintain a flat overload characteristic versus input voltage. PI-5611a-062710 In a high-power system, the standby power supply is the first power supply to begin operating. The main converter cannot Figure 10. Main and Standby Start-Up. begin working until the standby is in operation. Likewise the main converter will shutdown at a higher-voltage than the standby Main Reset Overvoltage Detection and thus the standby is always the last power supply to There is also an overvoltage threshold for the RESET pin. When shutdown. triggered, the RESET overvoltage will shutdown only the Main, leaving the Standby in operation. Standby On-Chip Current Limit with External Selection During start-up, the FEEDBACK pin and ENABLE pin are both used to select internal current limits for the Main and Standby converters respectively. The detection period occurs at the V initial start-up of the device (just after BYPASS pin voltage of IN To V 4.7 V is achieved), and before the main or standby MOSFETs 385 V IN To Clamp Reset Circuit start switching. This is done to minimize noise interference. 300 V R R L R I R 240 V R FS (ThreEsNhold) ILIMIT E(N1(S%ELE)CT) T L er Hip 0.0-8.5 mA L1 500 mA Open kW 40 V 8.5-17.7 mA L2 650 mA 280.0 kW 17.7-33.0 mA L3 750 mA 137.0 KW Standby Output 33.0-66.0 mA L4 550 mA 63.4 kW Table 4. ENABLE Pin Standby Current Limit Selection. t OuMtpauint ≥H O2L0D mUPs Tseycpoicnadllayr ytu srnuepde rovfifs obry circuit, once regulation below limit The ENABLE pin works in a similar way to the FEEDBACK pin selection. The only difference being that the ENABLE pin is not t t t t 1 2 3 4 clamped to 1 V during selection, instead remaining at 2.35 V PI-5612a-060910 during the detection period. Thus the selection resistor values Figure 11. L and R Pin Duty Limit Mode. 11 www.power.com Rev. E 04/15

TFS757-764HG are slightly different for the ENABLE pin versus the FEEDBACK However the standby will be forced to shutdown if this input pin. The ENABLE pin internal current selection is chosen voltage drops below approximately 40 V (as defined by I ). L(SB-UVOFF) according to the above table. Main and Standby Oscillator and Switching Frequency The current limit selection for both FEEDBACK pin and ENABLE The standby converter operates at a frequency of 132 kHz. The pin takes place when the BYPASS pin first reaches 4.7 V. Once main converter operates at exactly half that frequency at 66 kHz. the short detection period is complete, the BYPASS pin is The two converters both include a common frequency jitter ramped on up to 5.7 V, and the FEEDBACK pin is allowed to profile that varies the switching frequency ±4 kHz for the main float to it’s nominal voltage of 3.5 V. (twice the jitter frequency range ±8 kHz for the standby), during a 4 ms jitter period. The frequency jitter helps reduce quasi- Standby Line Compensated Current Limit peak and average EMI emissions. to Flatten Output Overload For many power supplies, the power output capability of the It should be noted that the HiperTFS has a collision avoidance power supply increases dramatically as the input voltage scheme in which the main converter is the master and the increases. This means that most power supplies are able to standby is the slave, which avoids the main and standby switching deliver much more power (up to 30-40% more power), into a at exactly simultaneous moments. The most common fault overload when operating at higher input voltage (versus condition would be close to 50% duty cycle, if the main (master) operating at lower input voltage). This can cause a problem is about to switch (turn-off), then the standby (slave), waits for since many specifications require that the output overload short instant (200 ns) before starting it’s next cycle. The power capability of the device is more tightly managed. standby is used as the slave, since the ON/OFF control of the HiperTFS standby is less easily disrupted by sudden delays in In the case of the HiperTFS, the standby current limit is adjusted switching, versus the linear control loop of the main converter. as a function of line (input voltage), in such a ways as to always provide substantially the same maximum overload power Standby and Main Thermal Shutdown capability. The input voltage is detected via the LINE-SENSE The HiperTFS provides a thermal shutdown function, (OTP) that pin current and the internal standby current limit of the device is protects the HiperTFS. This hysteretic thermal shutdown allows adjusted accordingly on a cycle-by-cycle basis. This means that the device to automatically recover from any thermal fault event. the HiperTFS standby will only deliver approximately 5% more The thermal shutdown is triggered at a die-temperature of overload power at high-line as it did at low-line. This feature approximately 118 °C and has a high hysteresis to ensure the provides a much safer design. average device temperature is within safe levels. In a well designed system the HiperTFS thermal shutdown is not 150 0 triggered during any normal operation and is only present as a 1 25 safety feature to protect against abnormal or fault conditions. wer (%) 114300 Not Compensated PI-5884-05 BThYeP BAYSPSA (SBSP )( BPPin) pOinp iesr tahteio snupply pin for the entire HiperTFS o P device. The BYPASS pin is internally connected to a high-voltage d 120 a current source via the STANDBY DRAIN power MOSFET. This o erl 110 high-voltage source will charge the BYPASS pin to 4.7 V during v initial power up. Once the BYPASS pin reaches 4.7 V, the O Compensated ut 100 BYPASS pin will check the main and standby current limit p selection (FEEDBACK pin and ENABLE pin resistors respectively). Out 90 This selection takes a very short period, thereafter the BYPASS pin continues being charged until it reaches 5.7 V, at which 80 point the standby power supply is ready to begin operation. 50 100 150 200 250 300 350 400 450 Like the TinySwitch-III the high-voltage current source will V DC (V) continue to charge the BYPASS pin if it droops below 5.7 V. IN However in most typical applications, a resistor (typically 7.5 kW) Figure 12. Shows Output Overload Power for Both Compensated and Uncompensated Standby Current Limits. is connected from primary bias (12 V) to the BYPASS pin. This resistor provides the operating current to the BYPASS pin, Standby Line Undervoltage Detection (UV) preventing the need to draw power from the high-voltage The LINE-SENSE pin resistor is connected to VIN and generates current source. Like the TinySwitch-III, the BYPASS pin contains a current signal proportional to VIN. The LINE-SENSE pin a shunt regulator, which will be enabled if the BYPASS pin voltage is held by the device at 2.35 V. The LINE-SENSE pin voltage is externally driven above 5.7 V. The BYPASS pin shunt current signal is used to trigger under/overvoltage thresholds for current is used for two functions: both the standby and main converters. Assuming a LINE-SENSE pin resistor of 4 MW, the standby will begin operating at 1. First, for a 4 mA threshold (I ) for main remote-on. When approximately 100 V (as defined by IL(SB_UVON)). The standby will the BYPASS pin current excBePe(OdN)s this threshold, the main is shutdown if regulation is lost when input voltage is below 100 V. enabled. 12 Rev. E 04/15 www.power.com

TFS757-764HG 2. Second a 15 mA threshold (I )for standby secondary OVP Output Power Table BP(SD) latch-off. When the BYPASS pin current exceeds this Two-Switched Forward Flyback threshold, the standby and main converters are latched-off. 380 V 100 V - 400 V This latch can be reset by pulling the LINE-SENSE pin below Product2 Continuous1 Continuous1 Peak the line undervoltage threshold (I ), or by discharging (25 °C) (50 °C) (50 °C) 50 °C L(SB-UVOFF) the BYPASS pin below 4.7 V. TFS757HG 193 W 163 W 228 W 20 W TFS758HG 236 W 200 W 278 W 20 W Note: unlike the TinySwitch-III the HiperTFS BYPASS pin capacitor TFS759HG 280 W 235 W 309 W 20 W does not provide any programming capability. Instead the TFS760HG 305 W 258 W 358 W 20 W recommended BYPASS pin capacitor should always be a 1 mF TFS761HG 326 W 276 W 383 W 20 W (ceramic) capacitor. TFS762HG 360 W 304 W 407 W 20 W TFS763HG 388 W 327 W 455 W 20 W Main and Standby Line Overvoltage Detection (OV) TFS764HG 414 W 344 W 530 W 20 W The overvoltage threshold is included in the device, and can be used to disable the device during overvoltage (with the use of Table 5. Output Power Table. Notes: an additional external signal Zener). The overvoltage threshold 1. Maximum practical continuous power in an open frame design with adequate is set sufficiently high to prevent accidental triggering during heat sinking (assuming heat sink θ of <4 °C/W), measured at specified C-A boost PFC overshoot conditions. When the overvoltage ambient temperature (see Key Applications Considerations for more information). condition is triggered, it will simultaneously shutdown both the 2. Package: eSIP16/12. (Note: Direct attach to heat sink, does not require insulation SIL pad) Main and Standby. The overvoltage feature is intended for use with external components (circuitry), to program the overvoltage threshold independently of the undervoltage thresholds (see the Applications section for details). High-Power eSIP Package The HiperTFS package is designed to minimize the physical size of the device, while maintaining a low thermal impedance and sufficient electrical spacing for the pins. The package has 12 functional pins with 4 pins removed for increased pin-to-pin spacing between high-voltage pins. The low-side two-switch forward and flyback MOSFETs have a thermal impedance of less than 1 °C/W to the exposed pad on the back of the package. Since this pad is referenced to the SOURCE pin (Source), it is at electrical ground potential and thus can be connected to the heat sink without need for electrical insulation. The high-side MOSFET is over-molded to achieve electrical isolation and thus also allows direct connection to the heat sink. 13 www.power.com Rev. E 04/15

TFS757-764HG Design, Assemble and Layout Considerations 80 Power Table 6700 PI-2576-010600 The data sheet power table (Table 1, page 1) represents the V) 50 maximum advised continuous power based on the following Bµ conditions; d 40 e ( d 30 1. +Ty5p Vic,a +l 3m.3u ltVi-, o-1u2tp Vu,t aPnCd m+a5i nV wstitahn tdhbey f.ollowing outputs +12 V, plitu 20 m 2. A boost regulated DC input for Main 300 VDC to 385 VDC A -10 minimum nominal of 375 VDC. 0 3. HiperTFS total efficiency at least 85% at full load. EN55022B (QP) -10 4. Schottky high-efficiency output diodes. EN55022B (AV) 5. DC input for Standby 130 VDC to 385 VDC. -20 6. Sufficient heat sinking and fan cooling to keep device 0.15 1 10 30 temperature below 100 °C. Frequency (MHz) 7. Transformer designed with nominal duty factor of 45%. Figure 13. Fixed Frequency Operation Without Jitter. HSomueiaptlexpeicumrtTti nuFpgmSo wt Sahemeer ,lob etpihcetetniimrotm ounample mHraaitpinneagrgT teFemSm edpneetpr,a e(thnuedraest. usOpinEokMnin tgahp,e ep ctlicoc.an), ttaiionnundso us V) 678000 PI-5856-030810 are typically 50 °C max ambient while clone PC supplies are µ 50 B usually specified at 25 °C ambient. Higher efficiency can be d 40 achieved with the larger devices. The maximum output power e ( d 30 can be tailored for any given device by programming primary u ILIMIT(MA). mplit 20 A -10 Hold-Up Time The input capacitor is a critical component in designing for a 0 guaranteed minimum hold-up time. Proper design of the EN55022B (QP) -10 transformer’s nominal duty cycle and sufficient primary winding EN55022B (AV) -20 clamp voltage for rest of Main transformer are also essential. 0.15 1 10 30 PIXLS (PI Expert Design Spreadsheet) can compute these values or refer to formula in AN-51. Frequency (MHz) Figure 14. Full Range EMI Scan (132 kHz with Jitter) With Identical Circuitry and Conditions. Bias Support for High-Side Driver Bias support for HiperTFS high-side switch is sourced from a forward phased winding of the Main transformer and should 150 V provide a minimum of 17 V at 300 VDC input (or minimum input +VBUS voltage at which regulation can be maintained) to guarantee the 12 V bias required for the high-side driver is maintained. HiperTFS VDDH Primary Bias Support The standby converter provides a minimum 17 V output that CONTROL HD biases the BYPASS pin of HiperTFS. It is also the source for R remote ON/OFF control and OVP. This output should be capable of delivering a minimum of 20 mA. The primary bias HS filter capacitor should be at 330 mF to hold up the bias during L DR1 the start-up transient. D FB Start-Up There is a duty factor soft-start function at start-up that slews EN from 30% duty factor to max duty factor in approximately 15 ms. The current limit during start-up is actually boosted by 115% for DSB the first 32 ms to provide the ability to drive heavy capacitive BP loads and meet less than 20 ms output rise time requirement. DR2 RTN G S PI-5846-111810 Figure 15. Typical Primary Winding Clamp-to-Rail. 14 Rev. E 04/15 www.power.com

TFS757-764HG HiperTFS VDDH CONTROL HD R HS L D FB ~50 Newtons EN DSB BP Minimum Clearance G S is 0.078 inches To Bulk PI-5883-032410 Capacitor PI-5882-111710 Figure 16. HiperTFS Layout Considerations. Figure 17. HiperTFS Heat Sink Mounting. EMI an over-molded, electrically isolated section of the package The frequency jitter feature modulates the switching frequency backside that provides isolation between the heat sink and the over a narrow band as a means to reduce conducted EMI internal high-side switch. Thermal heat sink compound, and a average and quasi-peaks associated with the harmonics of the mounting clip providing a minimum torque of 50 Newtons, are fundamental switching frequency. This is particularly beneficial required for good thermal performance. The heat sink for average conduction mode where the sampling bandwidth is temperature behind device should not exceed 95 °C to avoid narrow. The modulation rate is nominally 250 Hz which is high activating the over-temperature shutdown of HiperTFS. Since enough to reduce EMI but low enough to have negligible effect some of the HiperTFS pins are bent towards the heat sink, there on output ripple (rejected by control loop). needs to be a minimum of 0.078 inches clearance between heat sink and PC board. Transformer Design It is recommended that the transformer be designed for a Layout Considerations maximum flux density of 3000 Gauss during continuous maximum output power and a maximum peak transient flux Use a single point connection between, SOURCE pin, GROUND density no greater than 4000 Gauss. The turns ratio should be pin and bypass capacitor. Typically the bypass capacitor is a chosen for a nominal duty factor of 45% at 385 VDC input to surface mount type and is located directly under the HiperTFS guarantee transformer reset with typical primary winding package between the GROUND pin and the BYPASS pin. clamp-to-rail (Figure 15). For nominal duty factor of higher value it is recommend to refer to AN-51 and use PIXLS spreadsheet The FEEDBACK pin and ENABLE pin along with the LINE- for optimal transformer design. Typically the transformer should SENSE and RESET pins should be kept away from noisy, high have foil secondary windings for outputs above 10 amps. The voltage switching areas. If it is unavoidable to have long traces primary winding should be split primary type to keep leakage connecting to FEEDBACK pins then route these traces close to inductance low. quiet, low impedance traces, that act as a Faraday shield. The LINE-SENSE and RESET pins are associated with multiple Standby Mode Consumption series resistor sections due to the high-voltage sensing. Make The HiperTFS standby converter is essentially a TinySwitch-III sure the last resistor in series chain is SMD type and place it controller which uses whole-cycle ON/OFF control. This has the very close to the pin. This will minimize the pick-up of noise. benefit of operating at a low average frequency at lighter loads which increases efficiency and reducers no-load consumption. The primary auxiliary bias output rectifier and filter should be star referenced to bulk capacitor. Any Y capacitors referenced Heat Sinking to DC primary should also be tied to quiet nodes of bulk The HiperTFS package is eSIP-16/12. There is a metal exposed capacitor negative or positive terminal. pad that provides a low thermal path to the heat sink for the low-side power device and standby power device. There is also 15 www.power.com Rev. E 04/15

TFS757-764HG V IN R1 VHIGH_BIAS R1_MAX = VHIGH_BIAS –VDDH 1 mA Minimum Supply Current to V = V = 14 V HIGH_BIAS_(MIN) AUX_(MIN) VDDH = 1 mA C C HiperTFS VDDH 1 2 CONTROL HD Main Transformer R C HS R1 L D FB EN DSB Standby Transformer V AUX BP C 3 G S PI-5881-082610 Figure 18. High-Side Bias. HiperTFS VDDH V OUT VOUT(OV) = (15 mA × R1) + V1 + 1 CONTROL HD R R 1 HS V BIAS L IC1 D (CTR = 1) FB EN V 1 DSB BP I ≥ 15 mA OVP GG SS PI-5879-111710 Figure 19. Latching Output OVP. 16 Rev. E 04/15 www.power.com

TFS757-764HG V V BIAS IN V = V + 1 V OUT(OV) 1 R1 HiperTFS VDDH V OUT CONTROL HD R V - V HS R1 ≤ AIUX CE_OP TO L L(MA_OVOFF) 12 V- 0.3 V R ≤ D 1 146 µA FB EN V 1 DSB BP G S PI-5878-111710 Figure 20. Non-Latching Output OVP. Standby Out VBIAS IREMOTE_MIN = 1 mA HiperTFS VDDH CONTROL HD R REM I = 900 µA HS STANDBY_MIN L R 3 10 kΩ Q1 R2 D FB Remote ON VON 13 V R4 EN 1 kΩ R 1 6 V DSB BP I = 5 mA ON_MIN G S V - 6.7 V V - 6 V R1 = ON5 mA R2 = AU9X0(M0IN µ) A PI-5877-111710 Figure 21. Remote ON and Standby Bias. 17 www.power.com Rev. E 04/15

TFS757-764HG V IN V BIAS R 2 100 kΩ 3.9 MΩ HiperTFS VDDH 10 kΩ Q1 CONTROL HD R R 1 90 kΩ HS L D VR1 FB 300 kΩ (+12 V) EN R + R = 4 MΩ 1 2 DSB V I = IN(OV) L(OV) R + R BP 1 2 VR1- 1.9 V R1 = I G S L(OV) PI-5876-111710 Figure 22. Input OVP (Latching). V IN V BIAS R 2 3.9 MΩ 100 kΩ HiperTFS VDDH 10 kΩ CONTROL HD R1 R 90 kΩ HS VR1 L 20 kΩ (+12 V) D FB R + R = 4 MΩ EN 1 2 V DSB I = IN(OV) L(OV) R1 + R2 BP VR1- 1.9 V R = 1 I G S L(OV) PI-5875-111710 Figure 23. Non-latching Input OVP. 18 Rev. E 04/15 www.power.com

TFS757-764HG HiperTFS VDDH CONTROL HD R V BIAS HS L L 6.8 MΩ D 100 kΩ FB AC Input EN N 6.8 MΩ DSB 1 MΩ Q2 BP 0.1 µF 1 MΩ Q1 G S PI-5874-111710 Figure 24. Fast AC Reset of BP Latch. R1 = R2 = 4 MΩ 150 V R1 R2 HiperTFS VDDH CONTROL HD R HS L D FB EN DSB BP G S PI-5873-020411 Figure 25. L and R Pin Reset and Duty Limit Circuit. 19 www.power.com Rev. E 04/15

TFS757-764HG L and R Pin Transformer Reset and Forward Duty Clamp Protection Duty Regulation (FB) Factor duty cycle Hard limit 60% Reset duty clamp To V IN To Clamp Available Reset Circuit duty cycle range RL RR S R F T L er This region for p transient response Forward duty Hi clamp 45% 75 µA 100 µA L Pin Current PI-5880-111710 (300 V) (385 V) (V with RL = 4 MΩ) IN Figure 26. L and R Pin Duty Limit With R = 4 MW and R = 4 MW. L R Applications Example The standby section is designed to operate whether the boost PFC stage is on or off. The standby therefore is designed to High Efficiency +12 V, 25 A Main Output and +5 V 2.5 A operate from 100 VDC to 385 VDC which covers the normal Standby Power Supply universal input of 90 VAC to 265 VAC. The circuit in Figure 26 is an example of a design using HiperTFS providing a 300 W +12 V output forward derived Main converter The start-up sequence is initiated with HiperTFS charging the and a 12 W +5 V Standby output from the flyback controller of BYPASS pin capacitor via internal high-voltage current source. HiperTFS. The very high integration of two full converters within Current limit selection then follows via FEEDBACK pin and a single package immediately shows the result of very low ENABLE pin resistors. The HiperTFS then senses the input external parts count for the entire design. Both the main voltage via the LINE-SENSE pin resistor series chain R12, R13, converter and the flyback section of HiperTFS are designed to R35. When the input voltage reaches 100 V VDC the LINE- give very high-efficiency. The main converter takes advantage SENSE pin UV standby threshold is reached and the standby of the ability to operate above 50% duty factor which lowers converter turns on. After several milliseconds the standby RMS switch currents and allows using lower voltage more output will reach regulation and the primary V +12 V bias will ON efficient Schottky diodes on the output. The flyback section be stable. When the input bulk voltage reaches 315 VDC uses Power Integrations TinySwitch technology which is often which is the UV threshold for the main converter, the main used in designs that demand high-efficiency and low no-load converter will initiate a turn on sequence once the remote-on input power consumption. command from secondary is activated. The remote-on switch (SW1) on the secondary-side for this particular design allows The design in Figure 27 is intended to work with a PFC boost the user to manually activate that main converter by turning on front end that nominally provides a 385 VDC input. The main the remote-on optocoupler. In actual PC designs the remote- converter will regulate to full load between 300 VDC and 385 on would be controlled by a computer start-up command. This VDC. This voltage range guarantees greater than 20 ms hold-up optocoupler sources 5 mA into the BYPASS pin of the HiperTFS time with C1 (270 mF). which is the threshold current to start the turn on sequence for 20 Rev. E 04/15 www.power.com

TFS757-764HG the Main converter. The Main converter will first turn on the saturation of the transformer is completely avoided in all conditions bottom switch to allow the high-side drive to receive the boot- including brownout and load transients. The LINE- SENSE pin strap bias. After 14 ms the Main converter will start switching also has a UV low threshold which turns off the Main converter both switches at 66 kHz and the main output voltage will rise. when the input voltage is below 215 V. Once the regulator U5 becomes active, current will flow through the optocoupler U1. The collector of U1 will sink current out of This design in particular is intended to operate with a minimum the FEEDBACK pin to adjust for appropriate duty cycle to of 30 CFM airflow at full load. maintain regulation. The normal operating sink current is between 1 mA and 2 mA. There is a forward phased bias Both the main and standby output have overvoltage protection winding off the main transformer that provides sustained bias from sense circuit around U4 which will source >15 mA during for the high-side driver. During normal and brownout operation fault into bypass pin to cause latching shut-off of both converters. the RESET pin senses the turn off clamp voltage via the resistor The standby uses auto-restart to protect the standby output chain R6, R18, R19 and the internal controller determines the from overpower and over-current. The main output is current maximum safe duty factor by comparing the RESET pin current limited by the selected internal primary current limit of the main with the LINE-SENSE pin current. This features guarantees that switch path. J3-1 380 VDC ZMMV5R2412B-7 ZMMV5R2320B-7 F2 12 V 12 V 4.7 V 5 V 4 A 1.3R31 M2Ω P6KVER135100RA06 Ω 34.C3.R7 27n ΩF4.R75 Ω 11NNDD4430400077 2.R21 Ω 27C01 µF U4APC817XI1JD0F 10R03 Ω 1D5R204 Ω 1.3R31 M3Ω 4.R78 Ω R2 1k4Ω 1TMAIN13,14 3.3L 1µH +R1T2N V 1ND51430*4 4PR.7C2 k80Ω1U73XB1J00F 7R.51 k6Ω 8R201 7Ω 1.3R33 M5Ω 11..R33R3131 9 M8MΩ TFS7U7662HGCO1N3TRVODLDH 1H6D 10C06 nF 10BC0AD3 Vn5F20 M60M660D0C76-0EDC36-/4E53/45 7R5P012CR 5 Ω8k2Ω11U7X1AI115JR0 k90ΩF 102CR024 11n 0FΩ 4437RC.32 15n3 C1kF0Ω100 µF 33C0011 µF J4-1 4R.72 k2ΩMVRM4BQT14401BAS1RD1 k261Ω3H0T1GP2C3R8221 Uk57Ω4XB1J00F 1.3R33 M6ΩF1RBL90 11HDU4SFD48005 T262STANDB9Y19,01,C10001 3nF 4R72 Ω6 LMU4531 1C n92F.21L 02µC0H8 nF3.R922 4kΩ RTN MMSZ1532 4V3BT1G F4BR702 9Ω 28R02 k7Ω EB1NP18 D3SB 1 STPDS111045B 1R002 8Ω 47C01 4nF RemotSe+W 5O 1NV/OFF 1C 1n8F PC81U7X1BI1J00FEN 1C 1n9F 1C 1µ2F 5G 6S UFD49005 2C.22 n1F 22C0107 µF PC81U7X2AI1J00F 1R k3Ω0 4.R753 4kΩ 22C0105 µF 4R.73 k2Ω PC81U7X2BI1J00F D12 1R k3Ω3 J3-3 3134C0 2- 0µ2F5 V RGP10053 6,7 LMU4731 33C01 6nF 4.R753 1kΩ PC81U7X3AI1J00F PI-5969-102810 RTN *Optional component for accidental reverse connection Figure 27. Schematic of High-Efficiency +12 V, 25 A Main Output and +5 V, 2.5 A Standby Power Supply. 21 www.power.com Rev. E 04/15

TFS757-764HG Ð HV + Y Capacitor F1 C21 J3 + C1 C13 D8 D7 L1 C3D5 R14 C6 12 D1 R25 R 1 R35 D9 Transformer R C16 72 R13 C10+ VR3 R2C1 R36 6 C2 R7R8 R15 D HF LC Post-Filter D4 1 5 1 R1R9RC2C4 0 C11+ R6 D3 R18 R1 R21C8 R24 J1 TP1 T2 C13C9R26 Ð 12 V 2 D1 C17 1 + R C20 V 2 + R J2 4 V 1 5 V J4 D10C18 R16 VRR429 U2 R30R3C316R28U7R31R34 L2 C15 R4 Ð R22 0 U3 C R17 R23 R2 U4 R3 R32 SW1 D2 C7 PI-5872-042710 Figure 28. Layout of High-Efficiency +12 V, 25 A Main Output and +5 V, 2.5 A Standby Power Supply. 22 Rev. E 04/15 www.power.com

TFS757-764HG Absolute Maximum Ratings(1,5) DRAIN Voltage High-Side MOSFET .......................-0.3 V to 530 V Feedback (FB) Current ................... .................................100 mA DRAIN Peak Current High-Side: TFS757 ...................3.1 (5.9)4 A Line Sense (L) Pin Voltage ............................................-0.3 V to 9 V TFS758 ...................4.5 (8.4)4 A Line Sense (L) Pin Current ............................................ .......100 ma TFS759 ...................5.0 (9.3)4 A Reset (R) Pin Voltage ..................... ...........................-0.3 V to 9 V TFS760 .................5.7 (10.7)4 A Reset (R) Pin Current ..................................... ....................100 mA TFS761 ..................6.1 (11.4)4 A Bypass Supply (BP) Pin Voltage ...............................-0.3 V to 9 V TFS762 ..................6.4 (12.1)4 A Bypass Supply (BP) Pin Current ................................... .....100 mA TFS763 .................7.2 (13.4)4 A High Side (VDDH) Supply Pin Voltage ................. -0.3 V to 13.4 V TFS764 .................8.3 (15.5)4 A High Side (VDDH) Supply Pin Current ..................................50 mA DRAIN Voltage Low-Side MOSFET ....................-0.3 V to 725 V Storage Temperature ............................................ -65 °C to 150 °C DRAIN Peak Current Low-Side: TFS757 ...................3.1 (5.9)4 A Operating Junction Temperature(2).......................-40 °C to 150 °C TFS758 ...................4.5 (8.4)4 A Lead Temperature(3) ................................................................. 260 °C TFS759 ...................5.0 (9.3)4 A Notes: TFS760 .................5.7 (10.7)4 A 1. All voltages referenced to SOURCE, T = 25 °C. J TFS761 ..................6.1 (11.4)4 A 2. Normally limited by internal circuitry. TFS762 ..................6.4 (12.1)4 A 3. 1/16 in. (1.59 mm) from case for 5 seconds. TFS763 .................7.2 (13.4)4 A 4. The higher peak DRAIN current is allowed while the DRAIN TFS764.................8.3 (15.5)4 A voltage is simultaneously less than 400 V. DRAIN Voltage Standby MOSFET ......................-0.3 V to 725 V 5. Maximum ratings specified may be applied one at a time, DRAIN Peak Current Standby MOSFET ................1.20 (2.25)4 A without causing permanent damage to the product. Enable (EN) Pin Voltage ..................... .......................-0.3 V to 9 V Exposure to Absolute Rating conditions for extended periods Enable (EN) Pin Current ................. .................................100 mA of time may affect product reliability. Feedback (FB) Pin Voltage ................. ......................-0.3 V to 9 V Thermal Resistance High-Side MOSFET (θ ) TFS757, TFS758 ....................15 °C/W Low-Side MOSFET (θ ) ................................................1 °C/W JC JC TFS759, TFS760 ....................14 °C/W Notes: TFS761, TFS762 ....................13 °C/W 1. All voltages referenced to SOURCE, T = 25 °C. A TFS763, TFS764 ....................12 °C/W Conditions Parameter Symbol SOURCE = 0 V; T = 0 °C to 100 °C Min Typ Max Units J (Unless Otherwise Specified) Control Functions Switching Frequency Average 62 66 70 f T = 25 °C kHz – PC Main S(MA) J Peak-to-Peak Jitter 4 Frequency Jitter f 250 Hz Modulation Rate M(MA) Remote-ON Main BYPASS Pin I V = Open 3.2 3.8 4.4 mA Remote-ON Current BP(ON) EN BYPASS Pin Remote- I 1.1 mA OFF Current Hysteresis BP(OFF) BYPASS Pin Latching I 13 15.5 17.5 mA Shutdown Threshold BP(SD) Main/Standby Remote- t 2.5 ms ON Delay R(ON) Main/Standby Remote- t 2.5 ms OFF Delay R(OFF) Main/Standby Remote- t 80 ms OFF Long Time Period R(PERIOD) Soft-Start High-Side Start-Up t 14 ms Charge Time D(CH) Main Current Limit I See Note A 115 % at Start-Up LIM(SS) Soft-Start Period 12 ms 23 www.power.com Rev. E 04/15

TFS757-764HG Conditions Parameter Symbol SOURCE = 0 V; T = 0 °C to 100 °C Min Typ Max Units J (Unless Otherwise Specified) FEEDBACK Pin -1800 mA < I < -1500 mA, I = 60 mA, PWM Gain DC FB L -70 %/mA REG(MA) I = 160 mA R PWM Gain TC 0.05 %/°C Temperature Drift DCREG FEEDBACK Pin Feed- I -1.1 mA back Onset current FB(ON) I = 60 mA, I = 170 mA L R FEEDBACK Pin Current T = 25 °C I J -2.1 mA at Zero Duty Cycle FB(OFF) FEEDBACK Pin P 12 kHz Internal Filter Pole FB FEEDBACK Pin Voltage V I , I = I 3.56 V FB FB (OFF) FB FB(ON) LINE-SENSE Pin (Line Voltage) I Threshold 21.0 25.0 29.5 Line Undervoltage L(SB-UVON) T = 25 °C mA Threshold – Standby J I Threshold 8.7 10.5 12.7 L(SB-UVOFF) I Threshold 76 80 84 Line Undervoltage L(MA-UVON) T = 25 °C mA Threshold – Main J I Threshold 47 53 58 L(MA-UVOFF) Line Overvoltage I Threshold 119 135 146 L(MA-OVON) Threshold – Main T = 25 °C mA J and Standby I Threshold 135 146 164 L(MA-OVOFF) I = 79 mA 2.25 2.4 2.55 LINE-SENSE Pin L V T = 25 °C V Voltage L J I = 149 mA 2.45 2.6 2.75 L LINE-SENSE Pin I V = V 375 mA Short-Circuit L(SC) L BP RESET Pin (Duty Limit/Main Only Remote-OFF) I Threshold 165 205 245 Reset Overvoltage R(MA-OVON) T = 25 °C mA Threshold J I Threshold 175 215 255 R(MA-OVOFF) RESET Pin Voltage V I = 155 mA 2.5 V R R RESET Pin Short- I V = V 375 mA Circuit Current R(SC) R BP I = 100 mA, I = 110 mA 50.5 L R DC Duty Cycle – LIMIT(MA) I = 115 mA, I = 140 mA 47.5 % Programmable Limit L R DC I = 100 mA, I = 170 mA 63 MAX(MA) L R Current Limit Programming FEEDBACK Pin Start-up Current Limit I 0-5 mA LIM(1)(MA) See Note C Detection Range #1 FEEDBACK Pin Start-up Current Limit I 5-12 mA LIM(2)(MA) See Note C Detection Range #2 FEEDBACK Pin Start-up Current Limit I 12-24 mA LIM(3)(MA) See Note C Detection Range #3 24 Rev. E 04/15 www.power.com

TFS757-764HG Conditions Parameter Symbol SOURCE = 0 V; T = 0 °C to 100 °C Min Typ Max Units J (Unless Otherwise Specified) Maximum Current Limit I di/dt = 175 mA/ms 1.02 LIM(1)(MA) TFS757 I di/dt = 233 mA/ms 1.36 LIM(2)(MA) T = 25 °C I J di/dt = 291 mA/ms 1.58 1.70 1.82 LIM(3)(MA) I di/dt = 250 mA/ms 1.45 LIM(1)(MA) TFS758 I di/dt = 335 mA/ms 1.95 LIM(2)(MA) T = 25 °C I J di/dt = 420 mA/ms 2.28 2.45 2.62 LIM(3)(MA) I di/dt = 258 mA/ms 1.62 LIM(1)(MA) TFS759 I di/dt = 344 mA/ms 2.16 LIM(2)(MA) T = 25 °C I J di/dt = 430 mA/ms 2.55 2.70 2.94 LIM(3)(MA) I di/dt = 324 mA/ms 1.86 LIM(1)(MA) TFS760 I di/dt = 432 mA/ms 2.48 LIM(2)(MA) T = 25 °C I J di/dt = 540 mA/ms 2.88 3.10 3.30 Current Limit LIM(3)(MA) A I di/dt = 338 mA/ms 1.95 LIM(1)(MA) TFS761 I di/dt = 450 mA/ms 2.65 LIM(2)(MA) T = 25 °C I J di/dt = 564 mA/ms 3.07 3.30 3.53 LIM(3)(MA) I di/dt = 360 mA/ms 2.10 LIM(1)(MA) TFS762 I di/dt = 480 mA/ms 2.80 LIM(2)(MA) T = 25 °C I J di/dt = 600 mA/ms 3.25 3.50 3.75 LIM(3)(MA) I di/dt = 402 mA/ms 2.35 LIM(1)(MA) TFS763 I di/dt = 402 mA/ms 3.10 LIM(2)(MA) T = 25 °C I J di/dt = 670 mA/ms 3.60 3.90 4.16 LIM(3)(MA) I di/dt = 468 mA/ms 2.70 LIM(1)(MA) TFS764 I di/dt = 624 mA/ms 3.60 LIM(2)(MA) T = 25 °C I J di/dt = 780 mA/ms 4.18 4.50 4.81 LIM(3)(MA) Low-Side Main MOSFET TFS757 T = 25 °C 4.87 5.60 J I = I T = 100 °C 7.69 9.05 D LIM(3)(MA) J TFS758 T = 25 °C 3.25 3.73 J I = I T = 100 °C 4.90 5.83 D LIM(3)(MA) J TFS759 T = 25 °C 2.35 2.70 J I = I T = 100 °C 3.60 4.21 D LIM(3)(MA) J TFS760 T = 25 °C 1.96 2.24 J ON-State R ID = ILIM(3)(MA) TJ = 100 °C 2.80 3.29 W Resistance DS(ON) TFS761 T = 25 °C 1.60 1.85 J I = I T = 100 °C 2.30 2.75 D LIM(3)(MA) J TFS762 T = 25 °C 1.40 1.60 J I = I T = 100 °C 2.00 2.35 D LIM(3)(MA) J TFS763 T = 25 °C 1.20 1.40 J I = I T = 100 °C 1.70 2.05 D LIM(3)(MA) J TFS764 T = 25 °C 1.10 1.26 J I = I T = 100 °C 1.53 1.80 D LIM(3)(MA) J TFS757 150 TFS758 150 OFF-State Drain TFS759 V, V = 0 V, I = 6 mA, 150 I L R BP mA Leakage Current DSS(D) TFS760 V = 560 V, T = 100 °C 150 DS J TFS761 470 TFS762 470 25 www.power.com Rev. E 04/15

TFS757-764HG Conditions Parameter Symbol SOURCE = 0 V; T = 0 °C to 100 °C Min Typ Max Units J (Unless Otherwise Specified) Low-Side Main MOSFET (cont.) OFF-State Drain TFS763 V, V = 0 V, I = 6 mA, 470 I L R BP mA Leakage Current DSS(D) TFS764 V = 560 V, T = 100 °C 470 DS J Breakdown V, V = 0 V, I = 6 mA, BV L R BP 725 V Voltage DSS(D) T = 25 °C J Rise Time t 100 ns R(D) Fall Time t 50 ns F(D) High-Side Main MOSFET TFS757 T = 25 °C 1.76 J I = I T = 100 °C 2.12 D LIM(3)(MA) J TFS758 T = 25 °C 1.15 J I = I T = 100 °C 1.40 D LIM(3)(MA) J TFS759 T = 25 °C 0.88 J I = I T = 100 °C 1.06 D LIM(3)(MA) J TFS760 T = 25 °C 0.88 J I = I T = 100 °C 1.06 ON-State Resistance R D LIM(3)(MA) J W DS(ON)(HD) TFS761 T = 25 °C 0.69 J I = I T = 100 °C 0.84 D LIM(3)(MA) J TFS762 T = 25 °C 0.58 J I = I T = 100 °C 0.7 D LIM(3)(MA) J TFS763 T = 25 °C 0.46 J I = I T = 100 °C 0.56 D LIM(3)(MA) J TFS764 T = 25 °C 0.46 J I = I T = 100 °C 0.56 D LIM(3)(MA) J TFS757 55 TFS758 82 TFS759 110 Effective Output TFS760 T = 25 °C, V = 0 V 110 C J GS pF Capacitance OSS(EFF)(HD) TFS761 V = 0 V to 80% V 140 DS DSS(HD) TFS762 165 TFS763 205 TFS764 205 Breakdown Voltage BV T = 25 °C 530 V DSS(HD) J TFS757 60 TFS758 60 TFS759 60 OFF-State Drain TFS760 V = 424 V, 60 I D mA Current Leakage DSS(HD) TFS761 T = 100 °C 65 J TFS762 80 TFS763 110 TFS764 110 Turn-on Voltage t 30 ns Rise Time R(HD) Turn-off Voltage t 25 ns Fall Time F(HD) 26 Rev. E 04/15 www.power.com

TFS757-764HG Conditions Parameter Symbol SOURCE = 0 V; T = 0 °C to 100 °C Min Typ Max Units J (Unless Otherwise Specified) High-Side Main MOSFET (cont.) High-Side Bias See Note B V 11.4 12.1 12.8 V Shunt Voltage DDH(SHUNT) I = 2 mA DDH High-Side Undervoltage V See Note B 10.7 11.1 11.5 V ON-Threshold DDH(UVON) High-Side Undervoltage V See Note B 9.5 9.9 10.3 V OFF-Threshold DDH(UVOFF) High-Side Shunt V See Note B 0.7 1.2 1.5 V Hysteresis Voltage DDH(HYST) Standby MOSFET ON-State T = 25 °C 3.7 4.37 R I = I J W Resistance DS(ON)(DS) DSB LIM(3)(DSB) T = 100 °C 5.5 6.25 J V = 6.2 V BP V = 0 V I EN 200 DSS1(DS) V = 560 V OFF-State Drain TD S= 100 °C mA Leakage Current J V = 6.2 V V = 375 V, I BP DS 15 DSS2(DS) V = 0 V T = 50 °C EN J V = 6.2 V, V = 0 V, Breakdown Voltage BV BP EN 725 V DSS(DS) T = 25 °C J DRAIN Supply Voltage V 50 V DSB(START) Standby Controller Output Frequency Average 124 132 140 f T = 25 °C kHz in Standard Mode S(SB) J Peak-to-peak Jitter 8 Maximum Duty Cycle DC I = 40 mA 67 70 73 % MAX(DSB) L ENABLE Pin Upper Turnoff Threshold I -150 -115 -80 mA DIS Current I = 25 mA 2.0 2.4 2.8 ENABLE Pin Voltage V EN V EN I = -25 mA 0.8 1.2 1.6 EN V = 0 V, I BP -5 -3.2 -2 CH1 T = 25 °C BYPASS Pin J mA Charge Current V = 4 V, I BP -4 -1.5 0 CH2 T = 25 °C J BYPASS Pin Voltage V V = 50 V 5.50 5.70 5.90 V BP DS BYPASS Pin Voltage V 0.80 1.0 1.20 V Hysteresis BP(HYST) BYPASS Pin Shunt V I = 2 mA 5.8 6.0 6.2 V Voltage BP(SHUNT) BP Standby Circuit Protection ENABLE Pin Current I Start-up 0-8.5 mA Limit Selection Range #1 LIM(1)(DSB) 27 www.power.com Rev. E 04/15

TFS757-764HG Conditions Parameter Symbol SOURCE = 0 V; T = 0 °C to 100 °C Min Typ Max Units J (Unless Otherwise Specified) Standby Circuit Protection (cont.) ENABLE Pin Current I Start-up 8.5-18 mA Limit Selection Range #2 LIM(2)(DSB) ENABLE Pin Current I Start-up 18-33 mA Limit Selection Range #3 LIM(3)(DSB) ENABLE Pin Current I Start-up 33-60 mA Limit Selection Range #4 LIM(4)(DSB) I I = 20 mA, di/dt = 95 mA/ms, T = 25 °C 450 500 550 LIM(1)(DSB) L J I I = 20 mA, di/dt = 125 mA/ms, T = 25 °C 600 650 700 LIM(2)(DSB) L J mA I I = 20 mA, di/dt = 143 mA/ms, T = 25 °C 675 750 825 Standby Current Limit LIM(3)(DSB) L J I I = 20 mA, di/dt = 105 mA/ms, T = 25 °C 495 550 605 LIM(4)(DSB) L J I (I = 100 mA) / I (I = 20 mA) ΔI LIM L LIM L 80 % LIM di/dt = 125 mA/ms General Circuit Protection I2f = I × f Power Coefficient I2f LIM(2)(DSB)(TYP) S(SB)(OSC)(TYP) 0.9 × I2f I2f 1.12 × I2f A2Hz T = 25 °C J 0.75 × Initial Current Limit I T = 25 °C INIT J I LIM(MIN) Leading Edge t T = 25 °C 170 215 ns Blanking Time (Main) LEB(D) J Leading Edge Blanking t T = 25 °C 170 215 ns Time (Standby) LEB(DSB) J Current Limit t T = 25 °C 150 ns Delay (Main) ILD(D) J Current Limit t T = 25 °C 150 ns Delay (Standby) ILD(DSB) J Thermal Shutdown T 118 °C Temperature SD Thermal Shutdown T 55 °C Hysteresis SD(HYST) Auto-Restart ON-Time t T = 25 °C 64 ms at f Standby AR J OSC Auto-Restart Duty DC T = 25 °C 2.2 % Cycle Standby AR J Supply Current EN Current > I I DIS 400 750 1000 S1 (No MOSFETs Switching) DRAIN Supply Current mA EN Open (Standby MOSFET I 600 950 1200 S2 Switching at f ) NOTES: OSC A. The current limit is boosted for the first 34 ms of main supply switching and returns to normal level after this period. B. V minus V is equal to 250 mV minimum. DDH(SHUNT) DDH(UV_ON) C. Level 1 R = open, Level 2 R = 511 kW, Level 3 R = 232 kW. FB FB FB D. Level 1 R = open, Level 2 R = 280 kW, Level 3 R = 137 kW, Level 4 R = 63.4 kW. EN EN EN EN 28 Rev. E 04/15 www.power.com

TFS757-764HG Typical Performance Characteristics e wn Voltage C)°1.1 PI-5998-060210 own VoltagC)1.1 PI-5999-060210 do25 kd5 ° Pin Breakmalized to 1.0 N Pin Breaalized to 21.0 AIN Nor RAIorm R( DN D Y ( N B MAI 0.9 ND 0.9 -50 -25 0 25 50 75 100 125 150 A T -50 -25 0 25 50 75 100 125 150 S Junction Temperature (°C) Junction Temperature (°C) Figure 29. Main Supply. Breakdown Voltage vs. Temperature. Figure 30. Standby Supply. Breakdown vs. Temperature. y c put Frequencyo 25 C)°110...208 PI-6000-060210 Output Frequen o 25 °C)110...208 PI-6001-060210 AIN Pin Outormalized t00..64 DRAIN Pin ormalized t00..64 DR(N0.2 BY (N0.2 N D AI AN M 0 T 0 -50 -25 0 25 50 75 100 125 150 S -50 -25 0 25 50 75 100 125 Junction Temperature (°C) Junction Temperature (° C) Figure 31. Main Supply. Frequency vs. Temperature. Figure 32. Standby Supply. Frequency vs. Temperature. rrent Limit25 C)°110...208 PI-6002-060210 Current Limit25 C)°110...208 PI-6003-060210 Cuo n o AIN Pin malized t00..64 DRAIN Pimalized t 00..64 DRNor BY Nor AIN (0.2 ND( 0.2 A M T S 0 0 -50 -25 0 25 50 75 100 125 150 -50 -25 0 25 50 75 100 125 150 Junction Temperature (°C) Junction Temperature (°C) Figure 33. Main Supply. Internal Current Limit vs. Temperature. Figure 34. Standby Supply. External Current Limit vs. Temperature with R = 10.5 kW IL 29 www.power.com Rev. E 04/15

TFS757-764HG Typical Performance Characteristics (cont.) ervoltageo 25 C)°11..20 PI-5959-060210 54 PI-5955-051210 ndd t V) DRAIN Pin Ud (Normalize000...864 Pin Voltage ( 23 Y ol L Bh NDres0.2 1 Ah TT S 0 -50 -25 0 25 50 75 100 125 0 0 20 40 60 80 100 120 140 160 Junction Temperature (°C) L Pin Current (μA) Figure 35. Standby Supply. Undervoltage Threshold vs. Junction Temperature. Figure 36. L Pin Voltage vs. L Pin Current. 5 1 age (V) 43 PI-5954-050510 Current (mA) -01 PI-5953-051210 Volt Pin -2 n 2 K Pi C -3 R BA D 1 E -4 E F 0 -5 0 50 100 150 200 250 0 1 2 3 4 5 6 7 R Pin Current (μA) FEEDBACK Pin Voltage (V) Figure 37. R Pin Voltage vs. R Pin Current. Figure 38. FEEDBACK Pin Current vs. FEEDBACK Pin Voltage. A)µ540000 PI-5952-051210 mA) 30 PI-5951-050510 ent (300 ent ( 20 r r r r u200 u C C n n Pi100 Pi E S 10 L S B 0 A A P N Y E-100 B -200 0 0 1 2 3 4 5 6 7 0.0 2.0 4.0 6.0 8.0 ENABLE Pin Voltage (V) BYPASS Pin Voltage (V) Figure 39. ENABLE Pin Current vs. ENABLE Pin Voltage. Figure 40. BYPASS Pin Current vs. BYPASS Pin Voltage. 30 Rev. E 04/15 www.power.com

TFS757-764HG Typical Performance Characteristics (cont.) A) 30 PI-5950-012711 10705 PI-5949-052510 m %) nt ( 20 e ( rre ycl 50 u C H C uty D 10 D D 25 V 0 0 0 4 8 12 16 -50 -25 0 25 50 75 100 125 VDDH Votage (V) Temperature (°C) Figure 41. VDDH Current vs. VDDH Voltage. Figure 42. Duty Cycle vs. Temperature (T = 100 mA, J = 110 mA). J R 2.5 10705 PI-5948-052510 A) 2 PI-5942-060110 %) nt ( e ( re 1.5 cl ur y 50 C uty C AIN 1 T = 25 °C D 25 DR TCCAASSEE = 100 °C .5 0 0 0 2 4 6 8 10 12 14 16 18 20 -50 -25 0 25 50 75 100 125 STANDBY DRAIN Voltage (V) Temperature (°C) Figure 43. Duty Cycle vs. Temperature (I = 115 mA, I = 140 mA) Figure 44. Standby Supply. Output Characteristics. L R 45 PI-5943-091010 pF)1000 PI-5944-060110 nt (A) nce ( 100 e 3 a Curr TSFcaSl7in5g7 Fac0to.4rs: pacit RAIN 2 TTTFFFSSS777556890 001...680 N Ca 10 D TFS761 1.2 AI 1 TFS762 1.4 R TFS763 1.6 D T = 25 °C TFS764 1.8 CASE T = 100 °C CASE 0 0 0 100 200 300 400 500 600 0 2 4 6 8 10 12 14 16 18 20 DRAIN Voltage (V) STANDBY DRAIN Pin Voltage (V) Figure 45. Drain Supply. Output Characteristics. Figure 46. Standby Supply. Drain Capacitance vs. Drain Voltage. 31 www.power.com Rev. E 04/15

TFS757-764HG Typical Performance Characteristics (cont.) pF)10000 TTTSFFFcaSSSl777in555g789 Fac000to...468rs: PI-5945-091010 225000 PI-5946-060110 e ( TFS760 1.0 132 kHz pacitanc1000 TTTT FFFFSSSS777766661234 1111....2468 er (mW) 150 a w 100 C o N 100 P AI R 100 D 10 0 0 100 200 300 400 500 600 0 100 200 300 400 500 600 700 DRAIN Pin Voltage (V) STANDBY DRAIN Pin Voltage (V) Figure 47. Main Supply. Drain Capacitance vs. Drain Voltage. Figure 48. Standby Supply. Power vs. Drain Voltage. 540000 TTTSFFFcaSSSl777in555g789 Fac000to...468rs: PI-5947-091010 A) 1250 TTJJ == 2150 0° C°C 25 °C 100 °C PI-5970-091010 mW) 300 TTTFFFSSS777666012 111...024 ent ( Power ( 200 TT FFSS776634 11..68 AIN Curr 10 TSFcaSl7in5g7 Fac t o 0rs.1:7 R TFS758 0.25 66 kHz D 5 TFS759/760 0.33 100 TFS761 0.42 TFS762 0.50 TFS763/764 0.63 0 0 0 100 200 300 400 500 600 700 0 1 2 3 4 5 6 7 DRAIN Pin Voltage (V) DRAIN Voltage (V) Figure 49. Main Supply. Power vs. Drain Voltage. Figure 50. High-Side MOSFET Drain Current vs. Drain Voltage. 1000 PI-5971-083110 eC)1.1 PI-5972-051210 g° a5 F) Volto 2 (pS wn ed t1.0 S oz CO TSFcaSl7in5g7 Fac t o 0rs.1:7 akdmali TFS758 0.25 reor TFS759/760 0.33 BN TFS761 0.42 ( TFS762 0.50 TFS763/764 0.63 100 0.9 0 100 200 300 400 -50 -25 0 25 50 75 100 125 150 Drain Voltage (VHD-VHS) Temperature (°C) Figure 51. High-Side MOSFET Drain Current vs. Drain Voltage. Figure 52. High-Side MOSFET Breakdown Voltage vs. Temperature. 32 Rev. E 04/15 www.power.com

TFS757-764HG Typical Performance Characteristics (cont.) 2 TTSFFcaSSl77in55g78 Fac t o r00s..:1275 PI-5973-083110 1.5 TFS759/760 0.33 TFS761 0.42 W) TFS762 0.50 m TFS763/764 0.63 r ( 1 e w o 66 kHz P 0.5 0 0 100 200 300 400 DRAIN Voltage (VD) Figure 53. High-Side MOSFET Power vs. Drain Voltage. 33 www.power.com Rev. E 04/15

TFS757-764HG 0.381 (9.68)Ref. 0.201 (5.11)Ref. 0.519 (13.18)Ref. 0.207 (5.26)0.187 (4.75) 13141110716563189 430.024 (0.61)12×0.019 (0.48)0.076 (1.93)0.010 M 0.25 M C A B0.012 (0.30) Ref. BACK VIEW0.1140.152(2.91)(3.88) 79111451 6 0.164(4.18) 381016130.114(2.91)0.0760.0760.0760.1140.114(1.94)(1.94)(1.94)(2.91)(2.91) MOUNTING HOLE PATTERN (N.T.S)All dimensions in inches (mm) es of the plastic body exclusive of mold flash, tie bar burrs, gate burrs, and inter-d bottom of the plastic body. Maximum mold protrusion is 0.007 (0.18) per side. PI-5300-021411 mn eSIP-16B (H Package) C 0.081 (2.06)0.077 (1.96) Detail A0.290 (7.37)Ref. 0.016 (0.41)Ref.3.56)3.05) 350.016 (0.41)12×0.011 (0.28)0.020 M 0.51 M C 0.118 (3.00)118 (3.00) SIDE VIEW 0.020 (0.50) 0.023 (0.58) 0.027 (0.70) Detail A (N.T.S)Notes:1. Dimensioning and tolerancing per ASME Y14.5M-1994. 2. Dimensions noted are determined at the outermost extre lead flash, but including any mismatch between the top a3. Dimensions noted are inclusive of plating thickness.4. Does not include interlead flash or protrusions. 5. Pin #6 is the only straight (unformed) lead.6. Controlling dimensions in inches (mm).7 8. Tied to SOURCE (pin 6). 9. Tied to HS (pin 14). 10 11. Tied to HD (pin 16). B B 20.325 (8.25)0.320 (8.13) 0.140 (0.120 ( 16 0.056 (1.42) Ref. 0. 10° Ref.All Around 0.021 (0.53)0.019 (0.48) 0.048 (1.22)0.046 (1.17) 0.235 (5.96) Ref.0.167 (4.24) Ref.0.101 (2.57) Ref. 0.012 (0.30) Typ. 110.035 (0.89) Ref. W B-BMetal Tie-Bars 0.653 (16.59)0.647 (16.43)2 Pin 1 I.D. 131411107956318 5 0.038 (0.97) FRONT VIEW 9 (0.48) Ref. 0.060 (1.52) Ref. 5 0.628 (15.95) Ref. BOTTOM-END VIEW 020 (0.51) Ref. 870.041 (1.04) Ref.90.010 (0.25) Typ.10 n 1 TOP-END VIELocation of Exposed A 01 0. Pi 0. B 34 Rev. E 04/15 www.power.com

TFS757-764HG Part Ordering Information Part Number Option Quantity TFS757HG Tube 30 TFS758HG Tube 30 TFS759HG Tube 30 TFS760HG Tube 30 TFS761HG Tube 30 TFS762HG Tube 30 TFS763HG Tube 30 TFS764HG Tube 30 Part Marking Information • HiperTFS Product Family • TFS Series Number • Package Identifier H Plastic eSIP-16B • Pin Finish G Halogen Free and RoHS Compliant TFS 757 H G 35 www.power.com Rev. E 04/15