ICGOO在线商城 > 分立半导体产品 > 晶体管 - FET,MOSFET - 单 > STQ2LN60K3-AP

- 型号: STQ2LN60K3-AP

- 制造商: STMicroelectronics

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

STQ2LN60K3-AP产品简介:

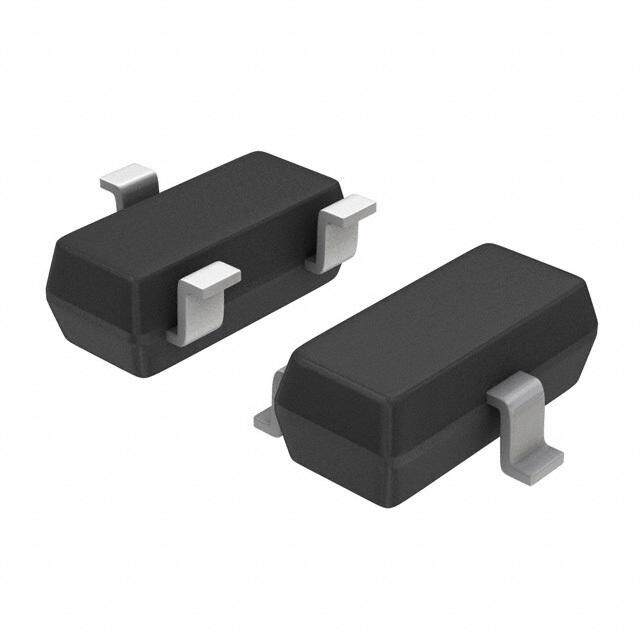

ICGOO电子元器件商城为您提供STQ2LN60K3-AP由STMicroelectronics设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 STQ2LN60K3-AP价格参考。STMicroelectronicsSTQ2LN60K3-AP封装/规格:晶体管 - FET,MOSFET - 单, 通孔 N 沟道 600V 600mA(Tc) 2.5W(Tc) TO-92-3。您可以下载STQ2LN60K3-AP参考资料、Datasheet数据手册功能说明书,资料中有STQ2LN60K3-AP 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | |

| ChannelMode | Enhancement |

| 描述 | MOSFET N CH 600V 600MA TO-92MOSFET N-Ch 600V 4 Ohm 0.6A SuperMESH3 FET TO92 |

| 产品分类 | FET - 单分离式半导体 |

| FET功能 | 标准 |

| FET类型 | MOSFET N 通道,金属氧化物 |

| Id-ContinuousDrainCurrent | 600 mA |

| Id-连续漏极电流 | 600 mA |

| 品牌 | STMicroelectronics |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 晶体管,MOSFET,STMicroelectronics STQ2LN60K3-APSuperMESH3™ |

| 数据手册 | |

| 产品型号 | STQ2LN60K3-AP |

| Pd-PowerDissipation | 2.5 W |

| Pd-功率耗散 | 2.5 W |

| Qg-GateCharge | 12 nC |

| Qg-栅极电荷 | 12 nC |

| RdsOn-Drain-SourceResistance | 4.5 Ohms |

| RdsOn-漏源导通电阻 | 4.5 Ohms |

| Vds-Drain-SourceBreakdownVoltage | 600 V |

| Vds-漏源极击穿电压 | 600 V |

| Vgs-Gate-SourceBreakdownVoltage | 30 V |

| Vgs-栅源极击穿电压 | 30 V |

| Vgsth-Gate-SourceThresholdVoltage | 4.5 V |

| Vgsth-栅源极阈值电压 | 4.5 V |

| 上升时间 | 8.5 ns |

| 下降时间 | 21 ns |

| 不同Id时的Vgs(th)(最大值) | 4.5V @ 50µA |

| 不同Vds时的输入电容(Ciss) | 235pF @ 50V |

| 不同Vgs时的栅极电荷(Qg) | 12nC @ 10V |

| 不同 Id、Vgs时的 RdsOn(最大值) | 4.5 欧姆 @ 1A,10V |

| 产品种类 | MOSFET |

| 供应商器件封装 | TO-92 |

| 其它名称 | 497-13391-3 |

| 其它有关文件 | http://www.st.com/web/catalog/sense_power/FM100/CL824/SC1167/PF254012?referrer=70071840 |

| 典型关闭延迟时间 | 23.5 ns |

| 功率-最大值 | 2.5W |

| 包装 | 带盒(TB) |

| 商标 | STMicroelectronics |

| 安装类型 | 通孔 |

| 安装风格 | Through Hole |

| 封装 | Ammo Pack |

| 封装/外壳 | TO-226-3、TO-92-3(TO-226AA)成形引线 |

| 封装/箱体 | TO-92-3 |

| 工厂包装数量 | 2000 |

| 晶体管极性 | N-Channel |

| 标准包装 | 2,000 |

| 漏源极电压(Vdss) | 600V |

| 电流-连续漏极(Id)(25°C时) | 600mA (Tc) |

| 系列 | STQ2LN60K3-AP |

| 通道模式 | Enhancement |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

STQ2LN60K3-AP N-channel 600 V, 4 Ω typ., 0.6 A MDmesh™ K3 Power MOSFET in a TO-92 package Datasheet - production data Features Order code VDS RmDSa(oxn ) ID PTOT STQ2LN60K3-AP 600 V 4.5 Ω 0.6 A 2.5 W 3 100% avalanche tested 2 Extremely high dv/dt capability 1 Very low intrinsic capacitance TO-92 ammopack Improved diode reverse recovery characteristics Zener-protected Figure 1: Internal schematic diagram Applications D(2) Switching applications Description This MDmesh™ K3 Power MOSFET is the result of improvements applied to STMicroelectronics’ G(1) MDmesh™ technology, combined with a new optimized vertical structure. This device boasts an extremely low on-resistance, superior dynamic performance and high avalanche capability, rendering it suitable for the most demanding applications. S(3) AM15572v1_no_tab Table 1: Device summary Order code Marking Package Packaging STQ2LN60K3-AP 2LN60K3 TO-92 Ammopack February 2017 DocID023499 Rev 3 1/13 This is information on a product in full production. www.st.com

Contents STQ2LN60K3-AP Contents 1 Electrical ratings ............................................................................. 3 2 Electrical characteristics ................................................................ 4 2.1 Electrical characteristics (curves) ...................................................... 6 3 Test circuits ..................................................................................... 9 4 Package information ..................................................................... 10 4.1 TO-92 ammopack package information .......................................... 10 5 Revision history ............................................................................ 12 2/13 DocID023499 Rev 3

STQ2LN60K3-AP Electrical ratings 1 Electrical ratings Table 2: Absolute maximum ratings Symbol Parameter Value Unit VDS Drain-source voltage 600 V VGS Gate-source voltage ±30 V ID Drain current (continuous) at TC = 25 °C 0.6 A ID Drain current (continuous) at TC = 100 °C 0.38 A IDM (1) Drain current (pulsed) 2.4 A PTOT Total dissipation at TC = 25 °C 2.5 W dv/dt (2) Peak diode recovery voltage slope 12 V/ns Tstg Storage temperature range -55 to 150 °C Tj Operating junction temperature range Notes: (1)Pulse width limited by safe operating area. (2)ISD ≤ 2 A, di/dt ≤ 400 A/µs, VDS(peak) < V(BR)DSS Table 3: Thermal data Symbol Parameter Value Unit Rthj-case Thermal resistance junction-case 50 °C/W Rthj-amb Thermal resistance junction-ambient 120 °C/W Table 4: Avalanche characteristics Symbol Parameter Value Unit Single pulse avalanche current IAS (pulse width limited by Tjmax) 2 A Single pulse avalanche energy EAS 80 mJ (starting TJ=25 °C, ID=IAR, VDD=50 V) DocID023499 Rev 3 3/13

Electrical characteristics STQ2LN60K3-AP 2 Electrical characteristics (T = 25 °C unless otherwise specified) CASE Table 5: On/off states Symbol Parameter Test conditions Min. Typ. Max. Unit Drain-source V(BR)DSS ID = 1 mA, VGS = 0 V 600 V breakdown voltage VGS = 0 V, VDS = 600 V 1 Zero gate voltage drain IDSS current VGS = 0 V, VDS = 600 V, 50 µA TC= 125 °C (1) IGSS Gate-body leakage current VDS = 0 V, VGS = ±20 V ±10 µA VGS(th) Gate threshold voltage VDS = VGS, ID = 50 µA 3 3.75 4.5 V Static drain-source on- RDS(on) resistance VGS = 10 V, ID = 1 A 4 4.5 Ω Notes: (1)Defined by design, not subject to production test. Table 6: Dynamic Symbol Parameter Test conditions Min. Typ. Max. Unit Ciss Input capacitance - 235 - pF Coss Output capacitance VDS = 50 V, f = 1 MHz, - 22 - pF Reverse transfer VGS = 0 V Crss capacitance - 3.5 - pF Eq. capacitance time Co(tr)(1) related - 14 - pF VGS = 0 V, VDS = 0 to 480 V Eq. capacitance energy Co(er)(2) related - 10 pF Qg Total gate charge VDD = 480 V, ID = 1 A, - 12 - nC Qgs Gate-source charge VGS = 0 to 10 V - 1.8 - nC (see Figure 16: "Test circuit for Qgd Gate-drain charge gate charge behavior") - 7.7 - nC RG Gate input resistance f=1 MHz, ID=0 A - 7 - Ω Notes: (1)Coss eq. time related is defined as a constant equivalent capacitance giving the same charging time as Coss when VDS increases from 0 to 80% VDSS (2)Coss eq. energy related is defined as a constant equivalent capacitance giving the same stored energy as Coss when VDS increases from 0 to 80% VDSS 4/13 DocID023499 Rev 3

STQ2LN60K3-AP Electrical characteristics Table 7: Switching times Symbol Parameter Test conditions Min. Typ. Max. Unit td(on) Turn-on delay time VDD = 300 V, ID = 1 A, - 10 - ns tr Rise time RG = 4.7 Ω, VGS = 10 V - 8.5 - ns (see Figure 15: "Test circuit for td(off) Turn-off delay time resistive load switching times" - 23.5 - ns and Figure 20: "Switching time tf Fall time waveform") - 21 - ns Table 8: Source-drain diode Symbol Parameter Test conditions Min. Typ. Max. Unit ISD(1) Source-drain current - 0.6 A Source-drain current ISDM(1) (pulsed) - 2.4 A VSD(2) Forward on voltage ISD = 2 A, VGS = 0 V - 1.5 V trr Reverse recovery time ISD = 2 A, di/dt = 100 A/µs - 200 ns Qrr Reverse recovery charge VDD = 60 V - 800 nC (see Figure 17: "Test circuit for inductive load switching and IRRM Reverse recovery current - 8 A diode recovery times") trr Reverse recovery time ISD = 2 A, di/dt = 100 A/µs - 230 ns Qrr Reverse recovery charge VDD = 60 V, Tj = 150 °C - 950 nC (see Figure 17: "Test circuit for inductive load switching and IRRM Reverse recovery current - 8.5 A diode recovery times") Notes: (1)Pulse width limited by safe operating area. (2)Pulsed: pulse duration = 300 µs, duty cycle 1.5% Table 9: Gate-source Zener diode Symbol Parameter Test conditions Min. Typ. Max. Unit V(BR)GSO Gate-source breakdown voltage IGS= ±1 mA, ID= 0 A 30 - - V The built-in back-to-back Zener diodes are specifically designed to enhance the ESD performance of the device. The Zener voltage facilitates efficient and cost-effective device integrity protection,thus eliminating the need for additional external componentry. DocID023499 Rev 3 5/13

Electrical characteristics STQ2LN60K3-AP 2.1 Electrical characteristics (curves) Figure 2: Safe operating area Figure 3: Thermal impedance Figure 4: Output characteristics Figure 5: Transfer characteristics ID AM13054v1 ID AM13055v1 (A) (A) VGS=10V VDS=15V 2.5 2.0 2.0 1.5 6V 1.5 1.0 1.0 0.5 0.5 5V 0 0 0 2 4 6 8 VDS(V) 0 2 4 6 8 VGS(V) Figure 6: Gate charge vs gate-source voltage Figure 7: Static drain-source on-resistance VGS AMV13D0S56v1 RDS(on) AM13057v1 (V) VDD=480V (V) (W) VGS=10V 12 ID=2A 4.2 500 VDS 10 4.0 400 8 3.8 300 6 3.6 200 4 3.4 2 100 3.2 0 0 3.0 0 5 10 Qg(nC) 0 0.2 0.4 0.6 0.8 1.0 1.2 ID(A) 6/13 DocID023499 Rev 3

STQ2LN60K3-AP Electrical characteristics Figure 8: Capacitance variations Figure 9: Source-drain diode forward characteristics C AM13058v1 AM13063v1 VSD(V) (pF) TJ=-50°C 0.9 TJ=25°C Ciss 0.8 0.7 100 TJ=150°C 0.6 0.5 0.4 10 Coss 0.3 0.2 Crss 0.1 1 0 0.1 1 10 100 VDS(V) 0 1 2 3 4 5 ISD(A) Figure 10: Normalized gate threshold voltage vs Figure 11: Normalized on-resistance vs temperature temperature VGS(th) AM13060v1 RDS(on) AM13061v1 (norm) ID=50µA (norm) ID=1A 1.10 VGS=10V 2.5 1.00 2.0 1.5 0.90 1.0 0.80 0.5 0.70 0 -75 -25 25 75 125 TJ(°C) -75 -25 25 75 125 TJ(°C) Figure 12: Normalized V(BR)DSS vs temperature Figure 13: Output capacitance stored energy V(BR)DSS AM13062v1 Eoss AM13059v1 (norm) (µJ) ID=1mA 1.10 1.5 1.05 1 1.00 0.5 0.95 0.90 0 -75 -25 25 75 125 TJ(°C) 0 100 200 300 400 500 600 VDS(V) DocID023499 Rev 3 7/13

Electrical characteristics STQ2LN60K3-AP Figure 14: Maximum avalanche energy vs temperature AM13064v1 EAS(mJ) 90 ID=2 A 80 VDD=50 V 70 60 50 40 30 20 10 0 0 20 40 60 80 100 120 140TJ(°C) 8/13 DocID023499 Rev 3

STQ2LN60K3-AP Test circuits 3 Test circuits Figure 15: Test circuit for resistive load Figure 16: Test circuit for gate charge switching times behavior Figure 17: Test circuit for inductive load Figure 18: Unclamped inductive load test switching and diode recovery times circuit Figure 19: Unclamped inductive waveform Figure 20: Switching time waveform DocID023499 Rev 3 9/13

Package information STQ2LN60K3-AP 4 Package information In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK® is an ST trademark. 4.1 TO-92 ammopack package information Figure 21: TO-92 ammopack package outline T A1 T2 T1 H1 delta H H H3 H0 d L W2 l1 W W0 W1 F1 F2 F3 D0 t P2 P0 0050910_Rev_22 10/13 DocID023499 Rev 3

STQ2LN60K3-AP Package information Table 10: TO-92 ammopak mechanical data mm Dim. Min. Typ. Max. A1 4.80 T 3.80 T1 1.60 T2 2.30 d 0.45 0.47 0.48 P0 12.50 12.70 12.90 P2 5.65 6.35 7.05 F1, F2 2.40 2.50 2.94 F3 4.98 5.08 5.48 delta H -2.00 2.00 W 17.50 18.00 19.00 W0 5.50 6.00 6.50 W1 8.50 9.00 9.25 W2 0.50 H 18.50 21.00 H0 15.50 16.00 18.20 H1 25.00 27.00 H3 0.50 1.00 2.00 D0 3.80 4.00 4.20 t 0.90 L 11.00 I1 3.00 delta P -1.00 1.00 DocID023499 Rev 3 11/13

Revision history STQ2LN60K3-AP 5 Revision history Table 11: Document revision history Date Revision Changes 19-Jul-2012 1 First release. Modified title, features and description on cover page Modified Table 2: "Absolute maximum ratings", Table 5: "On/off states" and Table 9: "Gate-source Zener diode" 24-Jan-2017 2 Modified: Figure 11: "Normalized on-resistance vs temperature" Updated Section 4.1: "TO-92 ammopack package information" Minor text changes Modified Figure 2: "Safe operating area". 01-Feb-2017 3 Minor text changes. 12/13 DocID023499 Rev 3

STQ2LN60K3-AP IMPORTANT NOTICE – PLEASE READ CAREFULLY STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST’s terms and conditions of sale in place at the time of order acknowledgement. Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers’ products. No license, express or implied, to any intellectual property right is granted by ST herein. Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product. ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners. Information in this document supersedes and replaces information previously supplied in any prior versions of this document. © 2017 STMicroelectronics – All rights reserved DocID023499 Rev 3 13/13

Datasheet下载

Datasheet下载

,TO-226_straightlead.jpg)