ICGOO在线商城 > 集成电路(IC) > 接口 - 串行器,解串行器 > SN65LVDS301ZQER

- 型号: SN65LVDS301ZQER

- 制造商: Texas Instruments

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

SN65LVDS301ZQER产品简介:

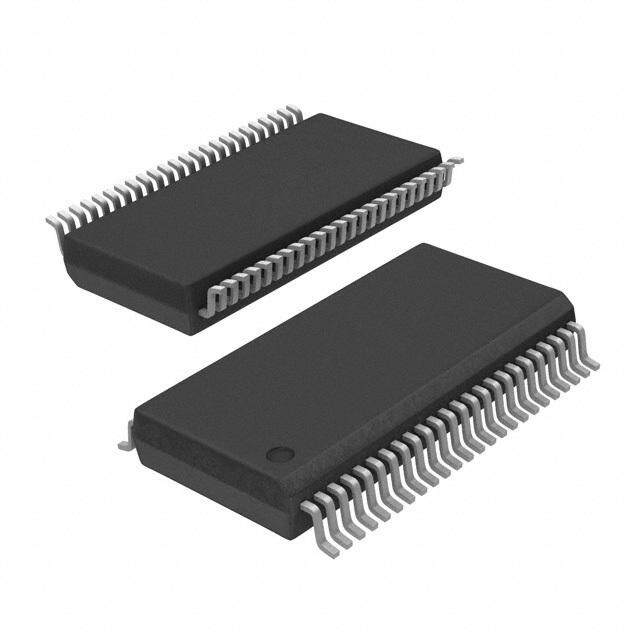

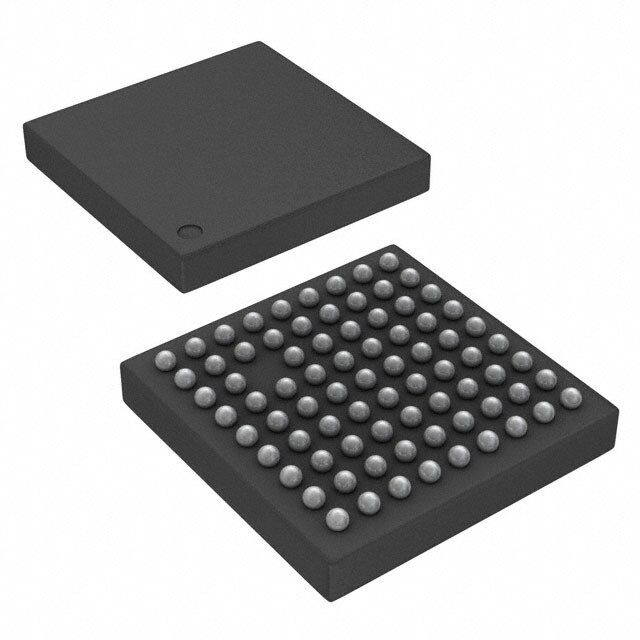

ICGOO电子元器件商城为您提供SN65LVDS301ZQER由Texas Instruments设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 SN65LVDS301ZQER价格参考¥38.52-¥38.52。Texas InstrumentsSN65LVDS301ZQER封装/规格:接口 - 串行器,解串行器, 1.755Gbps Serializer 24 Input 3 Output 80-BGA MICROSTAR JUNIOR (5x5)。您可以下载SN65LVDS301ZQER参考资料、Datasheet数据手册功能说明书,资料中有SN65LVDS301ZQER 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC) |

| 描述 | IC PROG 27BIT SERDES TX 80-BGA |

| 产品分类 | |

| 品牌 | Texas Instruments |

| 数据手册 | |

| 产品图片 |

|

| 产品型号 | SN65LVDS301ZQER |

| rohs | 无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 65LVDS |

| 供应商器件封装 | 80-BGA MICROSTAR JUNIOR(5x5) |

| 其它名称 | 296-21491-6 |

| 功能 | 串行器 |

| 包装 | Digi-Reel® |

| 安装类型 | 表面贴装 |

| 封装/外壳 | 80-VFBGA |

| 工作温度 | -40°C ~ 85°C |

| 数据速率 | 1.755Gbps |

| 标准包装 | 1 |

| 电压-电源 | 1.65 V ~ 1.95 V |

| 输入数 | 24 |

| 输入类型 | CMOS |

| 输出数 | 3 |

| 输出类型 | LVDS |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

SN65LVDS301 www.ti.com SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 PROGRAMMABLE 27-BIT DISPLAY SERIAL INTERFACE TRANSMITTER CheckforSamples:SN65LVDS301 FEATURES FPC cabling typically interconnects the 1 SN65LVDS301 with the display. Compared to parallel • FlatLink™3Gserialinterfacetechnology 23 signaling, the LVDS301 outputs significantly reduce • CompatiblewithFlatLink3Greceiverssuchas the EMI of the interconnect by over 20 dB. The SN65LVDS302 electromagnetic emission of the device itself is very • Inputsupports24-bitRGBvideomode low and meets the meets SAE J1752/3 'M'-spec. (see Figure37) interface • 24-BitRGBData,3ControlBits,1ParityBit The SN65LVDS301 supports three power modes and2ReservedBitsTransmittedover1,2or3 (Shutdown, Standby and Active) to conserve power. When transmitting, the PLL locks to the incoming DifferentialLines pixel clock PCLK and generates an internal high- • SubLVDSDifferentialVoltageLevels speed clock at the line rate of the data lines. The • EffectiveDataThroughputupto1755Mbps parallel data are latched on the rising or falling edge • ThreeOperatingModestoConservePower of PCLK as selected by the external control signal CPOL. The serialized data is presented on the serial – Active-ModeQVGA17.4mW(typ) outputs D0, D1, D2 with a recreated PCLK generated – Active-ModeVGA28.8mW(typ) from the internal high-speed clock, output on the CLK – ShutdownMode ≉≉0.5μA(typ) output. If PCLK stops, the device enters a standby modetoconservepower – StandbyMode ≉≉0.5μA(typ) • BusSwapforIncreasedPCBLayoutFlexibility The parallel (CMOS) input bus offers a bus-swap feature. The SWAP pin configures the input order of • 1.8-VSupplyVoltage the pixel data to be either R[7:0]. G[7:0], B[7:0], VS, • ESDRating> 2kV(HBM) HS, DE or B[0:7]. G[0:7], R[0:7], VS, HS, DE. This • TypicalApplication:Cameras,Embedded gives a PCB designer the flexibility to better match Computers the bus to the host controller pinout or to put the transmitter device on the top side or the bottom side • PixelClockRangeof4MHz–65MHz ofthePCB. • FailsafeonallCMOSInputs • Packaging:80Pin5mm× 5mmμBGA® • VerylowEMImeetsSAEJ1752/3'M'-spec DESCRIPTION The SN65LVDS301 serializer device converts 27 parallel data inputs to 1, 2, or 3 Sub Low-Voltage Differential Signaling (SubLVDS) serial outputs. It loads a shift register with 24 pixel bits and 3 control bits from the parallel CMOS input interface. In addition to the 27 data bits, the device adds a parity bit and two reserved bits into a 30-bit data word. Each word is latched into the device by the pixel LCD clock (PCLK). The parity bit (odd parity) allows a LLVVDDSoSr331042 rreecgeisivteerristoupdleotaedcetdsiantgl3e0,b1it5e,rororr1s0. Ttimheessethriealpsixheifl-t ViwdAPeiptrohop clICinceMatsetsOiroofaSnrce LLVVDDoSSr330111 DCALTKA clock data rate depending on the number of serial links used. A copy of the pixel clock is output on a separatedifferentialoutput. 1 Pleasebeawarethatanimportantnoticeconcerningavailability,standardwarranty,anduseincriticalapplicationsof TexasInstrumentssemiconductorproductsanddisclaimerstheretoappearsattheendofthisdatasheet. FlatLinkisatrademarkofTexasInstruments. 2 μBGAisaregisteredtrademarkofTessera,Inc.. 3 PRODUCTIONDATAinformationiscurrentasofpublicationdate. Copyright©2006–2012,TexasInstrumentsIncorporated Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarilyincludetestingofallparameters.

SN65LVDS301 SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 www.ti.com This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriateprecautions.Failuretoobserveproperhandlingandinstallationprocedurescancausedamage. ESDdamagecanrangefromsubtleperformancedegradationtocompletedevicefailure.Precisionintegratedcircuitsmaybemore susceptibletodamagebecauseverysmallparametricchangescouldcausethedevicenottomeetitspublishedspecifications. DESCRIPTION (CONTINUED) Two Link Select lines LS0 and LS1 control whether 1, 2 or 3 serial links are used. The TXEN input may be used to put the SN65LVDS301 in a shutdown mode. The SN65LVDS301 enters an active Standby mode if the input clock PCLK stops. This minimizes power consumption without the need for controlling an external pin. The SN65LVDS301 is characterized for operation over ambient air temperatures of –40°C to 85°C. All CMOS inputs offer failsafe features to protect them from damage during power-up and to avoid current flow into the device inputs during power-up. An input voltage of up to 2.165 V can be applied to all CMOS inputs while V is DD between0Vand1.65V. FunctionalBlockDiagram Parity Calc D0+ SWAP SubLVDS n o D0− Bit29 si r e 1 Bit28=0 v n o Bit27=0 c al D1+ ri SubLVDS 0 se 8 o D1− R[0:7] [0..26] el t all G[0:7] 8 par D2+ bit SubLVDS − D2− 8 0 B[0:7] 3 x 1 r o 5, HS 1 x 2 0, VS 1 3x CLK+ SubLVDS DE CLK− PCLK 0 iPCLK x10, x15, or x30 1 x1 PLL multiplier CPOL LS0 LS1 Control / Glitch standby Monitor TXEN supression 2 SubmitDocumentationFeedback Copyright©2006–2012,TexasInstrumentsIncorporated ProductFolderLinks:SN65LVDS301

SN65LVDS301 www.ti.com SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 PINOUT - TOP VIEW SWAP PIN FUNCTIONALITY The SWAP pin allows the pcb designer to reverse the RGB bus to minimize potential signal crossovers in the PCBrouting.ThetwodrawingsbeneathshowtheRGBsignalpinassignmentbasedontheSWAP-pinsetting. Copyright©2006–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback 3 ProductFolderLinks:SN65LVDS301

SN65LVDS301 SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 www.ti.com 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 A A G2 G4 G6 R0 R2 R4 R6 G5 G3 G1 B7 B5 B3 B1 B B G0 G1 G3 G5 G7 R1 R3 R5 R7 G7 G6 G4 G2 G0 B6 B4 B2 B0 C C B6 B7 R1 R0 SN65LVDS301 D D SN65LVDS301 B4 B5 R3 R2 E Top View E Top View B3 R4 F F B1 B2 R6 R5 G G PCLK B0 PCLK R7 H H HS VS HS VS J J DE SWAP DE SWAP SWAP=1 SWAP=0 1.8V Figure1.SWAPPIN=0 Figure2.SWAPPIN=1 Table1.NUMERICPINLIST PIN SWAP SIGNAL PIN SWAP .. SIGNAL PIN SWAP SIGNAL A1 — GND 0 B6 0 B1 C1 F1 0 G2 1 R1 1 R6 A2 1 G5 0 B7 0 B2 C2 F2 0 G4 1 R0 1 R5 A3 1 G3 C3 UNPOPULATED F3 — VDD 0 G6 C4 — VDD F4 — GND A4 1 G1 C5 — GND F5 — GND 0 R0 C6 — VDD F6 — GND A5 1 B7 C7 — VDD F7 — GND 0 R2 C8 — GND F8 — V DDPLLD A6 1 B5 C9 — LS0 F9 — D1+ 0 R4 0 B4 G1 — PCLK A7 D1 1 B3 1 R3 0 B0 G2 0 R6 0 B5 1 R7 A8 D2 1 B1 1 R2 G3 — V DD A9 — GND D3 — VDD G4 — GND 0 G0 D4 — GND G5 — GND B1 1 G7 D5 — GND G6 — GND 0 G1 D6 — GND G7 — GND B2 1 G6 D7 — GND G8 — GND LVDS 0 G3 D8 — LS1 G9 — D1– B3 1 G4 D9 — D2+ H1 — HS 0 G5 0 B3 H2 — VS B4 E1 1 G2 1 R4 H3 — GND 0 G7 E2 — GND H4 — GND LVDS B5 1 G0 E3 — VDD H5 — V DDLVDS 4 SubmitDocumentationFeedback Copyright©2006–2012,TexasInstrumentsIncorporated ProductFolderLinks:SN65LVDS301

SN65LVDS301 www.ti.com SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 Table1.NUMERICPINLIST(continued) PIN SWAP SIGNAL PIN SWAP .. SIGNAL PIN SWAP SIGNAL 0 R1 E4 — GND H6 — GND PLLA B6 1 B6 E5 — GND H7 — V DDPLLA 0 R3 E6 — GND H8 — V DDLVDS B7 1 B4 E7 — GND H9 — CPOL 0 R5 E8 — GND J1 — GND PLLD B8 1 B2 E9 — D2– J2 — DE 0 R7 J3 — TXEN B9 1 B0 J4 — D0– J5 — D0+ J6 — CLK– J7 — CLK+ J8 — SWAP J9 — GND LVDS Copyright©2006–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback 5 ProductFolderLinks:SN65LVDS301

SN65LVDS301 SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 www.ti.com TERMINALFUNCTIONS NAME I/O DESCRIPTION D0+,D0– SubLVDSDataLink(activeduringnormaloperation) SubLVDSDataLink(activeduringnormaloperationwhenLS0=highandLS1=low,or D1+,D1– LS0=lowandLS1=high;highimpedanceifLS0=LS1=low) SubLVDSOut SubLVDSDataLink(activeduringnormaloperationwhenLS0=lowandLS1=high, D2+,D2– high-impedancewhenLS1=low) CLK+,CLK– SubLVDSoutputClock;clockpolarityisfixed R0–R7 RedPixelData(8);pinassignmentdependsonSWAPpinsetting G0–G7 GreenPixelData(8);pinassignmentdependsonSWAPpinsetting B0–B7 BluePixelData(8);pinassignmentdependsonSWAPpinsetting HS HorizontalSync VS VerticalSync DE DataEnable PCLK InputPixelClock;risingorfallingclockpolarityisselectedbycontrolinputCPOL LS0,LS1 CMOSIN LinkSelect(DeterminesactiveSubLVDSDataLinksandPLLRange)SeeTable2 DisablestheCMOSDriversandTurnsOffthePLL,puttingdeviceinshutdownmode 1–Transmitterenabled 0–Transmitterdisabled (Shutdown) TXEN Note:TheTXENinputincorporatesglitch-suppressionlogictoavoiddevicemalfunction onshortinputspikes.ItisnecessarytopullTXENhighforlongerthan10μstoenable thetransmitter.ItisnecessarytopulltheTXENinputlowforlongerthan10μstodisable thetransmitter.Atpowerup,thetransmitterisenabledimmediatelyifTXEN=1and disabledifTXEN=0 InputClockPolaritySelection CPOL CMOSIn 0–risingedgeclocking 1–fallingedgeclocking BusSwapswapsthebuspinstoallowdeviceplacementontoporbottomofpcb.See pinoutdrawingforpinassignments. SWAP CMOSIn 0–datainputfromB0...R7 1–datainputfromR7...B0 V SupplyVoltage DD GND SupplyGround V SubLVDSI/OsupplyVoltage DDLVDS GND SubLVDSGround LVDS PowerSupply(1) V PLLanalogsupplyVoltage DDPLLA GND PLLanalogGND PLLA V PLLdigitalsupplyVoltage DDPLLD GND PLLdigitalGND PLLD (1) Foramultilayerpcb,itisrecommendedtokeeponecommonGNDlayerunderneaththedeviceandconnectallgroundterminals directlytothisplane. 6 SubmitDocumentationFeedback Copyright©2006–2012,TexasInstrumentsIncorporated ProductFolderLinks:SN65LVDS301

SN65LVDS301 www.ti.com SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 FUNCTIONAL DESCRIPTION Serialization Modes The SN65LVDS301 transmitter has three modes of operation controlled by link-select pins LS0 and LS1. Table 2 showstheserializermodesofoperation. Table2.LogicTable:LinkSelectOperatingModes LS1 LS0 ModeofOperation DataLinksStatus 0 0 1ChM 1-channelmode(30-bitserializationrate) D0active; D1,D2high-impedance 0 1 2ChM 2-channelmode(15-bitserializationrate) D0,D1active; D2high-impedance 1 0 3ChM 3-channelmode(10-bitserializationrate) D0,D1,D2active 1 1 Reserved Reserved 1-ChannelMode While LS0 and LS1 are held low, the SN65LVDS301 transmits payload data over a single SubLVDS data pair, D0. The PLL locks to PCLK and internally multiplies the clock by a factor of 30. The internal high-speed clock is used to serialize (shift out) the data payload on D0. Two reserved bits and the parity bit are added to the data frame.Figure3illustratesthetimingandthemappingofthedatapayloadintothe30-bitframe.Theinternalhigh- speed clock is divided by a factor of 30 to recreate the pixel clock, and presented on the SubLVDS CLK output. While in this mode, the PLL can lock to a clock that is in the range of 4 MHz through 15 MHz. This mode is intended for smaller video display formats (e.g. QVGA to HVGA) that do not require the full bandwidth capabilitiesoftheSN65LVDS301. CLK– CLK+ D0 +/–CHANNEL 0 0 CP R7 R6 R5 R4 R3 R2 R1R0 G7G6G5 G4 G3 G2 G1G0 B7 B6 B5 B4 B3 B2 B1 B0 VSHSDE 0 0 CP R7 R6 Figure3. DataandClockOutputin1-ChannelMode(LS0andLS1=low). 2-ChannelMode While LS0 is held high and LS1 is held low, the SN65LVDS301 transmits payload data over two SubLVDS data pairs, D0 and D1. The PLL locks to PCLK and internally multiplies it by a factor of 15. The internal high-speed clock is used to serialize the data payload on D0, and D1. Two reserved bits and the parity bit are added to the data frame. Figure 4 illustrates the timing and the mapping of the data payload into the 30-bit frame and how the frame becomes split into the two output channels. The internal high-speed clock is divided by 15 to recreate the pixel clock, and presented on SubLVDS CLK. The PLL can lock to a clock that is in the range of 8 MHz through 30MHzinthismode.Typicalapplicationsforusingthe2-channelmodeareHVGAandVGAdisplays. CLK– CLK + D0 +/–Channel CP R7 R6 R5 R4 R3 R2 R1 R0 G7 G6 G5 G4 VS 0 CP R7 R6 D1 +/–Channel 0 G3 G2 G1G0 B7 B6 B5 B4 B3 B2 B1 B0 HSDE 0 G3 G2 Figure4. DataandClockOutputin2-ChannelMode(LS0=high;LS1=low). Copyright©2006–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback 7 ProductFolderLinks:SN65LVDS301

SN65LVDS301 SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 www.ti.com 3-ChannelMode WhileLS0isheldlowandLS1isheldhigh,theSN65LVDS301transmitspayloaddataoverthreeSubLVDSdata pairs D0, D1, and D2. The PLL locks to PCLK, and internally multiplies it by 10. The internal high-speed clock is used to serialize the data payload on D0, D1, and D2. Two reserved bits and the parity bit are added to the data frame. Figure 5 illustrates the timing and the mapping of the data payload into the 30-bit frame and how the frame becomes split over the three output channels. The internal high speed clock is divided back down by a factor of 10 to recreate the pixel clock and presented on SubLVDS CLK output. While in this mode, the PLL can lock to a clock in the range of 20 MHz through 65 MHz. The 3-channel mode supports applications with very largedisplayresolutionssuchasVGAorXGA. CLK - CLK + D0 +/- CHANNEL CP R7 R6 R5 R4 R3 R2 R1 R0 VS CP R7 R6 D1 +/- CHANNEL 0 G7 G6 G5 G4 G3 G2 G1 G0 HS 0 G7 G6 D2 +/- CHANNEL 0 B7 B6 B5 B4 B3 B2 B1 B0 DE 0 B7 B6 Figure5. DataandClockOutputin3-ChannelMode(LS0=low;LS1=high). Powerdown Modes TheSN65LVDS301Transmitterhastwopowerdownmodestofacilitateefficientpowermanagement. Shutdown Mode The SN65LVDS301 enters Shutdown mode when the TXEN pin is asserted low. This turns off all transmitter circuitry, including the CMOS input, PLL, serializer, and SubLVDS transmitter output stage. All outputs are high- impedance.CurrentconsumptioninShutdownmodeisnearlyzero. Standby Mode The SN65LVDS301 enters the Standby mode if TXEN is high and the PCLK input signal frequency is less than 500kHz. All circuitry except the PCLK input monitor is shut down, and all outputs enter high-impedance mode. The current consumption in Standby mode is very low. When the PCLK input signal is completely stopped, the I currentconsumptionislessthan10μA.ThePCLKinputmustnotbeleftfloating. DD NOTE A floating (left open) CMOS input allows leakage currents to flow from V to GND. To DD prevent large leakage current, a CMOS gate must be kept at a valid logic level, either V IH or V . This can be achieved by applying an external voltage of V or V to all IL IH IL SN65LVDS301inputs. 8 SubmitDocumentationFeedback Copyright©2006–2012,TexasInstrumentsIncorporated ProductFolderLinks:SN65LVDS301

SN65LVDS301 www.ti.com SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 Active Modes When TXEN is high and the PCLK input clock signal is faster than 3 MHz, the SN65LVDS301 enters Active mode. Current consumption in Active mode depends on operating frequency and the number of data transitions inthedatapayload. Acquire Mode (PLL approaches lock) The PLL is enabled and attempts to lock to the input Clock. All outputs remain in high-impedance mode. When the PLL monitor detects stable PLL operation, the device switches from Acquire to Transmit mode. For proper device operation, the pixel clock frequency must fall within the valid f range specified under recommended PCLK operating conditions. If the pixel clock frequency is larger than 3 MHz but smaller than f (min), the PCLK SN65LVDS301 PLL is enabled. Under such conditions, it is possible for the PLL to lock temporarily to the pixel clock,causingthePLLmonitortoreleasethedeviceintotransmitmode.Ifthishappens,thePLLmayormaynot be properly locked to the pixel clock input, potentially causing data errors, frequency oscillation, and PLL deadlock(lossofVCOoscillation). Transmit Mode After the PLL achieves lock, the device enters the normal transmit mode. The CLK pin outputs a copy of PCLK. Based on the selected mode of operation, the D0, D1, and D2 outputs carry the serialized data. In 1-channel mode,outputsD1andD2remainhigh-impedance.Inthe2-channelmode,outputD2remainshigh-impedance. Parity Bit Generation The SN65LVDS301 transmitter calculates the parity of the transmit data word and sets the parity bit accordingly. The parity bit covers the 27 bit data payload consisting of 24 bits of pixel data plus VS, HS and DE. The two reserved bits are not included in the parity generation. ODD Parity bit signaling is used. The transmitter sets the Parity bit if the sum of the 27 data bits result in an even number of ones. The Parity bit is cleared otherwise. This allowsthereceivertoverifyParityanddetectsinglebiterrors. Status Detect and Operating Modes Flow diagram TheSN65LVDS301switchesbetweenthepowersavingandactivemodesinthefollowingway: Power Up Power Up TXEN = 0 TXEN Low TXEN = 1 > 10ms CLK Inactive Shutdown TXEN High > 10ms Standby Mode Mode PCLK Stops or Lost TXEN Low PCLK PCLK > 10ms Stops or Lost Active Power Up TXEN = 1 CLKActive TXEN Low > 10ms Transmit PLLAchieved Lock Acquire Mode Mode Figure6. StatusDetectandOperatingModesFlowDiagram Copyright©2006–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback 9 ProductFolderLinks:SN65LVDS301

SN65LVDS301 SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 www.ti.com Table3.StatusDetectandOperatingModesDescriptions Mode Characteristics Conditions ShutdownMode Leastamountofpowerconsumption(1)(mostcircuitryturned TXENislow(1) (2) off);Alloutputsarehigh-impedance StandbyMode Lowpowerconsumption(onlyclockactivitycircuitactive;PLL TXENishigh;PCLKinputsignalismissingor isdisabledtoconservepower);Alloutputsarehigh- inactive(2) impedance AcquireMode PLLtriestoachievelock;Alloutputsarehigh-impedance TXENishigh;PCLKinputmonitordetectedinput activity TransmitMode Datatransfer(normaloperation);Transmitterserializesdata TXENishighandPLLislockedtoincomingclock andtransmitsdataonserialoutput;unusedoutputsremain high-impedance (1) InShutdownMode,allSN65LVDS301internalswitchingcircuits(e.g.,PLL,serializer,etc.)areturnedofftominimizepower consumption.Theinputstageofanyinputpinremainsactive. (2) Leavinginputsunconnectedcancauserandomnoisetotoggletheinputstageandpotentiallyharmthedevice.Allinputsmustbetiedto avalidlogiclevelV orV duringShutdownorStandbyMode. IL IH Table4.OperatingModeTransitions MODETRANSITION USECASE TRANSITIONSPECIFICS Shutdown→Standby DriveTXENhightoenable 1. TXENhigh>10μs transmitter 2. Transmitterentersstandbymode a.Alloutputsarehigh-impedance b.Transmitterturnsonclockinputmonitor Standby→Acquire Transmitteractivitydetected 1. PCLKinputmonitordetectsclockinputactivity; 2. Outputsremainhigh-impedance; 3. PLLcircuitisenabled Acquire→Transmit Linkisreadytotransferdata 1. PLLisactiveandapproacheslock 2. PLLachievedlockwithin2ms 3. ParallelDatainputlatchesintoshiftregister 4. CLKoutputturnson 5. selectedDataoutputsturnonandsendoutfirstserialdatabit Transmit→Standby RequestTransmittertoenter 1. PCLKInputmonitordetectsmissingPCLK Standbymodebystopping 2. Transmitterindicatesstandby,puttingalloutputsintohigh-impedance; PCLK 3. PLLshutsdown; 4. PCLKactivityinputmonitorremainsactive Transmit/Standby→ TurnoffTransmitter 1. TXENpulledlowforlongerthan10us Shutdown 2. Transmitterindicatesstandby,puttingoutputCLK+andCLK–intohigh- impedancestate; 3. Transmitterputsallotheroutputsintohigh-impedancestate 4. MostICcircuitryisshutdownforleastpowerconsumption 10 SubmitDocumentationFeedback Copyright©2006–2012,TexasInstrumentsIncorporated ProductFolderLinks:SN65LVDS301

SN65LVDS301 www.ti.com SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 ORDERINGINFORMATION PARTNUMBER PACKAGE SHIPPINGMETHOD SN65LVDS301ZQE Tray ZQE SN65LVDS301ZQER Reel ABSOLUTE MAXIMUM RATINGS(1) overoperatingfree-airtemperaturerange(unlessotherwisenoted) VALUE UNIT Supplyvoltagerange,V (2),V ,V ,V -0.3to2.175 V DD DDPLLA DDPLLD DDLVDS Voltagerangeatanyinput WhenV >0V -0.5to2.175 V DDx oroutputterminal WhenV ≤0V -0.5toV +2.175 V DDx DD HumanBodyModel(3)(allPins) ±3 kV Electrostaticdischarge Charged-DeviceMode(4)l(allPins) ±500 V MachineModel(5)(allpins) ±200 Continuouspowerdissipation SeeDissipationRatingTable (1) Stressesbeyondthoselistedunderabsolutemaximumratingsmaycausepermanentdamagetothedevice.Thesearestressratings onlyandfunctionaloperationofthedeviceattheseoranyotherconditionsbeyondthoseindicatedunderrecommendedoperating conditionsisnotimplied.Exposuretoabsolutemaximum-ratedconditionsforextendedperiodsmayaffectdevicereliability. (2) AllvoltagevaluesarewithrespecttotheGNDterminals. (3) InaccordancewithJEDECStandard22,TestMethodA114-A. (4) InaccordancewithJEDECStandard22,TestMethodC101. (5) InaccordancewithJEDECStandard22,TestMethodA115-A DISSIPATION RATINGS CIRCUIT DERATINGFACTOR(1) T =85°C PACKAGE T <25°C A BOARDMODEL A ABOVET =25°C POWERRATING A ZQE Low-K(2) 592mW 7.407mW/°C 148mW (1) Thisistheinverseofthejunction-to-ambientthermalresistancewhenboard-mountedandwithnoairflow. (2) InaccordancewiththeLow-KthermalmetricdefinitionsofEIA/JESD51-2. THERMAL CHARACTERISTICS PARAMETER TESTCONDITIONS VALUE UNIT PCLKat4MHz 14.4 Typical V =1.8V,T =25°C mW DDx A PCLKat65MHz 44.5 P DevicePowerDissipation D PCLKat4MHz 22.3 Maximum V =1.95V,T =–40°C mW DDx A PCLK=65MHz 71.8 Copyright©2006–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback 11 ProductFolderLinks:SN65LVDS301

SN65LVDS301 SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 www.ti.com RECOMMENDED OPERATING CONDITIONS(1) MIN NOM MAX UNIT V Supplyvoltages 1.65 1.8 1.95 V DD V DDPLLA V DDPLLD V DDLVDS V Testset-upseeFigure12 DDn(PP) Supplyvoltagenoise f(PCLK)≤50MHz;f(noise)=1Hzto2GHz 100 mV magnitude(allsupplies) f(PCLK)>50MHz;f(noise)=1Hzto1MHz 100 f(PCLK)>50MHz;f(noise)>1MHz 40 1-Channeltransmitmode,seeFigure3 4 15 2-Channeltransmitmode,seeFigure4 8 30 fPCLK Pixelclockfrequency 3-Channeltransmitmode,seeFigure5 20 65 MHz FrequencythresholdStandbymodetoactive 0.5 3 mode(2),seeFigure16 t xf PCLKinputdutycycle 0.33 0.67 H PCLK T Operatingfree-air –40 85 °C A temperature t PCLKRMSperiodjitter(3) 5 ps-rms jit(per)PCLK t PCLKtotaljitter 0.05/f s jit(TJ)PCLK MeasuredonPCLKinput PCLK t PCLKpeak 0.02/f s jit(CC)PCLK PCLK cycle-to-cyclejitter(4) PCLK,R[0:7],G[0:7],B[0:7],VS,HS,DE,PCLK,LS[1:0],CPOL,TXEN,SWAP V High-levelinputvoltage 0.7×V V V IH DD DD V Low-levelinputvoltage 0.3×V V IL DD t Datasetuptimepriorto 2.0 ns DS PCLKtransition f(PCLK)=65MHz;seeFigure8 t DataholdtimeafterPCLK 2.0 ns DH transition (1) Unusedsingle-endedinputsmustbeheldhighorlowtopreventthemfromfloating. (2) PCLKinputfrequencieslowerthan500kHzforcetheSN65LVDS301intostandbymode.Inputfrequenciesbetween500kHzand3MHz mayormaynotactivatetheSN65LVDS301.Inputfrequenciesbeyond3MHzactivatetheSN65LVDS301. (3) Periodjitteristhedeviationincycletimeofasignalwithrespecttotheidealperiodoverarandomsampleof100,000cycles. (4) Cycle-to-cyclejitteristhevariationincycletimeofasignalbetweenadjacentcycles;overarandomsampleof1,000adjacentcycle pairs. 12 SubmitDocumentationFeedback Copyright©2006–2012,TexasInstrumentsIncorporated ProductFolderLinks:SN65LVDS301

SN65LVDS301 www.ti.com SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 DEVICE ELECTRICAL CHARACTERISTICS overrecommendedoperatingconditions(unlessotherwisenoted) PARAM TESTCONDITIONS MIN TYP(1) MAX UNIT ETER V =V =V =V , f =4MHz 9.0 11.4 DD DDPLLA DDPLLD DDLVDS PCLK R =R =100Ω,V =V ,V =0V,TXEN atL(VCLK), L(D0) IH DD IL fPCLK=6MHz 10.6 12.6 mA DD alternating1010serialbitpattern fPCLK=15MHz 16 18.8 1ChM V =V =V =V , f =4MHz 8.0 DD DDPLLA DDPLLD DDLVDS PCLK R =R =100Ω,V =V ,V =0V, TXL(EPCNLKa)tVL(D,0) IH DD IL fPCLK=6MHz 8.9 mA DD typicalpowertestpattern(seeTable6) fPCLK=15MHz 14.0 V =V =V =V , f =8MHz 13.7 15.9 DD DDPLLA DDPLLD DDLVDS PCLK R =R =100Ω,V =V ,V =0V,TXEN atL(VCLK), L(Dx) IH DD IL fPCLK=22MHz 18.4 22.0 mA DD alternating1010serialbitpattern; fPCLK=30MHz 21.4 25.8 2ChM V =V =V =V , f =8MHz 11.5 DD DDPLLA DDPLLD DDLVDS PCLK R =R =100Ω,V =V ,V =0V, TXL(EPCNLKa)tVL(D,0) IH DD IL fPCLK=22MHz 16.0 mA I DD DD typicalpowertestpattern(seeTable7) fPCLK=30MHz 19.1 V =V =V =V , f =20MHz 20.0 22.5 DD DDPLLA DDPLLD DDLVDS PCLK R =R =100Ω,V =V ,V =0V, TXL(EPCNLKa)tVDLD(D,0) IH DD IL fPCLK=65MHz 29.1 36.8 mA alternating1010serialbitpattern 3ChM V =V =V =V , f =20MHz 15.9 DD DDPLLA DDPLLD DDLVDS PCLK R =R =100Ω,V =V ,V =0V, TXL(EPCNLKa)tVDLD(D,0) IH DD IL fPCLK=65MHz 24.7 mA typicalpowertestpattern(seeTable8) StandbyMode V =V =V 0.61 10 μA DD DDPLLA DDPLLD =V , DDLVDS R =R =100Ω, L(PCLK) L(D0) ShutdownMode VIH=VDD,VIL=0V,all 0.55 10 μA inputsheldstatichighor staticlow (1) Alltypicalvaluesareat25°Candwith1.8Vsupplyunlessotherwisenoted. OUTPUT ELECTRICAL CHARACTERISTICS overoperatingfree-airtemperaturerange(unlessotherwisenoted) PARAMETER TESTCONDITIONS MIN TYP(1) MAX UNIT subLVDSoutput(D0+,D0–,D1+,D1–,D2+,D1–,CLK+,andCLK–) V Steady-statecommon-modeoutputvoltage OutputloadseeFigure10 0.8 0.9 1.0 V OCM(SS) V Changeinsteady-statecommon-modeoutputvoltage –10 10 mV OCM(SS) V Peak-to-peakcommonmodeoutputvoltage 75 mV OCM(PP) |V | Differentialoutputvoltagemagnitude 100 150 200 OD mV |V –V |,|V –V | Dx+ Dx– CLK+ CLK– Δ|V | Changeindifferentialoutputvoltagebetweenlogicstates –10 10 mV OD Z Differentialsmall-signaloutputimpedance TXENatV 210 Ω OD(CLK) DD I Differentialshort-circuitoutputcurrent V =0V,f =28MHz 10 OSD OD PCLK mA I Shortcircuitoutputcurrent(2) V =0VorV 5 OS O DD I High-impedancestateoutputcurrent V =0VorV (max), –3 3 OZ O DD μA TXENatGND (1) Alltypicalvaluesareat25°Candwith1.8Vsupplyunlessotherwisenoted. (2) AllSN65LVDS301outputstolerateshortstoGNDorV withoutpermanentdevicedamage. DD Copyright©2006–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback 13 ProductFolderLinks:SN65LVDS301

SN65LVDS301 SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 www.ti.com INPUT ELECTRICAL CHARACTERISTICS overoperatingfree-airtemperaturerange(unlessotherwisenoted) PARAMETER TESTCONDITIONS MIN TYP(1) MAX UNIT PCLK,R[0:7],G[0:7],B[0:7],VS,HS,DE,PCLK,LS[1:0],CPOL,TXEN,SWAP I High-levelinputcurrent V =0.7×V –200 200 IH IN DD nA I Low-levelinputcurrent V =0.3×V –200 200 IL IN DD C Inputcapacitance 1.5 pF IN (1) Alltypicalvaluesareat25°Candwith1.8Vsupplyunlessotherwisenoted. SWITCHING CHARACTERISTICS overrecommendedoperatingconditions(unlessotherwisenoted) PARAMETER TESTCONDITIONS MIN TYP(1) MAX UNIT tr 20%-to-80%differential SeeFigure9andFigure10 250 500 outputsignalrisetime ps tf 20%-to-80%differential SeeFigure9andFigure10 250 500 outputsignalfalltime PLLbandwidth(3dBcutoff TestedfromPCLKinputto fPCLK=22MHz 0.082×fPCLK fBW frequency) CLKoutput,SeeFigure7(2) fPCLK=65MHz 0.07×fPCLK MHz tpd(L) Propagationdelaytime, TXENatVDD,VIH=VDD, 1-channelmode 0.8/fPCLK 1/fPCLK 1.2/fPCLK ilnapteuntctyoFsiegruiarelo1u1tp)ut(data VIL=GND,RL=100Ω 2-channelmode 1.0/fPCLK 1.21/fPCLK 1.5/fPCLK s 3-channelmode 1.1/fPCLK 1.31/fPCLK 1.6/fPCLK tH×fCLK0 OutputCLKdutycycle 1-channeland3-channel 0.45 0.50 0.55 mode 2-channelmode 0.49 0.53 0.58 tGS TpuXlEseNwGidlittchh(3)suppression VseIHe=FViDgDu,reVI1L=4GaNndD,FTigXuEreN1t5ogglesbetweenVILandVIH, 3.8 10 μs tpwrup Enabletimefrompower TimefromTXENpulledhightoCLKandDxoutputs 0.24 2 ms down(↑TXEN) enabledandtransmitvaliddata;seeFigure15 tpwrdn Disabletimefromactive TXENispulledlowduringtransmitmode;time 0.5 11 mode(↓TXEN) measurementuntiloutputisdisabledandPLLisShutdown; μs seeFigure15 twakup EnabletimefromStandby TXENatVDD;deviceinstandby;timemeasurementfrom 0.23 2 (↕PCLK) PCLKstartsswitchingtoCLKandDxoutputsenabledand ms transmitvaliddata;seeFigure15 tsleep DisabletimefromActive TXENatVDD;deviceistransmitting;timemeasurement 0.4 100 mode(PCLKstopping) fromPCLKinputsignalstopsuntilCLK+Dxoutputsare μs disabledandPLLisdisabled;seeFigure15 (1) Alltypicalvaluesareat25°Candwith1.8Vsupplyunlessotherwisenoted. (2) TheMaximumLimitisbasedonstatisticalanalysisofthedeviceperformanceoverprocess,voltage,andtempranges.Thisparameter isfunctionalitytestedonlyonAutomaticTestEquipment(ATE). (3) TheTXENinputincorporatesglitch-suppressioncircuitrytodisregardshortinputpulses.t isthedurationofeitherahigh-to-loworlow- GS to-hightransitionthatissuppressed. 14 SubmitDocumentationFeedback Copyright©2006–2012,TexasInstrumentsIncorporated ProductFolderLinks:SN65LVDS301

SN65LVDS301 www.ti.com SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 12.0% 9.0 4 MHz: 8 MHz: 11.0% 8.5% 8.5% 20 MHz: 8.5 8.3% ncy]10.0% RX PLLBW e PCLK Frequ 89..00%% 8.59%% WIDTH - % 78..50 Sp1eCch LM1im5 itMHz: 2SLCipmheMict 30 MHz: Spec Limit 3ChM of 7.5% D 7.6% 7.6% W [% 7.0% 7% BAN 7.0 B LL 65 MHz: PLL 6.0% TX PLLBW P 7.0% 6.5 5.0% 4.0% 6.0 0 100 200 300 400 500 600 700 0 10 20 30 40 50 60 70 PLL frequency−MHz PCLK FREQUENCY- MHz Figure7. LVDS301PLLBandwidth(alsoshowingtheLVDS302PLLbandwidth) TIMING CHARACTERISTICS PARAMETER TESTCONDITIONS MIN TYP MAX UNIT 1ChM:x=0..29,fPCLK=15MHz;TXENat x -330ps x +330ps VDD,VIH=VDD,VIL=GND,RL=100Ω,test 30×f 30×f patternasinTable11(3) PCLK PCLK 1ChM:x=0..29, x–0.1845 x+0.1845 fPCLK=4MHzto15MHz(4) 30×fPCLK 30×fPCLK 2ChM:x=0..14,fPCLK=30MHz x -330ps x +330ps TXENatVDD,VIH=VDD,VIL=GND, 15×f 15×f OutputPulsePosition, RL=100Ω,testpatternasinTable12(3) PCLK PCLK tPPOSX ⇅(1s)e(2r)iaanlddaFtaigutore↑C13LK;see 2ChM:x=0..14, x–0.1845 x + 0.1845 ps fPCLK=8MHzto30MHz(4) 15×f 15×f PCLK PCLK 3ChM:x=0..9,fPCLK=65MHz, x -210ps x +210ps TXENatVDD,VIH=VDD,VIL=GND, 10×f 10×f RL=100Ω,testpatternasinTable13(3) PCLK PCLK 3ChM:x=0..9, x-0.153 x+0.153 fPCLK=20MHzto65MHz(4) 10×fPCLK 10×fPCLK (1) Thisnumberalsoincludesthehigh-frequencyrandomanddeterministicPLLclockjitterthatisnottraceablebytheSN65LVDS302 receiverPLL;tPPosxrepresentsthetotaltiminguncertaintyofthetransmitternecessarytocalculatethejitterbudgetwhencombined withtheSN65LVDS302receiver; (2) Thepulsepositionmin/maxvariationisgivenwithabiterrorratetargetof10–12;Themeasurementestimatestherandomjitter contributiontothetotaljittercontributionbymultiplyingtherandomRMSjitterbythefactor14;Measurementsofthetotaljitteraretaken overasampleamountof>10–12samples. (3) TheMinimumandMaximumLimitsarebasedonstatisticalanalysisofthedeviceperformanceoverprocess,voltage,andtempranges. ThisparameterisfunctionalitytestedonlyonAutomaticTestEquipment(ATE). (4) TheseMinimumandMaximumLimitsaresimulatedonly. Copyright©2006–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback 15 ProductFolderLinks:SN65LVDS301

SN65LVDS301 SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 www.ti.com PARAMETER MEASUREMENT INFORMATION t DS V R[7:0], G[7:0], B[7:0]; IH VS, HS, DE, LS0, LS1, TXEN, SWAP, CPOL V IL t DH V IH PCLK (CPOL=low) V IL t R Figure8. Setup/HoldTime VOD tf tr 150mV (nom) 80% 0 V 20% −150mV (nom) Figure9. RiseandFallTimeDefinitions VDx+or VCLK+ 975mV (nom) R1 = 49.9 VDx−or VCLK− 825mV (nom) CLK+, Dx+ VOD CLK−, Dx− R2 = 49.9 VOCM VOCM SN65LVDS301 C1 = 1 pF C2 = 1 pF VOCM(pp) VOCM(ss) NOTES: A. 20 MHz output test pattern on all differental outputs (CLK, D0, D1, and D2): this is achieved by: 1. Device is set to 3-channel-mode; 2. fPCLK= 20 MHz 3. Inputs R[7:3] = B[7:3] connected to V , all other data inputs set to GND. DD B. C1, C2 and C3 includes instrumentation and fixture capacitance; tolerance±20%; C, R1 and R2 tolerance±1%. C.The measurement of VOCM(pp) and VOC(ss) are taken with test equipment bandwidth >1 GHz. Figure10. DriverOutputVoltageTestCircuitandDefinitions 16 SubmitDocumentationFeedback Copyright©2006–2012,TexasInstrumentsIncorporated ProductFolderLinks:SN65LVDS301

SN65LVDS301 www.ti.com SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 DCaMtaO ISn pixel(n) pixel(n+1) R7(n−1) R7(n) R7(n+1) R6(n−1) R6(n) R6(n+1) PCLK VDD/2 tPROP CLK− CLK+ D0+ CPR7R6 CPR7R6 pixel(n−2) pixel(n−1) R7(n−1) R6(n−1) R7(n) R6(n) Figure11. t PropagationDelayInputtoOutput(LS0=LS1=0;CPOL=0) pd(L) SN65LVDS301 1 2 VDDPLLA VDDPLLD Noise 1 10mF VDD Generator 100 mV VDDLVDS GND Note:The generator regulates the 1.8 V noise amplitude at point 1 to the 1.6 H supply target amplitude given under the table Recommended Operating Conditions Figure12. PowerSupplyNoiseTestSet-Up tCLK+ CLK− CLK+ Current Cycle Next Cycle D[0:m](cid:1) Bit 0 Bit1 Bit2 Bitx Bit0 Bit1 tPPOS0 Note: tPPOS1 1−channel mode: x=0..29; m=0 2−channel mode: x=0..14; m=1 tPPOS2 3−channel mode: x=0....9; m=2 tPPOSx Figure13. t SubLVDSOutputPulsePositionMeasurement SK(0) Copyright©2006–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback 17 ProductFolderLinks:SN65LVDS301

SN65LVDS301 SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 www.ti.com VDD/2 TXEN tGS PCLK VCO Internal Signal PLLApproaches Lock tpwrup CLK D0, D1, D2 Figure14. TransmitterBehaviorWhileApproachingSync 3 s <20 ns 2 s Glitch Shorter LessThan 20 ns Than tGSWill Be Spike Will be Glitch Shorter Ignored Rejected Than tGSWill Be Ignored TXEN tpwrup tpwrdn CLK+ tGS ICC tGS PCLK Transmitter Disabled TransmitterAquires Lock Transmitter Enabled Transmitter (OFF) (ON) Transmitter Disabled Turns OFF (OFF) Figure15. TransmitterEnableGlitchSuppressionTime PCLK t t wakeup sleep CLK+ Transmitter Disabled TransmitterAquires Lock, Transmitter Enabled, Transmitter Transmitter (OFF) Outputs Still Disabled Output Data Valid Enabled, Disabled Output Data (OFF) Valid Figure16. StandbyDetection PowerConsumptionTests Table5showsanexampletestpatternword. 18 SubmitDocumentationFeedback Copyright©2006–2012,TexasInstrumentsIncorporated ProductFolderLinks:SN65LVDS301

SN65LVDS301 www.ti.com SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 Table5.ExampleTestPatternWord Word R[7:4],R[3:0],G[7:4],G[3:0],B[7-4],B[3-0],0,VS,HS,DE 1 0x7C3E1E7 7 C 3 E 1 E 7 R7 R6 R5 R4 R3 R2 R1 R0 G7 G6 G5 G4 G3 G2 G1 G0 B7 B6 B5 B4 B3 B2 B1 B0 0 VS HS DE 0 1 1 1 1 1 0 0 0 0 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 1 TypicalICPowerConsumptionTestPattern The typical power consumption test patterns consists of sixteen 30-bit transmit words in 1-channel mode, eight 30-bit transmit words in 2-channel mode and five 30-bit transmit words in 3-channel mode. The pattern repeats itself throughout the entire measurement. It is assumed that every possible transmit code on RGB inputs has the sameprobabilitytooccurduringtypicaldeviceoperation. Table6. TypicalICPowerConsumptionTestPattern, 1-ChannelMode Word TestPattern: R[7:4],R[3:0],G[7:4],G[3:0],B[7-4],B[3-0],0,VS,HS,DE 1 0x0000007 2 0xFFF0007 3 0x01FFF47 4 0xF0E07F7 5 0x7C3E1E7 6 0xE707C37 7 0xE1CE6C7 8 0xF1B9237 9 0x91BB347 10 0xD4CCC67 11 0xAD53377 12 0xACB2207 13 0xAAB2697 14 0x5556957 15 0xAAAAAB3 16 0xAAAAAA5 Copyright©2006–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback 19 ProductFolderLinks:SN65LVDS301

SN65LVDS301 SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 www.ti.com Table7.TypicalICPowerConsumptionTestPattern, 2-ChannelMode Word TestPattern: R[7:4],R[3:0],G[7:4],G[3:0],B[7-4],B[3-0],0,VS,HS,DE 1 0x0000001 2 0x03F03F1 3 0xBFFBFF1 4 0x1D71D71 5 0x4C74C71 6 0xC45C451 7 0xA3aA3A5 8 0x5555553 Table8.TypicalICPowerConsumptionTestPattern, 3-ChannelMode Word TestPattern: R[7:4],R[3:0],G[7:4],G[3:0],B[7-4],B[3-0],0,VS,HS,DE 1 0xFFFFFF1 2 0x0000001 3 0xF0F0F01 4 0xCCCCCC1 5 0xAAAAAA7 MaximumPowerConsumptionTestPattern The maximum (or worst-case) power consumption of the SN65LVDS301 is tested using the two different test patterns shown in Table 9 and Table 10. The test patterns consist of sixteen 30-bit transmit words in 1-channel mode, eight 30-bit transmit words in 2-channel mode and five 30-bit transmit words in 3-channel mode. The pattern repeats itself throughout the entire measurement. It is assumed that every possible transmit code on RGBinputshasthesameprobabilitytooccurduringtypicaldeviceoperation. Table9.Worst-CasePowerConsumptionTestPattern Word TestPattern: R[7:4],R[3:0],G[7:4],G[3:0],B[7-4],B[3-0],0,VS,HS,DE 1 0xAAAAAA5 2 0x5555555 Table10.Worst-CasePowerConsumptionTestPattern Word TestPattern: R[7:4],R[3:0],G[7:4],G[3:0],B[7-4],B[3-0],0,VS,HS,DE 1 0x0000000 2 0xFFFFFF7 20 SubmitDocumentationFeedback Copyright©2006–2012,TexasInstrumentsIncorporated ProductFolderLinks:SN65LVDS301

SN65LVDS301 www.ti.com SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 OutputSkewPulsePosition&JitterPerformance The following test patterns are used to measure the output-skew pulse position and the jitter performance of the SN65LVDS301. The jitter test pattern stresses the interconnect, particularly to test for ISI. Very long run-lengths of consecutive bits incorporate very high and low data rates, maximinges switching noise. Each pattern is self- repeatingforthedurationofthetest. Table11.TransmitJitterTestPattern,1-ChannelMode Word TestPattern: R[7:4],R[3:0],G[7:4],G[3:0],B[7-4],B[3-0],0,VS,HS,DE 1 0x0000001 2 0x0000031 3 0x00000F1 4 0x00003F1 5 0x0000FF1 6 0x0003FF1 7 0x000FFF1 8 0x0F0F0F1 9 0x0C30C31 10 0x0842111 11 0x1C71C71 12 0x18C6311 13 0x1111111 14 0x3333331 15 0x2452413 16 0x22A2A25 17 0x5555553 18 0xDB6DB65 19 0xCCCCCC1 20 0xEEEEEE1 21 0xE739CE1 22 0xE38E381 23 0xF7BDEE1 24 0xF3CF3C1 25 0xF0F0F01 26 0xFFF0001 27 0xFFFC001 28 0xFFFF001 29 0xFFFFC01 30 0xFFFFF01 31 0xFFFFFC1 32 0xFFFFFF1 Copyright©2006–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback 21 ProductFolderLinks:SN65LVDS301

SN65LVDS301 SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 www.ti.com Table12.TransmitJitterTestPattern,2-ChannelMode Word TestPattern: R[7:4],R[3:0],G[7:4],G[3:0],B[7-4],B[3-0],0,VS,HS,DE 1 0x0000001 2 0x000FFF3 3 0x8008001 4 0x0030037 5 0xE00E001 6 0x00FF001 7 0x007E001 8 0x003C001 9 0x0018001 10 0x1C7E381 11 0x3333331 12 0x555AAA5 13 0x6DBDB61 14 0x7777771 15 0x555AAA3 16 0xAAAAAA5 17 0x5555553 18 0xAAA5555 19 0x8888881 20 0x9242491 21 0xAAA5571 22 0xCCCCCC1 23 0xE3E1C71 24 0xFFE7FF1 25 0xFFC3FF1 26 0xFF81FF1 27 0xFE00FF1 28 0x1FF1FF1 29 0xFFCFFC3 30 0x7FF7FF1 31 0xFFF0007 32 0xFFFFFF1 22 SubmitDocumentationFeedback Copyright©2006–2012,TexasInstrumentsIncorporated ProductFolderLinks:SN65LVDS301

SN65LVDS301 www.ti.com SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 Table13.TransmitJitterTestPattern,3-ChannelMode Word TestPattern: R[7:4],R[3:0],G[7:4],G[3:0],B[7-4],B[3-0],0,VS,HS,DE 1 0x0000001 2 0x0000001 3 0x0000003 4 0x0101013 5 0x0303033 6 0x0707073 7 0x1818183 8 0xE7E7E71 9 0x3535351 10 0x0202021 11 0x5454543 12 0xA5A5A51 13 0xADADAD1 14 0x5555551 15 0xA6A2AA3 16 0xA6A2AA5 17 0x5555553 18 0x5555555 19 0xAAAAAA1 20 0x5252521 21 0x5A5A5A1 22 0xABABAB1 23 0xFDFCFD1 24 0xCAAACA1 25 0x1818181 26 0xE7E7E71 27 0xF8F8F81 28 0xFCFCFC1 29 0xFEFEFE1 30 0xFFFFFF1 31 0xFFFFFF5 32 0xFFFFFF5 Copyright©2006–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback 23 ProductFolderLinks:SN65LVDS301

SN65LVDS301 SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 www.ti.com TYPICAL CHARACTERISTICS POWERDOWN,STANDBYSUPPLYCURRENT SUPPLYCURRENTI DD vs vs TEMPERATURE TEMPERATURE 1.0 20 2-Channel Mode, 22 MHz (VGA) 15 2-Channel Mode, 11 MHz (HVGA) A m A DQ - StandbyCurrent D - m10 D D I I Power-Down Current 5 0.1 0 -50 -30 -10 10 30 50 70 90 -50 -30 -10 10 30 50 70 90 Temperature - °C Temperature - °C Figure17. Figure18. SUPPLYCURRENT DIFFERENTIALOUTPUTSWING vs vs PCLKFREQUENCY PCLKFREQUENCY 30 200 85°C 190 V m 25°C 25 3-Channel Mode D - 180 O 170 V –40°C 2-Channel Mode g 20 n 160 DD - mA 15 utput Swi 114500 I O al 130 10 enti 120 1-Channel Mode er Diff 110 5 100 0 10 20 30 40 50 60 70 0 10 20 30 40 50 60 70 FREQUENCY- MHz FREQUENCY- MHz Figure19. Figure20. 24 SubmitDocumentationFeedback Copyright©2006–2012,TexasInstrumentsIncorporated ProductFolderLinks:SN65LVDS301

SN65LVDS301 www.ti.com SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 TYPICAL CHARACTERISTICS (continued) CYCLE-TO-CYCLEOUTPUTJITTER vs PLLBANDWIDTH PCLKFREQUENCY 9.0 500 SpecLimit 1ChM,4 MHz:8.5% SpecLimit 2ChM8 MHz:8.5% 8.5 SpecLimit 3ChM 20 MHz:8.3% 8.0 400 % 7.5 SpecLimit 1ChM, SpecLimit 2ChM H - 7.0 15 MHz:7.6% 30 MHz:7.6% ps 300 WIDT 6.5 Spec65L iMmHit z3:C7h.0M% ER - BAND 6.0 2-ChM 3-ChM C JITT 200 L 5.5 C L P 5.0 100 3-Channel Mode 4.5 1-Channel Mode 2-Channel Mode 4.0 0 0 10 20 30 40 50 60 70 0 10 20 30 40 50 60 70 FREQUENCY- MHz FREQUENCY- MHz Figure21. Figure22. CYCLE-TO-CYCLEOUTPUTJITTER OUTPUTPULSEPOSITION vs vs TEMPERATURE TEMPERATURE 200 120 2-Channel Mode, S 11 MHz (VGA) P 150 2f(-PCChLaKn)n =el 1M1o MdeH,z ) - OS100 P P N (t 80 ps O R - 100 SITI 60 2-Channel Mode, C JITTE LSE PO 40 22 MHz (HVGA) C 50 2f(-PCChLaKn)n =el 2M2o MdeH,z T PU U 20 P T U O 0 0 -50 -25 0 25 50 75 100 -50 -25 0 25 50 75 100 Temperature - °C TEMPERATURE - °C Figure23. Figure24. DATAEYEPATTERN,2-CHANNELMODE DATAEYEPATTERN,3-CHANNELMODE 250 250 – – 1 1 D D 1+, 175 1+, 190 D D N N N N O 2-Channel Mode, O 3-Channel Mode, E f(PCLK) = 22 MHz E f(PCLK) = 65 MHz D D U U T T LI LI MP 0 MP 0 A A E E G G A A T T L L O O V V T T U U P–175 P–190 P P T T U U O O –250 –250 500 ps/div 200 ps/div Figure25. Figure26. Copyright©2006–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback 25 ProductFolderLinks:SN65LVDS301

SN65LVDS301 SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 www.ti.com TYPICAL CHARACTERISTICS (continued) QVGAOUTPUTWAVEFORM VGA2-CHANNELOUTPUTWAVEFORM 249 250 190 190 V V m m e - e - d d u u plit plit m 1-Channel Mode, m 2-Channel Mode, eA 0 f(PCLK) = 5.5 MHz eA 0 f(PCLK) = 22 MHz g g a a Volt Volt ut ut p p ut ut O O –190 –190 –251 –250 1 ns/div 500 ps/div Response Over 80-inch of FR-4 + 1m Coax Cable Response Over 8-inch FR-4 + 1m Coax Cable Figure27. Figure28. VGA2-CHANNELOUTPUTWAVEFORM VGA3-CHANNELOUTPUTWAVEFORM 249 249 190 190 V V m m e - e - d d u u plit plit m 2-Channel Mode, m 3-Channel Mode, eA 0 f(PCLK) = 22 MHz eA 0 f(PCLK) = 22 MHz g g a a Volt Volt ut ut p p ut ut O O –190 –190 –251 –251 500 ps/div 1 ns/div Response Over 80-inch FR-4 + 1m Coax Cable Response Over 80-inch FR-4 + 1m Coax Cable Figure29. Figure30. XGA3-CHANNELOUTPUTWAVEFORMONTHE XGA3-CHANNELOUTPUTWAVEFORM SN65LVDS302WHENDRIVENBYTHESN65LVDS301 249 190 V V m m Output VoltageAmplitude - 0 Output VoltageAmplitude - 400 mV/div f3(P-CChLaKn)n =e l5 M6 oMdHe,z –190 3-Channel Mode, f(PCLK) = 56 MHz –251 300 ps/div 3.5 ns/div Response Over 80-inch FR-4 + 1m Coax Cable Response With 10-pF Load Figure31. Figure32. 26 SubmitDocumentationFeedback Copyright©2006–2012,TexasInstrumentsIncorporated ProductFolderLinks:SN65LVDS301

SN65LVDS301 www.ti.com SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 TYPICAL CHARACTERISTICS (continued) PLLPHASENOISE OUTPUTRETURNLOSS -50 0 -60 -70 -80 B -1-9000 f(PCLK) = 65 MHz SS - d –5 O Bc/Hz --111200 RN L d U --113400 RET –10 CLK D0 T -150 U P D2 -160 UT D1 O -170 -180 –15 1 10 100 1k 10k 100k 1M 10M 0 500 1000 1500 2000 FREQUENCY- Hz FREQUENCY- Hz Figure33. Figure34. OUTPUTCOMMONMODENOISEREJECTION CROSSTALK 0 0 B d N - -20 O –5 TI C E D0 J CLK E -40 R B NOISE –10 D1 D2 ON - d -60 D0 to D1 MODE –15 SOLATI D0 to D2 N I -80 O M M CO –20 -100 0 500 1000 1500 2000 0 500 1000 1500 2000 FREQUENCY- MHz FREQUENCY- MHz Figure35. Figure36. GTEMSAEJ1752/3EMITEST 20 f(PCLK)=65MHz 2-ChM, f(PCLK)=22MHz 320MHz; 16dBuV 3-ChM, f(PCLK)=65MHz, Vm 15 988MHz, 12dBuV dB 2-ChM, f(PCLK)=22MHz N - 3-ChM, f(PCLK)=65MHz, 683MHz; 12dBuV 3-ChM, f(PCLK)=65MHz SIO 282MHz 777MHz; 11dBuV S MI 10 ED E 3-ChM, f(PCLK)=65MHz 1-C9h6M0M f(HPzC; L8Kd)B=u5VMHz, AT 113MHz; 6dBuV DI RA 5 0 0 200 400 600 800 1000 FREQUENCY- MHz Figure37. A. Figure37showsasuperimposedimageofthreeEMImeasurementswiththedeviceoperatingatf(PCLK)=5MHz, f(PCLK)=22MHz,andf(PCLK)=65MHz.ThisexcellentEMIperformancemeetsthesystemrequirementsofdense, mobiledesignswithanoisefloorof~2dBµV(-105dBm)andallspursbeingsmallerthan16dBµV(-101dBm).The testwasperformedincompliancewiththeSAEJ1752/3EMItestguidelines. Copyright©2006–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback 27 ProductFolderLinks:SN65LVDS301

SN65LVDS301 SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 www.ti.com APPLICATION INFORMATION Preventing Increased Leakage Currents in Control Inputs A floating (left open) CMOS input allows leakage currents to flow from V to GND. Do not leave any CMOS DD Input unconnected or floating. Every input must be connected to a valid logic level V or V while power is IH OL suppliedtoV .Thisalsominimizesthepowerconsumptionofstandbyandpowerdownmode. DD Power Supply Design Recommendation For a multilayer pcb, it is recommended to keep one common GND layer underneath the device and connect all groundterminalsdirectlytothisplane. Decoupling Recommendation The SN65LVDS301 was designed to operate reliably in a constricted environment with other digital switching ICs. In many designs, the SN65LVDS301 often shares a power supply with the application processor. The SN65LVDS301 can operate with power supply noise as specified in Recommend Device Operating Conditions. To minimize the power supply noise floor, provide good decoupling near the SN65LVDS301 power pins. The use of four ceramic capacitors (2×0.01 μF and 2×0.1 μF) provides good performance. At the very least, it is recommended to install one 0.1 μF and one 0.01 μF capacitor near the SN65LVDS301. To avoid large current loops and trace inductance, the trace length between decoupling capacitor and IC power inputs pins must be minimized.PlacingthecapacitorunderneaththeSN65LVDS301onthebottomofthepcbisoftenagoodchoice. VGA Application Figure 38 shows a possible implementation of a VGA display. The LVDS301 interfaces to the SN65LVDS302, which is the corresponding receiver device to deserialize the data and drive the display driver. The pixel clock rate of 22 MHz assumes ~10% blanking overhead and 60 Hz display refresh rate. The application assumes 24- bit color resolution. It is also shown, how the application processor provides a powerdown (reset) signal for both serializer and the display driver. The signal count over the FPC could be further decreased by using the standby optionontheSN65LVDS302andpullingRXENhighwitha30kΩ resistortoV . DD 2x0.1uF GND FPC GND 2x0.1uF 2.7V 2.7V 2x0.01uF 2x0.01uF 1.8V 1.8V x D x D Application DD GN GND GND DD GN Video Mode Display Processor V V Driver (e.g.OMAP) CLK+ CLK+ CLK- 22MHz CLK- D0+ D0+ Pixel CLK 22MHz PCLK D0- 330Mbps D0- PCLK 22MHz DD[[175::08]] RG[[77::00]] DD11+- 330Mbps DD11+- RG[[77::00]] D[23:16] B[7:0] B[7:0] A HS,VS,DE 27 HS,VS,DE HS,VS,DE 27 Gn Vo SPI RESET SLS0N65LS1LVDTXENS301 SLS0N65LS1LVDRXENS302 ENABLE SPI LCDwithresoluti 1.8V 1.8V If FPC wire count is critical,replace this Serial port interface connection with a pull-up resistor at RXEN (3-wire IF) 3 Figure38. TypicalVGADisplayApplication 28 SubmitDocumentationFeedback Copyright©2006–2012,TexasInstrumentsIncorporated ProductFolderLinks:SN65LVDS301

SN65LVDS301 www.ti.com SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 Dual LCD-Display Application The example in Figure 39 shows a possible application setup driving two video mode displays from one application processor. The data rate of 330 Mbps at a pixel clock rate of 5.5 MHz corresponds to QVGA resolutionat60Hzrefreshrateand10%blankingoverhead. 2x0.1uF GND FPC GND 2x0.1uF 2.7V 2.7V 2x0.01uF 2x0.01uF Display Driver1 1.8V 1.8V APprpolciceastsioorn VDDx GND GND GND VDDx GND 21 (e.PgDi.D[xOD[1eM[17l1A5: ::1CP062)L]]]K 5.5MHz PRGB[[[C555L:::K000]]] CCLLDD00KK+-+- 53.530MMHbzps DDCC00LL+-KK+- HSRGB,[[[V555PS:::,C000DL]]]EK SSESPCONICLUNLKTK LCDwithQVGAresolution HS,VS,DE HS,VS,DE 18+3 SN65LVDS301 SN65LVDS302 Display Driver2 K T21 N N LNULL 0 1 E 0 1 E CIOEE S S X S S X SSSSS L L T L L R PCLK GA 1.8V 1.8V SSEIONNUT withQVsolution SCLK CDre L Figure39. ExampleDual-QVGADisplayApplication Typical Application Frequencies The SN65LVDS301 supports pixel clock frequencies from 4 MHz to 65 MHz over 1, 2, or 3 data lanes. Table 14 providesafewtypicaldisplayresolutionexamplesandshowsthenumberofdatalanesnecessarytoconnectthe LVDS301 with the display. The blanking overhead is assumed to be 20%. Often, blanking overhead is smaller, resulting in a lower data rate. Furthermore, the examples in the table assumes a display frame refresh rate of 60 Hzor90Hz.Theactualrefreshratemaydifferdependingontheapplication-processorclockimplementation. Table14.TypicalApplicationDataRates&SerialLaneUsage DisplayScreen Visible Blanking Display PixelClockFrequency SerialDataRatePerLane Resolution PixelCount Overhead Refresh [MHz] 1-ChM 2-ChM 3-ChM Rate 176x220(QCIF+) 38,720 20% 90Hz 4.2MHz 125Mbps 240x320(QVGA) 76,800 60Hz 5.5MHz 166Mbps 640x200 128,000 9.2MHz 276Mbps 138Mbps 352x416(CIF+) 146,432 10.5MHz 316Mbps 158Mbps 352x440 154,880 11.2MHz 335Mbps 167Mbps 320x480(HVGA) 153,600 11.1MHz 332Mbps 166Mbps 800x250 200,000 14.4MHz 432Mbps 216Mbps 640x320 204,800 14.7MHz 442Mbps 221Mbps 640x480(VGA) 307,200 22.1MHz 332Mbps 221Mbps 1024x320 327,680 23.6MHz 354Mbps 236Mbps 854x480(WVGA) 409,920 29.5MHz 443Mbps 295Mbps 800x600(SVGA) 480,000 34.6MHz 346Mbps 1024x768(XGA) 786,432 56.6MHz 566Mbps Copyright©2006–2012,TexasInstrumentsIncorporated SubmitDocumentationFeedback 29 ProductFolderLinks:SN65LVDS301

SN65LVDS301 SLLS681D–FEBRUARY2006–REVISEDAUGUST2012 www.ti.com CalculationExample:HVGADisplay ThisexamplecalculationshowsatypicalHalf-VGAdisplaywiththeseparameters: DisplayResolution: 480x320 P FrameRefreshRate: 58.4Hz Hsync = 5 B Visible area = 480 column HFP= 20 H HorizontalVisiblePixel: 480columns HorizontalFrontPorch: 20columns Vsync = 5 VBP= 3 HorizontalSync: 5columns HorizontalBackPorch: 3columns Visible area VerticalVisiblePixel: 320lines = 320 lines Visible area VerticalFrontPorch: 10lines VerticalSync: 5lines VerticalBackPorch: 3lines VFP= 10 Entire display Figure40. HVGADisplayParameters CalculationofthetotalnumberofpixelandBlankingoverhead: VisibleAreaPixelCount: 480× 320=153600pixel TotalFramePixelCount: (480+20+5+3)×(320+10+5+3)=171704pixel BlankingOverhead: (171704-153600)÷153600=11.8% Theapplicationrequiresfollowingserial-linkparameters: PixelClkFrequency: 171704× 58.4Hz=10.0MHz SerialDataRate: 1-channelmode:10.0MHz×30bit/channel=300Mbps 2-channelmode:10.0MHz×15bit/channel=150Mbps 30 SubmitDocumentationFeedback Copyright©2006–2012,TexasInstrumentsIncorporated ProductFolderLinks:SN65LVDS301

PACKAGE OPTION ADDENDUM www.ti.com 21-Aug-2012 PACKAGING INFORMATION Orderable Device Status (1) Package Type Package Pins Package Qty Eco Plan (2) Lead/ MSL Peak Temp (3) Samples Drawing Ball Finish (Requires Login) SN65LVDS301ZQE ACTIVE BGA ZQE 80 360 Green (RoHS SNAGCU Level-3-260C-168 HR MICROSTAR & no Sb/Br) JUNIOR SN65LVDS301ZQER ACTIVE BGA ZQE 80 2500 Green (RoHS SNAGCU Level-3-260C-168 HR MICROSTAR & no Sb/Br) JUNIOR (1) The marketing status values are defined as follows: ACTIVE: Product device recommended for new designs. LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect. NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design. PREVIEW: Device has been announced but is not in production. Samples may or may not be available. OBSOLETE: TI has discontinued the production of the device. (2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details. TBD: The Pb-Free/Green conversion plan has not been defined. Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above. Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material) (3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature. Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release. In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis. Addendum-Page 1

None

IMPORTANTNOTICE TexasInstrumentsIncorporatedanditssubsidiaries(TI)reservetherighttomakecorrections,enhancements,improvementsandother changestoitssemiconductorproductsandservicesperJESD46,latestissue,andtodiscontinueanyproductorserviceperJESD48,latest issue.Buyersshouldobtainthelatestrelevantinformationbeforeplacingordersandshouldverifythatsuchinformationiscurrentand complete.Allsemiconductorproducts(alsoreferredtohereinas“components”)aresoldsubjecttoTI’stermsandconditionsofsale suppliedatthetimeoforderacknowledgment. TIwarrantsperformanceofitscomponentstothespecificationsapplicableatthetimeofsale,inaccordancewiththewarrantyinTI’sterms andconditionsofsaleofsemiconductorproducts.TestingandotherqualitycontroltechniquesareusedtotheextentTIdeemsnecessary tosupportthiswarranty.Exceptwheremandatedbyapplicablelaw,testingofallparametersofeachcomponentisnotnecessarily performed. TIassumesnoliabilityforapplicationsassistanceorthedesignofBuyers’products.Buyersareresponsiblefortheirproductsand applicationsusingTIcomponents.TominimizetherisksassociatedwithBuyers’productsandapplications,Buyersshouldprovide adequatedesignandoperatingsafeguards. TIdoesnotwarrantorrepresentthatanylicense,eitherexpressorimplied,isgrantedunderanypatentright,copyright,maskworkright,or otherintellectualpropertyrightrelatingtoanycombination,machine,orprocessinwhichTIcomponentsorservicesareused.Information publishedbyTIregardingthird-partyproductsorservicesdoesnotconstitutealicensetousesuchproductsorservicesorawarrantyor endorsementthereof.Useofsuchinformationmayrequirealicensefromathirdpartyunderthepatentsorotherintellectualpropertyofthe thirdparty,oralicensefromTIunderthepatentsorotherintellectualpropertyofTI. ReproductionofsignificantportionsofTIinformationinTIdatabooksordatasheetsispermissibleonlyifreproductioniswithoutalteration andisaccompaniedbyallassociatedwarranties,conditions,limitations,andnotices.TIisnotresponsibleorliableforsuchaltered documentation.Informationofthirdpartiesmaybesubjecttoadditionalrestrictions. ResaleofTIcomponentsorserviceswithstatementsdifferentfromorbeyondtheparametersstatedbyTIforthatcomponentorservice voidsallexpressandanyimpliedwarrantiesfortheassociatedTIcomponentorserviceandisanunfairanddeceptivebusinesspractice. TIisnotresponsibleorliableforanysuchstatements. Buyeracknowledgesandagreesthatitissolelyresponsibleforcompliancewithalllegal,regulatoryandsafety-relatedrequirements concerningitsproducts,andanyuseofTIcomponentsinitsapplications,notwithstandinganyapplications-relatedinformationorsupport thatmaybeprovidedbyTI.Buyerrepresentsandagreesthatithasallthenecessaryexpertisetocreateandimplementsafeguardswhich anticipatedangerousconsequencesoffailures,monitorfailuresandtheirconsequences,lessenthelikelihoodoffailuresthatmightcause harmandtakeappropriateremedialactions.BuyerwillfullyindemnifyTIanditsrepresentativesagainstanydamagesarisingoutoftheuse ofanyTIcomponentsinsafety-criticalapplications. Insomecases,TIcomponentsmaybepromotedspecificallytofacilitatesafety-relatedapplications.Withsuchcomponents,TI’sgoalisto helpenablecustomerstodesignandcreatetheirownend-productsolutionsthatmeetapplicablefunctionalsafetystandardsand requirements.Nonetheless,suchcomponentsaresubjecttotheseterms. NoTIcomponentsareauthorizedforuseinFDAClassIII(orsimilarlife-criticalmedicalequipment)unlessauthorizedofficersoftheparties haveexecutedaspecialagreementspecificallygoverningsuchuse. OnlythoseTIcomponentswhichTIhasspecificallydesignatedasmilitarygradeor“enhancedplastic”aredesignedandintendedforusein military/aerospaceapplicationsorenvironments.BuyeracknowledgesandagreesthatanymilitaryoraerospaceuseofTIcomponents whichhavenotbeensodesignatedissolelyattheBuyer'srisk,andthatBuyerissolelyresponsibleforcompliancewithalllegaland regulatoryrequirementsinconnectionwithsuchuse. TIhasspecificallydesignatedcertaincomponentsasmeetingISO/TS16949requirements,mainlyforautomotiveuse.Inanycaseofuseof non-designatedproducts,TIwillnotberesponsibleforanyfailuretomeetISO/TS16949. Products Applications Audio www.ti.com/audio AutomotiveandTransportation www.ti.com/automotive Amplifiers amplifier.ti.com CommunicationsandTelecom www.ti.com/communications DataConverters dataconverter.ti.com ComputersandPeripherals www.ti.com/computers DLP®Products www.dlp.com ConsumerElectronics www.ti.com/consumer-apps DSP dsp.ti.com EnergyandLighting www.ti.com/energy ClocksandTimers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical Logic logic.ti.com Security www.ti.com/security PowerMgmt power.ti.com Space,AvionicsandDefense www.ti.com/space-avionics-defense Microcontrollers microcontroller.ti.com VideoandImaging www.ti.com/video RFID www.ti-rfid.com OMAPApplicationsProcessors www.ti.com/omap TIE2ECommunity e2e.ti.com WirelessConnectivity www.ti.com/wirelessconnectivity MailingAddress:TexasInstruments,PostOfficeBox655303,Dallas,Texas75265 Copyright©2013,TexasInstrumentsIncorporated

Datasheet下载

Datasheet下载