ICGOO在线商城 > PM6680TR

- 型号: PM6680TR

- 制造商: STMicroelectronics

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

PM6680TR产品简介:

ICGOO电子元器件商城为您提供PM6680TR由STMicroelectronics设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 提供PM6680TR价格参考¥10.59-¥21.08以及STMicroelectronicsPM6680TR封装/规格参数等产品信息。 你可以下载PM6680TR参考资料、Datasheet数据手册功能说明书, 资料中有PM6680TR详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC) |

| 描述 | IC CTLR DUAL STEP DOWN 32VFQFPN |

| 产品分类 | |

| 品牌 | STMicroelectronics |

| 数据手册 | |

| 产品图片 |

|

| 产品型号 | PM6680TR |

| rohs | 无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | - |

| 产品目录页面 | |

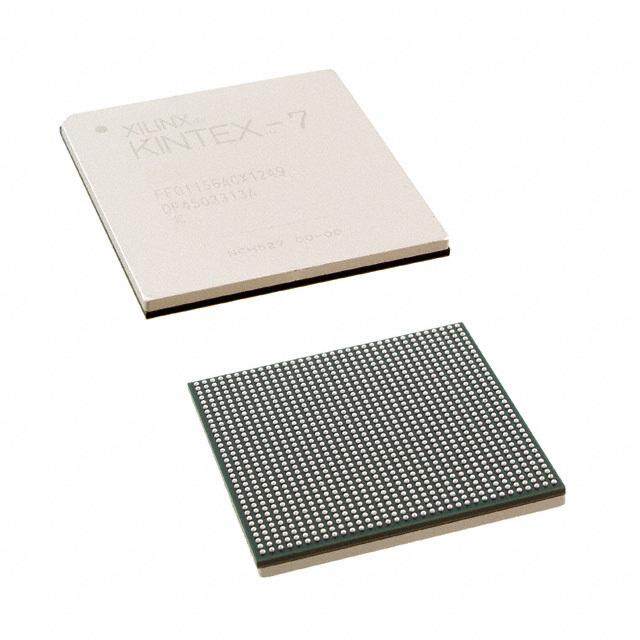

| 供应商器件封装 | 32-VFQFPN(5x5) |

| 其它名称 | 497-7859-2 |

| 其它有关文件 | http://www.st.com/web/catalog/sense_power/FM142/CL1456/SC358/PF129021?referrer=70071840 |

| 包装 | 带卷 (TR) |

| 安装类型 | 表面贴装 |

| 封装/外壳 | 32-VFQFN 裸露焊盘 |

| 工作温度 | 0°C ~ 85°C |

| 应用 | 控制器,笔记本电脑电源系统 |

| 标准包装 | 3,000 |

| 电压-输入 | 6 V ~ 28 V |

| 电压-输出 | 0.9 V ~ 5.5 V |

| 输出数 | 2 |

| 配用 | /product-detail/zh/STEVAL-ISA053V2/497-6379-ND/1833374/product-detail/zh/STEVAL-ISA053V1/497-6378-ND/1833372/product-detail/zh/STEVAL-PSQ001V1/497-6425-ND/1786212 |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

PM6680 No Rsense dual step-down controller with adjustable voltages for notebook system power Features ■ 6 V to 28 V input voltage range ■ Adjustable output voltages ■ 5 V always voltage available deliver 100 mA peak current ■ 1.237 V ± 1% reference voltage available VFQFPN-32 5X5 ■ Losslesscurrent sensing using low side MOSFETs R DS(on) ■ Negative current limit Description ■ Soft-start internally fixed at 2ms ■ Soft output discharge PM6680 is a dual step-down controller specifically designed to provide extremely high ■ Latched OVP and UVP efficiency conversion, with lossless current ■ Selectable pulse skipping at light loads sensing technique. The constant on-time ■ Selectable minimum frequency (33 kHz) in architecture assures fast load transient response pulse skip mode and the embedded voltage feed-forward provides nearly constant switching frequency operation. An ■ 4 mW maximum quiescent power embedded integrator control loop compensates ■ Independent power good signals the DC voltage error due to the output ripple. ■ Output voltage ripple compensation Pulse skipping technique increases efficiency at very light load. Moreover a minimum switching frequency of 33kHz is selectable to avoid audio Applications noise issues. The PM6680 provides a selectable switching frequency, allowing three different ■ Notebook computers values of switching frequencies for the two ■ Tablet PC or slates switching sections. The output voltages OUT1 ■ Mobile system power supply and OUT2 can be adjusted from 0.9 V to 5.5 V and from 0.9 V to 3.3 V respectively. ■ 3-4 cells Li+ battery powered devices Table 1. Device summary Order codes Package Packaging PM6680 Tray VFQFPN-32 5mm x 5mm (Exposed pad) PM6680TR Tape and reel January 2008 Rev 7 1/49 www.st.com 49

Contents PM6680 Contents 1 Simplified application schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 2 Electrical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 2.1 Maximum rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 2.2 Thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 3 Pin settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 3.1 Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 3.2 Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 4 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 5 Typical operating characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 6 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 7 Device description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 7.1 Constant On time PWM control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 7.2 Constant on time architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 7.3 Output ripple compensation and loop stability . . . . . . . . . . . . . . . . . . . . . 22 7.4 Pulse skip mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 7.5 No-audible skip mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 7.6 Current limit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 7.7 Soft start and soft end . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 7.8 Gate drivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 7.9 Reference voltage and bandgap . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 7.10 Internal linear regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 7.11 Power up sequencing and operative modes . . . . . . . . . . . . . . . . . . . . . . . 28 7.12 Monitoring and protections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 7.12.1 Power good signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 7.12.2 Thermal protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 7.12.3 Overvoltage protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 7.12.4 Undervoltage protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 2/49

PM6680 Contents 7.13 Design guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 7.13.1 Switching frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 7.13.2 Inductor selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 7.13.3 Output capacitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 7.13.4 Input capacitors selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 7.13.5 Power MOSFETs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33 7.13.6 Closing the integrator loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 7.13.7 Other parts design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38 7.13.8 Design example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40 8 Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44 9 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46 3/49

List of figures PM6680 List of figures Figure 1. Simplified application schematic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Figure 2. Pin connection (Through top view). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 3. 1.5V output efficiency vs load current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 4. 1.05V output efficiency vs load current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 5. PWM no load input battery vs input voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 6. Skip no load battery current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 7. No-audible skip no load battery current vs input voltage . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 8. Stand-by mode input battery current vs input voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 9. Shutdown mode input battery current vs input voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 10. 1.5V switching frequency vs load current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 11. 1.05V switching frequency vs load current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 12. LDO5 vs output current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 13. 1.5V voltage regulation vs load current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Figure 14. 1.05V voltage regulation vs load current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Figure 15. Voltage reference vs load current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Figure 16. OUT1, OUT2 and LDO5 power-up. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Figure 17. 1.5V load transient . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Figure 18. 1.05V load transient . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Figure 19. 1.5V soft start (0.25Ω load). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 20. 1.05V soft start (0.175Ω load). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 21. 1.5V soft end (No load). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 22. 1.05V soft end (No load). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 23. 1.5V soft end (1Ω Load) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 24. 1.05V soft end (1Ω Load) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 25. 1.5V no-audible skip mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Figure 26. 1.05V no-audible skip mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Figure 27. Functional block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Figure 28. Constant ON time PWM control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Figure 29. Constant on-time block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 Figure 30. Circuitry for output ripple compensation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 Figure 31. PWM and pulse skip mode inductor current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Figure 32. No audible skip mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Figure 33. RDSON sensing technique. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Figure 34. Current waveforms in current limit conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Figure 35. Soft start waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 Figure 36. Circuitry for output ripple compensation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37 Figure 37. Virtual ESR network . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38 Figure 38. VIN pin filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40 Figure 39. Inductor current waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41 Figure 40. Bootstrap circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41 Figure 41. Current paths, ground connection and driver traces layout . . . . . . . . . . . . . . . . . . . . . . . . 44 Figure 42. Package dimensions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47 4/49

PM6680 List of tables List of tables Table 1. Device summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Table 2. Absolute maximum ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Table 3. Thermal data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Table 4. Pin functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Table 5. Electrical characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Table 6. FSEL pin selection: typical switching frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Table 7. V5SW multifunction pin. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Table 8. Operatives modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Table 9. Protections and operatives modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 Table 10. Inductor manufacturer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33 Table 11. Output capacitor manufacturer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 Table 12. Input capacitor manufacturer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 Table 13. High side MOSFET manufacturer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 Table 14. Low side MOSFET manufacturer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36 Table 15. Dual MOSFET manufacturer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36 Table 16. Shottky diode manufacturer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36 Table 17. VFQFPN 5x5x1.0 32L Pitch 0.50 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46 Table 18. Exposed pad variations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46 Table 19. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48 5/49

Simplified application schematic PM6680 1 Simplified application schematic Figure 1. Simplified application schematic O O 1 1 D N G S VIN + PGND PGND D N G S D PGND SGN SGND9 10 11 13 12 14 1 8 2 6 28FB1 7 91 NIV BOOT2 HGATE2 PHASE2 LGATE2 CSENSE2 PGND 0SGND OUT2 COMP2 NC FB1 FB2 LPEIKSSF 423 SGND V+ 81 5ODL 68 FERV 23 SGND13 CCV BOOT1 HGATE1 PHASE1 LGATE1 CSENSE1 V5SW PM6OUT1 COMP1 SGND2 PGOOD1 PGOOD2 SHDN 12NNEE 524 + ND 23 22 21 15 20 17 29 30 16 26 27 5 SG ND G D S N G OT1 OT2 S O O B B D1 D2 O O V+ PGND V+ V+ PGO PGO D N G S PGND + N VI FB1 GND S 1 UT1+ 1 UT1- O O 6/49

PM6680 Electrical data 2 Electrical data 2.1 Maximum rating Table 2. Absolute maximum ratings Parameter Value Unit V5SW, LDO5 to PGND -0.3 to 6 V VIN to PGND -0.3 to 36 V HGATEx and BOOTx, to PHASEx -0.3 to 6 V PHASEx to PGND -0.6 (1) to36 V CSENSEx , to PGND -0.6 to 42 V CSENSEx to BOOTx -6 to 0.3 V LGATEx to PGND -0.3 (2) to LDO5 +0.3 V FBx, COMPx, SKIP, , FSEL,VREF to SGND1,SGND2 -0.3 to Vcc +0.3 V PGND to SGND1,SGND2 -0.3 to 0.3 V SHDN,PGOODx, OUTx, VCC, ENx to SGND1,SGND2 -0.3 to 6 V Power dissipation at T = 25ºC 2.8 W A Maximum withstanding voltage range test condition: VIN ±1000 CDF-AEC-Q100-002- “Human Body Model” V acceptance criteria: “Normal Performance” Other pins ±2000 1. PHASE to PGND up to -2.5 V for t<10 ns 2. LGATEx to PGND up to -1 V for t<40 ns 2.2 Thermal data Table 3. Thermal data Symbol Parameter Value Unit R Thermal resistance junction to ambient 35 °C/W thJA T Storage temperature range -50 to 150 °C STG T Junction operating temperature range -40 to 125 °C J T Operating ambient temperature range -40 to 85 °C A 7/49

Pin settings PM6680 3 Pin settings 3.1 Connections Figure 2. Pin connection (Through top view) PM6680 8/49

PM6680 Pin settings 3.2 Functions Table 4. Pin functions N° Pin Function Signal ground. Reference for internal logic circuitry. It must be connected to the signal ground plan of the power supply. The signal ground plan and the 1 SGND1 power ground plan must be connected together in one point near the PGND pin. 2 COMP2 DC voltage error compensation pin for the switching section 2 Frequency selection pin. It provides a selectable switching frequency, 3 FSEL allowing three different values of switching frequencies for the switching sections. Enable input for the switching section 2. • The section 2 is enabled applying a voltage greater than 2.4 V to this pin. • The section 2 is disabled applying a voltage lower than 0.8 V. 4 EN2 When the section is disabled the High Side gate driver goes low and Low Side gate driver goes high. If both EN1 and EN2 pins are low and SHDN pin is high the device enters in standby mode. Shutdown control input. • The device switch off if the SHDN voltage is lower than the device off threshold (Shutdown mode) • The device switch on if the SHDN voltage is greater than the device on 5 SHDN threshold. The SHDN pin can be connected to the battery through a voltage divider to program an undervoltage lockout. In shutdown mode, the gate drivers of the two switching sections are in high impedance (high-Z). 6 NC Not connected. Feedback input for the switching section 2 This pin is connected to a 7 FB2 resistive voltage-divider from OUT2 to PGND to adjust the output voltage from 0.9 V to 3.3 V. Output voltage sense for the switching section 2.This pin must be directly 8 OUT2 connected to the output voltage of the switching section. Bootstrap capacitor connection for the switching section 2. It supplies the 9 BOOT2 high-side gate driver. High-side gate driver output for section 2. This is the floating gate driver 10 HGATE2 output. Switch node connection and return path for the high side driver for the 11 PHASE2 section 2.It is also used as negative current sense input. Positive current sense input for the switching section 2. This pin must be connected through a resistor to the drain of the synchronous rectifier 12 CSENSE2 (R sensing) to obtain a positive current limit threshold for the power DSON supply controller. 13 LGATE2 Low-side gate driver output for the section 2. Power ground. This pin must be connected to the power ground plan of the 14 PGND power supply. 15 LGATE1 Low-side gate driver output for the section 1. 9/49

Pin settings PM6680 Table 4. Pin functions (continued) N° Pin Function Signal ground for analog circuitry. It must be connected to the signal ground 16 SGND2 plan of the power supply. Internal 5 V regulator bypass connection. • If V5SW is connected to OUT5 (or to an external 5 V supply) and V5SW is 17 V5SW greater than 4.9 V, the LDO5 regulator shuts down and the LDO5 pin is directly connected to OUT5 through a 3 Ω (max) switch. If V5SW is connected to GND, the LDO5 linear regulator is always on. 5 V internal regulator output. It can provide up to 100mA peak current. 18 LDO5 LDO5 pin supplies embedded low side gate drivers and an external load. Device supply voltage input and battery voltage sense. A bypass filter (4 Ω 19 VIN and 4.7 µF) between the battery and this pin is recommended. Positive current sense input for the switching section 1. This pin must be connected through a resistor to the drain of the synchronous rectifier 20 CSENSE1 (R sensing) to obtain a positive current limit threshold for the power DSON supply controller. Switch node connection and return path for the high side driver for the 21 PHASE1 section 1.It is also used as negative current sense input. High-side gate driver output for section 1. This is the floating gate driver 22 HGATE1 output. Bootstrap capacitor connection for the switching section 1. It supplies the 23 BOOT1 high-side gate driver. Pulse skipping mode control input. • If the pin is connected to LDO5 the PWM mode is enabled. • If the pin is connected to GND, the pulse skip mode is enabled. 24 SKIP • If the pin is connected to VREF the pulse skip mode is enabled but the switching frequency is kept higher than 33 kHz (No-audible pulse skip mode). Enable input for the switching section 1. • The section 1 is enabled applying a voltage greater than 2.4 V to this pin. 25 EN1 • The section 1 is disabled applying a voltage lower than 0.8 V. When the section is disabled the High Side gate driver goes low and Low Side gate driver goes high. Power Good output signal for the section 1. This pin is an open drain output 26 PGOOD1 and when the output of the switching section 1 is out of +/- 10 % of its nominal value.It is pulled down. Power Good output signal for the section 2. This pin is an open drain output 27 PGOOD2 and when the output of the switching section 2 is out of +/- 10 % of its nominal value.It is pulled down. Feedback input for the switching section 1. This pin is connected to a 28 FB1 resistive voltage-divider from OUT1 to PGND to adjust the output voltage from 0.9 V to 5.5 V. 10/49

PM6680 Pin settings Table 4. Pin functions (continued) N° Pin Function Output voltage sense for the switching section 1.This pin must be directly 29 OUT1 connected to the output voltage of the switching section. 30 COMP1 DC voltage error compensation pin for the switching section 1. Device Supply Voltage pin. It supplies all the internal analog circuitry except 31 VCC the gate drivers (see LDO5). Connect this pin to LDO5. Internal 1.237 V high accuracy voltage reference. It can deliver 50 uA. 32 VREF Bypass to SGND with a 100 nF capacitor to reduce noise. 11/49

Electrical characteristics PM6680 4 Electrical characteristics Table 5. Electrical characteristics V = 12 V, T = 0 °C to 85 °C, unless otherwise specified (1) IN A Symbol Parameter Test condition Min Typ Max Unit Supply section Vout = Vref, LDO5 in VIN Input voltage range 5.5 28 V regulation Vcc IC supply voltage 4.5 5.5 V Turn-on voltage threshold 4.8 4.9 V V Turn-off voltage threshold 4.6 4.75 V V5SW Hysteresis 20 50 mV V Maximum operating range 5.5 V V5SW LDO5 internal bootstrap Rdson V5SW > 4.9 1.8 3 Ω switch resistance OUTx,OUTx discharge-mode 18 25 Ω on-resistance OUTx,OUTx discharge-mode synchronous rectifier 0.2 0.36 0.6 V Turn-on level FBx > VREF, Vref in Pin Operating power consumption 4 mW regulation, V5WS to 5 V Ish Operating current sunk by V SHDN connected to GND, 14 18 µA IN Isb Operating current sunk by V ENx to GND, V5SW to GND 190 250 µA IN Shutdown section Device on threshold 1.2 1.5 1.7 V V SHDN Device off threshold 0.8 0.85 0.9 V Soft start section Soft start ramp time 2 3.5 ms Current limit and zero crossing comparator I Input bias current limit 90 100 110 µA CSENSE Comparator offset VCSENSE-VPGND -6 6 mV Zero crossing comparator offset V - V -1 11 mV PGND PHASE Fixed negative current limit V - V -120 mV threshold PGND PHASE 12/49

PM6680 Electrical characteristics Table 5. Electrical characteristics (continued) V = 12 V, T = 0 °C to 85 °C, unless otherwise specified (1) IN A Symbol Parameter Test condition Min Typ Max Unit On time pulse width FSEL to OUT1=1.5 V 550 650 750 GND OUT2=1.05 V 230 270 315 FSEL to OUT1=1.5 V 375 445 515 Ton On time duration ns VREF OUT2=1.05 V 175 210 245 FSEL to OUT1=1.5 V 285 340 395 LDO5 OUT2=1.05 V 125 150 175 OFF time T Minimum off time 350 500 ns OFFMIN Voltage reference Voltage accuracy 4 V < V < 5.5 V 1.224 1.236 1.249 V LDO5 Load regulation -100 µA< I < 100 µA -4 4 mV V REF REF Undervoltage lockout fault Falling edge of REF 0.95 mV threshold Integrator FB Voltage accuracy -909 900 909 mV FB Input bias current 0.1 µA Normal mode 250 Over voltage clamp COMP Pulse skip mode 60 mV Under voltage clamp -150 Line regulation Both SMPS, 6 V<Vin<28 V(2) 0.004 %/V LDO5 linear regulator 6 V<VIN<28 V , LDO5 linear output voltage 4.9 5.0 5.1 V 0 < I < 50 mA LDO5 V LDO5 6 V< VIN < 28 V, LDO5 line regulation 0.004 %/V I = 20 mA LDO5 , I LDO5 Current limit V > UVLO 270 330 400 mA LDO5 LDO5 ULVO Under Voltage Lockout of LDO5 3.94 4 4.13 V 13/49

Electrical characteristics PM6680 Table 5. Electrical characteristics (continued) V = 12 V, T = 0 °C to 85 °C, unless otherwise specified (1) IN A Symbol Parameter Test condition Min Typ Max Unit High and low gate drivers HGATEx high state (pullup) 2.0 3 Ω HGATE driver on-resistance HGATEx low state 1.6 2.7 Ω (pulldown) LGATEx high state (pullup) 1.4 2.1 Ω LGATE driver on-resistance LGATEx low state (pulldown) 0.8 1.2 Ω PGOOD pins UVP/OVP protections OVP Over voltage threshold Both SMPS sections with 112 116 120 % respect to VREF. UVP Under voltage threshold 65 68 71 % Upper threshold 107 110 113 % (VFB-VREF) PGOOD1,2 Lower threshold 88 91 94 % (VFB-VREF) I PGOOD leakage current V forced to 5.5 V 1 uA PGOOD1,2 PGOOD1,2 V Output low voltage ISink = 4 mA 150 250 mV PGOOD1,2 Thermal shutdown T Shutdown temperature 150 °C SDN Power management pins SMPS disabled level 0.8 EN1,2 V SMPS enabled level 2.4 Low level (3) 0.5 FSEL Frequency selection range Middle level (3) 1.0 V -1.5 V LDO5 High level (3) V -0.8 LDO5 Pulse skip mode (3) 0.5 SKIP Ultrasonic mode (3) 1.0 V -1.5 V LDO5 PWM mode (3) V -0.8 LDO5 V = 0 to 5 V 1 EN1,2 V = 0 to 5 V 1 SKIP Input leakage current µA V = 0 to 5 V 1 SHDN V = 0 to 5 V 1 FSEL 1. T = T All parameters at operating temperature extremes are guaranteed by design and statistical analysis A J, (not production tested). 2. by design 3. by demoboard test 14/49

PM6680 Typical operating characteristics 5 Typical operating characteristics FSEL = GND (200/300 kHz), SKIP = GND (skip mode), V5SW = V5SW = EXT5V (external 5 V power supply connected), input voltage VIN = 12 V, SHDN, EN1 and EN2 high, OUT1 = 1.5 V, OUT2 = 1.05 V, no load unless specified) Figure 3. 1.5 V output efficiency vs Figure 4. 1.05 V output efficiency vs load current load current Figure 5. PWM no load input battery vs Figure 6. Skip no load battery current input voltage 15/49

Typical operating characteristics PM6680 Figure 7. No-audible skip no load Figure 8. Stand-by mode input battery battery current vs input current vs input voltage voltage Figure 9. Shutdown mode input battery Figure 10. 1.5 V switching frequency vs current vs input voltage load current Figure 11. 1.05 V switching frequency vs Figure 12. LDO5 vs output current load current 16/49

PM6680 Typical operating characteristics Figure 13. 1.5 V voltage regulation Figure 14. 1.05 V voltage regulation vs load current vs load current Figure 15. Voltage reference vs Figure 16. OUT1, OUT2 and LDO5 load current power-up Figure 17. 1.5 V load transient Figure 18. 1.05 V load transient 17/49

Typical operating characteristics PM6680 Figure 19. 1.5 V soft start (0.25Ω load) Figure 20. 1.05 V soft start (0.175Ω load) Figure 21. 1.5 V soft end (No load) Figure 22. 1.05 V soft end (No load) Figure 23. 1.5 V soft end (1Ω Load) Figure 24. 1.05 V soft end (1Ω Load) 18/49

PM6680 Typical operating characteristics Figure 25. 1.5 V no-audible skip mode Figure 26. 1.05 V no-audible skip mode 19/49

Block diagram PM6680 6 Block diagram Figure 27. Functional block diagram VIN 5V + VCC REFERENCE VREF LINEAR UVLO GENERATOR REGULATOR 4V - VREF LDO5 LDO5 ENABLE NC 4.8V + - UVLO FB2 V5SW OUT2 FB1 VCC SKIP FREQUENCY FSEL SELECTOR OUT1 BOOT2 BOOT1 LEVEL OUT2 OUT1 LEVEL HGATE2 SHIFTER SHIFTER HGATE1 SMPS SMPS CONTROLLER CONTROLLER PHASE2 PHASE1 CSENSE2 CSENSE1 COMP2 COMP1 LDO5 LDO5 LGATE2 LGATE1 PGOOD2 PGOOD1 SHDN LDO5 ENABLE STARTUP CONTROLLER EN1 EN2 TERMIC TERMIC FAULT CONTROLLER UVLO 20/49

PM6680 Device description 7 Device description The PM6680 is a dual step-down controller dedicated to provide logic voltages for notebook computers. It is based on a Constant On Time control architecture. This type of control offers a very fast load transient response with a minimum external component count. A typical application circuit is shown in Figure27. The PM6680 regulates two adjustable output voltages: OUT1 and OUT2. The switching frequency of the two sections can be adjusted to 200/300 kHz, 300/400 kHz or 400/500 kHz respectively. In order to maximize the efficiency at light load condition, a pulse skipping mode can be selected. The PM6680 includes also a 5 V linear regulator (LDO5) that can power the switching drivers. If the output OUT1 regulates 5 V, in order to maximize the efficiency in higher consumption status, the linear regulator can be turned off and their outputs can be supplied directly from the switching outputs. The PM6680 provides protection versus overvoltage, undervoltage and over temperature as well as power good signals for monitoring purposes. An external 1.237 V reference is available. 7.1 Constant On time PWM control If the SKIP pin is tied to 5 V, the device works in PWM mode. Each power section has an independent on time control.The PM6680 employees a pseudo-fixed switching frequency, Constant On Time (COT) controller as core of the switched mode section. Each power section has an independent COT control. The COT controller is based on a relatively simple algorithm and uses the ripple voltage due to the output capacitor's ESR to trigger the fixed on-time one-shot generator. In this way, the output capacitor's ESR acts as a current sense resistor providing the appropriate ramp signal to the PWM comparator. On-time one-shot duration is directly proportional to the output voltage, sensed at the OUT1/OUT2 pins, and inversely proportional to the input voltage, sensed at the VIN pin, as follows: Equation 1 V T = K⋅-----O----U---T-- ON V IN This leads to a nearly constant switching frequency, regardless of input and output voltages. When the output voltage goes lower than the regulated voltage Vreg, the on-time one shot generator directly drives the high side MOSFET for a fixed on time allowing the inductor current to increase; after the on time, an off time phase, in which the low side MOSFET is turned on, follows. Figure28 shows the inductor current and the output voltage waveforms in PWM mode. 21/49

Device description PM6680 Figure 28. Constant ON time PWM control The duty cycle of the buck converter in steady state is: Equation 2 V D= -----O----U---T-- V IN The PWM control works at a nearly fixed frequency f : SW Equation 3 V -----O----U---T-- V f = ----------------I-N--------------= 1⁄K SW V on K ×-----O----U---T-- on V IN As mentioned the steady state switching frequency is theoretically independent from battery voltage and from output voltage. Actually the frequency depends on parasitic voltage drops that are present during the charging path(high side switch resistance, inductor resistance(DCR)) and discharging path(low side switch resistance, DCR). As a result the switching frequency increases as a function of the load current. Standard switching frequency values can be selected for both sections by pin FSEL as shown in the following table: T able 6. FSEL pin selection: typical switching frequency Fsw@OUT1 = 1.5 V (kHz) Fsw@OUT2 = 1.05 V (kHz) FSEL = GND 200 325 FSEL = VREF 290 425 FSEL = LDO5 390 590 22/49

PM6680 Device description 7.2 Constant on time architecture Figure29 shows the simplified block diagram of a Constant On Time controller. A minimum off-time constrain (300 ns typ.) is introduced to allow inductor valley current sensing on synchronous switch. A minimum on-time (70 ns) is also introduced to assure the start-up switching sequence. PM6680 has a one-shot generator for each power section that turns on the high side MOSFET when the following conditions are satisfied simultaneously: the PWM comparator is high, the synchronous rectifier current is below the current limit threshold, and the minimum off-time has timed out. Once the on-time has timed out, the high side switch is turned off, while the synchronous switch is turned on according to the anti-cross conduction circuitry management. When the negative input voltage at the PWM comparator (Figure29), which is a scaled- down replica of the output voltage (see the external R1/R2 divider in Figure29), reaches the valley limit (determined by internal reference Vr = 0.9 V), the low-side MOSFET is turned off according to the anti-cross conduction logic once again, and a new cycle begins. Figure 29. Constant on-time block diagram TTTTooooffffffff----mmmmiiiinnnn BBBBOOOOOOOOTTTT CCCCSSSSEEEENNNNSSSSEEEE +++ PPPPoooossssiiiittttiiiivvvveeee SS QQ LLLLeeeevvvveeeellll HHHHSSSS CCCCuuuurrrrrrrreeeennnntttt --- ddddrrrriiiivvvveeeerrrr HHHHGGGGAAAATTTTEEEE sssshhhhiiiifffftttteeee LLLLiiiimmmmiiiitttt rrrr VVVVrrrr ++ RR QQ PPPPHHHHAAAASSSSEEEE CCCCOOOOMMMMPPPP -- PPPPWWWWMMMM +++ 000...222555VVV +++ 000...555VVV CCCCoooommmmppppaaaarrrraaaattttoooo TTTToooonnnn --- ggggmmmm rrrr --- -- ++ LLLLDDDDOOOO5555 VVVVrrrr FFFFBBBB LLLLSSSS ZZZZeeeerrrroooo----ccccrrrroooossssssss.... SS QQ ddddrrrriiiivvvveeeerrrr LLLLGGGGAAAATTTTEEEE OOOOUUUUTTTT ++ CCCCoooommmmpppp.... PPPPGGGGNNNNDDDD -- RR bbbbaaaannnnddddggggaaaa VVVVIIIINNNN LLLLDDDDOOOO5555 pppp VVVVRRRREEEEFFFF 00..55VV ++ 1111....222233336666VVVV VVVVrrrr SSSSKKKKIIIIPPPP -- 23/49

Device description PM6680 7.3 Output ripple compensation and loop stability In a classic Constant On Time control, the system regulates the valley value of the output voltage and not the average value, as shown in Figure28 In this condition, the output voltage ripple is source of a DC static error. To compensate this error, an integrator network can be introduced in the control loop, by connecting the output voltage to the COMP1/COMP2 (for the OUT1 and OUT2 sections respectively) pin through a capacitor C as in Figure30 INT Figure 30. Circuitry for output ripple compensation COMP PIN VOLTAGE ∆V Vr VVrr + t CCOOMMPP I=gm(V1-Vr) - PPWWMM OVOULTTPAUGT E CCFFIILLTT CCoommppaarraattoorr ∆V CCIINNTT ggmm+ VVCCIINNTT VVrr VV11 t RRIINNTT LL OOUUTT RROOUUTT RR22 FFBB DD CCOOUUTT RR11 The integrator amplifier generates a current, proportional to the DC errors between the FB voltage and Vr, which decreases the output voltage in order to compensate the total static error, including the voltage drop on PCB traces. In addition, C provides an AC path for the INT output ripple. In steady state, the voltage on COMP1/COMP2 pin is the sum of the reference voltage Vr and the output ripple (see Figure30). In fact when the voltage on the COMP pin reaches Vr, a fixed Ton begins and the output increases. For example, we consider Vout = 5 V with an output ripple of ∆V = 50 mV. Considering C >> C , the C DC voltage drop V is about 5 V-Vr+25 mV = 4.125 V. C INT FILT INT CINT INT assures an AC path for the output voltage ripple. Then the COMP pin ripple is a replica of the output ripple, with a DC value of Vr + 25 mV = 925 mV. For more details about the output ripple compensation network, see the Section7.13.6: Closing the integrator loop on page37 in the Design guidelines. In steady state the FB pin voltage is about Vr and the regulated output voltage depends on the external divider: Equation 4 R OUT = Vr×⎛1+-----2--⎞ ⎝ R ⎠ 1 24/49

PM6680 Device description 7.4 Pulse skip mode If the SKIP pin is tied to ground, the device works in skip mode. At light loads a zero-crossing comparator truncates the low-side switch on-time when the inductor current becomes negative. In this condition the section works in discontinuous conduction mode. The threshold between continuous and discontinuous conduction mode is: Equation 5 V −V ILOAD(SKIP)= IN OUT ×T 2×L ON For higher loads the inductor current doesn't cross the zero and the device works in the same way as in PWM mode and the frequency is fixed to the nominal value. Figure 31. PWM and pulse skip mode inductor current PWM mode Pulse skip mode Low side on Inductor current Load current 0 Ton1 Toff Time Ton2 Toff Ton1=Ton2 Low side off Figure31 shows inductor current waveforms in PWM and SKIP mode. In order to keep average inductor current equal to load current, in SKIP mode some switching cycles are skipped. When the output ripple reaches the regulated voltage Vreg, a new cycle begins. The off cycle duration and the switching frequency depend on the load condition. As a result of the control technique, losses are reduced at light loads, improving the system efficiency. 7.5 No-audible skip mode If SKIP pin is tied to VREF, a no-audible skip mode with a minimum switching frequency of 33 kHz is enabled. At light load condition, If there is not a new switching cycle within a 30 us (typ.) period, a no-audible skip mode cycle begins. 25/49

Device description PM6680 Figure 32. No audible skip mode Inductor current No audible skip mode ∼30us Time 0 Low side The low side switch is turned on until the output voltage crosses about Vreg+1 %. Then the high side MOSFET is turned on for a fixed on time period. Afterwards the low side switch is enabled until the inductor current reaches the zero-crossing threshold. This keeps the switching frequency higher than 33 kHz. As a consequence of the control, the regulated voltage can be slightly higher than Vreg (up to 1 %). If, due to the load, the frequency is higher than 33 kHz, the device works like in skip mode. No-audible skip mode reduces audio frequency noise that may occur in pulse skip mode at very light loads, keeping the efficiency higher than in PWM mode. 7.6 Current limit The current-limit circuit employs a "valley" current-sensing algorithm. During the conduction time of the low side MOSFET the current flowing through it is sensed. The current-sensing element is the low side MOSFET on-resistance (Figure33). Figure 33. RDSON sensing technique HGATE HS PHASE Rcsense CSENSE LGATE LS RDSon 26/49

PM6680 Device description An internal 100 µA current source is connected to CSENSE pin and determines a voltage drop on R . If the voltage across the sensing element is greater than this voltage CSENSE drop, the controller doesn't initiate a new cycle. A new cycle starts only when the sensed current goes below the current limit. Since the current limit circuit is a valley current limit, the actual peak current limit is greater than the current limit threshold by an amount equal to the inductor ripple current. Moreover the maximum output current is equal to the valley current limit plus half of the inductor ripple current: Equation 6 ∆I I (max)=I + L LOAD Lvalley 2 The output current limit depends on the current ripple, as shown in Figure34: Figure 34. Current waveforms in current limit conditions Maximum load current Current DC current limit = maximum load is influenced by the inductor current ripple Inductor current Valley current threshold Time Being fixed the valley threshold, the greater the current ripple is, greater the DC output current is The valley current limit can be set with resistor R : CSENSE Equation 7 R ×I DSon Lvalley R = CSENSE I CSENSE Where I = 100 uA, R is the drain-source on resistance of the low side switch. CSENSE DSon Consider the temperature effect and the worst case value in R calculation. DSon The accuracy of the valley current threshold detection depends on the offset of the internal comparator (∆V ) and on the accuracy of the current generator(∆V ): OFF CSENSE Equation 8 ∆I ∆I ⎡ ∆V ⎤ ∆R ∆R Lvalley = CSENSE +⎢ OFF ×100⎥+ CSENSE + SNS ILvalley ICSENSE ⎣RCSENSE ×ICSENSE ⎦ RCSENSE RSNS 27/49

Device description PM6680 Where RSNS is the sensing element (R ) DSon PM6680 provides also a fixed negative peak current limit to prevent an excessive reverse inductor current when the switching section sinks current from the load in PWM mode. This negative current limit threshold is measured between PHASE and SGND pins, comparing the magnitude drop on the PHASE node during the conduction time of the low side MOSFET with an internal fixed voltage of 120 mV. If the current is sensed on the low side MOSFET, the negative valley-current limit I (if the NEG device works in PWM mode) is given by: Equation 9 120mV I = NEG R DSon 7.7 Soft start and soft end Each switching section is enabled separately by asserting high EN1/EN2 pins respectively. In order to realize the soft start, at the startup the overcurrent threshold is set 25 % of the nominal value and the undervoltage protection (see related sections) is disabled. The controller starts charging the output capacitor working in current limit. The overcurrent threshold is increased from 25 % to 100 % of the nominal value with steps of 25 % every 700 µs (typ.). After 2.8 ms (typ.) the undervoltage protection is enabled. The soft start time is not programmable. A minimum capacitor CINT is required to ensure a soft start without any overshoot on the output: Equation 10 6uA C ≥ ×C INT I ∆I out Lvalley + L 4 2 Figure 35. Soft start waveforms Switching output Current limit threshold EN1/EN2 Time 28/49

PM6680 Device description When a switching section is turned off (EN1/EN2 pins low), the controller enters in soft end mode.The output capacitor is discharged through an internal 18 Ω P-MOSFET switch; when the output voltage reaches 0.3 V, the low-side MOSFET turns on, keeping the output to ground. The soft end time also depends on load condition. 7.8 Gate drivers The integrated high-current drivers allow to use different power MOSFETs. The high side driver MOSFET uses a bootstrap circuit which is indirectly supplied by LDO5 output. The BOOT and PHASE pins work respectively as supply and return rails for the HS driver. The low side driver uses the internal LDO5 output for the supply rail and PGND pin as return rail. An important feature of the gate drivers is the adaptive anti-cross conduction protection, which prevents high side and low side MOSFETs from being on at the same time. When the high side MOSFET is turned off the voltage at the phase node begins to fall. The low side MOSFET is turned on when the voltage at the phase node reaches an internal threshold. When the low side MOSFET is turned off, the high side remains off until the LGATE pin voltage goes approximately under 1 V. The power dissipation of the drivers is a function of the total gate charge of the external power MOSFETs and the switching frequency, as shown in the following equation: Equation 11 P =V ×Q ×f driver driver g sw Where V is the 5 V driver supply. driver 7.9 Reference voltage and bandgap The 1.237 V (typ.) internal bandgap voltage is accurate to ± 1 % over the temperature range. It is externally available (VREF pin) and can supply up to 100 µA and can be used as a voltage threshold for the multifunction pins FSEL and SKIP to select the appropriate working mode. Bypass VREF to ground with a 100 nF minimum capacitor. If VREF goes below 0.87 V (typ.) , the system detects a fault condition and all the circuitry is turned off. A toggle on the input voltage (power on reset) or a toggle on SHDN pin is necessary to restart the device. An internal divider of the the bandgap provides a voltage reference Vr of 0.9 V. This voltage is used as reference for the linear and the switching regulators outputs. The overvoltage protection, the undervoltage protection and the power good signals are referred to Vr. 29/49

Device description PM6680 7.10 Internal linear regulator The PM6680 has an internal linear regulator providing 5 V (LDO5) at ±2 % accuracy. High side drivers, low side drivers and most of internal circuitry are supplied by LDO5 output through VCC pin (an external RC filter may be applied between LDO5 and VCC). The linear regulator can provide an average output current of 50 mA and a peak output current of 100mA. Bypass LDO5 output with a minimum 1 µF ceramic capacitor and a 4,7 µF tantalum capacitor ( ESR 2 Ω). If the 5 V output goes below 4 V, the system detects a fault condition and all the circuitry is turned off. A power on reset or a toggle on SHDN pin is necessary to restart the device. V5SW pin allows to keep the 5 V linear regulator always active or to enable the internal bootstrap-switch over function: if the 5 V switching output is connected to V5SW, when the voltage on V5SW pin is above 4.8 V, an internal 3.0 Ω max p-channel MOSFET switch connects V5SW pin to LDO5 pin and simultaneously LDO5 shuts down. This configuration allows to achieve higher efficiency. V5SW can be connected also to an external 5V supply. LDO5 regulator turns off and LDO5 is supplied externally. If V5SW is connected to ground, the internal 5V regulator is always on and supplies LDO5 output. Table 7. V5SW multifunction pin V5SW Description GND The 5 V linear regulator is always turned on and supplies LDO5 output. Switching 5V The 5 V linear regulator is turned off when the voltage on V5SW is above 4.8 V and output LDO5 output is supplied by the switching 5 V output. External 5V The 5 V linear regulator is turned off when the voltage on V5SW is above 4.8 V and supply LDO5 output is supplied by the external 5 V. 7.11 Power up sequencing and operative modes Let's consider SHDN, EN1 and EN2 low at the beginning. The battery voltage is applied as input voltage. The device is in shutdown mode. When the SHDN pin voltage is above the shutdown device on threshold (1.5 V typ.), the controller begins the power-up sequence. All the latched faults are cleared. LDO5 undervoltage control is blanked for 4 ms and the internal regulator LDO5 turns on. If the LDO5 output is above the UVLO threshold after this time, the device enters in standby mode. The switching outputs are kept to ground by turning on the low side MOSFETs. When EN1 and EN2 pins are forced high the switching sections begin their soft start sequence. T able 8. Operatives modes Mode Conditions Description SHDN is high, Switching regulators are enabled; internal linear Run EN1/EN2 pins are high regulators outputs are enabled. Internal Linear regulators active (LDO5 is always on). Both EN1/EN2 pins are low Standby In Standby mode LGATE1/LGATE2 pins are forced and SHDN pin is high high while HGATE1/HGATE2 pins are forced low. Shutdown SHDN is low All circuits off. 30/49

PM6680 Device description 7.12 Monitoring and protections 7.12.1 Power good signals The PM6680 provides three independent power good signals: one for each switching section (PGOOD1/PGOOD2). PGOOD1/PGOOD2 signals are low if the output voltage is out of ±10 % of the designed set point or during the soft-start, the soft end and when the device works in standby and shutdown mode. 7.12.2 Thermal protection The PM6680 has a thermal protection to preserve the device from overheating. The thermal shutdown occurs when the die temperature goes above +150 °C. In this case all internal circuitry is turned off and the power sections are turned off after the discharge mode. A power on reset or a toggle on the SHDN pin is necessary to restart the device. 7.12.3 Overvoltage protection When the switching output voltage is about 115 % of its nominal value, a latched overvoltage protection occurs. In this case, the synchronous rectifier immediately turns on while the high-side MOSFET turns off. The output capacitor is rapidly discharged and the load is preserved from being damaged. The overvoltage protection is also active during the soft start. Once an overvoltage protection has been detected, a toggle on SHDN, EN1/EN2 pins or a power on reset is necessary to exit from the latched state. 7.12.4 Undervoltage protection When the switching output voltage is below 70 % of its nominal value, a latched undervoltage protection occurs. In this case the switching section is immediately disabled and both switches are open. The controller enters in soft end mode and the output is eventually kept to ground, turning low side MOSFET on. The undervoltage circuit protection is enabled only at the end of the soft-start. Once an overvoltage protection has been detected, a toggle on SHDN, EN1/EN2 pin or a power on reset is necessary to clear the undervoltage fault and starts with a new soft-start phase. Table 9. Protections and operatives modes Mode Conditions Description LGATE1/LGATE2 pin is forced high, LDO5 remains Overvoltage OUT1/OUT2 > 115 % of active. Exit by a power on reset or toggling SHDN or protection the nominal value EN1/EN2 LGATE1/LGATE2 is forced high after the soft end Undervoltage OUT1/OUT2 < 70 % of the mode, LDO5 remains active. Exit by a power on reset protection nominal value or toggling SHDN or EN1/EN2 Thermal All circuitry off. Exit by a POR on VIN or toggling T > +150 ºC shutdown J SHDN. 31/49

Device description PM6680 7.13 Design guidelines The design of a switching section starts from two parameters: ● Input voltage range: in notebook applications it varies from the minimum battery voltage, V to the AC adapter voltage, V INmin INmax. ● Maximum load current: it is the maximum required output current, I . LOAD(max) 7.13.1 Switching frequency It's possible to set 3 different working frequency ranges for the two sections with F pin SEL (Table7 on page30). Switching frequency mainly influences two parameters: ● Inductor size: for a given saturation current and RMS current, greater frequency allows to use lower inductor values, which means smaller size. ● Efficiency: switching losses are proportional to frequency. High frequency generally involves low efficiency. 7.13.2 Inductor selection Once that switching frequency is defined, inductor selection depends on the desired inductor ripple current and load transient performance. Low inductance means great ripple current and could generate great output noise. On the other hand, low inductor values involve fast load transient response. A good compromise between the transient response time, the efficiency, the cost and the size is to choose the inductor value in order to maintain the inductor ripple current ∆I L between 20 % and 50 % of the maximum output current I (max). The maximum ∆I LOAD L occurs at the maximum input voltage. With this considerations, the inductor value can be calculated with the following relationship: Equation 12 V −V V L = IN OUT × OUT f ×∆I V sw L IN where f is the switching frequency, V is the input voltage, V is the output voltage and SW IN OUT ∆I is the selected inductor ripple current. L In order to prevent overtemperature working conditions, inductor must be able to provide an RMS current greater than the maximum RMS inductor current I : LRMS Equation 13 (∆I (max))2 I = (I (max))2 + L LRMS LOAD 12 Where ∆I (max) is the maximum ripple current: L 32/49

PM6680 Device description Equation 14 V −V V ∆I (max)= INmax OUT × OUT L f ×L V sw INmax If hard saturation inductors are used, the inductor saturation current should be much greater than the maximum inductor peak current I : peak Equation 15 ∆I (max) Ipeak =I (max)+ L LOAD 2 Using soft saturation inductors it's possible to choose inductors with saturation current limit nearly to Ipeak. Below there is a list of some inductor manufacturers. Table 10. Inductor manufacturer Manufacturer Series Inductor value (uH) RMS current (A) Saturation current (A) COILCRAFT SER1360 1 to 8 6 to 9.5 7 to 31 COILCRAFT MLC 0.7 to 4.5 13.6 to 17.3 11.5 to 26 TDK RLF12560 1 to 10 7.5 to 14.4 7.5 to 18.5 7.13.3 Output capacitor The selection of the output capacitor is based on the ESR value R and the voltage rating out rather than on the capacitor value C . out The output capacitor has to satisfy the output voltage ripple requirements. Lower inductor value can reduce the size of the choke but increases the inductor current ripple ∆I . L Since the voltage ripple V is given by: RIPPLEout Equation 16 V =R ×∆I RIPPLEout out L A low ESR capacitor is required to reduce the output voltage ripple. Switching sections can work correctly even with 20 mV output ripple. However, to reduce jitter noise between the two switching sections it's preferable to work with an output voltage ripple greater than 30 mV. If lower output ripple is required, a further compensation network is needed (see Section7.13.6: Closing the integrator loop on page37). Finally the output capacitor choice deeply impacts on the load transient response (see Load transient response paragraph). Below there is a list of some capacitor manufacturers. 33/49

Device description PM6680 Table 11. Output capacitor manufacturer Manufacturer Series Capacitor value (uF) Rated voltage (V) ESR max (mΩ) SANYO POSCAP TPB,TPD, TPE 100 to 470 2.5 to 6.3 12 to 65 PANASONIC SPCAP UD, UE 100 to 470 2 to 6.3 7 to 18 7.13.4 Input capacitors selection In a buck topology converter the current that flows into the input capacitor is a pulsed current with zero average value. The input RMS current of the two switching sections can be roughly estimated as follows: Equation 17 I = D ×I2×(1−D )+D ×I2×(1−D ) CinRMS 1 1 1 2 2 2 Where D , D are the duty cycles and I1, I2 are the maximum load currents of the two 1 2 sections. Input capacitor should be chosen with an RMS rated current higher than the maximum RMS current given by both sections. Tantalum capacitors are good in term of low ESR and small size, but they occasionally can burn out if subjected to very high current during the charge. Ceramic capacitors have usually a higher RMS current rating with smaller size and they remain the best choice. Below there is a list of some ceramic capacitor manufacturers. Table 12. Input capacitor manufacturer Manufacturer Series Capacitor value (uF) Rated voltage (V) TAYIO YUDEN UMK325BJ106KM-T 10 50 TAYIO YUDEN GMK325BJ106MN 10 35 TDK C3225X5R1E106M 10 25 34/49

PM6680 Device description 7.13.5 Power MOSFETs Logic-level MOSFETs are recommended, since low side and high side gate drivers are powered by LDO5. Their breakdown voltage VBR must be higher than V . DSS INmax In notebook applications, power management efficiency is a high level requirement. The power dissipation on the power switches becomes an important factor in switching selections. Losses of high-side and low-side MOSFETs depend on their working conditions. The power dissipation of the high-side MOSFET is given by: Equation 18 P =P +P DHighSide conduction switching Maximum conduction losses are approximately: Equation 19 V P =R × OUT ×I (max)2 conduction DSon LOAD V INmin where R is the drain-source on resistance of the high side MOSFET. Switching losses DSon are approximately: Equation 20 ∆I ∆I V ×(I (max)− L)×t ×f V ×(I (max)+ L)×t ×f IN LOAD 2 on sw IN LOAD 2 off sw P = + switching 2 2 where ton and toff are the switching times of the turn off and turn off phases of the MOSFET. As general rule, high side MOSFETs with low gate charge are recommended, in order to minimize driver losses. Below there is a list of possible choices for the high side MOSFET. Table 13. High side MOSFET manufacturer Manufacturer Type Gate charge (nC) Rated reverse voltage (V) ST STS12NH3LL 10 30 ST STS17NH3LL 18 30 The power dissipation of the low side MOSFET is given by: Equation 21 P =P DLowSide conduction Maximum conduction losses occur at the maximum input voltage: 35/49

Device description PM6680 Equation 22 ⎛ V ⎞ P =R ×⎜1− OUT ⎟×I (max)2 conduction DSon ⎜ ⎟ LOAD ⎝ VINmax ⎠ Choose a synchronous rectifier with low R . When high side MOSFET turns on, the fast DSon variation of the phase node voltage can bring up even the low side gate through its gate- drain capacitance C , causing cross-conduction problems. Choose a low side MOSFET RSS that minimizes the ratio C /C (C = C - C ). RSS GS GS ISS RSS Below there is a list of some possible low side MOSFETs. Table 14. Low side MOSFET manufacturer C Manufacturer Type R (mΩ) RSS Rated reverse voltage (V) DSon C GS ST STS17NF3LL 5.5 0.047 30 ST STS25NH3LL 3.5 0.011 30 Dual n-channel MOSFETS can be used in applications with a maximum output current of about 3 A. Below there is a list of some MOSFET manufacturers. Table 15. Dual MOSFET manufacturer Rated reverse Manufacturer Type RDSon (mΩ) Gate charge (nC) voltage (V) ST STS8DNH3LL 25 10 30 ST STS4DNF60L 65 32 60 A rectifier across the low side MOSFET is recommended. The rectifier works as a voltage clamp across the synchronous rectifier and reduces the negative inductor swing during the dead time between turning the high-side MOSFET off and the synchronous rectifier on. It can increase the efficiency of the switching section, since it reduces the low side switch losses. A shottky diode is suitable for its low forward voltage drop (0.3 V). The diode reverse voltage must be greater than the maximum input voltage V . A minimum recovery INmax reverse charge is preferable. Below there is a list of some shottky diode manufacturers. Table 16. Shottky diode manufacturer Forward Rated reverse Reverse current Manufacturer Series voltage (V) voltage (V) (uA) ST STPS1L30M 0.34 30 0.00039 ST STPS1L20M 0.37 20 0.000075 36/49

PM6680 Device description 7.13.6 Closing the integrator loop The design of external feedback network depends on the output voltage ripple. If the ripple is higher than approximately 30 mV, the feedback network (Figure35) is usually enough to keep the loop stable. Figure 36. Circuitry for output ripple compensation COMP PIN VOLTAGE ?V Vr VVrr + t CCOOMMPP I=gm(V1-Vr) - PPWWMM OVOULTTPAUGT E CCFFIILLTT CCoommppaarraattoorr ?V CCIINNTT ggmm+ VVCCIINNTT VVrr VV11 RRIINNTT t LL OOUUTT RR22 RROOUUTT FFBB DD CCOOUUTT RR11 The stability of the system depends firstly on the output capacitor zero frequency. The following condition should be satisfied: Equation 23 k f >k×f = sw Zout 2π×C ×R out out where k is a design parameter greater than 3 and R is the ESR of the output capacitor. It out determinates the minimum integrator capacitor value C : INT Equation 24 g Vr C > m × INT ⎛f ⎞ V 2π×⎜ sw −f ⎟ OUT Zout ⎝ k ⎠ where gm = 50 us is the integrator transconductance. In order to ensure stability it must be also verified that: Equation 25 g Vr C > m × INT 2π×f V Zout OUT 37/49

Device description PM6680 In order to reduce ground noise due to load transient on the other section, it is recommended to add a resistor R and a capacitor C that, together with C , realize a INT filt INT low pass filter (see Figure36). The cutoff frequency f must be much greater (10 or more CUT times) than the switching frequency of the section: Equation 26 1 R = INT C ×C 2π×f × INT filt CUT C +C INT filt Due to the capacitive divider (C , C ), the ripple voltage at the COMP pin is given by: INT filt Equation 27 C V =V × INT =V ×q RIPPLE RIPPLEout RIPPLEout INT C +C INT filt Where V is the output ripple and q is the attenuation factor of the output ripple. RIPPLEout If the ripple is very small (lower than approximately 30 mV), a further compensation network, named virtual ESR network, is needed. This additional part generates a triangular ripple that is added to the ESR output voltage ripple at the input of the integrator network. The complete control schematic is represented in Figure37. Figure 37. Virtual ESR network CCOOMMPP PPIINN TT NNOODDEE VVOOLLTTAAGGEE VVOOLLTTAAGGEE ??VV11 ??VV11 VVrr OOUUTTPPUUTT tt VVOOLLTTAAGGEE ??VV tt CCCCFFFFIIIILLLLTTTT CCCCOOOOMMMMPPPP VVVVrrrr ++ -- PPPPWWWWMMMM tt CCCCoooommmmppppaaaarrrraaaattttoooorrrr RRRR1111 TT RRRRIIIINNNNTTTT CCCCIIIINNNNTTTT ---ggggmmmm++ VVVVrrrr VVVV1111 CCCC RRRR OOOOUUUUTTTT LLLL RRRRRR222222 RRRROOOOUUUUTTTT FFFFBBBB DDDD CCCCOOOOUUUUTTTT RRRRRR111111 38/49

PM6680 Device description The T node voltage is the sum of the output voltage and the triangular waveform generated by the virtual ESR network. In fact the virtual ESR network behaves like a further equivalent ESR R . ESR A good trade-off is to design the network in order to achieve an R given by: ESR Equation 28 V R = RIPPLE −R ESR out ∆I L where ∆I is the inductor current ripple and V is the overall ripple of the T node L RIPPLE voltage. It should be chosen higher than approximately 30 mV. The new closed loop gain depends on C . In order to ensure stability it must be verified INT that: Equation 29 g Vr C > m × INT 2π×f V Z OUT Where: Equation 30 1 f = Z 2π×C ×R out TOT where R is the sum of the ESR of the output capacitor Rout and the equivalent ESR TOT given by the virtual ESR network R . ESR Moreover C must meet the following condition: INT Equation 31 k f >k×f = sw Z 2π×C ×R out TOT Where k is a free design parameter greater than 3 and determines the minimum integrator capacitor value C : INT Equation 32 g Vr C > m × INT ⎛f ⎞ V 2π×⎜ sw −f ⎟ OUT ⎜ Z⎟ ⎝ k ⎠ C must be selected as shown: Equation 33 C > 5×C INT 39/49

Device description PM6680 R must be chosen in order to have enough ripple voltage on integrator input: Equation 34 L R= R ×C ESR R1 can be selected as follows: Equation 35 ⎛ 1 ⎞ R×⎜ ⎟ ⎜ ⎟ R1= ⎝C×π×fZ ⎠ 1 R− C×π×f Z Example: OUT1 = 1.5 V, f = 290 kHz, L = 2.5 uH, C = 330 uF with R ≈12 mΩ. SW out out We design R = 12mW. We choose C = 1nF by equations 30, 33 and C = 47 pF, ESR INT filt R = 1 kΩ by eq.27, 28. C = 5.6 nF by Eq.34. Then R = 36 kΩ (eq.35) and R1 = 3 kΩ INT (eq.36). 7.13.7 Other parts design ● VIN filter A VIN pin low pass filter is suggested to reduce switching noise. The low pass filter is shown in the next figure: Figure 38. VIN pin filter RR VVIINN Input voltage CC 110000ppFF Typical components values are: R = 3.9 Ω and C = 4.7 uF. ● VCC filter A VCC low pass filter helps to reject switching commutations noise: 40/49

PM6680 Device description Figure 39. Inductor current waveforms LLDDOO55 RR VVCCCC CC Typical components values are: R=47 Ω and C = 1 uF. ● VREF capacitor A 10 nF to 100 nF ceramic capacitor on VREF pin must be added to ensure noise rejection. ● LDO5 output capacitors Bypass the output of each linear regulator with 1 uF ceramic capacitor closer to the LDO pin and a 4.7 uF tantalum capacitor (ESR = 2 Ω). In most applicative conditions a 4.7 uF ceramic output capacitor can be enough to ensure stability. ● Bootstrap circuit The external bootstrap circuit is represented in the next figure: Figure 40. Bootstrap circuit DD RRBBOOOOTT LLDDOO55 BBOOOOTT CCBBOOOOTT LL PPHHAASSEE The bootstrap circuit capacitor value C must provide the total gate charge to the high BOOT side MOSFET during turn on phase. A typical value is 100nF. The bootstrap diode D must charge the capacitor during the off time phases. The maximum rated voltage must be higher than V . INmax A resistor R on the BOOT pin could be added in order to reduce noise when the phase BOOT node rises up, working like a gate resistor for the turn on phase of the high side MOSFET. 41/49

Device description PM6680 7.13.8 Design example The following design example considers an input voltage from 7 V to 16 V. The two switching outputs are OUT1=1.5 V and OUT2=1.05 V and must deliver a maximum current of 5 A. The selected switching frequencies are about 290 kHz for OUT1 section and about 425 kHz for OUT2 section (see Table7 on page30). 1. Inductor selection OUT1: I = 5 A, 35 % ripple current. LOAD Equation 36 1.5V⋅(16V−1.5V) L = ≈ 2.5µH 290KHz⋅16V⋅0.35⋅5 We choose standard value L = 2.5 uH. ∆I = 1.8 A @V =12 V L(max) IN I = 5.03 A LRMS I = 5 A + 0.9 A = 5.9 A PEAK OUT2: I = 5 A, 30 % ripple current. LOAD Equation 37 1.05V⋅(16V−1.05V) L = ≈1.6µH 425KHz⋅16V⋅0.3⋅5 ∆I = 1.6 A @V = 12 V. L(max) IN I = 5.02 A LRMS I = 5 A + 0.8 A = 5.8 A PEAK 2. Output capacitor selection We would like to have an output ripple smaller than 25 mV. OUT1: POSCAP 6TPB330M OUT2: POSCAP 6TPB330M 3. Power MOSFETS OUT1: High side: STS12NH3LL Low side: STS12NH3LL OUT2:High side: STS12NH3LL Low side: STS12NH3LL 4. Current limit OUT1: Equation 38 ∆I (min) I (min)=I (max)− L =4.12A Lvalley LOAD 2 42/49

PM6680 Device description Equation 39 4.12A R ≡ ⋅16.25mΩ≈670Ω CSENSE 100µA (Let's assume the maximum temperature Tmax = 75 °C in RDSon calculation) OUT2: Equation 40 ∆I (min) I (min)=I (max)− L = 4.2A Lvalley LOAD 2 Equation 41 4.2A R ≡ ⋅16.25mΩ≈680Ω CSENSE 100µA (Let's assume Tmax = 75 °C in R calculation) DSon 5. Input capacitor Maximum input capacitor RMS current is about 2.8 A. Then I > 2.8 A. CinRMS We put three 10 uF ceramic capacitors with Irms = 1.5 A. 6. Synchronous rectifier OUT1: Shottky diode STPS1L30M OUT2: Shottky diode STPS1L30M 7. Integrator loop (Refer to Figure37) OUT1: The ripple is smaller than 40mV, then the virtual ESR network is required. C = 1 nF; C = 47 pF; R =1 kΩ INT filt INT C = 5.6 nF; R= 36 kΩ; R1 = 3 kΩ OUT2: The ripple is smaller than 40 mV, then the virtual ESR network is required. C = 1 nF; C = 110pF; R = 1 kΩ INT filt INT C = 5.6 nF; R = 22 kΩ; R1 = 3.3 kΩ 8. Output feedback divider (Refer to Figure30 on page24) OUT1: R1 = 10 kΩ; R2 = 6.8 kΩ OUT2: R1 = 11 kΩ; R2 = 1.8 kΩ 9. Layout guidelines The layout is very important in terms of efficiency, stability and noise of the system. It is possible to refer to the PM6680 demoboard for a complete layout example. For good PC board layout follows these guidelines: ● Place on the top side all the power components (inductors, input and output capacitors, MOSFETs and diodes). Refer them to a power ground plan, PGND. If possible, reserve a layer to PGND plan. The PGND plan is the same for both the switching sections. ● AC current paths layout is very critical (see Figure41 on page44). The first priority is to minimize their length. Trace the LS MOSFET connection to PGND plan as short as 43/49

Device description PM6680 possible. Place the synchronous diode D near the LS MOSFET. Connect the LS MOSFET drain to the switching node with a short trace. ● Place input capacitors near HS MOSFET drain. It is recommended to use the same input voltage plan for both the switching sections, in order to put together all input capacitors. ● Place all the sensitive analog signals (feedbacks, voltage reference, current sense paths) on the bottom side of the board or in an inner layer. Isolate them from the power top side with a signal ground layer, SGND. Connect the SGND and PGND plans only in one point (a multiple vias connection is preferable to a 0 ohm resistor connection) near the PGND device pin. Place the device on the top or on the bottom size and connect the exposed pad and the SGND pins to the SGND plan (see Figure41). Figure 41. Current paths, ground connection and driver traces layout ● As general rule, make the high side and low side drivers traces wide and short. The high side driver is powered by the bootstrap circuit. It's very important to place capacitor CBOOT and diode DBOOT as near as possible to the HGATE pin (for example on the layer opposite to the device). Route HGATE and PHASE traces as near as possible in order to minimize the area between them. The Low side gate driver is powered by the 5V linear regulator output. Placing PGND and LGATE pins near the low side MOSFETs reduces the length of the traces and the crosstalk noise between the two sections. ● The linear regulator output LDO5 is referred to SGND as long as the reference voltage Vref. Place their output filtering capacitors as near as possible to the device. ● Place input filtering capacitors near VCC and VIN pins. ● It would be better if the feedback networks connected to COMP, FB and OUT pins are "referred" to S in the same point as reference voltage V . To avoid capacitive GND ref 44/49

PM6680 Device description coupling place these traces as far as possible from the gate drivers and phase (switching) paths. ● Place the current sense traces on the bottom side. If low side MOSFET R sensing DSon is enabled, use a dedicated connection between the switching node and the current limit resistor R . CSENSE 45/49

Package mechanical data PM6680 8 Package mechanical data In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a Lead-free second level interconnect. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com. Table 17. VFQFPN 5x5x1.0 32L Pitch 0.50 Databook (mm) Dim. Min Typ Max A 0.8 0.9 1 A1 0 0.02 0.05 A3 0.2 b 0.18 0.25 0.3 D 4.85 5 5.15 D2 See exposed pad variations (2) E 4.85 5 5.15 E2 See exposed pad variations (2) e 0.5 L 0.3 0.4 0.5 ddd 0.05 T able 18. Exposed pad variations (1)(2)D2 E2 Min Typ Max Min Typ Max 2.90 3.10 3.20 2.90 3.10 3.20 1. VFQFPN stands for Thermally Enhanced Very thin Fine pitch Quad Flat Package No lead. Very thin: A = 1.00mm Max. 2. Dimensions D2 & E2 are not in accordance with JEDEC. 46/49

PM6680 Package mechanical data Figure 42. Package dimensions 47/49

Revision history PM6680 9 Revision history Table 19. Document revision history Date Revision Changes 17-Mar-2006 1 Initial release 10-May-2006 2 Few updates 29-Jun-2006 3 Mechanical data updated 28-Jul-2006 4 Application schematic updated Figure27 on page16 Changes electrical characteristics, added COMP value skip mode, 25-Oct-2006 5 Order code table updated 28-Aug-2007 6 Updated: Current sensing option and Absolute Maximum Ratings Updated: Table1 on page1, Table3 on page7, 21-Jan-2008 7 Section4 on page 12 48/49

PM6680 Please Read Carefully: Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice. All ST products are sold pursuant to ST’s terms and conditions of sale. Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein. UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK. Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST. ST and the ST logo are trademarks or registered trademarks of ST in various countries. Information in this document supersedes and replaces all information previously supplied. The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners. © 2008 STMicroelectronics - All rights reserved STMicroelectronics group of companies Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America www.st.com 49/49

Mouser Electronics Authorized Distributor Click to View Pricing, Inventory, Delivery & Lifecycle Information: S TMicroelectronics: PM6680TR PM6680

Datasheet下载

Datasheet下载.jpg)