ICGOO在线商城 > 射频/IF 和 RFID > RF 开关 > PE42420LGBB-Z

- 型号: PE42420LGBB-Z

- 制造商: Peregrine

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

PE42420LGBB-Z产品简介:

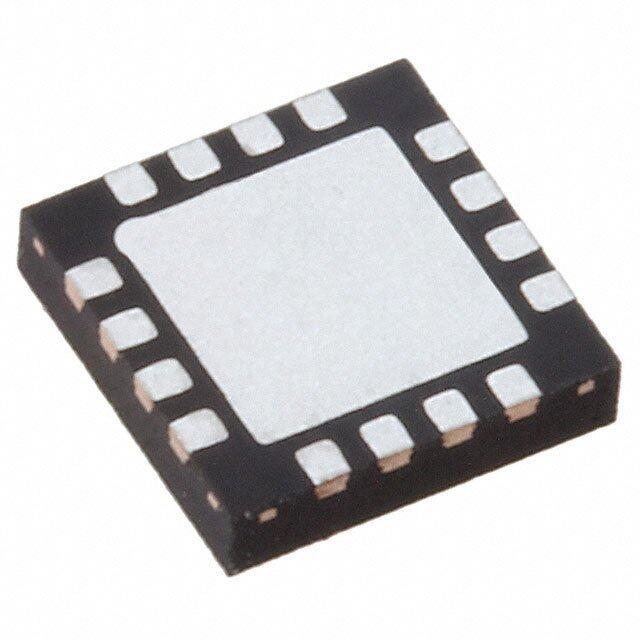

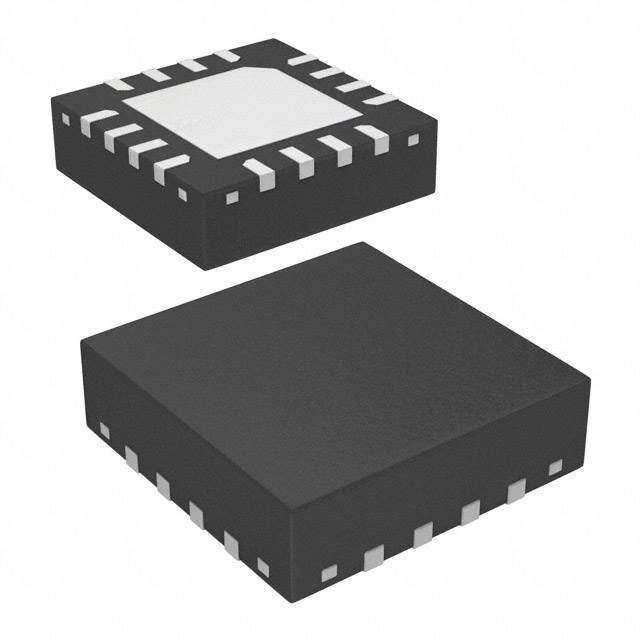

ICGOO电子元器件商城为您提供PE42420LGBB-Z由Peregrine设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 PE42420LGBB-Z价格参考。PeregrinePE42420LGBB-Z封装/规格:RF 开关, 射频开关 IC 通用 SPDT 6GHz 50 欧姆 20-LGA(4x4)。您可以下载PE42420LGBB-Z参考资料、Datasheet数据手册功能说明书,资料中有PE42420LGBB-Z 详细功能的应用电路图电压和使用方法及教程。

PE42420LGBB-Z是由pSemi公司生产的RF(射频)开关,主要应用于无线通信和射频系统中。以下是其应用场景的详细说明: 1. 移动通信设备 PE42420LGBB-Z广泛应用于智能手机、平板电脑和其他移动设备中的射频前端模块(FEM)。它能够在不同的射频频段之间快速切换,确保设备在不同网络制式(如4G LTE、5G NR等)下保持高效的信号传输。此外,该开关还支持多输入多输出(MIMO)技术,有助于提升数据传输速率和信号质量。 2. 基站与基础设施 在无线基站和通信基础设施中,PE42420LGBB-Z用于实现天线端口之间的快速切换,以适应不同的工作频段和信道配置。它能够有效减少信号干扰,提高基站的覆盖范围和通信效率。特别是在毫米波频段的应用中,该开关的低插入损耗和高隔离度特性尤为重要,有助于提升系统的整体性能。 3. 物联网(IoT)设备 随着物联网设备的普及,PE42420LGBB-Z也被广泛应用于各种智能终端中,如智能家居设备、可穿戴设备和工业传感器等。它可以在不同的无线协议(如Wi-Fi、Bluetooth、Zigbee等)之间进行快速切换,确保设备在不同环境下都能稳定连接并高效传输数据。 4. 卫星通信 在卫星通信系统中,PE42420LGBB-Z用于实现地面站与卫星之间的信号切换,确保通信链路的可靠性和稳定性。其低功耗和高可靠性使得它在长时间运行的卫星通信应用中表现出色,尤其是在需要频繁切换频率或信道的情况下。 5. 测试与测量设备 在射频测试仪器和测量设备中,PE42420LGBB-Z可以作为信号路径切换的关键组件。它能够精确控制信号的传输路径,确保测试结果的准确性和一致性。其快速响应时间和稳定的电气性能使其成为实验室和生产线上不可或缺的一部分。 总结 PE42420LGBB-Z凭借其优异的射频性能、低插入损耗、高隔离度以及快速切换能力,适用于多种射频应用场景,包括移动通信、基站基础设施、物联网设备、卫星通信和测试测量等领域。它的高可靠性和低功耗特性使其成为现代无线通信系统中的理想选择。

| 参数 | 数值 |

| 产品目录 | |

| 描述 | IC RF SWITCH SPDT 20LGA |

| 产品分类 | |

| IIP3 | 65dBm (标准) |

| 品牌 | Peregrine Semiconductor |

| 数据手册 | |

| 产品图片 |

|

| P1dB | 33dBm (最小) IP1dB |

| 产品型号 | PE42420LGBB-Z |

| RF类型 | 通用 |

| rohs | 无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | UltraCMOS®,HaRP™ |

| 供应商器件封装 | 20-LGA (20x20) |

| 其它名称 | 1046-1069-6 |

| 包装 | Digi-Reel® |

| 封装/外壳 | 20-TFQFN 裸露焊盘 |

| 工作温度 | -40°C ~ 85°C |

| 拓扑 | 吸收性 |

| 插损@频率 | 1.6dB @ 6GHz |

| 标准包装 | 1 |

| 特性 | - |

| 电压-电源 | 2.7 V ~ 5.5 V |

| 电路 | SPDT |

| 阻抗 | 50 欧姆 |

| 隔离@频率 | 50dB @ 6GHz (标准) |

| 频率 -上 | 6GHz |

| 频率 -下 | 100MHz |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

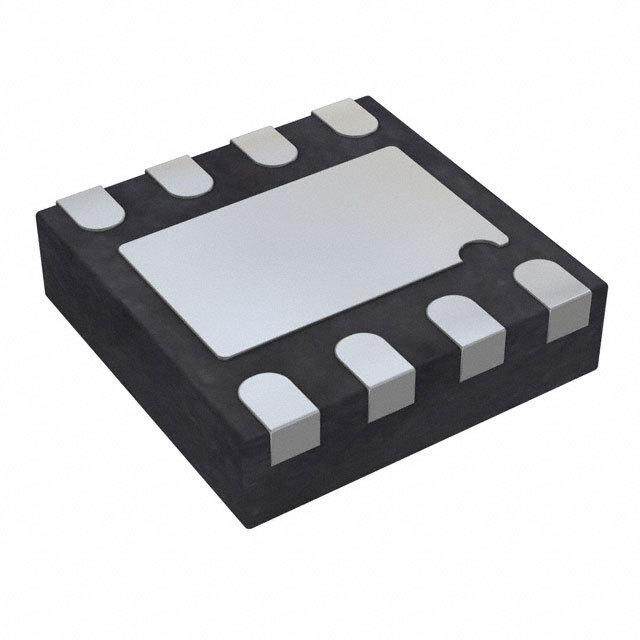

Product Specification PE42420 UltraCMOS® SPDT RF Switch 100–6000 MHz Product Description The PE42420 is a HaRP™ technology-enhanced Features absorptive SPDT RF switch designed for use in 3G/4G HaRP™ technology enhanced wireless infrastructure and other high performance RF No gate and phase lag applications. It is ideal for transmit path switching, RF and IF signal routing, AGC loops, and filter bank switching No drift in insertion loss and phase applications. High linearity IIP3 of 65 dBm This general purpose switch is comprised of two symmetric High isolation RF ports and has exceptional port to port isolation up to 6 GHz. An integrated CMOS decoder facilitates a two-pin 69 dB @ 1 GHz low voltage CMOS control interface. In addition, no 62 dB @ 3 GHz external blocking capacitors are required if 0 VDC is 50 dB @ 6 GHz present on the RF ports. Supports +1.8V control logic The PE42420 is manufactured on Peregrine’s UltraCMOS® +105 °C operating temperature process, a patented variation of silicon-on-insulator (SOI) High ESD tolerance technology on a sapphire substrate. 4 kV HBM on RFC Peregrine’s HaRP technology enhancements deliver high 2 kV HBM on all other pins linearity and excellent harmonics performance. It is an innovative feature of the UltraCMOS process, offering the performance of GaAs with the economy and integration of conventional CMOS. Figure 1. Functional Diagram Figure 2. Package Type 20-lead 4 × 4 mm LGA DOC-02177 Document No. DOC-14514-5 │ www.psemi.com ©2010-2016 Peregrine Semiconductor Corp. All rights reserved. Page 1 of 12

PE42420 Product Specification Table 1. Electrical Specifications @ +25 °C, V = 3.0V (Z = Z = 50Ω) DD S L Parameter Path Condition Min Typ Max Unit Operating frequency 100 6000 MHz 100–1000 MHz 0.95 1.15 dB 1000–2000 MHz 0.95 1.15 dB 2000–3000 MHz1 1.00 1.20 dB Insertion loss RFC–RFX 3000–4000 MHz1 1.15 1.35 dB 4000–5000 MHz1 1.25 1.55 dB 5000–6000 MHz1 1.60 1.90 dB 100–1000 MHz 67 69 dB 1000–2000 MHz 63 64 dB 2000–3000 MHz 59 62 dB Isolation RFX–RFX 3000–4000 MHz 60 64 dB 4000–5000 MHz 54 60 dB 5000–6000 MHz 44 50 dB 100–1000 MHz 69 71 dB 1000–2000 MHz 65 67 dB 2000–3000 MHz 63 68 dB Isolation RFC–RFX 3000–4000 MHz 62 67 dB 4000–5000 MHz 52 57 dB 5000–6000 MHz 44 48 dB 100–4000 MHz 20 dB Return loss (all ports) 4000–5000 MHz1 15 dB 5000–6000 MHz1 13 dB Input 1dB compression point2 RFC–RFX 100–6000 MHz 33 dBm Input IP2 RFC–RFX 100–6000 MHz 110 dBm Input IP3 RFC–RFX 100–6000 MHz 60 65 dBm Switching time 50% CTRL to 90% or 10% RF 300 400 ns Notes: 1. Insertion loss and return loss can be improved by external matching. 2. The input 1dB compression point is a linearity figure of merit. Refer to Table 3 for the maximum operating power PIN (50Ω). ©2010-2016 Peregrine Semiconductor Corp. All rights reserved. Document No. DOC-14514-5 │ UltraCMOS® RFIC Solutions Page 2 of 12

PE42420 Product Specification Table 1A. Electrical Specifications @ +105 °C, V = 2.3V to 5.5V (Z = Z = 50Ω) DD S L Parameter Path Condition Min Typ Max Unit Operating frequency 100 6000 MHz 100–1000 MHz 1.05 1.25 dB 1000–2000 MHz 1.10 1.35 dB 2000–3000 MHz1 1.25 1.45 dB Insertion loss RFC–RFX 3000–4000 MHz1 1.35 1.75 dB 4000–5000 MHz1 1.50 2.00 dB 5000–6000 MHz1 1.60 2.00 dB 100–1000 MHz 66 68 dB 1000–2000 MHz 63 64 dB 2000–3000 MHz 59 62 dB Isolation RFX–RFX 3000–4000 MHz 60 64 dB 4000–5000 MHz 54 60 dB 5000–6000 MHz 44 50 dB 100–1000 MHz 68 70 dB 1000–2000 MHz 65 67 dB 2000–3000 MHz 62 67 dB Isolation RFC–RFX 3000–4000 MHz 62 67 dB 4000–5000 MHz 51 55 dB 5000–6000 MHz 44 48 dB 100–4000 MHz 19 dB Return loss (all ports) 4000–5000 MHz1 15 dB 5000–6000 MHz1 13 dB Input 1dB compression point2 RFC–RFX 100–6000 MHz 33 dBm Input IP2 RFC–RFX 100–6000 MHz 110 dBm Input IP3 RFC–RFX 100–6000 MHz 60 65 dBm Switching time 50% CTRL to 90% or 10% RF 300 400 ns Notes: 1. Insertion loss and return loss can be improved by external matching. 2. The input 1dB compression point is a linearity figure of merit. Refer to Table 3 for the maximum operating power PIN (50Ω). Document No. DOC-14514-5 │ www.psemi.com ©2010-2016 Peregrine Semiconductor Corp. All rights reserved. Page 3 of 12

PE42420 Product Specification Figure 3. Pin Configuration (Top View) Table 3. Operating Ranges Parameter Symbol Min Typ Max Unit Supply voltage V 2.7 5.5 V DD Supply current I 120 200 µA V = 2.7–5.5V DD DD Digital input high V 1.17 3.6 V (CTRL1, CTRL2) IH Digital input low V –0.3 0.6 V (CTRL1, CTRL2) IL Digital input current I 9 12 µA CTRL Maximum operating power P 30 dBm (RFC–RFX)* IN Maximum power into P 20 dBm termination (RFX)* MAX Operating temperature T –40 +105 °C range OP Table 2. Pin Descriptions Note: * 100% duty cycle, all bands, 50Ω. Pin # Pin Name Description Table 4. Absolute Maximum Ratings 1, 2, 4–7, 9, 10–12, 14, GND Ground Parameter/Condition Symbol Min Max Unit 15, 18, 19 Supply voltage V –0.3 5.5 V DD 3 RF1* RF port Digital input voltage V –0.3 3.6 V 8 RFC* RF common (CTRL1, CTRL2) CTRL 13 RF2* RF port Operating power P 30 dBm (RFC–RFX)1 IN 16 CTRL2 Digital control logic input 2 Power into termination (RFX)1 P 20 dBm 17 CTRL1 Digital control logic input 1 MAX Storage temperature range T –65 +150 °C 20 V Supply voltage ST DD Maximum die junction temperature T +125 °C Pad GND Exposed pad: ground for proper operation JMAX ESD voltage HBM2 Note: * RF pins 3, 8 and 13 must be at 0 VDC. The RF pins do not require RFC V 4000 V DC blocking capacitors for proper operation if the 0 VDC requirement ESD All other pins 2000 V is met. ESD voltage MM3, all pins V 100 V ESD Notes: 1. 100% duty cycle, all bands, 50Ω. 2. Human Body Model (MIL-STD 883 Method 3015). 3. Machine Model (JEDEC JESD22-A115). Exceeding absolute maximum ratings may cause permanent damage. Operation should be restricted to the limits in the Operating Ranges table. Operation between operating range maximum and absolute maximum for extended periods may reduce reliability. ©2010-2016 Peregrine Semiconductor Corp. All rights reserved. Document No. DOC-14514-5 │ UltraCMOS® RFIC Solutions Page 4 of 12

PE42420 Product Specification Electrostatic Discharge (ESD) Precautions Table 5. Truth Table When handling this UltraCMOS device, observe CTRL1 CTRL2 RFC–RF1 RFC–RF2 the same precautions that you would use with Low Low OFF OFF other ESD-sensitive devices. Although this device Low High OFF ON contains circuitry to protect it from damage due to High Low ON OFF ESD, precautions should be taken to avoid exceeding the specified rating. High High N/A* N/A* Note: * CTRL1 = High and CTRL2 = High are not supported Latch-Up Immunity Moisture Sensitivity Level Unlike conventional CMOS devices, UltraCMOS The Moisture Sensitivity Level rating for the devices are immune to latch-up. PE42420 in the 20-lead 4 × 4 mm LGA package is Switching Frequency MSL3. The PE42420 has a maximum 25 kHz switching Spurious Performance frequency. The typical spurious performance of the PE42420 Switching frequency describes the time duration is –155 dBm. between switching events. Switching time is the time duration between the point the control signal reaches 50% of the final value and the point the output signal reaches within 10% or 90% of its target value. Switching time is provided in Table 1. Document No. DOC-14514-5 │ www.psemi.com ©2010-2016 Peregrine Semiconductor Corp. All rights reserved. Page 5 of 12

PE42420 Product Specification Typical Performance Data @ +25 °C and V = 3.0V, unless otherwise specified DD Figure 4. Insertion Loss (RFC–RFX) Figure 5. Insertion Loss vs Temp (RFX–RFC) Figure 6. Insertion Loss vs V (RFX–RFC) DD Figure 7. RFC Port Return Loss vs Temp Figure 8. RFC Port Return Loss vs V DD (RF1 Active) (RF1 Active) ©2010-2016 Peregrine Semiconductor Corp. All rights reserved. Document No. DOC-14514-5 │ UltraCMOS® RFIC Solutions Page 6 of 12

PE42420 Product Specification TTyyppiiccaall PPeerrffoorrmmaannccee DDaattaa@ +25 °C and V = 3.0V, unless otherwise specified (continued) DD Figure 9. RFC Port Return Loss vs Temp Figure 10. RFC Port Return Loss vs V DD (RF2 Active) (RF2 Active) Figure 11. Active Port Return Loss vs Temp Figure 12. Active Port Return Loss vs V DD (RF1 Active) (RF1 Active) Figure 13. Terminated Port Return Loss vs Temp Figure 14. Terminated Port Return Loss vs V DD (RF1 Active) (RF1 Active) Document No. DOC-14514-5 │ www.psemi.com ©2010-2016 Peregrine Semiconductor Corp. All rights reserved. Page 7 of 12

PE42420 Product Specification Typical Performance Data@ +25 °C and V = 3.0V, unless otherwise specified (continued) DD Figure 15. Isolation vs Temp (RFX–RFX) Figure 16. Isolation vs V (RFX–RFX) DD Figure 17. Isolation vs Temp (RFC–RFX) Figure 18. Isolation vs V (RFC–RFX) DD ©2010-2016 Peregrine Semiconductor Corp. All rights reserved. Document No. DOC-14514-5 │ UltraCMOS® RFIC Solutions Page 8 of 12

PE42420 Product Specification Evaluation Kit Figure 19. Evaluation Board Layout The SPDT switch evaluation board was designed to ease customer evaluation of Peregrine’s PE42420. The RF common port is connected through a 50Ω transmission line via the top SMA connector, J2. RF1 and RF2 ports are connected through 50Ω transmission lines via SMA connectors J1 and J3, respectively. A 50Ω through transmission line is available via SMA connectors J4 and J5, which can be used to calculate the loss of the PCB. J6 provides DC and digital inputs to the device. The board is constructed of a four metal layer material with a total thickness of 36 mils. To achieve high isolation, the 50Ω transmission lines are designed in layer 2 using a stripline waveguide design. The board stack up for 50Ω transmission lines has 10 mil thickness of Rogers 4350 between layer 1 and layer 2, and 10 mil thickness of Rogers 4350 between layer 2 and layer 3. For the true performance of the PE42420 to be realized, the PCB should be designed in such a way that RF transmission lines and sensitive DC I/O traces are heavily isolated from one another. PRT-11505 Document No. DOC-14514-5 │ www.psemi.com ©2010-2016 Peregrine Semiconductor Corp. All rights reserved. Page 9 of 12

PE42420 Product Specification Figure 20. Evaluation Board Schematic J6 HEADER 7X2 C1 1 1 2 2 C2 3 3 4 4 5 5 6 6 7 7 8 8 VDD 9 9 10 10 2C24pF 0OHM 0OHM 1131 1131 1124 1124 C1 R1 R2 R3 R4 0.1 uF 1M 1M 20 19 18 17 16 C2 C3 DD ND ND C1 C2 22pF 22pF V G G 1 GND GND 15 SJ1MASM 50 OHM T-Line 2 GND U1 GND 14 50 OHM T-Line JS3MASM 1 3 RF1 PE42420 RF2 13 1 2 4 GND GND 12 2 5 GND GND 11 GND GND RFC GND GND 6 7 8 9 10 J2 50 OHM T-Line SMASM 1 J4 50 OHM T-Line J5 SMASM SMASM 2 1 1 2 2 DOC-14527 ©2010-2016 Peregrine Semiconductor Corp. All rights reserved. Document No. DOC-14514-5 │ UltraCMOS® RFIC Solutions Page 10 of 12

PE42420 Product Specification Figure 21. Package Drawing 20-lead 4 × 4 mm LGA 0.10 C A 4.00 0.31 (2X) 2.00±0.05 0.40±0.05 (x20) 0.60 0.50 B (x20) (x20) (x16) 11 15 0.50 (x16) 10 16 4.00 2.00±0.05 2.05 4.20 20 6 0.26±0.05 (x20) 0.10 C 5 1 (2X) 0.10 2.00 Detail A 2.05 REF 4.20 PIN #1 CORNER TOP VIEW BOTTOM VIEW RECOMMENDED LAND PATTERN 0.70±0.04 DOC-01890 0.10 C 0.94±0.07 0.08 C SEATING PLANE SIDE VIEW C 0.16 0.28 0.33 1 0.34 Figure 22. Top Marking Specifications 42420 YYWW = Pin 1 designator ZZZZZZ YYWW = Last 2 digits of assembly year, starting from 2010 ZZZZZ = Assembly lot code (max 6 characters) DOC-65737 Document No. DOC-14514-5 │ www.psemi.com ©2010-2016 Peregrine Semiconductor Corp. All rights reserved. Page 11 of 12

PE42420 Product Specification Figure 23. Tape and Reel Drawing Tape Feed Direction Notes: 1. 10 sprocket hole pitch cumulative tolerance ±0.02. Ao = 4.35 mm 2. Camber not to exceed 1 mm in 100 mm. Bo = 4.35 mm 3. Material: PS + C. Ko = 1.1 mm 4. Ao and Bo measured as indicated. 5. Ko measured from a plane on the inside bottom of the pocket to the top surface of the carrier. 6. Pocket position relative to sprocket hole measured as true position of pocket, not pocket hole. Table 6. Ordering Information Order Code Description Package Shipping Method PE42420C-Z PE42420 SPDT RF switch Green 20-lead 4 × 4 mm LGA 3000 units / T&R EK42420C-02 PE42420 Evaluation kit Evaluation kit 1 / Box Sales Contact and Information For sales and contact information please visit www.psemi.com. Advance Information: The product is in a formative or design stage. The datasheet contains design target No patent rights or licenses to any circuits described in this datasheet are implied or granted to any third party. specifications for product development. Specifications and features may change in any manner without notice. Peregrine’s products are not designed or intended for use in devices or systems intended for surgical implant, Preliminary Specification: The datasheet contains preliminary data. Additional data may be added at a later or in other applications intended to support or sustain life, or in any application in which the failure of the date. Peregrine reserves the right to change specifications at any time without notice in order to supply the best Peregrine product could create a situation in which personal injury or death might occur. Peregrine assumes no possible product. Product Specification: The datasheet contains final data. In the event Peregrine decides to liability for damages, including consequential or incidental damages, arising out of the use of its products in change the specifications, Peregrine will notify customers of the intended changes by issuing a CNF (Customer such applications. Notification Form). The Peregrine name, logo, UltraCMOS and UTSi are registered trademarks and HaRP, MultiSwitch and DuNE The information in this datasheet is believed to be reliable. However, Peregrine assumes no liability for the use are trademarks of Peregrine Semiconductor Cor p. Peregrine products are protected under one or more of the of this information. Use shall be entirely at the user’s own risk. following U.S. Patents: http://patents.psemi.com. ©2010-2016 Peregrine Semiconductor Corp. All rights reserved. Document No. DOC-14514-5 │ UltraCMOS® RFIC Solutions Page 12 of 12

Datasheet下载

Datasheet下载