ICGOO在线商城 > 集成电路(IC) > 线性 - 放大器 - 仪表,运算放大器,缓冲器放大器 > OPA890IDBVT

- 型号: OPA890IDBVT

- 制造商: Texas Instruments

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

OPA890IDBVT产品简介:

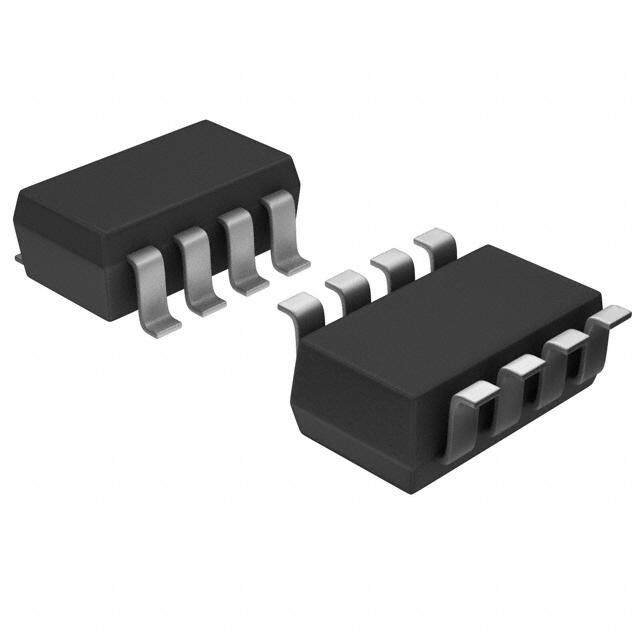

ICGOO电子元器件商城为您提供OPA890IDBVT由Texas Instruments设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 OPA890IDBVT价格参考¥7.53-¥17.02。Texas InstrumentsOPA890IDBVT封装/规格:线性 - 放大器 - 仪表,运算放大器,缓冲器放大器, 电压反馈 放大器 1 电路 SOT-23-6。您可以下载OPA890IDBVT参考资料、Datasheet数据手册功能说明书,资料中有OPA890IDBVT 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| -3db带宽 | 260MHz |

| 产品目录 | 集成电路 (IC)半导体 |

| 描述 | IC OPAMP VFB 130MHZ SOT23-6高速运算放大器 Low Pwr Wideband Vltg Feedback |

| 产品分类 | Linear - Amplifiers - Instrumentation, OP Amps, Buffer Amps集成电路 - IC |

| 品牌 | Texas Instruments |

| 产品手册 | http://www.ti.com/litv/sbos369b |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 放大器 IC,高速运算放大器,Texas Instruments OPA890IDBVT- |

| 数据手册 | |

| 产品型号 | OPA890IDBVT |

| 产品 | Voltage Feedback Amplifier |

| 产品目录页面 | |

| 产品种类 | |

| 供应商器件封装 | SOT-23-6 |

| 共模抑制比—最小值 | 59 dB |

| 其它名称 | 296-21960-1 |

| 包装 | 剪切带 (CT) |

| 压摆率 | 500 V/µs |

| 商标 | Texas Instruments |

| 增益带宽生成 | 130 MHz |

| 增益带宽积 | 130MHz |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装 | Reel |

| 封装/外壳 | SOT-23-6 |

| 封装/箱体 | SOT-23-6 |

| 工作温度 | -40°C ~ 85°C |

| 工作电源电压 | 3 V to 12 V |

| 工厂包装数量 | 250 |

| 拓扑结构 | Voltage Feedback |

| 放大器类型 | 电压反馈 |

| 最大功率耗散 | 79 mW |

| 最大工作温度 | + 85 C |

| 最小工作温度 | - 40 C |

| 标准包装 | 1 |

| 电压-电源,单/双 (±) | 3 V ~ 12 V, ±1.5 V ~ 6 V |

| 电压-输入失调 | 1mV |

| 电压增益dB | 60 dB |

| 电流-电源 | 1.1mA |

| 电流-输入偏置 | 100nA |

| 电流-输出/通道 | 40mA |

| 电源电压-最大 | 12 V |

| 电源电压-最小 | 3 V |

| 电源电流 | 1.1 mA |

| 电路数 | 1 |

| 稳定时间 | 16 ns |

| 系列 | OPA890 |

| 设计资源 | http://www.digikey.com/product-highlights/cn/zh/texas-instruments-webench-design-center/3176 |

| 转换速度 | 500 V/us |

| 输入补偿电压 | 5 mV |

| 输出电流 | 40 mA |

| 输出类型 | - |

| 通道数量 | 1 Channel |

| 配用 | /product-detail/zh/DEM-OPA-SOT-1A/296-20840-ND/1216445 |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

OPA890 www.ti.com SBOS369B–MAY2007–REVISEDDECEMBER2009 Low-Power, Wideband, Voltage-Feedback OPERATIONAL AMPLIFIER with Disable CheckforSamples:OPA890 FEATURES 1 DESCRIPTION • FLEXIBLESUPPLYRANGE: 2 +3Vto+12VSingleSupply The OPA890 represents a major step forward in ±1.5Vto ±6VDualSupplies unity-gain stable, voltage-feedback op amps. A new internal architecture provides slew rate and full-power • UNITY-GAINSTABLE bandwidth previously found only in wideband, • WIDEBAND+5VOPERATION:115MHz current-feedback op amps. These capabilities provide (G=+2V/V) exceptional full power bandwidth. Using a single +5V • OUTPUTVOLTAGESWING:±4V supply, the OPA890 can deliver a 1V to 4V output swing with over 35mA drive current and 220MHz • HIGHSLEWRATE:500V/μs bandwidth. This combination of features makes the • LOWQUIESCENTCURRENT:1.1mA OPA890 an ideal RGB line driver or single-supply • LOWDISABLECURRENT:30μA analog-to-digitalconverter(ADC)inputdriver. The low 1.1mA supply current of the OPA890 is APPLICATIONS precisely trimmed at +25°C. This trim, along with low • VIDEOLINEDRIVING temperature drift, ensures lower maximum supply • xDSLLINEDRIVERS/RECEIVERS current than competing products. System power may be reduced further using the optional disable control • HIGH-SPEEDIMAGINGCHANNELS pin. Leaving this disable pin open, or holding it HIGH, • ADCBUFFERS operates the OPA890 normally. If pulled LOW, the • PORTABLEINSTRUMENTS OPA890 supply current drops to less than 30μA while • TRANSIMPEDANCEAMPLIFIERS theoutputgoesintoahigh-impedancestate. • ACTIVEFILTERS RELATEDOPERATIONALAMPLIFIERPRODUCTS +5V DESCRIPTION SINGLES DUALS TRIPLES Low-PowerVoltage-Feedback — OPA2890 — withDisable V GND DB0 DD Voltage-FeedbackAmplifier OPA690 OPA2690 OPA3690 DB1 VREF -5V withDisable(1800V/μs) DB2 ½ Current-FeedbackAmplifier DB3 DAC7822 R1 withDisable(2100V/μs) OPA691 OPA2691 OPA3691 DB4 R DB5 FB 2.5pF +7.5V FixedGain OPA692 — OPA3692 DB6 I OUT1 DB7 I OUT2 DB8 OPA890 V OUT DB9 R 2 0V£V £5V DB10 R OUT 2_3 DB11 R 3 5.56kW 0.1mF -2.5V MultiplyingDACTransimpedanceAmplifier 1 Pleasebeawarethatanimportantnoticeconcerningavailability,standardwarranty,anduseincriticalapplicationsofTexas Instrumentssemiconductorproductsanddisclaimerstheretoappearsattheendofthisdatasheet. Alltrademarksarethepropertyoftheirrespectiveowners. 2 PRODUCTIONDATAinformationiscurrentasofpublicationdate. Copyright©2007–2009,TexasInstrumentsIncorporated Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarilyincludetestingofallparameters.

OPA890 SBOS369B–MAY2007–REVISEDDECEMBER2009 www.ti.com This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriateprecautions.Failuretoobserveproperhandlingandinstallationprocedurescancausedamage. ESDdamagecanrangefromsubtleperformancedegradationtocompletedevicefailure.Precisionintegratedcircuitsmaybemore susceptibletodamagebecauseverysmallparametricchangescouldcausethedevicenottomeetitspublishedspecifications. ORDERINGINFORMATION(1) SPECIFIED PACKAGE TEMPERATURE PACKAGE ORDERING TRANSPORT PRODUCT PACKAGE-LEAD DESIGNATOR RANGE MARKING NUMBER MEDIA,QUANTITY OPA890ID Rail,75 OPA890 SO-8 D –40°Cto+85°C OPA890 OPA890IDR TapeandReel,2500 OPA890IDBVT TapeandReel,250 OPA890 SOT23-6 DBV –40°Cto+85°C BRI OPA890IDBVR TapeandReel,3000 (1) ForthemostcurrentpackageandorderinginformationseethePackageOptionAddendumattheendofthisdocument,orseetheTI websiteatwww.ti.com. ABSOLUTE MAXIMUM RATINGS(1) Overoperatingfree-airtemperaturerange(unlessotherwisenoted). OPA890 UNIT PowerSupply ±6.5 V InternalPowerDissipation SeeThermalCharacteristics InputVoltageRange ±V V S StorageTemperatureRange –65to+125 °C MaximumJunctionTemperature(T) +150 °C J MaximumJunctionTemperature,ContinuousOperation,Long-TermReliability +140 °C HumanBodyModel(HBM) 2000 V ESDRating: ChargeDeviceModel(CDM) 1500 V MachineModel(MM) 200 V (1) Stressesabovetheseratingsmaycausepermanentdamage.Exposuretoabsolutemaximumconditionsforextendedperiodsmay degradedevicereliability.Thesearestressratingsonly,andfunctionaloperationofthedeviceattheseoranyotherconditionsbeyond thosespecifiedisnotimplied. PIN CONFIGURATIONS TOP VIEW SO TOP VIEW SOT23 Output 1 6 +V S -V 2 5 DIS S NC 1 8 DIS Noninverting Input 3 4 Inverting Input Inverting Input 2 7 +V S Noninverting Input 3 6 Output 6 5 4 -V 4 5 NC BRI S NC = No Connection 1 2 3 Pin Orientation/Package Marking 2 SubmitDocumentationFeedback Copyright©2007–2009,TexasInstrumentsIncorporated ProductFolderLink(s):OPA890

OPA890 www.ti.com SBOS369B–MAY2007–REVISEDDECEMBER2009 ELECTRICAL CHARACTERISTICS: V = ±5V S Boldfacelimitsaretestedat+25°C. AtR =750Ω,G=+2V/V,andR =100Ω,unlessotherwisenoted. F L OPA890ID,IDBV TYP MIN/MAXOVERTEMPERATURE 0°Cto –40°Cto MIN/ TEST PARAMETER CONDITIONS +25°C +25°C(2) +70°C(3) +85°C(3) UNITS MAX LEVEL(1) ACPERFORMANCE Small-SignalBandwidth G=+1V/V,VO=100mVPP,RF=0Ω 260 MHz typ C G=+2V/V,VO=100mVPP 115 75 65 60 MHz min B G=+10V/V,VO=100mVPP 13 9 8 7.5 MHz min B GainBandwidthProduct G>+20V/V 130 100 90 85 MHz min B Bandwidthfor0.1dBFlatness G=+2V/V,VO=100mVPP 20 MHz typ C PeakingataGainof+1V/V VO<100mVPP 1 dB typ C Large-SignalBandwidth G=+2V/V,VO=2VPP 170 MHz typ C SlewRate G=+2V/V,VO=2VStep 500 325 300 275 V/μs min B Rise-and-FallTime 0.2VStep 3.5 ns typ C SettlingTimeto0.02% G=+1V/V,VO=2VStep 16 ns typ C SettlingTimeto0.1% 10 ns typ C HarmonicDistortion G=+2V/V,f=1MHz,VO=2VPP 2nd-Harmonic RL=200Ω –88 –78 –76 –75 dBc max B RL ≥500Ω –102 –84 –82 –80 dBc max B 3rd-Harmonic RL=200Ω –89 –84 –81 –80 dBc max B RL ≥500Ω –94 –90 –87 –86 dBc max B InputVoltageNoise f>100kHz 8 9 10 11 nV/√Hz max B InputCurrentNoise f>100kHz 1 1.3 1.7 1.9 pA/√Hz max B DifferentialGain G=+2V/V,VO=1.4VPP,RL=150Ω 0.05 % typ C DifferentialPhase G=+2V/V,VO=1.4VPP,RL=150Ω 0.03 ° typ C DCPERFORMANCE(4) Open-LoopVoltageGain(AOL) VO=0V,RL=100Ω 62 57 56 54 dB min A InputOffsetVoltage VCM=0V ±1 ±5 ±5.7 ±6 mV max A AverageOffsetVoltageDrift VCM=0V ±15 ±15 μV/°C max B InputBiasCurrent VCM=0V ±0.1 ±1.6 ±1.8 ±2 μA max A AverageInputBiasCurrentDrift VCM=0V ±5 ±6 nA/°C max B InputOffsetCurrent VCM=0V ±70 ±350 ±450 ±500 nA max A AverageInputOffsetCurrentDrift VCM=0V ±2.5 ±2.5 nA/°C max B INPUT Common-ModeInputRange(CMIR)(5) ±3.9 ±3.7 ±3.6 ±3.5 V min A Common-ModeRejectionRatio(CMRR) VCM=0V,Input-Referred 67 61 58 57 dB min A InputImpedance Differential VCM=0V 190||0.6 kΩ||pF typ C Common-Mode VCM=0V 3.2||0.9 MΩ||pF typ C OUTPUT OutputVoltageSwing NoLoad ±4.0 ±3.9 ±3.8 ±3.7 V min A RL=100Ω ±3.5 ±3.1 ±3.05 ±2.9 V min A OutputCurrent,Sourcing,Sinking VO=0V ±40 ±35 ±33 ±30 mA min A PeakOutputCurrent OutputShortedtoGround ±75 mA typ C Closed-LoopOutputImpedance G=+2V/V,f=100kHz 0.04 Ω typ C (1) Testlevels:(A)100%testedat+25°C.Overtemperaturelimitssetbycharacterizationandsimulation.(B)Limitssetbycharacterization andsimulation.(C)Typicalvalueonlyforinformation. (2) Junctiontemperature=ambientfor+25°Ctestedspecifications. (3) Junctiontemperature=ambientatlowtemperaturelimit;junctiontemperature=ambient+2°Cathightemperaturelimitforover temperaturespecifications. (4) Currentisconsideredpositiveout-of-node.V istheinputcommon-modevoltage. CM (5) Tested<3dBbelowminimumspecifiedCMRRat±CMIRlimits Copyright©2007–2009,TexasInstrumentsIncorporated SubmitDocumentationFeedback 3 ProductFolderLink(s):OPA890

OPA890 SBOS369B–MAY2007–REVISEDDECEMBER2009 www.ti.com ELECTRICAL CHARACTERISTICS: V = ±5V (continued) S Boldfacelimitsaretestedat+25°C. AtR =750Ω,G=+2V/V,andR =100Ω,unlessotherwisenoted. F L OPA890ID,IDBV TYP MIN/MAXOVERTEMPERATURE 0°Cto –40°Cto MIN/ TEST PARAMETER CONDITIONS +25°C +25°C(2) +70°C(3) +85°C(3) UNITS MAX LEVEL(1) DISABLE DisableLOW Power-DownSupplyCurrent(+VS) VDIS=0 30 55 60 75 μA max A DisableTime VIN=1VDC 7 μs typ C EnableTime VIN=1VDC 200 ns typ C OffIsolation G=+2V/V,f=5MHz 70 dB typ C OutputCapacitanceinDisable 4 pF typ C EnableVoltage 3.0 3.2 3.4 3.8 V min A DisableVoltage 1.4 1.1 1.0 0.8 V max A ControlPinInputBiasCurrent(VDIS) VDIS=0V,EachChannel 15 30 35 40 μA max A POWERSUPPLY SpecifiedOperatingVoltage ±5 V typ C MinimumOperatingVoltage ±1.5 V typ C MaximumOperatingVoltage ±6.0 ±6.0 ±6.0 V max A MaximumQuiescentCurrent VS=±5V 1.1 1.2 1.22 1.25 mA max A MinimumQuiescentCurrent VS=±5V 1.1 1.05 1.02 1 mA min A Power-SupplyRejectionRatio (+PSRR) +VS=4.5Vto5.5V 74 66 62 60 dB min A THERMALCHARACTERISTICS SpecifiedOperatingRange –40to+85 °C typ C ThermalResistanceθJA Junction-to-Ambient D SO-8 105 °C/W typ C DBV SOT23-6 110 °C/W typ C 4 SubmitDocumentationFeedback Copyright©2007–2009,TexasInstrumentsIncorporated ProductFolderLink(s):OPA890

OPA890 www.ti.com SBOS369B–MAY2007–REVISEDDECEMBER2009 ELECTRICAL CHARACTERISTICS: V = +5V S Boldfacelimitsaretestedat+25°C. AtR =750Ω,G=+2V/V,andR =100Ω,unlessotherwisenoted. F L OPA890ID,IDBV TYP MIN/MAXOVERTEMPERATURE 0°Cto –40°Cto MIN/ TEST PARAMETER CONDITIONS +25°C +25°C(2) +70°C(3) +85°C(3) UNITS MAX LEVEL(1) ACPERFORMANCE Small-SignalBandwidth G=+1V/V,VO=100mVPP,RF=0Ω 220 MHz typ C G=+2V/V,VO=100mVPP 105 70 60 55 MHz min B G=+10V/V,VO=100mVPP 12 8 6.8 6.3 MHz min B GainBandwidthProduct G>+20V/V 125 90 75 70 MHz min B Bandwidthfor0.1dBFlatness G=+2V/V,VO=100mVPP 16 MHz typ C PeakingataGainof+1V/V VO<100mVPP 2 dB typ C Large-SignalBandwidth G=+2V/V,VO=2VPP 130 MHz typ C SlewRate G=+2V/V,VO=2VStep 350 250 200 175 V/μs min B Rise-and-FallTime 0.2VStep 3.8 ns typ C SettlingTimeto0.02% G=+1V/V,VO=2VStep 18 ns typ C SettlingTimeto0.1% 12 ns typ C HarmonicDistortion G=+2V/V,f=1MHz,VO=2VPP 2nd-Harmonic RL=200Ω –85 –76 -73 -72 dBc max B RL ≥500Ω –90 –78 –74 –73 dBc max B 3rd-Harmonic RL=200Ω –85 –81 –79 –78 dBc max B RL ≥500Ω –87 –84 –82 –81 dBc max B InputVoltageNoise f>100kHz 8.1 9.1 10.1 11.1 nV/√Hz max B InputCurrentNoise f>100kHz 1.1 1.4 1.7 2.0 pA/√Hz max B DifferentialGain G=+2V/V,VO=1.4VPP,RL=150Ω 0.06 % typ C DifferentialPhase G=+2V/V,VO=1.4VPP,RL=150Ω 0.04 ° typ C Channel-to-ChannelCrosstalk f=5MHz,Input-Referred –68 dB typ C DCPERFORMANCE(4) Open-LoopVoltageGain(AOL) VO=VS/2,RL=100Ω 60 55 54 52 dB min A InputOffsetVoltage VCM=VS/2 ±1 ±5 ±5.7 ±6 mV max A AverageOffsetVoltageDrift VCM=VS/2 ±15 ±15 μV/°C max B InputBiasCurrent VCM=VS/2 ±0.1 ±1.7 ±1.9 ±2.1 μA max A AverageInputBiasCurrentDrift VCM=VS/2 ±5 ±6 nA/°C max B InputOffsetCurrent VCM=VS/2 ±70 ±400 ±500 ±550 nA max A AverageInputOffsetCurrentDrift VCM=VS/2 ±2.5 ±2.5 nA/°C max B INPUT MostPositiveInputVoltage(5) +4 +3.7 +3.65 +3.6 V min A LeastPositiveInputVoltage(5) +1 +1.3 +1.3 +1.4 V max A Common-ModeRejectionRatio(CMRR) VCM=VS/2,Input-Referred 65 59 56 55 dB min A InputImpedance Differential VCM=VS/2 190||0.6 kΩ||pF typ C Common-Mode VCM=VS/2 3.2||0.9 MΩ||pF typ C OUTPUT MostPositiveOutputVoltage NoLoad +4.0 +3.9 +3.85 +3.8 V min A RL=100Ω +3.9 +3.75 +3.7 +3.65 V min A LeastPositiveOutputVoltage NoLoad +1.0 +1.1 +1.15 +1.2 V max A RL=100Ω +1.1 +1.35 +1.4 +1.45 V max A OutputCurrent:Sourcing,Sinking VO=VS/2 ±35 ±30 ±28 ±25 mA min A Short-CircuitOutputCurrent OutputShortedtoGround ±65 mA typ C Closed-LoopOutputImpedance G=+2V/V,f=100kHz 0.04 Ω typ C (1) Testlevels:(A)100%testedat+25°C.Overtemperaturelimitssetbycharacterizationandsimulation.(B)Limitssetbycharacterization andsimulation.(C)Typicalvalueonlyforinformation. (2) Junctiontemperature=ambientfor+25°Ctestedspecifications. (3) Junctiontemperature=ambientatlowtemperaturelimit;junctiontemperature=ambient+2°Cathightemperaturelimitforover temperaturespecifications. (4) Currentisconsideredpositiveout-of-node.V istheinputcommon-modevoltage. CM (5) Tested<3dBbelowminimumspecifiedCMRRat±CMIRlimits Copyright©2007–2009,TexasInstrumentsIncorporated SubmitDocumentationFeedback 5 ProductFolderLink(s):OPA890

OPA890 SBOS369B–MAY2007–REVISEDDECEMBER2009 www.ti.com ELECTRICAL CHARACTERISTICS: V = +5V (continued) S Boldfacelimitsaretestedat+25°C. AtR =750Ω,G=+2V/V,andR =100Ω,unlessotherwisenoted. F L OPA890ID,IDBV TYP MIN/MAXOVERTEMPERATURE 0°Cto –40°Cto MIN/ TEST PARAMETER CONDITIONS +25°C +25°C(2) +70°C(3) +85°C(3) UNITS MAX LEVEL(1) DISABLE DisableLOW Power-DownSupplyCurrent(+VS) VDIS=0V,bothchannels 18 45 50 65 μA max A DisableTime VOUT=1VDC 7 ns typ C EnableTime VOUT=1VDC 200 ns typ C OffIsolation G=+2V/V,f=5MHz 70 dB typ C OutputCapacitanceinDisable 4 pF typ C EnableVoltage 3.0 3.2 3.4 3.8 V min A DisableVoltage 1.4 1.1 1.0 0.8 V max A ControlPinInputBiasCurrent(VDIS) VDIS=0V,EachChannel 15 30 35 40 μA max A POWERSUPPLY SpecifiedOperatingVoltage +5 V typ C MinimumOperatingVoltage +3 V typ C MaximumOperatingVoltage +12 +12 +12 V max A MaximumQuiescentCurrent VS=+5V 1.06 1.18 1.20 1.25 mA max A MinimumQuiescentCurrent VS=+5V 1.06 0.92 0.90 0.87 mA min A Power-SupplyRejectionRatio (+PSRR) +VS=4.5Vto5.5V 65 dB typ C THERMALCHARACTERISTICS SpecifiedOperatingRange –40to+85 °C typ C ThermalResistanceθJA Junction-to-Ambient D SO-8 105 °C/W typ C DBV SOT23-6 110 °C/W typ C 6 SubmitDocumentationFeedback Copyright©2007–2009,TexasInstrumentsIncorporated ProductFolderLink(s):OPA890

OPA890 www.ti.com SBOS369B–MAY2007–REVISEDDECEMBER2009 TYPICAL CHARACTERISTICS: V = ±5V S AtT =+25°C,G=+2V/V,R =750Ω,andR =200Ω,unlessotherwisenoted. A F L SMALL-SIGNALFREQUENCYRESPONSE LARGE-SIGNALFREQUENCYRESPONSE 3 9 G = +1V/V R = 0W 1V 0 F PP 6 2V B) -3 PP ain (d -6 B) 3 G d malized -9 G = +2V/V Gain ( -03 4VPP or -12 N 7V -15 G = +5V/V -6 R = 200W PP VO= 0.1VPP G = +10V/V GL = +2V/V -18 -9 1 10 100 600 1 10 100 400 Frequency (MHz) Frequency (MHz) Figure1. Figure2. SMALL-SIGNALPULSERESPONSE LARGE-SIGNALPULSERESPONSE 400 3 VO= 0.5VPP VO= 5VPP 300 G = +2V/V G = +2V/V 2 Output Voltage (mV) --2112000000000 Output Voltage (V) -101 -2 -300 -400 -3 Time (10ns/div) Time (10ns/div) Figure3. Figure4. VIDEODIFFERENTIALGAIN/DIFFERENTIALPHASE DISABLEFEEDTHROUGH 0.20 0.40 -45 -dP V = 0V 0.18 0.36 -50 DIS Input Referred Differential Gain (%) 000000......111100642086 +dG +-ddPG 000000......322211284062 °Differential Phase () able Feedthrough (dB) -----5667750505 0.04 0.08 Dis -80 0.02 0.04 -85 0 0 -90 1 2 3 4 1 10 100 Number of 150WLoads Frequency (MHz) Figure5. Figure6. Copyright©2007–2009,TexasInstrumentsIncorporated SubmitDocumentationFeedback 7 ProductFolderLink(s):OPA890

OPA890 SBOS369B–MAY2007–REVISEDDECEMBER2009 www.ti.com TYPICAL CHARACTERISTICS: V = ±5V (continued) S AtT =+25°C,G=+2V/V,R =750Ω,andR =200Ω,unlessotherwisenoted. A F L HARMONICDISTORTIONvsLOADRESISTANCE 1MHzHARMONICDISTORTIONvsSUPPLYVOLTAGE -80 -80 -85 fV =O 1=M 2HVzPP VROL== 220V0PWP Bc) 3rd Harmonic G = +2V/V Bc) -85 G = +2V/V n (d -90 n (d 3rd Harmonic o o storti -95 storti -90 c Di 2nd Harmonic c Di 2nd Harmonic oni -100 oni arm arm -95 H -105 H -110 -100 100 1k 2.5 3.0 3.5 4.0 4.5 5.0 5.5 6.0 Load Resistance (W) Supply Voltage (±V ) S Figure7. Figure8. HARMONICDISTORTIONvsFREQUENCY HARMONICDISTORTIONvsOUTPUTVOLTAGE -50 -70 VO= 2VPP RL= 200W -60 RL= 200W -75 f = 1MHz c) G = +2V/V c) G = +2V/V B B n (d -70 n (d -80 o o storti -80 3rd Harmonic storti -85 3rd Harmonic Di Di c c oni -90 oni -90 m m ar 2nd Harmonic ar H -100 H -95 2nd Harmonic -110 -100 0.1 1 10 0.1 1 10 Frequency (MHz) Output Voltage Swing (V ) PP Figure9. Figure10. HARMONICDISTORTIONvsNONINVERTINGGAIN HARMONICDISTORTIONvsINVERTINGGAIN -70 -70 V = 2V V = 2V O PP O PP -75 RL= 200W RL= 200W 3rd Harmonic dBc) -80 f = 1MHz 3rd Harmonic dBc) -75 f = 1MHz n ( n ( Distortio --8950 2nd Harmonic Distortio -80 2nd Harmonic nic nic armo -95 armo -85 H H -100 -105 -90 1 10 20 -1 -10 -20 Gain (V/V) Gain (V/V) Figure11. Figure12. 8 SubmitDocumentationFeedback Copyright©2007–2009,TexasInstrumentsIncorporated ProductFolderLink(s):OPA890

OPA890 www.ti.com SBOS369B–MAY2007–REVISEDDECEMBER2009 TYPICAL CHARACTERISTICS: V = ±5V (continued) S AtT =+25°C,G=+2V/V,R =750Ω,andR =200Ω,unlessotherwisenoted. A F L LOW-FREQUENCYINVERTINGHARMONICDISTORTION TWO-TONE,3RD-ORDERINTERMODULATIONSPURIOUS -90 -40 V = 2V Load Power at Matched 50WLoad O PP -95 RL= 500W -50 monic Distortion (dBc) ---111001050 G =-1V/V 2nd Harmonic purious Point (dBc) ----67890000 10MHz 5MHz Har -115 3rd Harmonic S-100 1MHz -120 -110 1k 10k 100k 1M -8 -6 -4 -2 0 2 4 6 8 Frequency (Hz) Single-Tone Load Power (dBm) Figure13. Figure14. RECOMMENDEDR vsCAPACITIVELOAD FREQUENCYRESPONSEvsCAPACITIVELOAD S 100 9 G = +2V/V 6 C = 10pF L 3 W()S dB) CL= 100pF CL= 22pF R 10 n ( 0 ai C = 47pF G L -3 VIN OPA890 RS VOUT -6 750W CL 1kW(1) 750W NOTE: (1) 1kWis optional. 1 -9 1 10 100 1000 0 20 40 60 80 100 120 140 160 180 200 Capacitive Load (pF) Frequency (MHz) Figure15. Figure16. COMMON-MODEREJECTIONRATIOANDPOWER-SUPPLY REJECTIONRATIOvsFREQUENCY INPUTVOLTAGEANDCURRENTNOISE 80 100 -PSRR 70 )z)z CMRR HH ÖÖ RR (dB) 6500 +PSRR sity (nV/sity (pA/ 10 Voltage Noise Density (8nV/ÖHz) CMRR and PS 432000 oltage Noise Denurrent Noise Den 1 Current Noise Density (1pA/ÖHz) 10 VC 0 0.1 1k 10k 100k 1M 10M 100M 100 1k 10k 100k 1M 10M 100M Frequency (Hz) Frequency (Hz) Figure17. Figure18. Copyright©2007–2009,TexasInstrumentsIncorporated SubmitDocumentationFeedback 9 ProductFolderLink(s):OPA890

OPA890 SBOS369B–MAY2007–REVISEDDECEMBER2009 www.ti.com TYPICAL CHARACTERISTICS: V = ±5V (continued) S AtT =+25°C,G=+2V/V,R =750Ω,andR =200Ω,unlessotherwisenoted. A F L SUPPLYANDOUTPUTCURRENTvsTEMPERATURE TYPICALDCDRIFTvsTEMPERATURE 1.15 50 2.10 250 A) 1.14 Supply Current 49 2.05 Input Bias Current (IB) 200 s (n ent (mA) 111...111321 OutSpouut rCcuinrgrent, 444876 ent (mA) Voltage (V) 21..0905 Input Offset Current (IOS) 115000 Offset Current Supply Curr 1111....10000987 Output Current,Sinking 44445432 Output Curr Input Offset 111...988050 Input Offset Voltage (VOS) -50500 Bias and Input 1.06 41 ut p 1.05 40 1.75 -100 In -50 -25 0 25 50 75 100 125 -50 -25 0 25 50 75 100 125 Ambient Temperature (°C) Ambient Temperature (°C) Figure19. Figure20. LARGE-SIGNALDISABLE/ENABLERESPONSE NONINVERTINGOVERDRIVERECOVERY 6 8 4 4 6 3 V) 2 (DIS 4 2 Voltage (V) 432 0-2 V Output Voltage (V) --2024 OutpLuet fVt oSltcaaglee IRnipguhtt VSoclatalege 10--13 Input Voltage (V) ut 1 utp 0 -6 -3 O -1 -8 -4 Time (5ns/div) Time (10ns/div) Figure21. Figure22. CLOSED-LOOPOUTPUTIMPEDANCEvsFREQUENCY OPEN-LOOPGAINANDPHASE 100 80 180 70 160 10 324W OPA890 ZO 60 Open-Loop Gain 140 Wdance () 1 750W Gain (dB) 5400 Open-Loop Phase 112000 °Phase () mpe 750W oop 30 80 oop put I 0.1 en-L 20 60 en-L Out 0.01 Op 10 40 Op 0 20 0.001 -10 0 1k 10k 100k 1M 10M 100M 100 1k 10k 100k 1M 10M 100M 1G Frequency (Hz) Frequency (Hz) Figure23. Figure24. 10 SubmitDocumentationFeedback Copyright©2007–2009,TexasInstrumentsIncorporated ProductFolderLink(s):OPA890

OPA890 www.ti.com SBOS369B–MAY2007–REVISEDDECEMBER2009 TYPICAL CHARACTERISTICS: V = ±5V, Differential S AtT =+25°C,DifferentialGain=+2V/V,R =750Ω,andR =400Ω,unlessotherwisenoted. A F L DIFFERENTIALSMALL-SIGNALFREQUENCYRESPONSE DIFFERENTIALLARGE-SIGNALFREQUENCYRESPONSE 3 9 G = 1V/V D 0 6 B) -3 GD= 5VPP n (d 3 ai -6 B) G d zed -9 GD= 2V/V ain ( 0 G = 14V ali G D PP orm-12 GD= 5V/V -3 N G = 10V/V -15 R = 750W D -6 F G = 8V R = 400W D PP -18 L -9 1 10 100 300 1 10 100 300 Frequency (MHz) Frequency (MHz) Figure25. Figure26. DIFFERENTIALDISTORTIONvsLOADRESISTANCE DIFFERENTIALDISTORTIONvsFREQUENCY -70 -30 R = 400W -75 -40 GL = 2V/V 3rd Harmonic D 3rd Harmonic Bc) -80 Bc) -50 n (d -85 n (d -60 Distortio --9905 Distortio --7800 monic --110005 2nd Harmonic monic -90 2nd Harmonic Har -110 VO= 4VPP Har -100 -115 f = 1MHz -110 G = 2V/V -120 D -120 100 1k 1 10 20 Load Resistance (W) Frequency (MHz) Figure27. Figure28. DIFFERENTIALDISTORTIONvsOUTPUTVOLTAGE -75 R = 400W L -80 f = 1MHz dBc) -85 GD= 2V/V 3rd Harmonic n ( o orti -90 st c Di -95 ni mo -100 ar H 2nd Harmonic -105 -110 0.1 1 10 Output Voltage (V ) PP Figure29. Copyright©2007–2009,TexasInstrumentsIncorporated SubmitDocumentationFeedback 11 ProductFolderLink(s):OPA890

OPA890 SBOS369B–MAY2007–REVISEDDECEMBER2009 www.ti.com TYPICAL CHARACTERISTICS: V = +5V S AtT =+25°C,G=+2V/V,R =750Ω,andR =200Ω,unlessotherwisenoted. A F L SMALL-SIGNALFREQUENCYRESPONSE LARGE-SIGNALFREQUENCYRESPONSE 3 9 G = +1V/V R = 0W 0 F 6 1V B) -3 PP ain (d -6 B) 3 G d malized -9 G = +2V/V Gain ( -03 2VPP or -12 N 3V G = +5V/V PP -15 -6 R = 200W VO= 100mVPP G = +10V/V GL = +2V/V -18 -9 1 10 100 500 1 10 100 300 Frequency (MHz) Frequency (MHz) Figure30. Figure31. SMALL-SIGNALPULSERESPONSE LARGE-SIGNALPULSERESPONSE 2.9 4.1 V = 0.5V V = 0.5V O PP O PP 2.8 G = +2V/V 3.7 G = +2V/V 2.7 3.3 V) V) e ( 2.6 e ( 2.9 g g a a olt 2.5 olt 2.5 V V put 2.4 put 2.1 ut ut O O 2.3 1.7 2.2 1.3 2.1 0.9 Time (10ns/div) Time (10ns/div) Figure32. Figure33. RECOMMENDEDR vsCAPACITIVELOAD FREQUENCYRESPONSEvsCAPACITIVELOAD S 200 9 100 VIN OPA890 RS VOUT 6 750W CL 1kW(1) 750W NOTE: (1) 1kWis optional. 3 W) dB) R(S 10 Gain ( 0 CL= 22pF CL= 10pF -3 C = 47pF L -6 C = 100pF L 1 -9 1 10 100 1000 0 20 40 60 80 100 120 140 160 180 200 Capacitive Load (pF) Frequency (MHz) Figure34. Figure35. 12 SubmitDocumentationFeedback Copyright©2007–2009,TexasInstrumentsIncorporated ProductFolderLink(s):OPA890

OPA890 www.ti.com SBOS369B–MAY2007–REVISEDDECEMBER2009 TYPICAL CHARACTERISTICS: V = +5V (continued) S AtT =+25°C,G=+2V/V,R =750Ω,andR =200Ω,unlessotherwisenoted. A F L NONINVERTINGOVERDRIVERECOVERY HARMONICDISTORTIONvsLOADRESISTANCE 6.5 4.5 -75 V = 2V O PP 5.5 4.0 f = 1MHz put Voltage (1V/div) 4321....5555 OutpLuet fVt oSltcaaglee IRnipguhtt VSoclatalege 3322....5050 put Voltage (1V/div) monic Distortion (dBc) --8805 GD= +2V/V 3rd Harmonic Out 0.5 1.5 In Har -90 -0.5 1.0 2nd Harmonic -1.5 0.5 -95 Time (10ns/div) 100 1k Load Resistance (W) Figure36. Figure37. HARMONICDISTORTIONvsFREQUENCY HARMONICDISTORTIONvsOUTPUTVOLTAGE -50 -45 V = 2V f = 1MHz O PP R = 200Wto V /2 3rd Harmonic G = +2V/V c) -60 GL = +2V/V S c) -55 RL= 200Wto VS/2 B B d d n ( n ( ortio -70 2nd Harmonic ortio -65 2nd Harmonic st st Di Di c -80 c -75 ni ni o o m m Har -90 Har -85 3rd Harmonic -100 -95 0.1 1 10 0.1 1 10 Frequency (MHz) Output Voltage Swing (V ) PP Figure38. Figure39. TWO-TONE,3RD-ORDERINTERMODULATIONSPURIOUS -40 Load Power at Matched 50WLoad 10MHz -50 c) dB -60 nt ( 5MHz Poi -70 s u o uri -80 p S 1MHz -90 -100 -8 -7 -6 -5 -4 -3 -2 -1 0 1 2 Single-Tone Load Power (dBm) Figure40. Copyright©2007–2009,TexasInstrumentsIncorporated SubmitDocumentationFeedback 13 ProductFolderLink(s):OPA890

OPA890 SBOS369B–MAY2007–REVISEDDECEMBER2009 www.ti.com TYPICAL CHARACTERISTICS: V = +5V, Differential S AtT =+25°C,DifferentialGain=+2V/V,R =750Ω,andR =400Ω,unlessotherwisenoted. A F L DIFFERENTIALSMALL-SIGNALFREQUENCYRESPONSE DIFFERENTIALLARGE-SIGNALFREQUENCYRESPONSE 6 9 G = 1V/V D 3 G = 2V/V RF= 0W 6 D B) 0 ain (d -3 B) 3 4VPP G d zed -6 ain ( 0 ali -9 G m -3 Nor -12 GD= 5V/V 1V PP -15 RF= 750W -6 -18 RL= 400W GD= 10V/V -9 1 10 100 200 1 10 100 300 Frequency (MHz) Frequency (MHz) Figure41. Figure42. DIFFERENTIALDISTORTIONvsLOADRESISTANCE DIFFERENTIALDISTORTIONvsFREQUENCY -70 -40 -75 RL= 400W 3rd Harmonic -50 f = 1MHz dBc) --8805 dBc) -60 GD= 2V/V 3rd Harmonic Distortion ( -1--099005 VfG =OD 1==M 42HVVzP/VP Distortion ( --7800 nic -105 nic -90 armo -110 2nd Harmonic armo -100 2nd Harmonic H -115 H -120 -110 -125 -120 100 1k 1 10 Load Resistance (W) Frequency (MHz) Figure43. Figure44. DIFFERENTIALDISTORTIONvsOUTPUTVOLTAGE -60 -70 c) dB -80 n ( o 3rd Harmonic orti -90 st c Di -100 ni o m -110 ar 2nd Harmonic H -120 -130 0.1 1 10 Output Voltage Swing (V ) PP Figure45. 14 SubmitDocumentationFeedback Copyright©2007–2009,TexasInstrumentsIncorporated ProductFolderLink(s):OPA890

OPA890 www.ti.com SBOS369B–MAY2007–REVISEDDECEMBER2009 APPLICATION INFORMATION WIDEBAND VOLTAGE-FEEDBACK OPERATION +5V The OPA890 provides an exceptional combination of 0.1mF 6.8mF + low quiescent current with a wideband, unity-gain stable, voltage-feedback op amp using a new high slew rate input stage. Typical differential input stages 50WSource used for voltage-feedback op amps are designed to 324W DIS steer a fixed-bias current to the compensation 50WLoad capacitor, setting a limit to the achievable slew rate. VI 50W VO 50W OPA890 The OPA890 uses an input stage that places the transconductance element between two input buffers, using the combined output currents as the forward signal. As the error voltage increases across the two 0.1mF R F inputs, an increasing current is delivered to the 750W compensation capacitor. This increasing current provides very high slew rate (500V/μs) while R G consuming relatively low quiescent current (1.1mA). 750W This exceptional full-power performance comes at the 6.8mF 0.1mF + price of a slightly higher input noise voltage than alternative architectures. The 8nV/√Hz input voltage -5V noise for the OPA890 is low for this combination of inputstageandlowquiescentcurrent. Figure46. DC-Coupled,G=+2,BipolarSupply, SpecificationandTestCircuit Figure 46 shows the dc-coupled, gain of +2, dual power-supply circuit configuration used as the basis of the ±5V Electrical Characteristics and Typical Figure 47 shows the ac-coupled, gain of +2, Characteristics. For test purposes, the input single-supply circuit configuration used as the basis impedance is set to 50Ω with a resistor to ground and of the +5V Electrical Characteristics and Typical the output impedance is set to 50Ω with a series Characteristics. Though not a rail-to-rail design, the outputresistor.VoltageswingsreportedintheTypical OPA890 requires minimal input and output voltage Characteristics are taken directly at the input and headroom compared to other very wideband output pins, while output powers (dBm) are at the voltage-feedback op amps. It delivers a 2V output PP matched 50Ω load. For the circuit of Figure 46, the swing on a single +5V supply with > 100MHz totaleffectiveloadwillbe100Ω 1.5kΩ.Thedisable bandwidth. The key requirement of broadband control line is typically left open to ensure normal single-supply operation is to maintain input and amplifier operation. Two optional components are output signal swings within the usable voltage ranges included in Figure 46. An additional resistor (324Ω) is at both the input and the output. The circuit of included in series with the noninverting input. Figure 47 establishes an input midpoint bias using a Combined with the 25Ω dc source resistance looking simple resistive divider from the +5V supply (two back towards the signal generator, this configuration 698Ω resistors). The input signal is then ac-coupled gives an input bias current cancelling resistance that into the midpoint voltage bias. The input voltage can matches the 375Ω source resistance seen at the swing to within 1.5V of either supply pin, giving a inverting input (see the DC Accuracy and Offset 2V input signal range centered between the supply PP Controlsection).Inadditiontotheusualpower-supply pins. The input impedance matching resistor (59Ω) decoupling capacitors to ground, a 0.1μF capacitor is used for testing is adjusted to give a 50Ω input load included between the two power-supply pins. In when the parallel combination of the biasing divider practical printed circuit board (PCB) layouts, this networkisincluded. optional-added capacitor typically improves the 2nd-harmonicdistortionperformanceby3dBto6dB. Copyright©2007–2009,TexasInstrumentsIncorporated SubmitDocumentationFeedback 15 ProductFolderLink(s):OPA890

OPA890 SBOS369B–MAY2007–REVISEDDECEMBER2009 www.ti.com The frequency response of the schematic shown in +5V +V Figure48isshowninFigure49. S +5V + 0.1mF 6.8mF 50WSource 698W V GND DD 0.1mF 50W DIS DB0 DB1 VREF -5V VI 59W 698W OPA890 VO 100W VS/2 DDDDBBBB2345 DAC½7822 RRFB1 2.5pF +7.5V DB6 I OUT1 75R0FW DDBB78 IOUT2 OPA890 VOUT DB9 R 2 0V£V £5V DB10 R OUT 2_3 RG DB11 R3 5.56kW 0.1mF-2.5V 750W 0.1mF Figure48. DACTransimpedanceAmplifier Figure47. AC-Coupled,G=+2,Single-Supply, 83 SpecificationandTestCircuit 77 Again, an additional resistor (50Ω, in this case) is 71 included directly in series with the noninverting input. This minimum recommended value provides part of B) 65 d the dc source resistance matching for the n ( noninverting input bias current. It is also used to form Gai 59 a simple parasitic pole to roll off the frequency 53 response at very high frequencies ( > 500MHz) using the input parasitic capacitance to form a bandlimiting 47 pole. The gain resistor (R ) is ac-coupled, giving the G 41 circuit a dc gain of +1, which puts the input dc bias 100k 1M 10M 100M voltage (2.5V) at the output as well. The voltage can Frequency (Hz) swing to within 1.35V of either supply pin. Driving a demanding 100Ω load to a midpoint bias is used in this characterization circuit. Higher swings are Figure49. OPA890(asDACTransimpedance Amplifier)FrequencyResponse possibleusingalighterload. MULTIPLYING DAC SINGLE-ENDED OUTPUT TRANSIMPEDANCE AMPLIFIER Multiplying digital-to-analog converters (DACs), such as the DAC7822, can make good use of the low-power,highslewrateamplifier,OPA890. 16 SubmitDocumentationFeedback Copyright©2007–2009,TexasInstrumentsIncorporated ProductFolderLink(s):OPA890

OPA890 www.ti.com SBOS369B–MAY2007–REVISEDDECEMBER2009 Driving a light load, the OPA890 can output ±4V over Notice that most of the error occurs mainly at the first ±5V supplies. Setting the reference voltage to –5V codes (0, 1, 2); excluding these codes from the results in an output voltage swing from 0V to 5V. In analysis yields the following results, shown in order to optimize the OPA2890 operation for this Table1. application, the supply voltages have been adjusted so that the output voltage swing is balanced around Table1.DCAccuracyvsCode mid-supply of the amplifier. Note that as a result of TOTALERRORDUETO the internal architecture of the multiplying DAC, the CODES V andI OS B I output is not high impedance. The I output OUT1 OUT1 Allcodes 3.9LSB resistance is between 4.5kΩ and 22.1kΩ (excluding code 000h) for a 10kΩ nominal V input resistance. Excludingcode0 2.5LSB REF I output resistance changes are directly related to Excludingcodes0and1 2LSB OUT1 the code change. This low impedance has multiple Excludingcodes0,1,and2 1.83LSB effectswhenabipolartechnologyamplifierisused. Note that 1LSB = 1.221mV in the example shown in Someoftheseeffectsare: Figure48 • The noise gain of the amplifier changes for each If more precision is required while maintaining the ac code. performance, a FET-input amplifier (such as the • The output offset voltage of the amplifier changes OPA656ortheTHS4631)isagoodalternative. foreachcode,becauseoftheinputoffsetvoltage. • The input bias current cannot be cancelled. The Figure 48 shows a single-ended output drive effects of the input bias current can be reduced, implementation. In this circuit, only one side of the but not eliminated, thereby affecting the total complementary output drive signal is used. A dual output offset voltage of the amplifier with each amplifier, such as the OPA2890, provides both output code. drivers for the DAC7822. If even lower quiescent currentisneeded,theOPA2889canbeusedinstead, • The noninverting pin of the amplifier must be tied with minor modifications. The diagram shows the to ground and cannot be used to create a dc signaloutputcurrentconnectedintothevirtualground offset on the output amplifier, as is the case for summing junction of the OPA890, which is set up as thetransimpedanceamplifier. a transimpedance stage or I-V converter. The unused The following analysis excludes the input offset current output of the DAC is connected to ground. current. The dc gain for this circuit is equal to R . At high F frequencies, the DAC output capacitance produces a The total output offset voltage variations because of zerointhenoisegainfortheOPA890thatmaycause codechangingintheDACcanbeexpressedas: peaking in the closed-loop frequency response. C is F ΔVOSO=+ΔNG{[(RF ROUT1)–RS]+VOS} added across RF to compensate for this noise gain Where: peaking. To achieve a flat transimpedance frequency response, the pole in the feedback network should be 4.5kΩ ≤ R ≤ 22.1kΩ OUT1 setto: R =10kΩ F 1 (cid:2) GBP Using the previous values, the variation of the parallel 2(cid:1)R C (cid:1) 4(cid:1)R C combination of R and R can be constrained to: F F F D (2) F OUT1 4.19kΩ ≤ (R R )≤ 6.88kΩ.Inordertooptimize F OUT1 which gives a closed-loop transimpedance the bias current cancellation, we select R to be the S bandwidth,f ,ofapproximately: average of those limiting numbers, or R = (6.88kΩ + –3dB S 4.19kΩ)/2=5.56kΩ. (cid:3) GBP f(cid:1)3dB(cid:2) 2(cid:1)R C Looking at the variation for each code, the total error F D (3) (when including all codes) is ~3.9LSB for the Using the DAC7822 internal output capacitance of OPA890. 25pF gives a feedback capacitance (C ) of 2.5pF and F an8.8MHzbandwidth. Copyright©2007–2009,TexasInstrumentsIncorporated SubmitDocumentationFeedback 17 ProductFolderLink(s):OPA890

OPA890 SBOS369B–MAY2007–REVISEDDECEMBER2009 www.ti.com SINGLE-SUPPLY ACTIVE FILTERS The capacitor to ground on the noninverting input is intentionally set larger to dominate input parasitic The high bandwidth provided by the OPA890, while terms. At a gain of +4, the OPA890 on a single operating on a single +5V supply, lends itself well to supply shows ~30MHz small- and large-signal high-frequency active filter designs. Again, the key bandwidth. The resistor values have been slightly additional requirement is to establish the dc operating adjusted to account for this limited bandwidth in the point of the signal near the supply midpoint for amplifier stage. Tests of this circuit show a precise highestdynamicrange.SeeFigure50foranexample 5MHz, –3dB point with a maximally flat passband design of a 5MHz low-pass Butterworth filter using (above the 32kHz ac-coupling corner), and a theSallen-Keytopology. maximum stop band attenuation of 24dB at the Both the input signal and the gain setting resistor are amplifier–3dBbandwidthof30MHz. ac-coupled using 0.1μF blocking capacitors (actually Note that the dc impedance looking out of each input giving band pass response with the low-frequency for this circuit has been set to 1.5kΩ to reduce the pole set to 32kHz for the component values shown). output offset voltage retaining maximum signal swing As discussed for Figure 47, this configuration allows for a mid supply nominal operating voltage at the the midpoint bias formed by the two 1.87kΩ resistors output. to appear at both the input and output pins. The midband signal gain is set to +4 (12dB) in this case. +5V 15 1.87kW 100pF 12 9 0.1mF 137W 432W DIS V B) 6 I d OPA890 4VI ain ( 3 1.87kW 150pF 5MHz, G 2nd-Order, 0 Butterworth 1.5kW Filter -3 500W -6 0.1mF 100k 1M 10M Frequency (Hz) Figure50. Single-Supply,High-FrequencyActiveFilter DESIGN-IN TOOLS DEMONSTRATION FIXTURES MACROMODELS AND APPLICATIONS SUPPORT Two printed circuit boards (PCBs) are available to assist in the initial evaluation of circuit performance Computer simulation of circuit performance using using the OPA890 in its two package options. Both of SPICE is often useful when analyzing the these are offered free of charge as unpopulated performance of analog circuits and systems. This PCBs, delivered with a user's guide. The summary practice is particularly true for video and RF amplifier informationforthesefixturesisshowninTable2. circuits where parasitic capacitance and inductance can have a major effect on circuit performance. A Table2.DemonstrationBoardSummary SPICE model for the OPA890 is available through the Texas Instruments web page (www.ti.com). These ORDERING LITERATURE models do a good job of predicting small-signal ac PRODUCT PACKAGE NUMBER NUMBER and transient performance under a wide variety of OPA890ID SO-8 DEM-OPA-SO-1A SBOU009 operating conditions. They do not do as well in OPA890IDBV SOT23-6 DEM-OPA-SOT-1A SBOU010 predicting the harmonic distortion or dG/dP The demonstration fixtures can be requested at the characteristics. These models do not attempt to Texas Instruments web site (www.ti.com) through the distinguish between package types in the small-signal OPA890productfolder. acperformance. 18 SubmitDocumentationFeedback Copyright©2007–2009,TexasInstrumentsIncorporated ProductFolderLink(s):OPA890

OPA890 www.ti.com SBOS369B–MAY2007–REVISEDDECEMBER2009 OPERATING SUGGESTIONS OPTIMIZING RESISTOR VALUES the bandwidth to more closely approach the predicted value of (GBP/NG). At a gain of +10V/V, the 13MHz Because the OPA890 is a unity-gain stable, bandwidth shown in the Electrical Characteristics voltage-feedback op amp, a wide range of resistor agrees with that predicted using the simple formula values can be used for the feedback and gain setting andthetypicalGBPof130MHz. resistors. The primary limits on these values are set by dynamic range (noise and distortion) and parasitic The OPA890 exhibits minimal bandwidth reduction capacitance considerations. Usually, for G > 1 going to single-supply (+5V) operation as compared applications, the feedback resistor value should be with ±5V. This difference in performance occurs between 200Ω and 1.5kΩ. Below 200Ω, the feedback because the internal bias control circuitry retains network presents additional output loading that can nearly constant quiescent current as the total supply degrade the harmonic distortion performance of the voltagebetweenthesupplypinsischanged. OPA890. Above 1.5kΩ, the typical parasitic capacitance (approximately 0.2pF) across the InvertingAmplifierOperation feedback resistor may cause unintentional The OPA890 is a general-purpose, wideband band-limitingintheamplifierresponse. voltage-feedback op amp; therefore, all of the familiar The combined impedance of R || R interacts with op amp application circuits are available to the F G the inverting input capacitance, placing an additional designer. Inverting operation is one of the more pole in the feedback network and thus, a zero in the common requirements and offers several forward response. Assuming a 2pF total parasitic on performance benefits. Figure 51 shows a typical the inverting node, having R || R < 400Ω keeps inverting configuration where the I/O impedances and F G this pole above 250MHz. By itself, this constraint signal gain from Figure 46 are retained in an inverting implies that the feedback resistor R can increase to circuitconfiguration. F several kΩ at high gains. This increase is acceptable, In the inverting configuration, three key design as long as the pole formed by R and any parasitic F considerations must be noted. First, the gain resistor capacitance appearing in parallel is kept out of the (R ) becomes part of the signal channel input frequencyrangeofinterest. G impedance. If input impedance matching is desired (which is beneficial whenever the signal is coupled BANDWIDTH VERSUS GAIN through a cable, twisted-pair, long PCB trace, or other transmission line conductor), R may be set NoninvertingAmplifierOperation G equal to the required termination value and R F Voltage-feedback op amps exhibit decreasing adjusted to give the desired gain. This approach is closed-loop bandwidth as the signal gain is the simplest, and results in optimum bandwidth and increased. In theory, this relationship is described by noise performance. However, at low inverting gains, the gain bandwidth product (GBP) shown in the the resultant feedback resistor value can present a Electrical Characteristics. Ideally, dividing GBP by the significant load to the amplifier output. For an noninvertingsignalgain(alsocalledthenoisegain,or inverting gain of –2V/V, setting R to 50Ω for input G NG) predicts the closed-loop bandwidth. In practice, matching eliminates the need for R but requires a M this relationship only holds true when the phase 100Ω feedback resistor. This option has the margin approaches 90°, as it does in high-gain interesting advantage that the noise gain becomes configurations. At low gains (increased feedback equal to 2V/V for a 50Ω source impedance—the factors), most amplifiers exhibit a more complex same as the noninverting circuits considered in the response with lower phase margin. The OPA890 is previous section. The amplifier output, however, now compensated to give a slightly peaked response in a sees the 100Ω feedback resistor in parallel with the noninverting gain of 2V/V (see Figure 46). This externalload.Ingeneral,thefeedbackresistorshould compensation results in a typical gain of +2V/V be limited to a range of 200Ω to 1.5kΩ. In this case, it bandwidth of 115MHz, far exceeding that predicted is preferable to increase both the R and R values, F G by dividing the 130MHz GBP by 2. Increasing the as shown in Figure 51, and then achieve the input gain causes the phase margin to approach 90° and matching impedance with a third resistor (R ) to M ground. The total input impedance becomes the parallelcombinationofR andR . G M Copyright©2007–2009,TexasInstrumentsIncorporated SubmitDocumentationFeedback 19 ProductFolderLink(s):OPA890

OPA890 SBOS369B–MAY2007–REVISEDDECEMBER2009 www.ti.com DRIVING CAPACITIVE LOADS +5V One of the most demanding and yet very common + load conditions for an op amp is capacitive loading. 0.1mF 6.8mF Often, the capacitive load is the input of an 0.1mF ADC—including additional external capacitance that DIS R may be recommended to improve ADC linearity. A O 50W high-speed, high open-loop gain amplifier such as the RB 0.1mF OPA890 OPA890 can be very susceptible to decreased 240W 50WLoad stability and closed-loop response peaking when a capacitive load is placed directly on the output pin. 50W When the amplifier open-loop output resistance is R R Source 324GW 750FW considered, this capacitive load introduces an additional pole in the signal path that can decrease the phase margin. Several external solutions to this R M 59W 0.1mF 6.8mF problem have been suggested. When the primary + considerations are frequency response flatness, -5V pulse response fidelity, and/or distortion, the simplest and most effective solution is to isolate the capacitive Figure51. Gainof–2V/VExampleCircuit load from the feedback loop by inserting a series-isolation resistor between the amplifier output The second major consideration, touched on in the and the capacitive load. This solution does not previous paragraph, is that the signal source eliminate the pole from the loop response, but rather impedance becomes part of the noise gain equation shifts it and adds a zero at a higher frequency. The and influences the bandwidth. For the example in additional zero acts to reduce the phase lag from the Figure 51, the R value combines in parallel with the capacitive load pole, thus increasing the phase M external 50Ω source impedance, yielding an effective marginandimprovingstability. driving impedance of 50Ω 59Ω = 27Ω. This The Typical Characteristics show the recommended impedance is added in series with R for calculating G R versus capacitive load and the resulting frequency the noise gain (NG). The resulting NG is 3.14V/V for S response at the load. Parasitic capacitive loads Figure 51, as opposed to only 2 if R could be M greater than 2pF can begin to degrade the eliminated as discussed previously. The bandwidth is performance of the OPA890. Long PCB traces, therefore slightly lower for the gain of –2V/V circuit of unmatched cables, and connections to multiple Figure 51 than for the gain of +2V/V circuit of devices can easily exceed this value. Always Figure46. consider this effect carefully, and add the The third important consideration in inverting amplifier recommended series resistor as close as possible to design is setting the bias current cancellation resistor the OPA890 output pin (see the Board Layout on the noninverting input (R ). If this resistor is set Guidelinessection). B equal to the total dc resistance looking out of the inverting node, the output dc error (because of the NOISE PERFORMANCE input bias currents) is reduced to (Input Offset The input-referred voltage noise, and the two Current) × R . If the 50Ω source impedance is F input-referred current noise terms, combine to give dc-coupled in Figure 51, the total resistance to low output noise under a wide variety of operating ground on the inverting input is 351Ω. Combining this conditions. Figure 52 shows the op amp noise resistance in parallel with the feedback resistor gives analysis model with all the noise terms included. In the value of R = 240Ω used in this example. To B this model, all noise terms are taken to be noise reduce the additional high-frequency noise introduced voltage or current density terms in either nV/√Hz or by this resistor, it is sometimes bypassed with a pA/√Hz. capacitor. As long as R < 350Ω, a capacitor is not B required because the total noise contribution of all other terms is less than that of the op amp input noise voltage. As a minimum, the OPA890 requires an R value of 50Ω to damp out parasitic-induced B peaking—a direct short to ground on the noninverting input runs the risk of a very high-frequency instability intheinputstage. 20 SubmitDocumentationFeedback Copyright©2007–2009,TexasInstrumentsIncorporated ProductFolderLink(s):OPA890

OPA890 www.ti.com SBOS369B–MAY2007–REVISEDDECEMBER2009 DC ACCURACY AND OFFSET CONTROL E NI The balanced input stage of a wideband voltage-feedback op amp allows good output dc OPA890 E RS IBN O accuracy in a wide variety of applications. The power-supply current trim for the OPA890 gives even R F tighter control than comparable amplifiers. Although ERS Ö4kTRS the high-speed input stage does require relatively 4kT RG IBI Ö4kTRF heiagchhininppuuttbitaesrmciunrarel)n,tth(+e25c°lCosewomrsattcchaisneg, 1b.e6tμwAeeant R 4kT = 1.6E-20J G at 290°K them may be used to reduce the output dc error caused by this current. The total output offset voltage may be considerably reduced by matching the dc Figure52. OpAmpNoiseAnalysisModel source resistances appearing at the two inputs. This matching reduces the output dc error resulting from The total output spot noise voltage can be computed the input bias currents to the offset current times the as the square root of the sum of all squared output feedback resistor. Evaluating the configuration of noise voltage contributors. Equation 4 shows the Figure 46, and using worst-case +25°C input offset general form for the output noise voltage using the voltage and current specifications, gives a worst-case termsshowninFigure52. outputoffsetvoltageequalto: EO(cid:2)(cid:5)(cid:3)E2NI(cid:1)(cid:3)IBNRS(cid:4)2(cid:1)4kTRS(cid:4)NG2(cid:1)(IBIRF)2(cid:1)4kTRFNG ±(NG ×VOS(MAX))±(RF× IOS(MAX)) =±(2 ×5mV) ±(750Ω ×0.35μA) (4) =±11.3mV Dividing this expression by the noise gain [NG = (1 + R /R )] gives the equivalent input-referred spot noise withNG=noninvertingsignalgain F G voltage at the noninverting input, as shown in A fine-scale output offset null or dc operating point Equation5. adjustment is often required. Numerous techniques (cid:5) 2 are available for introducing dc offset control into an EN(cid:2) E2NI(cid:1)(cid:3)IBNRS(cid:4)2(cid:1)4kTRS(cid:1)(cid:3)INBIRGF(cid:4) (cid:1)4kNTGRF op amp circuit. Most of these techniques eventually reduce to adding a dc current through the feedback (5) resistor. In selecting an offset trim method, one key consideration is the impact on the desired signal path Evaluating these two equations for the OPA890 frequency response. If the signal path is intended to circuit and component values (see Figure 46) gives a be noninverting, the offset control is best applied as total output spot noise voltage of 17.4nV/√Hz and a an inverting summing signal to avoid interaction with totalequivalentinputspotnoisevoltageof8.7nV/√Hz. the signal source. If the signal path is intended to be This total includes the noise added by the bias inverting, applying the offset control to the current cancellation resistor (175Ω) on the noninverting input may be considered. However, the noninverting input. This total input-referred spot noise dc offset voltage on the summing junction will set up voltage is only slightly higher than the 8nV/√Hz a dc current back into the source that must be specification for the op amp voltage noise alone. This considered. Applying an offset adjustment to the result will be the case, as long as the impedances invertingopampinputcanchangethenoisegainand appearing at each op amp input are limited to the frequency response flatness. For a dc-coupled previously recommend maximum value of 350Ω. inverting amplifier, see Figure 53 for one example of Keeping both (R || R ) and the noninverting input F G an offset adjustment technique that has minimal source impedance less than 350Ω satisfies both impact on the signal frequency response. In this noise and frequency response flatness case, the dc offsetting current is brought into the considerations. Because the resistor-induced noise is inverting input node through resistor values that are relatively negligible, additional capacitive decoupling much larger than the signal path resistors. This across the bias current cancellation resistor (R ) for B configuration ensures that the adjustment circuit has the inverting op amp configuration of Figure 51 is not minimal effect on the loop gain and thus, the required. frequencyresponse. Copyright©2007–2009,TexasInstrumentsIncorporated SubmitDocumentationFeedback 21 ProductFolderLink(s):OPA890

OPA890 SBOS369B–MAY2007–REVISEDDECEMBER2009 www.ti.com current out of Q1, turning the amplifier off. The supply +5V Power-supply decoupling current in the disable mode is only that required to not shown. operate the circuit of Figure 54. Additional circuitry ensures that turn-on time occurs faster than turn-off 0.1mF 226W OPA890 V O time(make-before-break). When disabled, the output and input nodes go to a +5V RG RF 324W -5V 750W high-impedancestate.IftheOPA890isoperatingata V gain of +1V/V, it shows a very high impedance at the I 5kW output and exceptional signal isolation. If operating at 20kW ±150mV Output Adjustment a gain greater than +1V/V, the total feedback network 10kW resistance (R + R ) appears as the impedance V R F G 0.1mF O=- F=-2 looking back into the output, but the circuit still shows 5kW VI RG very-high forward and reverse isolation. If configured as an inverting amplifier, the input and output are -5V connected through the feedback network resistance (R +R )andtheisolationisverypoor,asaresult. F G Figure53. DC-Coupled,InvertingGainof-2V/V, withOffsetAdjustment THERMAL ANALYSIS Maximum desired junction temperature sets the DISABLE OPERATION maximum allowed internal power dissipation, as described below. In no case should the maximum TheOPA890providesanoptionaldisablefeaturethat junctiontemperaturebeallowedtoexceed+150°C. may be used either to reduce system power or to implement a simple channel multiplexing operation. If Operating junction temperature (T ) is given by T + J A the DIS control pin is left unconnected, the OPA890 P × θ . The total internal power dissipation (P ) is D JA D operates normally. To disable the OPA890, the the sum of quiescent power (P ) and additional DQ control pin must be asserted low. Figure 54 shows a power dissipated in the output stage (P ) to deliver DL simplified internal circuit for the disable control load power. Quiescent power is simply the specified feature. no-load supply current times the total supply voltage across the part. P depends on the required output DL +V signal and load, but for a grounded resistive load is at S a maximum when the output is fixed at a voltage equal to 1/2 of either supply voltage (for equal bipolar supplies). Under this condition, P = V 2/(4 × R ) DL S L 80kW whereRLincludesfeedbacknetworkloading. Note that it is the power in the output stage and not into the load that determines internal power Q1 dissipation. As a worst-case example, compute the maximum T J 200kW 2MW using an OPA890IDBV (SOT23-6 package) in the circuit of Figure 46 operating at the maximum V DIS I -V specified ambient temperature of +85°C and driving a S S Control grounded100Ω load. P = 10V × 1.25mA + 52/(4 × (100Ω || 1.5kΩ)) = Figure54. SimplifiedDisableControlCircuit D 79mW MaximumT =+85°C+(79W×150°C/W)=+97°C. In normal operation, base current to Q1 is provided J through the 2MΩ resistor, while the emitter current Although this result is still well below the specified through the 80kΩ resistor sets up a voltage drop that maximum junction temperature, system reliability is inadequate to turn on the two diodes in the Q1 considerations may require lower operating junction emitter. As V DIS is pulled low, additional current is temperatures. The highest possible internal pulled through the 80kΩ resistor, eventually turning dissipation occurs if the load requires current to be on those two diodes ( 15μA). At this point, any forced into the output for positive output voltages, or further current pulled out of V DIS goes through those sourced from the output for negative output voltages. diodes, holding the emitter-base voltage of Q1 at This configuration puts a high current through a large approximately 0V. This process shuts off the collector internalvoltagedropintheoutputtransistors. 22 SubmitDocumentationFeedback Copyright©2007–2009,TexasInstrumentsIncorporated ProductFolderLink(s):OPA890

OPA890 www.ti.com SBOS369B–MAY2007–REVISEDDECEMBER2009 BOARD LAYOUT GUIDELINES with a low parasitic capacitance shunting the external resistors, excessively high resistor Achieving optimum performance with a values can create significant time constants that high-frequency amplifier such as the OPA890 can degrade performance. Good axial metal film requires careful attention to board layout parasitics or surface-mount resistors have approximately and external component types. Recommendations 0.2pF in shunt with the resistor. For resistor thatoptimizeperformanceincludethefollowing: values > 1.5kΩ, this parasitic capacitance can a. Minimize parasitic capacitance to any ac add a pole and/or zero below 500MHz that can ground for all of the signal I/O pins. Parasitic effect circuit operation. Keep resistor values as capacitanceontheoutputandinvertinginputpins low as possible consistent with load driving can cause instability; on the noninverting input, it considerations. The 750Ω feedback used in the can react with the source impedance to cause Typical Characteristics is a good starting point for unintentional bandlimiting. To reduce unwanted design. Note that a direct short is suggested for capacitance, a window around the signal I/O pins theunity-gainfollowerapplication. should be opened in all of the ground and power d. Connections to other wideband devices on the planes around those pins. Otherwise, ground and board may be made with short, direct traces or power planes should be unbroken elsewhere on through onboard transmission lines. For short theboard. connections, consider the trace and the input to b. Minimize the distance (< 0.25") from the the next device as a lumped capacitive load. power-supply pins to high-frequency 0.1μF Relatively wide traces (50mils to 100mils) should decoupling capacitors. At the device pins, the be used, preferably with ground and power ground and power-plane layout should not be in planes opened up around them. Estimate the close proximity to the signal I/O pins. Avoid total capacitive load and set R from the plot of S narrow power and ground traces to minimize Recommended R vs Capacitive Load. Low S inductance between the pins and the decoupling parasitic capacitive loads (< 5pF) may not need capacitors. The power-supply connections should an R because the OPA890 is nominally S always be decoupled with these capacitors. An compensated to operate with a 2pF parasitic optional supply decoupling capacitor (0.1μF) load. Higher parasitic capacitive loads without an across the two power supplies (for bipolar R are allowed as the signal gain increases S operation) will improve 2nd-harmonic distortion (increasing the unloaded phase margin). If a long performance. Larger (2.2μF to 6.8μF) decoupling trace is required, and the 6dB signal loss intrinsic capacitors, effective at lower frequencies, should to a doubly-terminated transmission line is also be used on the main supply pins. These acceptable, implement a matched impedance capacitors may be placed somewhat farther from transmission line using microstrip or stripline the device and may be shared among several techniques (consult an ECL design handbook for devicesinthesameareaofthePCB. microstrip and stripline layout techniques). A 50Ω c. Careful selection and placement of external environment is normally not necessary on the components preserves the high-frequency board, and in fact, a higher impedance performance of the OPA890. Resistors should environment will improve distortion as shown in be a very low reactance type. Surface-mount the distortion versus load plots. With a resistors work best and allow a tighter overall characteristic board trace impedance defined layout. Metal film or carbon composition (based on board material and trace dimensions), axially-leaded resistors can also provide good a matching series resistor into the trace from the high-frequency performance. Again, keep the output of the OPA890 is used as well as a leadsandPCBtracesasshortaspossible.Never terminating shunt resistor at the input of the use wirewound type resistors in a high-frequency destination device. Remember also that the application. Because the output pin and inverting terminating impedance is the parallel combination input pin are the most sensitive to parasitic of the shunt resistor and the input impedance of capacitance, always position the feedback and the destination device; this total effective series output resistor, if any, as close as possible impedance should be set to match the trace to the output pin. Other network components, impedance. The high output voltage and current such as noninverting input termination resistors, capability of the OPA890 allows multiple should also be placed close to the package. destination devices to be handled as separate Where double-side component mounting is transmission lines, each with its respective series allowed, place the feedback resistor directly and shunt terminations. If the 6dB attenuation of under the package on the other side of the board a doubly-terminated transmission line is between the output and inverting input pins. Even unacceptable, a long trace can be Copyright©2007–2009,TexasInstrumentsIncorporated SubmitDocumentationFeedback 23 ProductFolderLink(s):OPA890

OPA890 SBOS369B–MAY2007–REVISEDDECEMBER2009 www.ti.com series-terminated at the source end only. Treat INPUT AND ESD PROTECTION the trace as a capacitive load in this case, and The OPA890 is built using a very high-speed, set the series resistor value as shown in the plot complementary, bipolar process. The internal junction of Recommended R vs Capacitive Load. This S breakdown voltages are relatively low for these very configurationdoesnotpreservesignalintegrityas small geometry devices. These breakdowns are well as a doubly-terminated line. If the input reflected in the Absolute Maximum Ratings table. All impedance of the destination device is low, there devicepinsareprotectedwithinternalESDprotection will be some signal attenuation because of the diodestothepowersupplies,asshowninFigure55. voltage divider formed by the series output into theterminatingimpedance. +V e. Socketing a high-speed part such as the CC OPA890 is not recommended. The additional lead length and pin-to-pin capacitance introduced External Internal by the socket can create an extremely Pin Circuitry troublesome parasitic network that can make it almost impossible to achieve a smooth, stable frequency response. Best results are obtained by -VCC solderingtheOPA890directlyontotheboard. Figure55. InternalESDProtection These diodes provide moderate protection to input overdrive voltages above the supplies as well. The protection diodes can typically support 30mA continuous current. Where higher currents are possible (for example, in systems with ±15V supply parts driving into the OPA890), current-limiting series resistors should be added into the two inputs. Keep these resistor values as low as possible, because high values degrade both noise performance and frequencyresponse. 24 SubmitDocumentationFeedback Copyright©2007–2009,TexasInstrumentsIncorporated ProductFolderLink(s):OPA890

OPA890 www.ti.com SBOS369B–MAY2007–REVISEDDECEMBER2009 REVISION HISTORY NOTE:Pagenumbersforpreviousrevisionsmaydifferfrompagenumbersinthecurrentversion. ChangesfromRevisionA(May2008)toRevisionB Page • Changedmin/maxovertemperaturespecificationsforInput,Common-ModeInputRange(CMIR)parameterof±5V electricalcharacteristics ........................................................................................................................................................ 3 • Changedmin/maxovertemperaturespecificationsforInput,MostPositiveInputVoltageparameterof+5Velectrical characteristics ....................................................................................................................................................................... 5 • Changedmin/maxovertemperaturespecificationsforInput,LeastPositiveInputVoltageparameterof+5V electricalcharacteristics ........................................................................................................................................................ 5 • Correctedx-axisinFigure18................................................................................................................................................ 9 • CorrectedtypoinFigure49title ......................................................................................................................................... 16 ChangesfromOriginal(May2007)toRevisionA Page • ChangedstoragetemperaturerangeratinginAbsoluteMaximumRatingstablefrom–40°Cto+125°Cto–65°Cto +125°C .................................................................................................................................................................................. 2 • DeletedChannel-to-ChannelCrosstalkrowfromACPerformancesectionof±5VElectricalCharacteristics ..................... 3 Copyright©2007–2009,TexasInstrumentsIncorporated SubmitDocumentationFeedback 25 ProductFolderLink(s):OPA890

PACKAGE OPTION ADDENDUM www.ti.com 6-Feb-2020 PACKAGING INFORMATION Orderable Device Status Package Type Package Pins Package Eco Plan Lead/Ball Finish MSL Peak Temp Op Temp (°C) Device Marking Samples (1) Drawing Qty (2) (6) (3) (4/5) OPA890ID ACTIVE SOIC D 8 75 Green (RoHS NIPDAU Level-2-260C-1 YEAR -40 to 85 OPA890 & no Sb/Br) OPA890IDBVR ACTIVE SOT-23 DBV 6 3000 Green (RoHS NIPDAU Level-2-260C-1 YEAR -40 to 85 BRI & no Sb/Br) OPA890IDBVT ACTIVE SOT-23 DBV 6 250 Green (RoHS NIPDAU Level-2-260C-1 YEAR -40 to 85 BRI & no Sb/Br) OPA890IDBVTG4 ACTIVE SOT-23 DBV 6 250 Green (RoHS NIPDAU Level-2-260C-1 YEAR -40 to 85 BRI & no Sb/Br) (1) The marketing status values are defined as follows: ACTIVE: Product device recommended for new designs. LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect. NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design. PREVIEW: Device has been announced but is not in production. Samples may or may not be available. OBSOLETE: TI has discontinued the production of the device. (2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free". RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption. Green: TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement. (3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature. (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device. (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device. (6) Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width. Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and Addendum-Page 1

PACKAGE OPTION ADDENDUM www.ti.com 6-Feb-2020 continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release. In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis. Addendum-Page 2

PACKAGE OUTLINE D0008A SOIC - 1.75 mm max height SCALE 2.800 SMALL OUTLINE INTEGRATED CIRCUIT C SEATING PLANE .228-.244 TYP [5.80-6.19] .004 [0.1] C A PIN 1 ID AREA 6X .050 [1.27] 8 1 2X .189-.197 [4.81-5.00] .150 NOTE 3 [3.81] 4X (0 -15 ) 4 5 8X .012-.020 B .150-.157 [0.31-0.51] .069 MAX [3.81-3.98] .010 [0.25] C A B [1.75] NOTE 4 .005-.010 TYP [0.13-0.25] 4X (0 -15 ) SEE DETAIL A .010 [0.25] .004-.010 0 - 8 [0.11-0.25] .016-.050 [0.41-1.27] DETAIL A (.041) TYPICAL [1.04] 4214825/C 02/2019 NOTES: 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side. 4. This dimension does not include interlead flash. 5. Reference JEDEC registration MS-012, variation AA. www.ti.com

EXAMPLE BOARD LAYOUT D0008A SOIC - 1.75 mm max height SMALL OUTLINE INTEGRATED CIRCUIT 8X (.061 ) [1.55] SYMM SEE DETAILS 1 8 8X (.024) [0.6] SYMM (R.002 ) TYP [0.05] 5 4 6X (.050 ) [1.27] (.213) [5.4] LAND PATTERN EXAMPLE EXPOSED METAL SHOWN SCALE:8X SOLDER MASK SOLDER MASK METAL OPENING OPENING METAL UNDER SOLDER MASK EXPOSED METAL EXPOSED METAL .0028 MAX .0028 MIN [0.07] [0.07] ALL AROUND ALL AROUND NON SOLDER MASK SOLDER MASK DEFINED DEFINED SOLDER MASK DETAILS 4214825/C 02/2019 NOTES: (continued) 6. Publication IPC-7351 may have alternate designs. 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site. www.ti.com

EXAMPLE STENCIL DESIGN D0008A SOIC - 1.75 mm max height SMALL OUTLINE INTEGRATED CIRCUIT 8X (.061 ) [1.55] SYMM 1 8 8X (.024) [0.6] SYMM (R.002 ) TYP [0.05] 5 4 6X (.050 ) [1.27] (.213) [5.4] SOLDER PASTE EXAMPLE BASED ON .005 INCH [0.125 MM] THICK STENCIL SCALE:8X 4214825/C 02/2019 NOTES: (continued) 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations. 9. Board assembly site may have different recommendations for stencil design. www.ti.com

PACKAGE OUTLINE DBV0006A SOT-23 - 1.45 mm max height SCALE 4.000 SMALL OUTLINE TRANSISTOR C 3.0 2.6 0.1 C 1.75 1.45 B A 1.45 MAX PIN 1 INDEX AREA 1 6 2X 0.95 3.05 2.75 1.9 5 2 4 3 0.50 6X 0.25 0.15 0.2 C A B (1.1) TYP 0.00 0.25 GAGE PLANE 0.22 TYP 0.08 8 TYP 0.6 0 0.3 TYP SEATING PLANE 4214840/B 03/2018 NOTES: 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.15 per side. 4. Leads 1,2,3 may be wider than leads 4,5,6 for package orientation. 5. Refernce JEDEC MO-178. www.ti.com

EXAMPLE BOARD LAYOUT DBV0006A SOT-23 - 1.45 mm max height SMALL OUTLINE TRANSISTOR PKG 6X (1.1) 1 6X (0.6) 6 SYMM 2 5 2X (0.95) 3 4 (R0.05) TYP (2.6) LAND PATTERN EXAMPLE EXPOSED METAL SHOWN SCALE:15X SOLDER MASK SOLDER MASK METAL UNDER METAL OPENING OPENING SOLDER MASK EXPOSED METAL EXPOSED METAL 0.07 MAX 0.07 MIN ARROUND ARROUND NON SOLDER MASK SOLDER MASK DEFINED DEFINED (PREFERRED) SOLDER MASK DETAILS 4214840/B 03/2018 NOTES: (continued) 6. Publication IPC-7351 may have alternate designs. 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site. www.ti.com

EXAMPLE STENCIL DESIGN DBV0006A SOT-23 - 1.45 mm max height SMALL OUTLINE TRANSISTOR PKG 6X (1.1) 1 6X (0.6) 6 SYMM 2 5 2X(0.95) 3 4 (R0.05) TYP (2.6) SOLDER PASTE EXAMPLE BASED ON 0.125 mm THICK STENCIL SCALE:15X 4214840/B 03/2018 NOTES: (continued) 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations. 9. Board assembly site may have different recommendations for stencil design. www.ti.com

IMPORTANTNOTICEANDDISCLAIMER TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS. These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources. TI’s products are provided subject to TI’s Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI’s provision of these resources does not expand or otherwise alter TI’s applicable warranties or warranty disclaimers for TI products. Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated

Datasheet下载

Datasheet下载