ICGOO在线商城 > 集成电路(IC) > 线性 - 放大器 - 仪表,运算放大器,缓冲器放大器 > OP282GS

- 型号: OP282GS

- 制造商: Analog

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

OP282GS产品简介:

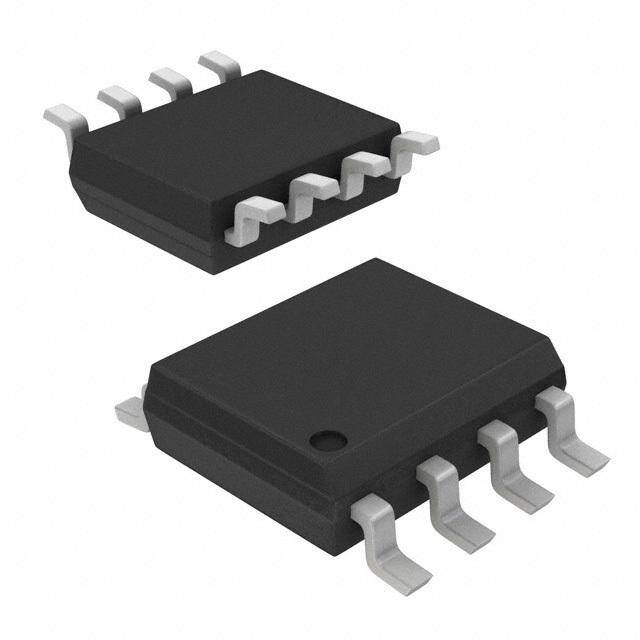

ICGOO电子元器件商城为您提供OP282GS由Analog设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 OP282GS价格参考。AnalogOP282GS封装/规格:线性 - 放大器 - 仪表,运算放大器,缓冲器放大器, J-FET 放大器 2 电路 8-SOIC。您可以下载OP282GS参考资料、Datasheet数据手册功能说明书,资料中有OP282GS 详细功能的应用电路图电压和使用方法及教程。

OP282GS 是由 Analog Devices Inc.(ADI)生产的一款高性能双通道运算放大器,属于线性 - 放大器 - 仪表、运算放大器和缓冲器放大器分类。以下是其主要应用场景: 1. 精密测量与信号调理 OP282GS 具有低噪声、低失调电压和高增益精度的特点,非常适合用于精密测量系统。例如: - 数据采集系统中的信号调理。 - 传感器信号放大(如压力传感器、温度传感器等)。 - 医疗设备中对微弱生物电信号的放大。 2. 音频处理 由于其低失真和宽频带特性,OP282GS 可应用于高质量音频信号处理领域,例如: - 音频前置放大器。 - 高保真音响设备中的信号放大。 3. 工业自动化 在工业控制和自动化系统中,OP282GS 的稳定性使其适用于以下场景: - 工业传感器接口设计。 - 过程控制中的信号放大与转换。 4. 通信系统 OP282GS 的宽带宽和低噪声性能使其适合于通信领域的应用,例如: - 射频(RF)信号链中的中频信号放大。 - 调制解调器中的信号处理。 5. 测试与测量设备 在需要高精度和稳定性的测试仪器中,OP282GS 可以发挥重要作用,例如: - 示波器中的信号放大。 - 数字万用表中的信号调理电路。 6. 医疗电子 由于其低噪声和高输入阻抗特性,OP282GS 广泛应用于医疗电子领域,例如: - 心电图(ECG)、脑电图(EEG)等生物医学信号的放大。 - 医疗成像设备中的信号处理。 7. 汽车电子 在汽车电子系统中,OP282GS 可用于: - 汽车传感器信号的放大与处理。 - 车载信息娱乐系统的音频信号处理。 总结 OP282GS 凭借其卓越的性能参数(如低噪声、低失真、高增益精度等),广泛应用于精密测量、音频处理、工业自动化、通信系统、测试与测量设备、医疗电子以及汽车电子等领域。它特别适合需要高精度和低噪声放大的应用场景。

| 参数 | 数值 |

| -3db带宽 | - |

| 产品目录 | 集成电路 (IC)半导体 |

| 描述 | IC OPAMP JFET 4MHZ 8SOIC运算放大器 - 运放 DUAL LOW PWR JFET IC HI SPEED 4Mhz |

| 产品分类 | Linear - Amplifiers - Instrumentation, OP Amps, Buffer Amps集成电路 - IC |

| 品牌 | Analog Devices Inc |

| 产品手册 | |

| 产品图片 |

|

| rohs | 否不符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 放大器 IC,运算放大器 - 运放,Analog Devices OP282GS- |

| 数据手册 | |

| 产品型号 | OP282GS |

| 产品培训模块 | http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=30008http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=26202 |

| 产品种类 | 运算放大器 - 运放 |

| 供应商器件封装 | 8-SOIC |

| 共模抑制比—最小值 | 70 dB |

| 关闭 | No Shutdown |

| 包装 | 管件 |

| 压摆率 | 9 V/µs |

| 商标 | Analog Devices |

| 增益带宽生成 | 4 Mhz |

| 增益带宽积 | 4MHz |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装 | Tube |

| 封装/外壳 | 8-SOIC(0.154",3.90mm 宽) |

| 封装/箱体 | SOIC-8 |

| 工作温度 | -40°C ~ 90°C |

| 工作电源电压 | +/- 18 V |

| 工厂包装数量 | 98 |

| 放大器类型 | J-FET |

| 最大工作温度 | + 85 C |

| 最小工作温度 | - 40 C |

| 标准包装 | 98 |

| 电压-电源,单/双 (±) | 9 V ~ 36 V, ±4.5 V ~ 18 V |

| 电压-输入失调 | 200µV |

| 电流-电源 | 210µA |

| 电流-输入偏置 | 3pA |

| 电流-输出/通道 | 12mA |

| 电源电流 | 250 uA |

| 电路数 | 2 |

| 系列 | OP282 |

| 视频文件 | http://www.digikey.cn/classic/video.aspx?PlayerID=1364138032001&width=640&height=505&videoID=2245193153001http://www.digikey.cn/classic/video.aspx?PlayerID=1364138032001&width=640&height=505&videoID=2245193159001 |

| 转换速度 | 9 V/us |

| 输入偏压电流—最大 | 100 pA |

| 输入补偿电压 | 3 mV |

| 输出类型 | - |

| 通道数量 | 2 Channel |

PDF Datasheet 数据手册内容提取

Dual/Quad, Low Power, High Speed JFET Operational Amplifiers Data Sheet OP282/OP482 FEATURES PIN CONNECTIONS High slew rate: 9 V/µs OUT A 1 8 V+ Wide bandwidth: 4 MHz –IN A 2 7 OUT B Low supply current: 250 µA/amplifier maximum OP282 +IN A 3 6 –IN B LLooww obfiafsse ctu vroreltnatg: e1:0 30 m pAV mmaaxxiimmuumm V– 4 OP-482 5 +IN B 00301-001 Fast settling time Figure 1. 8-Lead, Narrow-Body SOIC (S-Suffix) [R-8] Common-mode range includes V+ Unity-gain stable OUT A 1 8 V+ OP282 14-ball wafer level chip scale for quad –IN A 2 7 OUT B TOP VIEW APPLICATIONS +INV A– 34 (Not to Scale) 65 +–IINN BB 00301-002 Active filters Figure 2. 8-Lead MSOP [RM-8] Fast amplifiers Integrators OUT A 1 14 OUT D Supply current monitoring –IN A 2 – + + – 13 –IN D GENERAL DESCRIPTION +IN A 3 12 +IN D V+ 4 OP482 11 V– The OP282/OP482 dual and quad operational amplifiers feature +IN B 5 10 +IN C excellent speed at exceptionally low supply currents. The slew –IN B 6 – + + – 9 –IN C rpaetre aims tpylpifiicearl.l yT h9 eVse/ µusn witiyt-hg aa isnu sptpalbyl ec uamrrepnlitf ioefr sle hssa vteh aan t y2p5i0c aµlA OUT B 7 8 OUT C00301-003 gain bandwidth of 4 MHz. Figure 3. 14-Lead PDIP (P-Suffix) [N-14] The JFET input stage of the OP282/OP482 ensures that the bias OUT A 1 14 OUT D current is typically a few picoamps and is less than 500 pA over –IN A 2 13 –IN D the full temperature range. The offset voltage is less than 3 mV for the dual amplifier and less than 4 mV for the quad amplifier. +IN A 3 12 +IN D V+ 4 OP482 11 V– With a wide output swing (within 1.5 V of each supply), low +IN B 5 10 +IN C power consumption, and high slew rate, the OP282/OP482 are –IN B 6 9 –IN C tidioenasl .f oArn b iantpteurty c-opmowmeorend- msyosdteem rsa nogre p tohwate rin-rcelsutdriecst ethde a ppopsliictiav-e OUT B 7 8 OUT C00301-004 supply makes the OP282/OP482 an excellent choice for high- Figure 4. 14-Lead, Narrow-Body SOIC (S-Suffix) [R-14] side signal conditioning. BALLA1 CORNER 1 2 3 The OP282/OP482 are specified over the extended industrial OUT D OUT A temperature range. The OP282 is available in the standard A –IN D 8-lead, narrow SOIC and MSOP packages. The OP482 is B +IN D –IN A available in the PDIP and narrow SOIC packages, as well as C +IN A a 14-ball WLCSP. D V– V+ E +IN B F +IN C –IN B –IN C G H OUT C OUT B J TOP VIEWN o(Bt AtoL LS cSaIlDeE DOWN) 00301-048 Figure 5. 14-Ball WLCSP [CB-14-2] Rev. I Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Tel: 781.329.4700 ©1991–2013 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. Technical Support www.analog.com

OP282/OP482 Data Sheet TABLE OF CONTENTS Features .............................................................................................. 1 ESD Caution...................................................................................4 Applications ....................................................................................... 1 Typical Performance Characteristics ..............................................5 General Description ......................................................................... 1 Applications Information .............................................................. 12 Pin Connections ............................................................................... 1 High-Side Signal Conditioning ................................................ 12 Revision History ............................................................................... 2 Phase Inversion ........................................................................... 12 Specifications ..................................................................................... 3 Active Filters ............................................................................... 12 Electrical Characteristics ............................................................. 3 Programmable State Variable Filter ......................................... 13 Absolute Maximum Ratings ............................................................ 4 Outline Dimensions ....................................................................... 14 Thermal Resistance ...................................................................... 4 Ordering Guide .......................................................................... 16 REVISION HISTORY 9/13—Rev. H to Rev. I Added Figure 5 through Figure 20; Renumbered Successive Figures .............................................................................. 5 Changes to Figure 5 .......................................................................... 1 Updated Figure 21 and Figure 22 .................................................... 7 Updated Outline Dimensions ....................................................... 14 Updated Figure 23 and Figure 27 .................................................... 8 Changes to Ordering Guide .......................................................... 16 Updated Figure 29 ............................................................................. 9 9/10—Rev. G to Rev. H Updated Figure 35 and Figure 36 ................................................. 10 Added WLCSP .................................................................... Universal Updated Figure 43 .......................................................................... 11 Changes to Features Section............................................................ 1 Changes to Applications Information ......................................... 12 Changes to General Description Section ...................................... 1 Changes to Figure 44 ...................................................................... 12 Added Figure 5; Renumbered Sequentially .................................. 1 Deleted OP282/OP482 Spice Macro Model Section .................... 9 Changes to Large-Signal Voltage Gain Parameter, Table 1 ......... 3 Deleted Figure 4 ................................................................................. 9 Changes to Table 2, Thermal Resistance Section, and Table 3 ... 4 Deleted OP282 Spice Marco Model ............................................. 10 Change to Figure 30 ......................................................................... 9 Updated Outline Dimensions ....................................................... 14 Added Figure 53 .............................................................................. 16 Changes to Ordering Guide .......................................................... 14 Changes to Ordering Guide .......................................................... 16 10/02—Rev. D to Rev. E 7/08—Rev. F to Rev. G Edits to 8-Lead Epoxy DIP (P-Suffix) Pin ...................................... 1 Edits to Ordering Guide ................................................................... 3 Changes to Phase Inversion Section ............................................ 12 Edits to Outline Dimensions ......................................................... 11 Deleted Figure 45 ............................................................................ 12 Added Figure 45 and Figure 46..................................................... 12 9/02—Rev. C to Rev. D Updated Outline Dimensions ....................................................... 14 Edits to 14-Lead SOIC (S-Suffix) Pin ............................................. 1 Changes to Ordering Guide .......................................................... 16 Replaced 8-Lead SOIC (S-Suffix) ................................................. 11 10/04—Rev. E to Rev. F 4/02—Rev. B to Rev. C Deleted 8-Lead PDIP ......................................................... Universal Wafer Test Limits Deleted ................................................................ 2 Added 8-Lead MSOP ......................................................... Universal Edits to Absolute Maximum Ratings .............................................. 3 Changes to Format and Layout ......................................... Universal Dice Characteristics Deleted ............................................................ 3 Changes to Features .......................................................................... 1 Edits to Ordering Guide ................................................................... 3 Changes to Pin Configurations ....................................................... 1 Edits to Figure 1 ................................................................................. 7 Changes to General Description .................................................... 1 Edits to Figure 3 ................................................................................. 8 Changes to Specifications ................................................................ 3 20-Position Chip Carrier (RC Suffix) Deleted ........................... 11 Changes to Absolute Maximum Ratings ....................................... 4 Changes to Table 3 ............................................................................ 4 Rev. I | Page 2 of 16

Data Sheet OP282/OP482 SPECIFICATIONS ELECTRICAL CHARACTERISTICS At V = ±15.0 V, T = 25°C, unless otherwise noted; applies to both A and G grades. S A Table 1. Parameter Symbol Test Conditions/Comments Min Typ Max Unit INPUT CHARACTERISTICS Offset Voltage V OP282 0.2 3 mV OS OP282, −40°C ≤ T ≤ +85°C 4.5 mV A OP482 0.2 4 mV OP482, −40°C ≤ T ≤ +85°C 6 mV A Input Bias Current I V = 0 V 3 100 pA B CM V = 0 V1 500 pA CM Input Offset Current I V = 0 V 1 50 pA OS CM V = 0 V1 250 pA CM Input Voltage Range −11 +15 V Common-Mode Rejection Ratio CMRR −11 V ≤ V ≤ +15 V, −40°C ≤ T ≤ +85°C 70 90 dB CM A Large-Signal Voltage Gain A R = 10 kΩ, V = ±13.5 V 20 V/mV VO L O R = 10 kΩ, −40°C ≤ T ≤ +85°C 15 V/mV L A Offset Voltage Drift ΔV /ΔT 10 µV/°C OS Bias Current Drift ΔI /ΔT 8 pA/°C B OUTPUT CHARACTERISTICS Output Voltage High V R = 10 kΩ 13.5 13.9 V OH L Output Voltage Low V R = 10 kΩ −13.9 −13.5 V OL L Short-Circuit Limit I Source 3 10 mA SC Sink −12 −8 mA Open-Loop Output Impedance Z f = 1 MHz 200 Ω OUT POWER SUPPLY Power Supply Rejection Ratio PSRR V = ±4.5 V to ±18 V, −40°C ≤ T ≤ +85°C 25 316 µV/V S A Supply Current/Amplifier I V = 0 V, −40°C ≤ T ≤ 85°C 210 250 µA SY O A Supply Voltage Range V ±4.5 ±18 V S DYNAMIC PERFORMANCE Slew Rate SR R = 10 kΩ 7 9 V/µs L Full-Power Bandwidth BW 1% distortion 125 kHz P Settling Time t To 0.01% 1.6 µs S Gain Bandwidth Product GBP 4 MHz Phase Margin Ø 55 Degrees M NOISE PERFORMANCE Voltage Noise e p-p 0.1 Hz to 10 Hz 1.3 µV p-p n Voltage Noise Density e f = 1 kHz 36 nV/√Hz n Current Noise Density i 0.01 pA/√Hz n 1 The input bias and offset currents are characterized at TA = TJ = 85°C. Bias and offset currents are guaranteed but not tested at −40°C. Rev. I | Page 3 of 16

OP282/OP482 Data Sheet ABSOLUTE MAXIMUM RATINGS Table 2. THERMAL RESISTANCE Parameter Rating θ is specified for the worst-case conditions, that is, a device in JA Supply Voltage ±18 V socket for PDIP. θ is specified for a device soldered in the circuit JA Input Voltage ±18 V board for SOIC_N, MSOP, and WLCSP packages. This was Differential Input Voltage1 36 V measured using a standard 4-layer board. Output Short-Circuit Duration Indefinite Storage Temperature Range −65°C to +150°C Table 3. Operating Temperature Range −40°C to +85°C Package Type θJA θJC Unit Junction Temperature Range −65°C to +150°C 8-Lead MSOP [RM] 142 45 °C/W Lead Temperature (Soldering 60 sec) 300°C 8-Lead SOIC_N (S-Suffix) [R] 120 45 °C/W 14-Lead PDIP (P-Suffix) [N] 83 39 °C/W 1 For supply voltages less than ±18 V, the absolute maximum input voltage is 14-Lead SOIC_N (S-Suffix) [R] 112 35 °C/W equal to the supply voltage. 14-Ball WLCSP [CB]1, 2 70 16 °C/W Stresses above those listed under Absolute Maximum Ratings 1 Simulated thermal numbers per JESD51-9. may cause permanent damage to the device. This is a stress 2 Junction-to-board thermal resistance. rating only; functional operation of the device at these or any other conditions above those indicated in the operational ESD CAUTION section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Rev. I | Page 4 of 16

Data Sheet OP282/OP482 TYPICAL PERFORMANCE CHARACTERISTICS 80 180 70 VS = ±15V VS = ±15V TA = 25°C 60 TA = 25°C 60 135 50 P GAIN (dB) 2400 4950 Degrees) OP GAIN (dB) 243000 AAVVCCLL== 11000 PEN-LOO 0 0 PHASE ( OSED-LO 100 AVCL= 1 O L C –10 –20 –45 –401k 10k FREQU1E0N0kCY (Hz) 1M 10M–90 00301-005 ––23001k 10k FREQU1E0N0kCY (Hz) 1M 10M00301-008 Figure 6. OP282 Open-Loop Gain and Phase vs. Frequency Figure 9. OP282 Closed-Loop Gain vs. Frequency 45 30 VS = ±15V VS = ±15V 40 RL = 10kΩ RL = 10kΩ 25 CL = 50pF 35 –SR V) N (V/m 30 V/µs) 20 OOP GAI 2205 W RATE ( 15 EN-L 15 SLE 10 P +SR O 10 5 05 00301-006 0 00301-009 –75 –50 –25 0 25 50 75 100 125 –75 –50 –25 0 25 50 75 100 125 TEMPERATURE (°C) TEMPERATURE (°C) Figure 7. OP282 Open-Loop Gain vs. Temperature Figure 10. OP282 Slew Rate vs. Temperature 80 1000 VS = ±15V VS = ±15V 70 RVILN == 21k0Ω0mV p-p VCM = 0V AVCL= 1 60 TA = 25°C A)100 p %) 50 +OS NT ( T ( RE OO 40 –OS UR 10 H C VERS 30 BIAS O T U 20 NP 1 I 100 00301-007 0.1 00301-010 0 100 200 300 400 500 –75 –50 –25 0 25 50 75 100 125 LOAD CAPACITANCE (pF) TEMPERATURE (°C) Figure 8. OP282 Small-Signal Overshoot vs. Load Capacitance Figure 11. OP282 Input Bias Current vs. Temperature Rev. I | Page 5 of 16

OP282/OP482 Data Sheet 1000 20 VS = ±15V TA = 25°C TA = 25°C 15 RL = 10kΩ Hz) VOH nV/√ G (V) 10 SITY ( 100 SWIN 5 E DEN TAGE 0 S L E NOI 10 UT VO –5 G P TA UT–10 VOL O VOL 1 00301-011 ––2105 00301-014 10 100 1k 10k 0 ±5 ±10 ±15 ±20 FREQUENCY (Hz) SUPPLY VOLTAGE (V) Figure 12. OP282 Voltage Noise Density vs. Frequency Figure 15. OP282 Output Voltage Swing vs. Supply Voltage 1000 1000 VS = ±15V VS = ±15V TA = 25°C TA = 25°C pA)100 Ω) 100 NT ( CE ( AVCL = 100 CURRE 10 PEDAN 10 S M T BIA PUT I AVCL = 10 U T NP 1 OU 1 I AVCL = 1 0.1 00301-012 0.1 00301-015 –15 –10 –5 0 5 10 15 100 1k 10k 100k 1M COMMON-MODE VOLTAGE (V) FREQUENCY (Hz) Figure 13. OP282 Input Bias Current vs. Common-Mode Voltage Figure 16. OP282 Closed-Loop Output Impedance vs. Frequency 480 480 TA = 25°C 475 475 A) A) NT (µ470 NT (µ 470 CURRE465 CURRE 465 UPPLY 460 UPPLY 460 S S 455 455 450 00301-013 450 00301-016 0 ±5 ±10 ±15 ±20 –50 –25 0 25 50 75 100 125 SUPPLY VOLTAGE (V) TEMPERATURE (°C) Figure 14. OP282 Supply Current vs. Supply Voltage Figure 17. OP282 Supply Current vs. Temperature Rev. I | Page 6 of 16

Data Sheet OP282/OP482 16 30 VS = ±15V VS = ±15V V) 14 TA = 25°C VOL p) 25 TRAALV C==L 2 1=50 °k1CΩ GE ( 12 V p- TA G ( 20 PUT VOL 108 VOH UT SWIN 15 T P U T TE O 6 M OU 10 U U ABSOL 4 MAXIM 5 02 00301-017 0 00301-020 100 1k 10k 100 1k 10k 100k 1M LOAD RESISTANCE (Ω) FREQUENCY (Hz) Figure 18. OP282 Absolute Output Voltage vs. Load Resistance Figure 21. OP282 Maximum Output Swing vs. Frequency 140 140 VS = ±15V VS = ±15V 120 TA = 25°C 120 TA = 25°C 100 100 +PSRR 80 80 PSRR (dB) 426000 –PSRR CMRR (dB) 426000 0 0 –20 –20 ––6400 00301-018 ––6400 00301-021 100 1k 10k 100k 1M 100 1k 10k 100k 1M FREQUENCY (Hz) FREQUENCY (Hz) Figure 19. OP282 PSRR vs. Frequency Figure 22. OP282 CMRR vs. Frequency 14 200 VS = ±15V VS = ±15V TA = 25°C TA = 25°C 12 300× OP282 A) 160 (600 OPAMPS) m T ( 10 SINK N E RCUIT CURR 68 SOURCE UNITS 12800 CI RT- 4 O SH 40 2 0 00301-019 0 00301-022 –50 –25 0 25 50 75 100 125 –2000 –1200 –400 0 400 1200 2000 TEMPERATURE (°C) VOS (µV) Figure 20. OP282 Short-Circuit Current vs. Temperature Figure 23. OP282 VOS Distribution, SOIC_N Package Rev. I | Page 7 of 16

OP282/OP482 Data Sheet 400 70 360 V3(60S00 0=× O± O1P5PAV2M82PS) 60 VRSL == 2±k1Ω5V ANEVCGLA=T I1VE EDGE 320 VIN = 100mV p-p 280 50 S 240 OT (%)40 APOVCSLIT=I V1E EDGE UNIT 200 RSHO30 160 E V O 120 20 80 10 400 00301-023 0 00301-026 0 4 8 12 16 20 24 28 32 36 0 100 200 300 400 500 TCVOS (µV/°C) LOAD CAPACITANCE (pF) Figure 24. OP282 TCVOS Distribution, SOIC_N Package Figure 27. OP482 Small-Signal Overshoot vs. Load Capacitance 80 0 60 VS = ±15V VS = ±15V TA = 25°C 50 TA = 25°C 60 45 AVCL = 100 B) 40 OPEN-LOOP GAIN (dB) 4200 91035 PHASE (Degrees) CLOSED-LOOP GAIN (d 2130000 AAVVCCLL == 110 0 180 1k 10k F1R00EkQUENCY 1(HMz) 10M 100M 00301-024 ––12001k 10k 1F0R0EkQUENCY1 (MHz) 10M 100M00301-027 Figure 25. OP482 Open-Loop Gain and Phase vs. Frequency Figure 28. OP482 Closed-Loop Gain vs. Frequency 35 25 VS = ±15V –SR 30 RL = 10kΩ 20 mV) 25 VRSL == ±1105kVΩ P GAIN (V/ 20 ATE (V/µs)15 CL = 50pF O R N-LO 15 LEW 10 +SR E S P 10 O 5 50 00301-025 0 00301-028 –75 –50 –25 0 25 50 75 100 125 –75 –50 –25 0 25 50 75 100 125 TEMPERATURE (°C) TEMPERATURE (°C) Figure 26. OP482 Open-Loop Gain vs. Temperature Figure 29. OP482 Slew Rate vs. Temperature Rev. I | Page 8 of 16

Data Sheet OP282/OP482 1000 1000 VS = ±15V VS = ±15V VCM = 0V TA = 25°C INPUT BIAS CURRENT (pA) 1101.000 INPUT BIAS CURRENT (pA) 101001 0.1 00301-029 0.1 00301-032 –75 –50 –25 0 25 50 75 100 125 –15 –10 –5 0 5 10 15 TEMPERATURE (°C) COMMON-MODE VOLTAGE (V) Figure 30. OP482 Input Bias Current vs. Temperature Figure 33. OP482 Input Bias Current vs. Common-Mode Voltage 60 5.0 1.15 VS = ±15V TA = 25°C RL = 10kΩ Degrees) 55 GBW 4.5 UCT (MHz) RENT (I)SY11..1005 N ( OD UR SE MARGI 50 ØM 4.0 WIDTH PR SUPPLY C 1.00 PHA 45 3.5 N BAND LATIVE 0.95 GAI RE 0.90 40–75 –50 –25 TE0MPERA2T5URE (5°C0) 75 100 1253.0 00301-030 0.850 ±5 SUPPLY V±O1L0TAGE (V) ±15 ±2000301-033 Figure 31. OP482 Phase Margin and Gain Bandwidth Product vs. Figure 34. OP482 Relative Supply Current vs. Supply Voltage Temperature 80 20 VS = ±15V RL = 10kΩ TA = 25°C TA = 25°C 70 15 Hz) nV/√ 60 G (V) 10 SITY ( 50 SWIN 5 E DEN 40 TAGE 0 E NOIS 30 UT VOL –5 G P TA 20 UT–10 L O O V 100 00301-031 ––2105 00301-034 10 100 1k 10k 0 ±5 ±10 ±15 ±20 FREQUENCY (Hz) SUPPLYVOLTAGE(V) Figure 32. OP482 Voltage Noise Density vs. Frequency Figure 35. OP482 Output Voltage Swing vs. Supply Voltage Rev. I | Page 9 of 16

OP282/OP482 Data Sheet 600 100 VS = ±15V +PSRR VS = ±15V TA = 25°C ΔV = 100mV 500 80 TA = 25°C Ω) 400 60 –PSRR E ( B) C d DAN 300 RR ( 40 PE PS M I 200 20 AVCL = 100 AVCL = 10 100 0 0 AVCL = 1 00301-035 20 00301-038 100 1k 10k 100k 1M 100 1k 10k 100k 1M FREQUENCY (Hz) FREQUENCY (Hz) Figure 36. OP482 Closed-Loop Output Impedance vs. Frequency Figure 39. OP482 Power Supply Rejection Ratio (PSRR) vs. Frequency 1.20 20 VS = ±15V VS = ±15V SINK )Y1.15 mA) T (IS1.10 NT ( 15 N E E R RR1.05 UR U C PLY C1.00 CUIT 10 P R LATIVE SU00..9905 SHORT-CI 5 SOURCE E R 00..8805 00301-036 0 00301-039 –75 –50 –25 0 25 50 75 100 125 –75 –50 –25 0 25 50 75 100 125 TEMPERATURE (°C) TEMPERATURE (°C) Figure 37. OP482 Relative Supply Current vs. Temperature Figure 40. OP482 Short-Circuit Current vs. Temperature 16 30 VS = ±15V VS = ±15V 14 TA = 25°C TA = 25°C AGE (V) 12 POSITIVE G (V) 25 RAVL C=L 1=0 k1Ω OLT 10 SWING WIN 20 LUTE OUTPUT V 86 NSWEGINAGTIVE MUM OUTPUT S 1150 ABSO 4 MAXI 5 02 00301-037 0 00301-040 100 1k 10k 1k 10k 100k 1M LOAD RESISTANCE (Ω) FREQUENCY (Hz) Figure 38. OP482 Maximum Output Voltage vs. Load Resistance Figure 41. OP482 Maximum Output Swing vs. Frequency Rev. I | Page 10 of 16

Data Sheet OP282/OP482 100 320 280 80 240 60 200 B) d S MRR ( 40 UNIT160 C 120 20 80 0 –20 VTVASC M== =2± 511°50CV0mV 00301-041 400 00301-043 100 1k 10k 100k 1M 0 4 8 12 16 20 24 28 32 FREQUENCY (Hz) TCVOS (µV/°C) Figure 42. OP482 Common-Mode Rejection Ratio (CMRR) vs. Frequency Figure 44. OP482 TCVOS Distribution, PDIP Package 700 VS = ±15V TA = 25°C 600 300× OP482 (1200 OPAMPS) 500 S400 T NI U 300 200 1000 00301-045 –2000–1600–1200 –800 –400 0 400 800 1200 1600 2000 VOS (µV) Figure 43. OP482 VOS Distribution, PDIP Package Rev. I | Page 11 of 16

OP282/OP482 Data Sheet APPLICATIONS INFORMATION The OP282 and OP482 are dual and quad JFET op amps that amp against phase reversal. R1, D2, and D3 limit the input are optimized for high speed at low power. This combination current when the input exceeds the supply rail. The resistor makes these amplifiers excellent choices for battery-powered or should be selected to limit the amount of input current below low power applications that require above average performance. the absolute maximum rating. Applications benefiting from this performance combination V+ include telecommunications, geophysical exploration, portable medical equipment, and navigational instrumentation. 10Rk1Ω DIN25711 OP282/ HIGH-SIDE SIGNAL CONDITIONING VIN DIN15711 VV+–OP482 VOUT Many applications require the sensing of signals near the positive D3 IN5711 rail. OP282 and OP482 were tested and are guaranteed over a cpoomsitmivoen s-umppoldye. range (−11 V ≤ VCM ≤ +15 V) that includes the V– 00301-042 Figure 46. Phase Reversal Solution Circuit One application where such sensing is commonly used is in the sensing of power supply currents. Therefore, the OP282/OP482 can be used in current sensing applications, such as the partial VS = ±15V circuit shown in Figure 45. In this circuit, the voltage drop across a low value resistor, such as the 0.1 Ω shown here, is amplified and compared to 7.5 V. The output can then be used for current limiting. DIV) V/ 15V 0.1Ω E (5 2 G 500kΩ TA L O 100kΩ RL V 100kΩ VOUT OP1/2282 VIN 00301-044 TIME (200µs/DIV) 500kΩ 00301-046 ACTIVE FILTERSF igure 47. No Phase Reversal Figure 45. High-Side Signal Conditioning The wide bandwidth and high slew rates of the OP282/OP482 PHASE INVERSION make either one an excellent choice for many filter applications. Most JFET input amplifiers invert the phase of the input signal There are many active filter configurations, but the four most if either input exceeds the input common-mode range. For the popular configurations are Butterworth, elliptic, Bessel, and OP282/OP482, a negative signal in excess of 11 V causes phase Chebyshev. Each type has a response that is optimized for a inversion. This is caused by saturation of the input stage, leading given characteristic, as shown in Table 4. to the forward-biasing of a gate-drain diode. Phase reversal in the OP282/OP482 can be prevented by using Schottky diodes to clamp the input terminals to each other and to the supplies. In the simple buffer circuit shown in Figure 46, D1 protects the op Table 4. Active Filter Configurations Type Selectivity Overshoot Phase Amplitude (Pass Band) Amplitude (Stop Band) Butterworth Moderate Good Maximum flat Chebyshev Good Moderate Nonlinear Equal ripple Elliptic Best Poor Equal ripple Equal ripple Bessel (Thompson) Poor Best Linear Rev. I | Page 12 of 16

Data Sheet OP282/OP482 PROGRAMMABLE STATE VARIABLE FILTER This cutoff frequency can now be expressed as The circuit shown in Figure 48 can be used to accurately f = 1 D1 program the Q, the cutoff frequency (f ), and the gain of a two- C 2πR1C1256 C pole state variable filter. OP482 devices have been used in this where D1 is the digital code for the DAC. design because of their high bandwidths, low power, and low The gain of this circuit is set by adjusting D3. The gain equation is noise. This circuit takes only three packages to build because of the quad configuration of the op amps and DACs. R4 D3 Gain= The DACs shown are used in the voltage mode; therefore, many R5256 values are dependent on the accuracy of the DAC only and not DAC 2 is used to set the Q of the circuit. Adjusting this DAC on the absolute values of the DAC’s resistive ladders. This controls the amount of feedback from the band-pass node to makes this circuit unusually accurate for a programmable filter. the input summing node. Note that the digital value of the Adjusting DAC 1 changes the signal amplitude across R1; therefore, DAC is in the numerator; therefore, zero code is not a valid the DAC attenuation times R1 determines the amount of signal operating point. current that charges the integrating capacitor, C1. R2256 Q= R3 D2 R7 2kΩ R4 2kΩ VIN R5 C1 1/4 1/4 2kΩ 1000pF DAC8408 OP482 OP14/482 1/4 1/4 2Rk1Ω 10C001pF DAC8408 OP482 1/4 OP482 R1 1/4 1/4 2kΩ DAC8408 OP482 1/4 HIGHPASS OP482 LOW PASS R6 BANDPASS 2kΩ R3 2kΩ R2 2kΩ 1/4 1/4 1/4 OP482 DAC8408 OP482 00301-047 Figure 48. Programmable State Variable Filter Rev. I | Page 13 of 16

OP282/OP482 Data Sheet OUTLINE DIMENSIONS 3.20 3.00 2.80 8 5 5.15 3.20 4.90 3.00 4.65 2.80 1 4 PIN1 IDENTIFIER 0.65BSC 0.95 15°MAX 0.85 1.10MAX 0.75 0.80 0.15 0.40 6° 0.23 0.55 CO0P.0L50A.1N0ARICTOYMPLIANT0.T25OJEDECSTA0°NDARDS0M.0O9-187-AA 0.40 10-07-2009-B Figure 49. 8-Lead Mini Small Outline Package [MSOP] (RM-8) Dimensions shown in millimeters 5.00(0.1968) 4.80(0.1890) 8 5 4.00(0.1574) 6.20(0.2441) 3.80(0.1497) 1 4 5.80(0.2284) 1.27(0.0500) 0.50(0.0196) BSC 1.75(0.0688) 0.25(0.0099) 45° 0.25(0.0098) 1.35(0.0532) 8° 0.10(0.0040) 0° COPLANARITY 0.51(0.0201) 0.10 SEATING 0.31(0.0122) 0.25(0.0098) 10..2470((00..00510507)) PLANE 0.17(0.0067) COMPLIANTTOJEDECSTANDARDSMS-012-AA C(RINOEFNPEATRRREOENNLCLTEIHNEOGSNDELISYM)AEANNRDSEIAORRNOESUNANORDETEDAIN-POMPFRIFLOLMPIMIRLELIATIMTEEERTFSEO;RIRNECUQHSUEDIVIINMAELDENENSSTIIOGSNNFS.OR 012407-A Figure 50. 8-Lead Standard Small Outline Package [SOIC_N] Narrow Body S-Suffix (R-8) Dimensions shown in millimeters and (inches) Rev. I | Page 14 of 16

Data Sheet OP282/OP482 0.775 (19.69) 0.750 (19.05) 0.735 (18.67) 14 8 0.280 (7.11) 0.250 (6.35) 1 7 0.240 (6.10) 0.325 (8.26) 0.310 (7.87) 0.100 (2.54) 0.300 (7.62) BSC 0.060 (1.52) 0.195 (4.95) 0.210 (5.33) MAX 0.130 (3.30) MAX 0.115 (2.92) 0.015 0.150 (3.81) (0.38) 0.015 (0.38) 0.130 (3.30) MIN GAUGE 0.110 (2.79) SEATING PLANE 0.014 (0.36) PLANE 0.010 (0.25) 0.022 (0.56) 0.008 (0.20) 0.005 (0.13) 0.430 (10.92) 0.018 (0.46) MIN MAX 0.014 (0.36) 0.070 (1.78) 0.050 (1.27) 0.045 (1.14) COMPLIANTTO JEDEC STANDARDS MS-001 CONTROLLING DIMENSIONSARE IN INCHES; MILLIMETER DIMENSIONS (RCINEOFRPEANRREERENN LCTEEHA EODSNSEL MSY)AAAYNR BDEE AR CROOEU NNNFODIGETUDAR-POEPFDRFOA INSPC RWHIAH ETOEQL UFEIO VORAR LU EHSNAETL ISFN FLDOEEARSDIGSN.. 070606-A Figure 51. 14-Lead Plastic Dual In-Line Package [PDIP] P-Suffix (N-14) Dimension shown in inches and (millimeters) 8.75 (0.3445) 8.55 (0.3366) 4.00 (0.1575) 14 8 6.20 (0.2441) 3.80 (0.1496) 1 7 5.80 (0.2283) 1.27 (0.0500) 0.50 (0.0197) BSC 45° 1.75 (0.0689) 0.25 (0.0098) 0.25 (0.0098) 1.35 (0.0531) 8° 0.10 (0.0039) 0° COPLANARITY SEATING 0.10 0.51 (0.0201) PLANE 0.25 (0.0098) 1.27 (0.0500) 0.31 (0.0122) 0.17 (0.0067) 0.40 (0.0157) COMPLIANTTO JEDEC STANDARDS MS-012-AB C(RINOEFNPEATRRREOENNLCLTEIHN EOGSN EDLSIYM)AEANNRDSEI AORRNOESU NANORDEET DAIN-PO MPFRIFLO LMPIIMRLELIATIMTEEER TFSEO; RIRN ECUQHSU EDI VIINMA LEDENENSSTIIOGSN NFS.OR 060606-A Figure 52. 14-Lead Standard Small Outline Package [SOIC_N] Narrow Body S-Suffix (R-14) Dimensions shown in millimeters and (inches) Rev. I | Page 15 of 16

OP282/OP482 Data Sheet 1.165 1.128 0.347 0.347 1.090 BSC BSC 3 2 1 A BALLA1 0.20 B IDENTIFIER BSC 2.160 C 2.123 D 1.60 2.085 REF E F G H J 0.40 TOP VIEW BSC BOTTOM VIEW (BALL SIDE DOWN) (BALL SIDE UP) 0.415 0.694 0.645 REF 0.400 0.600 END VIEW 0.385 0.555 COPLANARITY 0.05 SEATING 0.287 0.230 PLANE 0.200 00..226477 0.170 09-11-2012-B Figure 53. 14-Ball Wafer Level Chip Scale Package [WLCSP] CB-14-2 Controlling dimensions are millimeters ORDERING GUIDE Model1 Temperature Range Package Description Package Option Branding OP282ARMZ −40°C to +85°C 8-Lead MSOP RM-8 A0B OP282ARMZ-REEL −40°C to +85°C 8-Lead MSOP RM-8 A0B OP282GS −40°C to +85°C 8-Lead SOIC_N S-Suffix (R-8) OP282GS-REEL −40°C to +85°C 8-Lead SOIC_N S-Suffix (R-8) OP282GS-REEL7 −40°C to +85°C 8-Lead SOIC_N S-Suffix (R-8) OP282GSZ −40°C to +85°C 8-Lead SOIC_N S-Suffix (R-8) OP282GSZ-REEL −40°C to +85°C 8-Lead SOIC_N S-Suffix (R-8) OP282GSZ-REEL7 −40°C to +85°C 8-Lead SOIC_N S-Suffix (R-8) OP482ACBZ-RL −40°C to +85°C 14-Ball WLCSP CB-14-2 A2J OP482ACBZ-R7 −40°C to +85°C 14-Ball WLCSP CB-14-2 A2J OP482GPZ −40°C to +85°C 14-Lead PDIP P-Suffix (N-14) OP482GS −40°C to +85°C 14-Lead SOIC_N S-Suffix (R-14) OP482GS-REEL −40°C to +85°C 14-Lead SOIC_N S-Suffix (R-14) OP482GS-REEL7 −40°C to +85°C 14-Lead SOIC_N S-Suffix (R-14) OP482GSZ −40°C to +85°C 14-Lead SOIC_N S-Suffix (R-14) OP482GSZ-REEL −40°C to +85°C 14-Lead SOIC_N S-Suffix (R-14) OP482GSZ-REEL7 −40°C to +85°C 14-Lead SOIC_N S-Suffix (R-14) 1 Z = RoHS Compliant Part. ©1991–2013 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D00301-0-9/13(I) Rev. I | Page 16 of 16

Datasheet下载

Datasheet下载