ICGOO在线商城 > 集成电路(IC) > 时钟/计时 - 可编程计时器和振荡器 > LTC6909IMS#PBF

- 型号: LTC6909IMS#PBF

- 制造商: LINEAR TECHNOLOGY

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

LTC6909IMS#PBF产品简介:

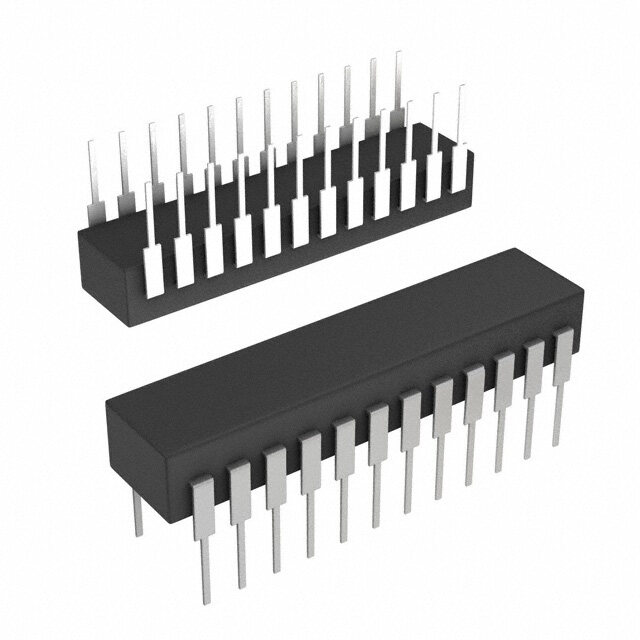

ICGOO电子元器件商城为您提供LTC6909IMS#PBF由LINEAR TECHNOLOGY设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 LTC6909IMS#PBF价格参考。LINEAR TECHNOLOGYLTC6909IMS#PBF封装/规格:时钟/计时 - 可编程计时器和振荡器, Oscillator, Silicon IC 12.5kHz ~ 6.67MHz 16-MSOP。您可以下载LTC6909IMS#PBF参考资料、Datasheet数据手册功能说明书,资料中有LTC6909IMS#PBF 详细功能的应用电路图电压和使用方法及教程。

LTC6909IMS#PBF是Linear Technology(现已被Analog Devices收购)生产的一款可编程计时器和振荡器。它属于时钟/计时器件,具有广泛的应用场景,尤其适用于需要精确、灵活定时控制的系统中。 应用场景: 1. 通信设备: - 在通信系统中,LTC6909IMS#PBF可以用于生成精确的时钟信号,确保数据传输的同步性和稳定性。例如,在基站、路由器和交换机等设备中,它可以提供稳定的时钟源,支持多种通信协议。 2. 工业自动化: - 工业控制系统通常需要高精度的定时功能来协调不同设备的操作。LTC6909IMS#PBF可以用于PLC(可编程逻辑控制器)、伺服驱动器和传感器接口等设备中,确保各个组件在正确的时间点执行任务。 3. 消费电子产品: - 在智能家居、智能手表、健身追踪器等消费电子产品中,LTC6909IMS#PBF可以作为内部时钟源,提供准确的时间基准。它还可以用于音频设备中的采样率同步,确保音频信号的质量。 4. 医疗设备: - 医疗仪器如心电图仪、血压计和其他监测设备需要高精度的定时功能。LTC6909IMS#PBF可以为这些设备提供稳定的时间基准,确保测量结果的准确性。 5. 汽车电子: - 在汽车电子系统中,LTC6909IMS#PBF可以用于发动机控制单元(ECU)、车身控制系统和车载娱乐系统等。它能够提供精确的时钟信号,确保各个子系统的协同工作。 6. 测试与测量设备: - 测试仪器如示波器、频谱分析仪等需要高精度的时钟源来确保测量的准确性。LTC6909IMS#PBF可以为这些设备提供稳定的时钟信号,提高测量的可靠性和精度。 7. 电源管理: - 在电源管理系统中,LTC6909IMS#PBF可以用于控制开关电源的工作频率,优化电源效率并减少电磁干扰(EMI)。它还可以用于电池管理系统中的定时功能,确保电池充放电的安全性和可靠性。 总之,LTC6909IMS#PBF凭借其高精度、低功耗和灵活性,适用于各种需要精确定时控制的应用场景,特别是在对时钟信号要求严格的领域中表现出色。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC) |

| 描述 | IC OSC SILICON PROG 16-MSOP |

| 产品分类 | |

| 品牌 | Linear Technology |

| 数据手册 | http://www.linear.com/docs/27567 |

| 产品图片 |

|

| 产品型号 | LTC6909IMS#PBF |

| rohs | 无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | - |

| 产品目录绘图 |

|

| 产品目录页面 | |

| 供应商器件封装 | 16-MSOP |

| 其它名称 | LTC6909IMSPBF |

| 包装 | 管件 |

| 安装类型 | 表面贴装 |

| 封装/外壳 | 16-TFSOP(0.118",3.00mm 宽) |

| 工作温度 | -40°C ~ 85°C |

| 标准包装 | 37 |

| 电压-电源 | 2.7 V ~ 5.5 V |

| 电流-电源 | 2.4mA |

| 类型 | 振荡器 - 硅 |

| 计数 | - |

| 频率 | 12.5kHz ~ 6.67MHz |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

LTC6909 1 to 8 Output, Multiphase Silicon Oscillator with Spread Spectrum Modulation FeAtures Description n 1-, 2-, 3-, 4-, 5-, 6-, 7- or 8-Phase Outputs The LTC®6909 is an easy to use precision oscillator that n One External Resistor Sets the Output Frequency can provide 1-, 2-, 3-, 4-, 5-, 6-, 7- or 8-phase synchro- from 12.5kHz to 6.67MHz nized outputs. The LTC6909 also offers spread spectrum n Optional Spread Spectrum Frequency for Improved frequency modulation (SSFM), which can be enabled to im- EMI Performance prove electromagnetic compatibility (EMC) performance. n ±10% Frequency Spreading Eight separate outputs provide up to eight rail-to-rail, n Outputs Can Be Held Low or Floated (Hi-Z) 50% duty cycle clock signals. Using three logic inputs, the n Three Spread Spectrum Modulation Rates outputs are configured for phase separation, ranging from f /16, f /32 and f /64 OUT OUT OUT 45° to 120° (three to eight phases). The clock outputs can n 400µA Supply Current also be held low or configured for Hi-Z. A single resistor, n Operates from a Single 2.7V to 5.5V Supply combined with the phase configuration, sets the output n Fast Start-Up Time frequency, based on the following formula: n First Cycle Accurate f = 20MHz • 10k/(R • PH) n Outputs Are High Impedance Until Frequency Settles OUT SET n MS16 Package where PH = 3, 4, 5, 6, 7 or 8 The LTC6909 can be used in applications requiring only ApplicAtions one or two output phases. Alternatively, the LTC6908 family of parts provides the same two output signals but n Synchronizing Multiple Switching Power Supplies in a smaller SOT-23 or 2mm × 3mm DFN package. The L, LT, LTC, LTM, Linear Technology, the Linear logo and µModule are registered trademarks LTC6908-1 provides complimentary (180°) outputs while and ThinSOT is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents including 6342817, 6614313, the LTC6908-2 provides quadrature (90°) outputs. 7417509. typicAl ApplicAtion 150kHz to 30MHz Output Frequency Spectrum Providing a 4-Phase Synchronizing Clock to LTM Modules (9kHz Res BW) 0 10V TO 14V SSFM DISABLED Bc)–10 0.1µF V+DLTC690O9UT1 INLTTVMC4C601 S0FT-START 1.5V UTPUT (d––2300 GND OUT2 TRACKING 48A O–40 V+A OUT3 LTM4601-1 –50 71.5k 0.1µF SET OUT4 0 SSFM ENABLED PPHH01 OOUUTT56 LTM4601-1 TRACKING Bc)–10 SSFM = fOUT/32 PH2 OUT7 UT (d–20 MOD OUT8 TRACKING UTP–30 LTM4601-1 O–40 ENABLE SSFM DISABLE SSFM 6909 TA01 –51050kHz 30MHz FREQUENCY 0.01µF (FUNDAMENTAL AND HARMONICS SHOWN) 6909 TA01b 6909fa 1

LTC6909 Absolute MAxiMuM rAtings pin conFigurAtion (Note 1) Supply Voltage (V+A) to GND ......................................6V TOP VIEW Supply Voltage (V+D) to GND ......................................6V V+A 1 16 SET GND 2 15 PH2 Maximum Voltage PH0 3 14 MOD on Any Pin ................(GND – 0.3V) ≤ VPIN ≤ (V+ + 0.3V) OPUHT11 45 1132 OV+UDT8 OUT2 6 11 OUT7 Operating Temperature Range (Note 2) OUT3 7 10 OUT6 LTC6909C ............................................–40°C to 85°C OUT4 8 9 OUT5 MS PACKAGE LTC6909I .............................................–40°C to 85°C 16-LEAD PLASTIC MSOP LTC6909H ..........................................–40°C to 125°C TJMAX = 150°C, θJA = 125°C/W Specified Temperature Range (Note 3) LTC6909C ................................................0°C to 70°C LTC6909I .............................................–40°C to 85°C LTC6909H ..........................................–40°C to 125°C Junction Temperature ...........................................150°C Storage Temperature Range ..................–65°C to 150°C Lead Temperature (Soldering, 10 sec) ...................300°C orDer inForMAtion LEAD FREE FINISH TAPE AND REEL PART MARKING* PACKAGE DESCRIPTION SPECIFIED TEMPERATURE RANGE LTC6909CMS#PBF LTC6909CMS#TRPBF 6909 16-Lead Plastic MSOP 0°C to 70°C LTC6909IMS#PBF LTC6909IMS#TRPBF 6909 16-Lead Plastic MSOP –40°C to 85°C LTC6909HMS#PBF LTC6909HMS#TRPBF 6909 16-Lead Plastic MSOP –40°C to 125°C Consult LTC Marketing for parts specified with wider operating temperature ranges. *The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts. For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/ electricAl chArActeristics The l denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T = 25°C or as noted. Test conditions are V+ = V+A = V+D = 2.7V to 5.5V, R = 5k, A L C = 5pF unless otherwise noted. The modulation is turned off (MOD is connected to OUT1) and PH = 8 unless otherwise specified. L R is defined as the resistor connected from the SET pin to the V+A pin. SET SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS ΔfMASTER Frequency Accuracy (Notes 4, 5) V+ = 5V 500kHz ≤ fMASTER ≤ 10MHz ±1 ±2.5 % PH = 3 500kHz ≤ f ≤ 10MHz l ±2.5 ±3 % MASTER 100kHz ≤ f < 500kHz l ±3 ±4.5 % MASTER 10MHz ≤ f ≤ 20MHz l ±2.7 ±3.5 % MASTER V+ = 2.7V 500kHz ≤ f ≤ 10MHz ±0.5 ±2.5 % MASTER PH = 3 500kHz ≤ f ≤ 10MHz l ±2 ±3 % MASTER 100kHz ≤ f < 500kHz l ±2.5 ±4.5 % MASTER ΔfOUT/ΔT Frequency Drift Over Temperature RSET = 100k l ±0.004 %/°C ΔfOUT/ΔV+ Frequency Drift Over Supply V+ = 4.5V to 5.5V, RSET = 100k l 0.4 0.9 %/V V+ = 2.7V to 3.6V, R = 100k l 0.04 0.35 %/V SET 6909fa 2

LTC6909 electricAl chArActeristics The l denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T = 25°C or as noted. Test conditions are V+ = V+A = V+D = 2.7V to 5.5V, R = 5k, A L C = 5pF unless otherwise noted. The modulation is turned off (MOD is connected to OUT1) and PH = 8 unless otherwise specified. L R is defined as the resistor connected from the SET pin to the V+A pin. SET SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS R Range of the R Resistor 4.5V ≤ V+ ≤ 5.5V 10 2000 kΩ SET SET Connected Between the V+A Pin and 2.7V ≤ V+ ≤ 4.5V 20 2000 kΩ the SET Pin Frequency Spread with SSFM R = 100k l ±7 ±10 ±13 % SET Enabled MOD Pin = V+, GND or Open Long-Term Stability of the Output 300 ppm/√kHr Frequency (Note 9) Duty Cycle (Note 6) SSFM Disabled l 45 50 55 % V+A, V+D Operating Supply Voltage Range l 2.7 5.5 V I V+ Combined Supply Current R = 2M, R = ∞, PH = 8, MOD = V+, S SET L (f = 12.5kHz), SSFM = f /64 OUT OUT V+ = 5V l 0.6 0.85 mA V+ = 2.7V l 0.55 0.8 mA R = 20k, R = ∞, PH = 3, MOD = GND, SET L (f = 3.33MHz), SSFM = f /16 OUT OUT V+ = 5V l 2.4 2.7 mA V+ = 2.7V l 1.55 1.8 mA R = 2M, R = ∞, PH = 8, MOD = OUT1, SET L (f = 12.5kHz), SSFM Off OUT V+ = 5V l 0.4 0.65 mA V+ = 2.7V l 0.37 0.6 mA V High Level MOD Input Voltage l V+ – 0.4 V IH_MOD V Low Level MOD Input Voltage l 0.4 V IL_MOD I MOD Input Current (Note 7) MOD Pin = V+, V+ = 5V l 2 4 µA MOD MOD Pin = GND, V+ = 5V l –4 –2 µA V High Level PHx Input Voltage PHx Refers to PH0, PH1 and PH2 l V+ – 0.4 V IH_PH V Low Level PHx Input Voltage PHx Refers to PH0, PH1 and PH2 l 0.4 V IL_PH I Digital Input Current, PH0, PH1, PH2 0V < V < V+ l ±1 µA IN_PHX IN V High Level Output Voltage V+ = 5V No Load 4.92 V OH (OUT1 Through OUT8)(Note 7) 5mA Load to GND l 4.35 4.65 V V+ = 2.7V No Load 2.63 V 3mA Load to GND l 2.1 2.4 V V Low Level Output Voltage V+ = 5V No Load 0.07 V OL (OUT1 Through OUT8)(Note 7) 5mA Load to V+ l 0.25 0.55 V V+ = 2.7V No Load 0.07 V 3mA Load to V+ l 0.25 0.55 V t Output Rise Time (Note 8) V+ = 5V 1.6 ns r V+ = 2.7V 2.5 ns t Output Fall Time (Note 8) V+ = 5V 1.6 ns f V+ = 2.7V 2 ns Note 1: Stresses beyond those listed under Absolute Maximum Ratings Note 3: The LTC6909C is guaranteed to meet specified performance from may cause permanent damage to the device. Exposure to any Absolute 0°C to 70°C. The LTC6909C is designed, characterized and expected to Maximum Rating condition for extended periods may affect device meet specified performance from –40°C to 85°C but is not tested or QA reliability and lifetime. sampled at these temperatures. The LTC6909I is guaranteed to meet Note 2: LTC6909C and the LTC6909I are guaranteed functional over the specified performance from –40°C to 85°C. The LTC6909H is guaranteed operating temperature range of –40°C to 85°C. to meet specified performance from –40°C to 125°C. 6909fa 3

LTC6909 electricAl chArActeristics Note 4: f is the internal master oscillator frequency. The output Note 9: Long term drift on silicon oscillators is primarily due to the MASTER frequency is f /PH. The PH value is determined by the connections movement of ions and impurities within the silicon and is tested at 30°C MASTER of the PH0, PH1 and PH2 pins as described in the Applications Information under otherwise nominal operating conditions. Long term drift is specified section. as ppm/√kHr due to the typically nonlinear nature of the drift. To calculate Note 5: Frequency accuracy is defined as the deviation from the f drift for a set time period, translate that time into thousands of hours, take OUT equation. f = 20MHz • 10k/R , f = 20MHz • 10k/(R • PH), the square root and multiply by the typical drift number. For instance, a MASTER SET OUT SET PH = 3, 4, 5, 6, 7 or 8. year is 8.77kHr and would yield a drift of 888ppm at 300ppm/√kHr. Drift without power applied to the device (aging) may be approximated as Note 6: Guaranteed by 5V test. 1/10th of the drift with power, or 30ppm/√kHr for a 300ppm/√kHr device. Note 7: To conform to the Logic IC Standard, current out of a pin is defined as a negative value. Note 8: Output rise and fall times are measured between the 10% and the 90% power supply levels with no output loading. These specifications are based on characterization. typicAl perForMAnce chArActeristics Frequency Error vs R , V+ = 2.7V Frequency Error vs R , V+ = 5V Frequency Error vs Temperature SET SET 5 5 1.00 4 GUARANTEED MAX TA = 25°C 4 TA = 25°C OVER TEMPERATURE 0.75 3 3 %) %) GUARANTEED MAX %) 0.50 R ( 2 R ( 2 OVER TEMPERATURE R ( RO 1 TYPICAL MAX RO 1 TYPICAL MAX RO 0.25 R R R Y E 0 Y E 0 Y E 0 TYPICAL MAX C C C UEN –1 TYPICAL MIN UEN –1 UEN–0.25 FREQ –2 FREQ –2 TYPICAL MIN GOUVEARR ATNEMTEPEEDR MATINURE FREQ–0.50 –3 –3 –4 GUARANTEED MIN –4 –0.75 TYPICAL MIN OVER TEMPERATURE –5 –5 –1.00 10k 100k 1M 10M 10k 100k 1M 10M –40 –20 0 20 40 60 80 RSET (Ω) RSET (Ω) TEMPERATURE (°C) 6909 G01 6909 G02 6909 G03 Supply Current Supply Current Supply Current vs Supply Voltage vs R (SSFM Enabled) vs R (SSFM Disabled) SET SET 1800 3000 3000 PH = 3, SSFM ENABLED CLOAD = 5pF CLOAD = 5pF 1600 CLOAD = 5pF V+ = 5V, PH = 3 V+ = 5V, PH = 3 RLOAD = 5k RLOAD = 5k 2500 2500 A)1400 RSET = 20k V+ = 5V, PH = 8 NT (µ1200 A)2000 A)2000 V+ = 5V, PH = 8 PPLY CURRE1806000000 RSET = 100k RSET = 400k I (µSUPPLY11050000 V+ = 2.7V, PH = 3 I (µSUPPLY11050000 V+ = 2.7V, PH = 3 U S 400 200 RSET = 2M 500 V+ = 2.7V, PH = 8 500 V+ = 2.7V, PH = 8 0 0 0 2.7 3.2 3.7 4.2 4.7 10k 100k 1M 10M 10k 100k 1M 10M SUPPLY VOLTAGE (V) RSET (Ω) RSET (Ω) 6909 G04 6909 G05 6909 G06 6909fa 4

LTC6909 typicAl perForMAnce chArActeristics Typical Output Resistance Output Rise/Fall Time Supply Current vs Temperature vs Supply Voltage vs Supply Voltage 700 110 4.5 CLOAD = 5pF 100 4.0 TA = 25°C RENT (µA)660500 V+ = 5V STANCE (Ω) 789000 ALL TIME (ns) 332...505 RLORAISD E= T5IkME PPLY CUR550500 V+ = 2.7V PUT RESI 5600 UT RISE/F 21..05 FALL TIME U T P S U T RSET = 100k O 40 OU 1.0 450 PH = 3 CLOAD = 5pF 30 0.5 SSFM DISABLED 400 20 0 –40 –20 0 20 40 60 80 100 120 2.8 3 3.23.4 3.63.8 4 4.2 4.4 4.6 4.8 5 2.7 3.2 3.7 4.2 4.7 5.2 TEMPERATURE (°C) SUPPLY VOLTAGE (V) SUPPLY VOLTAGE (V) 6909 G09 6909 G07 6909 G08 Jitter vs R Output Operating at 3.33MHz SET 1.2 CLOAD = 5pF 1.0 V+ = 5V, DIV = 3 500mV/DIV P-P) 0.8 V+ = 2.7V, DIV = 3 % R ( 0.6 E T T JI 0.4 50ns/DIV V+ = 5V, DIV = 8 V+ = 3.3V 6909 G11 0.2 CLOAD = 15pF V+ = 2.7V, DIV = 8 RLOAD = 5k 0 10k 100k 1M 10M RSET (Ω) 6909 G10 Output Frequency Spectrum Output Operating at 6.66MHz SSFM Enable and Disabled 0 RES BW = 9kHz SSFM ENABLED (N = 16) V 1V/DIV DI B/ d 0 1 SSFM DISABLED –100 50ns/DIV 2.5 MHz V+ = 5V 6909 G12 FREQUENCY (200kHz/DIV) CLOAD = 15pF 6909 G13 RLOAD = 5k 6909fa 5

LTC6909 pin Functions V+A (Pin 1): Analog Voltage Supply (2.7V ≤ V+A ≤ 5.5V). part’s internal frequency setting loop has settled, the out- This supply should be kept free of noise and ripple. It puts are active, clean and operating at the set frequency should be bypassed directly to GND with a 0.1µF or greater (first cycle accurate). low ESR capacitor. V+A and V+D must be connected to the V+D (Pin 13): Digital Voltage Supply (2.7V ≤ V+D ≤ 5.5V). same supply voltage. This pin should be bypassed directly to GND with a 0.1µF GND (Pin 2): Ground Connections. Should be tied to a or greater low ESR capacitor. V+D and V+A must be con- ground plane for best performance. nected to the same supply voltage. PH0, PH1, PH2 (Pins 3, 4, 15): Output Phasing Selec- MOD (Pin 14): Spread Spectrum Frequency Modulation tion Pins. These are standard CMOS logic input pins and Setting Input. This input selects among four modulation they do not have an internal pull-up or pull-down. These rate settings. The MOD pin should be tied to ground for pins must be connected to a valid logic input 0 or 1 volt- an f /16 modulation rate. Floating the MOD pin selects OUT age. Connect the pins to GND for a logic 0 and to the V+D an f /32 modulation rate. The MOD pin should be tied OUT pin for a logic 1. These pins configure the output phase to V+D for the f /64 modulation rate. Tying one of the OUT relationships as follows: active outputs to the MOD pin turns the modulation off. To detect a floating MOD pin, the LTC6909 attempts to PH2 PH1 PH0 MODE pull the pin to the midsupply point. This is realized with 0 0 0 All Outputs Are Floating (Hi-Z) two internal current sources, one tied to V+D and MOD 0 0 1 All Outputs Are Held Low and the other one tied to GND and MOD. Therefore, driv- 0 1 0 3-Phase Mode (PH = 3) ing the MOD pin high requires sourcing approximately 0 1 1 4-Phase Mode (PH = 4) 2µA. Likewise, driving the MOD pin low requires sinking 1 0 0 5-Phase Mode (PH = 5) approximately 2µA. When the MOD pin is floated for the 1 0 1 6-Phase Mode (PH = 6) f /32 modulation rate, it must be bypassed using a OUT 1 1 0 7-Phase Mode (PH = 7) 1nF or larger, capacitor to GND. Any AC signal coupling 1 1 1 8-Phase Mode (PH = 8) to the MOD pin could potentially be detected and stop the frequency modulation. The PH0, PH1, PH2 pin connections not only determine SET (Pin 16): Frequency Setting Resistor Input. The value the phase relationship of the output signals but also divide of the resistor connected between this pin and V+A deter- the master oscillator frequency by the value PH. mines the frequency of the master oscillator. The output OUT1 Through OUT8 (Pins 5 Through 12): Oscillator frequency, f , is the master oscillator frequency divided OUT Outputs. These are CMOS rail-to-rail logic outputs with by PH as set by the PH0, PH1 and PH2 pin connections. a series resistance of approximately 40Ω, capable of The voltage on this pin is held approximately 1.1V below driving 1k and/or 50pF loads. Larger loads may cause V+A. For best performance, use a precision metal film minor frequency inaccuracies due to supply bounce at resistor with a value between 20k and 400k, and limit the high frequencies. When any output pin is not in use, it is capacitance on the pin to less than 10pF. Resistor values in a floating, high impedance state. The outputs are also outside of this range will have some loss of accuracy as held in a high impedance state during start-up. After the noted in the Electrical Characteristics table. 6909fa 6

LTC6909 block DiAgrAM PH0 PH1 PH2 V+D 3 4 15 13 (fMSSASFMTE R= =O F2F0)MHz • 10k • VI+M –AS VTSEERT = 20MHz • 10k/RSET V+A 1 + MASTER DRIVER 5 OUT1 OSCILLATOR RSET V DRIVER 6 OUT2 16 VSET – OUT SET DRIVER 7 OUT3 VBIAS ISET = V+ R–S VESTET 1 LPPOFLE IMASTER PDOHRUAITVSPEIUNRTGS DRIVER 8 OUT4 DRIVER 9 OUT5 IREF DRIVER 10 OUT6 MDAC DRIVER 11 OUT7 DRIVER 12 OUT8 V+ OUTPUT PSEUDORANDOM Hi-Z + CODE GENERATOR UNTIL – POR STABLE DIVIDE BY MOD 14 3-STATE 16/32/64 INPUT DECODER + DETECT WHEN A CLOCK SIGNAL IS PRESENT AT THE – CLOCK INPUT MOD PIN INPUT, THE MODULATION IS DISABLED GND 2 GND 6909 BD 6909fa 7

LTC6909 operAtion As shown in the Block Diagram, the LTC6909’s master When the spread spectrum frequency modulation (SSFM) oscillator is controlled by the ratio of the voltage between is disabled, the master oscillator frequency is stationary. the V+A and SET pins and the current entering the SET pin When SSFM is enabled, the master oscillator frequency (I ). When the spread spectrum frequency modula- varies from 0.9 • f to 1.1 • f . MASTER MASTER MASTER tion (SSFM) is disabled, I is strictly determined by MASTER the (V+A – V ) voltage and the R resistor. When SSFM Output Frequency and Configurations SET SET is enabled, I is modulated by a filtered pseudoran- MASTER The output frequency of the LTC6909 is set by the R SET dom noise (PRN) signal. Here the I current is a MASTER resistor value and the connections of the PH0, PH1 and random value uniformly distributed between (I – 10%) SET PH2 logic input pins. The following formula defines the and (I + 10%). In this way, the frequency is modulated SET relationship: to produce an approximately flat frequency spectrum, f = 20MHz • 10k/(R • PH) centered about the set frequency with a bandwidth equal OUT SET to approximately 20% of the center frequency. where PH = 3, 4, 5, 6, 7 or 8 and is defined as follows: The voltage on the SET pin is forced to approximately 1.1V PH2 PH1 PH0 MODE below V+A by the PMOS transistor and its gate bias volt- 0 0 0 All Outputs Are Floating (Hi-Z) age. This voltage is accurate to ±5% at a particular input 0 0 1 All Outputs Are Held Low current and supply voltage (see Figure 1). The LTC6909 0 1 0 3-Phase Mode (PH = 3) is optimized for use with resistors between 20k and 400k 0 1 1 4-Phase Mode (PH = 4) corresponding to master oscillator frequencies between 1 0 0 5-Phase Mode (PH = 5) 500kHz and 10MHz. Accurate master oscillator frequen- 1 0 1 6-Phase Mode (PH = 6) cies up to 20MHz (R = 10k) are attainable if the supply SET 1 1 0 7-Phase Mode (PH = 7) voltage is greater than 4V. The R resistor, connected SET 1 1 1 8-Phase Mode (PH = 8) between the V+A and SET pins, locks together the (V+A – V ) voltage and the current I . This allows the parts SET SET The PH0, PH1 and PH2 pins are standard logic input pins. to attain excellent frequency accuracy regardless of the These pins do not have any active pull-up or pull-down precision of the SET pin. The master oscillation frequency is: circuitry. As such, they cannot be left floating and must be f = 20MHz • 10k/R connected to a valid logic high or low voltage. The PH0, MASTER SET PH1 and PH2 pin connections not only divide the master 1.4 oscillator frequency by the value PH but also determine TA = 25°C the phase relationship between the output signals. Figure 1.3 2 shows the output waveforms for each of the eight pos- sible output configurations. VSET 1.2 V+ = 5V +V – 1.1 Note that 2-phase, complementary (180° phase shifted) = S V+ = 3V outputs are available in the 4-, 6- and 8-phase modes RE V 1.0 by choosing the correct pair of signals. For example, in 4-phase mode, OUT1 and OUT3 (or OUT2 and OUT4) are 0.9 complementary. 0.8 0.1 1 10 100 1000 IRES (µA) 6909 F01 Figure 1. V+ – V Variation with I SET RES 6909fa 8

LTC6909 operAtion MASTER OSCILLATOR PH2 - PH1 - PH0 = 000 ALL OUTPUTS ARE Hi-Z PH2 - PH1 - PH0 = 001 ALL OUTPUTS ARE LOW PH2 - PH1 - PH0 = 010 PH = 3, fOUTPUT = fMASTER/3 ADJACENT OUTPUTS ARE PHASE SHIFTED BY 120° OUT1 OUT2 OUT3 OUT4 Hi-Z OUT5 Hi-Z OUT6 Hi-Z OUT7 Hi-Z OUT8 Hi-Z PH2 - PH1 - PH0 = 011 PH = 4, fOUTPUT = fMASTER/4 ADJACENT OUTPUTS ARE PHASE SHIFTED BY 90° OUT1 OUT2 OUT3 OUT4 OUT5 Hi-Z OUT6 Hi-Z OUT7 Hi-Z OUT8 Hi-Z PH2 - PH1 - PH0 = 100 PH = 5, fOUTPUT = fMASTER/5 ADJACENT OUTPUTS ARE PHASE SHIFTED BY 72° OUT1 OUT2 OUT3 OUT4 OUT5 OUT6 Hi-Z OUT7 Hi-Z OUT8 Hi-Z PH2 - PH1 - PH0 = 101 PH = 6, fOUTPUT = fMASTER/6 ADJACENT OUTPUTS ARE PHASE SHIFTED BY 60° OUT1 OUT2 OUT3 OUT4 OUT5 OUT6 OUT7 Hi-Z OUT8 Hi-Z 6909 F02a Figure 2a. Output Waveforms for Different PH Settings 6909fa 9

LTC6909 operAtion MASTER OSCILLATOR PH2 - PH1 - PH0 = 110 PH = 7, fOUTPUT = fMASTER/7 ADJACENT OUTPUTS ARE PHASE SHIFTED BY 51.43° OUT1 OUT2 OUT3 OUT4 OUT5 OUT6 OUT7 OUT8 Hi-Z PH2 - PH1 - PH0 = 111 PH = 8, fOUTPUT = fMASTER/8 ADJACENT OUTPUTS ARE PHASE SHIFTED BY 45° OUT1 OUT2 OUT3 OUT4 OUT5 OUT6 OUT7 OUT8 6909 F02b Figure 2b. Output Waveforms for Different PH Settings 6909fa 10

LTC6909 operAtion Spread Spectrum Frequency Modulation is generated by a linear feedback shift register that is 15 bits long. The pseudorandom sequence will repeat every The LTC6909 can operate with spread spectrum frequency (215 – 1) • N clock cycles. This guarantees a repetition modulation (SSFM). In this mode, the oscillator’s frequency rate below 13Hz for output frequencies up to 6.67MHz. is modulated by a pseudorandom noise (PRN) signal Seven bits of the shift register are sent in parallel to the to spread the oscillator’s energy over a wide frequency MDAC which produces the modulating current waveform. band. This spreading decreases the peak electromagnetic Being a digitally generated signal, the output of the MDAC radiation levels and improves electromanetic compatibility is not a perfectly smooth waveform, but consists of (27) (EMC) performance. discrete steps that change every shift register clock cycle. The amount of frequency spreading is fixed at 20% (±10%), Note that the shift register clock is the output frequency, where frequency spreading is defined as: f , divided by N, where N is the modulation rate divider OUT Frequency Spreading (in %) = 100 • (f – f )/f setting, which is determined by the state of the MOD pin. MAX MIN OUT The MOD pin should be tied to ground for the N = 16 set- The I current is a dynamic signal generated by MASTER ting. Floating the MOD pin selects N = 32. The MOD pin a multiplying digital-to-analog converter (MDAC) refer- should be tied to V+ for the N = 64 setting. enced to I and lowpass filtered. I varies in a SET MASTER psuedorandom noise-like manner between 0.9 • I and The output of the MDAC is then filtered by a lowpass filter SET 1.1 • I . This causes the output frequency to vary in a with a corner frequency set to the modulation rate (f /N). SET OUT pseudorandom noise-like manner between 0.9 • f and This limits the rate of frequency change and softens the OUT 1.1 f . corners of the frequency control signal, but allows the OUT waveform to fully settle at each frequency step. The rise To disable the SSFM, connect one of the active outputs and fall times of this single pole filter are approximately to the MOD pin. An AC detector circuit shuts down the 0.35/f . This is beneficial for clocking switching modulation circuitry if a frequency in the vicinity of the CORNER regulators, as discussed in the Applications Information output frequency is detected at the MOD pin. section. Figure 3 illustrates how the output frequency As stated previously, the modulating waveform is a pseu- varies over time. dorandom noise-like waveform. The pseudorandom signal fOUT + 10% Y C 128 STEPS N E U Q E R F fOUT – 10% tSTEP tSTEP = N/fOUT tREPEAT tREPEAT = ((215 – 1) • N)/fOUT TIME 6909 F03 Figure 3 6909fa 11

LTC6909 ApplicAtions inForMAtion SELECTING THE FREqUENCY-SETTING RESISTOR CBYP V+ V+A The LTC6909 has a master oscillator frequency range spanning 100kHz to 20MHz depending on the RSET resis- VCONTROL –+ GND tor value. However, accuracy may suffer if the oscillator is operated at a master oscillator frequency greater than SET RSET 10MHz with a supply voltage lower than 4V. With a linear 6909 F05 correspondence between the master oscillator period and fOUT = 10k • 20MHz/RSET(1 – VCONTROL/1.13V) the R resistance, a simple equation relates resistance SET Figure 5. Voltage Controlled Oscillator with frequency. the relationship between the input current and the volt- R =10k • 20MHz/f SET MASTER age between V+ and SET; the frequency accuracy will be R = 10k (5V supply), 20k (2.7V supply), degraded. The oscillator frequency, however, will increase SETMIN monotonically with decreasing V . R = 2M CONTROL SETMAX Any R resistor tolerance will shift the output frequency SET SETTING THE MODULATION RATE OF THE LTC6909 by the same amount. The modulation rate of the LTC6909 is equal to f /N, OUT where N is the modulation rate divider setting, which is ALTERNATIVE METHODS OF SETTING THE OUTPUT determined by the state of the MOD pin. The MOD pin should FREqUENCY OF THE LTC6909 be tied to ground for the N = 16 setting. Floating the MOD The oscillator may be programmed by any method that pin selects N = 32. The MOD pin should be tied to V+ for sources a current into the SET pin. The circuit in Figure 4 the N = 64 setting. To disable the SSFM, connect one of sets the oscillator frequency using a programmable current the active outputs to the MOD pin. An AC detector circuit source and in the expression for fOUT, the resistor RSET is shuts down the modulation circuitry if a frequency that is replaced by the ratio of 1.1V/I . As already explained CONTROL close to the output frequency is detected at the MOD pin. in the Operation section, the voltage difference between V+ and SET is approximately 1.1V ±5%, therefore, the When the MOD pin is floated, for the fOUT/32 modulation rate, it must be bypassed by at least a 1nF capacitor Figure 4 circuit is less accurate than if a resistor controls to GND. Any AC signal coupling to the MOD pin could the output frequency. potentially be detected and stop the frequency modulation. CBYP V+ V+A DRIVING LOGIC CIRCUITS The outputs of the LTC6909 are suitable for driving gen- ICONTROL GND eral digital logic circuits. However, the form of frequency SET spreading used in the LTC6909 may not be suitable for 6909 F04 many logic designs. Many logic designs have fairly tight fMASTER = 10k • (20MHz/1.13V) • ICONTROL(A) timing and cycle-to-cycle jitter requirements. These sys- tems often benefit from a spread spectrum clocking system Figure 4. Current Controlled Oscillator where the frequency is slowly and linearly modulated by a triangular waveform, not a pseudorandom waveform. This Figure 5 shows the LTC6909 configured as a V . A volt- CO type of frequency spreading maintains a minimal difference age source is connected in series with an external 10k in the timing from one clock edge to the next adjacent resistor. The master oscillator frequency, f , will MASTER clock edge (cycle-to-cycle jitter). The LTC6909 uses a vary with V , that is the voltage source connected CONTROL pseudorandom modulating signal where the frequency between V+ and the SET pin. Again, this circuit decouples 6909fa 12

LTC6909 ApplicAtions inForMAtion transitions have been slowed and the corners rounded the modulation rate divider setting, which is determined by a first order lowpass filter with a corner frequency set by the state of the MOD pin. The MOD pin should be tied to the modulation rate (f /N), where N is the modula- to ground for the N = 16 setting. Floating the MOD pin OUT tion rate divider setting, which is determined by the state selects N = 32. The MOD pin should be tied to V+ for the of the MOD pin. This filtered modulating signal may be N = 64 setting. This is an important feature when driving acceptable for many logic systems but the cycle-to-cycle a switching regulator. The switching regulator is itself jitter issues must be considered carefully. a servo loop with a bandwidth typically on the order of 1/10 to 1/20 of the operating frequency. When the clock frequency’s transition is within the bandwidth of the switch- DRIVING SWITCHING REGULATORS ing regulator, the regulator’s output stays in regulation. If The LTC6909 is designed primarily to provide an accurate the transition is too sharp, beyond the bandwidth of the and stable clock for switching regulator systems. The switching regulator, the regulator’s output will experience CMOS logic outputs are suitable for directly driving most a sharp jump and then settle back into regulation. If the switching regulators and switching controllers. Linear bandwidth of the regulator is sufficiently high, beyond Technology has a broad line of fully integrated switching f /N, then there will not be any regulation issues. OUT regulators and switching regulator controllers designed One aspect of the output voltage that will change is the for synchronization to an external clock. All of these output ripple voltage. Every switching regulator has some parts have one pin assigned for external clock input. The output ripple at the clock frequency. For most switching nomenclature varies depending on the part’s family his- regulator designs with fixed MOSFET’s, fixed inductor, tory. SYNC, PLLIN, SYNC/MODE, EXTCLK, FCB and S/S fixed capacitors, the amount of ripple will vary with the (shorthand for SYNC/SHDN) are examples of clock input regulator’s operating frequency (the main exception be- pin names used with Linear Technology ICs. ing hysteretic architecture regulators). An increase in For the best EMC performance, the LTC6909 should be run frequency results in lower ripple and a frequency decrease with the MOD pin tied to ground (SSFM enabled, modula- gives more ripple. This is true for static frequencies or tion rate set to f /16). Regulatory testing is done with OUT dynamic frequency modulated systems. If the modulating strictly specified bandwidths and conditions. Modulating signal was a triangle wave, the regulator’s output would faster than, or as close to, the test bandwidth as possible have a ripple that is amplitude modulated by the triangle gives the lowest readings. The optimal modulating rate is wave. This repetitive signal on the power supply could not as straightforward when the goal is to lower radiated cause system problems by mixing with other desired signal levels interfering with other circuitry in the system. signals creating distortion. Depending on the switching The modulation rate will have to be evaluated with the regulator’s inductor design and triangle wave frequency, specific system conditions to determine the optimal rate. it may even result in an audible noise. The LTC6909 uses Depending on the specific frequency synchronization a pseudorandom noise-like signal. On an oscilloscope, it method a switching regulator employs, the modulation looks essentially noise-like of even amplitude. The signal rate must be within the synchronization capability of the is broadband and any mixing issues are eliminated. Ad- regulator. Many regulators use a phase-locked loop (PLL) ditionally, the pseudorandom signal repeats at such a low for synchronization. For these parts, the PLL loop filter rate that it is well below the audible range. should be designed to have sufficient capture range and The LTC6909 with the spread spectrum frequency modula- bandwidth. tion enabled results in improved EMC performance. If the The frequency hopping transitions of the LTC6909 are bandwidth of the switching regulator is sufficient, not a slowed by a lowpass filter. The corner frequency of this difficult requirement in most cases, the regulator’s regula- filter is set to the modulation rate (f /N), where N is OUT tion, efficiency and load response are maintained while 6909fa 13

LTC6909 ApplicAtions inForMAtion peak electromagnetic radiation (or conduction) is reduced. multiple (three to four minimum) vias to minimize Output ripple may be somewhat increased, but its behavior inductance. is very much like noise and its system impact is benign. 2. Place the bypass capacitors, C1 and C2, as close to the V+A and V+D pins as possible to minimize the inductance SUPPLY BYPASSING, SIGNAL CONNECTIONS AND between the capacitor’s lead and the part’s pins. PCB LAYOUT 3. The connection to the V+A and V+D pins to the main Using the LTC6909 in spread spectrum mode naturally supply should be through a low impedance path. If eliminates any concerns for output frequency accuracy the board has a V+ power plane, use it instead of the and stability as it is continually hopping to new settings. top layer connection shown in Figure 6. Use multiple In fixed frequency applications however, some attention to vias (three to four minimum) at each point to connect V+ supply voltage ripple is required to minimize additional the V+A and V+D pins to the V+ plane to minimize the output frequency error. Ripple frequency components on inductance. the supply line near the programmed output frequency of 4. Connect the bypass capacitors, C1 and C2, directly to the the LTC6909 in excess of 30mV could create an addi- P-P GND pin using a low inductance path. The connection tional 0.2% of frequency error. In applications where a fixed from C1 to the GND pin is easily done directly on the top frequency LTC6909 output clock is used to synchronize layer. The C2 path is more difficult but is accomplished the same switching regulator that provides the V+ supply through multiple vias to the ground plane. to the oscillator, noticeable jitter of the clock may occur if the ripple exceeds 30mV . 5. Connect the R resistor directly to the SET pin and P-P SET the V+A pin. Connecting the resistor to the V+ supply The LTC6909’s accuracy is affected as described above through any manner other than directly to the V+A pin by supply ripple on the V+A pin only. The V+D pin is es- will result greater frequency error. sentially insensitive to supply ripple. The V+A pin supplies the power for the analog section of the LTC6909 and its 6. Provide a ground shield around the R resistor and SET current is largely constant for a given R resistor value. its connections to V+A and SET. The SET pin is a fairly SET The V+D pin supplies the digital section including the out- high impedance point and is susceptible to interference put drivers and its current requirement consists mainly of from noisy signal lines such as the part’s CMOS outputs large bursts that digital circuitry requires when switching. OUT1 through OUT8. The peak current required by the output drivers is by far 7. Route the output signals, OUT1 through OUT8, away from the largest. The current is mainly dependent on output the SET pin as soon as possible to minimize coupling. capacitive loading and the supply voltage. 8. When using the LTC6909 with spread spectrum disabled, Figure 6 shows how to connect the V+A and V+D supply an active output is connected to the MOD pin. This is pins to the power supply as well as a suggested PCB layout. best done by routing the OUT1 signal under the part The PCB layout assumes a two layer board with a ground as shown in Figure 6. The ground shield between this plane in the layer beneath the part and 0805 sized passive trace and the R resistor is very important to minimize SET components. The PCB layout in Figure 6 is a guide and coupling of the OUT1 signal into the SET pin. need not be followed exactly. However, there are several items to note from the layout as follows: 1. There should be a ground plane underneath and around the part. Connect the GND pin to this plane through 6909fa 14

LTC6909 ApplicAtions inForMAtion 9. The connections for PH0, PH1 and PH2 are not shown To assist in an orderly start-up sequence, the LTC6909’s in Figure 6. These pins are connected to either GND or outputs are in a high impedance state for the first 128 V+D depending on the output phasing required for the master clock cycles after power-up. This ensures that application. Connection to ground is done underneath the first clock cycle is very close to the desired operating the part. Connecting PH2 to V+D is also straightforward. frequency. Connecting PH0 or PH1 to V+D may require one or Powering up and down complex multiphase switching both traces to go down a layer. If you are dynamically regulator circuits is always chaotic and can have serious changing one or all of the PH pins, place a 10k resis- system consequences if it is not done carefully. In addition tor in series with the signal line. Locate the resistor to the LTC6909’s muting of the outputs to ensure first cycle fairly close to the PH pin. This signal typically comes accuracy, the PH0-PH1-PH2 codes 000 (all outputs are from a microcontroller or the power good signal from a switching regulator and is usually quite noisy. The 10000 series resistor provides some isolation between the VTA+ == 235V°C noisy signal and the LTC6909. µs)1000 Y ( START-UP ISSUES AND CONSIDERATIONS LA E D P U The start-up time and settling time to within 1% of the ART- 100 T final value is estimated by the following equation: S 25µs t ≈R • +10µs 10 START SET 1k 1k 10k 100k 1M 10M RSET (Ω) 6909 F07 For instance, with RSET = 100k, the LTC6909 will settle to Figure 7. Start-Up Time within 1% of its 1MHz final value in approximately 260µs. Figure 7 shows the start-up time for various R resistors. SET RSET C1 0.1µF LTC6909 V+A SET RSET GND PH2 C1 PH0 MOD GPRLOAUNNED PH1 V+D C2 DCOIRNENCET,C LTOIOWN ITMOP TEHDEA NVC+ E V+A SET OUT1 OUT8 0.1µF SUPPLY GND PH2 C2 GROUND PH0 MOD PLANE PH1 V+D OUT1 OUT8 OUT2 OUT7 OUT3 OUT6 OUT4 OUT5 6909 F06 Figure 6. Supply Bypassing and PCB Layout 6909fa 15

LTC6909 ApplicAtions inForMAtion high impedance) and 001 (all outputs are low) are useful LTC6909 does not have its own internal UVLO. If the for controlling the clocking of switching regulators during supply is below 2.7V, frequency accuracy may suffer. At start-up. At start-up, most switching regulators ignore the a supply voltage around 2V or lower, the LTC6909 will clock input until a power good state is achieved. Nearly operate erratically or will stop. It may stop randomly in a all of Linear Technology’s switching regulators operate in logic high or low state. this manner. However, some switching regulators from Figure 8 shows a circuit using an LTC1998 to monitor the other vendors do not ignore the clock input on start-up supply voltage and control the logic state of the PH0 and and yet are not synchronizable until the power good state PH1 pins. The LTC1998’s threshold is set at 2.5V with is reached. Attempting to synchronize these switching 50mV of hysteresis. On power-up, as the supply ramps regulators before they reach the power good state can up, the LTC1998 holds PH0 and PH1 low, keeping the lead to problems. For these switching regulators it is best LTC6909’s outputs in a high impedance state. Once the to have the LTC6909 held in the PH0-PH1-PH2 codes supply is above 2.55V, the LTC1998 pulls the PH0 and PH1 000 or 001 until the switching regulator issues a power pins high, setting the LTC6909 into the 4-phase operating good signal. In most cases, simply connecting a switch- mode. On power-down, the supply ramps down and the ing regulator’s power good signal to the PH0, PH1 and/ LTC1998’s output goes low once the supply is below 2.45V. or PH2 pins accomplishes this. At most, an additional This puts the LTC6909’s outputs in the high impedance single logic inverter is required to switch from either the state. All switch overs are synchronized to the LTC6909’s 000 or 001 states to any of the other six states through internal oscillator to avoid glitches and runt pulses. a power good signal. To adjust the on/off supply voltage threshold, change the Another way to use the PH0, PH1 and PH2 inputs to as- configuration of the LTC1998. As with the power good sist with power-up/down issues is to use an external part signal, at most an additional single logic inverter is required to provide a supply monitor or an undervoltage lockout to switch from either the 000 or 001 states to any of the (UVLO). There are several parts available that combine a other six states. comparator with a reference to fulfill this function. The V+ RSET LTC6909 1 V+A SET 16 0.1µF 2 15 GND PH2 LTC1998 1 6 3 14 BATT BATTLO PH0 MOD 0.1µF 2 GND VLOGIC 5 4 PH1 V+D 13 3 VTHA VHA 4 953k 5 OUT1 OUT8 12 0.1µF 6 11 OUT2 OUT7 7 10 49.9k OUT3 OUT6 8 9 OUT4 OUT5 6909 F08 Figure 8. Adding a UVLO Feature to the LTC6909. In This Example, the LTC6909 Is in 4-Phase Mode for a V+ > ≈2.5V (PHx = 011) and the Outputs Are All High Impedance for V+ < ≈2.5V (PHx = 000) 6909fa 16

LTC6909 typicAl ApplicAtions Simply Parallel Multiple DC/DC µModule® Regulator Systems to Achieve Higher Output Current. Board Layout Is as Easy as Copying and Pasting Each µModule Regulator’s Layout With Very Few External Components Required CLOCK SYNC VOUT = 0.6V 60N.4 R k S +E T R SET VIN 0° PHASE TRACK/SS CONTROL N = NUMBER OF PHASES 10V TO 14V 51.1k 51.1k VIN PLLINTRACK/SS VOUT PGOOD VOUT 1.5V 220pF 48A MAX MPGM VFB 22µF RUN MARG0 6.3V COMP LTM4601 MARG1 470µF+ + C1205IN0V*µF IDNRTVVCCCC VDOIVFUFOTVS_ONLUCSLT+ 6.3V VOSNS– 71.5k 1205µVF 392k SGND PGND fSET RSET 120pF ×2 10k LTC6909 5% V+A SET MARGIN MARGIN CONTROL 0.1µF GND PH2 SSFM DISABLED CLOCK SYNC PH0 MOD 90° PHASE PH1 V+D 0.1µF SSFM 4.5V TO 20V TRACK/SS CONTROL OUT1 OUT8 ENABLED OUT2 OUT7 0.01µF VIN PLLINTRACK/SS OUT3 OUT6 PGOOD VOUT OUT4 OUT5 MPGM VFB 22µF RUN MARG0 6.3V+ COMP LTM4601-1 MARG1 467.30VµF INTVCC VOUT_LCL DRVCC NC3 10µF NC2 25V 392k NC1 ×2 SGND PGND fSET CLOCK SYNC 180° PHASE 4.5V TO 20V TRACK/SS CONTROL VIN PLLINTRACK/SS PGOOD VOUT MPGM VFB 22µF RUN MARG0 6.3V+ COMP LTM4601-1 MARG1 467.30VµF INTVCC VOUT_LCL DRVCC NC3 10µF NC2 25V 392k NC1 ×2 SGND PGND fSET CLOCK SYNC 270° PHASE 4.5V TO 20V TRACK/SS CONTROL VIN PLLINTRACK/SS 0.1µF PGOOD PGOOD VOUT MPGM VFB 22µF 10µF RUN MARG0 6.3V+ 2×52V CINOTMVCPC LTM4601-1 VOMUAT_RLGC1L 467.30VµF DRVCC NC3 NC2 392k NC1 SGND PGND fSET 6909 TA02 *CIN OPTIONAL TO REDUCE ANY LC RINGING. NOT NEEDED FOR LOW INDUCTANCE PLANE CONNECTION 6909fa 17

LTC6909 typicAl ApplicAtions Using Additional Standard Logic Inverters to Achieve 10- and 14-Phase Outputs (Inverters Are 74HC04 or Equivalent) 10 OUTPUT PHASES (OUTPUTS SHIFTED BY 36 DEGREES) 14 OUTPUT PHASES (OUTPUTS SHIFTED BY 25.71 DEGREES) V+ V+ 0.1µF 0.1µF LTC6909 LTC6909 V+D OUT1 0° (360°) V+D OUT1 0° (360°) GND OUT2 180° GND OUT2 180° V+A OUT3 72° V+A OUT3 51.43° 0.1µF SET OUT4 252° 0.1µF SET OUT4 231.43° RSET RSET PH0 OUT5 144° PH0 OUT5 102.86° PH1 OUT6 324° PH1 OUT6 282.86° PH2 OUT7 216° PH2 OUT7 154.29° MOD OUT8 36° MOD OUT8 334.29° 288° 205.71° 108° 25.71° 257.14° 77.14° 308.57° 128.57° 6909 TA03 6909fa 18

LTC6909 typicAl ApplicAtions Combining Eight Outputs With a Lowpass Filter to Create a Sine Wave 2.7V TO 5.5V 249k 1 V+A SET 16 500mV/DIV 0.1µF 2 15 GND PH2 3 LTC6909 14 PH0 MOD 4 PH1 V+D 13 0.1µF 787k 5 12 787k 2µs/DIV OUT1 OUT8 V+ = 5V 6909 TA06 402k 6 11 402k THD = 0.2% OUT2 OUT7 140k 7 10 140k OUT3 OUT6 80.6k 8 9 80.6k OUT4 OUT5 1 LP V+ 16 0.1µF 2 LTC1563-2 15 100kHz OPEN SA LPB SINE WAVE 3 NC NC 14 16.2k OUTPUT 4 13 INVA INVB 21k 5 NC NC 12 20k 6 11 LPA SB 7 10 AGND NC 0.1µF 8 V– EN 9 16.2k 6909 TA04 6909fa 19

LTC6909 pAckAge Description MS Package 16-Lead Plastic MSOP (Reference LTCM DSW PGa c#k 0a5g-e08-1669 Rev Ø) 16-Lead Plastic MSOP (Reference LTC DWG # 05-08-1669 Rev Ø) 0.889 ± 0.127 (.035 ± .005) 5.23 3.20 – 3.45 (.206) (.126 – .136) MIN 4.039 ± 0.102 0.305 ± 0.038 0.50 (.159 ± .004) (.0120 ± .0015) (.0197) (NOTE 3) 0.280 ± 0.076 TYP BSC 16151413121110 9 (.011 ± .003) RECOMMENDED SOLDER PAD LAYOUT REF DETAIL “A” 3.00 ± 0.102 0.254 4.90 ± 0.152 (.118 ± .004) (.010) 0° – 6° TYP (.193 ± .006) (NOTE 4) GAUGE PLANE 0.53 ± 0.152 1234567 8 (.021 ± .006) 1.10 0.86 (.043) (.034) DETAIL “A” MAX REF 0.18 (.007) SEATING PLANE 0.17 – 0.27 0.1016 ± 0.0508 (.007 – .011) (.004 ± .002) TYP 0.50 NOTE: (.0197) MSOP (MS16) 1107 REV Ø 1. DIMENSIONS IN MILLIMETER/(INCH) BSC 2. DRAWING NOT TO SCALE 3. DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE 4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX 6909fa 20

LTC6909 revision history REV DATE DESCRIPTION PAGE NUMBER A 1/11 Revised typical value for ∆f , 10MHz ≤ f ≤ 20MHz to ±2.7. 2 MASTER MASTER Revised Typical Applications drawings for 10 and 14 output phases. 18 6909fa Information furnished by Linear Technology Corporation is believed to be accurate and reliable. 21 However, no responsibility is assumed for its use. Linear Technology Corporation makes no representa- tion that the interconnection of its circuits as described herein will not infringe on existing patent rights.

LTC6909 typicAl ApplicAtion Providing an 8-Phase Synchronizing Clock to LTM Modules INPUT SUPPLY 0.1µF INTVCC S0FT-START LTC6909 LTM4601 V+D OUT1 OUTPUT1 GND OUT2 TRACKING V+A OUT3 LTM4601-1 35.7k OUTPUT2 0.1µF SET OUT4 PH0 OUT5 TRACKING PH1 OUT6 LTM4601-1 OUTPUT3 PH2 OUT7 MOD OUT8 TRACKING LTM4601-1 OUTPUT4 TRACKING LTM4601-1 OUTPUT3 TRACKING LTM4601-1 OUTPUT4 TRACKING LTM4601-1 OUTPUT3 TRACKING LTM4601-1 OUTPUT4 6909 TA05 relAteD pArts PART NUMBER DESCRIPTION COMMENTS LTC1799 1kHz to 33MHz ThinSOT™ Oscillator, Resistor Set Wide Frequency Range LTC6900 1kHz to 20MHz ThinSOT Oscillator, Resistor Set Low Power, Wide Frequency Range LTC6902 Multiphase Oscillator with Spread Spectrum Modulation 2-, 3- or 4-Phase Outputs LTC6903/LTC6904 1kHz to 68MHz Serial Port Programmable Oscillator 0.1% Frequency Resolution, I2C or SPI Interface LTC6905 17MHz to 170MHz ThinSOT Oscillator, Resistor Set High Frequency, 100µs Start-Up, 7ps RMS Jitter LTC6905-XXX Fixed Frequency ThinSOT Oscillators, Up to 133MHz No Trim Components Required LTC6906 Micropower ThinSOT Oscillator, Resistor Set 10kHz to 1MHz, 12mA at 100kHz LTC6907 Micropower ThinSOT Oscillator, Resistor Set 40kHz to 4MHz, 36µA at 400kHz LTC6908-1 50kHz to 10MHz Dual Output ThinSOT Oscillator, Resistor Set Complementary Outputs (0°/180°) LTC6908-2 50kHz to 10MHz Dual Output ThinSOT Oscillator, Resistor Set Quadrature Outputs (0°/90°) LTC6930-XXX Fixed Frequency Oscillator, 32.768kHz to 8.192MHz 0.09% Accuracy, 110μs Startup Time, 105μA at 32kHz 6909fa 22 Linear Technology Corporation LT 0111 REV A • PRINTED IN USA 1630 McCarthy Blvd., Milpitas, CA 95035-7417 (408) 432-1900 ● FAX: (408) 434-0507 ● www.linear.com LINEAR TECHNOLOGY CORPORATION 2009

Mouser Electronics Authorized Distributor Click to View Pricing, Inventory, Delivery & Lifecycle Information: A nalog Devices Inc.: LTC6909IMS#TRPBF LTC6909HMS#PBF LTC6909HMS#TRPBF LTC6909CMS#PBF LTC6909IMS#PBF LTC6909CMS#TRPBF

Datasheet下载

Datasheet下载