ICGOO在线商城 > 集成电路(IC) > PMIC - 稳压器 - DC DC 开关稳压器 > LTC3111EMSE#PBF

- 型号: LTC3111EMSE#PBF

- 制造商: LINEAR TECHNOLOGY

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

LTC3111EMSE#PBF产品简介:

ICGOO电子元器件商城为您提供LTC3111EMSE#PBF由LINEAR TECHNOLOGY设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 LTC3111EMSE#PBF价格参考。LINEAR TECHNOLOGYLTC3111EMSE#PBF封装/规格:PMIC - 稳压器 - DC DC 开关稳压器, 可调式 降压升压 开关稳压器 IC 正 2.5V 1 输出 1.5A 16-TFSOP(0.118",3.00mm 宽)裸露焊盘。您可以下载LTC3111EMSE#PBF参考资料、Datasheet数据手册功能说明书,资料中有LTC3111EMSE#PBF 详细功能的应用电路图电压和使用方法及教程。

LTC3111EMSE#PBF 是 Linear Technology(现已被 Analog Devices 收购)生产的一款高效同步降压型 DC-DC 开关稳压器。它具有高效率、低静态电流和宽输入电压范围的特点,适用于多种应用场景。 主要特性: - 输入电压范围:2.5V 至 5.5V - 输出电压范围:0.6V 至 5V(可调) - 最大输出电流:高达 1A - 高效率:在轻载条件下,通过脉冲跳跃模式保持高效率 - 低静态电流:典型值为 45μA,适合电池供电设备 - 内置功率 MOSFET:减少了外部元件数量,简化了设计 应用场景: 1. 便携式电子设备 LTC3111EMSE#PBF 的低静态电流和高效率使其非常适合用于电池供电的便携式设备,如智能手机、平板电脑、便携式媒体播放器等。这些设备通常需要长时间工作且对功耗要求严格,LTC3111 可以有效延长电池寿命。 2. 物联网 (IoT) 设备 在 IoT 领域,许多传感器节点和无线模块依赖电池供电,LTC3111 的高效能和低功耗特性可以确保这些设备在长时间运行时仍能保持稳定的性能。例如,智能家居设备、环境监测系统等都可以从中受益。 3. 工业自动化 在工业环境中,电源管理至关重要。LTC3111 可以为各种工业控制器、PLC、传感器和其他低功耗设备提供稳定可靠的电源。其宽输入电压范围和强大的输出能力使其能够适应不同的电源条件。 4. 医疗设备 对于便携式医疗设备,如血糖仪、心率监测器等,LTC3111 的小尺寸和高效率是理想选择。它可以在不影响性能的情况下,帮助设备实现更长的续航时间,提高用户体验。 5. 汽车电子 在汽车应用中,LTC3111 可以为车载电子系统中的低功耗模块提供稳定的电源。例如,车内娱乐系统、导航设备、传感器等都需要高效的电源管理,LTC3111 能够满足这些需求。 总之,LTC3111EMSE#PBF 凭借其出色的性能和灵活性,广泛应用于各种需要高效电源管理的领域,特别适合那些对功耗和空间有严格要求的应用场景。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC) |

| 描述 | IC REG BUCK BST SYNC ADJ 16-MSOP |

| 产品分类 | |

| 品牌 | Linear Technology |

| 数据手册 | http://www.linear.com/docs/44189 |

| 产品图片 | |

| 产品型号 | LTC3111EMSE#PBF |

| PWM类型 | 电压模式,Burst Mode® |

| rohs | 无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | - |

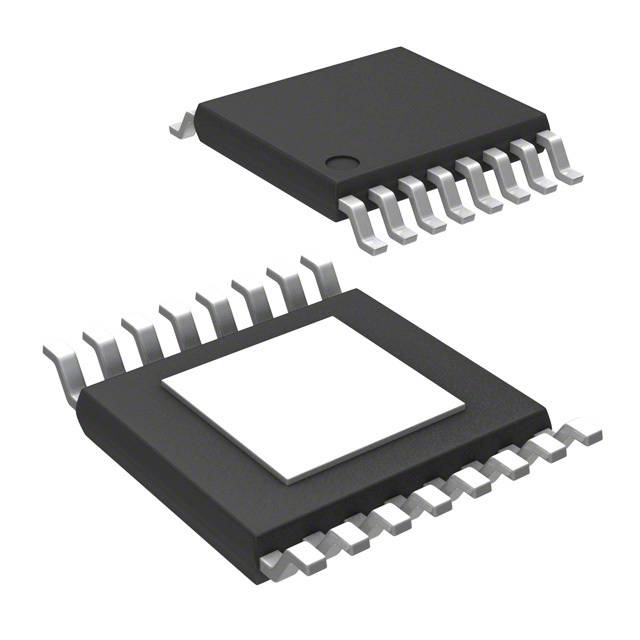

| 供应商器件封装 | 16-MSOP-EP |

| 包装 | 管件 |

| 同步整流器 | 是 |

| 安装类型 | 表面贴装 |

| 封装/外壳 | 16-TFSOP(0.118",3.00mm 宽)裸露焊盘 |

| 工作温度 | -40°C ~ 125°C |

| 标准包装 | 37 |

| 电压-输入 | 2.5 V ~ 15 V |

| 电压-输出 | 2.5 V ~ 15 V |

| 电流-输出 | 1.5A |

| 类型 | 降压(降压),升压(升压) |

| 输出数 | 1 |

| 输出类型 | 可调式 |

| 频率-开关 | 800kHz |

PDF Datasheet 数据手册内容提取

LTC3111 15V, 1.5A Synchronous Buck-Boost DC/DC Converter FEATURES DESCRIPTION n Regulated Output with V Above, Below The LTC®3111 is a fixed frequency, synchronous buck- IN or Equal to V boost DC/DC converter with an extended input and output OUT n 2.5V to 15V Input and Output Voltage Range range. The unique 4-switch, single inductor architecture n 1.5A Continuous Output Current: V ≥ 5V, provides low noise and seamless operation from input IN V = 5V, PWM Mode voltages above, below or equal to the output voltage. OUT n Single Inductor With an input and output range of 2.5V to 15V, the LTC3111 n Accurate RUN Threshold is well suited for a wide variety of single or multiple-cell n Up to 95% Efficiency batteries, back-up capacitor or wall adapter source applica- n 800kHz Switching Frequency, Synchronizable tions. Low R internal N-channel MOSFET switches DS(ON) Between 600kHz and 1.5MHz and selectable PWM or Burst Mode operation produce n 49µA No-Load Quiescent Current in Burst Mode® high efficiency over a wide range of operating conditions. Operation n Output Disconnect in Shutdown An accurate RUN pin allows the user to program the n Shutdown Current < 1µA turn-on threshold voltage of the converter. Other features n Internal Soft-Start include: short-circuit protection, internal soft-start and n Small, Thermally Enhanced 14-Lead (3mm × 4mm × thermal shutdown. 0.75mm) DFN and 16-Lead MSOP Packages The LTC3111 is offered in both thermally enhanced APPLICATIONS 14-lead (3mm × 4mm × 0.75mm) DFN and 16-lead MSOP packages. n 3.3V or 5V from 1, 2 or 3 Li-Ion, Multiple-Cell L, LT, LTC, LTM, Linear Technology, the Linear logo, Burst Mode, LTspice are registered Alkaline/NiMH Batteries trademarks and No RSENSE and PowerPath are trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents, n RF Transmitters including 6404251, 6166527, 5481178, 6304066, 6580258. n Military, Industrial Power Systems TYPICAL APPLICATION 5V, 800kHz Wide Input Voltage Buck-Boost Regulator Efficiency at 5V OUT 4.7µH 100 PWM 90 0.1µF 0.1µF SW1 SW2 BURST 80 2.5V TO 1V5IVN 10µF BVISNT1 LTC3111 CBVOSOMTUP2T 680pF26.1k 1M 20k 22µF V51(VV.O5IUNAT > 5V) CIENCY (%) 6700 FI BURST PWM PWM/SYNC 27pF 33pF EF OFF ON RUN FB 50 SNSGND VCC 1µF 191k 40 VVIINN == 25.V7V SGND PGND 3111 TA01a 30 VIN = 12V 0.0001 0.001 0.01 0.1 1 10 LOAD CURRENT (A) 3111 TA01b 3111fa 1 For more information www.linear.com/LTC3111

LTC3111 ABSOLUTE MAXIMUM RATINGS (Notes 1, 3) V Voltage .................................................–0.3V to 16V Operating Junction Temperature Range (Notes 2, 5) IN V Voltage ..............................................–0.3V to 16V LTC3111E, LTC3111I ...........................–40°C to 125°C OUT SW1 Voltage (Note 4) ...................–0.3V to (V + 0.3V) LTC3111H ...........................................–40°C to 150°C IN SW2 Voltage (Note 4) .................–0.3V to (V + 0.3V) LTC3111MP ........................................–55°C to 150°C OUT BST1 Voltage ...................(V – 0.3V) to (V + 6V) Maximum Junction Temperature (Note 3).............150°C SW1 SW1 BST2 Voltage ...................(V – 0.3V) to (V + 6V) Storage Temperature Range ..................–65°C to 150°C SW2 SW2 RUN Voltage...............................................–0.3V to 16V Lead Temperature (Soldering, 10sec) PWM/SYNC, V Voltage .............................–0.3V to 6V MSOP ...............................................................300°C CC FB, COMP, Voltage .......................................–0.3V to 6V PIN CONFIGURATION TOP VIEW TOP VIEW COMP 1 14 SGND COMP 1 16 SGND FB 2 13 PWM/SYNC FB 2 15 PWM/SYNC SNSGND 3 12 VCC SNSGND 3 14 VCC 15 RUN 4 17 13 NC RUN 4 11 NC PGND VIN 5 PGND 12 VOUT VIN 5 10 VOUT SW1 6 11 SW2 BST1 7 10 BST2 SW1 6 9 SW2 PGND 8 9 PGND BST1 7 8 BST2 MSE PACKAGE 16-LEAD PLASTIC MSOP DE PACKAGE 14-LEAD (4mm × 3mm) PLASTIC DFN TJMAX = 150°C, θJA = 40°C/W, θJC = 10°C/W EXPOSED PAD (PIN 17) IS PGND, MUST BE SOLDERED TO PCB TJMAX = 150°C, θJA = 43°C/W, θJC = 5°C/W EXPOSED PAD (PIN 15) IS PGND, MUST BE SOLDERED TO PCB ORDER INFORMATION LEAD FREE FINISH TAPE AND REEL PART MARKING* PACKAGE DESCRIPTION TEMPERATURE RANGE LTC3111EDE#PBF LTC3111EDE#TRPBF 3111 14-Lead (4mm × 3mm) Plastic DFN –40°C to 125°C LTC3111IDE#PBF LTC3111IDE#TRPBF 3111 14-Lead (4mm × 3mm) Plastic DFN –40°C to 125°C LTC3111HDE#PBF LTC3111HDE#TRPBF 3111 14-Lead (4mm × 3mm) Plastic DFN –40°C to 150°C LTC3111MPDE#PBF LTC3111MPDE#TRPBF 3111 14-Lead (4mm × 3mm) Plastic DFN –55°C to 150°C LTC3111EMSE#PBF LTC3111EMSE#TRPBF 3111 16-Lead Plastic MSOP –40°C to 125°C LTC3111IMSE#PBF LTC3111IMSE#TRPBF 3111 16-Lead Plastic MSOP –40°C to 125°C LTC3111HMSE#PBF LTC3111HMSE#TRPBF 3111 16-Lead Plastic MSOP –40°C to 150°C LTC3111MPMSE#PBF LTC3111MPMSE#TRPBF 3111 16-Lead Plastic MSOP –55°C to 150°C Consult LTC Marketing for parts specified with wider operating temperature ranges. *The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on nonstandard lead based finish parts. For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/ 3111fa 2 For more information www.linear.com/LTC3111

LTC3111 ELECTRICAL CHARACTERISTICS The l denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at T = 25°C (Note 2). V = V = PWM/SYNC = RUN = 5V unless otherwise A IN OUT noted. PARAMETER CONDITION MIN TYP MAX UNITS Input Operating Range l 2.5 15 V V UVLO Threshold Rising l 1.9 2.1 2.3 V IN V UVLO Hysteresis 200 mV IN V UVLO Threshold Rising l 2.2 2.35 2.5 V CC V UVLO Hysteresis 190 mV CC Output Voltage Adjust Range l 2.5 15 V INTV Clamp Voltage V = 5V or 15V l 3.9 4.2 4.5 V CC IN Quiescent Current—Burst Mode Operation FB = 1V, PWM/SYNC = 0V 55 80 µA Quiescent Current—Shutdown RUN = V = V = 0V, Not Including Switch Leakage 0 1 µA OUT CC Feedback Voltage PWM Operation l 0.78 0.8 0.82 V Feedback Leakage FB = 0.8V 0 50 nA NMOS Switch Leakage Switches A, B, C, D, V = V = 15V 0.5 5 µA IN OUT NMOS Switch On-Resistance Switch A 90 mΩ Switch B, C, D 105 mΩ Input Current Limit l 2.3 3 3.7 A Peak Current Limit 5.8 A Burst Current Limit PWM/SYNC = 0V 0.8 A Burst Zero Current Threshold PWM/SYNC = 0V 0.1 A Reverse Current Limit –1 A Maximum Duty Cycle Percentage of the Period SW2 is Low in Boost Mode l 85 90 % (Note 7) Minimum Duty Cycle Percentage of the Period SW1 is Low in Buck Mode l 0 % (Note 7) SW1, SW2 Minimum Low Time (Note 7) 160 ns Frequency PWM/SYNC = 5V l 700 800 900 kHz SYNC Frequency Range (Note 6) l 600 1500 kHz PWM/SYNC Threshold l 0.5 0.9 1.5 V RUN Threshold to Enable V Rising l 0.35 0.8 1.15 V CC RUN Threshold to Disable V Falling l 0.3 V CC RUN Threshold to Enable Switching Rising l 1.15 1.18 1.23 V RUN Hysteresis 120 mV Note 1: Stresses beyond those listed under Absolute Maximum Ratings to 125°C junction temperature, the LTC3111H is guaranteed to meet may cause permanent damage to the device. Exposure to any Absolute performance specifications from –40°C to 150°C junction temperature Maximum Rating condition for extended periods may affect device and the LTC3111MP is guaranteed and tested to meet performance reliability and lifetimes. specifications from –55°C to 150°C junction temperature. High junction Note 2: The LTC3111 is tested under pulsed load conditions such that temperatures degrade operating lifetimes: operating lifetime is derated T ≈ T . The LTC3111E is guaranteed to meet specifications from for junction temperatures greater than 125°C. Note that the maximum J A 0°C to 85°C junction temperature. Specifications over the –40°C to ambient temperature consistent with these specifications is determined by 125°C operating junction temperature range are assured by design, specific operating conditions in conjunction with board layout, the rated characterization and correlation with statistical process controls. The package thermal resistance and other environmental factors. LTC3111I is guaranteed to meet performance specifications from –40°C 3111fa 3 For more information www.linear.com/LTC3111

LTC3111 ELECTRICAL CHARACTERISTICS Note 3: This IC includes overtemperature protection that is intended Note 5: The junction temperature (TJ in °C) is calculated from the ambient to protect the device during momentary overload conditions. Junction temperature (TA in °C) and power dissipation (PD in Watts) according to temperatures will exceed 150°C when overtemperature protection is the formula: active. Continuous operation above the specified maximum operating TJ = TA + (PD • θJA) junction temperature may impair device reliability. where θJA (in °C/W) is the package thermal impedance. Note 4: Voltage transients on the switch pins beyond the DC limit specified Note 6: SYNC frequency range is tested with a square wave. Operation in the Absolute Maximum Ratings, are non-disruptive to normal operation with 100ns minimum high or low time is assured by design. when using good layout practices, as shown on the demo board or Note 7: Switch timing measurements are made in an open-loop test described in the data sheet and application notes. configuration. Timing in the application may vary somewhat from these values due to differences in the switch pin voltage during the non-overlap durations when the switch pin voltage is influenced by the magnitude and direction of the inductor current. TYPICAL PERFORMANCE CHARACTERISTICS T = 25°C, V = 5V, V = 5V, unless otherwise specified A IN OUT Maximum Output Current Maximum Load Current in Burst in PWM Mode vs V Mode Operation vs V Wide V to 5V Efficiency IN IN IN OUT 2.0 800 100 1.8 VOUT = 3.3V PWM M OUTPUT CURRENT (A) 11101.....24680 M OUTPUT CURRENT (mA) 463570000000000 VVOOUUTT == 51V2V EFFICIENCY (%) 68790000 BURST MAXIMU 000...264 INPUT CVVUOORUUTTR E==N 35T.V3 ,L VLI,M L= I=6T . 48=.µ 72Hµ.3HA MAXIMU 210000 5400 VVIINN == 25.V7V VOUT = 12V, L = 10µH VIN = 12V 0 0 30 2 3 4 5 6 7 8 9 10 11 12 13 14 15 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0.0001 0.001 0.01 0.1 1 10 VIN (V) VIN (V) LOAD CURRENT (A) 3111 G01 3111 G02 3111 G03 Wide V to 5V Power Loss Wide V to 3.3V Efficiency Wide V to 3.3V Power Loss IN OUT IN OUT IN OUT 10 100 10 VIN = 2.7V PWM 90 VIN = 5V 1 VIN = 12V 1 PWM 80 W) PWM %) BURST W) OWER LOSS (00.0.11 BURST EFFICIENCY ( 6700 OWER LOSS ( 0.00.11 BURST P 50 P 0.001 VVIINN == 25.V7V 40 0.001 VVIINN == 25.V7V VIN = 12V VIN = 12V 0.0001 30 0.0001 0.0001 0.001 0.01 0.1 1 10 0.0001 0.001 0.01 0.1 1 0.0001 0.001 0.01 0.1 1 LOAD CURRENT (A) LOAD CURRENT (A) LOAD CURRENT (A) 3111 G04 3111 G05 3111 G06 3111fa 4 For more information www.linear.com/LTC3111

LTC3111 TYPICAL PERFORMANCE CHARACTERISTICS T = 25°C, V = 5V, V = 5V, unless otherwise specified A IN OUT 12V to 12V Efficiency at IN OUT f = 600kHz, 800kHz, 1MHz and Wide V to 12V Efficiency Wide V to 12V Power Loss 1.5MHz with L = 10µH IN OUT IN OUT 100 10 100 PWM 90 PWM 90 BURST 1 80 80 FICIENCY (%) 6700 WER LOSS (W)00.0.11 BURST FICIENCY (%) 6700 EF PO EF 50 50 f = 600kHz 40 VVIINN == 25.V7V 0.001 VVIINN == 25.V7V 40 ff == 810M0HkzHz VIN = 12V VIN = 12V f = 1.5MHz 30 0.0001 30 0.0001 0.001 0.01 0.1 1 0.0001 0.001 0.01 0.1 1 10 0.01 0.1 1 LOAD CURRENT (A) LOAD CURRENT (A) LOAD CURRENT (A) 3111 G07 3111 G08 3111 G09 Burst Mode No-Load Current with 800kHz PWM Mode No-Load Input V from V or Back-Fed from V Voltage vs V PWM Mode CC IN CC IN Current V with an Optional Diode No Load OUT 20 450 4.5 VOUT = 5V 18 400 4.3 16 4.1 350 RENT (mA) 111204 RENT (µA)320500 LTAGE (V) 333...957 R R200 O V CUIN 86 V CUIN150 V VCC 33..31 4 100 VCC FROM VIN 2.9 2 50 2.7 VCC FROM VOUT 0 0 2.5 2 3 4 5 6 7 8 9 10 11 12 13 14 15 2 3 4 5 6 7 8 9 10 11 12 13 14 15 2 3 4 5 6 7 8 9 10 11 12 13 14 15 VIN (V) VIN (V) VIN (V) 31111 G10 3111 G11 3111 G12 Normalized N-Channel MOSFET Normalized N-Channel MOSFET V Voltage vs V Current Resistance vs V Resistance vs Temperature CC CC CC 4.2 1.30 1.6 1.5 4.1 CE 1.25 CE AN AN 1.4 4.0 SIST1.20 SIST 1.3 V (V)CC 33..98 MOSFET RE11..1105 MOSFET RE 11..21 D 1.05 D 1.0 3.7 RMALIZE1.00 RMALIZE 00..98 3.6 O O N0.95 N 0.7 3.5 0.90 0.6 0 10 20 30 40 50 60 70 80 2.5 3.0 3.5 4.0 4.5 5.0 –50 0 50 100 150 CURRENT FROM VCC (mA) VCC (V) TEMPERATURE (°C) 3111 G13 3111 G14 3111 G15 3111fa 5 For more information www.linear.com/LTC3111

LTC3111 TYPICAL PERFORMANCE CHARACTERISTICS T = 25°C, V = 5V, V = 5V, unless otherwise specified A IN OUT Feedback Pin Program Voltage V and V UVLO Voltage RUN Threshold to Enable/Disable CC IN vs Temperature Thresholds vs Temperature V vs V CC IN 800.5 2.4 1.00 RAM VOLTAGE (mV)778990990...050 THRESHOLDS (V) 2222....1230 VVVCCICNC U UUVVVLLLOOO F RRAIILSSLIININNGGG O ENABLE V (V)CC0000....89890055 FRAILSLIINNGG PROG798.5 UVLO 1.9 VIN UVLO FALLING OLD T00..7705 N 798.0 N H EEDBACK PI779977..50 V AND VCCI 111...876 RUN THRES000...665055 F 796.5 1.5 0.50 –50 0 50 100 150 –50 0 50 100 150 2 3 4 5 6 7 8 9 10 11 12 13 14 15 TEMPERATURE (°C) TEMPERATURE (°C) VIN (V) 3111 G16 3111 G17 3111 G18 RUN Threshold to Enable/Disable RUN Threshold to Enable/Disable RUN Threshold to Enable/Disable V vs Temperature Switching vs V Switching vs Temperature CC IN O ENABLE V (V)CC01000.....8089900505 FALLING RISING ABLE SWITCHING (V)111...322050 RISING ENABLE SWITCHING (V)111...232005 RISING N THRESHOLDS T0000....67765050 HRESHOLD TO EN111...101055 FALLING N THRESHOLD TO 111...101055 FALLING RU00..5505 RUN T1.00 RUN PI1.00 –50 0 50 100 150 2 3 4 5 6 7 8 9 10 11 12 13 14 15 –50 0 50 100 150 TEMPERATURE (°C) VIN (V) TEMPERATURE (°C) 3111 G21 3111 G19 3111 G20 PWM Mode Input, Peak and Reverse Current Limits vs Burst Mode Peak Current, I ZERO Temperature Limits vs Temperature 6 1.0 PEAK CURRENT LIMIT 5 0.9 PEAK CURRENT LIMIT A) A) 0.8 (REVERSE 34 INPUT CURRENT LIMIT (REVERSE 00..67 D I D I N 2 N 0.5 A A , I MITPEAK 10 , I, MITPEAK 00..43 ILI REVERSE CURRENT LIMIT IL 0.2 IZERO –1 0.1 –2 0 –50 0 50 100 150 –50 0 50 100 150 TEMPERATURE (°C) TEMPERATURE (°C) 3111 G23 3111 G22 3111fa 6 For more information www.linear.com/LTC3111

LTC3111 TYPICAL PERFORMANCE CHARACTERISTICS T = 25°C, V = 5V, V = 5V, unless otherwise specified A IN OUT 3V to 5V 0.05A to 0.25A 5V to 5V 0.05A to 0.5A 12V to 5V 0.05A to 0.5A IN OUT IN OUT IN OUT Load Response Load Response Load Response 200mVV/ODUIVT 200mVV/ODUIVT VOUT 500mV/DIV INDUCTOR INDUCTOR CURRENT CURRENT INDUCTOR 500mA/DIV 500mA/DIV CURRENT 1A/DIV LOAD LOAD LOAD CURRENT CURRENT CURRENT 200mA/DIV 500mA/DIV 500mA/DIV 500µs/DIV 3111 G24 500µs/DIV 3111 G25 500µs/DIV 3111 G26 FRONT PAGE APPLICATION FRONT PAGE APPLICATION FRONT PAGE APPLICATION 5V to 5V Burst to PWM 12V to 5V Burst Mode V IN OUT IN OUT OUT Response Ripple 12V to 5V PWM V Ripple IN OUT OUT 200mVV/ODUIVT 200mVV/ODUIVT 50mVV/ODUIVT PWM/SYNC 5V/DIV INDUCTOR INDUCTOR CURRENT CURRENT INDUCTOR 500mA/DIV 500mA/DIV CURRENT 500mA/DIV ILOAD = 10mA 500µs/DIV 3111 G27 ILOAD = 50mA 20µs/DIV 3111 G28 ILOAD = 500mA 1µs/DIV 3111 G29 L = 4.7µH L = 4.7µH L = 4.7µH COUT = 22µF COUT = 22µF COUT = 22µF 7.5V to 5V Start-Up 1.5MHz SYNC Signal Capture and 12V to 5V SW1 and SW2 IN OUT IN OUT Response Release Waveforms SW2 VOUT 5V/DIV RUN 200mV/DIV 5V/DIV SW1 10V/DIV PWM/SYNC VOUT 5V/DIV 2V/DIV INDUCTOR INDUCTOR INDUCTOR CURRENT CURRENT CURRENT 500mA/DIV 1A/DIV 500mA/DIV ILOAD = 500mA 500µs/DIV 3111 G30 100µs/DIV 3111 G31 1µs/DIV 3111 G32 L = 4.7µH COUT = 22µF 3111fa 7 For more information www.linear.com/LTC3111

LTC3111 TYPICAL PERFORMANCE CHARACTERISTICS T = 25°C, V = 5V, V = 5V, unless otherwise specified A IN OUT 3.3V Die Temperature Rise vs OUT V Short-Circuit Response and V Short-Circuit Response and Continuous Load Current 4-Layer OUT CC Recovery Recovery Demo Board at 25°C 50 VCC 2VV/ODUIVT 52VVV//ODDUIIVVT SOFT-START SE (°C) 434055 VIN = 2.7V VIN = 12V INDUCTOR E RI 30 CURRENT R 1A/DIV INDUCTOR TU 25 CURRENT RA VIN = 5V 1A/DIV PE 20 1ms/DIV 3111 G33 1ms/DIV 3111 G34 TEM 15 E DI 10 5 0 0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 2.0 LOAD CURRENT (A) 3111 G35 5V Die Temperature Rise vs 12V Die Temperature Rise vs OUT OUT Continuous Load Current 4-Layer Continuous Load Current 4-Layer Demo Board at 25°C Demo Board at 25°C 60 80 70 50 DIE TEMPERATURE (°C) 243000 VIN = 2.7V VIN = 5V VIN = 12V E TEMPERATURE RISE (°C) 5362400000 VIN = 2.7V VIN = 5VVIN = 12V DI 10 10 0 0 0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 2.0 0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 2.0 LOAD CURRENT (A) LOAD CURRENT (A) 3111 G36 3111 G37 SW1, SW2 Minimum Low Time SW1, SW2 Minimum Low Time vs V vs Temperature CC 300 250 ILOAD = 300mA ILOAD = 300mA 230 s) s) n250 n ME ( SW1, VIN = 4V ME (210 SW1, VIN = 4V TI TI190 W 200 W LO LO170 SW2, VIN = 6V M M U150 U150 M M NI SW2, VIN = 6V NI130 MI MI W2 100 W2 110 S S W1, 50 W1, 90 S S 70 0 50 2 2.5 3 3.5 4 4.5 5 –50 0 50 100 150 VCC (V) TEMPERATURE (°C) 3111 G38 3111 G39 3111fa 8 For more information www.linear.com/LTC3111

LTC3111 PIN FUNCTIONS (DFN/MSOP) COMP (Pin 1/Pin 1): Error Amp Output. An R-C network BST1 (Pin 7/Pin 7): Boosted Floating Driver Supply for connected from this pin to FB sets the loop compensa- A-Switch Driver. Connect a 0.1µF capacitor from this pin tion for the voltage converter. Refer to the Applications to SW1. Information section for component selection details. BST2 (Pin 8/Pin 10): Boosted Floating Driver Supply for FB (Pin 2/Pin 2): Feedback Voltage Input. Connect the D-Switch Driver. Connect a 0.1µF capacitor from this pin V resistor divider tap to this pin. The output voltage can to SW2. OUT be adjusted from 2.5V to 15V by the following equation: SW2 (Pin 9/Pin 11): The external inductor and internal R1 switches C and D are connected here. VOUT =0.8V•1+R2 VOUT (Pin 10/Pin 12): Regulated Output Voltage. This pin should be connected to a low ESR ceramic capacitor. The where R1 is the resistor between V and FB and R2 is OUT capacitor should be placed as close to the pin as possible the resistor between FB and GND and have a short return to the ground plane. SNSGND (Pin 3/Pin 3): This pin must be connected to NC (Pin 11/Pin 13): Not Connected. This pin should be ground. connected to ground. RUN (Pin 4/Pin 4): Input to Enable or Disable the IC and Set V (Pin 12/Pin 14): External Capacitor Connection for CC Custom Input Undervoltage Lockout (UVLO) Thresholds. the Regulated V Supply. This supply is used to operate CC The RUN pin can be driven by an external logic signal to internal circuitry and switch drivers. V will track V up CC IN enable and disable the IC. In addition, the voltage on this to 4.2V typical, but will maintain this voltage when V > IN pin can be set by a resistive voltage divider connected to 4.2V. Connect a 1µF ceramic capacitor from this pin to the input supply in order to provide accurate turn-on and GND. This pin can be tied to an external supply up to 5.5V. turn-off (UVLO) thresholds determined by: Refer to the Operation section of this data sheet under R5 Power VCC from an External Source for more details. VIN(RUN)=1.2V•1+R6 PWM/SYNC (Pin 13/Pin 15): Burst Mode Control and Synchronization Input. A DC voltage < 0.5V commands The IC is enabled if RUN exceeds 1.2V nominally. Once Burst Mode operation independent of load current, >1.5V enabled, the UVLO threshold has a built-in hysteresis of commands 800kHz fixed frequency mode. A digital pulse approximately 120mV, turn-off will occur when the voltage train between 600kHz and 1.5MHz applied to this pin will on RUN drops to below 1.08V nominally. To continuously override the internal oscillator and set the operating fre- enable the IC, RUN can be tied directly to the input voltage quency. The pulse train should have a minimum high time up to the absolute maximum rating. This pin should not or low time greater than 100ns (Note 6). Note the LTC3111 be left unconnected. has reduced power capability when operating in Burst V (Pin 5/Pin 5): Input Supply Voltage. This pin should Mode operation. This pin should not be left unconnected. IN be bypassed to the ground plane with at least 10µF of low SGND (Pin 14/Pin 16): Signal Ground. Terminate the RUN ESR, low ESL ceramic capacitance. Place this capacitor as input voltage divider and output voltage divider to SGND. close to the pin as possible and provide as short a return path to the ground plane as possible. PGND (Exposed Pad Pin 15/Pin 8, 9, Exposed Pad Pin 17) Power Ground. The exposed pad must be soldered to SW1 (Pin 6/Pin 6): The external inductor and internal the PCB and electrically connected to ground through switches A and B are connected here. the shortest and lowest impedance connection possible. 3111fa 9 For more information www.linear.com/LTC3111

LTC3111 SIMPLIFIED BLOCK DIAGRAM 4.7µH BST1 VIN SW1 SW2 VOUT BST2 VCC VCC CIN COUT ADRV DDRV VCC VCC BDRV CDRV GND GND ADRVBDRVCDRVDDRV DRIVERS VCC REVERSE ILIM – IZERO – 0.1A + + –1A + IPEAK LOGIC 5.8A – VCC + ILIMIT 3A – + VINVOUT RUN RUN + – – FB STOP 1.2V – ÷ ++ 0.8V + SOFT-START + – ERROR AMP RAMP COMP START 0.8V – VIN + VIN UVLO OSC8IL0L0AkTOR 2.1V – + VCC UVLO PLL 2.35V – Burst Mode PWM/SYNC OPERATION VCC 4.2V REGULATOR/ START CLAMP REFERENCE 1.2V 3111 BD 3111fa 10 For more information www.linear.com/LTC3111

LTC3111 OPERATION INTRODUCTION VOUT The LTC3111 is an extended input and output range, syn- LTC3111 VINVOUT chronous 1.5A buck-boost DC/DC converter optimized for RFF R1 a variety of applications. The LTC3111 utilizes a proprietary CFF FB0.8V +– ÷ COMPPAWRMATORS SSWW12 switching algorithm, which allows its output voltage to be RFB CFB COMP regulated above, below or equal to the input voltage. The R2 CPOLE SGND error amplifier output on COMP determines the output duty 3111 F01 cycle of the switches. The low R , low gate charge DS(ON) synchronous switches provide high efficiency pulse width modulation control. High efficiency is achieved at light Figure 1. Error Amplifier and Compensation Network loads when Burst Mode operation is commanded. on designing the compensation network for the LTC3111 applications can be found in the Applications Information LOW NOISE FIXED FREQUENCY OPERATION section of this data sheet. Oscillator, Phase Lock Loop Current Limit Operation An internal oscillator circuit sets the normal frequency of The buck-boost converter has two current limit circuits. operation to 800kHz. A pulse train applied to the PWM/ The input current limit sources current into the feedback SYNC pin allows the operating frequency to be programmed divider network whenever the current in switch A exceeds between 600kHz to 1.5MHz via an internal phase-lock-loop 3A typical. Due to the high gain of the feedback loop, the circuit. The pulse train must have a minimum high or low injected current forces the error amplifier output to decrease state of at least 100ns to guarantee operation (see Note 6 until the average current through switch A decreases ap- of the Electrical Characteristics). proximately to the current limit value. The input current limit utilizes the error amplifier in an active state and Error Amplifier thereby provides a smooth recovery with little overshoot The LTC3111 contains a high gain operational amplifier once the current limit fault condition is removed. Since which provides frequency compensation of the control the current limit is based on the average current through loop to maintain output voltage regulation. To ensure switch A, the peak inductor current in current limit will loop stability, an external compensation network must be have a dependency on the duty cycle (i.e., on the input installed in the application circuit. A Type III compensation and output voltages) in the overcurrent condition. For this network, as shown in Figure 1, is recommended for most current limit feature to be most effective, the Thevenin applications since it provides the flexibility to optimize resistance from the FB to ground should exceed 100kΩ. the converter’s transient response while simultaneously The speed of the input current limit circuit is limited by the minimizing any DC error in the output voltage. dynamics of the converter loop. On a hard output short, it As shown in Figure 1, the error amplifier is followed by is possible for the inductor current to increase substantially an internal analog divider which adjusts the loop gain by beyond the input current limit before the input current limit the reciprocal of the input voltage when the converter is in circuit can react. For this reason, there is a peak current buck mode and by the output voltage when the converter limit circuit which turns off switch A if the current in switch is in boost mode which minimizes loop-gain variation A exceeds approximately 190% of the input current limit over changes in the input voltage. This simplifies design value. This provides additional protection in the case of of the compensation network and optimizes the transient an instantaneous hard output short. response over the entire range of input voltages. Details 3111fa 11 For more information www.linear.com/LTC3111

LTC3111 OPERATION Should the output voltage become shorted, the input The temperature rise curves given in the Typical Perfor- current limit is reduced to approximately one half of the mance Characteristics section can be used as a guide to normal operating current limit. predict junction temperature rise from ambient. These curves were generated by mounting the LTC3111 to the Reverse Current Limit 4-layer FR-4 demo printed circuit board layout shown in Figure 4. The curves were taken at room temperature, During fixed frequency operation, a reverse current com- elevated ambient temperature will result in greater ther- parator on switch D monitors the current entering the V OUT mal rise rates due to increased R of the N-channel pin. When this current exceeds 1A (typical) switch D will DS(ON) MOSFETs with temperature. The die temperature of the be turned off for the remainder of the switching cycle. This LTC3111 should be kept below the maximum junction feature protects the buck-boost converter from excessive rating of 125°C for E- and I-grades and 150°C for H- and reverse current if the buck-boost output is held above the MP-grades. regulation voltage. In the event that the junction temperature gets too high Internal Soft-Start (approximately 170°C), the input current limit will be The LTC3111 buck-boost converter has an independent linearly decreased from its typical value. If the junction internal soft-start circuit with a nominal duration of 2ms. temperature continues to rise and exceeds approximately The converter remains in regulation during soft-start and 175°C the LTC3111 will be disabled. All power devices will therefore respond to output load transients which are turned off and all switch nodes put to a high imped- occur during this time. In addition, the output voltage rise ance state. The soft-start circuit for the converter is reset time has minimal dependency on the size of the output during thermal shutdown to provide a smooth recovery capacitor or load current during start-up. Soft-start is reset once the overtemperature condition is eliminated. When during a thermal shutdown. the die temperature drops to approximately 170°C the LTC3111 will restart. THERMAL CONSIDERATIONS UNDERVOLTAGE LOCKOUTS For the LTC3111 to provide maximum output power, it is imperative that a good thermal path be provided to dis- The LTC3111 buck-boost converter is disabled and all sipate the heat generated within the package. This can be power devices are turned off until the VCC supply reaches accomplished by taking advantage of the large thermal 2.35V (typical). The soft-start circuit is reset during under- pad on the underside of the IC. It is recommended that voltage lockout to provide a smooth restart once the input multiple vias in the printed circuit board be used to conduct voltage rises above the undervoltage lockout threshold. A the heat away from the IC and into a copper plane with as second UVLO circuit disables all power devices if VIN is much area as possible. below 2.1V rising, 1.9V falling (typical). This can provide a lower V operating range in applications where V is IN CC The efficiency and maximum output current capability of powered from an alternate source or V after start-up. OUT the LTC3111 will be reduced if the converter is required to continuously deliver large amounts of power or oper- INDUCTOR DAMPING ate at high temperatures. The amount of output current derated is dependent upon factors such as board ground When the LTC3111 is disabled (RUN = 0V) or sleeping plane or heat sink area, ambient operating temperature during Burst Mode operation (PWM/SYNC = 0V), active and the input/output voltages of the application. A poor circuits “damp” the inductor voltage through 1kΩ (typical) thermal design can cause excessive heating, resulting in impedance between SW1 and SW2 and GND to reduce impaired performance or reliability. ringing and EMI. 3111fa 12 For more information www.linear.com/LTC3111

LTC3111 OPERATION PWM MODE OPERATION This switching algorithm provides a seamless transition between operating modes and eliminates discontinuities When the PWM/SYNC pin is held high, the LTC3111 buck- in average inductor current, inductor current ripple, and boost converter operates in a fixed-frequency pulse-width loop transfer function throughout the operational modes. modulation (PWM) mode using voltage mode control. Full These advantages result in increased efficiency and stabil- output current is only available in PWM mode. A proprietary ity in comparison to the traditional 4-switch buck-boost switching algorithm allows the converter to transition converter. between buck, buck-boost, and boost modes without discontinuity in inductor current. The switch topology for the buck-boost converter is shown in Figure 2. OUTPUT VOLTAGE PROGRAMMING The output voltage is set via the external resistor divider VIN VOUT comprised of resistors R1 and R2 as show in Figures 1. The resistor divider values determine the output regulation A D voltage according to: L R1 B C VOUT =0.8V•1+R2 3111 F02 Figure 2. Buck-Boost Switch Topology In addition to setting the output voltage, the value of R1 is instrumental in controlling the dynamics of the compensa- When the input voltage is significantly greater than the tion network. When changing the value of this resistor, output voltage, the buck-boost converter operates in buck care must be taken to understand the impact this will have mode. Switch D turns on at maximum duty cycle and on the compensation network. switch C turns on just long enough to refresh the voltage In addition, the Thevenin equivalent resistance of the resis- on the BST2 capacitor used to drive switch D. Switches A tor divider controls the gain of the input current limit. To and B are pulse-width modulated to produce the required maintain sufficient gain in this loop, it is recommended duty cycle to support the output regulation voltage. that the Thevenin resistance be greater than 100kΩ. As the input voltage nears the output voltage, switches A and D are on for a greater portion of the switching pe- RUN Comparator riod, providing a direct current path from V to V . IN OUT In addition to serving as a logic-level input to enable the IC, Switches B and C are turned on only enough to ensure the RUN pin includes an accurate internal comparator that proper regulation and/or provide charging of the BST1 allows it to be used to set custom rising and falling on/off and BST2 capacitors. The internal control circuitry will thresholds with the addition of an external resistor divider. determine the proper duty cycle in all modes of operation, When RUN is driven above its logic threshold (0.8V typi- which will vary with load current. cal), the LDO regulator is enabled, which provides power As the input voltage drops well below the output voltage, to the internal control circuitry of the IC. If the voltage the converter operates solely in boost mode. Switch A on RUN is increased further so that it exceeds the RUN turns on at maximum duty cycle and switch B turns on comparator accurate analog threshold (1.2V typical), all just long enough to refresh the voltage on the BST1 ca- functions of the buck-boost converter will be enabled and pacitor used to drive A. Switches C and D are pulse-width a start-up sequence will ensue. modulated to produce the required duty cycle to regulate If RUN is brought below the accurate comparator threshold, the output voltage. the buck-boost converter will inhibit switching, but the 3111fa 13 For more information www.linear.com/LTC3111

LTC3111 OPERATION LDO regulator and control circuitry will remain powered Powering V from an External Source CC unless RUN is brought below its logic threshold. Therefore, The LTC3111’s V regulator can be powered or back-fed CC in order to completely shut down the IC, it is necessary from an external source up to 5.5V. The advantage of back to ensure that RUN is brought below its worst-case low feeding V from a voltage above 4.2V is higher efficiency. CC logic threshold of 0.3V. RUN is a high voltage input and For 5V applications, V can be easily powered from OUT CC can be tied directly to V to continuously enable the IC IN V using an external low current Schottky as shown in OUT when the input supply is present. The RUN pin can be several applications circuits in the Typical Applications driven above V or V as long as it stays within the IN OUT section. operating range of 15V. Back feeding V also improves a light load PWM mode CC With the addition of an optional resistor divider as shown output voltage ripple that occurs when the inductor passes in Figure 3, the RUN pin can be used to establish a user- through zero current by reducing the switch pin anti-cross programmable turn on and turn off threshold. conduction times. A disadvantage of powering V from CC VIN VOUT is that no-load quiescent current increases at lower LTC3111 input voltage in Burst Mode operation as shown in the R5 1.2V – RUN + ENABLE SWITCHING Typical Performance Characteristics (compared to VCC powered from V ). R6 ACCURATE IN THRESHOLD 0.8V – ENABLE SWITCHING LDO Burst Mode OPERATION + AND CONTROL CIRCUITS When the PWM/SYNC pin is held low, the buck-boost LOGIC THRESHOLD converter operates utilizing a variable frequency switch- 3111 F03 ing algorithm designed to improve efficiency at light load Figure 3. Accurate RUN Comparator and reduce the standby current at zero load. In Burst Mode operation, the inductor is charged with fixed peak The buck-boost converter is enabled when the voltage amplitude current pulses and as a result only a fraction on RUN reaches 1.2V (nominal). Therefore, the turn-on of the maximum output current can be delivered when in voltage threshold on VIN is given by: Burst Mode operation. R5 These current pulses are repeated as often as necessary VIN(RUN)=1.2V•1+R6 to maintain the output regulation voltage. The maximum output current, I , which can be supplied in Burst Mode MAX Once the converter is enabled, the RUN comparator in- operation is dependent upon the input and output voltage cludes a built-in hysteresis of approximately 120mV, so as approximated by the following formula: that the turn-off threshold will be approximately 10% lower I V than the turn-on threshold. Put another way, the internal I = PK •η• IN A MAX threshold level for the RUN comparator looks like 1.08V 2 VIN+VOUT after the IC is enabled. where I is the Burst Mode peak current limit (0.8A typi- PK The RUN comparator is relatively noise insensitive, but cal) in amps and η is the efficiency. there may be cases due to PCB layout, very large value If the buck-boost load exceeds the maximum Burst Mode resistors for R5 and R6 or proximity to noisy components current capability, the output rail will lose regulation. In where noise pickup is unavoidable and may cause the Burst Mode operation, the error amplifier is configured for turn-on or turn-off of the IC to be intermittent. In these low power operation and used to hold the compensation cases, a filter capacitor can be added across R6 to ensure pin, COMP, to reduce transients that may occur during proper operation. transitions from and to burst and PWM mode operation. 3111fa 14 For more information www.linear.com/LTC3111

LTC3111 APPLICATIONS INFORMATION The basic LTC3111 application circuit is shown on the front reaching the current limit value. However, in boost mode, page of this data sheet. The external component selection especially at large step-up ratios, the output current capa- is dependent upon the required performance of the IC in bility can also be limited by the total resistive losses in the each particular application given trade-offs such as PCB power stage. These include switch resistances, inductor area, output voltages, output currents, ripple voltages, resistance, and PCB trace resistance. Use of an inductor and efficiency. This section of the data sheet provides with high DC resistance can degrade the output current some basic guidelines and considerations to aid in the capability from that shown in the graph in the Typical selection of external components and the design of the Performance Characteristics section of this data sheet. application circuit. Different inductor core materials and styles have an impact on the size and price of an inductor at any given current Inductor Selection rating. Shielded construction is generally preferred as it To achieve high efficiency, a low ESR inductor should be minimizes the chances of interference with other circuitry. utilized for the buck-boost converter. In addition, the buck- The choice of inductor style depends upon the price, boost inductor must have a saturation current rating that sizing, and EMI requirements of a particular application. is greater than the worst-case average inductor current Table 1 provides a small sampling of inductors that are plus half the ripple current. The peak-to-peak inductor well suited to many LTC3111 buck-boost converter ap- current ripple for buck or boost mode operation can be plications. Within each family (i.e., at a fixed size), the DC calculated from the following formulas: resistance generally increases and the maximum current generally decreases with increased inductance. V V –V 1 ∆IL(P-P_BUCK)= OLUT • IN V OUT• f–tLOW Table 1. Representative Buck-Boost Surface Mount Inductors IN MAX DC V V –V 1 VALUE DCR CURRENT SIZE (mm) ∆IL(P-P_BOOST)= LIN • OUVTOUT IN• f–tLOW CPAoiRlcTr aNfUt MBER (μ H) (m Ω) (A ) W × L × H LPS6225 4.7 65 3.2 6.2 × 6.2 × 2.5 where f is the frequency in Hz and L is the inductance in LPS6235 6.8 75 2.8 6.2 × 6.2 × 3.5 Henries and t is the switch pin minimum low time in Cooper-Bussmann LOW FP3-8R2-R 8.2 74 3.4 7.3 × 6.7 × 3.0 seconds, which is typically 160ns. CD1-150-R 15 50 3.6 10.5 × 10.4 × 4.0 In addition to affecting output current ripple, the inductor Sumida CDRH8D28/HP 10 78 3.0 8.3 × 8.3 × 3.0 value can also impact the stability of the feedback loop. In CDRH8D28NP 4.7 24.7 3.4 8.3 × 8.3 × 3.0 boost mode, the converter transfer function has a right- TOKO half-plane zero at a frequency that is inversely proportional B1047AS-6R8N 6.8 36 2.9 7.6 × 7.6 × 5.0 to the value of the inductor. As a result, a large inductance B1179BS-150M 15 56 2.7 12.0 × 12.0 × 6.0 can move this zero to a frequency that is low enough to Würth 7447789004 4.7 33 2.9 7.3 × 7.3 × 3.2 degrade the phase margin of the feedback loop. It is rec- 744311470 4.7 19.5 6 6.9 × 6.9 × 3.8 ommended that the inductor value be chosen less than Output Capacitor Selection 15μH if the converter is to be used in the boost region. For 800kHz operation, a 4.7μH inductor is recommended A low ESR output capacitor should be utilized at the for 5VOUT and 10μH for 12VOUT. buck-boost converter output in order to minimize output voltage ripple. Multilayer X5R and X7R dielectric ceramic The inductor DC resistance can impact the efficiency of capacitors are an excellent choice as they have low ESR and the buck-boost converter as well as the maximum output are available in small footprints. The capacitor should be current capability at low input voltage. In buck mode, the output current is limited only by the inductor current 3111fa 15 For more information www.linear.com/LTC3111

LTC3111 APPLICATIONS INFORMATION chosen large enough to reduce the output voltage ripple to Capacitor Vendor Information acceptable levels. The minimum output capacitor needed Both the input bypass capacitors and output capacitors for a given output voltage ripple (neglecting the capacitor used with the LTC3111 must be low ESR and designed ESR and ESL) can be calculated by the following formulas: to handle the large AC currents generated by switching I •t converters. This is important to maintain proper functioning ∆V = LOAD LOW P-P(BUCK) C of the IC and to reduce input/output ripple. Many modern OUT low voltage ceramic capacitors experience significant I V –V +t •f•V loss in capacitance from their rated value with increased ∆VP-P(BOOST)= f•LCOAD • OUT INV LOW IN DC bias voltages. For example, it is not uncommon for a OUT OUT small surface mount ceramic capacitor to lose more than 50% of its rated capacitance when operated near its rated where f is the frequency in Hz, C is the output capaci- OUT voltage. As a result, it is sometimes necessary to use a tance in μF, I is the output current in amps and t LOAD LOW larger value capacitance or a capacitor with a larger case is the switch pin minimum low time in seconds, which is size than required in order to actually realize the intended typically 160ns. capacitance at the full operating voltage. For details, con- In addition to output ripple generated across the output sult the capacitor vendor’s curve of capacitance versus capacitor, there is also output ripple produced across DC bias voltage. the internal resistance of the output capacitor. The ESR- The capacitors listed in Table 2 provide a sampling of small generated output voltage ripple is proportional to the surface mount ceramic capacitors that are well suited to series resistance of the output capacitor and is given by LTC3111 application circuits. All listed capacitors are either the following expression: X5R or X7R dielectric in order to ensure that capacitance ∆V =ILOAD•RESR ≅I •R loss over temperature is minimized. P-P(BUCK) 1–t •f LOAD ESR LOW Table 2. Representative Bypass and Output Capacitors I •R •V I •R •V VALUE VOLTAGE SIZE (mm) L × W × H ∆VP-P(BOOST)= LOVAD(1–EtSR •OfU)T ≅ LOAD VESR OUT PART NUMBER (μF) (V) (FOOTPRINT) IN LOW IN AVX 12103D226MAT2A 22 25 3.2 × 2.5 × 2.79 where R is the series resistor of the output capacitor ESR X5R Ceramic and all other terms are as previously defined. Kemet C220X226K3RACTU 22 25 5.7 × 5.0 × 2.4 Input Capacitor Selection X7R Ceramic A700D226M016ATE030 22 16 7.3 × 4.3 × 2.8 It is recommended that a low ESR ceramic capacitor with Al Poly, 25mΩ a value of at least 10μF be located as close to the V pin Murata IN GRM32ER71E226KE15L 22 25 3.2 × 2.5 × 2.5 as possible. In addition, the return trace from the pin to X7R Ceramic the ground plane should be made as short as possible. Panasonic It is important to minimize any stray resistance from the ECJ-4YB1E226M 22 25 3.2 × 2.5 × 2.5 converter to the battery or power source. If cabling is X5R Ceramic required to connect the LTC3111 to the battery or power Sanyo 25SVPF47M 47 25 6.6 × 6.6 × 5.9 supply, a higher ESR capacitor or a series resistor with a OS-CON, 30mΩ low ESR capacitor in parallel with the low ESR capacitor Vishay may be required to damp out ringing caused by the cable 94SVPD476X0035F12 47 35 10.3 × 10.3 × 12.6 OS-CON, 30mΩ inductance. 3111fa 16 For more information www.linear.com/LTC3111

LTC3111 APPLICATIONS INFORMATION PCB Layout Considerations 2. The exposed pad is the power ground connection for the LTC3111. Multiple vias should connect the back The LTC3111 switches large currents at high frequencies. pad directly to the ground plane. In addition maximi- Special attention should be paid to the PCB layout to en- zation of the metallization connected to the back pad sure a stable, noise-free and efficient application circuit. will improve the thermal environment and improve the Figure 4 presents a representative PCB layout to outline power handling capabilities of the IC. some of the primary considerations. A few key guidelines are outlined below: 3. The circled components and their connections should all be placed over a complete ground plane to minimize 1. All circulating high current paths should be kept as short loop cross-sectional areas. This minimizes EMI and as possible. This can be accomplished by keeping the reduces inductive drops. routes to all circled components in the figure below as short and as wide as possible. Capacitor ground 4. Connections to all of the circled components should be connections should via down to the ground plane in made as wide as possible to reduce the series resistance. the shortest route possible. The bypass capacitors on This will improve efficiency and maximize the output V should be placed as close to the IC as possible and current capability of the buck-boost converter. IN should have the shortest possible paths to ground. THERMAL AND PGND VIAS CIN COUT CBST1 CBST2 Figure 4a. Top and Fabrication Layer of Example PCB Figure 4b. Bottom and Fabrication Layer of Example PCB 3111fa 17 For more information www.linear.com/LTC3111

LTC3111 APPLICATIONS INFORMATION 5. To prevent large circulating currents from disrupting mum low time, which is typically 160ns. The parameter the output voltage sensing, the ground for each resistor R represents the average series resistance of the power S divider should be returned to the ground plane using stage and can be approximated as twice the average power a via placed close to the IC and away from the power switch resistance plus the DC resistance of the inductor. connections. G =G •G •G BUCK DIVIDER PWM POWER 6. Keep the connection from the resistor dividers to the 18 feedback pins (FB pin) as short as possible and away G = DIVIDER from the switch pin connections. V IN 7. Crossover connections should be made on inner copper G =2.5•(1–t •f) PWM LOW layers if available. If it is necessary to place these on the ground plane, make the trace on the ground plane V •R G = IN as short as possible to minimize the disruption to the POWER (1–t •f)•(R+R ) ground plane. LOW S Notice that the gain of the analog divider cancels the input Buck Mode Small-Signal Model voltage dependence of the power stage. As a result, the The LTC3111 uses a voltage mode control loop to maintain buck mode gain is approximated by a constant as given regulation of the output voltage. An externally compen- by the following equation: sated error amplifier drives the COMP pin to generate the R appropriate duty cycle of the power switches. Use of an G =45• ≅45=33dB BUCK R+R external compensation network provides the flexibility for S optimization of closed-loop performance over the wide The buck mode transfer function has a single zero which variety of output voltages, switching frequencies, and is generated by the ESR of the output capacitor. The zero external component values supported by the LTC3111. frequency, f , is given by the following expression where Z The small-signal transfer function of the buck-boost con- R and C are the ESR and value of the output filter ca- C O verter is different in the buck and boost modes of operation pacitor respectively. and care must be taken to ensure stability in both operating 1 regions. When stepping down from a higher input voltage f = Z 2•π•R •C to a lower output voltage, the converter will operate in C O buck mode and the small-signal transfer function from In most applications, an output capacitor with a very low the error amplifier output COMP, to the converter output ESR is utilized in order to reduce the output voltage ripple voltage is given by the following equation: to acceptable levels. Such low values of capacitor ESR s result in a very high frequency zero and as a result the zero 1+ V 2•π•f is commonly too high in frequency to significantly impact O =G Z VCOMP BUCK BUCK s s 2 compensation of the feedback loop. The denominator of 1+ + the buck mode transfer function exhibits a pair of resonant 2•π•f •Q 2•π•f O O poles generated by the LC filtering of the power stage. The The gain term, G , is comprised of three different resonant frequency of the power stage, f , is given by the BUCK O components: the gain of the analog divider, the gain of the following expression where L is the value of the inductor: pulse-width modulator, and the gain of the power stage as 1 R+R 1 vgoivlteang bey t oth teh feo clloonwvinergt eerx,p fr eiss sthioen ssw withcehrien gV IfNr eisq utheen cinyp, uRt fO=2•π• L•CO(R+SRC) ≅2•π• L•CO is the load resistance, and t is the switch pin mini- LOW 3111fa 18 For more information www.linear.com/LTC3111

LTC3111 APPLICATIONS INFORMATION The quality factor, Q, has a significant impact on compen- the same as in buck mode operation, but the gain of the sation of the voltage loop since a higher Q factor produces analog divider and power stage in boost mode are given a sharper loss of phase near the resonant frequency. The by the following equation: quality factor is inversely related to the amount of damping 18 in the power stage and is substantially influenced by the G = DIVIDER V average series resistance of the power stage, R . Lower OUT S values of RS will increase the Q and result in a sharper V 2 G = OUT loss of phase near the resonant frequency and will require POWER (1–t •f)•V more phase boost or lower bandwidth to maintain an LOW IN adequate phase margin. By combining the individual terms, the total gain in boost mode can be reduced to the following expression. Notice L•C (R+R )•(R+R ) Q= O C S that unlike in buck mode, the gain in boost mode is a R•R •C +L+C •R •(R+R ) C O O S C function of both the input and output voltage: L•CO G =45•VOUT ≅ BOOST L VIN +C •R O S R In boost mode operation, the frequency of the right-half- plane zero, f , is given by the following expression. Boost Mode Small-Signal Model RHPZ The frequency of the right-half-plane zero decreases at When stepping up from a lower input voltage to a higher higher loads and with larger inductors: output voltage, the buck-boost converter will operate in boost mode where the small-signal transfer function from R•(1–tLOW •f)2•VIN2 f − control voltage, V , to the output voltage is given by RHPZ 2•π•L•V 2 COMP OUT the following expression: In boost mode, the resonant frequency of the power stage s s has a dependence on the input and outputvoltage as shown 1+ • 1– VO =G 2•π•fZ 2•π•fRHPZ by the following equation: VCOMP BOOST BOOST s s 2 R•V 2 1+ + R + IN 2•π•fO•Q 2•π•fO f = 1 • S VOUT2 ≅ 1 • VIN • 1 O 2•π L•C •(R+R ) 2•π V L•C In boost mode operation, the transfer function is character- O C OUT O ized by a pair of resonant poles and a zero generated by the Finally, the magnitude of the quality factor of the power ESR of the output capacitor as in buck mode. However, in stage in boost mode operation is given by the following addition there is a right-half-plane zero which generates expression: increasing gain and decreasing phase at higher frequen- cies. As a result, the crossover frequency in boost mode R•V 2 operation generally must be set lower than in buck mode L•CO•R•RS+ V IN2 OUT in order to maintain sufficient phase margin. Q= L+C •R •R O S The boost mode gain, G , is comprised of three BOOST components: the analog divider, the pulse width modula- tor and the power stage. The gain of the PWM remains 3111fa 19 For more information www.linear.com/LTC3111

LTC3111 APPLICATIONS INFORMATION Compensation Of The Voltage Loop GAIN The small-signal models of the LTC3111 reveal that the transfer function from the error amplifier output, COMP, –40dB/DEC to the output voltage is characterized by a set of resonant poles and a possible zero generated by the ESR of the –20dB/DEC output capacitor as shown in the Bode plot of Figure 5. In boost mode operation, there is an additional right-half- PHASE plane zero that produces phase lag and increasing gain at higher frequencies. Typically, the compensation network BUCK MODE is designed to ensure that the loop crossover frequency is low enough that the phase loss from the right-half-plane BOOST MODE zero is minimized. The low frequency gain in buck mode is a constant, but varies with both VIN and VOUT in boost fO fRHPZ 3111 F05 mode. Figure 5: Buck-Boost Converter Bode Plot For charging or other applications that do not require an optimized output voltage transient response, a simple Type I compensation network as shown in Figure 6 can VOUT LTC3111 be used to stabilize the voltage loop. To ensure sufficient R1 phase margin, the gain of the error amplifier must be low 0.8V + FB – enough that the resultant crossover frequency of the control C1 loop is well below the resonant frequency. COMP R2 SGND In most applications, the low bandwidth of the Type I com- 3111 F06 pensated loop will not provide sufficient transient response performance. To obtain a wider bandwidth feedback loop, Figure 6: Error Amplifier with Type I Compensation optimize the transient response, and minimize the size of the output capacitor, a Type III compensation network as shown in Figure 7 is required. A Bode plot of the typical Type III compensation network VOUT is shown in Figure 8. The Type III compensation network LTC3111 provides a pole near the origin which produces a very high RFF R1 loop gain at DC to minimize any steady-state error in the CFF FB0.8V + – regulation voltage. Two zeros located at f and f provide sufficient phase boost to allow thZeE lRoOo1p crosZsEoRvOe2r RFB CFB COMP R2 frequency to be set above the resonant frequency, f , of CPOLE O SGND the power stage. The Type III compensation network also 3111 F07 introduces a second and third pole. The second pole, at frequency f , reduces the error amplifier gain to a POLE2 Figure 7: Error Amplifier with Type III Compensation zero slope to prevent the loop crossover from extending 3111fa 20 For more information www.linear.com/LTC3111

LTC3111 APPLICATIONS INFORMATION where all frequencies are in Hz, resistances are in ohms, and capacitances are in farads. GAIN 1 f = –20dB/DEC ZERO1 2•π•R •C FB FB –20dB/DEC 1 1 f = ≅ ZERO2 2•π(R1+R )•C 2•π•R1•C FF FF FF 1 1 PHASE f = ≅ f POLE2 2•π•CFB•CPOLE •RFB 2•π•RFB•CPOLE fZERO1 fPOLE2fPOLE3 3111 F08 CFB+CPOLE fZERO2 1 Figure 8: Type III Compensation Bode Plot fPOLE3= 2•π•R •C FF FF too high in frequency. The third pole at frequency fPOLE3 In most applications the compensation network is designed provides attenuation of high frequency switching noise. so that the loop crossover frequency is above the resonant frequency of the power stage, but sufficiently below the The transfer function of the compensated Type III error boost mode right-half-plane zero to minimize the additional amplifier from the input of the resistor divider to the output phase loss. Once the crossover frequency is decided upon, of the error amplifier, COMP, is: the phase boost provided by the compensation network s s is centered at that point in order to maximize the phase 1+ • 1+ V 2•π•f 2•π•f margin. A larger separation in frequency between the COMP =G • ZERO1 ZERO2 V COMP s s zeros and higher order poles will provide a higher peak O s• 1+ • 1+ 2•π•f 2•π•f phase boost but may also increase the gain of the error POLE2 POLE3 amplifier which can push out the loop crossover to a The compensation gain is given by the following equation. higher frequency. The simpler approximate value is sufficiently accurate in The Q of the power stage can have a significant influence most cases since C is typically much larger in value FB on the design of the compensation network because it than C . POLE determines how rapidly the 180° of phase loss in the power 1 1 stage occurs. For very low values of series resistance, R , G ≅ ≅ S COMP R1•(C +C ) R1•C the Q will be higher and the phase loss will occur sharply. FB POLE FB In such cases, the phase of the power stage will fall rapidly The pole and zero frequencies of the Type III compensation to –180° above the resonant frequency and the total phase network can be calculated from the following equations margin must be provided by the compensation network. 3111fa 21 For more information www.linear.com/LTC3111

LTC3111 APPLICATIONS INFORMATION However, with higher losses in the power stage (larger the worst-case inductor current ripple to less than 1A peak R ) the Q factor will be lower and the phase loss will occur to peak. A low ESR output capacitor with a value of 22µF S more gradually. As a result, the power stage phase will is specified to yield a worst-case output voltage ripple not be as close to –180° at the crossover frequency and (occurring at the worst-case step-up ratio and maximum less phase boost is required of the compensation network. load current) of approximately 20mV. In summary, the key power stage specifications for this LTC3111 example The LTC3111 error amplifier is designed to have a fixed application are given below. maximum bandwidth in order to provide rejection of switching noise to prevent it from interfering with the f = 0.8MHz, t = 160ns LOW control loop. From a frequency domain perspective, this V = 3.5V to 15V IN can be viewed as an additional single pole as illustrated V = 5V at R = 10Ω in Figure 9. The nominal frequency of this pole is 400kHz. OUT For typical loop crossover frequencies below about 60kHz C = 22µF, R = 10mΩ OUT C the phase contributed by this additional pole is negligible. L = 4.7µH, R = 25mΩ However, for loops with higher crossover frequencies this L additional phase loss should be taken into account when R = 200mΩ S designing the compensation network. With the power stage parameters specified, the compen- sation network can be designed. In most applications, LTC3111 the most challenging compensation corner is boost mode operation at the greatest step-up ratio and highest 0.8V + RFILT FB load current since this generates the lowest frequency – CFILT right-half-plane zero and results in the greatest phase COMP loss. Therefore, a reasonable approach is to design the 3111 F09 compensation network at this worst-case corner and then verify that sufficient phase margin exists across all other Figure 9. Internal Loop Filter operating conditions. In this example application, at V = IN Loop Compensation Example 3.5V and the full 500mA load current, the right-half-plane zero will be located at 136kHz and this will be a dominant This section provides an example illustrating the design of factor in determining the bandwidth of the control loop. a compensation network for a typical LTC3111 application circuit. In this example a 5V regulated output voltage is The first step in designing the compensation network is generated with the ability to supply a 500mA load from an to determine the target crossover frequency for the com- input power source ranging from 3.5V to 15V. To reduce pensated loop. A reasonable starting point is to assume switching losses a 800kHz switching frequency has been that the compensation network will generate a peak phase chosen for this example. In this application the maximum boost of approximately 60°. Therefore, in order to obtain inductor current ripple will occur at the highest input volt- a phase margin of 60°, the loop crossover frequency, f , C age. An inductor value of 4.7µH has been chosen to limit should be selected as the frequency at which the phase 3111fa 22 For more information www.linear.com/LTC3111

LTC3111 APPLICATIONS INFORMATION of the buck-boost converter reaches –180°. As a result, at model equations using LTspice® software. In this case, the loop crossover frequency the total phase will be simply the phase reaches –180° at 40kHz making f = 40kHz the C the 60° of phase provided by the error amplifier as shown: target crossover frequency for the compensated loop. Phase Margin = ϕ + ϕ + 180° From the Bode plot of Figure 10 the gain of the power stage BUCK-BOOST ERRORAMPLIFIER at the target crossover frequency is 13.5dB. Therefore, in = –180° + 60° + 180° = 60° order to make this frequency the crossover frequency in Similarly, if a phase margin of 45° is required, the target the compensated loop, the total loop gain at f must be C crossover frequency should be picked as the frequency adjusted to 0dB. To achieve this, the gain of the compen- at which the buck-boost converter phase reaches –195° sation network must be designed to be –13.5dB at the so that the combined phase at the crossover frequency crossover frequency. yields the desired 45° of phase margin. At this point in the design process, there are three con- This example will be designed for a 60° phase margin to straints that have been established for the compensation ensure adequate performance over parametric variations network. It must have –13.5dB of gain at f = 40kHz, a peak C and varying operating conditions. As a result, the target phase boost of 60° that is centered at f = 40kHz. One way C crossover frequency, fC, will be the point at which the to design a compensation network to meet these targets phase of the buck-boost converter reaches –180°. It is is to simulate the compensation error amplifier Bode plot generally difficult to determine this frequency analytically in LTspice for the typical compensation network shown given that it is significantly impacted by the Q factor of on the front page of this data sheet. Then, the gain, pole the resonance in the power stage. As a result, it is best and zero frequencies can be iteratively adjusted until the determined from a Bode plot of the buck-boost converter required constraints are met. Alternatively, an analytical as shown in Figure 10. This Bode plot is for the LTC3111 approach can be used to design a compensation network buck-boost converter using the previously specified power with the desired phase boost, center frequency and gain. stage parameters and was generated from the small-signal In general, this procedure can be cumbersome due to the large number of degrees of freedom in the Type III com- 40 90 pensation network. However the design process can be 30 45 simplified by assuming that both the compensation zeros GAIN 20 0 occur at the same frequency, fZ, and both higher order poles (f and f ) occur at the common frequency, 10 –45 POLE2 POLE3 dB) 0 PHASE –90 (DEG fP. In most cases this is a reasonable assumption since ( ) the zeros are typically located between 1kHz and 10kHz –10 –135 and the poles are typically located near each other at much –20 –180 higher frequencies. Given this assumption, the maximum –30 –255 phase boost, provided by the compensation error amplifier fC = 40kHz is determined simply by the amount of separation between –40 –270 10 100 1k 10k 100k 1M the poles and zeros as shown by the following equation: (Hz) 3111 F10 f Figure 10. Converter Bode Plot VIN = 3.5V, VOUT = 5V, R = 10Ω φMAX =4•arctan P–270° f Z 3111fa 23 For more information www.linear.com/LTC3111

LTC3111 APPLICATIONS INFORMATION A reasonable choice is to pick the frequency of the poles, This equation completes the set of constraints needed to f , to be 50 times higher than the frequency of the zeros, determine the compensation component values. Specifi- P fZ, which provides a peak phase boost of approximately cally, the two zeros, fZERO1 and fZERO2, should be located 60° as was assumed previously. Next, the phase boost near 5.71kHz. The two poles, fPOLE2 and fPOLE3, should be must be centered so that the peak phase occurs at the located near 280kHz and the gain should be set to provide target crossover frequency. The frequency of the maximum a gain at the crossover frequency of GCENTER = –13.5dB. phase boost, f , is the geometric mean of the pole CENTER The first step in defining the compensation component and zero frequency as: values is to pick a value for R1 that provides an acceptably low quiescent current through the resistor divider. A value f = f •f = 50•f ≅7•f CENTER P Z Z Z of R1 = 1MΩ is a reasonable choice. Next, the value of C FB Therefore, in order to center the phase boost given a factor can be found in order to set the error amplifier gain at the of 50 separation between the pole and zero frequencies, crossover frequency to –13.5dB as follows: the zero should be located at one-seventh of the crossover 50 frequency and the poles should be located at seventh times G =–13.5dB=20•log CENTER the crossover frequency as given by the following equation: 2•π•40kHz•1MΩ•CFB f 40kHz 50 f = C = =5.71kHz C = ≅1000pF Z 7 7 FB –13.5 2•π•40kHz•1MΩ•10 20 f =7•f =7•40kHz=280kHz P C The compensation poles can be set at 280kHz and the This placement of the poles and zeros will yield a peak phase zeros at 5.71kHz by using the expressions for the pole and boost of 60° that is centered at the crossover frequency, zero frequencies given in the previous sections. Setting f . Next, in order to produce the desired target crossover the frequency of the first zero, f , to 5.71kHz results C ZERO1 frequency, the gain of the compensation network at the in the following value for R : FB point of maximum phase boost, G , must be set to CENTER 1 –13.5dB. The gain of the compensated error amplifier at R = ≅28.0kΩ FB 2•π•5.71kHz•1000pF the point of the phase gain is given by: 2•π•f This leaves the free parameter, CPOLE, to set frequency G =10•log P dB f to the common pole frequency of 280kHz as given: CENTER (2•π•f )3•(R1•C )2 POLE1 Z FB 1 C = ≅22pF POLE Assuming a multiple of 50 separation between the pole 2•π•280kHz•28kΩ and zero frequencies this can be simplified to the follow- ing expression: 50 G =20•log dB CENTER 2•π•f •R1•C C FB 3111fa 24 For more information www.linear.com/LTC3111

LTC3111 APPLICATIONS INFORMATION Next, C can be chosen to set the second zero, f , to FF ZERO2 40 90 the common zero frequency of 5.71kHz. 30 40kHz, 57° 1 20 45 CFF = ≅27pF 40kHz, –14dB PHASE 2•π•5.71kHz•1MΩ 10 GAIN Finally, the resistor value RFF can be chosen to place the (dB) 0 0 (DEG) second pole at 280kHz. –10 –20 –45 1 R = ≅20kΩ FF –30 2•π•280kHz•27pF –40 –90 10 100 1k 10k 100k 1M Now that the pole frequencies, zero frequencies and gain (Hz) of the compensation network have been established, the 3111 F11 next step is to generate a Bode plot for the compensated Figure 11: Compensation Error Amplifier Bode Plot error amplifier to confirm its gain and phase properties. A Bode plot of the error amplifier with the designed com- 60 180 pensation component values is shown in Figure 11. The 50 135 Bode plot confirms that the peak phase occurs at 40kHz PHASE 40kHz, 59° 40 90 and the phase boost at that point is 57°. In addition, the 30 45 gain at the peak phase frequency is –14dB which is close 20 0 to the design target. (dB) 10 GAIN –45 (DEG) The final step in the design process is to compute the 0 –90 Bode plot for the entire designed compensation network –10 –135 and confirm its phase margin and crossover frequency. –20 –180 –30 –225 The complete loop Bode plot for this example is shown –40 –270 in Figure 12. The loop crossover frequency is 40kHz and 10 100 1k 10k 100k 1M the phase margin is approximately 59°. (Hz) 3111 F12 The Bode plot for the complete loop should be checked over Figure 12: Complete Loop Bode Plot all operating conditions and for variations in component values to ensure that sufficient phase margin exist in all cases. The stability of the loop should also be confirmed via time domain simulation and by the transient response of the converter in the actual circuit. 3111fa 25 For more information www.linear.com/LTC3111

LTC3111 TYPICAL APPLICATIONS 1, 2, 3 Li-Ion to 5V 4.7µH 0.1µF 0.1µF SW1 SW2 BST1 BST2 VOUT 3V TO 12V.6IVN VIN VOUT 680pF 57V50mA 1 TO 3-CELL + 10µF LTC3111 COMP 26.1k 1M 20k 22µF VIN > 4V Li-Ion BURST PWM PWM/SYNC 33pF 27pF RUN FB R NUMBER SNSGND VCC 191k OF CELLS R SGND PGND 1µF 1 274k 154k 3111 TA02a 2 698k 3 1.13M Wide V to 5V Efficiency IN OUT 100 90 80 %) Y ( 70 C N E CI 60 FI F E 50 VIN = 3.6V 40 VIN = 7.2V VIN = 10.8V 30 0.0001 0.001 0.01 0.1 1 10 LOAD CURRENT (A) 3111 TA02b 3111fa 26 For more information www.linear.com/LTC3111

LTC3111 TYPICAL APPLICATIONS LTC3111 Synchronized to a 1.5MHz Clock, 5V/1A Output 2.2µH 0.1µF 0.1µF SW1 SW2 BST1 BST2 VOUT 2.5V TO 1V5IVN VIN VOUT 270pF 51VA 10µF LTC3111 57.6k 22µF VIN > 5V 1.5MHz CLOCK COMP 1M PWM/SYNC 15pF MBR0520L OFF ON RUN FB OPTIONAL SNSGND VCC 191k SGND PGND 1µF 3111 TA03a PWM/SYNC 5V/DIV SW1 10V/DIV SW2 5V/DIV INDUCTOR CURRENT 1A/DIV 500ns/DIV 3111 TA03b 3.3V Backup from a High Voltage Capacitor Bank Runs Down to V = 2V with 500mA Load IN 4.7µH 0.1µF 0.1µF SW1 SW2 2V TO 1V5IVN C21IN4mF 100µF VCC BVISNT1 LTC3111 BVSOTU2T 1600pF24.3k 20k 33µF V35.0O30UVmTA COMP 1M PWM/SYNC 36pF MBR0520L 33pF OPTIONAL RUN FB VCC SNSGND VCC 316k SGND PGND 1µF 3111 TA04a VIN POWER SUPPLY REMOVED 5V/DIV VOUT 2V/DIV IOUT 500mA/DIV 2 SEC/DIV 3111 TA04b 3111fa 27 For more information www.linear.com/LTC3111

LTC3111 TYPICAL APPLICATIONS Stepped Response from 1 or 2 Li-Ion to 12V Adapter Source V = 5V OUT 1- OR 2-SERIES Li-Ion CELLS 4.7µH LT®4352 IDEAL DIODE 0.1µF 0.1µF SW1 SW2 B520C BST1 BST2 VOUT 12V 5V ADAPTER VIN VOUT 680pF 1.5A 47µF LTC3111 26.1k 20k 22µF VIN > 5V COMP 1M BURST PWM PWM/SYNC 33pF 27pF OFF ON RUN FB SNSGND VCC 191k 1µF SGND PGND 3111 TA05a VOUT 500mV/DIV VIN 2V/DIV TWO Li-Ion CELLS INDUCTOR CURRENT 1A/DIV IOUT = 500mA 1ms/DIV 3111 TA05b Custom Input Undervoltage Lockout Thresholds 4.7µH 0.1µF 0.1µF SW1 SW2 5V TO 1V5IVN 10µF VCC BVSINT1 LTC3111 CBVOSOMTUP2T 680pF26.1k 1M 20k 22µF V51V.O5UAT ENABLED WHEN VIN REACHED 5V 1M PWM/SYNC 27pF 33pF RUN FB DISFAALBLLSE DB EWLHOEWN 4V.5INV 316k SNSGND VCC VCC 191k SGND PGND 1µF 3111 TA08a VIN 10V/DVIIVN 10V/DIV VOUT VOUT 5V/DIV 5V/DIV INDUCTOR INDUCTOR CURRENT CURRENT 1A/DIV 1A/DIV RLOAD = 3.3Ω 2ms/DIV 3111 TA08b RLOAD = 3.3Ω 2ms/DIV 3111 TA08c 3111fa 28 For more information www.linear.com/LTC3111

LTC3111 PACKAGE DESCRIPTION Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings. DE Package 14-Lead Plastic DFN (4mm × 3mm) (Reference LTC DWG # 05-08-1708 Rev B) 0.70 ±0.05 3.60 ±0.05 3.30 ±0.05 2.20 ±0.05 1.70 ±0.05 PACKAGE OUTLINE 0.25 ±0.05 0.50 BSC 3.00 REF RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS APPLY SOLDER MASK TO AREAS THAT ARE NOT SOLDERED 4.00 ±0.10 R = 0.115 0.40 ±0.10 TYP (2 SIDES) 8 14 R = 0.05 TYP 3.30 ±0.10 3.00 ±0.10 (2 SIDES) 1.70 ±0.10 PIN 1 NOTCH PIN 1 R = 0.20 OR TOP MARK 0.35 × 45° (SEE NOTE 6) CHAMFER (DE14) DFN 0806 REV B 7 1 0.200 REF 0.75 ±0.05 0.25 ±0.05 0.50 BSC 3.00 REF 0.00 – 0.05 BOTTOM VIEW—EXPOSED PAD NOTE: 1. DRAWING PROPOSED TO BE MADE VARIATION OF VERSION (WGED-3) IN JEDEC PACKAGE OUTLINE MO-229 2. DRAWING NOT TO SCALE 3. ALL DIMENSIONS ARE IN MILLIMETERS 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE 5. EXPOSED PAD SHALL BE SOLDER PLATED 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE 3111fa 29 For more information www.linear.com/LTC3111

LTC3111 PACKAGE DESCRIPTION Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings. MSE Package 16-Lead Plastic MSOP, Exposed Die Pad (Reference LTC DWG # 05-08-1667 Rev F) BOTTOM VIEW OF EXPOSED PAD OPTION 2.845 ±0.102 2.845 ±0.102 (.112 ±.004) 0.889 ±0.127 (.112 ±.004) (.035 ±.005) 1 8 0.35 REF 5.10 1.651 ±0.102 3.20 – 3.45 1.651 ±0.102 (.M20IN1) (.065 ±.004) (.126 – .136) (.065 ±.004) 0.12 REF DETAIL “B” CORNER TAIL IS PART OF DETAIL “B” THE LEADFRAME FEATURE. FOR REFERENCE ONLY 16 9 0.305 ±0.038 0.50 NO MEASUREMENT PURPOSE (.0120 ±.0015) (.0197) 4.039 ±0.102 TYP BSC (.159 ±.004) (NOTE 3) 0.280 ±0.076 RECOMMENDED SOLDER PAD LAYOUT 16151413121110 9 (.011 ±.003) REF DETAIL “A” 0.254 (.010) 3.00 ±0.102 0° – 6° TYP 4.90 ±0.152 (.118 ±.004) (.193 ±.006) GAUGE PLANE (NOTE 4) 0.53 ±0.152 (.021 ±.006) 1234567 8 DETAIL “A” 1.10 0.86 0.18 (.043) (.034) (.007) MAX REF SEATING PLANE 0.17 – 0.27 0.1016 ±0.0508 (.007 – .011) (.004 ±.002) TYP 0.50 NOTE: (.0197) MSOP (MSE16) 0213 REV F 1. DIMENSIONS IN MILLIMETER/(INCH) BSC 2. DRAWING NOT TO SCALE 3. DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE 4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX 6. EXPOSED PAD DIMENSION DOES INCLUDE MOLD FLASH. MOLD FLASH ON E-PAD SHALL NOT EXCEED 0.254mm (.010") PER SIDE. 3111fa 30 For more information www.linear.com/LTC3111

LTC3111 REVISION HISTORY REV DATE DESCRIPTION PAGE NUMBER A 1/14 Clarified graphs 1, 4, 5, 6 3111fa 31 Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representa- tion that the interconnecFtoiorn m ofo itrse c iinrcfuoitrsm asa tdieosnc rwibwedw h.elirneeina wr.cillo nmot/ iLnTfrCin3g1e1 o1n existing patent rights.

LTC3111 TYPICAL APPLICATION Regulated 12V Output from Wide Range Input Supply Wide V to 12V Efficiency IN OUT 100 10µH PWM 90 BURST 0.1µF 0.1µF SW1 SW2 80 BST1 BST2 VOUT %) 2.5V TO 1V5IVN VIN VOUT 1000pF 102.5VA, VIN > 5V NCY ( 70 10µF LTC3111 44.2k 20k 22µF 1.0A, VIN > 9V CIE 60 VCC COMP 2.21M FFI E BURST PWM PWM/SYNC 39pF 18pF 50 OFF ON RUN FB 40 SNSGND VCC 158k VVIINN == 51V2V SGND PGND 1µF 30 3111 TA06a 0.0001 0.001 0.01 0.1 1 10 LOAD CURRENT (A) 3111 TA06b RELATED PARTS PART NUMBER DESCRIPTION COMMENTS LTC3533 2A (I ), 2MHz Synchronous Buck-Boost DC/DC V : 1.8V to 5.5V, V : 1.8V to 5.25V, I = 40μA, I < 1μA, DFN Package OUT IN OUT Q SD Converter LTC3113 3A (I ), 2MHz Low Noise Buck-Boost DC/DC V : 1.8V to 5.5V, V : 1.8V to 5.5V, I = 40μA, I < 1μA, DFN and TSSOP OUT IN OUT Q SD Converter Packages LTC3534 7V, 500mA (I ), Synchronous Buck-Boost DC/DC V : 2.4V to 7V, V : 1.8V to 7V, I = 25μA, I < 1μA, DFN and GN Packages OUT IN OUT Q SD Converter LTC3129/ 15V, 200mA (I ), Synchronous Buck-Boost DC/DC V : 2.42V to 15V, V : 1.4V to 15.75V, I = 1.3μA, I < 100nA, QFN and OUT IN OUT Q SD LTC3129-1 Converter with 1.3µA Quiescent Current MSOP Packages LTC3112 15V, 2.5A (I ), Synchronous Buck-Boost DC/DC V : 2.7V to 15V, V = 5V, I = 50μA, I < 1μA, DFN and TSSOP Packages OUT IN OUT Q SD Converter LTC3785 10V, High Efficiency, Synchronous, No R ™ V : 2.7V to 10V, V : 2.7V to 10V, I = 86μA, I < 15μA, QFN Package SENSE IN OUT Q SD Buck-Boost Controller LTC3115-1/ 40V, 2A (I ), Synchronous Buck-Boost DC/DC V : 2.7V to 40V, V = 2.7V to 40V, I = 30μA, I < 1μA, DFN and TSSOP OUT IN OUT Q SD LTC3115-2 Converter Packages LTC3789 High Efficiency, Synchronous, 4-Switch Buck-Boost V : 4V to 38V, V : 0.8V to 38V, I = 3mA, I < 60μA, QFN and SSOP IN OUT Q SD Converter Packages LTC3122 15V, 2.5A (I ), Synchronous Step-Up DC/DC V :1.8V to 5.5V, V : 2.2V to 15V. I = 25µA, I < 1µA, DFN and MSOP OUT IN OUT Q SD Converter with Output Disconnect Packages 3111fa 32 Linear Technology Corporation LT 0114 REV A • PRINTED IN USA 1630 McCarthy Blvd., Milpitas, CA 95035-7417 For more information www.linear.com/LTC3111 (408) 432-1900 ● FAX: (408) 434-0507 ● www.linear.com/LTC3111 LINEAR TECHNOLOGY CORPORATION 2013

Datasheet下载

Datasheet下载