ICGOO在线商城 > 集成电路(IC) > 数据采集 - 数模转换器 > LTC1661CN8#PBF

- 型号: LTC1661CN8#PBF

- 制造商: LINEAR TECHNOLOGY

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

LTC1661CN8#PBF产品简介:

ICGOO电子元器件商城为您提供LTC1661CN8#PBF由LINEAR TECHNOLOGY设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 LTC1661CN8#PBF价格参考。LINEAR TECHNOLOGYLTC1661CN8#PBF封装/规格:数据采集 - 数模转换器, 10 位 数模转换器 2 8-PDIP。您可以下载LTC1661CN8#PBF参考资料、Datasheet数据手册功能说明书,资料中有LTC1661CN8#PBF 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC) |

| 描述 | IC D/A CONV 10BIT MICRPWR 8-DIP |

| 产品分类 | |

| 品牌 | Linear Technology |

| 数据手册 | http://www.linear.com/docs/2060 |

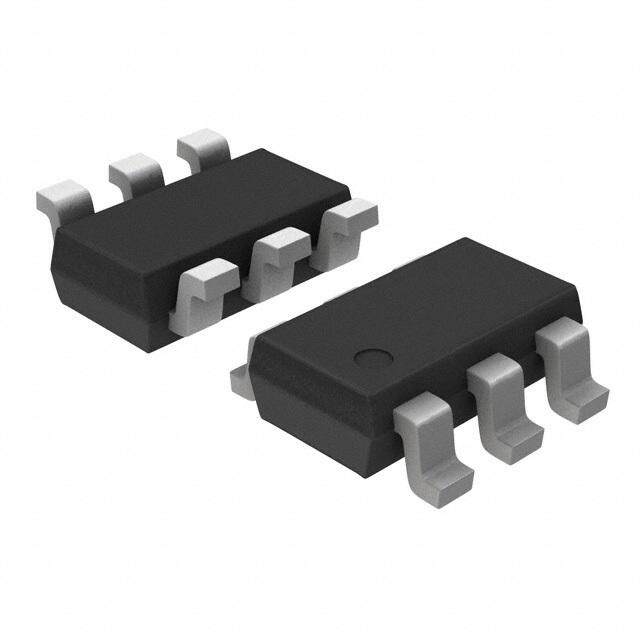

| 产品图片 |

|

| 产品型号 | LTC1661CN8#PBF |

| rohs | 无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | - |

| 产品目录页面 | |

| 位数 | 10 |

| 供应商器件封装 | 8-PDIP |

| 其它名称 | LTC1661CN8PBF |

| 包装 | 管件 |

| 安装类型 | 通孔 |

| 封装/外壳 | 8-DIP(0.300",7.62mm) |

| 工作温度 | 0°C ~ 70°C |

| 建立时间 | 30µs |

| 数据接口 | 串行 |

| 标准包装 | 50 |

| 电压源 | 单电源 |

| 转换器数 | 2 |

| 输出数和类型 | 2 电压,单极 |

| 采样率(每秒) | - |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

LTC1661 Micropower Dual 10-Bit DAC in MSOP Features Description n Tiny: Two 10-Bit DACs in an 8-Lead MSOP— The LTC®1661 integrates two accurate, serially address- Half the Board Space of an SO-8 able, 10-bit digital-to-analog converters (DACs) in a single n Micropower: 60µA per DAC tiny MS8 package. Each buffered DAC draws just 60µA Sleep Mode: 1µA for Extended Battery Life total supply current, yet is capable of supplying DC output n Rail-to-Rail Voltage Outputs Drive 1000pF currents in excess of 5mA and reliably driving capacitive n Wide 2.7V to 5.5V Supply Range loads up to 1000pF. Sleep mode further reduces total n Double Buffered for Independent or Simultaneous supply current to a negligible 1µA. DAC Updates Linear Technology’s proprietary, inherently monotonic n Reference Range Includes Supply for Ratiometric voltage interpolation architecture provides excellent lin- 0V-to-V Output CC earity while allowing for an exceptionally small external n Reference Input Has Constant Impedance over All form factor. The double-buffered input logic provides Codes (260kΩ Typ)—Eliminates External Buffers simultaneous update capability and can be used to write n 3-Wire Serial Interface with Schmitt Trigger Inputs to either DAC without interrupting sleep mode. n Differential Nonlinearity: ≤±0.75LSB Max Ultralow supply current, power-saving sleep mode and applications extremely compact size make the LTC1661 ideal for battery-powered applications, while its straightforward n Mobile Communications usability, high performance and wide supply range make n Digitally Controlled Amplifiers and Attenuators it an excellent choice as a general purpose converter. n Portable Battery-Powered Instruments n Automatic Calibration for Manufacturing For additional outputs and even greater board density, n Remote Industrial Devices please refer to the LTC1660 micropower octal DAC for L, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear 10-bit applications. For 8-bit applications, please consult Technology Corporation. All other trademarks are the property of their respective owners. the LTC1665 micropower octal DAC. Block Diagram VOUT A GND VCC VOUT B 8 7 6 5 Differential Nonlinearity (DNL) 0.75 10-BIT CH CH CH CH 10-BIT 0.60 DAC A AT AT AT AT DAC B L L L L 0.40 0.20 SB 0 L CONTROL ADDRESS –0.20 LOGIC DECODER –0.40 –0.60 SHIFT REGISTER –0.75 0 256 512 768 1023 CODE 1 2 3 4 1661 G02 1661 BD CS/LD SCK DIN REF 1661fb 1 For more information www.linear.com/LTC1661

LTC1661 aBsolute maximum ratings (Note 1) V to GND .............................................. –0.3V to 7.5V Operating Temperature Range CC Logic Inputs to GND ............................... –0.3V to 7.5V LTC1661C ............................................... 0°C to 70°C V , V , REF to GND ...........–0.3V to V + 0.3V LTC1661I ............................................ –40°C to 85°C OUT A OUT B CC Maximum Junction Temperature...........................125°C Lead Temperature (Soldering, 10 sec) ................. 300°C Storage Temperature Range .................. –65°C to 150°C pin conFiguration TOP VIEW TOP VIEW CS/LD 1 8 VOUT A CS/LD 1 8VOUT A SCK 2 7GND SCK 2 7 GND DIN 3 6VCC DIN 3 6 VCC REF 4 5VOUT B REF 4 5 VOUT B MS8 PACKAGE 8-LEAD PLASTIC MSOP N8 PACKAGE TJMAX = 125°C, θJA = 150°C/W 8-LEAD PLASTIC DIP TJMAX = 150°C, θJA = 100°C/W orDer inFormation (http://www.linear.com/product/LTC1661#orderinfo) Lead Free Finish TUBE TAPE AND REEL PART MARKING PACKAGE DESCRIPTION TEMPERATURE RANGE LTC1661CMS8#PBF LTC1661CMS8#TRPBF LTDV 8-Lead Plastic MSOP 0°C to 70°C LTC1661IMS8#PBF LTC1661IMS8#TRPBF LTDW 8-Lead Plastic MSOP –40°C to 85°C LTC1661CN8#PBF LTC1661CN8#TRPBF LTC1661CN8 8-Lead Plastic DIP 0°C to 70°C LTC1661IN8#PBF LTC1661IN8#TRPBF LTC1661IN8 8-Lead Plastic DIP –40°C to 85°C Consult LTC Marketing for parts specified with wider operating temperature ranges. For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix. electrical characteristics The l denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T = 25°C. V = 2.7V to 5.5V, V ≤ V , V unloaded unless otherwise noted. A CC REF CC OUT SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS Accuracy Resolution l 10 Bits Monotonicity 1V ≤ V ≤ V – 0.1V (Note 2) l 10 Bits REF CC DNL Differential Nonlinearity 1V ≤ V ≤ V – 0.1V (Note 2) l ±0.1 ±0.75 LSB REF CC INL Integral Nonlinearity 1V ≤ V ≤ V – 0.1V (Note 2) l ±0.4 ±2 LSB REF CC V Offset Error Measured at Code 20 l ±5 ±30 mV OS V Temperature Coefficient ±15 µV/°C OS FSE Full-Scale Error V = 5V, V = 4.096V l ±1 ±12 LSB CC REF Full-Scale Error Temperature Coefficient ±30 µV/°C 1661fb 2 For more information www.linear.com/LTC1661

LTC1661 electrical characteristics The l denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T = 25°C. V = 2.7V to 5.5V, V ≤ V , V unloaded unless otherwise noted. A CC REF CC OUT SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS PSR Power Supply Rejection V = 2.5V 0.18 LSB/V REF Reference Input Input Voltage Range l 0 V V CC Resistance Active Mode l 140 260 kΩ Capacitance l 15 pF I Reference Current Sleep Mode l 0.001 1 µA REF Power Supply V Positive Supply Voltage For Specified Performance l 2.7 5.5 V CC I Supply Current V = 5V (Note 3) l 120 195 µA CC CC V = 3V (Note 3) l 95 154 µA CC Sleep Mode (Note 3) l 1 3 µA DC Performance Short-Circuit Current Low V = 0V, V = V = 5V, Code = 1023 l 10 25 100 mA OUT CC REF Short-Circuit Current High V = V = V = 5V, Code = 0 l 7 19 120 mA OUT CC REF AC Performance Voltage Output Slew Rate Rising (Notes 4, 5) 0.60 V/µs Falling (Notes 4, 5) 0.25 V/µs Voltage Output Settling Time To ±0.5LSB (Notes 4, 5) 30 µs Capacitive Load Driving 1000 pF Digital I/O V Digital Input High Voltage V = 2.7V to 5.5V l 2.4 V IH CC V = 2.7V to 3.6V l 2.0 V CC V Digital Input Low Voltage V = 4.5V to 5.5V l 0.8 V IL CC V = 2.7V to 5.5V l 0.6 V CC I Digital Input Leakage V = GND to V l ±10 µA LK IN CC C Digital Input Capacitance (Note 6) l 10 pF IN timing characteristics The l denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T = 25°C. A SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS V = 4.5V to 5.5V CC t D Valid to SCK Setup l 40 ns 1 IN t D Valid to SCK Hold l 0 ns 2 IN t SCK High Time (Note 6) l 30 ns 3 t SCK Low Time (Note 6) l 30 ns 4 t CS/LD Pulse Width (Note 6) l 80 ns 5 t LSB SCK High to CS/LD High (Note 6) l 30 ns 6 t CS/LD Low to SCK High (Note 6) l 20 ns 7 t SCK Low to CS/LD Low (Note 6) l 0 ns 9 t CS/LD High to SCK Positive Edge (Note 6) l 20 ns 11 SCK Frequency Square Wave (Note 6) l 16.7 MHz 1661fb 3 For more information www.linear.com/LTC1661

LTC1661 timing characteristics The l denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T = 25°C. A SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS V = 2.7V to 5.5V CC t D Valid to SCK Setup (Note 6) l 60 ns 1 IN t D Valid to SCK Hold (Note 6) l 0 ns 2 IN t SCK High Time (Note 6) l 50 ns 3 t SCK Low Time (Note 6) l 50 ns 4 t CS/LD Pulse Width (Note 6) l 100 ns 5 t LSB SCK High to CS/LD High (Note 6) l 50 ns 6 t CS/LD Low to SCK High (Note 6) l 30 ns 7 t SCK Low to CS/LD Low (Note 6) l 0 ns 9 t CS/LD High to SCK Positive Edge (Note 6) l 30 ns 11 SCK Frequency Square Wave (Note 6) l 10 MHz Note 1: Stresses beyond those listed under Absolute Maximum Ratings Note 3: Digital inputs at 0V or V . CC may cause permanent damage to the device. Exposure to any Absolute Note 4: Load is 10kΩ in parallel with 100pF. Maximum Rating condition for extended periods may affect device Note 5: V = V = 5V. DAC switched between 0.1V and 0.9V , CC REF FS FS reliability and lifetime. i.e., codes k = 102 and k = 922. Note 2: Nonlinearity and monotonicity are defined from code 20 to code Note 6: Guaranteed by design and not subject to test. 1023 (full scale). See Applications Information. timing Diagram t1 t2 t3 t4 t6 SCK t9 t11 DIN A3 A2 A1 X1 X0 t5 t7 CS/LD 1661 TD 1661fb 4 For more information www.linear.com/LTC1661

LTC1661 typical perFormance characteristics Minimum Supply Headroom vs Integral Nonlinearity (INL) Differential Nonlinearity (DNL) Load Current (Output Sourcing) 2.0 0.75 1400 0.60 VREF = 4.096V 1.5 1200 ∆VOUT < 1LSB CODE = 1023 0.40 1.0 1000 125°C 0.5 0.20 mV) SB 0 SB 0 (OUT 800 25°C L L V – 600 –0.5 –0.20 CC –55°C V 400 –1.0 –0.40 200 –1.5 –0.60 –2.0 –0.75 0 0 256 512 768 1023 0 256 512 768 1023 0 2 4 6 8 10 | | CODE CODE IOUT (mA) (Sourcing) 1661 G01 1661 G02 1661 G03 Minimum V vs Load Current Mid-Scale Output Voltage Mid-Scale Output Voltage OUT (Output Sinking) vs Load Current vs Load Current 1400 3.0 2.0 VCC = 5V VREF = VCC VREF = VCC 1200 CODE = 0 125°C 2.9 CODE = 512 1.9 CODE = 512 1000 2.8 VCC = 5.5V 1.8 VCC = 3.6V 2.7 1.7 V (mV)OUT 860000 25°C V (V)OUT 222...654 VCC = 5V V (V)OUT 111...654 VCC = 3V –55°C 400 2.3 VCC = 4.5V 1.3 VCC = 2.7V 2.2 1.2 200 2.1 1.1 SOURCE SINK SOURCE SINK 2.0 1.0 0 0 2 4 6 8 10 –30 –20 –10 0 10 20 30 –15–12 –8 –4 0 4 8 12 15 | | IOUT (mA) (SINKING) IOUT (mA) IOUT (mA) 1661 G04 1661 G05 1661 G06 Load Regulation Load Regulation vs Output Current vs Output Current Large-Signal Step Response 5 2.0 VCC = VREF = 5V 2.0 VCC = VREF = 3V VCC = V1R0E%F = T 5OV 1.5 CODE = 512 1.5 CODE = 512 4 CODE = 922 90% STEP 1.0 1.0 B) 0.5 B) 0.5 3 ∆V (LSOUT –0.05 ∆V (LSOUT –0.05 V (V)OUT 2 –1.0 –1.0 1 –1.5 –1.5 –2.0 SOURCE SINK –2.0 SOURCE SINK CODE = 102 0 –2 –1 0 1 2 –500 0 500 0 20 40 60 80 100 IOUT (mA) IOUT (µA) TIME (µs) 1661 G07 1661 G08 1661 G09 1661fb 5 For more information www.linear.com/LTC1661

LTC1661 typical perFormance characteristics Supply Current vs Logic Input Voltage Supply Current vs Temperature 1.0 150 ALL DIGITAL INPUTS 140 VREF = VCC SHORTED TOGETHER CODE = 1023 0.8 130 mA) µA) 120 ENT ( 0.6 ENT ( 110 VCC = 5.5V R R UR UR 100 VCC = 4.5V C C PLY 0.4 PLY 90 VCC = 3.6V UP UP 80 S S 0.2 70 VCC = 2.7V 60 0 50 0 1 2 3 4 5 –55 –35 –15 5 25 45 65 85 105 125 LOGIC INPUT VOLTAGE (V) TEMPERATURE (°C) 1661 G10 1661 G11 pin Functions CS/LD (Pin 1): Serial Interface Chip Select/Load Input. REF (Pin 4): Reference Voltage Input. 0V ≤ V ≤ V . REF CC When CS/LD is low, SCK is enabled for shifting data on V , V (Pin 8, Pin 5): DAC Analog Voltage Outputs. OUT A OUT B D into the register. When CS/LD is pulled high, SCK is IN The output range is disabled and the operation(s) specified in the control code, A3-A0, is (are) performed. CMOS and TTL compatible. ⎛1023⎞ 0≤V V ≤V OUTA, OUTB REF⎜ ⎟ ⎝1024⎠ SCK (Pin 2): Serial Interface Clock Input. CMOS and TTL compatible. V (Pin 6): Supply Voltage Input. 2.7V ≤ V ≤ 5.5V. CC CC D (Pin 3): Serial Interface Data Input. Input word data on IN GND (Pin 7): System Ground. the D pin is shifted into the 16-bit register on the rising IN edge of SCK. CMOS and TTL compatible. 1661fb 6 For more information www.linear.com/LTC1661

LTC1661 DeFinitions Differential Nonlinearity (DNL): The difference between Least Significant Bit (LSB): The ideal voltage difference the measured change and the ideal 1LSB change for any between two successive codes. two adjacent codes. The DNL error between any two codes V is calculated as follows: LSB= REF 1024 ΔV –LSB DNL= OUT Resolution (n): Defines the number of DAC output states LSB (2n) that divide the full-scale range. Resolution does not where ∆V is the measured voltage difference between imply linearity. OUT two adjacent codes. Voltage Offset Error (V ): Nominally, the voltage at the OS Full-Scale Error (FSE): The deviation of the actual full-scale output when the DAC is loaded with all zeros. A single voltage from ideal. FSE includes the effects of offset and supply DAC can have a true negative offset, but the out- gain errors (see Applications Information). put cannot go below zero (see Applications Information). Integral Nonlinearity (INL): The deviation from a straight For this reason, single supply DAC offset is measured at line passing through the endpoints of the DAC transfer the lowest code that guarantees the output will be greater curve (endpoint INL). Because the output cannot go than zero. below zero, the linearity is measured between full scale and the lowest code which guarantees the output will be greater than zero. The INL error at a given input code is calculated as follows: ⎛Code⎞ V –V –(V –V ) OUT OS FS OS ⎝⎜1023⎠⎟ INL= LSB where V is the output voltage of the DAC measured at OUT the given input code. 1661fb 7 For more information www.linear.com/LTC1661

LTC1661 operation Transfer Function By selecting the appropriate 4-bit control code (see Table 2) it is possible to perform single operations, such as loading The transfer function for the LTC1661 is: one DAC or changing power-down status (sleep/wake). ⎛ k ⎞ In addition, some Control codes perform two or more V = V OUT(DEAL) ⎝⎜1024⎠⎟ REF operations at the same time. For example, one such code loads DAC A, updates both outputs and wakes the part where k is the decimal equivalent of the binary DAC input up. The DACs can be loaded separately or together, but code D9-D0 and V is the voltage at REF (Pin 6). the outputs are always updated together. REF Power-On Reset Register Loading Sequence The LTC1661 positively clears the outputs to zero scale See Figure 1. With CS/LD held low, data on the D input IN when power is first applied, making system initialization is shifted into the 16-bit shift register on the positive edge consistent and repeatable. of SCK. The 4-bit control code, A3-A0, is loaded first, then the 10-bit Input code, D9-D0, ordered MSB-to-LSB in each Power Supply Sequencing case. Two don’t-care bits, X1 and X0, are loaded last. When the full 16-bit Input word has been shifted in, CS/LD is The voltage at REF (Pin 4) must not ever exceed the pulled high, causing the system to respond according to voltage at V (Pin 6) by more than 0.3V. Particular care CC Table 2. The clock is disabled internally when CS/LD is should be taken in the power supply turn-on and turn- high. Note: SCK must be low when CS/LD is pulled low. off sequences to assure that this limit is observed. See Absolute Maximum Ratings. Sleep Mode Serial Interface DAC control code 1110 is reserved for the special sleep b instruction (see Table 2). In this mode, the digital parts See Table 1. The 16-bit Input word consists of the 4-bit of the circuit stay active while the analog sections are Control code, the 10-bit Input code and two don’t-care bits. disabled; static power consumption is greatly reduced. Table 1. LTC1661 Input Word The reference input and analog outputs are set in a high INPUT WORD impedance state and all DAC settings are retained in memory so that when Sleep mode is exited, the outputs A3 A2 A1 A0 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 X1 X0 of DACs not updated by the wake command are restored CONTROL CODE INPUT CODE DON’T to their last active state. CARE Sleep mode is initiated by performing a load sequence After the Input word is loaded into the register (see using control code 1110 (the DAC input code D9-D0 is Figure 1), it is internally converted from serial to parallel b ignored). format. The parallel 10-bit-wide input code data path is then buffered by two latch registers. To save instruction cycles, the DACs may be prepared with new input codes during Sleep (control codes 0001 The first of these, the input register, is used for loading b and 0010 ); then, a single command (1000 ) can be used new input codes. The second buffer, the DAC register, is b b both to wake the part and to update the output values. used for updating the DAC outputs. Each DAC has its own 10-bit input register and 10-bit DAC register. 1661fb 8 For more information www.linear.com/LTC1661

LTC1661 operation Table 2. DAC Control Functions CONTROL INPUT REGISTER DAC REGISTER POWER-DOWN STATUS A3 A2 A1 A0 STATUS STATUS (SLEEP/WAKE) COMMENTS 0 0 0 0 No Change No Update No Change No Operation. Power-Down Status Unchanged (Part Stays in Wake or Sleep Mode) 0 0 0 1 Load DAC A No Update No Change Load Input Register A with Data. DAC Outputs Unchanged. Power-Down Status Unchanged 0 0 1 0 Load DAC B No Update No Change Load Input Register B with Data. DAC Outputs Unchanged. Power-Down Status Unchanged 0 0 1 1 Reserved 0 1 0 0 Reserved 0 1 0 1 Reserved 0 1 1 0 Reserved 0 1 1 1 Reserved 1 0 0 0 No Change Update Outputs Wake Load Both DAC Regs with Existing Contents of Input Regs. Outputs Update. Part Wakes Up 1 0 0 1 Load DAC A Update Outputs Wake Load Input Reg A. Load DAC Regs with New Contents of Input Reg A and Existing Contents of Reg B. Outputs Update. Part Wakes Up 1 0 1 0 Load DAC B Update Outputs Wake Load Input Reg B. Load DAC Regs with Existing Contents of Input Reg A and New Contents of Reg B. Outputs Update. Part Wakes Up 1 0 1 1 Reserved 1 1 0 0 Reserved 1 1 0 1 No Change No Update Wake Part Wakes Up. Input and DAC Regs Unchanged. DAC Outputs Reflect Existing Contents of DAC Regs 1 1 1 0 No Change No Update Sleep Part Goes to Sleep. Input and DAC Regs Unchanged. DAC Outputs Set to High Impedance State 1 1 1 1 Load DACs A, B with Update Outputs Wake Load Both Input Regs. Load Both DAC Regs with New Same 10-Bit Code Contents of Input Regs. Outputs Update. Part Wakes Up SCK 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 DIN A3 A2 A1 A0 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 X1 X0 CONTROL CODE INPUT CODE DON’T CARE INPUT WORD W0 CS/LD (SCK ENABLED) (LTC1661 RESPONDS) 1661 F01 Figure 1. Register Loading Sequence 1661fb 9 For more information www.linear.com/LTC1661

LTC1661 operation Voltage Outputs Rail-to-Rail Output Considerations Each of the rail-to-rail output amplifiers contained in the In any rail-to-rail DAC, the output swing is limited to volt- LTC1661 can typically source or sink up to 5mA (V = 5V). ages within the supply range. CC The outputs swing to within a few millivolts of either supply If the DAC offset is negative, the output for the lowest when unloaded and have an equivalent output resistance of codes limits at 0V as shown in Figure 2b. 85Ω (typical) when driving a load to the rails. The output amplifiers are stable driving capacitive loads up to 1000pF. Similarly, limiting can occur near full scale when the REF pin is tied to V . If V = V and the DAC full-scale CC REF CC A small resistor placed in series with the output can be error (FSE) is positive, the output for the highest codes used to achieve stability for any load capacitance. A 1µF limits at V as shown in Figure 2c. No full-scale limiting CC load can be successfully driven by inserting a 20Ω resis- can occur if V is less than V – FSE. REF CC tor in series with the V pin. A 2.2µF load needs only a OUT 10Ω resistor, and a 10µF electrolytic capacitor can be used Offset and linearity are defined and tested over the region without any resistor (the equivalent series resistance of the of the DAC transfer function where no output limiting can capacitor itself provides the required small resistance). In occur. any of these cases, larger values of resistance, capacitance or both may be substituted for the values given. POSITIVE VREF = VCC FSE OUTPUT VOLTAGE INPUT CODE (2c) VREF = VCC OUTPUT VOLTAGE 0 512 1023 INPUT CODE (2a) OUTPUT VOLTAGE 0V NEGATIVE INPUT CODE OFFSET (2b) 1661 F02 Figure 2. Effects of Rail-to-Rail Operation On a DAC Transfer Curve. (2a) Overall Transfer Function (2b) Effect of Negative Offset for Codes Near Zero Scale (2c) Effect of Positive Full-Scale Error for Input Codes Near Full Scale When V = V REF CC 1661fb 10 For more information www.linear.com/LTC1661

LTC1661 typical applications 5V 0.1µF FOR EACH U1 AND U2 VH = 7.5V (FROM MAIN CODE A CODE B ∆VH, ∆VL 4 6 INPUT DAC) 512 1023 –250mV R1 R2 5k 512 512 0 8 50k 10V DAC A 0.1µF 512 0 250mV VA1 = 2.5V 8 CS/LD 1 3 + VH′ = VH + VH U3A 1 3 LTC1661 LT1368 DIN U1 2 – 0.1µF 0.1µF 2 SCK 4 R3 5 50k –5V DAC B VB1 R4 5k VH 5V 0.1µF VL DRPIIVNER VOUT (1 0F N) 4 6 LOGIC DRIVE R5 R6 7.5V 250mV 5 50k 5k DAC B –2.5V 250mV VB2 1 6 – VL′ = VL + ∆VL U3B 7 3 LTC1661 LT1368 U2 5 + 0.1µF 2 R7 V = V = 2.5V A1 A2 8 50k DAC A R1 VA2 = 2.5V R8 VH′ = VH + (VA1 – VB1) R2 5k 7 VL = –2.5V V ′ = V + R1 (V – V ) (FROM MAIN L L A2 B2 R2 INPUT DAC) FOR VALUES SHOWN, ∆V , ∆V ADJUSTMENT RANGE = ±250mV H L ∆V , ∆V STEP SIZE = 500µV H L 1661 F03 Figure 3. Pin Driver V and V Adjustment in ATE Applications H L VIN ≥ 4.3V 0.1µF 0.1µF 6 2 VCC 1 4 8 0V TO 4.096V LTC1258-4.1 4.096V REF VOUTA (4mV/BIT) 4 3 DIN LTC1661 2 SCK 1 5 T CS/LD VOUTB 0V TO 4.096V (4mV/BIT) GND 7 1661 F04 Figure 4. Using the LTC1258 and the LTC1661 In a Single Li-Ion Battery Application 1661fb 11 For more information www.linear.com/LTC1661

LTC1661 package Description Please refer to http://www.linear.com/product/LTC1661#packaging for the most recent package drawings. MS8 Package 8-Lead Plastic MSOP (Reference LTC DWG # 05-08-1660 Rev G) 3.00 ±0.102 0.889 ±0.127 (.118 ±.004) 0.52 (.035 ±.005) (NOTE 3) 8 7 6 5 (.0205) REF 5.10 3.20 – 3.45 3.00 ±0.102 (.201) 4.90 ±0.152 MIN (.126 – .136) (.193 ±.006) (.118 ±.004) (NOTE 4) 0.42 ± 0.038 0.65 (.0165 ±.0015) (.0256) 1 2 3 4 TYP BSC 1.10 0.86 RECOMMENDED SOLDER PAD LAYOUT (.043) (.034) MAX REF DETAIL “A” 0.254 (.010) 0° – 6° TYP SEATING PLANE 0.22 – 0.38 0.1016 ±0.0508 GAUGE PLANE (.009 – .015) (.004 ±.002) TYP 0.65 MSOP (MS8) 0213 REV G 0.53 ±0.152 (.0256) (.021 ±.006) BSC DETAIL “A” NOTE: 0.18 1. DIMENSIONS IN MILLIMETER/(INCH) (.007) 2. DRAWING NOT TO SCALE 3. DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE 4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX N Package 8-Lead PDIP (Narrow .300 Inch) (Reference LTC DWG # 05-08-1510 Rev I) .400* (10.160) .300 – .325 .045 – .065 .130 ±.005 MAX (7.620 – 8.255) (1.143 – 1.651) (3.302 ±0.127) 8 7 6 5 .065 .255 ±.015* (1.651) .008 – .015 TYP (6.477 ±0.381) (0.203 – 0.381) .120 (3.048) .020 .325+.035 MIN (0.508) 1 2 3 4 –.015 .100 .018 ±.003 MIN ( +0.889) 8.255 (2.54) (0.457 ±0.076) N8 REV I 0711 –0.381 BSC NOTE: INCHES 1. DIMENSIONS ARE MILLIMETERS *THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .010 INCH (0.254mm) 1661fb 12 For more information www.linear.com/LTC1661

LTC1661 revision history REV DATE DESCRIPTION PAGE NUMBER A 11/10 Removed typical values from Timing Characteristics section 3, 4 B 4/16 Corrected typo for V under Power Supply 3 CC 1661fb Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representa- 13 tion that the interconneFcotiro nm oof rites cinirfcouritms aast idoens cwribwewd h.leinreeina rw.cilol nmot/ LinTfrCin1g6e 6o1n existing patent rights.

LTC1661 typical application Pin Driver V and V Adjustment in ATE Applications H L 5V 0.1µF FOR EACH U1 AND U2 VH = 7.5V (FROM MAIN CODE A CODE B ∆VH, ∆VL 4 6 INPUT DAC) 512 1023 –250mV R1 R2 5k 512 512 0 8 50k 10V DAC A 0.1µF 512 0 250mV VA1 = 2.5V 8 CS/LD 1 3 + VH′ = VH + VH U3A 1 3 LTC1661 LT1368 DIN U1 2 – 0.1µF 0.1µF 2 SCK 4 R3 5 50k –5V DAC B VB1 R4 5k VH 5V 0.1µF VL DRPIIVNER VOUT (1 0F N) 4 6 LOGIC DRIVE R5 R6 7.5V 250mV 5 50k 5k DAC B –2.5V 250mV VB2 1 6 – VL′ = VL + ∆VL U3B 7 3 LTC1661 LT1368 U2 5 + 0.1µF 2 R7 V = V = 2.5V A1 A2 8 50k DAC A R1 VA2 = 2.5V R8 VH′ = VH + (VA1 – VB1) R2 5k 7 VL = –2.5V V ′ = V + R1 (V – V ) (FROM MAIN L L A2 B2 R2 INPUT DAC) FOR VALUES SHOWN, ∆V , ∆V ADJUSTMENT RANGE = ±250mV H L ∆V , ∆V STEP SIZE = 500µV H L 1661 F03 relateD parts PART NUMBER DESCRIPTION COMMENTS LTC1446/LTC1446L Dual 12-Bit V DACs in SO-8 Package with Internal Reference LTC1446: V = 4.5V to 5.5V, V = 0V to 4.095V OUT CC OUT LTC1446L: V = 2.7V to 5.5V, V = 0V to 2.5V CC OUT LTC1448 Dual 12-Bit V DAC in SO-8 Package V = 2.7V to 5.5V, External Reference Can Be Tied to V OUT CC CC LTC1454/LTC1454L Dual 12-Bit V DACs in SO-16 Package with Added LTC1454: V = 4.5V to 5.5V, V = 0V to 4.095V OUT CC OUT Functionality LTC1454L: V = 2.7V to 5.5V, V = 0V to 2.5V CC OUT LTC1458/LTC1458L Quad 12-Bit Rail-to-Rail Output DACs with Added Functionality LTC1458: V = 4.5V to 5.5V, V = 0V to 4.095V CC OUT LTC1458L: V = 2.7V to 5.5V, V = 0V to 2.5V CC OUT LTC1659 Single Rail-to-Rail 12-Bit V DAC in 8-Lead MSOP Package Low Power Multiplying V DAC. Output Swings from GND to OUT OUT V : 2.7V to 5.5V REF. REF Input Can Be Tied to V CC CC LTC1663 Single 10-Bit V DAC in SOT-23 Package V = 2.7V to 5.5V, Internal Reference, 60µA OUT CC LTC1665/LTC1660 Octal 8/10-Bit V DAC in 16-Pin Narrow SSOP V = 2.7V to 5.5V, Micropower, Rail-to-Rail Output OUT CC 1661fb Linear Technology Corporation LT 0416 REV B • PRINTED IN USA 14 1630 McCarthy Blvd., Milpitas, CA 95035-7417 For more information www.linear.com/LTC1661 (408) 432-1900 ● FAX: (408) 434-0507 ● www.linear.com/LTC1661 LINEAR TECHNOLOGY CORPORATION 1999

Datasheet下载

Datasheet下载