ICGOO在线商城 > 集成电路(IC) > 时钟/计时 - 时钟发生器,PLL,频率合成器 > LMX2541SQ3320E/NOPB

- 型号: LMX2541SQ3320E/NOPB

- 制造商: Texas Instruments

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

LMX2541SQ3320E/NOPB产品简介:

ICGOO电子元器件商城为您提供LMX2541SQ3320E/NOPB由Texas Instruments设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 LMX2541SQ3320E/NOPB价格参考。Texas InstrumentsLMX2541SQ3320E/NOPB封装/规格:时钟/计时 - 时钟发生器,PLL,频率合成器, 。您可以下载LMX2541SQ3320E/NOPB参考资料、Datasheet数据手册功能说明书,资料中有LMX2541SQ3320E/NOPB 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC)半导体 |

| 描述 | IC PLL FREQ SYNTH W/VCO 36LLP锁相环 - PLL Ultra-Lo Noise PLLatinum Freq Synth |

| 产品分类 | |

| 品牌 | Texas Instruments |

| 产品手册 | http://www.ti.com/lit/gpn/lmx2541 |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | RF集成电路,锁相环 - PLL,Texas Instruments LMX2541SQ3320E/NOPB- |

| 数据手册 | |

| 产品型号 | LMX2541SQ3320E/NOPB |

| PLL | 是 |

| 产品种类 | 锁相环 - PLL |

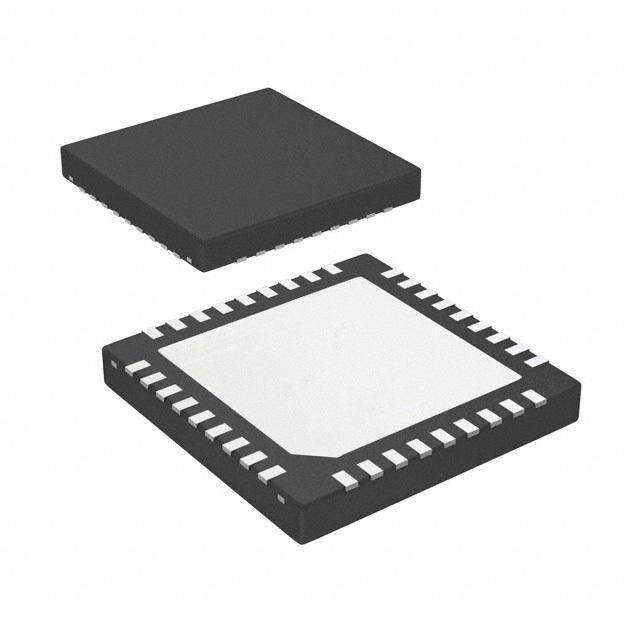

| 供应商器件封装 | 36-WQFN (6x6) |

| 其它名称 | *LMX2541SQ3320E/NOPB |

| 分频器/倍频器 | 是/是 |

| 包装 | 剪切带 (CT) |

| 商标 | Texas Instruments |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装 | Reel |

| 封装/外壳 | 36-WFQFN 裸露焊盘 |

| 封装/箱体 | LLP EP |

| 工作温度 | -40°C ~ 85°C |

| 工作电源电压 | 3.3 V |

| 工厂包装数量 | 1000 |

| 差分-输入:输出 | 无/无 |

| 最大工作温度 | + 85 C |

| 最大输入频率 | 6000 MHz |

| 最小工作温度 | - 40 C |

| 最小输入频率 | 5 MHz |

| 标准包装 | 1 |

| 比率-输入:输出 | 2:2 |

| 电压-电源 | 3.15 V ~ 3.45 V |

| 电源电压-最大 | 3.45 V |

| 电源电压-最小 | 3.15 V |

| 电路数 | 1 |

| 电路数量 | 1 |

| 类型 | 时钟/频率合成器,RF |

| 系列 | LMX2541 |

| 输入 | 时钟 |

| 输出 | 时钟 |

| 频率-最大值 | 3.6GHz |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

Product Sample & Technical Tools & Support & Folder Buy Documents Software Community LMX2541 SNOSB31J–JULY2009–REVISEDDECEMBER2014 LMX2541 Ultra-Low Noise PLLatinum Frequency Synthesizer With Integrated VCO 1 Features 3 Description • MultipleFrequencyOptionsAvailable The LMX2541 device is an ultra low-noise frequency 1 synthesizer which integrates a high-performance (SeeDeviceComparisonTable) delta-sigma fractional N PLL, a VCO with fully • FrequenciesFrom31.6MHzto4000MHz integrated tank circuit, and an optional frequency • VeryLowRMSNoiseandSpurs divider. The PLL offers an unprecedented normalized • –225dBc/HzNormalizedPLLPhaseNoise noise floor of –225 dBc/Hz and can be operated with up to 104 MHz of phase-detector rate (comparison • IntegratedRMSNoise(100Hzto20MHz) frequency) in both integer and fractional modes. The – 2mRad(100Hzto20MHz)at2.1GHz PLL can also be configured to work with an external – 3.5mRad(100Hzto20MHz)at3.5GHz VCO. • UltraLow-NoiseIntegratedVCO The LMX2541 integrates several low-noise, high- • ExternalVCOOption(InternalVCOBypassed) precisionLDOsandoutputdrivermatchingnetworkto provide higher supply noise immunity and more • VCOFrequencyDivider1to63(AllValues) consistent performance, while reducing the number of • ProgrammableOutputPower external components. When combined with a high- • Upto104-MHzPhaseDetectorFrequency quality reference oscillator, the LMX2541 generates a verystable,ultralow-noisesignal. • IntegratedLow-NoiseLDOs • ProgrammableChargePumpOutput The LMX2541 is offered in a family of 6 devices with varying VCO frequency range from 1990 MHz up to 4 • PartiallyIntegratedLoopFilter GHz. Using a flexible divider, the LMX2541 can • DigitalFrequencyShiftKeying(FSK)Modulation generatefrequenciesaslowas31.6MHz. Pin The LMX2541 is a monolithic integrated circuit, • IntegratedReferenceCrystalOscillatorCircuit fabricated in a proprietary BiCMOS process. Device • HardwareandSoftwarePowerDown programming is facilitated using a three-wire • FastLockModeandVCO-BasedCycleSlip MICROWIRE interface that can operate down to 1.6 Reduction volts. Supply voltage ranges from 3.15 V to 3.45 V. The LMX2541 is available in a 36-pin 6-mm × 6-mm • AnalogandDigitalLockDetect ×0.8-mmWQFNpackage. • 1.6-VLogicCompatibility DeviceInformation(1) 2 Applications VCOFREQUENCY PARTNUMBER PACKAGE (MHz) • WirelessInfrastructure(UMTS,LTE,WiMax) LMX2541SQ2060E WQFN(36) 1990-2240 • BroadbandWireless LMX2541SQ2380E WQFN(36) 2200-2530 • WirelessMeterReading LMX2541SQ2690E WQFN(36) 2490-2865 • TestandMeasurement LMX2541SQ3030E WQFN(36) 2810-3230 • FMMobileRadio LMX2541SQ3320E WQFN(36) 3130-3600 space LMX2541SQ3740E WQFN(36) 3480-4000 (1) For all available packages, see the orderable addendum at theendofthedatasheet. SystemBlockDiagram Clean Ultra-Clean Dirty Input Reference Local Oscillator Clock Clock PLL Dist. PLL LMK04000 LMX2541 (Clock Jitter Cleaner) (RF Synthesizer) 1 An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectualpropertymattersandotherimportantdisclaimers.PRODUCTIONDATA.

LMX2541 SNOSB31J–JULY2009–REVISEDDECEMBER2014 www.ti.com Table of Contents 1 Features.................................................................. 1 9.2 FunctionalBlockDiagrams.....................................25 2 Applications........................................................... 1 9.3 FeatureDescription.................................................26 3 Description............................................................. 1 9.4 DeviceFunctionalModes........................................36 9.5 Programming...........................................................37 4 RevisionHistory..................................................... 2 9.6 RegisterMaps.........................................................38 5 DeviceComparisonTable..................................... 3 10 ApplicationandImplementation........................ 51 6 PinConfigurationandFunctions......................... 4 10.1 ApplicationInformation..........................................51 7 Specifications......................................................... 6 10.2 TypicalApplication ...............................................59 7.1 AbsoluteMaximumRatings......................................6 11 PowerSupplyRecommendations..................... 61 7.2 ESDRatings..............................................................6 12 Layout................................................................... 62 7.3 RecommendedOperatingConditions.......................6 12.1 LayoutGuidelines.................................................62 7.4 ThermalInformation..................................................6 12.2 LayoutExample....................................................63 7.5 ElectricalCharacteristics...........................................7 13 DeviceandDocumentationSupport................. 64 7.6 TimingRequirements..............................................11 7.7 TypicalCharacteristics............................................12 13.1 DeviceSupport......................................................64 13.2 Trademarks...........................................................64 8 ParameterMeasurementInformation................23 13.3 ElectrostaticDischargeCaution............................64 8.1 BenchTestSetups..................................................23 13.4 Glossary................................................................64 9 DetailedDescription............................................ 25 14 Mechanical,Packaging,andOrderable 9.1 Overview.................................................................25 Information........................................................... 64 4 Revision History ChangesfromRevisionI(February2013)toRevisionJ Page • AddedESDRatingstable,FeatureDescriptionsection,DeviceFunctionalModes,ApplicationandImplementation section,PowerSupplyRecommendationssection,Layoutsection,DeviceandDocumentationSupportsection,and Mechanical,Packaging,andOrderableInformationsection.................................................................................................. 1 ChangesfromRevisionH(February2013)toRevisionI Page • ChangedlayoutofNationalDataSheettoTIformat........................................................................................................... 36 2 SubmitDocumentationFeedback Copyright©2009–2014,TexasInstrumentsIncorporated ProductFolderLinks:LMX2541

LMX2541 www.ti.com SNOSB31J–JULY2009–REVISEDDECEMBER2014 5 Device Comparison Table VCO LMX2541SQ2060E LMX2541SQ2380E LMX2541SQ2690E LMX2541SQ3030E LMX2541SQ3320E LMX2541SQ3740E _DIV Fmin Fmax Fmin Fmax Fmin Fmax Fmin Fmax Fmin Fmax Fmin Fmax 1 1990.0 2240.0 2200.0 2530.0 2490.0 2865.0 2810.0 3230.0 3130.0 3600.0 3480.0 4000.0 2 995.0 1120.0 1100.0 1265.0 1245.0 1432.5 1405.0 1615.0 1565.0 1800.0 1740.0 2000.0 3 663.3 746.7 733.3 843.3 830.0 955.0 936.7 1076.7 1043.3 1200.0 1160.0 1333.3 4 497.5 560.0 550.0 632.5 622.5 716.3 702.5 807.5 782.5 900.0 870.0 1000.0 5 398.0 448.0 440.0 506.0 498.0 573.0 562.0 646.0 626.0 720.0 696.0 800.0 6 331.7 373.3 366.7 421.7 415.0 477.5 468.3 538.3 521.7 600.0 580.0 666.7 7 284.3 320.0 314.3 361.4 355.7 409.3 401.4 461.4 447.1 514.3 497.1 571.4 8 248.8 280.0 275.0 316.3 311.3 358.1 351.3 403.8 391.3 450.0 435.0 500.0 ... ... ... ... ... ... ... ... ... ... ... ... ... 63 31.6 35.6 34.9 40.2 39.5 45.5 44.6 51.3 49.7 57.1 55.2 63.5 All devices have continuous frequency coverage below a divide value of 8 (7 for most devices) down to their minimum frequency achievable with divide by 63. The numbers in bold show the upper end of this minimum continuous frequency range. For instance, the LMX2541SQ3740E option offers continuous frequency coverage from 55.2 MHz to 571.4 MHz and LMX2541SQ2060E offers continuous frequency coverage from 31.6 MHz to 280 MHz. If using the part in External VCO mode, all parts have roughly the same performance and any option willdo. Copyright©2009–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 3 ProductFolderLinks:LMX2541

LMX2541 SNOSB31J–JULY2009–REVISEDDECEMBER2014 www.ti.com 6 Pin Configuration and Functions NJKPackage 36-PinWQFN TopView RFout NC LE CLK DATA VccDiv Bypass VccBias VccDig 36 35 34 33 32 31 30 29 28 GND 1 27 GND VregRFout 2 26 VregFRAC VccRFout 3 25 VccFRAC L1 4 24 RFoutEN 0 Lmid 5 GND 23 VccOSCin L2 6 22 OSCin* VccVCO 7 21 OSCin VregVCO 8 20 Ftest/LD VrefVCO 9 19 VccPLL2 10 11 12 13 14 15 16 17 18 GND CE ExtVCOin VccPLL1 VccCP1 Vtune CPout FLout VccCP2 PinFunctions PIN TYPE DESCRIPTION NAME NO. Bypass 30 Bypass PutacaptotheVccBiaspin. ChipEnable. CE 11 CMOS Thedeviceneedstobeprogrammedforthispintoproperlypowerdownthedevice. MICROWIREclockinput.HighimpedanceCMOSinput. CLK 33 High-ZInput ThispinisusedforthedigitalFSKmodulationfeature. CPout 16 Output Chargepumpoutput. DATA 32 High-ZInput MICROWIREserialdatainput.HighimpedanceCMOSinput. OptionalinputforusewithanexternalVCO. ExtVCOin 12 RFInput ThispinshouldbeACcoupledifusedorleftopenifnotused. FLout 17 Output Fastlockoutput. SoftwarecontrollablemultiplexedCMOSoutput. Ftest/LD 20 Output CanbeusedtomonitorPLLlockcondition. GND 0 GND TheDAPpadmustbegrounded. GND 1 GND GND 10 GND GND 27 GND L1 4 NC Donotconnectthispin. L2 6 NC Donotconnectthispin. LE 34 High-ZInput MICROWIRELatchEnableinput.HighimpedanceCMOSinput. Lmid 5 NC Donotconnectthispin. NC 35 NC Noconnect. Oscillatorinputsignal.Ifnotbeingusedwithanexternalcrystal,thisinputshouldbeAC OSCin 21 High-ZInput coupled. 4 SubmitDocumentationFeedback Copyright©2009–2014,TexasInstrumentsIncorporated ProductFolderLinks:LMX2541

LMX2541 www.ti.com SNOSB31J–JULY2009–REVISEDDECEMBER2014 PinFunctions(continued) PIN TYPE DESCRIPTION NAME NO. Complementaryoscillatorinputsignal.Canalsobeusedwithanexternalcrystal.Ifnot OSCin* 22 High-ZInput beingusedwithanexternalcrystal,thisinputshouldbeACcoupled. RFout 36 RFOutput RFoutput.MustbeACcoupledifused. RFoutEN 24 Input Softwareprogrammableoutputenablepin. VccBias 29 Supply SupplyforBiascircuitrythatisforthewholechip. VccCP1 14 Supply PowersupplyforPLLchargepump. VccCP2 18 Supply PowersupplyforPLLchargepump. VccDig 28 Supply Supplyfordigitalcircuitry,suchtheMICROWIRE. VccDiv 31 Supply Supplyfortheoutputdivider Supply VccFRAC 25 PowerSupplyforthePLLfractionalcircuitry. (LDOInput) VccOSCin 23 Supply SupplyfortheOSCinbuffer. VccPLL1 13 Supply PowersupplyforPLL. VccPLL2 19 Supply PowersupplyforPLL. Supply VccRFout 3 SupplyfortheRFoutputbuffer. (LDOInput) Supply VccVCO 7 SupplyfortheVCO. (LDOInput) VregFRAC 26 LDOOutput Regulatedpowersupplyusedforthefractionaldelta-sigmacircuitry. VregRFout 2 LDOOutput LDOOutputforRFoutputbuffer. VrefVCO 9 LDOBypass LDOBypass VregVCO 8 LDOOutput LDOOutputforVCO Vtune 15 High-ZInput TuningvoltageinputtotheVCO. Copyright©2009–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 5 ProductFolderLinks:LMX2541

LMX2541 SNOSB31J–JULY2009–REVISEDDECEMBER2014 www.ti.com 7 Specifications 7.1 Absolute Maximum Ratings overoperatingfree-airtemperaturerange(unlessotherwisenoted) (1)(2) MIN MAX UNIT Vcc PowerSupplyVoltage –0.3 3.6 V V InputVoltagetopinsotherthanVccPins –0.3 (Vcc+0.3) V IN (3) T LeadTemperature(solder4sec.) 260 °C L T StorageTemperature –65 150 °C stg (1) StressesbeyondthoselistedunderAbsoluteMaximumRatingsmaycausepermanentdamagetothedevice.Thesearestressratings only,whichdonotimplyfunctionaloperationofthedeviceattheseoranyotherconditionsbeyondthoseindicatedunderRecommended OperatingConditions.Exposuretoabsolute-maximum-ratedconditionsforextendedperiodsmayaffectdevicereliability. (2) IfMilitary/Aerospacespecifieddevicesarerequired,pleasecontacttheTexasInstrumentsSalesOffice/Distributorsforavailabilityand specifications. (3) Nevertoexceed3.6V. 7.2 ESD Ratings VALUE UNIT Humanbodymodel(HBM),perANSI/ESDA/JEDECJS-001(1) ±2500 Charged-devicemodel(CDM),perJEDECspecificationJESD22- ±1750 V(ESD) Electrostaticdischarge C101(2) V Machinemodel(MM) ±400 (1) JEDECdocumentJEP155statesthat500-VHBMallowssafemanufacturingwithastandardESDcontrolprocess. (2) JEDECdocumentJEP157statesthat250-VCDMallowssafemanufacturingwithastandardESDcontrolprocess. 7.3 Recommended Operating Conditions MIN NOM MAX UNIT Vcc PowerSupplyVoltage(AllVccPins) 3.15 3.3 3.45 V T AmbientTemperature –40 85 °C A 7.4 Thermal Information LMX2541 LMX2541 LMX2541 SQ2060E SQ2060E SQ2060E THERMALMETRIC(1) UNIT 9Thermal 13Thermal 16Thermal Vias(2) Vias(3) Vias(4) R Junction-to-ambientthermalresistance 31.7 30.3 29.8 θJA °C/W ψ Junction-to-topcharacterizationparameter 7.3 7.3 7.3 JT (1) Formoreinformationabouttraditionalandnewthermalmetrics,seetheICPackageThermalMetricsapplicationreport,SPRA953. (2) RecommendedforMostReliableSolderability. (3) CompromiseBetweenSolderability,HeatDissipation,andFractionalSpurs. (4) RecommendedforOptimalHeatDissipationandFractionalSpurs. 6 SubmitDocumentationFeedback Copyright©2009–2014,TexasInstrumentsIncorporated ProductFolderLinks:LMX2541

LMX2541 www.ti.com SNOSB31J–JULY2009–REVISEDDECEMBER2014 7.5 Electrical Characteristics (3.15V≤V ≤3.45V,-40°C≤T ≤85°C;exceptasspecified.TypicalvaluesareatVcc=3.3V,25C.) CC A PARAMETER TESTCONDITIONS MIN TYP MAX UNIT CURRENTCONSUMPTION DefaultPower VCO_DIV>1 170 204 EntireChipSupplyCurrentwith I Mode mA CC allblocksenabled (1) VCO_DIV=1 130 156 I CurrentforExternalVCOMode RFoutEN=LOW 72 94 mA PLL VCO_DIV>1 I CurrentforDividerOnlyMode DefaultPowerMode 84 110 mA DIV (1) I PD PowerDownCurrent CE=0V,DeviceInitialized 100 250 µA CC OSCILLATOR(NORMALMODEOPERATIONWITHXO=0) I OSC OscillatorInputHighCurrentfor IH V =2.75V 300 µA in OSCinandOSCin* IH I OSCi OscillatorInputLowCurrentfor IL V =0 –100 µA n OSCinandOSCin*pins IL OSC_2X=1 5 52 OSCinFrequencyRange fOSCin (2) MODE=0 5 700 MHz OSC_2X=0 MODE=1 5 900 dv SlewRate (2) 150 V/µs OSCin Single-Ended 0.2 2.0 v OscillatorSensitivity dv ≥150V/µs Vpp OSCin OSCin Differential 0.4 3.1 OSCILLATOR(CRYSTALMODEWITHXO=1) f CrystalFrequencyRange V =2.75V 5 20 MHz XTAL IH ESR CrystalEquivalentSeries Thisarequirementforthecrystal,nota XTA 100 Ω Resistance characteristicoftheLMX2541. L Thisrequirementisforthecrystal,nota P PowerDissipationinCrystal 200 µW XTAL characteristicoftheLMX2541. C InputCapacitanceofOSCin 6 pF OSCin PLL f PhaseDetectorFrequency 104 MHz PD CPG=1X 100 CPG=2X 200 ChargePump I CPG=3X 300 µA CPout OutputCurrentMagnitude ... ... CPG=32X 3200 I TR CPout CPTRI-STATECurrent 0.4V<V <Vcc-0.4 1 5 nA I CPout I M ChargePump V =Vcc/2 CPout CPout 3% 10% M Sinkvs.SourceMismatch T =25°C A ChargePump 0.4V<V <Vcc-0.4 I V CPout 4% CPout Currentvs.CPVoltageVariation T =25°C A CPCurrentvs.Temperature I T V =Vcc/2 8% CPout Variation CPout NormalizedPLL1/fNoise CPG=1X –116 dBc/Hz LN(f) LNPLL_flicker(10kHz) CPG=32X –124.5 (3) NormalizedPLLNoiseFloor CPG=1X –220.8 dBc/Hz LNPLL_flat(1Hz) CPG=32X –225.4 (1) TheLMX2541RFoutpowerlevelisprogrammablewiththeprogramwordsofVCOGAIN,OUTTERM,andDIVGAIN.Changingthese wordscanchangetheoutputpoweroftheVCOaswellasthecurrentconsumptionoftheoutputbuffer.Forthepurposeofconsistency inelectricalspecifications,"DefaultPowerMode"isdefinedtobethesettingsofVCOGAIN=OUTTERM=DIVGAIN=12. (2) Nottestedinproduction.Specifiedbycharacterization.OSCinistestedonlyto400MHz. (3) SeeApplicationandImplementationformoredetailsontheseparameters. Copyright©2009–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 7 ProductFolderLinks:LMX2541

LMX2541 SNOSB31J–JULY2009–REVISEDDECEMBER2014 www.ti.com Electrical Characteristics (continued) (3.15V≤V ≤3.45V,-40°C≤T ≤85°C;exceptasspecified.TypicalvaluesareatVcc=3.3V,25C.) CC A PARAMETER TESTCONDITIONS MIN TYP MAX UNIT RFoutBufferEnabledandVCO_DIV>1 400 4000 f PLLInputFrequency MHz ExtVCOin RFoutBufferDisabledandVCO_DIV=1 400 6000 pnExtVCOi P((2L)LaIpnppluietsSteonMsiativxitLyimitOnly) ffEExxttVVCCOOiinn≤>44GGHHzz –1–55 1100 dBm VCOSPECIFICATIONS 2060E 1990 2240 2380E 2200 2530 Mode=FullChipMode 2690E 2490 2865 f InternalVCOFrequencyRange Thisisthefrequencybeforethe MHz VCO VCOdivider. 3030E 2810 3230 3320E 3130 3600 3740E 3480 4000 ΔT MaximumAllowableTemperature (2),(4) 125 °C CL DriftforContinuousLock 2060E 3.5 2380E 2.8 MaximumFrequency 2690E 1.6 p RFOutputPower DefaultPowerMode dBm RFout VCO_DIV=1 3030E 1.2 3320E 0.2 3740E –0.3 FixedTemperaturewith100MHzfrequencychange 0.3 attheoutput ΔP ChangeinOutputPower dB RFout Fixedfrequencywithachangeovertheentire 0.4 temperaturerange Thelowernumberintherange 2060E 13-23 applieswhentheVCOisatits 2380E 16-30 lowestfrequencyandthehigher numberapplieswhentheVCO 2690E 17-32 K FineTuningSensitivity MHz/V Vtune isatitshighestfrequency.A 3030E 20-37 linearapproximationcanbe usedforfrequenciesbetween 3320E 21-37 thesetwocases. 3740E 24-42 DefaultPowerMode VCO_DIV=2 –20 HSRFout S(5e)condHarmonic (1) dBc 50ΩLoad VCO_DIV=3 –20 DefaultPowerMode VCO_DIV=2 3% DERFout D(5u)tyCycleError (1) 50ΩLoad VCO_DIV=3 3% PSH VCOFrequencyPushing C =4.7µF,OpenLoop 600 kHz/V VCO VregVCO VSWR1.7to1 VCO_DIV=1 ±800 PUL VCOFrequencyPulling kHz VCO (6dBPad) VCO_DIV>1 ±60 (4) MaximumAllowableTemperatureDriftforContinuousLockishowfarthetemperaturecandriftineitherdirectionfromthevalueitwas atthetimethattheR0registerwaslastprogrammed,andstillhavethedevicestayinlock.TheactionofprogrammingtheR0register, eventothesamevalue,activatesafrequencycalibrationroutine.Thisimpliesthatthedevicewillworkovertheentirefrequencyrange, butifthetemperaturedriftsmorethanthemaximumallowabledriftforcontinuouslock,thenitwillbenecessarytoreloadtheR0register toensurethatitstaysinlock.Regardlessofwhattemperaturethedevicewasinitiallyprogrammedat,thetemperaturecanneverdrift outsidethefrequencyrangeof-40°C≤T ≤85°Cwithoutviolatingspecifications. A (5) Thedutycycleerror(DE)andsecondharmonic(HS)aretheoreticallyrelatedbytheequationHS=10·log|2π·DE|-6dB.Asquare wavewith3%dutycycletheoreticallyhasasecondharmonicof-20dBc. 8 SubmitDocumentationFeedback Copyright©2009–2014,TexasInstrumentsIncorporated ProductFolderLinks:LMX2541

LMX2541 www.ti.com SNOSB31J–JULY2009–REVISEDDECEMBER2014 Electrical Characteristics (continued) (3.15V≤V ≤3.45V,-40°C≤T ≤85°C;exceptasspecified.TypicalvaluesareatVcc=3.3V,25C.) CC A PARAMETER TESTCONDITIONS MIN TYP MAX UNIT 2060E 1.6 IntegrationBandwidth =100Hzto20MHz 2380E 1.8 MiddleVCOFrequency 2690E 2.1 σ RMSPhaseError 100MHzWenzelCrystal mRad Φ Reference 3030E 2.1 IntegerMode 3320E 2.3 OptimizedLoopBandwidth 3740E 2.6 VCOPHASENOISE(6) 10-kHzOffset –89.7 100-kHzOffset –113.7 f = RFout MinVCO 1-MHzOffset –134.9 Frequency 10-MHzOffset –155.4 PhaseNoise 20-MHzOffset –160.3 L(f) dBc/Hz Fout 2060E 10-kHzOffset –86.5 100-kHzOffset –111.4 f = RFout MaxVCO 1-MHzOffset –132.8 Frequency 10-MHzOffset –153.4 20-MHzOffset –158.5 10-kHzOffset –87.9 100-kHzOffset –112.7 f = RFout MinVCO 1-MHzOffset –133.8 Frequency 10-MHzOffset –154.2 PhaseNoise 20-MHzOffset –159.5 L(f) dBc/Hz Fout 2380E 10-kHzOffset –83.4 100-kHzOffset –109.1 f = RFout MaxVCO 1-MHzOffset –130.8 Frequency 10-MHzOffset –151.8 20-MHzOffset –157.5 10-kHzOffset –86.9 100-kHzOffset –111.8 f = RFout MinVCO 1-MHzOffset –133.3 Frequency 10-MHzOffset –154.2 PhaseNoise 20-MHzOffset –159.4 L(f) dBc/Hz Fout 2690E 10-kHzOffset –82.3 100-kHzOffset –108.4 f = RFout MaxVCO 1-MHzOffset –130.3 Frequency 10-MHzOffset –151.1 20-MHzOffset –156.7 (6) TheVCOphasenoiseismeasuredassumingthattheloopbandwidthissufficientlynarrowthattheVCOnoisedominates.Thephase noiseismeasuredwithAC_TEMP_COMP=5andthedeviceisreloadedateachtestfrequency.Thetypicalperformance characteristicssectionshowshowtheVCOphasenoisevariesovertemperatureandfrequency. Copyright©2009–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 9 ProductFolderLinks:LMX2541

LMX2541 SNOSB31J–JULY2009–REVISEDDECEMBER2014 www.ti.com Electrical Characteristics (continued) (3.15V≤V ≤3.45V,-40°C≤T ≤85°C;exceptasspecified.TypicalvaluesareatVcc=3.3V,25C.) CC A PARAMETER TESTCONDITIONS MIN TYP MAX UNIT 10-kHzOffset –86.1 100-kHzOffset –110.5 f = RFout MinVCO 1-MHzOffset –132.0 Frequency 10-MHzOffset –152.2 PhaseNoise 20-MHzOffset –157.1 L(f) dBc/Hz Fout 3030E 10-kHzOffset –82.2 100-kHzOffset –107.7 f = RFout MaxVCO 1-MHzOffset –129.4 Frequency 10-MHzOffset –150.5 20-MHzOffset –156.1 10-kHzOffset –84.1 100-kHzOffset –109.1 f = RFout MinVCO 1-MHzOffset –130.7 Frequency 10-MHzOffset –151.6 PhaseNoise 20-MHzOffset –156.9 L(f) dBc/Hz Fout 3320E 10-kHzOffset –82.0 100-kHzOffset –107.0 f = RFout MaxVCO 1-MHzOffset –128.5 Frequency 10-MHzOffset –149.6 20-MHzOffset –155.2 10-kHzOffset –83.9 100-kHzOffset –108.3 f = RFout MinVCO 1-MHzOffset –129.9 Frequency 10-MHzoffset –150.6 PhaseNoise 20-MHzOffset –156.5 L(f) dBc/Hz Fout 3740E 10-kHzOffset –81.6 100-kHzOffset –106.5 f = RFout MaxVCO 1-MHzOffset –127.7 Frequency 10-MHzOffset –148.6 20-MHzOffset –154.2 DIGITALINTERFACE(DATA,CLK,LE,CE,Ftest/LD,FLout,RFoutEN) V High-LevelInputVoltage 1.6 Vcc V IH V Low-LevelInputVoltage 0.4 V IL I High-LevelInputCurrent V =1.75,XO=0 –5 5 µA IH IH I Low-LevelInputCurrent V =0V,XO=0 –5 5 µA IL IL V High-LevelOutputVoltage I =500µA 2 V OH OH V Low-LevelOutputVoltage I =-500µA 0 0.4 V OL OL I LeakageCurrent Ftest/LDandFLoutPinsOnly –5 5 µA Leak 10 SubmitDocumentationFeedback Copyright©2009–2014,TexasInstrumentsIncorporated ProductFolderLinks:LMX2541

LMX2541 www.ti.com SNOSB31J–JULY2009–REVISEDDECEMBER2014 7.6 Timing Requirements MIN NOM MAX UNIT t ClocktoEnableLowTime SeeFigure1 25 ns CE t DatatoClockSetUpTime SeeFigure1 25 ns CS t DatatoClockHoldTime SeeFigure1 20 ns CH t ClockPulseWidthHigh SeeFigure1 25 ns CWH t ClockPulseWidthLow SeeFigure1 25 ns CWL t EnabletoClockSetUpTime SeeFigure1 25 ns CES t EnablePulseWidthHigh SeeFigure1 25 ns EWH MSB LSB DATA D19 D18 D17 D16 D15 D0 C3 C2 C1 C0 CLK tCES tCS tCH tCWH tCWL tES LE tEWH Figure1. SerialDataTimingDiagram Copyright©2009–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 11 ProductFolderLinks:LMX2541

LMX2541 SNOSB31J–JULY2009–REVISEDDECEMBER2014 www.ti.com 7.7 Typical Characteristics 7.7.1 NotEnsuredCharacteristics )zH/cBd( RO --220160 )zH/cBd( RO --221168 O O LF E -214 LF E -220 S S IO IO N N D -218 D -222 E E Z Z ILA ILA MR -222 MR -224 O O N LLP -226 1 2 3 4 N LLP -226 10 10 10 10 1X 2X 4X 8X 16X 32X SLEW RATE (V/Ps) CHARGE PUMP GAIN Figure2.PLLNormalizedNoiseFloorvsOSCinSlewRate Figure3.PLLNormalizedNoiseFloorvsChargePump (K =32X) Gain(SlewRate=2000V/μs) PD -105 -115 )zH )zH /cBd -109 /cBd -117 ( E ( E S S ION -113 ION -119 f/1 D f/1 D EZ -117 EZ -121 ILA ILA M M RO -121 RO -123 N N LLP LLP -125 -125 101 102 103 104 1X 2X 4X 8X 16X 32X SLEW RATE (V/Ps) CHARGE PUMP GAIN Figure4.PLLNormalized1/fNoisevsOSCinSlewRate Figure5.PLLNormalized1/fNoisevsChargePumpGain (K =32X) (SlewRate=2000V/μs) PD -90 Modeled Noise -93 Measured Noise -96 1/f Noise Flat Noise Hz) -99 c/ B -102 d se ( -105 oi e N -108 s ha -111 P -114 -117 -120 1x102 1x103 1x104 1x105 1x106 Offset (Hz) D001 SeePhaseNoiseMeasurementTestSetup Figure6.PLL1/fandNoiseFloorMeasurementoftheLMX2541SQ3740E 12 SubmitDocumentationFeedback Copyright©2009–2014,TexasInstrumentsIncorporated ProductFolderLinks:LMX2541

LMX2541 www.ti.com SNOSB31J–JULY2009–REVISEDDECEMBER2014 Not Ensured Characteristics (continued) -80 -145 -88 -147.5 -96 Hz) -104 Hz) -150 c/ c/ B -112 B d d -152.5 se ( -120 se ( oi oi N -128 N -155 e e s s ha -136 ha -157.5 P P -144 -160 -152 -160 -162.5 1x103 1x104 1x105 1x106 1x107 1x108 5x101 1x102 2x102 5x102 1x103 2x103 Offset (Hz) Offset (Hz) D001 D001 Engagingthedividerreducesthephasenoiseby20× Theaboveplotshowshowthisnoisefloorchangesasafunctionof log(VCO_DIV)exceptatfaroffsetswhereitaddsnoise. thefrequencyoftheRFoutpin. Figure7.DividerNoiseFloorvsDividerValue(f =3700 Figure8.DividerNoiseFloorvsFrequency VCO MHz,VariousValuesforVCO_DIV) Table1.RelativeVCOPhaseNoiseOverTemperatureDrift (AC_TEMP_COMP=24,Vcc=3.3V)(1) TEMPERATURE PHASENOISECHANGEINCELSIUSFORVARIOUSOFFSETS LOCK CURRENT 10kHz 100kHz 1MHz 10MHz 20MHz –40 –40 +0.4 –2.0 –1.6 –1.8 –1.6 –40 25 +0.3 +0.5 +0.5 +0.5 +0.4 –40 85 +0.9 +2.0 +2.4 +2.5 +2.3 25 –40 +0.2 –2.2 –1.7 –2.0 –1.8 25 25 Thisisthedefaultconditiontowhichtheseothernumbersarenormalizedto. 25 85 +0.6 +1.5 +2.0 +2.0 +1.9 85 –40 +0.2 –2.2 –1.7 –1.9 –1.8 85 25 +0.2 +0.2 +0.3 +0.2 +0.2 85 85 +0.6 +1.8 +2.2 +2.3 +2.1 (1) ThetableshowsthetypicaldegradationforVCOphasenoisewhentheVCOislockedatonetemperatureandthetemperatureis allowedtodrifttoanothertemperature.Anegativevalueindicatesaphasenoiseimprovement. Copyright©2009–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 13 ProductFolderLinks:LMX2541

LMX2541 SNOSB31J–JULY2009–REVISEDDECEMBER2014 www.ti.com 7.7.2 OutputPowerinBypassMode The following plots show the trends in output power as a function of temperature, voltage, and frequency. For states where VCOGAIN and OUTTERM are not 12, the table below shows how the output power is modified based on these programmable settings. The measurement of the output power is sensitive to the test circuit. All thenumbersintheelectricalspecificationsandtypicalperformancecurveswereobtainedfromacharacterization setup that accommodate temperature testing and changing of parts. In a more optimized setup the measured RF outputpoweristypicallyontheorderof1.5to2.4dBhigher. 5 6 OUTTERM=12 4 Vcc = 3.3V OUTTERM=15 2 3 )m Vcc = 3.45V )m Bd 2 Bd ( R ( R -2 E E W 1 W OUTTERM=9 O O P 0 P OUTTERM=6 -6 Vcc = 3.15V -1 OUTTERM=3 -2 -10 1750 2250 2750 3250 3750 4250 1750 2250 2750 3250 3750 4250 FREQUENCY (MHz) FREQUENCY (MHz) Figure9.OutputPowervsVoltage(VCO_DIV=1, Figure10.OutputPowervsOUTTERMandFREQUENCY VCOGAIN=12,OUTTERM=12,T =25°C) (VCO_DIV=1,T =25°C,Vcc=3.3V,VCOGAIN=12) A A 5 6 TA = 25o C VCOGAIN=12 4 TA = -40o C VCOGAIN=15 2 3 )m )m Bd 2 Bd VCOGAIN=9 ( R ( R -2 E E W 1 W VCOGAIN=6 O O P 0 TA = 85o C P -6 VCOGAIN=3 -1 -2 -10 1750 2250 2750 3250 3750 4250 1750 2250 2750 3250 3750 4250 FREQUENCY (MHz) FREQUENCY (MHz) Figure11.OutputPowervsTemperature(VCO_DIV=1, Figure12.OutputPowervsVCOGAINandFREQUENCY VCOGAIN=12,OUTTERM=12,Vcc=3.3V) (VCO_DIV=1,T =25°C,Vcc=3.3V,OUTTERM=12) A Table2.ChangeinOutputPowerinBypassModeasaFunctionofVCOGAINandOUTTERM VCOGAIN 3 6 9 12 15 3 –9.7 –8.4 –7.9 –7.8 –7.9 6 –6.6 –4.5 –3.6 –3.4 –3.6 OUTTERM 9 –5.7 –3.1 –1.7 –1.3 –1.3 12 –5.4 –2.5 –0.8 +0.0 +0.1 15 –5.3 –2.2 –0.3 +0.8 +1.1 14 SubmitDocumentationFeedback Copyright©2009–2014,TexasInstrumentsIncorporated ProductFolderLinks:LMX2541

LMX2541 www.ti.com SNOSB31J–JULY2009–REVISEDDECEMBER2014 7.7.3 OutputPowerinDividedMode The measurement of the output power is sensitive to the test circuit. All the numbers in the electrical specifications and typical performance curves were obtained from a characterization setup that accommodate temperature testing and changing of parts. In a more optimized setup the measured RF output power is typically ontheorderof1.5to2.4dBhigher. 9 10 Vcc = 3.3 V OUTTERM=15 8 8 OUTTERM=12 7 6 6 4 )mB 5 Vcc = 3.45 V )mB 2 OUTTERM=6 d d ( R 4 ( R 0 E E OUTTERM=9 W 3 W -2 O O P 2 P -4 1 -6 Vcc = 3.15 V OUTTERM=3 0 -8 -1 -10 0 500 1000 1500 2000 2500 0 500 1000 1500 2000 2500 FREQUENCY (MHz) FREQUENCY (MHz) Figure13.OutputPowervsVoltage(VCO_DIV>1, Figure14.OutputPowervsOUTTERMandFREQUENCY DIVGAIN=12,OUTTERM=12,T =25°C) (VCO_DIV>1,T =25°C,Vcc=3.3V,DIVGAIN=12) A A 9 10 DIVGAIN=15 8 8 DIVGAIN=12 7 6 6 4 )mB 5 TA = -40o C )mB 2 d d ( R 4 ( R 0 EW 3 TA = 25o C EW -2 DIVGAIN=6 O O P 2 P -4 DIVGAIN=9 1 -6 TA = 85o C 0 -8 DIVGAIN=3 -1 -10 0 500 1000 1500 2000 2500 0 500 1000 1500 2000 2500 FREQUENCY (MHz) FREQUENCY (MHz) Figure15.OutputPowervsTemperature(VCO_DIV>1, Figure16.OutputPowervsDIVGAINand DIVGAIN=OUTTERM=12,Vcc=3.3V) FREQUENCY(VCO_DIV>1,T =25°C,Vcc=3.3V, A OUTTERM=12) Table3.ChangeinOutputPowerinDividedModeasaFunctionofDIVGAINandOUTTERM(1) DIVGAIN 3 6 9 12 15 3 –10.2 –6.1 –5.7 –5.5 –5.5 6 –9.8 –4.4 –2.4 –2.1 –2.0 OUTTERM 9 –9.8 –4.3 –1.5 –0.7 –0.5 12 –9.9 –4.3 –1.4 +0.0 +0.2 15 –9.9 –4.4 –1.4 +0.3 +0.7 (1) ThetableshowstheRELATIVEoutputpowertothecaseofVCOGAIN=OUTTERM=12. Copyright©2009–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 15 ProductFolderLinks:LMX2541

LMX2541 SNOSB31J–JULY2009–REVISEDDECEMBER2014 www.ti.com 7.7.4 RFoutOutputImpedance TheimpedanceoftheRFoutpinvariesasafunctionoffrequency,VCO_DIV,OUTTERM,VCOGAIN,DIVGAIN,and frequency.Wheninbypassmode(VCO_DIV=1),theDIVGAINwordhasnoimpactontheoutputimpedance.When individedmode(VCO_DIV>1),theVCOGAINhasnoimpactontheoutputimpedance.Thisgraphicshowshowthe inputimpedancevariesasafunctionoffrequencyforboththebypassanddividedcases. 4 Marker 1: 2 3 1 GHz VCO_DIV 1 2 = 1 Marker 2: 1 2 GHz Marker 3: VCO_DIV > 1 3 GHz Marker 4: 4 GHz Start 30 MHz Stop 5 GHz Figure17.RFoutOutputImpedance Table4.RFoutOutputImpedancevs.VCOGAIN(BypassMode)(1) Freq. VCOGAIN=3 VCOGAIN=6 VCOGAIN=9 VCOGAIN=12 VCOGAIN=15 (MHz) IMAGINA IMAGINA IMAGINA IMAGINA IMAGINA REAL REAL REAL REAL REAL RY RY RY RY RY 50 3.8 2.1 5.5 1.9 7.3 1.8 9.5 1.7 10.1 1.7 100 4.8 4.1 6.1 3.9 7.8 3.7 9.8 3.6 10.3 3.6 200 5.4 5.7 6.8 6.0 8.7 6.3 10.9 6.5 11.4 6.6 400 5.5 9.4 7.5 10.0 9.8 10.6 12.4 11.0 13.1 11.0 600 5.8 15.1 8.1 15.4 10.7 15.7 13.7 15.7 14.5 15.6 800 7.0 20.7 9.6 20.8 12.6 20.8 15.8 20.3 16.7 20.1 1000 9.2 26.3 12.1 26.1 15.4 25.6 19.0 24.6 19.8 24.1 1200 10.7 28.6 13.4 27.9 16.3 26.9 19.3 25.5 20.0 25.0 1400 12.2 30.9 14.7 29.7 17.1 28.2 19.7 26.4 20.2 25.9 1600 13.7 33.2 15.9 31.5 18.0 29.5 20.1 27.4 20.5 26.8 1800 15.2 35.5 17.2 33.3 18.8 30.8 20.5 28.3 20.7 27.7 2000 14.5 39.5 16.4 37.4 17.9 35.0 19.6 32.5 19.8 31.9 2200 15.6 42.9 17.4 40.7 18.7 38.2 20.3 35.6 20.4 35.0 2400 14.2 47.6 16.0 45.3 17.4 42.8 19.0 40.1 19.2 39.4 2600 12.2 51.3 14.1 48.7 15.6 46.5 17.2 43.5 17.3 42.5 2800 11.5 57.9 13.7 55.3 15.3 52.4 17.0 49.0 17.1 48.3 3000 10.6 67.1 13.1 64.0 14.8 60.5 16.3 56.5 16.4 55.7 3200 13.1 77.3 15.7 73.2 17.3 69.0 18.4 64.2 18.4 63.3 3400 17.6 88.1 20.0 82.8 21.1 77.4 21.7 71.8 21.5 70.8 3600 29.0 96.0 30.6 90.2 30.9 83.6 30.2 76.7 29.8 75.6 3800 38.2 99.4 38.0 94.4 36.4 87.3 34.1 80.5 33.4 79.4 (1) ThisisfortheVCOdividerinbypassmode(VCO_DIV=1)andtheRFoutpinpoweredup.OUTTERMwassetto12. 16 SubmitDocumentationFeedback Copyright©2009–2014,TexasInstrumentsIncorporated ProductFolderLinks:LMX2541

LMX2541 www.ti.com SNOSB31J–JULY2009–REVISEDDECEMBER2014 RFout Output Impedance (continued) Table4.RFoutOutputImpedancevs.VCOGAIN(BypassMode)(1)(continued) Freq. VCOGAIN=3 VCOGAIN=6 VCOGAIN=9 VCOGAIN=12 VCOGAIN=15 (MHz) IMAGINA IMAGINA IMAGINA IMAGINA IMAGINA REAL REAL REAL REAL REAL RY RY RY RY RY 4000 43.5 106.0 41.6 99.0 38.9 92.0 35.5 85.1 34.8 83.7 4200 48.0 119.3 45.9 109.8 43.1 101.9 37.2 94.2 36.0 93.0 4400 62.4 137.9 56.4 126.6 49.8 117.6 42.3 109.5 40.8 108.3 4600 87.0 149.4 76.0 138.1 65.4 129.5 54.3 122.2 52.3 121.2 4800 128.1 153.7 109.7 145.6 93.0 140.1 76.7 135.9 74.0 135.5 5000 168.1 134.7 145.4 135.5 124.9 138.0 105.4 141.1 102.4 141.9 Table5.RFoutOutputImpedancevs.OUTTERM(BypassMode)(1) Freq. OUTTERM=3 OUTTERM=6 OUTTERM=9 OUTTERM=12 TERM=15 (MHz) IMAGINA IMAGINA IMAGINA IMAGINA IMAGINA REAL REAL REAL REAL REAL RY RY RY RY RY 50 27.9 1.6 16.2 1.9 12.3 1.8 9.5 1.7 7.8 1.7 100 28.5 2.8 16.7 3.6 12.7 3.6 9.8 3.6 8.0 3.5 200 29.2 3.8 18.1 5.9 14.0 6.3 10.9 6.5 9.0 6.6 400 28.8 5.7 19.2 9.5 15.3 10.3 12.4 11.0 10.6 11.2 600 28.8 8.8 20.4 13.7 16.5 14.9 13.7 15.7 11.9 16.0 800 29.1 11.7 22.5 17.5 18.7 19.2 15.8 20.3 14.0 20.8 1000 28.6 13.4 22.8 19.2 19.3 21.2 16.5 22.5 14.6 23.1 1200 28.0 15.0 23.1 20.9 19.8 23.2 17.1 24.7 15.2 25.4 1400 27.5 16.7 23.3 22.7 20.4 25.2 17.7 26.9 15.8 27.7 1600 27.0 18.4 23.6 24.4 20.9 27.2 18.4 29.0 16.5 30.0 1800 26.4 20.1 23.9 26.1 21.4 29.2 19.0 31.2 17.1 32.3 2000 25.9 21.8 24.1 27.9 22.0 31.1 19.6 33.4 17.7 34.6 2200 25.3 23.5 24.4 29.6 22.5 33.1 20.3 35.6 18.3 36.9 2400 23.1 26.9 22.9 33.2 21.3 37.1 19.0 40.1 17.0 41.8 2600 20.1 29.3 20.5 35.4 19.3 39.6 17.2 42.9 15.1 44.9 2800 18.5 34.2 19.6 40.4 18.8 45.0 17.0 49.0 14.8 51.6 3000 16.6 40.6 18.1 46.9 17.8 51.9 16.3 56.5 14.3 59.7 3200 16.5 47.0 18.9 53.4 19.3 58.9 18.4 64.2 16.7 68.2 3400 17.1 53.8 20.4 60.1 21.8 65.8 21.7 71.8 20.4 76.6 3600 20.8 59.4 25.4 65.0 28.3 70.5 30.2 76.8 30.3 82.5 3800 22.0 64.9 27.3 69.7 31.1 74.6 34.1 80.5 35.4 86.1 4000 23.0 70.0 28.1 74.9 32.1 80.0 35.5 86.4 37.6 92.0 4200 23.7 77.9 28.6 82.8 32.8 87.7 37.0 94.2 39.9 100.9 4400 23.7 93.2 30.1 98.0 35.4 102.9 42.3 109.4 47.8 116.6 4600 27.3 107.4 36.6 112.0 44.8 116.3 54.3 122.2 62.6 128.9 4800 40.1 126.6 52.2 129.8 63.3 132.3 76.7 135.9 89.3 140.5 5000 61.4 142.8 76.2 143.3 89.5 142.3 105.5 141.0 121.0 140.5 (1) TheVCOdividerwasbypassed(VCO_DIV=1)andtheRFoutpinwasenabled.TheVCOGAINwordwassetto12. Copyright©2009–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 17 ProductFolderLinks:LMX2541

LMX2541 SNOSB31J–JULY2009–REVISEDDECEMBER2014 www.ti.com Table6.RFoutOutputImpedancevs.DIVGAIN(DividedMode)(1) Freq. DIVGAIN=3 DIVGAIN=6 DIVGAIN=9 DIVGAIN=12 DIVGAIN=15 (MHz) IMAGINAR IMAGINAR IMAGINAR IMAGINAR IMAGINAR REAL REAL REAL REAL REAL Y Y Y Y Y 50 3.2 2.2 3.6 2.1 5.8 2.0 13.9 1.9 22.3 1.6 100 4.5 4.1 4.6 4.0 6.6 3.8 14.7 3.2 23.2 2.3 200 5.7 5.3 6.4 5.7 7.0 5.9 15.0 4.7 23.0 2.7 400 5.0 9.2 5.6 9.4 7.7 9.5 15.6 7.7 22.8 4.4 600 5.2 14.6 5.7 14.6 7.8 14.6 15.9 12.1 22.2 7.9 800 6.0 20.2 6.5 20.2 8.7 20.2 16.9 16.5 22.3 11.4 1000 7.9 25.7 8.4 25.7 10.7 25.5 18.7 20.5 22.9 14.6 1200 11.0 29.9 11.6 30.0 13.9 29.5 21.4 23.1 24.3 16.8 1400 13.2 32.3 13.9 32.3 16.1 31.7 22.5 24.3 23.9 18.2 1600 14.2 34.4 15.0 34.3 17.1 33.5 22.5 25.8 23.1 20.1 1800 13.9 37.2 14.6 37.0 16.7 36.2 21.6 28.2 21.7 22.9 2000 13.5 41.1 14.3 40.9 16.4 39.9 20.9 31.4 20.6 26.4 2200 14.8 45.1 15.6 44.7 17.8 43.6 21.7 34.5 20.9 29.7 2400 14.1 49.4 14.9 49.0 17.1 47.7 20.4 38.1 19.3 33.5 2600 12.4 52.1 13.2 51.6 15.5 50.1 18.2 40.4 16.8 36.2 2800 11.8 59.3 12.5 58.7 15.0 56.8 17.0 46.2 15.3 42.0 3000 10.7 68.3 11.5 67.6 14.0 65.2 15.2 53.4 13.0 49.2 3200 13.1 78.6 14.0 77.6 16.7 74.5 16.5 61.1 13.8 56.9 3400 18.1 89.6 18.9 88.4 21.6 84.4 19.4 69.2 16.0 65.1 3600 29.2 98.6 29.8 96.9 31.9 91.6 26.1 75.4 21.7 71.6 3800 36.0 105.8 36.5 103.9 37.8 97.5 28.9 81.1 24.0 77.8 4000 43.6 101.4 43.7 99.5 43.7 92.9 32.3 78.8 27.1 76.3 4200 40.6 122.9 40.8 120.3 40.6 111.8 26.6 94.7 20.7 91.8 4400 63.6 143.0 62.9 139.6 59.9 128.6 37.8 111.4 30.0 109.2 4600 90.9 155.3 88.8 151.4 81.1 139.6 49.9 125.8 40.3 124.9 4800 135.8 159.1 131.2 155.7 116.3 145.5 73.7 142.1 61.7 144.0 5000 179.4 135.1 173.2 133.9 153.3 131.4 107.1 147.7 94.5 155.2 (1) ThiswasdonewithRFoutbufferpoweredupandwithOUTTERM=12.VCO_DIVwassetto50. Table7.RFoutOutputImpedancevs.OUTTERM(DividedMode)(1) Freq.(MHz) OUTTERM=3 OUTTERM=6 OUTTERM=9 OUTTERM=12 OUTTERM=15 IMAGINA IMAGINA IMAGINA IMAGINA IMAGINA REAL REAL REAL REAL REAL RY RY RY RY RY 50 44.1 –0.3 31.8 1.0 21.2 1.7 14.0 1.9 9.3 2.0 100 44.9 –2.2 32.8 0.7 22.1 2.5 14.8 3.2 10.0 3.5 200 43.2 –7.2 33.2 –1.2 23.3 2.8 16.1 4.7 11.3 5.6 400 33.2 –8.1 28.5 –1.5 21.9 4.5 15.7 7.7 11.2 9.1 600 28.0 –3.8 25.7 1.8 21.4 8.0 15.9 12.1 11.4 13.9 800 25.1 1.1 24.0 5.6 21.7 11.5 16.9 16.5 12.5 19.0 1000 23.7 5.8 23.3 9.6 22.4 14.7 18.7 20.5 14.6 23.8 1200 23.5 9.3 23.7 12.4 23.8 16.7 21.4 23.1 17.7 27.2 1400 22.6 12.3 22.9 14.8 23.5 18.1 22.5 24.3 19.5 28.9 1600 21.5 15.3 21.8 17.4 22.6 20.0 22.5 25.8 20.2 30.5 1800 20.2 18.8 20.5 20.7 21.3 22.8 21.6 28.2 19.7 33.0 (1) Thiswasdoneindividedmode(VCO_DIV=50)withVCOGAIN=12. 18 SubmitDocumentationFeedback Copyright©2009–2014,TexasInstrumentsIncorporated ProductFolderLinks:LMX2541

LMX2541 www.ti.com SNOSB31J–JULY2009–REVISEDDECEMBER2014 Table7.RFoutOutputImpedancevs.OUTTERM(DividedMode)(1)(continued) Freq.(MHz) OUTTERM=3 OUTTERM=6 OUTTERM=9 OUTTERM=12 OUTTERM=15 2000 19.1 22.9 19.4 24.5 20.1 26.3 20.9 31.4 19.3 36.4 2200 19.4 26.4 19.7 28.0 20.5 29.6 21.7 34.5 20.6 39.8 2400 17.9 30.4 18.2 32.0 18.9 33.4 20.4 38.1 19.8 43.6 2600 15.7 33.3 15.9 34.9 16.5 36.1 18.2 40.4 17.9 45.7 2800 14.5 39.0 14.5 40.7 15.1 42.0 17.0 46.2 17.2 51.9 3000 12.7 46.1 12.6 47.9 12.9 49.2 15.2 53.4 15.8 59.5 3200 13.5 53.5 13.3 55.5 13.8 56.9 16.5 61.1 18.0 67.8 3400 15.5 61.3 15.4 63.5 15.9 65.0 19.4 69.2 22.0 76.5 3600 20.9 67.5 21.1 70.0 21.7 71.5 26.1 75.4 30.5 82.8 3800 22.7 73.3 23.1 76.0 23.9 77.6 28.9 81.1 34.7 88.2 4000 25.4 71.7 26.2 74.5 27.1 76.1 32.3 78.8 39.0 84.7 4200 19.0 86.1 19.8 89.5 20.7 91.4 26.6 94.7 34.6 101.8 4400 26.6 102.0 28.3 106.3 29.9 108.7 37.8 111.4 49.4 118.0 4600 34.9 116.4 37.8 121.5 40.1 124.1 49.8 125.9 65.3 130.6 4800 52.1 134.8 57.4 140.3 61.1 143.1 73.7 141.9 93.8 141.8 5000 78.5 147.4 87.4 152.0 93.3 154.0 107.2 148.0 129.0 138.6 7.7.4.1 OSCinandFinSensitivity Thischartshowsthetypicalsensitivityforasinewave.Notethatatlowerfrequencies,thereisaconstant slopethatsuggeststhatthepartfailswhentheslewratefallsbelow27V/us.Theelectricalspecifications callforaminimumof150V/ustoensuremargin.Also,assomeoftheotherperformancegraphsshow,the OSCinslewratehasanimpactonfractionalspursandphasenoiseaswell.Itisrecommendedtodesignto theelectricalspecifications,notthetypicalperformanceplots. Variationovervoltageandtemperatureistypicallyverysmallandontheorderthanless±1dB. Figure18.OSCinSensitivityforSingle-EndedSINEWave Copyright©2009–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 19 ProductFolderLinks:LMX2541

LMX2541 SNOSB31J–JULY2009–REVISEDDECEMBER2014 www.ti.com 20 10 TA = 25oC Ensured Operating Range 0 m) B d (Oin -10 TA = 85oC C V T X E p -20 TA = -40oC -30 -40 0 1000 2000 3000 4000 5000 6000 7000 8000 fExtVCOin (MHz) ThisplotshowstheExtVCOinsensitivitywhichappliesonlywhenthedeviceisbeingusedinExternalVCO mode. Variationovervoltageistypicallyverysmallandontheorderoflessthan±1dB. Figure19.SINEwaveExtVCOinSensitivity Marker 1: 50 MHz Marker 2: 100 MHz Marker 3: 1 500 MHz XO = 1 4 2 Marker 4: 3 1000 MHz 2 XO = 0 Start 50 MHz 3 4 Stop 1000 MHz Figure20.OSCinInputImpedance Table8.OSCinFrequency FREQUENCY OSCin(NORMALMODE) OSCin(XOMODE) OSCin#(NORMALMODE) (MHz) REAL IMAGINARY REAL IMAGINARY REAL IMAGINARY 1 3945.3 2261.6 9452.3 2182.1 3975.5 2287.0 5 4846.0 –189.6 2397.9 –916.7 4890.1 –150.1 10 4253.4 –1850.1 428.2 –1105.7 4297.4 –1886.7 20 2295.3 –2366.9 248.4 –591.8 2288.6 –2383.8 30 1290.0 –2087.0 187.1 –410.1 1304.3 –2079.1 40 847.9 –1716.1 163.5 –313.3 855.5 –1718.0 20 SubmitDocumentationFeedback Copyright©2009–2014,TexasInstrumentsIncorporated ProductFolderLinks:LMX2541

LMX2541 www.ti.com SNOSB31J–JULY2009–REVISEDDECEMBER2014 Table8.OSCinFrequency(continued) FREQUENCY OSCin(NORMALMODE) OSCin(XOMODE) OSCin#(NORMALMODE) (MHz) 50 581.3 –1464.9 147.9 –257.1 590.7 –1471.6 60 439.2 –1254.1 138.3 –219.0 449.4 –1264.2 70 337.9 –1105.7 131.1 –192.0 349.0 –1115.4 80 269.4 –983.6 127.0 –171.8 276.3 –989.1 90 223.4 –869.9 119.7 –158.0 231.9 –876.2 100 179.2 –776.8 114.5 –143.9 186.9 –783.9 200 52.4 –379.8 93.9 –85.1 54.3 –382.5 300 31.2 –247.0 80.9 –68.9 31.9 –247.4 400 23.5 –181.7 72.3 –58.1 23.8 –180.5 500 20.4 –140.5 65.1 –49.4 20.4 –138.4 600 18.4 –110.2 58.1 –42.1 18.2 –107.6 700 17.0 –88.0 51.9 –35.6 16.7 –85.3 800 15.8 –71.2 47.4 –29.5 15.7 –68.4 900 15.2 –57.6 43.6 –23.4 14.7 –56.3 1000 15.1 –45.2 40.9 –17.2 14.3 –44.7 Marker 1: 7 100 MHz 8 Marker 2: 1 GHz Marker 3: 2 GHz 6 Marker 4: 3 GHz Marker 5: 1 4 GHz 5 Marker 6: 5 GHz Marker 7: 6 GHz 2 Marker 8: 3 7 GHz 4 Start 100 MHz Stop 7000 MHz Figure21.ExtVCOinInputImpedance Copyright©2009–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 21 ProductFolderLinks:LMX2541

LMX2541 SNOSB31J–JULY2009–REVISEDDECEMBER2014 www.ti.com Table9.ExtVCOinFrequency FREQUENCY REAL IMAGINARY 100 627.9 –1532.3 200 193.8 –852.6 400 56.4 –434.5 600 31.3 –287.4 800 23.2 –212.9 1000 17.8 –167.0 1200 15.4 –134.9 1400 14.0 –111.4 1600 12.8 –93.7 1800 11.8 –79.5 2000 11.2 –67.5 2200 10.7 –57.4 2400 10.2 –48.6 2600 10.5 –42.0 2800 9.1 –35.5 3000 7.8 –29.0 3200 7.2 –23.4 3400 6.6 –18.3 3600 5.9 –13.3 3800 5.3 –8.5 4000 5.0 –3.7 4200 4.5 –1.4 4400 4.0 0.9 4600 3.5 3.1 4800 2.6 7.7 5000 1.7 12.1 6000 0.9 26.7 7000 2.3 51.9 22 SubmitDocumentationFeedback Copyright©2009–2014,TexasInstrumentsIncorporated ProductFolderLinks:LMX2541

LMX2541 www.ti.com SNOSB31J–JULY2009–REVISEDDECEMBER2014 8 Parameter Measurement Information 8.1 Bench Test Setups DC Blocking 10 MHz Capacitor SMA Cable Signal Generator OSCin Device Under Test Semiconductor SMA Cable CPout Parameter Pin Analyzer 3.3 V Evaluation Board Power Supply Figure22. ChargePumpCurrentsTestSetup The charge pump is tested in external VCO mode (MODE=1), although it is no external VCO hooked up. The CPout pin should be disconnected from the any external VCO tuning pin, external loop filter, and also the Vtune pin on the device. A signal is then applied to the OSCin pin to ensure that the R counter is oscillating. This signal does not have to be clean and the frequency is very critical. These currents at the CPout pin are typically measuredwithasemiconductorparameteranalyzer. 8.1.1 ChargePumpCurrentMeasurements In order to test the TRI-STATE current, the CPT bit is set to one and the current is measured. Aside from having no other sources of leakage attached to this pin, it is also important that the board be well cleaned before doing this test. The temperature and voltage at the charge pump can then be varied and the resulting leakage current is then recorded. Typically, the leakage currents are worst at higher temperatures and higher charge pump voltages. In order to test the source and sink currents, the CPT bit is set to active mode and the frequency is programmed to something much higher than can be achieved in order to force the charge pump to rail. The reason why this is necessary is that the duty cycle of the charge pump is not 100% unless it is forced against one of the rails. If the charge pump polarity bit (CPP) is set to positive, then the charge pump source current is measured. To measure the sink current, the CPT bit is set to negative. The part is then programmed and the charge pump will rail in one direction. The semiconductor parameter analyzer measures the current at a particular charge pump voltage. The phase detector polarity bit, CPP, can be toggled to test between the negative and positive charge pump gains. In order to test leakage, set the TRI-STATE bit, CPT, to 1 so that this can be measured. For the most accurate measurements, it is desirable that the CPout and Vtune pin are not shorted together for these measurements. Oncethesecurrentsaremeasured,thenthedatasheetparameterscanbecalculated. Asummaryofthesechargepumptestsisgiveninthetablebelow. MEASUREMENT PLL_R PLL_N CPG CPT CPP LeakageCurrent X X X 1(TRI-STATE) X SourceCurrent 1 4000 0-31 0(Active) 1(Positive) SinkCurrent 1 4000 0-31 0(Active) 0(Negative) Copyright©2009–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 23 ProductFolderLinks:LMX2541

LMX2541 SNOSB31J–JULY2009–REVISEDDECEMBER2014 www.ti.com 8.1.2 ChargePumpCurrentDefinitions Figure23. ChargePumpCurrentDefinitions I1=ChargePumpSinkCurrentatV =Vcc-ΔV CPout I2=ChargePumpSinkCurrentatV =Vcc/2 CPout I3=ChargePumpSinkCurrentatV =ΔV CPout I4=ChargePumpSourceCurrentatV =Vcc-ΔV CPout I5=ChargePumpSourceCurrentatV =Vcc/2 CPout I6=ChargePumpSourceCurrentatV =ΔV CPout ΔV=Voltageoffsetfromthepositiveandnegativesupplyrails.Definedtobe0.4voltsforthispart. Figure24. VariationofChargePumpCurrentMagnitudevs.ChargePumpVoltage Figure25. VariationofChargePumpCurrentMagnitudevs.Temperature Figure26. ChargePumpSinkvs.SourceCurrentMismatch 24 SubmitDocumentationFeedback Copyright©2009–2014,TexasInstrumentsIncorporated ProductFolderLinks:LMX2541

LMX2541 www.ti.com SNOSB31J–JULY2009–REVISEDDECEMBER2014 9 Detailed Description 9.1 Overview The LMX2541 is a low-noise synthesizer that can be used with the internal VCO or with an external VCO. The functionaldescriptiongivesmoredetailsonthis. 9.2 Functional Block Diagrams Clean Ultra-Clean Dirty Input Reference Local Oscillator Clock Clock PLL Dist. PLL LMK04000 LMX2541 (Clock Jitter Cleaner) (RF Synthesizer) Figure27. SystemBlockDiagram Vtune VregVCO VCO Charge CPout VrefVCO VREG Pump N Divider ExtVCOin 4/5 Prescaler I(cid:3) Fast FLout 2-63 Modulus Lock Divider Control Comp Ftest/LD RFout VREG RFout VregFRAC MUX FRAC VREG RFoutEN OSCin 2X DATA MUX Serial Interface CLK OSCin* R Control LE Divider CE Figure28. FunctionalBlockDiagram Copyright©2009–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 25 ProductFolderLinks:LMX2541

LMX2541 SNOSB31J–JULY2009–REVISEDDECEMBER2014 www.ti.com 9.3 Feature Description The LMX2541 is a low power, high performance frequency synthesizer system which includes a PLL, Partially Integrated Loop Filter, VCO, VCO Divider, and Programmable Output Buffer. There are three basic modes that the device can be configured in: Full Chip Mode, External VCO Mode, and Divider Only Mode. Full chip mode is intendedtobeusedwiththeinternalVCOandPLL.ThereisalsotheoptionofExternalVCOmode,whichallows the user to connect their own external VCO. Finally, there is Divider only, which is just the VCO divider and outputbuffer.TheactiveblocksforthesemodesaredescribedinTable10: Table10.ActiveBlocks AVAILABLEBLOCKS MODE LOOP VCO OUTPUT PLL VCO FILTER DIVIDER BUFFER Full Yes Yes Yes Yes Yes Chip External Yes No No Yes Yes VCO Divider No No No Yes Yes Only 9.3.1 PLLReferenceOscillatorInputPins TherearethreebasicwaysthattheOSCin/OSCin*pinsmaybeconfiguredasshowninthetablebelow: MODE DESCRIPTION XOBIT Crystal Deviceisusedwithacrystaloscillator 1 Single Deviceisdrivenwithasingle-endedsource,suchasaTCXO. 0 Ended Use this mode when driving with a differential signal, such as an LVDS Differential 0 signal. InadditiontothewaythattheOSCin/OSCin*pinsaredriven,therearealsobitsthateffectthefrequencythatthe chip uses. The OSC_FREQ word needs to be programmed correctly, or the VCO may have issues locking to the properfrequency,becausetheVCOfrequencycalibrationisbasedonthisword. Table11.WordNameandFunction WORDNAME FUNCTION ThisneedstobesetcorrectlyiftheinternalVCOisusedforproper OSC_FREQ calibration. This allows the oscillator frequency to be doubled. The R divider is OSC2X bypassedinthiscase. Higher slew rates tend to yield the best fractional spurs and phase noise, so a square wave signal is best for OSCin. Single ended mode and differential mode have similar results if a square wave is used to drive the OSCinpin.Ifusingasinewave,higherfrequenciestendtoworkbetterduetotheirhigherslewrates. 9.3.2 PLLRDivider The R divider divides the OSCin frequency down to the phase detector frequency. If the doubler is enabled, then theRdividerisbypassed. 9.3.3 PLLPhaseDetectorandChargePump The phase detector compares the outputs of the R and N dividers and generates a correction current corresponding to the phase error. This charge pump current is software programmable to 32 different levels. The phasedetectorfrequency,f ,canbecalculatedasfollows: PD f =f /R (1) PD OSCin 26 SubmitDocumentationFeedback Copyright©2009–2014,TexasInstrumentsIncorporated ProductFolderLinks:LMX2541

LMX2541 www.ti.com SNOSB31J–JULY2009–REVISEDDECEMBER2014 9.3.4 PLLNDividerandFractionalCircuitry The N divider in the LMX2541 includes fractional compensation and can achieve any fractional denominator (PLL_DEN) from 1 to 4,194,303. The integer portion, PLL_N, is the whole part of the N divider value and the fractional portion, PLL_NUM / PLL_DEN, is the remaining fraction. PLL_N, PLL_NUM, and PLL_DEN are softwareprogrammable.Soingeneral,thetotalNdividervalue,N,isdeterminedby: N=PLL_N+PLL_NUM/PLL_DEN (2) The order of the delta-sigma modulator is programmable from integer mode to fourth order. There are also several dithering modes that are also programmable. In order to make the fractional spurs consistent, the modulatorisresetanytimethattheR0registerisprogrammed. 9.3.5 PartiallyIntegratedLoopFilter The LMX2541 integrates the third pole (formed by R3_LF and C3_LF) and fourth pole (formed by R4_LF and C4_LF) of the loop filter. The values for these integrated components can be programmed independently through the MICROWIRE interface. The larger the values of these components, the stronger the attenuation of the internal loop filter. The maximum attenuation can be achieved by setting the internal resistors and capacitors to their maximum value and the minimum attenuation can be attained by setting all of these to their minimum setting.Thispartiallyintegratedloopfiltercanonlybeusedinfullchipmode. Charge CPout Pump R4_LF R3_LF Vtune C2_LF C1_LF R2_LF Figure29. PartiallyIntegratedLoopFilter 9.3.6 LowNoise,FullyIntegratedVCO The LMX2541 includes a fully integrated VCO, including the inductors. The VCO (Voltage Controlled Oscillator) takes the voltage from the loop filter and converts this into a frequency. The VCO frequency is related to the otherfrequenciesanddividervaluesasfollows: f =f ×N=f ×N/R (3) VCO PD OSCin In order to the reduce the VCO tuning gain and therefore improve the VCO phase noise performance, the VCO frequencyrangeisdividedintomanydifferentfrequencybands.Thiscreatestheneedforfrequencycalibrationin order to determine the correct frequency band given a desired output frequency. The frequency calibration routine is activated any time that the R0 register is programmed. It is important that the OSC_FREQ word is set correctlytohavethisworkcorrectly. The VCO also has an internal amplitude calibration algorithm to optimize the phase noise which is also activated any time the R0 register is programmed. The optimum internal settings for this are temperature dependent. If the temperature is allowed to drift too much without being re-calibrated, some minor phase noise degradation could result. For applications where this is an issue, the AC_TEMP_COMP word can be used to sacrifice phase noise at room temperature in order to improve the VCO phase noise over all temperatures. The maximum allowable drift for continuous lock, ΔT , is stated in the electrical specifications. For this part, a number of +125 C means CL thepartwillneverloselockifthepartisoperatedunderrecommendedoperatingconditions. Copyright©2009–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 27 ProductFolderLinks:LMX2541

LMX2541 SNOSB31J–JULY2009–REVISEDDECEMBER2014 www.ti.com 9.3.7 ProgrammableVCODivider The VCO divider can be programmed to any value from 2 to 63 as well as bypass mode if device is in full chip mode. In external VCO mode or divider mode, all values except bypass mode can be used for the VCO divider. The VCO divider is not in the feedback path between the VCO and the PLL and therefore has no impact on the PLLloopdynamics.Afterthisprogrammabledividerischanged,itmaybebeneficialtoreprogramtheR0register to recallibrate the VCO . The frequency at the RFout pin is related to the VCO frequency and divider value, VCO_DIV,asfollows: f =f /VCO_DIV (4) RFout VCO When this divider is enabled, there will be some far-out phase noise contribution to the VCO noise. Also, it may be beneficial for VCO phase noise to reprogram the R0 register to recalibrate the VCO if the VCO_DIV value is changedfrombypasstodivided,orvice-versa. The duty cycle for this divider is always 50%, even for odd divide values. Because of the architecture of this divider that allows it to work to high frequencies and always have a 50% duty cycle, there are a few extra considerations: • In divider only mode, there must be five clock cycles on the ExtVCOin pin after the divide value is programmed in order to cause the divide value to properly changed. It is fine to use more than 5 clock cycles forthispurpose. • For a divide of 4 or 5 ONLY, the R4 register needs to be programmed one more time after the device is fully programmed in order synchronize the divider. Failure to do so will cause the VCO divider to divide by the wrong value. Furthermore, if the VCO signal ever goes away, as is the case when the part is powered down, it is necessary to reprogram the R4 register again to re-synchronize the divider. Furthermore, if the R0 registeriseverprogrammedinfullchipmode,itisalsonecessarytoreprogramtheR4register. 9.3.8 ProgrammableRFOutputBuffer The output power at the RFout pin can be programmed to various levels as well as on and off states. The output state of this pin is controlled by the RFoutEN pin as well as the RFOUT word. The RF output buffer can be disabled while still keeping the PLL in lock. In addition to this, the actual output power level of this pin can be adjusted using the VCOGAIN, DIVGAIN, and OUTTERM programming words. The reader should note that VCOGAINcontrolsthegainoftheVCObuffer,notthetuningconstantinoftheVCO. 9.3.9 PowerdownModes The LMX2541 can be powered up and down using the CE pin or the POWERDOWN bit. When the device is powered down, the programming and VCO calibration information is retained, so it is not necessary to re- program the device when the device comes out of the powered down state (The one exception is when the VCO_DIV value is 4 or 5, which has already been discussed.). The following table shows how to use the bit and pin. CEPIN POWERDOWNBIT DEVICESTATE Low Don'tCare PoweredDown 0 PoweredUp High 1 PoweredDown The device can be programmed in the powerdown state. However, the VCO frequency needs to be changed when the device is powered up because the VCO calibration does not run in the powerdown state. Also, the special programming for VCO_DIV = 4 or 5 has to be done when the part is powered up. In order for the CE pin to properly power the device down when it is held low, the all registers in the device need to have been programmedatleastonetime. 9.3.10 Fastlock The LMX2541 includes the Fastlock feature that can be used to improve the lock times. When the frequency is changed, a timeout counter is used to engage the fastlock for a programmable amount of time. During the time that the device is in Fastlock, the FLout pin changes from high impedance to low, thus switching in the external resistorR2pLFwithR2_LFaswellaschangingtheinternalloopfiltervaluesforR3_LFandR4_LF. 28 SubmitDocumentationFeedback Copyright©2009–2014,TexasInstrumentsIncorporated ProductFolderLinks:LMX2541

LMX2541 www.ti.com SNOSB31J–JULY2009–REVISEDDECEMBER2014 R4_LF R3_LF Vtune Charge CPout Pump C2_LF Fastlock Control FLout C1_LF R2pLF R2_LF Figure30. FastlockSchematic Table 12 shows the charge pump gain, loop filter resistors, and FLout pin change between normal operation and Fastlock. Table12.NormalOperationvsFastlock NORMAL PARAMETER FASTLOCK OPERATION ChargePumpGain CPG FL_CPG LoopFilterResistorR3_LF R3_LF FL_R3_LF LoopFilterResistorR4_LF R4_LF FL_R4_LF High FLoutPin Low Impedance Once the loop filter values and charge pump gain are known for normal mode operation, they can be determined for fastlock operation as well. In normal operation, one cannot use the highest charge pump gain and still use fastlock because there will be no larger current to switch in. If the resistors and the charge pump current are done simultaneously, then the phase margin can be preserved while increasing the loop bandwidth by a factor of Kasshowninthefollowingtable: Copyright©2009–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 29 ProductFolderLinks:LMX2541

LMX2541 SNOSB31J–JULY2009–REVISEDDECEMBER2014 www.ti.com PARAMETER SYMBOL CALCULATION ChargepumpgaininFastlock FL_CPG Typicallychoosetobethelargestvalue. K= LoopBandwidthMultiplier K sqrt(FL_CPG/CPG) FL_R3_LF= InternalLoopFilterResistor FL_R3_LF R3_LF/K FL_R4_LF= InternalLoopFilterResistor FL_R4_LF R4_LF/K R2pLF= ExternalLoopFilterResistor R2pLF R2_LF/(K-1) 9.3.11 LockDetect The Ftest/LD pin of the LMX2541 can be configured to output a signal that gives an indication for the PLL being locked. There are two styles of lock detect; analog and digital. The analog lock detect signal is more of a legacy feature and consists a series of narrow pulses that correspond to when the charge pump comes on. These pulsescanbeintegratedwithanexternalRCfiltertocreategeneratealockdetectsignal.Analoglockdetectcan be configured in a push-pull output or an open drain output. The analog open drain lock detect signal can be integrated with a similar RC filter and requires an additional pullup resistor. This pullup resistor can be much largerthantheresistorintheRCfilterinordertomakeunbalancedtimeconstantsforimprovedsensitivity. The digital lock detect function can also be selected for the Ftest/LD pin to give a logic level indication of lock or unlock. The digital lock detect circuitry works by comparing the difference between the phase of the inputs to the phase detector with a RC generated delay of ε. To indicate a locked state (Lock = HIGH) the phase error must be less than ε for 5 consecutive phase detector cycles. Once in lock (Lock = HIGH), the RC delay is changed to δ. To indicate an out of lock state (Lock = LOW), the phase error must become greater than δ. The values of ε andδ areprogrammablewiththeDLOCKword. 30 SubmitDocumentationFeedback Copyright©2009–2014,TexasInstrumentsIncorporated ProductFolderLinks:LMX2541

LMX2541 www.ti.com SNOSB31J–JULY2009–REVISEDDECEMBER2014 START LD = LOW (Not Locked) NO Phase Error < H YES NO Phase Error < H YES NO Phase Error < H YES NO Phase Error < H YES NO Phase Error < H YES LD = HIGH (Locked) NO YES Phase Error > G Figure31. LockDetect 9.3.12 CurrentConsumption The current consumption of the LMX2541 has many factors that influence it. Determining the current consumption for the entire device involves knowing which blocks are powered up and adding their currents together. The current in the electrical specifications gives some typical cases, but there could be some variation over factors such as the phase detector frequency. Also, the output buffer current can be impacted by the software controllable settings. By subtracting or adding combinations of the currents for the RFout buffer and VCO divider, the current consumption for the device can be estimated for any usable configuration. The currents forthebufferandVCOdividerareasfollows: BLOCK CURRENT(mA) ~40 RFOutputBuffer (SeeProgrammableOutputPowerwithOn/Off) VCODivider 32 Copyright©2009–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 31 ProductFolderLinks:LMX2541

LMX2541 SNOSB31J–JULY2009–REVISEDDECEMBER2014 www.ti.com 9.3.13 FractionalSpurs 9.3.13.1 PrimaryFractionalSpurs The primary fractional spurs occur at multiples of the channel spacing and can change based on the fraction. For instance, if the phase detector frequency is 10 MHz, and the channel spacing is 100 kHz, then this could be achievedusingafractionof1/100.Thefractionalspurswouldbeatoffsetsthataremultiples100kHz. 9.3.13.2 Sub-FractionalSpurs Sub-fractional spurs occur at sub-multiples of the channel spacing, Fch. For instance, in the above example, there could be a sub-fractional spur at 50 kHz. The occurrence of these spurs is dependent on the modulator order. Integer mode and the first order modulator never have sub-fractional spurs. If the fractional denominator can be chosen to avoid factors of 2 or 3, then there will also be no sub-fractional spurs. Sub-fractional spurs get worse for higher order modulators. Dithering tends to reduce sub-fractional spurs at the expense of increasing PLLphasenoise.Table13providesguidanceonpredictingsub-fractionalspuroffsetfrequencies. Table13.Sub-FractionalSpurOffsetFrequencies vs. ModulatorOrderandFractionalDenominatorFactors FRACTIONALDENOMINATORFACTORS ORDER NOFACTORof2or3 FACTORof2butnot3 FACTORof3butnot2 FACTORof2and3 IntegerMode None None None None 1stOrderModulator None None None None 2ndOrderModulator None Fch/2 None Fch/2 3rdOrderModulator None Fch/2 Fch/3 Fch/6 4thOrderModulator None Fch/4 Fch/3 Fch/12 9.3.14 ImpactofVCO_DIVonFractionalSpurs Because the fractional and sub-fractional spur levels do not depend on output frequency, there is a big benefit to division. In general, every factor of 2 gives a 6 dB improvement to fractional spurs. Also, because the spur offset frequency is not divided, the channel spacing at the VCO can be also increased to improve the spurs. However, if the on-chip VCO is used, crosstalk can cause spurs at a frequency of f mod f . Consider the following RFout PD exampleofa50MHzphasedetectorfrequencyandVCO_DIV=2.IftheVCOisat3000.1MHzanddividedby2 to get 1500.05 MHz, there will be a spur at an offset of 50 kHz (1500.05 MHz mod 50 MHz). However, if the VCO frequency is at 3050.1 MHz, the output will be at 1525.05 MHz, but the spur will be at a much farther offset thatcaneasilybefilteredbytheloopfilterof25.05MHz(1525.05MHzmod50MHz). 9.3.15 PLLPhaseNoise 9.3.15.1 Figure6,LMX2541SQ3740ERawPhaseNoiseMeasurementPlotDescription The above plot demonstrates the PLL phase noise of the LMX2541SQ3700E operating at 3700 MHz output frequency, phase detector frequency of 100 MHz, and charge pump gain of 32X. The loop bandwidth was made as wide as possible to fully expose the PLL phase noise and reference source was a 100 MHz Wenzel crystal. This measurement was done in integer mode. To better understand the impact of using fractional mode, consult theapplicationssection. The measured noise is the sum of the PLL 1/f noise and noise floor. At offsets below 1 kHz, the PLL 1/f noise dominates and changes at a rate of 10 dB/decade. The noise at 1 kHz is dominated by this 1/f noise and has a value of -103 dBc/Hz. In the 100 - 200 kHz offset range, the noise is -113.7 dBc/Hz and is dominated by the PLL noisefloor.Itcanbeshownthatiftheeffectsoftheloopfilterpeakingandthe1/fnoisearesubtractedawayfrom thismeasurement,itwouldbeabout0.6dBbetter. If the phase detector frequency is changed with the VCO frequency held constant, the PLL noise floor will change, but the 1/f noise will remain the same. If the VCO frequency is changed, both the 1/f noise and PLL noisefloorchangeatarateof20dB/decade. 32 SubmitDocumentationFeedback Copyright©2009–2014,TexasInstrumentsIncorporated ProductFolderLinks:LMX2541

LMX2541 www.ti.com SNOSB31J–JULY2009–REVISEDDECEMBER2014 9.3.15.2 Figure37,LMX2541SQ2690SystemPhaseNoisePlotDescription For this plot, a third order modulator with dithering disabled was used with a fractional denominator of 500000. The charge pump gain was 32X and the loop filter components were C1 = 2.2 nF, C2 = 22 nF, R2 = 470 Ω. The internal loop filter components were C3_LF = 20 pF, C4_LF = 100 pF, R3_LF = 1 kΩ, R4_LF = 200 Ω. The VCO frequency is 2720.1 MHz. The OSCin signal was a 500 MHz differential LVPECL output of the LMK04033. 9.3.15.3 PhaseNoiseofPLL Disregarding the impact of reference oscillator noise, loop filter resistor thermal noise, and loop filter shaping, the phase noise of the PLL can be decomposed into three components: flicker noise, flat noise, and fractional noise. ThesenoisesourcesaddinanRMSsensetoproducethetotalPLLnoise.Inotherwords: L (f)=10·log(10(L (f)/10)+10(L (f)/10)+10(L (f)/10) (5) PLL PLL_flat PLL_flicker PLL_fractional Table14.PotentialInfluencingFactors POTENTIALINFLUENCINGFACTORS SYMBOL f f f K FRAC VCO PD PD L (f) No Yes Yes Yes No PLL_flat L (f) Yes Yes No Yes No PLL_flicker L (f) Yes No Yes No Yes PLL_fractional The preceding table shows which factors of offset frequency (f), VCO frequency (f ), phase detector frequency VCO (f ), charge pump gain (K ), and the fractional settings (FRAC) can potentially influence each phase noise PD PD component.Thefractionalsettingsincludethefraction,modulatororder,anddithering. For the flat noise and flicker noise, it is possible to normalize each of these noise sources into a single index. By normalizing these noise sources to an index, it makes it possible to calculate the flicker and flat noise for an arbitrary condition. These indices are reported in the electrical characteristics section and in the typical performancecurves. Table15.NoiseComponent NOISECOMPONENT INDEX RELATIONSHIP L (f)= LN PLL_flat L (f) PLL_flat LN PLL_flat (1Hz) PLL_flat(1Hz) +20·log(N)+10·log(f ) PD L (f)= LN PLL_flicker L (f) PLL_flicker LN (10kHz) PLL_flicker (10kHz) PLL_flicker -10·log(10kHz/f)+20·log(f /1GHz) VCO The flat noise is dependent on the PLL N divider value (N) and the phase detector frequency (f ) and the 1 Hz PD Normalized phase noise ( LN ). The 1 Hz normalized phase noise can also depend on the charge PLL_flat(1 Hz) pump gain as well. In order to make an accurate measurement of just the flat noise component, the offset frequency must be chosen sufficiently smaller then the loop bandwidth of the PLL, and yet large enough to avoid a substantial noise contribution from the reference and PLL flicker noise. This becomes easier to measure for lowerphasedetectorfrequencies. The flicker noise, also known as 1/f noise, can be normalized to 1 GHz carrier frequency and 10 kHz offset, LN (10kHz).Flickernoisecandominateatlowoffsetsfromthecarrierandhasa10dB/decadeslopeand PLL_flicker improves with higher charge pump currents and at higher offset frequencies . To accurately measure the flicker noise it is important to use a high phase detector frequency and a clean crystal to make it such that this measurement is on the 10 dB/decade slope close to the carrier. L (f) can be masked by the reference PLL_flicker oscillatorperformanceifalowpowerornoisysourceisused. An alternative way to interpret the flicker noise is the 1/f noise corner, f . This would be the offset frequency corner where the flat noise and flicker noise are equal. This corner frequency changes as a function of the phase detectorfrequencyandcanberelatedtotheflatandflickernoiseindicesasshownbelow. f =10((LN (10kHz)-LN (1Hz)-140)/10)×f (6) corner PLL_flicker PLL_flat PD Copyright©2009–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 33 ProductFolderLinks:LMX2541

LMX2541 SNOSB31J–JULY2009–REVISEDDECEMBER2014 www.ti.com Based on the values for LNPLL_flicker(10 kHz) and LNPLL_flat(1Hz) as reported in the electrical specifications, the corner frequency can be calculated. For example, one of the plots in the typical performance characteristics shows the phase noise with a 100 MHz phase detector frequency and 32X charge pump gain. In this case, this cornerfrequencyworksouttobe0.000123 ×100MHz=12.3kHz. K LN LN f PD PLL_flicker(10kHz) PLL_flat(1Hz) corner 1X -116.0dBc/Hz -220.8dBc/Hz 0.000302×f PD 32X -124.5dBc/Hz -225.4dBc/Hz 0.000123×f PD For integer mode or a first order modulator, there is no fractional noise (disregarding fractional spurs). For higher order modulators, the fractional engine may or may not add significant phase noise depending on the fraction andchoiceofdithering. 9.3.16 ImpactofModulatorOrder,Dithering,andLargerEquivalentFractionsonSpursandPhaseNoise To achieve a fractional N value, an integer N divider is modulated between different values. This gives rise to three main degrees of freedom with the LMX2541 delta-sigma engine: the modulator order, dithering, and the way that the fractional portion is expressed. The first degree of freedom, the modulator order, can be selected as zero (integer mode), one, two, three, or four. One simple technique to better understand the impact of the delta- sigma fractional engine on noise and spurs is to tune the VCO to an integer channel and observe the impact of changing the modulator order from integer mode to a higher order. A higher fractional modulator order in theory yields lower primary fractional spurs. However, this can also give rise to sub-fractional spurs in some applications. The second degree of freedom is dithering. Dithering seeks to improve the sub-fractional spurs by randomizing the sequence of N divider values. In theory, a perfectly randomized sequence would eliminate all sub-fractional spurs, but add phase noise by spreading the energy that would otherwise be contained in the spurs.Thethirddegreeoffreedomisthewaythatthefractionisexpressed.Forexample,1/10canbeexpressed as a larger equivalent fraction of 100000/1000000. Using larger equivalent fractions tends to increase randomization similar to dithering. In general, the very low phase noise of the LMX2541 exposes the modulator noise when dithering and large fractions are used, so use these with caution. The avid reader is highly encouraged to read application note 1879 for more details on fractional spurs. The following table summarizes therelationshipsbetweenspurtypes,phasenoise,modulatororder,ditheringandfractionalexpression. ACTION USING NOISE/SPURTYPE INCREASE INCREASE LARGER MODULATOR DITHERING EQUIVALENT ORDER FRACTIONS WORSE PhaseNoise (Butonlyforlargerfractionsor WORSE WORSE moredithering) PrimaryFractionalSpur BETTER NOIMPACT NOIMPACT WORSE Sub-FractionalSpurs (Createsmoresub BETTER BETTER -fractionalspurs) 9.3.17 ModulatorOrder In general, the fractional mode of the PLL enables the use of a higher phase detector frequency relative to the channel spacing, which enables the in-band noise of the PLL to be lower. The choice of modulator order to be used in fractional mode is based on how much higher f can be made relative to the channel spacing and the PD acceptable spur levels. The LMX2541 has a programmable modulator order which allows the user to make a trade-offbetweenPLLnoiseandprimaryandsub-fractionalspurperformance.Thefollowingtableprovidessome general guidelines for choosing modulator order: Note that the spurs due to crosstalk will not be impacted by modulatororder. 34 SubmitDocumentationFeedback Copyright©2009–2014,TexasInstrumentsIncorporated ProductFolderLinks:LMX2541

LMX2541 www.ti.com SNOSB31J–JULY2009–REVISEDDECEMBER2014 ORDER GUIDELINESFORUSE • Useiff canbemadeveryhighwithoutusingafractionalNvalue. PD IntegerMode • Use if it is not desired to make f higher using a fractional N value. This could be the case if the loop PD bandwidthisverynarrowandsmallerloopfiltercapacitorsaredesired. • Use 1st order if f can be increased by at least a factor of four over the integer case and fractional spur PD frequenciesandlevelsareacceptable. 1stOrderModulator • Ifthechannelspacingis5MHzorgreater,the1stordermodulatormayprovidebetterspurperformancethan integermode. • If the spurs of the 1st order modulator are unacceptable, use a higher order modulator. If the spurious componentsareduetocrosstalktheywillnotbeimprovedbyincreasingmodulatororder.Inthiscase,usethe 2ndOrderModulator lowestordermodulatorthatgivesacceptableperformance. 3rdOrderModulator • Useifthespursofthe1stordermodulatorareunacceptable. 4thOrderModulator • Ingeneral, use thelowestordermodulatorunlessa higherordermodulatoryields an improvementinprimary fractional spurs. If the spurious components are due to crosstalk, they will not be improved by increasing the modulatororder. 9.3.18 ProgrammableOutputPowerwithOn/Off The power level of the RFout pin is programmable, including on/off controls. The RFoutEN pin and RFOUT word can be used to turn the RFout pin on and off while still keeping the VCO running and in lock. In addition to on/off states, the power level can also be programmed in various steps using the VCOGAIN, DIVGAIN, and OUTTERM programming words. There are tables in the Typical Characteristics section that discuss the impact of these words on the output power. In addition to impacting the output power, these words also impact the current consumption of the device. This data was obtained as an average over all frequencies. In general, it is desirable tofindthecombinationofprogrammingwordsthatgivesthelowestcurrentconsumptionforagivenoutputpower level. All numbers reported are relative to the case of VCOGAIN = OUTTERM = 12. According to this data, using a VCOGAIN or OUTTERM value of 12 or greater yields only a small increase in output power, but a large increaseincurrentconsumption. Table16.ChangeinCurrentConsumptioninBypassModeasaFunctionofVCOGAINandOUTTERM VCOGAIN 3 6 9 12 15 3 -26.0 -22.3 -18.6 -15.1 -11.8 6 -18.5 -15.5 -12.6 -9.7 -6.9 OUTTERM 9 -11.1 -9.0 -6.9 -4.7 -2.5 12 -3.8 -2.6 -1.4 +0.0 +1.5 15 +3.3 +3.7 +4.0 +4.5 +5.3 Table17.ChangeinCurrentConsumptioninDividedModeasaFunctionofDIVGAINandOUTTERM DIVGAIN 3 6 9 12 15 3 -24.4 -21.7 -18.7 -15.9 -13.3 6 -16.2 -14.6 -12.6 -10.1 -8.0 OUTTERM 9 -8.3 -7.6 -6.8 -5.0 -3.2 12 -0.5 -0.7 -0.7 +0.0 +1.3 15 +7.1 +6.0 +5.2 +4.9 +5.6 9.3.19 LoopFilter Loop filter design can be rather complicated, but there are design tools and references available at www.ti.com. The loop bandwidth can impact the size of loop filter capacitors and also how the phase noise is filtered. For optimal integrated phase noise, choose the bandwidth to be about 20% wider than the frequency where the in- band PLL phase noise (as described in PLL Phase Noise) and open loop VCO noise cross. This optimal loop bandwidthmayneedadjustmentdependingontheapplicationrequirements.Reductionofspurscanbeachieved Copyright©2009–2014,TexasInstrumentsIncorporated SubmitDocumentationFeedback 35 ProductFolderLinks:LMX2541

LMX2541 SNOSB31J–JULY2009–REVISEDDECEMBER2014 www.ti.com by reducing the loop bandwidth. On the other hand, a wider loop bandwidth may be required for faster lock time. Note that using the integrated loop filter components can lead to a significant restriction on the loop bandwidth and should be used with care. 2 kΩ for R3_LF and R4_LF is a good starting point. If the integrated loop filter restricts the loop bandwidth, then first try to relieve this restriction by reducing the integrated loop filter resistors andthenreducethecapacitorsonlyifnecessary. 9.3.20 InternalVCODigitalCalibrationTime When the LMX2541 is used in full chip mode, the integrated VCO can impact the lock time of the system. This digital calibration chooses the closest VCO frequency band, which typically gets the device within a frequency error 10 MHz or less of the final settling frequency, although this final frequency error can change slightly between the different options of the LMX2541. Once this digital calibration is finished, this remaining frequency errormustsettleout,andthisremaininglocktimeisdictatedbytheloopbandwidth. Basedonmeasureddata,thisdigitalcalibrationtimecanbeapproximatedbythefollowingformula: LockTime=A+B/CLK+C·ΔF+D·(ΔF/CLK) (7) SYMBOL1 VALUE UNITS Locktime Varies µs A 30 μs B 3800 None C 0.1 us/MHz D 2 µs ΔF Varies MHz f /2 OSCin for0≤OSC_FREQ≤63 f /4 CLK OSCin None for64≤OSC_FREQ≤127 f /8 OSCin for128≤OSC_FREQ For example, consider the LMX2541SQ3320E changing from 3600 to 3400 with an OSCin frequency of 100 MHz. In this case, ΔF = 200 (direction of frequency change does not matter), f = 100 MHz, and OSCin OSC_FREQ=100. The calibration circuitry is run at a clock speed of CLK = 100 MHz / 4 = 25 MHz. When this values are substituted in the formula, the resulting lock time is 218 μs. After this time, the VCO will be within about 10 MHz of the final frequency and this final frequency error will settle out in an analog fashion. This final frequencyerrorcanbeslightlydifferentdependingonwhichoptionoftheLMX2541isbeingused. 9.4 Device Functional Modes 9.4.1 ExternalVCOMode The LMX2541 also has provisions to be driven with an external VCO as well. In this mode, the user has the option of using the RFout pin output, although if this pin is used, the VCO input frequency is restricted to 4 GHz. If not used, the RFout pin should be left open. The VCO input is connected to the ExtVCOin pin. Because the internal VCO is not being used, the part option that is being used does not have a large impact on phase noise orspurperformance.ItisalsopossibletoswitchbetweenbothFullChipmodeandExternalVCOmode. 9.4.2 DigitalFSKMode The LMX2541 supports 2-level digital frequency shift keying (FSK) modulation. The bit rate is limited by the loop bandwidth of the PLL loop. As a general rule of thumb, it is desirable to have the loop bandwidth at least twice thebitrate.ThisisachievedbychangingtheNcounterrapidlybetweentwostates.Thefractionalnumeratorand denominator are restricted to a length of 12 bits. The 12 LSB’s of the numerator and denominator set the center frequency, Fcenter, and the 10 MSB’s of the numerator set the frequency deviation, Fdev. The LMX2541 has the ability to switch between two different numerator values based on the voltage at the DATA pin. When DATA is low, the output frequency will be Fcenter – Fdev and when the DATA pin is high the output frequency will be Fcenter + Fdev. A limitation of the FSK mode is the frequency deviation cannot cause the N counter to cross integerboundaries.WhenusingFSKmode,theFDMbitneedstobesettozero. 36 SubmitDocumentationFeedback Copyright©2009–2014,TexasInstrumentsIncorporated ProductFolderLinks:LMX2541