- 型号: LMH7322SQ/NOPB

- 制造商: Texas Instruments

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

LMH7322SQ/NOPB产品简介:

ICGOO电子元器件商城为您提供LMH7322SQ/NOPB由Texas Instruments设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 LMH7322SQ/NOPB价格参考。Texas InstrumentsLMH7322SQ/NOPB封装/规格:线性 - 比较器, 通用 比较器 差分,LVDS,RSPECL 24-WQFN(4x4)。您可以下载LMH7322SQ/NOPB参考资料、Datasheet数据手册功能说明书,资料中有LMH7322SQ/NOPB 详细功能的应用电路图电压和使用方法及教程。

LMH7322SQ/NOPB 是德州仪器 (Texas Instruments) 生产的一款高性能、低功耗的双通道高速比较器,属于线性 - 比较器类别。该型号具有多种应用场景,尤其适用于对速度和精度要求较高的领域。 1. 高速信号处理:LMH7322SQ/NOPB 的高工作频率(高达 600 MHz)使其非常适合用于高速信号处理系统中,如通信设备、数据采集系统等。它可以快速响应输入信号的变化,确保系统的实时性和准确性。 2. 过压保护电路:在电源管理或传感器接口中,比较器可以用来检测电压是否超过设定阈值,从而触发保护机制。LMH7322SQ/NOPB 的快速响应时间能够有效防止过压损坏敏感元件。 3. 模拟-数字转换器 (ADC):作为 ADC 的前端组件,比较器负责将模拟信号与参考电压进行比较,并输出相应的数字信号。其低功耗特性有助于延长电池供电设备的工作时间。 4. 音频处理:在专业音频设备中,该比较器可用于音量控制、峰值检测等功能,提供更精确的声音处理效果。 5. 工业自动化:在工业控制系统中,比较器常用于监控温度、压力等物理量的变化。LMH7322SQ/NOPB 的宽工作温度范围 (-40°C 至 +85°C) 和稳定性使其成为理想选择。 6. 医疗设备:对于需要高精度测量的生命体征监测仪等医疗设备而言,这款比较器能提供可靠的性能支持。 总之,LMH7322SQ/NOPB 凭借其出色的电气参数,在众多需要快速、准确比较功能的应用场景中表现出色。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC) |

| CMRR,PSRR(典型值) | 80dB CMRR,80dB PSRR |

| 描述 | IC COMPARATOR DUAL 700PS 24-LLP |

| 产品分类 | |

| 品牌 | Texas Instruments |

| 数据手册 | |

| 产品图片 |

|

| 产品型号 | LMH7322SQ/NOPB |

| rohs | 无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | - |

| 产品目录页面 | |

| 传播延迟(最大值) | 0.783ns |

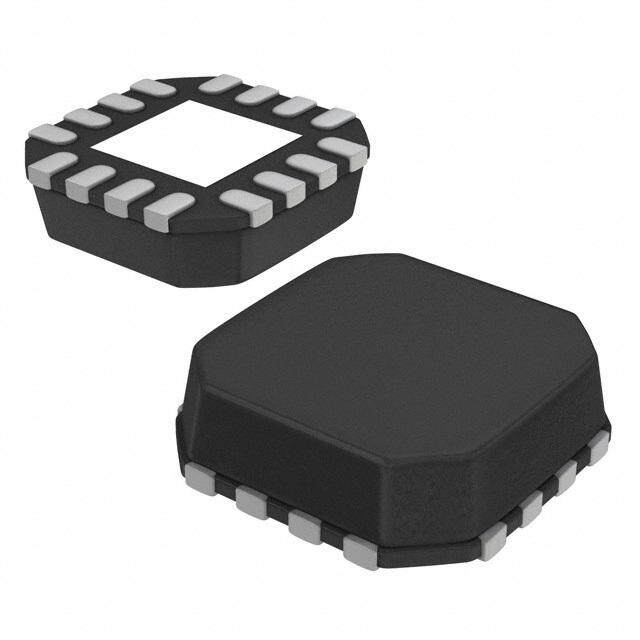

| 供应商器件封装 | 24-WQFN(4x4) |

| 元件数 | 2 |

| 其它名称 | LMH7322SQ |

| 包装 | 带卷 (TR) |

| 安装类型 | 表面贴装 |

| 封装/外壳 | 24-WFQFN 裸露焊盘 |

| 工作温度 | -40°C ~ 125°C |

| 标准包装 | 1,000 |

| 滞后 | 75mV |

| 电压-电源,单/双 (±) | 2.7 V ~ 12 V, ±1.35 V ~ 6 V |

| 电压-输入失调(最大值) | 8mV @ 5V |

| 电流-输入偏置(最大值) | 5µA @ 5V |

| 电流-输出(典型值) | 25mA |

| 电流-静态(最大值) | 10mA |

| 类型 | 通用 |

| 输出类型 | 差分,LVDS,RSPECL |

| 配用 | /product-detail/zh/LMH7322EVAL/LMH7322EVAL-ND/1640850 |

PDF Datasheet 数据手册内容提取

LMH7322 www.ti.com SNOSAU8I–MARCH2007–REVISEDMARCH2013 LMH7322 Dual 700 ps High Speed Comparator with RSPECL Outputs CheckforSamples:LMH7322 FEATURES DESCRIPTION 1 • (V =+5V,V =+5V) The LMH7322 is a dual comparator with 700 ps 2 CCI CCO propagation delay, low dispersion of 75 ps and an • PropagationDelay700ps input voltage range that extends from V -1.5V to CC • OverdriveDispersion20mV-1V75ps V . The devices can be operated from a wide supply EE • FastRiseandFallTimes160ps voltage range of 2.7V to 12V. The adjustable hysteresis adds flexibility and prevents oscillations. • WideSupplyRange2.7Vto12V Both the outputs and latch inputs of the LMH7322 are • InputCommonModeRangeExtends200mV RSPECL compatible. When used in combination with BelowNegativeRail aV supplyvoltageof2.5VtheoutputshaveLVDS CCO • AdjustableHysteresis compatiblelevels. • (RS)PECLOutputs(seeApplication The LMH7322 is available in a 24-pin WQFN Information) package. • (RS)PECLLatchInputs(seeApplication Information) APPLICATIONS • DigitalReceivers • High-SpeedSignalRestoration • Zero-CrossingDetectors • High-SpeedSampling • WindowComparators • High-SpeedSignalTriggering Typical Application 5V + O O VCCI VCC VCC ECL driver Ctraonuspmleids sion line Line TerminationIN+ Q IN- 1/2 ORUS-TPPEUCTL LMH 7322 VOH = 3.9V VT = VCCO-2V VOL = 3.5V or RHYS Q VT = VEE RT RT LL R V VT EE H E R E E 10k F -5.2V LE levels referred to VCCO + Figure1. (RS)ECLtoRSPECLConverter 1 Pleasebeawarethatanimportantnoticeconcerningavailability,standardwarranty,anduseincriticalapplicationsof TexasInstrumentssemiconductorproductsanddisclaimerstheretoappearsattheendofthisdatasheet. Alltrademarksarethepropertyoftheirrespectiveowners. 2 PRODUCTIONDATAinformationiscurrentasofpublicationdate. Copyright©2007–2013,TexasInstrumentsIncorporated Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarilyincludetestingofallparameters.

LMH7322 SNOSAU8I–MARCH2007–REVISEDMARCH2013 www.ti.com Thesedeviceshavelimitedbuilt-inESDprotection.Theleadsshouldbeshortedtogetherorthedeviceplacedinconductivefoam duringstorageorhandlingtopreventelectrostaticdamagetotheMOSgates. Absolute Maximum Ratings (1)(2) ESDTolerance (3) HumanBodyModel 2.5kV MachineModel 250V OutputShortCircuitDuration See (4)(5)(6) SupplyVoltages(V –V ) 13.2V CCx EE DifferentialVoltageatInputPins ±13V VoltageatInputPins V -0.2VtoV +0.2V EE CCI VoltageatLEPins V -0.2VtoV +0.2V EE CCO CurrentatOutputPins 25mA SolderingInformation: SeeProductFolderatwww.ti.comandSNOA549 StorageTemperatureRange −65°Cto+150°C JunctionTemperature (7) +150°C (1) AbsoluteMaximumRatingsindicatelimitsbeyondwhichdamagetothedevicemayoccur.OperatingRatingsindicateconditionsfor whichthedeviceisintendedtobefunctional,butspecificperformanceisnotensured.Forensuredspecificationsandthetest conditions,seetheElectricalCharacteristics. (2) IfMilitary/Aerospacespecifieddevicesarerequired,pleasecontacttheTexasInstrumentsSalesOffice/Distributorsforavailabilityand specifications. (3) HumanBodyModel,applicablestd.MIL-STD-883,Method3015.7.MachineModel,applicablestd.JESD22-A115-A(ESDMMstd.of JEDEC).Field-InducedCharge-DeviceModel,applicablestd.JESD22-C101-C(ESDFICDMstd.ofJEDEC). (4) Appliestobothsingle-supplyandsplit-supplyoperation.Continuousshortcircuitoperationatelevatedambienttemperaturecanresultin exceedingthemaximumallowedjunctiontemperatureof150°C. (5) Shortcircuittestisamomentarytest.Seenextnote. (6) ThemaximumpowerdissipationisafunctionofT ,θ .Themaximumallowablepowerdissipationatanyambienttemperatureis J(MAX) JA P =(T –T )/θ .AllnumbersapplyforpackagessoldereddirectlyontoaPCBoard. D J(MAX) A JA (7) Typicalvaluesrepresentthemostlikelyparametricnormasdeterminedatthetimeofcharacterization.Actualtypicalvaluesmayvary overtimeandwillalsodependontheapplicationandconfiguration.Thetypicalvaluesarenottestedandarenotensuredonshipped productionmaterial. Operating Conditions (1) SupplyVoltage(V –V ) 2.7Vto12V CCx EE OperatingTemperatureRange (2)(3) −40°Cto+125°C PackageThermalResistance (2)(3) 24-PinWQFN 38°C/W (1) AbsoluteMaximumRatingsindicatelimitsbeyondwhichdamagetothedevicemayoccur.OperatingRatingsindicateconditionsfor whichthedeviceisintendedtobefunctional,butspecificperformanceisnotensured.Forensuredspecificationsandthetest conditions,seetheElectricalCharacteristics. (2) ThemaximumpowerdissipationisafunctionofT ,θ .Themaximumallowablepowerdissipationatanyambienttemperatureis J(MAX) JA P =(T –T )/θ .AllnumbersapplyforpackagessoldereddirectlyontoaPCBoard. D J(MAX) A JA (3) ElectricalTablevaluesapplyonlyforfactorytestingconditionsatthetemperatureindicated.Factorytestingconditionsresultinvery limitedself-heatingofthedevicesuchthatT =T .Nospecificationofparametricperformanceisindicatedintheelectricaltablesunder J A conditionsofinternalself-heatingwhereT >T .SeeApplicationssectionforinformationontemperaturede-ratingofthisdevice. J A 2 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LMH7322

LMH7322 www.ti.com SNOSAU8I–MARCH2007–REVISEDMARCH2013 12V DC Electrical Characteristics Unlessotherwisespecified,alllimitsarespecifiedforT =25°C,V =V =12V,V =0V,R =50ΩtoV -2V,V = J CCI CCO EE L CCO CM 300mV,R =1kΩ.Boldfacelimitsapplyattemperatureextremes. HYS Min Typ Max Symbol Parameter Conditions (1) (2) (1) Units INPUTCHARACTERISTICS I InputBiasCurrent V Differential=0V;R =8kΩ −5 −2.9 µA B IN HYS BiasedatV CM I InputOffsetCurrent V Differential=0V −250 40 +250 nA OS IN TCI InputOffsetCurrentTC V Differential=0V 0.2 nA/°C OS IN V InputOffsetVoltage −8 −2 +8 mV OS TCV InputOffsetVoltageTC 12 µV/°C OS V InputVoltageRange forCMRR≥50dB V −0.2 V −1.5 V RI EE CCI V InputDifferentialVoltageRange −1 +1 V RID CMRR CommonModeRejectionRatio 0V≤V ≤V −0.2 80 dB CM CC1 PSRR PowerSupplyRejectionRatio 80 dB A ActiveGain 53 dB V Hyst Hysteresis VHYS=V(HYS+)-V(HYS-),RHYS=0Ω 25 50 75 mV LATCHENABLECHARACTERISTICS I LatchEnableBiasCurrent BiasedatRSPECLLevel 3 10 µA B-LE V LatchEnableOffsetVoltage BiasedatRSPECLLevel −5 mV OS-LE V LatchEnableVoltageRange forCMRR≥50dB V +1.4 V -0.8 V RI-LE EE CCO V LatchEnableDifferentialVoltage ±0.4 V RID-LE Range OUTPUTCHARACTERISTICS V OutputVoltageHigh V Differential=50mV V −1.1 mV OH IN CCO V V OutputVoltageLow V Differential=50mV V −1.5 mV OL IN CCO V V OutputVoltageDifferential V Differential=50mV 360 mV OD IN POWERSUPPLIES I V SupplyCurrent/Channel 6.5 10 VCCI CCI mA 12 I V SupplyCurrent/Channel LoadCurrentExcluded 16.3 20 mA VCCO CCO 25 (1) Alllimitsarespecifiedbytestingorstatisticalanalysis. (2) Typicalvaluesrepresentthemostlikelyparametricnormasdeterminedatthetimeofcharacterization.Actualtypicalvaluesmayvary overtimeandwillalsodependontheapplicationandconfiguration.Thetypicalvaluesarenottestedandarenotensuredonshipped productionmaterial. 12 AC Electrical Characteristics Unlessotherwisespecified,alllimitsarespecifiedforT =25°C,V =V =12V,V =0V,R =50ΩtoV -2V,V = J CCI CCO EE L CCO CM 300mV,R =none.Boldfacelimitsapplyattemperatureextremes. HYS Min Typ Max Symbol Parameter Conditions (1) (2) (1) Units TR MaximumToggleRate Overdrive=±50mV;C =2pF 4 Gb/s L @50%ofOutputSwing MinimumPulseWidth Overdrive=±50mV;C =2pF 255 ps L @50%ofOutputSwing (1) Alllimitsarespecifiedbytestingorstatisticalanalysis. (2) Typicalvaluesrepresentthemostlikelyparametricnormasdeterminedatthetimeofcharacterization.Actualtypicalvaluesmayvary overtimeandwillalsodependontheapplicationandconfiguration.Thetypicalvaluesarenottestedandarenotensuredonshipped productionmaterial. Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 3 ProductFolderLinks:LMH7322

LMH7322 SNOSAU8I–MARCH2007–REVISEDMARCH2013 www.ti.com 12 AC Electrical Characteristics (continued) Unlessotherwisespecified,alllimitsarespecifiedforT =25°C,V =V =12V,V =0V,R =50ΩtoV -2V,V = J CCI CCO EE L CCO CM 300mV,R =none.Boldfacelimitsapplyattemperatureextremes. HYS Min Typ Max Symbol Parameter Conditions (1) (2) (1) Units t RMSRandomJitter Overdrive=±100mV;C =2pF 702 fs jitter-RMS L CenterFrequency=140MHz Bandwidth=10Hz–20MHz t PropagationDelay. Overdrive20mV 818 PDH (seeFigure19applicationnote) ps Overdrive50mV 723 InputSR=Constant Overdrive100mV 708 V Startvalue=V −100mV ps IN REF Overdrive1V 703 t InputOverdriveDispersion t @Overdrive20mV↔100mV 110 OD-disp PDH ps t @Overdrive100mV↔1V 5 PDH t InputSlewRateDispersion 0.1V/nsto1V/ns;Overdrive=100 48 ps SR-disp mV t InputCommonModeDispersion SR=1V/ns;Overdrive=100mV; 43 ps CM-disp 0V≤V ≤V -1.5V CM CCI Δt QtoQTimeSkew|t –t | Overdrive=100mV;C =2pF 24 ps PDLH PDH PDL L Δt QtoQTimeSkew|t –t | Overdrive=100mV;C =2pF 45 ps PDHL PDL PDH L t OutputRiseTime(20%–80%) Overdrive=100mV;C =2pF 155 ps r L t OutputFallTime(20%–80%) Overdrive=100mV;C =2pF 155 ps f L t LatchSetupTime 77 ps sLE t LatchHoldTime 33 ps hLE t LatchtoOutputDelayTime 944 ps PD_LE 5V DC Electrical Characteristics Unlessotherwisespecified,alllimitsarespecifiedforT =25°C,V =V =5V,V =0V,R =50ΩtoV -2V,V =300 J CCI CCO EE L CCO CM mV,R =1kΩ.Boldfacelimitsapplyattemperatureextremes. HYS Min Typ Max Symbol Parameter Conditions (1) (2) (1) Units INPUTCHARACTERISTICS I InputBiasCurrent V Differential=0V;R =8kΩ −5 −2.6 µA B IN HYS BiasedatV CM I InputOffsetCurrent V Differential=0V −250 40 +250 nA OS IN TCI InputOffsetCurrentTC V Differential=0V 0.3 nA/°C OS IN V InputOffsetVoltage −8 −2 +8 mV OS TCV InputOffsetVoltageTC 12 µV/°C OS V InputVoltageRange forCMRR≥50dB V −0.2 V −1.5 V RI EE CCI V InputDifferentialVoltageRange −1 +1 V RID CMRR CommonModeRejectionRatio 0V≤V ≤V −0.2 80 dB CM CC1 PSRR PowerSupplyRejectionRatio 80 dB A ActiveGain 53 dB V Hyst Hysteresis VHYS=V(HYS+)-V(HYS-),RHYS=0Ω 25 50 75 mV LATCHENABLECHARACTERISTICS I LatchEnableBiasCurrent BiasedatRSPECLLevel 3 10 µA B-LE V LatchEnableOffsetVoltage BiasedatRSPECLLevel +5 mV OS-LE V LatchEnableVoltageRange forCMRR≥50dB V +1.4 V -0.8 V RI-LE EE CCO (1) Alllimitsarespecifiedbytestingorstatisticalanalysis. (2) Typicalvaluesrepresentthemostlikelyparametricnormasdeterminedatthetimeofcharacterization.Actualtypicalvaluesmayvary overtimeandwillalsodependontheapplicationandconfiguration.Thetypicalvaluesarenottestedandarenotensuredonshipped productionmaterial. 4 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LMH7322

LMH7322 www.ti.com SNOSAU8I–MARCH2007–REVISEDMARCH2013 5V DC Electrical Characteristics (continued) Unlessotherwisespecified,alllimitsarespecifiedforT =25°C,V =V =5V,V =0V,R =50ΩtoV -2V,V =300 J CCI CCO EE L CCO CM mV,R =1kΩ.Boldfacelimitsapplyattemperatureextremes. HYS Min Typ Max Symbol Parameter Conditions (1) (2) (1) Units V LatchEnableDifferentialVoltage ±0.4 V RID-LE Range OUTPUTCHARACTERISTICS V OutputVoltageHigh V −1.1 mV OH CCO V V OutputVoltageLow V −1.5 mV OL CCO V V OutputVoltageDifferential 355 mV OD POWERSUPPLIES I V SupplyCurrent/Channel 6.3 10 mA VCCI CCI 12 I V SupplyCurrent/Channel LoadCurrentExcluded 15.8 20 mA VCCO CCO 25 5V AC Electrical Characteristics Unlessotherwisespecified,alllimitsarespecifiedforT =25°C,V =V =5V,V =0V,R =50ΩtoV -2V,V =300 J CCI CCO EE L CCO CM mV,R =none.Boldfacelimitsapplyattemperatureextremes. HYS Min Typ Max Symbol Parameter Conditions (1) (2) (1) Units TR MaximumToggleRate Overdrive=±50mV;C =2pF 3.9 Gb/s L @50%ofOutputSwing MinimumPulseWidth Overdrive=±50mV;C =2pF 260 ps L @50%ofOutputSwing t RMSRandomJitter Overdrive=±100mV;C =2pF 572 fs jitter_RMS L CenterFrequency=140MHz Bandwidth=10Hz–20MHz t PropagationDelay. Overdrive20mV 783 PDLH (seeFigure19applicationnote) ps Overdrive50mV 718 InputSR=Constant Overdrive100mV 708 V startvalue=V –100mV ps IN REF Overdrive1V 708 t InputOverdriveDispersion t @Overdrive20mV↔100mV 75 OD-disp PDH ps t @Overdrive100mV↔1V 5 PDH t InputSlewRateDispersion 0.1V/nsto1V/ns;Overdrive=100mV 50 ps SR-disp t InputCommonModeDispersion SR=1V/ns;Overdrive=100mV; 24 ps CM-disp 0V≤V ≤V -1.5V CM CCI Δt QtoQTimeSkew|t –t | Overdrive=100mV;C =2pF 29 ps PDLH PDH PDL L Δt QtoQTimeSkew|t –t | Overdrive=100mV;C =2pF 47 ps PDHL PDL PDH L t OutputRiseTime(20%–80%) Overdrive=100mV;C =2pF 160 ps r L t OutputFallTime(20%–80%) Overdrive=100mV;C =2pF 160 ps f L t LatchSetupTime 95 ps sLE t LatchHoldTime 29 ps hLE t LatchtoOutputDelayTime 893 ps PD_LE (1) Alllimitsarespecifiedbytestingorstatisticalanalysis. (2) Typicalvaluesrepresentthemostlikelyparametricnormasdeterminedatthetimeofcharacterization.Actualtypicalvaluesmayvary overtimeandwillalsodependontheapplicationandconfiguration.Thetypicalvaluesarenottestedandarenotensuredonshipped productionmaterial. Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 5 ProductFolderLinks:LMH7322

LMH7322 SNOSAU8I–MARCH2007–REVISEDMARCH2013 www.ti.com 2.7V DC Electrical Characteristics Unlessotherwisespecified,alllimitsarespecifiedforT =25°C,V =V =2.7V,V =0V,R =50ΩtoV -2V,V = J CCI CCO EE L CCO CM 300mV,R =1kΩ.Boldfacelimitsapplyattemperatureextremes. HYS Min Typ Max Symbol Parameter Conditions (1) (2) (1) Units INPUTCHARACTERISTICS I InputBiasCurrent V Differential=0V;R =8kΩBiasedatV −5 −2.5 µA B IN HYS CM I InputOffsetCurrent V Differential=0V −250 40 +250 nA OS IN TCI InputOffsetCurrentTC V Differential=0V 0.2 nA/°C OS IN V InputOffsetVoltage −8 −2 +8 mV OS TCV InputOffsetVoltageTC 12 µV/°C OS V InputVoltageRange forCMRR≥50dB V −0 V − V RI EE CCI .2 1.5 V InputDifferentialVoltageRange −1 +1 V RID CMRR CommonModeRejectionRatio 0V≤V ≤V −2 80 dB CM CC1 PSRR PowerSupplyRejectionRatio 80 dB A ActiveGain 53 dB V Hyst Hysteresis VHYS=V(HYS+)-V(HYS-),RHYS=0Ω 25 50 75 mV LATCHENABLECHARACTERISTICS I LatchEnableBiasCurrent BiasedatRSPECLLevel 3 10 µA B-LE V LatchEnableOffsetVoltage BiasedatRSPECLLevel −5 mV OS-LE V LatchEnableVoltageRange forCMRR≥50dB V +1 V - V RI-LE EE CCO .4 0.8 V LatchEnableDifferential ±0.4 V RID-LE VoltageRange OUTPUTCHARACTERISTICS V OutputVoltageHigh V −1.1 mV OH CCO V V OutputVoltageLow V −1.5 mV OL CCO V V OutputVoltageDifferential 350 mV OD POWERSUPPLIES I V SupplyCurrent/Channel 6.2 10 mA VCCI CCI 12 I V SupplyCurrent/Channel LoadCurrentExcluded 15.5 20 mA VCCO CCO 25 (1) Alllimitsarespecifiedbytestingorstatisticalanalysis. (2) Typicalvaluesrepresentthemostlikelyparametricnormasdeterminedatthetimeofcharacterization.Actualtypicalvaluesmayvary overtimeandwillalsodependontheapplicationandconfiguration.Thetypicalvaluesarenottestedandarenotensuredonshipped productionmaterial. 2.7V AC Electrical Characteristics Unlessotherwisespecified,alllimitsarespecifiedforT =25°C,V =V =2.7V,V =0V,R =50ΩtoV -2V,V = J CCI CCO EE L CCO CM 300mV,R =none.Boldfacelimitsapplyattemperatureextremes. HYS Min Typ Max Symbol Parameter Conditions (1) (2) (1) Units TR MaximumToggleRate Overdrive=±50mV;C =2pF 3.8 Gb/s L @50%ofOutputSwing MinimumPulseWidth Overdrive=±50mV;C =2pF 265 ps L @50%ofOutputSwing (1) Alllimitsarespecifiedbytestingorstatisticalanalysis. (2) Typicalvaluesrepresentthemostlikelyparametricnormasdeterminedatthetimeofcharacterization.Actualtypicalvaluesmayvary overtimeandwillalsodependontheapplicationandconfiguration.Thetypicalvaluesarenottestedandarenotensuredonshipped productionmaterial. 6 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LMH7322

LMH7322 www.ti.com SNOSAU8I–MARCH2007–REVISEDMARCH2013 2.7V AC Electrical Characteristics (continued) Unlessotherwisespecified,alllimitsarespecifiedforT =25°C,V =V =2.7V,V =0V,R =50ΩtoV -2V,V = J CCI CCO EE L CCO CM 300mV,R =none.Boldfacelimitsapplyattemperatureextremes. HYS Min Typ Max Symbol Parameter Conditions (1) (2) (1) Units t RMSRandomJitter Overdrive=±50mV;C =2pF 551 fs jitter_RMS L CenterFrequency=140MHz Bandwidth=10Hz–20MHz t PropagationDelay. Overdrive20mV 783 PDH (seeFigure19applicationnote) ps Overdrive50mV 728 InputSR=Constant Overdrive100mV 713 V startvalue=V –100mV ps IN REF Overdrive1V 718 t InputOverdriveDispersion t @Overdrive20mV↔100mV 70 OD-disp PDH ps t @Overdrive100mV↔1V 5 PDH t InputSlewRateDispersion 0.1V/nsto1V/ns;Overdrive=100mV 54 ps SR-disp t InputCommonModeDispersion SR=1V/ns;Overdrive=100mV; 12 ps CM-disp 0V≤V ≤V -1.5V CM CCI Δt QtoQTimeSkew|t –t | Overdrive=100mV;C =2pF 35 ps PDLH PDH PDL L Δt QtoQTimeSkew|t –t | Overdrive=100mV;C =2pF 53 ps PDHL PDL PDH L t OutputRiseTime(20%–80%) Overdrive=100mV;C =2pF 165 ps r L t OutputFallTime(20%–80%) Overdrive=100mV;C =2pF 165 ps f L t LatchSetupTime 102 ps sLE t LatchHoldTime 37 ps hLE t LatchtoOutputDelayTime 906 ps PD_LE Connection Diagrams CCI CCOCCO OA OB V VV C C A A C C B B Q Q V V Q Q Q 24 23 22 21 20 19 IN+ 1/2 IN- LMH7322 VCCOA 1 18 VCCOB RHYS Q LEA 2 17 LEB EEFE LLREVE LEA 3 LMH7322 16 LEB H R 24-pin WQFN VEEA 4 15 VEEB Figure2. Schematic VCCIA 5 14 VCCIB RHYSA 6 13 RHYSB 7 8 9 10 11 12 INA- INA+ REFA REFB INB+ INB- H H R R Figure3. Footprint Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 7 ProductFolderLinks:LMH7322

LMH7322 SNOSAU8I–MARCH2007–REVISEDMARCH2013 www.ti.com Typical Performance Characteristics AtT =25°C;V =+5V;V =+3.3V;V =−5V;unlessotherwisespecified. J CCI CCO EE PropagationDelayvs.SupplyVoltage PropagationDelayvs.Temperature 1100 1100 1050 1050 )sp( YALED NOITAG 1889900050500000 18255°C°C )sp( YALED NOITAG 1889900505000000 VS = 2V.7SV = 12V APO 750 25°C APO 750 RP 700 RP 700 650 -40°C 650 VS = 5V 600 600 2 3 4 5 6 7 8 9 10 11 12 -40 -20 0 20 40 60 80 100 120 SUPPLY VOLTAGE (V) TEMPERATURE (°C) Figure4. Figure. PropagationDelayvs.SupplyVoltage PropagationDelayvs.OverdriveVoltage 1000 900 VCM = 0.3V VCM = 0.3V 950 VIN_DIFF = VCM – 100 mV 850 VIN_DIFF = VCM – 100 mV )sp( Y 900 to VCM + VOVERDRIVE )sp( Y to VCM + VOVERDIVE ALED NO 880500 VOD = 10 mV ALED NO 785000 VS = 2.7V VS = 5V ITAG 750 VOD = 20 mV VOD = 50 mV ITAG A A 700 P P O 700 O RP VOD = 200 mV VOD = 50 mV RP 650 VS = 12V 650 500 mV 1V 600 600 2 3 4 5 6 7 8 9 10 11 12 0 200 400 600 800 1000 SUPPLY VOLTAGE (V) OVERDRIVE VOLTAGE (mV) Figure5. Figure6. PropagationDelayvs.CommonModeVoltage PropagationDelayvs.SlewRate 800 900 780 VS = 2.7V 850 )s 760 )s p( Y 740 VS = 5V p( Y VS = 2.7V A A 800 L L ED 720 ED VS = 12V NO 700 VS = 12V NO 750 IT IT A 680 A G G A A 700 P 660 P ORP 640 ORP 650 VS = 5V OVERDRIVE 100 mV 620 VOVERDRIVE = 100 mV VCM = 300 mV 600 600 -1 0 1 2 3 4 5 6 7 8 9 10 1112 100200 300 400 500 600 700 800 9001000 COMMON MODE VOLTAGE (V) SLEW RATE (V/Ps) Figure7. Figure8. 8 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LMH7322

LMH7322 www.ti.com SNOSAU8I–MARCH2007–REVISEDMARCH2013 Typical Performance Characteristics (continued) AtT =25°C;V =+5V;V =+3.3V;V =−5V;unlessotherwisespecified. J CCI CCO EE T Dispersionvs.SupplyVoltage SlewRateDispersionvs.VoltageSupply PD 110 75 100 OVERDRIVE 100 mV 90 VOD = 20 mV - 100 mV )sp 6750 VSCRM = =0 .310 –0 1m VV/Ps 80 ( N )sp 70 OIS 60 ( NOIS 5600 VVCINM_ D=I F0F. 3=V VCM - 100 mV REPS 5550 REP 40 to VCM + VOVERDIVE ID E 45 SID 30 TAR 40 20 VOD = 50 mV - 1V W 10 EL 35 S 0 30 VOD = 100 mV - 1V -10 25 2 3 4 5 6 7 8 9 10 11 12 2 3 4 5 6 7 8 9 10 11 12 SUPPLY VOLTAGE (V) SUPPLY VOLTAGE (V) Figure9. Figure10. CommonModeDispersionvs.SupplyVoltage BiasCurrentvs.Temperature 80 -1 )sp( NO 70 V0 O<V VECRMD R<I VVEC =C 1I 0–0 1 m.5V -1.5 2.7V IS 60 -2 R )A E P PS 50 ( T -2.5 ID E 40 NER -3 D R O U 12V M NO 30 C SA -3.5 5V MM 20 IB -4 VCM = 300 mV O C 10 -4.5 VIN_DIFF = 0 mV IBIAS = (IIN+ + IIN-)/2 0 -5 2 4 6 8 10 12 -40 -20 0 20 40 60 80 100 120 SUPPLY VOLTAGE (V) TEMPERATURE (°C) Figure11. Figure12. InputCurrentvs.DifferentialInputVoltage MaximumToggleRate 10 400 VCM = 2.5V 300 )Aµ( T 5 IIN- VVVSIINN =+- = =5 V31..55 ttoo 13..55VV IIN+ )Vm( TUP 120000 N 0 T ER UO 0 R L UC T -5 AITN -100 U E -200 PNI -10 IIN+ IIN- REFFID -300 OMUATXP TURT -400 OUTPUT 140 MHz -15 -500 -2.0 -1.5 -1.0 -0.5 0.0 0.5 1.0 1.5 2.0 0 1 2 3 4 5 6 7 DIFFERENTIAL INPUT VOLTAGE (V) TIME (ns) Figure13. Figure14. Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 9 ProductFolderLinks:LMH7322

LMH7322 SNOSAU8I–MARCH2007–REVISEDMARCH2013 www.ti.com Typical Performance Characteristics (continued) AtT =25°C;V =+5V;V =+3.3V;V =−5V;unlessotherwisespecified. J CCI CCO EE OutputVoltagevs.InputVoltage HysteresisVoltagevs.HysteresisResistor 0.4 70 )V( EG 0.3 VTECMM P= =3 0205 °mCV )V 60 VTECMM P= =3 0205 °mCV ATLO 0.2 VS = 5V m( EG 50 VVSH Y=S 2 =.7 VV(,H 5YVS,+1)2 -V V(HYS-) V T 0.1 = VHYS+ AT UP = VHYS- LO 40 T 0 V UO LAITNE --00..21 RHYS = 32 k: SISERETS 2300 REF -0.3 RHYS = 0 YH 10 F ID -0.4 0 -0.05 -0.03 -0.01 0 0.01 0.03 0.05 0 5 10 15 20 25 30 35 DIFFERENTIAL INPUT VOLTAGE (V) HYSTERESIS RESISTOR (k:) Figure15. Figure16. 10 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LMH7322

LMH7322 www.ti.com SNOSAU8I–MARCH2007–REVISEDMARCH2013 APPLICATION INFORMATION Introduction The LMH7322 is a high speed comparator with RS(P)ECL (Reduced Swing Positive Emitter Coupled Logic) outputs, and is compatible with LVDS (Low Voltage Differential Signaling) if V is set to 2.5V. The use of CCO complementary outputs gives a high level of suppression for common mode noise. The very fast rise and fall times of the LMH7322 enable data transmission rates up to several Gigabits per second (Gbps). The LMH7322 inputshaveacommonmodevoltagerangethatextends200mVbelowthenegativesupplyvoltagethusallowing ground sensing in case of single supply. The rise and fall times of the LMH7322 are about 160 ps, while the propagation delay time is about 700 ps. The LMH7322 can operate over the full supply voltage range of 2.7V to 12V, while using single or dual supply voltages. This is a very useful feature because it provides a flexible way to interface between several high speed logic families. Several setups are shown in the application information section “Interface Between Logic Families”. The outputs are referenced to the positive V supply rail. The CCO supply current is 23 mA at 5V (per comparator, load current excluded.) The LMH7322 is available in a 24-Pin WQFNpackage. Thefollowingtopicswillbediscussedinthisapplicationsection. • Inputandoutputtopology • Specificationdefinitions • Propagationdelayanddispersion • Hysteresisandoscillations • Output • Applyingtransmissionlines • PCBlayout Input & Output Topology All input and output pins are protected against excessive voltages by ESD diodes. These diodes are conducting from the negative supply to the positive supply. As can be seen in Figure 17, both inputs are connected to these diodes. Further protection of the inputs is provided by the two resistors of 250Ω, in conjunction with the string of anti-parallel diodes connected between both bases of the input stage. This combination of resistors and diodes reduces excessive input voltages over the input stage, but is low enough to maintain switching speed to the outputsignal. ProtectionagainstexcessivesupplyvoltagesisprovidedbyapowerclampbetweenV andGND. CC When using this part be aware of situations in which the differential input voltage level is such that these diodes are conducting. In this case the input current is raised far above the normal value stated in the datasheet tables becauseinputcurrentisflowingthroughthebypassdiodestringbetweenbothinputs. VCCI VCCI VCCI VCCI VCCO 250: 250: IN+ IN- VEE VEE Power Clamp 2X VEE VEE PART A PART B Figure17. EquivalentInputCircuitry Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 11 ProductFolderLinks:LMH7322

LMH7322 SNOSAU8I–MARCH2007–REVISEDMARCH2013 www.ti.com The output stage of the LMH7322 is built using two emitter followers, which are referenced to the V (see CCO Figure 18.) Each of the output transistors is active when a current is flowing through any external output resistor connectedtoalowersupplyrail.TheoutputstructureisactuallythesameasforallotherECLdevices.Activating theoutputsisdonebyconnectingtheemitterstoaterminationvoltagewhichlies2VbelowtheV .Inthiscase CCO a termination resistor of 50Ω can be used and a transmission line of 50Ω can be driven. Another method is to connect the emitters through a resistor to the most negative supply by calculating the right value for the emitter current in accordance with the datasheet tables. Both methods are useful, and it is up to the customer which method is used. Using 50Ω to the termination voltage means the introduction of an extra supply in the system, while using resistors to a negative supply means the use of resistors that are much larger than 50Ω and a more constant output current per stage. The following calculation will show the difference. In this example a V of CCO 2.5V is used and a V of V -2V and a negative supply of −5V. When connecting the outputs through a 50Ω T CCO resistor to the V , the output currents for the high and the low state are respectively 18 mA and 10 mA. T Connecting the outputs through a 400Ω resistor to the −5V supply the output currents for the high and the low state are respectively 16 mA and 15 mA. Higher resistor values to the V will further reduce power consumption EE but will cause a slower transition of the output stage. In the case that this will not harm your application it is a usefulmethodtoreducepowerconsumption. VCCO Output Q r Output Q VEE Figure18. EquivalentOutputCircuitry The output voltages for ‘1’ and ‘0’ have a difference of approximately 400 mV and are respectively 1.1V (for the ‘1’) and 1.5V (for the ‘0’) below the V . This swing of 400 mV is enough to drive any LVDS input but can also CCO be used to drive any ECL or PECL input, when the right supply voltage is chosen, especially the right level for theV . CCO Table1.Definitions Symbol Text Description I InputBiasCurrent Currentflowinginoroutoftheinputpins,whenbotharebiasedattheV B CM voltageasspecifiedinthetables. I InputOffsetCurrent Differencebetweentheinputbiascurrentoftheinvertingandnon-inverting OS inputs. TCI AverageInputOffsetCurrentDrift TemperaturecoefficientofI . OS OS V InputOffsetVoltage VoltagedifferenceneededbetweenIN+andIN-tomaketheoutputschange OS state,averagedforHtoLandLtoHtransitions. TCV AverageInputOffsetVoltageDrift TemperaturecoefficientofV . OS OS V InputVoltageRange Voltagewhichcanbeappliedtotheinputpinmaintainingnormaloperation. RI V InputDifferentialVoltageRange Differentialvoltagebetweenpositiveandnegativeinputatwhichtheinputclamp RID isnotworking.Thedifferencecanbeashighasthesupplyvoltagebutexcessive inputcurrentsareflowingthroughtheclampdiodesandprotectionresistors. CMRR CommonModeRejectionRatio Ratioofinputoffsetvoltagechangeandinputcommonmodevoltagechange. PSRR PowerSupplyRejectionRatio RatioofinputoffsetvoltagechangeandsupplyvoltagechangefromV toV S-MIN S- . MAX A ActiveGain Overallgainofthecircuit. V 12 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LMH7322

LMH7322 www.ti.com SNOSAU8I–MARCH2007–REVISEDMARCH2013 Table1.Definitions(continued) Symbol Text Description Hyst Hysteresis Differencebetweentheswitchingpoint‘0’to‘1’andviceversa. I LatchEnableBiasCurrent Currentflowinginoroutoftheinputpins,whenbotharebiasedatnormalPECL B-LE levels. I LatchEnableOffsetCurrent DifferencebetweentheinputbiascurrentoftheLEandLEpin. OS-LE TCI TempCoefficientLatchEnableOffset TemperaturecoefficientofI . OS-LE OS-LE Current V LatchEnableOffsetVoltage VoltagedifferenceneededbetweenLEandLEtoplacethepartinthelatchedor OS-LE thetransparentstate. TCV TempCoefficientLatchEnableOffset TemperaturecoefficientofV . OS-LE OS-LE Voltage V LatchEnableVoltageRange VoltagewhichcanbeappliedtotheLEinputpinswithoutdamagingthedevice. RI-LE V LatchEnableDifferentialVoltageRange DifferentialVoltagebetweenLEandLEatwhichtheclampisn’tworking.The RID-LE differencecanbeashighasthesupplyvoltagebutexcessiveinputcurrentsare flowingthroughtheclampdiodesandprotectionresistors. V OutputVoltageHigh Highstatesingleendedoutputvoltage(QorQ)(seeFigure34). OH V OutputVoltageLow Lowstatesingleendedoutputvoltage(QorQ)(seeFigure34). OL V averageofV andV (V +V )/2. OD ODH ODL ODH ODL I SupplyCurrentInputStage Supplycurrentintotheinputstage. VCCI I SupplyCurrentOutputStage Supplycurrentintotheoutputstagewhilecurrentthroughtheloadresistorsis VCCO excluded. I SupplyCurrentV pin Currentflowingtothenegativesupplypin. VEE EE TR MaximumToggleRate MaximumfrequencyatwhichtheoutputscantogglebetweenthenominalV OH andV . OL PW PulseWidth Timefrom50%oftherisingedgeofasignalto50%ofthefallingedge. t respt PropagationDelay DelaytimebetweenthemomenttheinputsignalcrossestheswitchinglevelLto PDH PDL Handthemomenttheoutputsignalcrosses50%oftherisingedgeofQoutput (t ),ordelaytimebetweenthemomenttheinputsignalcrossestheswitching PDH levelHtoLandthemomenttheoutputsignalcrosses50%ofthefallingedgeof Qoutput(t ). PDL t respt DelaytimebetweenthemomenttheinputsignalcrossestheswitchinglevelLto PDL PDH Handthemomenttheoutputsignalcrosses50%ofthefallingedgeofQoutput (t ),ordelaytimebetweenthemomenttheinputsignalcrossestheswitching PDL levelHtoLandthemomenttheoutputsignalcrosses50%oftherisingedgeof Qoutput(t ). PDH t Averageoft andt . PDLH PDH PDL t Averageoft andt . PDHL PDL PDH t Averageoft andt . PD PDLH PDHL t resp DelaytimebetweenthemomenttheinputsignalcrossestheswitchinglevelLto PDHd t Handthezerocrossingoftherisingedgeofthedifferentialoutputsignal(t ), PDLd PDHd ordelaytimebetweenthemomenttheinputsignalcrossestheswitchinglevelH toLandthezerocrossingofthefallingedgeofthedifferentialoutputsignal (t ). PDLd t InputOverdriveDispersion Changeint fordifferentoverdrivevoltagesattheinputpins. OD-disp PD t InputSlewRateDispersion Changeint fordifferentslewratesattheinputpins. SR-disp PD t InputCommonModeDispersion Changeint fordifferentcommonmodevoltagesattheinputpins. CM-disp PD Δt resp QtoQTimeSkew Timeskewbetween50%levelsoftherisingedgeofQoutputandthefalling PDLH Δt edgeofoutput(Δt ),ortimeskewbetween50%levelsoffallingedgeofQ PDHL PDLH outputandrisingedgeofQoutput(Δt ). PDHL Δt AverageQtoQTimeSkew Averageoft andt forLtoHandHtoLtransients. PD PDLH PDHL ΔtP AverageDiff.TimeSkew Averageoft andt forLtoHandHtoLtransients. Dd PDHd PDLd t /t OutputRiseTime(20%-80%) Timeneededforthe(singleendedordifferential)outputvoltagetochangefrom r rd 20%ofitsnominalvalueto80%. t /t OutputFallTime(20%-80%) Timeneededforthe(singleendedordifferential)outputvoltagetochangefrom f fd 80%ofitsnominalvalueto20%. tLE LatchSetupTime Timetheinputsignalhastobestablebeforeenablingthelatchfunctionality. s Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 13 ProductFolderLinks:LMH7322

LMH7322 SNOSAU8I–MARCH2007–REVISEDMARCH2013 www.ti.com Table1.Definitions(continued) Symbol Text Description t LE LatchHoldTime Timetheinputsignalhastoremainstableafterenablingthelatchfunctionality. h t LatchtoOutputDelayTime DelaytimebetweenthemomentthelatchinputcrossestheswitchinglevelHtoL PD-LE andthemomentthedifferentialoutputsignalcrossesthe50%level. Note:inputsignalisoppositetooutputsignalwhenlatchbecomesenabled. PW InDpiuffte Sreignntiaall Voverdrive 0 tPDLH = (tPDH + tPDL)/ 2 ’tPDLH ’tPDHL tf tPDHL = (tPDL + tPDH)/ 2 tr tPD = (tPDLH + tPDHL)/ 2 tPDH Output Q tPDL 1800%% oorr 2900%% VO ’tPDLH = | tPDH - tPDL | ’tPDHL = | tPDL - tPDH | Output Q tPDH VO ’tPD = (cid:11)’tPDLH + ’tPDHL)/ 2 tPDL ’tPDQ = | tPDH - tPDL | trd ’tPDQ = | tPDL - tPDH | tPDHd Differential 80% or 90% Output Signal 0 tPDd = (tPDHd + tPDLd)/ 2 tPDLd 10% or 20% ’tPDd = | tPDHd - tPDLd | tfd Figure19. TimingDefinitions th LE Diff input LE Q output tPD LE ts LE tPDHL Figure20. LETiming Table2.PINDESCRIPTIONS Pin Name Description Comment 1. VCCOA PositiveSupplyOutputStage partA Thesupplypinfortheoutputstageisindependentofthesupplypinfor theinputpin.Thisallowsoutputlevelsofdifferentlogicfamilies. 2. LEA LatchEnableInput partA Logic‘1’setsthepartonhold.LogiclevelsareRSPECL(Reduced SwingPECL)compatible. 3. LEA LatchEnableInputNot partA Logic‘0’setsthepartonhold.LogiclevelsareRSPECLcompatible. 4. VEEA NegativeSupply partA ThesupplypinforthenegativesupplyisconnectedtotheVEEBviaa stringoftwoanti-paralleldiodes(seeFigure17) 5. VCCIA PositiveSupplyforInputStage partA Thesupplypinfortheinputstageisindependentofthesupplyforthe outputstage. 6. RHYSA HysteresisResistor partA Thehysteresisvoltageisdeterminedbyconnectingaresistorfromthis pintoRHREFA. 7. INA- NegativeInput partA Inputforanalogvoltagesbetween200mVbelowVEEAand2Vbelow VCCIA. 14 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LMH7322

LMH7322 www.ti.com SNOSAU8I–MARCH2007–REVISEDMARCH2013 Table2.PINDESCRIPTIONS(continued) Pin Name Description Comment 8. INA+ PositiveInput partA Inputforanalogvoltagesbetween200mVbelowVEEAand2Vbelow VCCIA. 9. RHREFA ReferenceVoltageHysteresis partA Thehysteresisvoltageisdeterminedbyconnectingaresistorfromthis Resistor pintoRHYSA. 10. RHREFB ReferenceVoltageHysteresis partB Thehysteresisvoltageisdeterminedbyconnectingaresistorfromthis Resistor pintoRHYSB. 11. INB+ PositiveInput partB Inputforanalogvoltagesbetween200mVbelowVEEBand2Vbelow VCCIB. 12. INB− NegativeInput partB Inputforanalogvoltagesbetween200mVbelowVEEBand2Vbelow VCCIB. 13. RHYSB HysteresisResistor partB Thehysteresisvoltageisdeterminedbyconnectingaresistorfromthis pintoRHREFB. 14. VCCIB PositiveSupplyforInputStage partB Thesupplypinfortheinputstageisindependentofthesupplyforthe outputstage. 15. VEEB NegativeSupply partB ThesupplypinforthenegativesupplyisconnectedtotheVEEAviaa stringoftwoanti-paralleldiodes(seeFigure17). 16. LEB LatchEnableInputNot partB Logic‘0’setsthepartonhold.LogiclevelsareRSPECLcompatible. 17. LEB LatchEnableInputLogic partB ‘1’setsthepartonhold.LogiclevelsareRSPECLcompatible. 18. VCCOB PositiveSupplyforOutput partB Thesupplypinfortheoutputstageisindependentofthesupplypinfor Stage theinputpin.Thisallowsoutputlevelsofdifferentlogicfamilies. 19. QB InvertedOutput partB OutputlevelsaredeterminedbythechoiceofVCCOB. 20. QB Output partB OutputlevelsaredeterminedbythechoiceofVCCOB. 21. VCCOB PositiveSupplyforOutput partB SeeotherVCCOB Stage 22. VCCOA PositiveSupplyforOutput partA SeeotherVCCOA. Stage 23. QA Output partA OutputlevelsaredeterminedbythechoiceofVCCOA. 24. QA InvertedOutput partA OutputlevelsaredeterminedbythechoiceofVCCOA. 25. DAP Centralpadatthebottomofthe A&B ThispadisconnectedtotheVEEpinsanditspurposeistotransfer package heatoutsidethepart. Tips & Tricks Using the LMH7322 InthissectionseveralaspectsarediscussedconcerningspecialapplicationsusingtheLMH7322. This concerns the LE function, the connection of the DAP in conjunction to the V pins and the use of this part EE asaninterfacebetweenseverallogicfamilies. The Latch Enable Pins The latch function is intended to stop the device from comparing the signals on both input pins. If the latch function is enabled, the output is frozen and the logic information on the output pins, present at that moment, is held until the latch function is disabled. The timing of this process can be seen in Figure 20. The input levels for the latch pins should comply with RSPECL, but can also be driven with PECL type of signals if the minimum supply (V –V ) is larger or equal to 3.3V. The minimum differential latch input voltage should be 100 mV. CCO EE Another possibility to set the LE function in a steady state is to connect the pins via a resistor to the power supply. If the LE pin is connected to V via a resistor of 10 kΩ and the LE-not pin is connected via 10 kΩ to the EE V pin the part is continuously on. Since the latch input stage is referenced to V , the resistors to set the LE CCO CCO function should be connected to this voltage. This is very important when working with different voltages for V CCI andV .Ifconnectedtothewrongsupply,thelatchfunctionwillnotwork. CCO Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 15 ProductFolderLinks:LMH7322

LMH7322 SNOSAU8I–MARCH2007–REVISEDMARCH2013 www.ti.com The DAP and the VEE Pins To ensure that both VEE pins are operating at the same voltage, both pins are connected to the DAP, and thus toeachother,throughbondwires.Asaconsequence,theDAPisatthesamepotentialastheVEEpinsandcan be used to connect the device to the minimum supply voltage. A more solid VEE connection is obtained if the two VEE pins and the DAP are all connected to the minimum supply on the PCB, rather than an indirect connectionthroughtheinternalbondwires. To protect the device during handling and production two anti-parallel connected diodes are connected between bothVEEpins.UndernormaloperatingconditionsthesediodesareshortedviatheDAP. The DAP (Die Attach Paddle) functions as a heat sink which means that heat can be transferred using vias belowthispadtothecopperplaneVEEisconnectedto. V D V E A E E P E Figure21. DAPConnection Interface Between Logic Families As can be seen in the typical schematics (see Figure 1) the LMH7322 can be used to interface between different logic families. The feature that facilitates this property is the fact that the input stage and the output stage use different positive power supply pins which can be used at different supply voltages. The negative supply pins are connected together for both parts. Using the power pins at different supply voltages makes it possible to create several translations for logic families. It is possible to translate from logic at negative voltage levels such as ECL to logic at positive levels such as RSPECL and LVDS and vice versa. The drawings in the next paragraphs do not show the output resistors except the first one. This is intentionally done for simplicity. All outputs need an output resistor to a termination voltage or to the negative rail as can be seen on the front page in the Typical ApplicationofanECLtoRSPECLconverter. InterfacefromECLtoRSPECL The supply pin V can be connected to ground because the input levels are negative and the V pin must CCI CCO operate at 5V to create the RSPECL levels (see Figure 22). When working with ECL, the negative supply pin (V )canbeconnectedtothe−5.2VECLsupplyvoltage. EE 5V + O O VCCI VCC VCC ECL driver Ctraonuspmleids sion line Line TerminationIN+ Q IN- 1/2 ORUS-TPPEUCTL LMH 7322 VOH = 3.9V VT = VCCO-2V VOL = 3.5V or RHYS Q VT = VEE RT RT LL R V VT EE H E R E E 10k F -5.2V LE levels referred to VCCO + Figure22. ECLTORSPECL 16 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LMH7322

LMH7322 www.ti.com SNOSAU8I–MARCH2007–REVISEDMARCH2013 InterfacefromPECLto(RS)ECL The conversion from PECL to RS-ECL is possible when connecting the V pin to +5V, which allows the input CCI stage to handle these positive levels. The V pin must be connected to the ground level in order to create the CCO RSECL levels. The high level of the output of the LMH7322 is normally 1.1V below the V supply voltage, and CCO the low level is 1.5V below this supply. The output levels are now −1100 mV for the logic ‘1’ and −1500 mV for thelogic‘0’(seeFigure23).InthesamewaytheV canbeconnectedtotheECLsupplyvoltageof−5.2V. EE 5V + O O CI C C C C C V V V PECL driver Coupled Line Termination transmission line IN+ Q IN- 1/2 RSECL levels: LMH 7322 VOH = -1100 mV PECL levels: Q VOL = -1500 mV VOH = 3.9V RHYS VOL = 3.5V LELE RH VE R E 10k EF -5.2V LE levels referred to VCCO + Figure23. PECLTORSECL InterfacefromAnalogtoLVDS As seen in Figure 24, the LMH7322 can be configured to create LVDS levels. This is done by connecting the V to2.5V.AsdiscussedbeforetheoutputlevelsarenowatV –1.1Vforthelogic‘1’andatV −1.5Vfor CCO CCO CCO the logic ‘0’. These levels of 1000 mV and 1400 mV comply with the LVDS levels. As can be seen in this setup, anACcoupledsignalviaatransmissionlineisused.Thissignalisterminatedwith50Ω. 5V + 2.5V + O O CI C C C C C 50: V V V + IN+ Q - IN- 1/2 Levels: LMH 7322 VOH = 1.4V Signal Source Q VOL = 1.0V 50 50 RHYS LL RV EE HE RE 10k EF -5V LE levels referred to VCCO + Figure24. ANALOGTOLVDS Figure 25 shows a standard comparator setup which creates RSPECL levels because the V supply voltage is CCO +5V.InthiscasetheV pinisconnectedtothegroundlevel.TheV pinisconnectedtotheV pinbecause EE CCI CCO there is no need to use different positive supply voltages. The input signal is AC coupled to the positive input. To maintain reliable results the input pins IN+ and IN− are biased at 1.4V through a resistive divider using a resistor of 1 kΩ to ground and a resistor of 2.5 kΩ to the V and by adding two decoupling capacitors. Both inputs are CC connected to the bias level by the use of a 10 kΩ resistor. With this input configuration the input stage can work in a linear area with signals of approximately 3 V (see Input Voltage Range or V in the Electrical PP RI Characteristicstables.) Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 17 ProductFolderLinks:LMH7322

LMH7322 SNOSAU8I–MARCH2007–REVISEDMARCH2013 www.ti.com 5V + O 2k5 CCI CCO VCC V V Vin IN+ Q IN- 1/2 Levels: LMH 7322 VOH = 3.9V Q VOL = 3.5V RHYS 10k 10k VREF + EE F E LL E E R V H 10k R 1k 5k 5k Figure25. StandardSetup Delay and Dispersion Comparators are widely used to connect the analog world to the digital one. The accuracy of a comparator is dictated by its DC properties, such as offset voltage and hysteresis, and by its timing aspects, such as rise and fall times and delay. For low frequency applications most comparators are much faster than the analog input signals they handle. The timing aspects are less important here than the accuracy of the input switching levels. The higher the frequencies, the more important the timing properties of the comparator become, because the response of the comparator can make a noticeable change in critical parameters such as time frame or duty cycle. A designer has to know these effects and has to deal with them. In order to predict what the output signal willdo,severalparametersaredefinedwhichdescribethebehaviorofthecomparator.Foragoodunderstanding of the timing parameters discussed in the following section, a brief explanation is given and several timing diagramsareshownforclarification. Propagation Delay The propagation delay parameter is described in the Table 1 section. Due to this definition there are two parameters, t and t (Figure 26). Both parameters do not necessarily have the same value. It is possible PDH PDL thatdifferenceswilloccurduetoadifferentresponseoftheinternalcircuitry.Asaderivativeofthiseffectanother parameter is defined: Δt . This parameter is defined as the absolute value of the difference between t and PD PDH t . PDL PW 80% 80% VIN 50% 50% 20% 20% tPDH tPDL 80% 80% Output Q 50% 50% 20% 20% tr tf Figure26. PropagationDelay 18 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LMH7322

LMH7322 www.ti.com SNOSAU8I–MARCH2007–REVISEDMARCH2013 If Δt is not zero, duty cycle distortion will occur. For example when applying a symmetrical waveform (e.g. a PD sinewave) at the input, it is expected that the comparator will produce a symmetrical square wave at the output with a duty cycle of 50%. When t and t are different, the duty cycle of the output signal will not remain at PDH PDL 50%, but will be increased or decreased. In addition to the propagation delay parameters for single ended outputs discussed before, there are other parameters in the case of complementary outputs. These parameters describe the delay from input to each of the outputs and the difference between both delay times (See Figure 27.) When the differential input signal crosses the reference level from L to H, both outputs will switch to their new state with some delay. This is defined as t for the Q output and t for the Q output, while the PDH PDL difference between both signals is defined as Δt . Similar definitions for the falling slope of the input signal PDLH canbeseeninFigure19. al n g Si VREF ut time p n I tPDH Q put VO ut time O ’tPDLH Q put VO ut time O tPDL Figure27. t withComplementaryOutputs PD Both output circuits should be symmetrical. At the moment one output is switching ‘on’ the other is switching ‘off’ withideallynoskewbetweenbothoutputs.ThedesignoftheLMH7322isoptimizedsothatthistimingdifference is minimized. The propagation delay, t , is defined as the average delay of both outputs at both slopes: (t + PD PDLH t )/2. PDHL BothoverdriveandstartingpointshouldbeequallydividedaroundtheV (absolutevalues). REF Dispersion There are several circumstances that will produce a variation of the propagation delay time. This effect is called dispersion. AmplitudeOverdriveDispersion One of the parameters that causes dispersion is the amplitude variation of the input signal. Figure 28 shows the dispersion due to a variation of the input overdrive voltage. The overdrive is defined as the ‘go to’ differential voltage applied to the inputs. Figure 28 shows the impact it has on the propagation delay time if the overdrive is variedfrom10mVto100mV.Thisparameterismeasuredwithaconstantslewrateoftheinputsignal. Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 19 ProductFolderLinks:LMH7322

LMH7322 SNOSAU8I–MARCH2007–REVISEDMARCH2013 www.ti.com Overdrive 100 mV + al n g Si ential 0 Overdrive 10 mV er time Diff -100 mV ut p n I - Overdrive Dispersion + al n g Si al Dispersion enti 0 er time Diff ut p ut O - Figure28. OverdriveDispersion Theoverdrivedispersioniscausedbytheswitchingcurrentsintheinputstagewhichisdependentonthelevelof thedifferentialinputsignal. SlewRateDispersion The slew rate is another parameter that affects propagation delay. The higher the input slew rate, the faster the inputstageswitches(SeeFigure29). al + n g Si al nti Differe 0 time ut p n I - Slew Rate Dispersion nal + g Si ntial Dispersion Differe 0 time ut p ut O - Figure29. SlewRateDispersion A combination of overdrive and slew rate dispersion occurs when applying signals with different amplitudes at constant frequency. A small amplitude will produce a small voltage change per time unit (dV/dt) but also a small maximum switching current (overdrive) in the input transistors. High amplitudes produce a high dV/dt and a largeroverdrive. CommonModeDispersion Dispersion will also occur when changing the common mode level of the input signal (Figure 30). When V is REF swept through the CMVR (Common Mode Voltage Range), It results in a variation of the propagation delay time. ThisvariationiscalledCommonModeDispersion. 20 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LMH7322

LMH7322 www.ti.com SNOSAU8I–MARCH2007–REVISEDMARCH2013 Vin cm al + n g Si al nti Vin cm ere 0 time Diff ut p n I - Common Mode Dispersion nal+ g Si ntial Dispersion Differe0 time ut p ut O - Figure30. CommonModeDispersion All of the dispersion effects described previously influence the propagation delay. In practice the dispersion is oftencausedbyacombinationofmorethanonevariedparameter. Hysteresis & Oscillations In contrast to an op amp, the output of a comparator has only two defined states ‘0’ or ‘1.’ Due to finite comparator gain however, there will be a small band of input differential voltage where the output is in an undefined state. An input signal with fast slopes will pass this band very quickly without problems. During slow slopes however, passing the band of uncertainty can take a relatively long time. This enables the comparators outputtoswitchbackandforthseveraltimesbetween‘0’and ‘1’onasingleslope.Thecomparatorwillswitchon its input noise, ground bounce (possible oscillations), ringing etc. Noise in the input signal will also contribute to these undesired switching actions. The next sections explain these phenomena in situations where no hysteresis isapplied,anddiscussthepossibleimprovementhysteresiscangive. UsingNoHysteresis Figure 31 shows what happens when the input signal rises from just under the threshold V to a level just REF above it. From the moment the input reaches the lowest dotted line around V at t=0, the output toggles on REF noise etc. Toggling ends when the input signal leaves the undefined area at t=1. In this example the output was fast enough to toggle three times. Due to this behavior digital circuitry connected to the output will count a wrong number of pulses. One way to prevent this is to choose a very slow comparator with an output that is not able to switchmorethanoncebetween‘0’ and‘1’duringthetimetheinputstateisundefined. Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 21 ProductFolderLinks:LMH7322

LMH7322 SNOSAU8I–MARCH2007–REVISEDMARCH2013 www.ti.com mV al n g SiVref ut np time I ut 1 p ut o st time fa 0 ut 1 p ut o w time slo 0 t=0 t=1 Oscillations & Noise Figure31. OscillationsonOutputSignal Inmostcircumstancesthisisnotanoptionbecausetheslewrateoftheinputsignalwillvary. UsingHysteresis Hysteresis can be introduced to avoid oscillations, e.g. due to noise on the input signal, especially for slow edges. For this purpose the switching level without hysteresis (V ) is forced to a new level (A or B) at the REF momenttheinputsignalcrossesoneoftheselevels.ThiscanbeseeninFigure32. mV al n Sig Vref A ut B p n I 1 ut p ut O 0 t = 0 t = 1 Figure32. Hysteresis In this picture the two dotted lines A and B, represent the resulting reference level at which the comparator will compare the input level against. Assume that for this situation the input signal is connected to the negative input and the switching level (V ) to the positive input. The input level drawn in Figure 32 starts much lower as the REF reference level and this means that the input stage is well defined with the inverting input much lower than the non-inverting input. As a result the output will be in the high state. Internally the switching level is at level A, with the input signal sloping up, this situation remains until V crosses level A at t=1. Now the output toggles, and the IN internal switching level is lowered to level B. So before the output has the possibility to toggle again, the voltage difference between the inputs is sufficient to have a stable situation again. When the input signal comes down from high to low, the situation is stable until level B is reached at t=0. At this moment the output will toggle back, and the circuit returns to the starting situation with the inverting input at a much lower level than the non inverting input. Varying the levels A and B due to the change of the hysteresis resistor will also vary the timing of t=0 and t=1. When designing a circuit be aware of this effect. Introducing hysteresis will cause some time shift between outputandinput(e.g.dutycyclevariations),butwilleliminateundesiredswitchingoftheoutput. 22 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LMH7322

LMH7322 www.ti.com SNOSAU8I–MARCH2007–REVISEDMARCH2013 ConfiguringHysteresisfortheLMH7322 The LMH7322 offers the possibility to introduce hysteresis by connecting a resistor between the RHYS pin and the RHREF pin. This hysteresis setting resistor may vary between zero ohm and infinite. The current drawn from the RHYS pin determines the setting of the internal reference voltage. When no resistor is present the internal used reference voltage is set to zero (the difference between A and B level is zero, see explanation Using Hysteresis) and no hysteresis is configured. This means the output will change state when the difference between the positive en negative input signals crosses zero level. Connecting a resistor between the RHYS pin and the RHREF pin produces a difference for the A and B levels which means hysteresis is introduced and the output will change state at different levels for an up or down transition of the input signal. Due to the internal structure a current must be drawn from the RHYS pin. This can be done by connecting a resistor to the lowest supply voltage. In order to assure the RHYS pin is connected to the correct voltage level, and unwanted current variations in the hysteresis level are avoided, the RHREF and VEE are connected internally within the LMH7322. Therefore, the hysteresis resistor should only be connected between RHYS and RHREF or left open if no hysteresisisrequired.ToselectthecorrectresistorforthedesiredhysteresisvoltageseeFigure33. 70 VCM = 300 mV )V 60 TEMP = 25°C m( EG 50 VVSH Y=S 2 =.7 VV(,H 5YVS,+1)2 -V V(HYS-) A T L 40 O V S IS 30 E R E 20 T S Y H 10 0 0 5 10 15 20 25 30 35 HYSTERESIS RESISTOR (k:) Figure33. HysteresisVoltagevs.HysteresisResistor With the use of a resistor to set the hysteresis voltage no external conditions will effect these setting as long as they stay within the normal operating ranges. Temperature changes may cause a variation of the hysteresis resistor dictated by the temperature coefficient of the used type. Connecting the RHYS pin to another voltage as providedbytheRHREFpinisnotcoveredintheresistorselectionplotandthedesignerofsuchacircuitmustbe awareofabnormalbehavior. The Output OutputSwingProperties The LMH7322 has differential outputs which means that both outputs have the same swing but in opposite directions (See Figure 34). Both outputs swing around the common mode output voltage (V ). This voltage can O be measured at the midpoint between two equal resistors connected to each output. The absolute value of the difference between both voltages is called V . The outputs cannot be held at the V level because of their OD O digital nature. They only cross this level during a transition. Due to the symmetrical structure of the circuit, both outputvoltagescrossatV regardlessofwhethertheoutputchangesfrom‘0’to ‘1’orviseversa. O Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 23 ProductFolderLinks:LMH7322

LMH7322 SNOSAU8I–MARCH2007–REVISEDMARCH2013 www.ti.com Output Q VOH VOD VO Output Q VOL Figure34. OutputSwing LoadingtheOutput Both outputs are activated when current is flowing through a resistor that is externally connected to V . The T termination voltage should be set 2V below the V . This makes it possible to terminate each of the outputs CCO directly with 50Ω, and if needed to connect through a transmission line with the same impedance (see Figure 35). Due to the low ohmic nature of the output emitter followers and the 50Ω load resistor, a capacitive load of several pF does not dramatically affect the speed and shape of the signal. When transmitting the signal from one output to any input the termination resistor should match the transmission line. The capacitive load (C ) P will distort the received signal. When measuring this input with a probe, a certain amount of capacitance from the probe is parallel to the termination resistor. The total capacitance can be as large as 10 pF. In this case there is apoleat: f=1/(2*π*C*R) (1) f=1e9/π (2) f=318MHz (3) InthiscasethecurrentI hasthesamevalueasthecurrentthroughtheterminationresistor.Thismeansthatthe P voltage drops at the input and the rise and fall times are dramatically different from the specified numbers for this part. Another parasitic capacitance that can affect the output signal is the capacitance directly between both outputs, calledC (seeFigure35).TheLMH7322hastwocomplementaryoutputssothereisthepossibilitytotransport PAR the output signal by a symmetrical transmission line. In this case both output tracks form a coupled line with their own parasitics and both receiver inputs connected to the transmission line. Actually the line termination looks like 100Ω and the input capacitances, which are in series, are parallel to the 100Ω termination. The best way to measure the input signal is to use a differential probe directly across both inputs. Such a probe is very suitable for measuring these fast signals because it has good high frequency characteristics and low parasitic capacitance. VCCO IP VCCI CP RT IN+ VT + Q - Q CPAR IN- VEE RT CP IP VT Figure35. ParasiticCapacitance 24 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LMH7322

LMH7322 www.ti.com SNOSAU8I–MARCH2007–REVISEDMARCH2013 TransmissionLines&TerminationTechnologies The LMH7322 uses complementary RSPECL outputs and emitter followers, which means high output current capability and low sensitivity to parasitic capacitance. The use of Reduced Swing Positive Emitter Coupled Logic reduces the supply voltage to 2.7V, being the lowest possible value, and raises the maximum frequency response.Dataratesaregrowing,whichrequiresincreasingspeed.DataisnotonlyconnectedtootherIC’sona single PCB board but, in many cases, there are interconnections from board to board or from equipment to equipment. Distances can be short or long but it is always necessary to have a reliable connection, which consumes low power and is able to handle high data rates. The complementary outputs of the LMH7322 make it possible to use symmetrical transmission lines The advantage over single ended signal transmission is that the LMH7322 has higher immunity to common mode noise. Common mode signals are signals that are equally apparent on both lines and because the receiver only looks at the difference between both lines, this noise is canceled. MaximumBitRates The maximum toggle rate is defined at an amplitude of 50% of the nominal output signal. This toggle rate is a number for the maximum transfer rate of the part and can be given in Hz or in Bps. When transmitting signals in a NRZ (Non Return to Zero) format the bitrate is double this frequency number, because during one period two bits can be transmitted. (See Figure 36.) The rise and fall times are very important specifications in high speed circuits. In fact these times determine the maximum toggle rate of the part. Rise and fall times are normally specified at 20% and 80% of the signal amplitude (60% difference). Assuming that the edges at 50% amplitude are coming up and down like a sawtooth it is possible to calculate the maximum toggle rate but this number is toooptimistic.Inpracticetheedgesarenotlinearwhilethepulseshapeismoreorlessasinewave. period period 1 2 80% VOUT Decision Level 20% 1 bit Ideal Pulse Out 0 1 0 1 0 1 0 0 Figure36. BitRates NeedforTerminatedTransmissionLines During the 1980’s and 90’s, TI fabricated the 100K ECL logic family. The rise and fall time specifications were 0.75 ns, which are considered very fast. If sufficient care has not been given in designing the transmission lines and choosing the correct terminations, then errors in digital circuits are introduced. To be helpful to designers thatuseECLwith“old”PCB-techniques,the10KECLfamilywasintroducedwithariseandfalltimespecification of 2 ns. This was much slower and easier to use. The RSPECL output signals of the LMH7322 have transition times that extend the fastest ECL family. A careful PCB design is needed using RF techniques for transmission and termination. Transmission lines can be formed in several ways. The most commonly used types are the coaxialcableandthetwistedpairtelephonycable(Figure37). D 2h d d Parallel Wire Coax Cable Figure37. CableTypes Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 25 ProductFolderLinks:LMH7322

LMH7322 SNOSAU8I–MARCH2007–REVISEDMARCH2013 www.ti.com These cables have a characteristic impedance determined by their geometric parameters. Widely used impedances for the coaxial cable are 50Ω and 75Ω. Twisted pair cables have impedances of about 120Ω to 150Ω. Other types of transmission lines are the strip line and the micro strip line. These last types are used on PCB boards. They have the characteristic impedance dictated by the physical dimensions of a track placed over a metalgroundplane(seeFigure38). top copper signal line PCB FR4 bottom copper stripline signal line Top Copper PCB FR4 bottom copper Microstrip signal lines Top Copper PCB FR4 bottom copper differential microstrip Figure38. PBCLines DifferentialMicrostrip LineThetransmissionlinewhichisideallysuitedforcomplementarysignalsisthedifferentialmicrostripline.This is a double microstrip line with a narrow space in between. This means both lines have strong coupling and this determines the characteristic impedance. The fact that they are routed above a copper plane does not affect differential impedance, only CM-capacitance is added. Each of the structures above has its own geometric parameters, so for each structure there is different formula to calculate the right impedance. For calculations on these transmission lines visit the TI website or order RAPIDESIGNER. At the end of the transmission line there must be a termination having the same impedance as that of the transmission line itself. It does not matter what impedance the line has, if the load has the same value no reflections will occur. When designing a PCB board with transmission lines on it, space becomes an important item especially on high density boards. With a single microstrip line, line width is fixed for given impedance and a board material. Other line widths will result in differentimpedances. AdvantagesofDifferentialMicrostripLines Impedances of transmission lines are always dictated by their geometric parameters. This is also true for differential microstrip lines. Using this type of transmission line, the distance of the track determines the resulting impedance. So, if the PCB manufacturer can produce reliable boards with low track spacing the track width for a given impedance is also small. The wider the spacing, the wider tracks are needed for a specific impedance. For example two tracks of 0.2 mm width and 0.1 mm spacing have the same impedance as two tracks of 0.8 mm width and 0.4 mm spacing. With high-end PCB processes, it is possible to design very narrow differential microstriptransmissionlines.Itisdesirabletousethesetocreateoptimalconnectionstothereceivingpartorthe terminating resistor, in accordance to their physical dimensions. Seen from the comparator, the termination resistor must be connected at the far end of the line. Open connections after the termination resistor (e.g. to an input of a receiver) must be as short as possible. The allowed length of such connections varies with the receivedtransients.Thefasterthetransients,theshortertheopenlinesmustbetopreventsignaldegradation. 26 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LMH7322

LMH7322 www.ti.com SNOSAU8I–MARCH2007–REVISEDMARCH2013 PCBLayoutConsiderationsandComponentValueSelection High frequency designs require that both active and passive components be selected from those that are specially designed for this purpose. The LMH7322 is fabricated in a 24-pin WQFN package intended for surface mount design. For reliable high speed design it is highly recommended to use small surface mount passive components because these packages have low parasitic capacitance and low inductance simply because they have no leads to connect them to the PCB. It is possible to amplify signals at frequencies of several hundreds of MHz using standard through-hole resistors. Surface mount devices however, are better suited for this purpose. Another important issue is the PCB itself, which is no longer a simple carrier for all the parts and a medium to interconnect them. The PCB becomes a real component itself and consequently contributes its own high frequencypropertiestotheoverallperformanceofthecircuit.Goodpracticedictatesthatahighfrequencydesign have at least one ground plane, providing a low impedance path for all decoupling capacitors and other ground connections. Care should be given especially that on-board transmission lines have the same impedance as the cables to which they are connected. Most single ended applications have 50Ω impedance (75Ω for video and cable TV applications). Such low impedance, single ended microstrip transmission lines usually require much wider traces (2 to 3 mm) on a standard double sided PCB board than needed for a ‘normal’ trace. Another important issue is that inputs and outputs should not ‘see’ each other. This occurs if input and output tracks are routed in parallel over the PCB with only a small amount of physical separation, particularly when the difference in signal level is high. Furthermore, components should be placed as flat and low as possible on the surface of the PCB. For higher frequencies a long lead can act as a coil, a capacitor or an antenna. A pair of leads can even form a transformer. Careful design of the PCB minimizes oscillations, ringing and other unwanted behavior. For ultra high frequency designs only surface mount components will give acceptable results. (For more informationseeOA-15[SNOA367]). TIsuggeststhefollowingevaluationboardasaguideforhighfrequencylayoutandasanaidindevicetesting: LMH7322EVAL Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 27 ProductFolderLinks:LMH7322

LMH7322 SNOSAU8I–MARCH2007–REVISEDMARCH2013 www.ti.com REVISION HISTORY ChangesfromRevisionH(March2013)toRevisionI Page • ChangedlayoutofNationalDataSheettoTIformat.......................................................................................................... 27 28 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LMH7322

PACKAGE OPTION ADDENDUM www.ti.com 14-Sep-2018 PACKAGING INFORMATION Orderable Device Status Package Type Package Pins Package Eco Plan Lead/Ball Finish MSL Peak Temp Op Temp (°C) Device Marking Samples (1) Drawing Qty (2) (6) (3) (4/5) LMH7322SQ/NOPB ACTIVE WQFN RTW 24 1000 Green (RoHS CU SN Level-3-260C-168 HR -40 to 125 L7322SQ & no Sb/Br) LMH7322SQE/NOPB ACTIVE WQFN RTW 24 250 Green (RoHS CU SN Level-3-260C-168 HR -40 to 125 L7322SQ & no Sb/Br) (1) The marketing status values are defined as follows: ACTIVE: Product device recommended for new designs. LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect. NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design. PREVIEW: Device has been announced but is not in production. Samples may or may not be available. OBSOLETE: TI has discontinued the production of the device. (2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free". RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption. Green: TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement. (3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature. (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device. (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device. (6) Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width. Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release. In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis. Addendum-Page 1

PACKAGE OPTION ADDENDUM www.ti.com 14-Sep-2018 Addendum-Page 2

PACKAGE MATERIALS INFORMATION www.ti.com 15-Sep-2018 TAPE AND REEL INFORMATION *Alldimensionsarenominal Device Package Package Pins SPQ Reel Reel A0 B0 K0 P1 W Pin1 Type Drawing Diameter Width (mm) (mm) (mm) (mm) (mm) Quadrant (mm) W1(mm) LMH7322SQ/NOPB WQFN RTW 24 1000 178.0 12.4 4.3 4.3 1.3 8.0 12.0 Q1 LMH7322SQE/NOPB WQFN RTW 24 250 178.0 12.4 4.3 4.3 1.3 8.0 12.0 Q1 PackMaterials-Page1

PACKAGE MATERIALS INFORMATION www.ti.com 15-Sep-2018 *Alldimensionsarenominal Device PackageType PackageDrawing Pins SPQ Length(mm) Width(mm) Height(mm) LMH7322SQ/NOPB WQFN RTW 24 1000 210.0 185.0 35.0 LMH7322SQE/NOPB WQFN RTW 24 250 210.0 185.0 35.0 PackMaterials-Page2

PACKAGE OUTLINE RTW0024A WQFN - 0.8 mm max height SCALE 3.000 PLASTIC QUAD FLATPACK - NO LEAD A 4.1 B 3.9 PIN 1 INDEX AREA 4.1 3.9 C 0.8 MAX SEATING PLANE 0.05 0.00 0.08 C 2X 2.5 (0.1) TYP EXPOSED 7 12 THERMAL PAD 20X 0.5 6 13 2X 25 2.5 2.6 0.1 1 18 0.3 24X 0.2 PIN 1 ID 24 19 0.1 C A B (OPTIONAL) 0.5 0.05 C 24X 0.3 4222815/A 03/2016 NOTES: 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance. www.ti.com

EXAMPLE BOARD LAYOUT RTW0024A WQFN - 0.8 mm max height PLASTIC QUAD FLATPACK - NO LEAD ( 2.6) SYMM 24 19 24X (0.6) 1 18 24X (0.25) (1.05) SYMM 25 (3.8) 20X (0.5) (R0.05) TYP 6 13 ( 0.2) TYP VIA 7 12 (1.05) (3.8) LAND PATTERN EXAMPLE SCALE:15X 0.07 MAX 0.07 MIN ALL AROUND ALL AROUND SOLDER MASK METAL OPENING SOLDER MASK METAL UNDER OPENING SOLDER MASK NON SOLDER MASK SOLDER MASK DEFINED DEFINED (PREFERRED) SOLDER MASK DETAILS 4222815/A 03/2016 NOTES: (continued) 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271). www.ti.com

EXAMPLE STENCIL DESIGN RTW0024A WQFN - 0.8 mm max height PLASTIC QUAD FLATPACK - NO LEAD 4X ( 1.15) (0.675) TYP (R0.05) TYP 24 19 24X (0.6) 1 18 24X (0.25) (0.675) TYP SYMM 20X (0.5) 25 (3.8) 6 13 METAL TYP 7 12 SYMM (3.8) SOLDER PASTE EXAMPLE BASED ON 0.125 mm THICK STENCIL EXPOSED PAD 25: 78% PRINTED SOLDER COVERAGE BY AREA UNDER PACKAGE SCALE:20X 4222815/A 03/2016 NOTES: (continued) 5. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations. www.ti.com

IMPORTANTNOTICEANDDISCLAIMER TIPROVIDESTECHNICALANDRELIABILITYDATA(INCLUDINGDATASHEETS),DESIGNRESOURCES(INCLUDINGREFERENCE DESIGNS),APPLICATIONOROTHERDESIGNADVICE,WEBTOOLS,SAFETYINFORMATION,ANDOTHERRESOURCES“ASIS” ANDWITHALLFAULTS,ANDDISCLAIMSALLWARRANTIES,EXPRESSANDIMPLIED,INCLUDINGWITHOUTLIMITATIONANY IMPLIEDWARRANTIESOFMERCHANTABILITY,FITNESSFORAPARTICULARPURPOSEORNON-INFRINGEMENTOFTHIRD PARTYINTELLECTUALPROPERTYRIGHTS. TheseresourcesareintendedforskilleddevelopersdesigningwithTIproducts.Youaresolelyresponsiblefor(1)selectingtheappropriate TIproductsforyourapplication,(2)designing,validatingandtestingyourapplication,and(3)ensuringyourapplicationmeetsapplicable standards,andanyothersafety,security,orotherrequirements.Theseresourcesaresubjecttochangewithoutnotice.TIgrantsyou permissiontousetheseresourcesonlyfordevelopmentofanapplicationthatusestheTIproductsdescribedintheresource.Other reproductionanddisplayoftheseresourcesisprohibited.NolicenseisgrantedtoanyotherTIintellectualpropertyrightortoanythird partyintellectualpropertyright.TIdisclaimsresponsibilityfor,andyouwillfullyindemnifyTIanditsrepresentativesagainst,anyclaims, damages,costs,losses,andliabilitiesarisingoutofyouruseoftheseresources. TI’sproductsareprovidedsubjecttoTI’sTermsofSale(www.ti.com/legal/termsofsale.html)orotherapplicabletermsavailableeitheron ti.comorprovidedinconjunctionwithsuchTIproducts.TI’sprovisionoftheseresourcesdoesnotexpandorotherwisealterTI’sapplicable warrantiesorwarrantydisclaimersforTIproducts. MailingAddress:TexasInstruments,PostOfficeBox655303,Dallas,Texas75265 Copyright©2018,TexasInstrumentsIncorporated

Datasheet下载

Datasheet下载