ICGOO在线商城 > 集成电路(IC) > PMIC - 稳压器 - DC DC 开关稳压器 > LM20145QMHE/NOPB

- 型号: LM20145QMHE/NOPB

- 制造商: Texas Instruments

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

LM20145QMHE/NOPB产品简介:

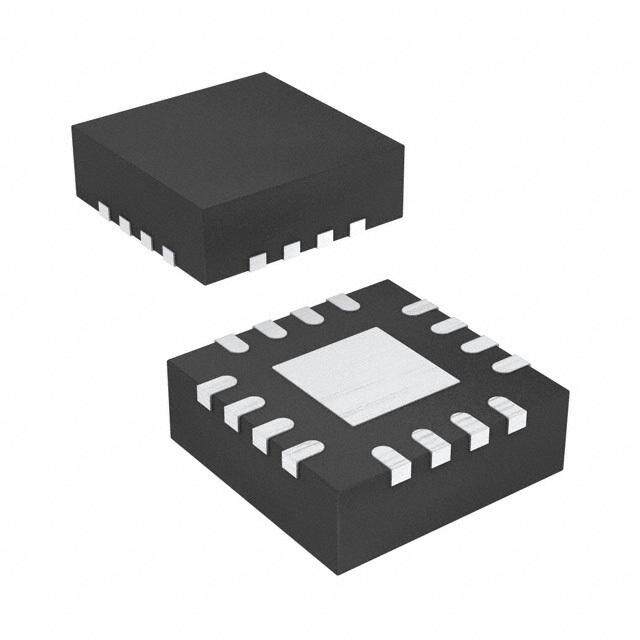

ICGOO电子元器件商城为您提供LM20145QMHE/NOPB由Texas Instruments设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 LM20145QMHE/NOPB价格参考¥12.36-¥19.06。Texas InstrumentsLM20145QMHE/NOPB封装/规格:PMIC - 稳压器 - DC DC 开关稳压器, 可调式 降压 开关稳压器 IC 正 0.8V 1 输出 5A 16-TSSOP(0.173",4.40mm 宽)裸露焊盘。您可以下载LM20145QMHE/NOPB参考资料、Datasheet数据手册功能说明书,资料中有LM20145QMHE/NOPB 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC)半导体 |

| 描述 | IC REG BUCK SYNC ADJ 5A 16-TSSOP稳压器—开关式稳压器 5A,PwrWise Adj Freq Sync Buck Reg |

| 产品分类 | |

| 品牌 | Texas Instruments |

| 产品手册 | |

| 产品图片 | |

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 电源管理 IC,稳压器—开关式稳压器,Texas Instruments LM20145QMHE/NOPB- |

| 数据手册 | |

| 产品型号 | LM20145QMHE/NOPB |

| PWM类型 | 电流模式 |

| 产品种类 | 稳压器—开关式稳压器 |

| 供应商器件封装 | 16-HTSSOP |

| 其它名称 | LM20145QMHE/NOPBCT |

| 包装 | 剪切带 (CT) |

| 参考设计库 | http://www.digikey.com/rdl/4294959904/4294959903/278http://www.digikey.com/rdl/4294959904/4294959903/279 |

| 同步整流器 | 是 |

| 商标 | Texas Instruments |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装 | Reel |

| 封装/外壳 | 16-TSSOP (0.173", 4.40mm 宽)裸焊盘 |

| 封装/箱体 | HTSSOP-16 |

| 工作温度 | -40°C ~ 125°C |

| 工厂包装数量 | 250 |

| 开关频率 | 250 kHz to 750 kHz |

| 最大工作温度 | + 125 C |

| 最大输入电压 | 5.5 V |

| 最小工作温度 | - 40 C |

| 最小输入电压 | 2.95 V |

| 标准包装 | 1 |

| 电压-输入 | 2.95 V ~ 5.5 V |

| 电压-输出 | 0.8 V ~ 5 V |

| 电流-输出 | 5A |

| 类型 | 降压(降压) |

| 系列 | LM20145-Q1 |

| 负载调节 | 0.08 %/A |

| 输出数 | 1 |

| 输出电压 | Adj |

| 输出电流 | 5 A |

| 输出端数量 | 1 Output |

| 输出类型 | 可调式 |

| 频率-开关 | 260kHz ~ 750kHz |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

LM20145 www.ti.com SNVS530E–OCTOBER2007–REVISEDMARCH2013 ® LM20145/LM20145Q 5A, PowerWise Adjustable Frequency Synchronous Buck Regulator CheckforSamples:LM20145 FEATURES DESCRIPTION 1 • AvailableinAEC-Q100TemperatureGrade1 The LM20145 is a full featured adjustable frequency 2 synchronous buck regulator capable of delivering up • InputVoltageRange2.95Vto5.5V to 5A of continuous output current. The current mode • AccurateCurrentLimitMinimizesInductor control loop can be compensated to be stable with Size virtually any type of output capacitor. For most cases, • 97%PeakEfficiency compensating the device only requires two external components, providing maximum flexibility and ease • AdjustableSwitchingFrequency(250kHzto of use. The device is optimized to work over the input 750kHz) voltage range of 2.95V to 5.5V making it suited for a • 32mΩIntegratedFETSwitches widevarietyoflowvoltagesystems. • StartsupintoPre-BiasedLoads The device features internal over voltage protection • OutputVoltageTracking (OVP) and over current protection (OCP) circuits for increased system reliability. A precision enable pin • PeakCurrentModeControl and integrated UVLO allows the turn-on of the device • AdjustableOutputVoltagedownto0.8V to be tightly controlled and sequenced. Start-up • AdjustableSoft-StartwithExternalCapacitor inrush currents are limited by both an internally fixed and externally adjustable Soft-Start circuit. Fault • PrecisionEnablePinwithHysteresis detection and supply sequencing is possible with the • IntegratedOVP,UVLO,PowerGoodand integratedpowergoodcircuit. ThermalShutdown The LM20145 is designed to work well in multi-rail • HTSSOP16-PinExposedPadPackage power supply architectures. The output voltage of the device can be configured to track a higher voltage rail APPLICATIONS using the SS/TRK pin. If the output of the LM20145 is • SimpletoDesign,HighEfficiencyPointof pre-biased at startup it will not sink current to pull the LoadRegulationfroma5Vor3.3VBus output low until the internal soft-start ramp exceeds thevoltageatthefeedbackpin. • HighPerformanceDSPs,FPGAs,ASICsand Microprocessors The frequency of this device can be adjusted from 250 kHz to 750 kHz by connecting an external • Broadband,NetworkingandOptical resistorfromtheRTpintoground. CommunicationsInfrastructure The LM20145 is offered in a 16-pin HTSSOP package with an exposed pad that can be soldered to thePCB,eliminatingtheneedforbulkyheatsinks. TypicalApplicationCircuit LM20145 L VIN PVIN SW VOUT RFB1 CIN RF EN FB COUT AVIN RFB2 CF RT PGOOD RT VCC COMP RC1 SS/TRK CVCC CC1 PGND AGND CSS (optional) 1 Pleasebeawarethatanimportantnoticeconcerningavailability,standardwarranty,anduseincriticalapplicationsof TexasInstrumentssemiconductorproductsanddisclaimerstheretoappearsattheendofthisdatasheet. Alltrademarksarethepropertyoftheirrespectiveowners. 2 PRODUCTIONDATAinformationiscurrentasofpublicationdate. Copyright©2007–2013,TexasInstrumentsIncorporated Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarilyincludetestingofallparameters.

LM20145 SNVS530E–OCTOBER2007–REVISEDMARCH2013 www.ti.com Thesedeviceshavelimitedbuilt-inESDprotection.Theleadsshouldbeshortedtogetherorthedeviceplacedinconductivefoam duringstorageorhandlingtopreventelectrostaticdamagetotheMOSgates. ConnectionDiagram TopView SS/TRK 1 16 RT FB 2 15 AGND PGOOD 3 14 AVIN COMP 4 Exposed Pad 13 VCC On Bottom NC 5 (EP) 12 EN PVIN 6 11 PGND PVIN 7 10 PGND SW 8 9 SW SeePackageNumberPWP0016A PinDescriptions Pin# Name Description Soft-StartorTrackingcontrolinput.Aninternal5µAcurrentsourcechargesanexternalcapacitortosetthe 1 SS/TRK Soft-Startramprate.Ifdrivenbyaexternalsourcelessthan800mV,thispinoverridestheinternalreference thatsetstheoutputvoltage.Ifleftopen,aninternal1msSoft-Startrampisactivated. Feedbackinputtotheerroramplifierfromtheregulatedoutput.Thispinisconnectedtotheinvertinginputof 2 FB theinternaltransconductanceerroramplifier.An800mVreferenceconnectedtothenon-invertinginputofthe erroramplifiersetstheclosedloopregulationvoltageattheFBpin. Powergoodoutputsignal.Opendrainoutputindicatingtheoutputvoltageisregulatingwithintolerance.A 3 PGOOD pull-upresistorof10kΩto100kΩisrecommendformostapplications. 4 COMP Externalcompensationpin.Connectaresistorandcapacitortothispintocompensatethedevice. Thispinhasnointernalconnection.Whilethispinmaybeleftopen,itisstronglyrecommendedthatthispin 5 NC beconnectedtoGround. Inputvoltagetothepowerswitchesinsidethedevice.Thesepinsshouldbeconnectedtogetheratthedevice. 6,7 PVIN AlowESRcapacitorshouldbeplacednearthesepinstostabilizetheinputvoltage. 8,9 SW Switchpin.ThePWMoutputoftheinternalpowerswitches. 10,11 PGND Powergroundpinfortheinternalpowerswitches. Precisionenableinputforthedevice.Anexternalvoltagedividercanbeusedtosetthedeviceturn-on 12 EN threshold.IfnotusedtheENpinshouldbeconnectedtoPVIN. 13 VCC Internal2.7Vsub-regulator.Thispinshouldbebypassedwitha1µFceramiccapacitor. 14 AVIN Analoginputsupplythatgeneratestheinternalbias.MustbeconnectedtoVINthroughalowpassRCfilter. 15 AGND Quietanaloggroundfortheinternalbiascircuitry. 16 RT Frequencyadjustpin.Connectingaresistoronthispintogroundwillsettheoscillatorfrequency. Exposedmetalpadontheundersideofthepackagewithaweakelectricalconnectiontoground.Itis EP ExposedPad recommendedtoconnectthispadtothePCboardgroundplaneinordertoimproveheatdissipationand reducethepackageθ .DonotconnecttoanypotentialotherthanGround. JA 2 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LM20145

LM20145 www.ti.com SNVS530E–OCTOBER2007–REVISEDMARCH2013 ABSOLUTE MAXIMUM RATINGS(1) VoltagesfromtheindicatedpinstoGND AVIN,PVIN,EN,PGOOD,SS/TRK,COMP,FB,RT -0.3Vto+6V StorageTemperature -65°Cto150°C JunctionTemperature 150°C PowerDissipation(2) 2.6W LeadTemperature(Soldering,10sec) 260°C MinimumESDRating(3) ±2kV (1) AbsoluteMaximumRatingsindicatelimitsbeyondwhichdamagetothedevicemayoccur.OperatingRatingsindicateconditionsfor whichthedeviceisintendedtobefunctional,butdonotspecificperformancelimits.Forspecificationsandtestconditions,seethe ElectricalCharacteristics. (2) Themaximumallowablepowerdissipationisafunctionofthemaximumjunctiontemperature,T ,thejunctions-to-ambientthermal J_MAX resistance,θ ,andtheambienttemperature,T .Themaximumallowablepowerdissipationatanyambienttemperatureiscalculated JA A using:P =(T –T )/θ .Themaximumpowerdissipationsof2.6WisdeterminedusingT =25°C,θ =38°C/W,andT D_MAX J_MAX A JA A JA J_MAX =125°C. (3) Thehumanbodymodelisa100pFcapacitordischargedthrougha1.5kΩresistortoeachpin. OPERATING RATINGS PVIN,AVINtoGND 2.95Vto5.5V JunctionTemperature −40°Cto+125°C Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 3 ProductFolderLinks:LM20145

LM20145 SNVS530E–OCTOBER2007–REVISEDMARCH2013 www.ti.com ELECTRICAL CHARACTERISTICS Unlessotherwisestated,thefollowingconditionsapply:AVIN=PVIN=VIN=5V.LimitsinstandardtypeareforT =25°C J only,limitsinboldfacetypeapplyoverthejunctiontemperature(T)rangeof-40°Cto+125°C.MinimumandMaximumlimits J arespecifiedbytest,design,orstatisticalcorrelation.TypicalvaluesrepresentthemostlikelyparametricnormatT =25°C, J andareprovidedforreferencepurposesonly. Symbol Parameter Conditions Min Typ Max Unit V Feedbackpinvoltage V =2.95Vto5.5V 0.788 0.8 0.812 V FB IN ΔV /ΔI LoadRegulation I =100mAto5A 0.08 %/A OUT OUT OUT I SwitchCurrentLimitThreshold V =3.3V 6.7 7.4 8.1 A CL IN R High-SideSwitchOnResistance I =3.5A 36 55 mΩ DS_ON SW R Low-SideSwitchOnResistance I =3.5A 32 52 mΩ DS_ON SW I OperatingQuiescentCurrent Non-switching,V =V 3.5 6 mA Q FB COMP I ShutdownQuiescentcurrent V =0V 90 180 µA SD EN V VINUnderVoltageLockout RisingV 2.45 2.7 2.95 V UVLO IN V VINUnderVoltageLockoutHysteresis FallingV 45 100 mV UVLO_HYS IN V VCCVoltage I =0µA 2.45 2.7 2.95 V VCC VCC I Soft-StartPinSourceCurrent V =0V 2 4.5 7 µA SS SS/TRK V SS/TRKAccuracy,V -V V =0.4V -10 3 15 mV TRACK SS FB SS/TRK Oscillator F OscillatorFrequency R =49.9kΩ 675 750 825 kHz OSCH T F OscillatorFrequency R =249kΩ 225 260 290 kHz OSCL T DC MaximumDutyCycle I =0A 85 % MAX LOAD T MinimumOnTime 100 ns ON_TIME T CurrentSenseBlankingTime AfterRisingV 80 ns CL_BLANK SW ErrorAmplifierandModulator I Feedbackpinbiascurrent V =0.8V 1 100 nA FB FB I COMPOutputSourceCurrent V =V =0.6V 80 100 µA COMP_SRC FB COMP I COMPOutputSinkCurrent V =1.0V,V =0.6V 80 100 µA COMP_SNK FB COMP Gm ErrorAmplifierTransconductance I =±50µA 450 510 600 µmho COMP A ErrorAmplifierVoltageGain 2000 V/V VOL PowerGood V OverVoltageProtectionRisingThreshold 105 108 111 % OVP WithrespecttoV FB V OverVoltageProtectionHysteresis 2 3 % OVP_HYS V PGOODRisingThreshold 92 94 96 % PGTH WithrespecttoV FB V PGOODFallingHysteresis 2 3 % PGHYS T PGOODdeglitchtime 16 µs PGOOD I PGOODLowSinkCurrent V =0.4V 0.6 1 mA OL PGOOD I PGOODHighLeakageCurrent V =5V 5 100 nA OH PGOOD Enable V ENPinturn-onThreshold V Rising 1.08 1.18 1.28 V IH_EN EN V ENPinHysteresis 66 mV EN_HYS ThermalShutdown T ThermalShutdown 160 °C SD T ThermalShutdownHysteresis 10 °C SD_HYS ThermalResistance θ JunctiontoAmbient See(1) 38 JA °C/W θ JunctiontoCase See(2) 3.5 JC (1) OnJEDEC4-Layertestboard(JESD51-7witheight(8)thermalvias. (2) θ referstothecenteroftheExposedPadonthebottomofthepackageastheCase. JC 4 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LM20145

LM20145 www.ti.com SNVS530E–OCTOBER2007–REVISEDMARCH2013 TYPICAL PERFORMANCE CHARACTERISTICS Unlessotherwisespecified:C =C =100µF,L=1.5µH(CoilcraftMSS1038),V =5V,V =1.2V,R =1.2Ω, IN OUT IN OUT LOAD f =500kHz,T =25°Cforefficiencycurves,loopgainplotsandwaveforms,andT =25°Cforallothers. SW A J Efficiency Efficiency vs. vs. LoadCurrent(V =5V) LoadCurrent(V =3.3V) IN IN Figure1. Figure2. High-SideFETResistance Low-SideFETResistance vs. vs. Temperature Temperature Figure3. Figure4. ErrorAmplifierGain vs. Frequency LineRegulation Figure5. Figure6. Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 5 ProductFolderLinks:LM20145

LM20145 SNVS530E–OCTOBER2007–REVISEDMARCH2013 www.ti.com TYPICAL PERFORMANCE CHARACTERISTICS (continued) Unlessotherwisespecified:C =C =100µF,L=1.5µH(CoilcraftMSS1038),V =5V,V =1.2V,R =1.2Ω, IN OUT IN OUT LOAD f =500kHz,T =25°Cforefficiencycurves,loopgainplotsandwaveforms,andT =25°Cforallothers. SW A J FeedbackPinVoltage vs. LoadRegulation Temperature Figure7. Figure8. SwitchingFrequency SwitchingFrequency vs. vs. Temperature R T Figure9. Figure10. QuiescentCurrent ShutdownCurrent vs. vs. V (NotSwitching) Temperature IN Figure11. Figure12. 6 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LM20145

LM20145 www.ti.com SNVS530E–OCTOBER2007–REVISEDMARCH2013 TYPICAL PERFORMANCE CHARACTERISTICS (continued) Unlessotherwisespecified:C =C =100µF,L=1.5µH(CoilcraftMSS1038),V =5V,V =1.2V,R =1.2Ω, IN OUT IN OUT LOAD f =500kHz,T =25°Cforefficiencycurves,loopgainplotsandwaveforms,andT =25°Cforallothers. SW A J EnableThreshold UVLOThreshold vs. vs. Temperature Temperature Figure13. Figure14. PeakCurrentLimit PeakCurrentLimit vs. vs. Temperature V OUT Figure15. Figure16. PeakCurrentLimit vs. V LoadTransientResponse IN Figure17. Figure18. Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 7 ProductFolderLinks:LM20145

LM20145 SNVS530E–OCTOBER2007–REVISEDMARCH2013 www.ti.com TYPICAL PERFORMANCE CHARACTERISTICS (continued) Unlessotherwisespecified:C =C =100µF,L=1.5µH(CoilcraftMSS1038),V =5V,V =1.2V,R =1.2Ω, IN OUT IN OUT LOAD f =500kHz,T =25°Cforefficiencycurves,loopgainplotsandwaveforms,andT =25°Cforallothers. SW A J LineTransientResponse Start-Up(Soft-Start) Figure19. Figure20. Start-Up(Tracking) PowerDown Figure21. Figure22. ShortCircuitInputCurrent P GOOD vs. vs. V I IN PGOOD Figure23. Figure24. 8 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LM20145

LM20145 www.ti.com SNVS530E–OCTOBER2007–REVISEDMARCH2013 BLOCK DIAGRAM +2.7V REGULATOR AVIN VCC + UVLO 2.7V - SLOPE COMP PVIN COMP 2.7V + CURRENT SENSE 5 PA DISCHARGE(50 Ps) SS/TRK ERROR AMP gm = 510 Pmho + CURRENT DISCHARGE - LIMIT FB + + VREF 7.4A - PVIN + - 800 mV + - PWM COMPARATOR + OVERVOLTAGE DIODE 864 mV - EMULATION PG-L CONTROL +- SW 752 mV + UNDERVOLTAGE LOGIC - PVIN THERMAL PROTECTION + 1.18V - EN PGND PG-L OSCILLATOR PGOOD RT AGND Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 9 ProductFolderLinks:LM20145

LM20145 SNVS530E–OCTOBER2007–REVISEDMARCH2013 www.ti.com OPERATION DESCRIPTION GENERAL The LM20145 switching regulator features all of the functions necessary to implement an efficient low voltage buck regulator using a minimum number of external components. This easy to use regulator features two integratedswitchesandiscapableofsupplyingupto5Aofcontinuousoutputcurrent.Theregulatorutilizespeak current mode control with nonlinear slope compensation to optimize stability and transient response over the entire output voltage range. Peak current mode control also provides inherent line feed-forward, cycle-by-cycle current limiting and easy loop compensation. The switching frequency can be varied from 250 kHz to 750 kHz. The device can operate at high switching frequency allowing use of a small inductor while still achieving high efficiency. The precision internal voltage reference allows the output to be set as low as 0.8V. Fault protection features include: current limiting, thermal shutdown, over voltage protection, and shutdown capability. The device is available in the HTSSOP-16 package featuring an exposed pad to aid thermal dissipation. The LM20145 can be used in numerous applications to efficiently step-down from a 5V or 3.3V bus. The typical application circuit fortheLM20145isshowninFigure26inthedesignguide. PRECISION ENABLE The enable (EN) pin allows the output of the device to be enabled or disabled with an external control signal. Thispinisaprecisionanaloginputthatenablesthedevicewhenthevoltageexceeds1.18V(typical).TheENpin has 66 mV of hysteresis and will disable the output when the enable voltage falls below 1.11V (typical). If the EN pin is not used, it should be connected to VIN. Since the enable pin has a precise turn-on threshold it can be used along with an external resistor divider network from V to configure the device to turn-on at a precise input IN voltage.Theprecisionenablecircuitrywillremainactiveevenwhenthedeviceisdisabled. PEAK CURRENT MODE CONTROL In most cases, the peak current mode control architecture used in the LM20145 only requires two external components to achieve a stable design. The compensation can be selected to accommodate any capacitor type or value. The external compensation also allows the user to set the crossover frequency and optimize the transientperformanceofthedevice. For duty cycles above 50% all current mode control buck converters require the addition of an artificial ramp to avoid sub-harmonic oscillation. This artificial linear ramp is commonly referred to as slope compensation. What makes the LM20145 unique is the amount of slope compensation will change depending on the output voltage. When operating at high output voltages the device will have more slope compensation than when operating at lower output voltages. This is accomplished in the LM20145 by using a non-linear parabolic ramp for the slope compensation. The parabolic slope compensation of the LM20145 is much better than the traditional linear slope compensationbecauseitoptimizesthestabilityofthedeviceovertheentireoutputvoltagerange. CURRENT LIMIT The precise current limit of the LM20123 is set at the factory to be within 10% over the entire operating temperature range. This enables the device to operate with smaller inductors that have lower saturation currents. When the peak inductor current reaches the current limit threshold, an over current event is triggered and the internal high-side FET turns off and the low-side FET turns on allowing the inductor current to ramp down until thenextswitchingcycle.Foreachsequentialover-currentevent,thereferencevoltageisdecrementedandPWM pulses are skipped resulting in a current limit that does not aggressively fold back for brief over-current events, whileatthesametimeprovidingfrequencyandvoltagefoldbackprotectionduringhardshortcircuitconditions. SOFT-START AND VOLTAGE TRACKING The SS/TRK pin is a dual function pin that can be used to set the start up time or track an external voltage source.ThestartuporSoft-StarttimecanbeadjustedbyconnectingacapacitorfromtheSS/TRKpintoground. The Soft-Start feature allows the regulator output to gradually reach the steady state operating point, thus reducingstressesontheinputsupplyandcontrollingstartupcurrent.IfnoSoft-Startcapacitorisusedthedevice defaults to the internal Soft-Start circuitry resulting in a start up time of approximately 1 ms. For applications that require a monotonic start up or utilize the PGOOD pin, an external Soft-Start capacitor is recommended. The SS/TRK pin can also be set to track an external voltage source. The tracking behavior can be adjusted by two externalresistorsconnectedtotheSS/TRKpinasshowninFigure31.inthedesignguide. 10 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LM20145

LM20145 www.ti.com SNVS530E–OCTOBER2007–REVISEDMARCH2013 PRE-BIAS START UP CAPABILITY The LM20145 is in a pre-biased state when the device starts up with an output voltage greater than zero. This often occurs in many multi-rail applications such as when powering an FPGA, ASIC, or DSP. In these applications the output can be pre-biased through parasitic conduction paths from one supply rail to another. Even though the LM20145 is a synchronous converter it will not pull the output low when a prebias condition exists. During start up the LM20145 will not sink current until the Soft-Start voltage exceeds the voltage on the FB pin. Since the device can not sink current it protects the load from damage that might otherwise occur if currentisconductedthroughtheparasiticpathsoftheload. POWER GOOD AND OVER VOLTAGE FAULT HANDLING The LM20145 has built in under and over voltage comparators that control the power switches. Whenever there is an excursion in output voltage above the set OVP threshold, the part will terminate the present on-pulse, turn- on the low-side FET, and pull the PGOOD pin low. The low-side FET will remain on until either the FB voltage falls back into regulation or the zero cross detection is triggered which in turn tri-states the FETs. If the output reaches the UVP threshold the part will continue switching and the PGOOD pin will be asserted and go low. Typical values for the PGOOD resistor are on the order of 100 kΩ or less. To avoid false tripping during transient glitchesthePGOODpinhas16µsofbuiltindeglitchtimetobothrisingandfallingedges. UVLO The LM20145 has a built-in under-voltage lockout protection circuit that keeps the device from switching until the input voltage reaches 2.7V (typical). The UVLO threshold has 45 mV of hysteresis that keeps the device from responding to power-on glitches during start up. If desired the turn-on point of the supply can be changed by using the precision enable pin and a resistor divider network connected to V as shown in Figure 30. in the IN designguide. THERMAL PROTECTION Internal thermal shutdown circuitry is provided to protect the integrated circuit in the event that the maximum junction temperature is exceeded. When activated, typically at 160°C, the LM20145 tri-states the power FETs and resets soft start. After the junction cools to approximately 150°C, the part starts up using the normal start up routine.Thisfeatureisprovidedtopreventcatastrophicfailuresfromaccidentaldeviceoverheating. LIGHT LOAD OPERATION The LM20145 offers increased efficiency when operating at light loads. Whenever the load current is reduced to a point where the peak to peak inductor ripple current is greater than two times the load current, the part will enter the diode emulation mode preventing significant negative inductor current. The point at which this occurs is thecriticalconductionboundaryandcanbecalculatedbythefollowingequation: (VIN – VOUT) x D IBOUNDARY = 2 x L x fSW (1) Several diagrams are shown in Figure 25 illustrating continuous conduction mode (CCM), discontinuous conductionmode,andtheboundarycondition. It can be seen that in diode emulation mode, whenever the inductor current reaches zero the SW node will become high impedance. Ringing will occur on this pin as a result of the LC tank circuit formed by the inductor and the parasitic capacitance at the node. If this ringing is of concern an additional RC snubber circuit can be addedfromtheswitchnodetoground. Atverylightloads,usuallybelow100mA,severalpulsesmaybeskippedinbetweenswitchingcycles,effectively reducingtheswitchingfrequencyandfurtherimprovinglight-loadefficiency. Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 11 ProductFolderLinks:LM20145

LM20145 SNVS530E–OCTOBER2007–REVISEDMARCH2013 www.ti.com e g Continuous Conduction Mode (CCM) a Volt VIN e d o n h c wit S Time (s) nt Continuous Conduction Mode (CCM) e urr C ctor IAVERAGE u d n I Time (s) nt e urr DCM - CCM Boundary C or ct u nd IAVERAGE I Time (s) e g Discontinuous Conduction Mode (DCM) a olt VIN V e d o n h c wit S Time (s) nt e urr Discontinuous Conduction Mode (DCM) C or ct du IPeak n I Time (s) Figure25. ModesofOperationforLM20145 Design Guide This section walks the designer through the steps necessary to select the external components to build a fully functional power supply. As with any DC-DC converter numerous trade-offs are possible to optimize the design for efficiency, size, or performance. These will be taken into account and highlighted throughout this discussion. To facilitate component selection discussions the circuit shown in Figure 26 below may be used as a reference. Unless otherwise indicated all formulas assume units of amps (A) for current, farads (F) for capacitance, henries (H)forinductanceandvolts(V)forvoltages. 12 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LM20145

LM20145 www.ti.com SNVS530E–OCTOBER2007–REVISEDMARCH2013 LM20145 L VIN PVIN SW VOUT CIN RF EANVIN FB RFB1 COUT CF VIN RFB2 RPG RT PGOOD VPG RT COMP VCC RC1 SS/TRK CVCC CC1 PGND GND CSS Figure26. TypicalApplicationCircuit The first equation to calculate for any buck converter is duty-cycle. Ignoring conduction losses associated with theFETsandparasiticresistancesitcanbeapproximatedby: VOUT D = VIN (2) INDUCTORSELECTION(L) Theinductorvalueisdeterminedbasedontheoperatingfrequency,loadcurrent,ripplecurrent,anddutycycle. The inductor selected should have a saturation current rating greater than the peak current limit of the device. Keep in mind the specified current limit does not account for delay of the current limit comparator, therefore the current limit in the application may be higher than the specified value. To optimize the performance and prevent the device from entering current limit at maximum load, the inductance is typically selected such that the ripple current, Δi , is less than 30% of the rated output current. Figure 27, shown below illustrates the switch and L inductorripplecurrentwaveforms.Oncetheinputvoltage,outputvoltage,operatingfrequency,anddesiredripple currentareknown,theminimumvaluefortheinductorcanbecalculatedbytheformulashownbelow: (VIN - VOUT) x D LMIN = ’iL x fSW (3) VSW VIN Time IL IL AVG = IOUT ’IL Time Figure27. SwitchandInductorCurrentWaveforms If needed, slightly smaller value inductors can be used, however, the peak inductor current, I + Δi /2, should OUT L be kept below the peak current limit of the device. In general, the inductor ripple current, Δi , should be greater L than 10% of the rated output current to provide adequate current sense information for the current mode control loop. If the ripple current in the inductor is too low, the control loop will not have sufficient current sense informationandcanbepronetoinstability. Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 13 ProductFolderLinks:LM20145

LM20145 SNVS530E–OCTOBER2007–REVISEDMARCH2013 www.ti.com OUTPUTCAPACITORSELECTION(C ) OUT The output capacitor, C , filters the inductor ripple current and provides a source of charge for transient load OUT conditions.AwiderangeofoutputcapacitorsmaybeusedwiththeLM20145thatprovideexcellentperformance. The best performance is typically obtained using ceramic, SP, or OSCON type chemistries. Typical trade-offs are that the ceramic capacitor provides extremely low ESR to reduce the output ripple voltage and noise spikes, while the SP and OSCON capacitors provide a large bulk capacitance in a small volume for transient loading conditions. When selecting the value for the output capacitor the two performance characteristics to consider are the output voltagerippleandtransientresponse.Theoutputvoltageripplecanbeapproximatedbyusingtheformulashown below. 1 ’VOUT = ’iL x RESR +8 x fSW x COUT where • ΔV (V)istheamountofpeaktopeakvoltagerippleatthepowersupplyoutput OUT • R (Ω)istheseriesresistanceoftheoutputcapacitor ESR • f (Hz)istheswitchingfrequency SW • C (F)istheoutputcapacitanceusedinthedesign (4) OUT Theamountofoutputripplethatcanbetoleratedisapplicationspecific;howeverageneralrecommendationisto keep the output ripple less than 1% of the rated output voltage. Keep in mind ceramic capacitors are sometimes preferred because they have very low ESR; however, depending on package and voltage rating of the capacitor the value of the capacitance can drop significantly with applied voltage. The output capacitor selection will also affect the output voltage droop during a load transient. The peak droop on the output voltage during a load transient is dependent on many factors; however, an approximation of the transient droop ignoring loop bandwidthcanbeobtainedusingthefollowingequation. L x ’I 2 V = ’I x R + OUTSTEP DROOP OUTSTEP ESR C x (V - V ) OUT IN OUT where • C (F)istheminimumrequiredoutputcapacitance OUT • L(H)isthevalueoftheinductor • V (V)istheoutputvoltagedropignoringloopbandwidthconsiderations DROOP • ΔI (A)istheloadstepchange OUTSTEP • R (Ω)istheoutputcapacitorESR,V (V)istheinputvoltage ESR IN • V (V)isthesetregulatoroutputvoltage (5) OUT Both the tolerance and voltage coefficient of the capacitor needs to be examined when designing for a specific outputrippleortransientdroptarget. INPUTCAPACITORSELECTION(C ) IN Good quality input capacitors are necessary to limit the ripple voltage at the VIN pin while supplying most of the switch current during the on-time. In general it is recommended to use a ceramic capacitor for the input as they provide both a low impedance and small footprint. One important note is to use a good dielectric for the ceramic capacitor such as X5R or X7R. These provide better over temperature performance and also minimize the DC voltage derating that occurs on Y5V capacitors. For most applications, a 22 µF, X5R, 6.3V input capacitor is sufficient; however, additional capacitance may be required if the connection to the input supply is far from the PVINpins.TheinputcapacitorshouldbeplacedascloseaspossiblePVINandPGNDpinsofthedevice. Non-ceramic input capacitors should be selected for RMS current rating and minimum ripple voltage. A good approximationfortherequiredripplecurrentratingisgivenbytherelationship: IIN-RMS = IOUT D(1 - D) (6) 14 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LM20145

LM20145 www.ti.com SNVS530E–OCTOBER2007–REVISEDMARCH2013 As indicated by the RMS ripple current equation, highest requirement for RMS current rating occurs at 50% duty cycle. For this case, the RMS ripple current rating of the input capacitor should be greater than half the output current. For best performance, low ESR ceramic capacitors should be placed in parallel with higher capacitance capacitorstoprovidethebestinputfilteringforthedevice. SETTINGTHEOUTPUTVOLTAGE(R ,R ) FB1 FB2 TheresistorsR andR areselectedtosettheoutputvoltageforthedevice.Table1,shownbelow,provides FB1 FB2 suggestionsforR andR forcommonoutputvoltages. FB1 FB2 Table1.SuggestedValuesforR andR FB1 FB2 R (kΩ) R (kΩ) V FB1 FB2 OUT short open 0.8 4.99 10 1.2 8.87 10.2 1.5 12.7 10.2 1.8 21.5 10.2 2.5 31.6 10.2 3.3 If different output voltages are required, R should be selected to be between 4.99 kΩ to 49.9 kΩ and R can FB2 FB1 becalculatedusingtheequationbelow. V OUT RFB1 = - 1 x RFB2 0.8 (7) ADJUSTINGTHEOPERATINGFREQUENCY(R ) T The operating frequency of the LM20145 can be adjusted by connecting a resistor from the RT pin to ground. TheequationshownbelowcanbeusedtocalculatethevalueofR foragivenoperatingfrequency. T 78000 RT = - 55 f SW where • f istheswitchingfrequencyinkHz SW • R isthefrequencyadjustresistorinkΩ (8) T Please refer to the curve Oscillator Frequency verses R in the typical performance characteristics section If the T R resistorisomittedthedevicewillnotoperate. T LOOPCOMPENSATION(R ,C ) C1 C1 The purpose of loop compensation is to meet static and dynamic performance requirements while maintaining adequate stability. Optimal loop compensation depends on the output capacitor, inductor, load, and the device itself. Table 2 below gives values for the compensation network that will result in a stable system when using a 100µF,6.3VceramicX5Routputcapacitorand2.5 µHinductor. Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 15 ProductFolderLinks:LM20145

LM20145 SNVS530E–OCTOBER2007–REVISEDMARCH2013 www.ti.com Table2.RecommendedCompensationfor C =100µF,L=2.5 µH &f =250kHz OUT SW V V C (nF) R (kΩ) IN OUT C1 C1 5.00 3.30 4.7 11 5.00 2.50 4.7 9.53 5.00 1.80 4.7 6.98 5.00 1.50 4.7 5.36 5.00 1.20 4.7 4.87 5.00 0.80 4.7 1.91 3.30 2.50 4.7 10.5 3.30 1.80 4.7 7.87 3.30 1.50 4.7 5.62 3.30 1.20 4.7 4.42 3.30 0.80 4.7 2.26 If the desired solution differs from the table above the loop transfer function should be analyzed to optimize the loopcompensation.Theoveralllooptransferfunctionistheproductofthepowerstageandthefeedbacknetwork transfer functions. For stability purposes, the objective is to have a loop gain slope that is -20db/decade from a very low frequency to beyond the crossover frequency. Figure 28, shown below, shows the transfer functions for powerstage,feedback/compensationnetwork,andtheresultingclosedloopsystemfortheLM20145. er Filt Output Filter Pole, fP(FIL) ut on AM Outpuncti 0 dB Output Filter Zero, fZ(FIL) ulator and Transfer F d Complex Double Pole, fP(MOD) Mo Error Amp Pole, fP1(EA) N (dB) AEA OptPioonlea,l EfPr2ro(Er AA)mp mplifier Function GAI 0 dB Error Amp Zero, fZ(EA) Error ATransfer AEA +0 A dMB Error Amp Pole, fP(EA) pensated Closed Transfer Function Complex Double Pole, fP(MOD) omop Co L fC fSW/2 FREQUENCY (Hz) Figure28. LM20145LoopCompensation The power stage transfer function is dictated by the modulator, output LC filter, and load; while the feedback transferfunctionissetbythefeedbackresistorratio,errorampgain,andexternalcompensationnetwork. To achieve a -20dB/decade slope, the error amplifier zero, located at f , should positioned to cancel the Z(EA) output filter pole (f ). An additional error amp pole, located at f , can be added to cancel the output filter P(FIL) P2(EA) zero at f . Cancellation of the output filter zero is recommended if larger value, non-ceramic output capacitors Z(FIL) areused. CompensationoftheLM20144isachievedbyaddinganRCnetworkasshowninFigure29below. 16 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LM20145

LM20145 www.ti.com SNVS530E–OCTOBER2007–REVISEDMARCH2013 LM20145 COMP RC1 CC2 (optional) CC1 Figure29. CompensationNetworkforLM20145 A good starting value for C for most applications is 4.7 nF. Once the value of C is chosen the value of RC C1 C1 shouldbecalculatedusingtheequationbelowtocanceltheoutputfilterpole(F )asshowninFigure28. P(FIL) -1 C I 1-D 10 x D R = C1 x OUT + + C1 C V f x L V OUT OUT SW IN (9) A higher crossover frequency can be obtained, usually at the expense of phase margin, by lowering the value of C and recalculating the value of R . Likewise, increasing C and recalculating R will provide additional C1 C1 C1 C1 phase margin at a lower crossover frequency. As with any attempt to compensate the LM20145 the stability of thesystemshouldbeverifiedfordesiredtransientdroopandsettlingtime. If the output filter zero, F approaches the crossover frequency (F ), an additional capacitor (C ) should be Z(FIL) C C2 placed at the COMP pin to ground. This capacitor adds a pole to cancel the output filter zero assuring the crossover frequency will occur before the double pole at f /2 degrades the phase margin. The output filter zero SW issetbytheoutputcapacitorvalueandESRasshownintheequationbelow. 1 fZ(FIL) = 2 x S x COUT x RESR (10) Ifneeded,thevalueforC shouldbecalculatedusingtheequationshownbelow. C2 COUT x RESR CC2 = RC1 where • R istheoutputcapacitorseriesresistance ESR • R isthecalculatedcompensationresistance (11) C1 AVINFILTERINGCOMPONENTS(C andR ) F F To prevent high frequency noise spikes from disturbing the sensitive analog circuitry connected to the AVIN and AGND pins, a high frequency RC filter is required between PVIN and AVIN. These components are shown in Figure 26. as C and R . The required value for R is 1Ω. C must be used. Recommended value of C is 1.0 F F F F F µF. The filter capacitor, C should be placed as close to the IC as possible with a direct connection from AVIN to F AGND.AgoodqualityX5RorX7RceramiccapacitorshouldbeusedforC . F SUB-REGULATORBYPASSCAPACITOR(C ) VCC The capacitor at the VCC pin provides noise filtering and stability for the internal sub-regulator. The recommendedvalueofC shouldbenosmallerthan1µFandnogreaterthan10µF.Thecapacitorshouldbe VCC a good quality ceramic X5R or X7R capacitor. In general, a 1 µF ceramic capacitor is recommended for most applications. SETTINGTHESTARTUPTIME(C ) SS The addition of a capacitor connected from the SS pin to ground sets the time at which the output voltage will reach the final regulated value. Larger values for C will result in longer start up times. Table 3, shown below SS providesalistofsoftstartcapacitorsandthecorrespondingtypicalstartuptimes. Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 17 ProductFolderLinks:LM20145

LM20145 SNVS530E–OCTOBER2007–REVISEDMARCH2013 www.ti.com Table3.StartUpTimesforDifferentSoft-StartCapacitors StartUpTime(ms) C (nF) SS 1 none 5 33 10 68 15 100 20 120 Ifdifferentstartuptimesareneededtheequationshownbelowcanbeusedtocalculatethestartuptime. 0.8V x CSS tSS = ISS (12) Asshownabove,thestartuptimeisinfluencedbythevalueoftheSoft-StartcapacitorC (F)andthe5µASoft- SS StartpincurrentI (A).thatmaybefoundintheelectricalcharacteristicstable. SS While the Soft-Start capacitor can be sized to meet many start up requirements, there are limitations to its size. The Soft-Start time can never be faster than 1ms due to the internal default 1 ms start up time. When the device is enabled there is an approximate time interval of 50 µs when the Soft-Start capacitor will be discharged just priortotheSoft-Startramp.IftheenablepinisrapidlypulsedortheSoft-Startcapacitorislargetheremaynotbe enough time for C to completely discharge resulting in start up times less than predicted. To aid in discharging SS of Soft-Start capacitor during long disable periods an external 1 MΩ resistor from SS/TRK to ground can be used withoutgreatlyaffectingthestart-uptime. USINGPRECISIONENABLEANDPOWERGOOD The precision enable (EN) and power good (PGOOD) pins of the LM20145 can be used to address many sequencing requirements. The turn-on of the LM20145 can be controlled with the precision enable pin by using twoexternalresistorsasshowninFigure30. External VOUT1 Power Supply RA LM20145 VOUT2 EN RB Figure30. SequencingLM20145withPrecisionEnable The value for resistor R can be selected by the user to control the current through the divider. Typically this B resistor will be selected to be between 10 kΩ and 1 MΩ. Once the value for R is chosen the resistor R can be B A solvedusingtheequationbelowtosetthedesiredturn-onvoltage. V RA = V TO - 1 x RB IH_EN (13) When designing for a specific turn-on threshold (V ) the tolerance on the input supply, enable threshold TO (V ),andexternalresistorsneedstobeconsideredtoinsureproperturn-onofthedevice. IH_EN The LM20145 features an open drain power good (PGOOD) pin to sequence external supplies or loads and to provide fault detection. This pin requires an external resistor (R ) to pull PGOOD high while when the output is PG withinthePGOODtolerancewindow.Typicalvaluesforthisresistorrangefrom10kΩto100kΩ. TRACKINGANEXTERNALSUPPLY By using a properly chosen resistor divider network connected to the SS/TRK pin, as shown in Figure 31, the output of the LM20145 can be configured to track an external voltage source to obtain a simultaneous or ratiometricstartup. 18 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LM20145

LM20145 www.ti.com SNVS530E–OCTOBER2007–REVISEDMARCH2013 External VOUT1 Power Supply EN R1 LM20145 VOUT2 SS/TRK R2 Figure31. TrackinganExternalSupply Since the Soft-Start charging current I is always present on the SS/TRK pin, the size of R2 should be less than SS 10 kΩ to minimize the errors in the tracking output. Once a value for R2 is selected the value for R1 can be calculated using appropriate equation in Figure 32, to give the desired start up. Figure 32 shows two common start up sequences; the top waveform shows a simultaneous start up while the waveform at the bottom illustrates aratiometricstartup. SIMULTANEOUS START UP VOUT1 AGE VOUT2 R1=¤§¤VOUT2-1‚•‚xR2 LT ' 0.8V „ O V VEN V <0.8xV OUT2 OUT1 TIME RATIOMETRIC START UP VOUT1 VOUT2 R1=(VOUT1-1)xR2 E G A T L O V VEN TIME Figure32. CommonStartUpSequences A simultaneous start up is preferred when powering most FPGAs, DSPs, or other microprocessors. In these systems the higher voltage, V , usually powers the I/O, and the lower voltage, V , powers the core. A OUT1 OUT2 simultaneous start up provides a more robust power up for these applications since it avoids turning on any parasiticconductionpathsthatmayexistbetweenthecoreandtheI/Opinsoftheprocessor.. The second most common power on behavior is known as a ratiometric start up. This start up is preferred in applicationswherebothsuppliesneedtobeatthefinalvalueatthesametime. Similar to the Soft-Start function, the fastest start up possible is 1ms regardless of the rise time of the tracking voltage. When using the track feature the final voltage seen by the SS/TRACK pin should exceed 1V to provide sufficientoverdriveandtransientimmunity. Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 19 ProductFolderLinks:LM20145

LM20145 SNVS530E–OCTOBER2007–REVISEDMARCH2013 www.ti.com THERMALCONSIDERATIONS The thermal characteristics of the LM20145 are specified using the parameter θ , which relates the junction JA temperature to the ambient temperature. Although the value of θ is dependant on many variables, it still can be JA usedtoapproximatetheoperatingjunctiontemperatureofthedevice. Toobtainanestimateofthedevicejunctiontemperature,onemayusethefollowingrelationship: T =P θ +T (14) J D JA A and P =P x(1-Efficiency)-1.1xI 2xDC D IN OUT where • T isthejunctiontemperaturein°C J • P istheinputpowerinWatts(P =V xI ) IN IN IN IN • θ isthejunctiontoambientthermalresistancefortheLM20145 JA • T istheambienttemperaturein°C A • I istheoutputloadcurrent OUT • DCRistheinductorseriesresistanceR (15) It is important to always keep the operating junction temperature (T ) below 125°C for reliable operation. If the J junction temperature exceeds 160°C the device will cycle in and out of thermal shutdown. If thermal shutdown occursitisasignofinadequateheatsinkingorexcessivepowerdissipationinthedevice. Figure 33, shown below, provides a better approximation of the θ for a given PCB copper area. The PCB JA heatsink area consists of 2oz. copper located on the bottom layer of the PCB directly under the HTSSOP exposed pad. The bottom copper area is connected to the HTSSOP exposed pad by means of a 4 x 4 array of 12milthermalvias. Figure33. ThermalResistancevsPCBArea 20 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LM20145

LM20145 www.ti.com SNVS530E–OCTOBER2007–REVISEDMARCH2013 PCBLAYOUTCONSIDERATIONS PC board layout is an important part of DC-DC converter design. Poor board layout can disrupt the performance of a DC-DC converter and surrounding circuitry by contributing to EMI, ground bounce, and resistive voltage loss inthetraces.ThesecansenderroneoussignalstotheDC-DCconverterresultinginpoorregulationorinstability. Goodlayoutcanbeimplementedbyfollowingafewsimpledesignrules. 1. Minimize area of switched current loops. In a buck regulator there are two loops where currents are switched very fast. The first loop starts from the input capacitor, to the regulator VIN pin, to the regulator SW pin, to the inductor then out to the output capacitor and load. The second loop starts from the output capacitor ground, to the regulator PGND pins, to the inductor and then out to the load (see Figure 34). To minimize both loop areas the input capacitor should be placed as close as possible to the PVIN pin. Grounding for both the input and output capacitor should consist of a small localized top side plane that connects to PGND and the die attach pad (DAP). The inductor should be placed as close as possible to the SW pin and output capacitor. 2. Minimize the copper area of the switch node. Since the LM20145 has the SW pins on opposite sides of the package it is recommended to via these pins down to the bottom or internal layer with 2 to 4 vias on each SW pin. The SW pins should be directly connected with a trace that runs across the bottom of the package. To minimize IR losses this trace should be no smaller that 50 mils wide, but no larger than 100 mils wide to keepthecopperareatoaminimum.IngeneraltheSWpinsshouldnotbeconnectedonthetoplayersinceit could block the ground return path for the power ground. The inductor should be placed as close as possible tooneoftheSWpinstofurtherminimizethecopperareaoftheswitchnode. 3. Have a single point ground for all device analog grounds located under the DAP. The ground connections for the compensation, feedback, and Soft-Start components should be connected together then routed to the AGND pin of the device. The AGND pin should connect to PGND under the DAP. This prevents any switched or load currents from flowing in the analog ground plane. If not properly handled poor grounding canresultindegradedloadregulationorerraticswitchingbehavior. 4. Minimize trace length to the FB pin. Since the feedback node can be high impedance the trace from the output resistor divider to FB pin should be as short as possible. This is most important when high value resistors are used to set the output voltage. The feedback trace should be routed away from the SW pin and inductortoavoidcontaminatingthefeedbacksignalwithswitchnoise. 5. Make input and output bus connections as wide as possible. This reduces any voltage drops on the input or output of the converter and can improve efficiency. If voltage accuracy at the load is important make sure feedback voltage sense is made at the load. Doing so will correct for voltage drops at the load and provide thebestoutputaccuracy. 6. Provide adequate device heatsinking. Use as many vias as is possible to connect the DAP to the power planeheatsink.Forbestresultsusea4x4viaarraywithaminimumviadiameterof12mils.SeetheThermal Considerations section to insure enough copper heatsinking area is used to keep the junction temperature below125°C. LM20145 L PVIN SW VOUT CIN COUT PGND LOOP1 LOOP2 Figure34. SchematicofLM20145HighlightingLayoutSensitiveNodes Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 21 ProductFolderLinks:LM20145

LM20145 SNVS530E–OCTOBER2007–REVISEDMARCH2013 www.ti.com TypicalApplicationCircuits This section provides several application solutions with a bill of materials. All bill of materials reference the below figure. The compensation for these solutions were optimized to work over a wide range of input and output voltages; if a faster transient response is needed reduce the value of C and calculate the new value for R as C1 C1 outlineinthedesignguide. LM20145 L VIN PVIN SW VOUT CIN RF EN FB RFB1 COUT AVIN CF RT PGOOD RFB2 RT VCC RC1 COMP SS/TRK CVCC PGND AGND CSS CC2 CC1 (optional) Bill of Materials (V = 5V, V = 3.3V, F = 300kHz, I = 5A) IN OUT SW OUTMAX Designator Description PartNumber Manufacturer Qty U1 SynchronousBuckRegulator LM20145 TexasInstruments 1 C 100µF,1210,X5R,6.3V GRM32ER60J107ME20 Murata 1 IN C 330µF,6.3V 6TPE330ML Sanyo 1 OUT L 2.2µH,8.2mΩ IHLP4040DZER2R2M01 Vishay 1 R 1Ω,0603 CRCW06031R0J-e3 Vishay-Dale 1 F C 100nF,0603,X7R,16V GRM188R71C104KA01 Murata 1 F C 1µF,0603,X5R,6.3V GRM188R60J105KA01 Murata 1 VCC R 49.9kΩ,0603 CRCW06034992F-e3 Vishay-Dale 1 C1 C 2.2nF,0603,X7R,25V VJ0603Y222KXXA Vishay-Vitramon 1 C1 C 100pF,0603,COG,50V VJ0603A101KXAA Vishay-Dale 1 C2 C 33nF,0603,X7R,25V VJ0603Y333KXXA Vishay-Vitramon 1 SS R 205kΩ,0603 CRCW06032053F-e3 Vishay-Dale 1 T R 31.6kΩ,0603 CRCW06033162F-e3 Vishay-Dale 1 FB1 R 10.2kΩ,0603 CRCW06031022F-e3 Vishay-Dale 1 FB2 Bill of Materials (V = 3.3V to 5V, V = 1.2V, F = 300kHz, I = 5A) IN OUT SW OUTMAX Designator Description PartNumber Manufacturer Qty U1 SynchronousBuckRegulator LM20145 TexasInstruments 1 C 100µF,1210,X5R,6.3V GRM32ER60J107ME20 Murata 1 IN C 330µF,6.3V 6TPE330ML Sanyo 1 OUT L 2.2µH,8.2mΩ IHLP4040DZER2R2M01 Vishay 1 R 1Ω,0603 CRCW06031R0J-e3 Vishay-Dale 1 F C 100nF,0603,X7R,16V GRM188R71C104KA01 Murata 1 F C 1µF,0603,X5R,6.3V GRM188R60J105KA01 Murata 1 VCC R 20kΩ,0603 CRCW06032002F-e3 Vishay-Dale 1 C1 C 3.3nF,0603,X7R,25V VJ0603Y332KXXA Vishay-Vitramon 1 C1 C 330pF,0603,COG,50V VJ0603A331AKXAA Vishay-Dale 1 C2 C 33nF,0603,X7R,25V VJ0603Y333KXXA Vishay-Vitramon 1 SS R 205kΩ,0603 CRCW06032053F-e3 Vishay-Dale 1 T R 4.99kΩ,0603 CRCW06034991F-e3 Vishay-Dale 1 FB1 R 10kΩ,0603 CRCW06031002F-e3 Vishay-Dale 1 FB2 22 SubmitDocumentationFeedback Copyright©2007–2013,TexasInstrumentsIncorporated ProductFolderLinks:LM20145

LM20145 www.ti.com SNVS530E–OCTOBER2007–REVISEDMARCH2013 REVISION HISTORY ChangesfromRevisionD(March2013)toRevisionE Page • ChangedlayoutofNationalDataSheettoTIformat.......................................................................................................... 22 Copyright©2007–2013,TexasInstrumentsIncorporated SubmitDocumentationFeedback 23 ProductFolderLinks:LM20145

PACKAGE OPTION ADDENDUM www.ti.com 6-Feb-2020 PACKAGING INFORMATION Orderable Device Status Package Type Package Pins Package Eco Plan Lead/Ball Finish MSL Peak Temp Op Temp (°C) Device Marking Samples (1) Drawing Qty (2) (6) (3) (4/5) LM20145MH/NOPB ACTIVE HTSSOP PWP 16 92 Green (RoHS SN Level-1-260C-UNLIM -40 to 125 20145 & no Sb/Br) MH LM20145MHE/NOPB ACTIVE HTSSOP PWP 16 250 Green (RoHS SN Level-1-260C-UNLIM -40 to 125 20145 & no Sb/Br) MH LM20145MHX/NOPB ACTIVE HTSSOP PWP 16 2500 Green (RoHS SN Level-1-260C-UNLIM -40 to 125 20145 & no Sb/Br) MH LM20145QMH/NOPB ACTIVE HTSSOP PWP 16 92 Green (RoHS SN Level-1-260C-UNLIM -40 to 125 20145 & no Sb/Br) QMH LM20145QMHE/NOPB ACTIVE HTSSOP PWP 16 250 Green (RoHS SN Level-1-260C-UNLIM -40 to 125 20145 & no Sb/Br) QMH LM20145QMHX/NOPB ACTIVE HTSSOP PWP 16 2500 Green (RoHS SN Level-1-260C-UNLIM -40 to 125 20145 & no Sb/Br) QMH (1) The marketing status values are defined as follows: ACTIVE: Product device recommended for new designs. LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect. NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design. PREVIEW: Device has been announced but is not in production. Samples may or may not be available. OBSOLETE: TI has discontinued the production of the device. (2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free". RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption. Green: TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement. (3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature. (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device. (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device. Addendum-Page 1

PACKAGE OPTION ADDENDUM www.ti.com 6-Feb-2020 (6) Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width. Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release. In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis. OTHER QUALIFIED VERSIONS OF LM20145, LM20145-Q1 : •Catalog: LM20145 •Automotive: LM20145-Q1 NOTE: Qualified Version Definitions: •Catalog - TI's standard catalog product •Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects Addendum-Page 2

PACKAGE MATERIALS INFORMATION www.ti.com 20-Jul-2019 TAPE AND REEL INFORMATION *Alldimensionsarenominal Device Package Package Pins SPQ Reel Reel A0 B0 K0 P1 W Pin1 Type Drawing Diameter Width (mm) (mm) (mm) (mm) (mm) Quadrant (mm) W1(mm) LM20145MHE/NOPB HTSSOP PWP 16 250 178.0 12.4 6.95 5.6 1.6 8.0 12.0 Q1 LM20145MHX/NOPB HTSSOP PWP 16 2500 330.0 12.4 6.95 5.6 1.6 8.0 12.0 Q1 LM20145QMHE/NOPB HTSSOP PWP 16 250 178.0 12.4 6.95 5.6 1.6 8.0 12.0 Q1 LM20145QMHX/NOPB HTSSOP PWP 16 2500 330.0 12.4 6.95 5.6 1.6 8.0 12.0 Q1 PackMaterials-Page1

PACKAGE MATERIALS INFORMATION www.ti.com 20-Jul-2019 *Alldimensionsarenominal Device PackageType PackageDrawing Pins SPQ Length(mm) Width(mm) Height(mm) LM20145MHE/NOPB HTSSOP PWP 16 250 210.0 185.0 35.0 LM20145MHX/NOPB HTSSOP PWP 16 2500 367.0 367.0 35.0 LM20145QMHE/NOPB HTSSOP PWP 16 250 210.0 185.0 35.0 LM20145QMHX/NOPB HTSSOP PWP 16 2500 367.0 367.0 35.0 PackMaterials-Page2

PACKAGE OUTLINE PWP0016A PowerPAD T M HTSSOP - 1.2 mm max height SCALE 2.400 PLASTIC SMALL OUTLINE C 6.6 TYP SEATING PLANE 6.2 A PIN 1 ID 0.1 C AREA 14X 0.65 16 1 5.1 2X 4.9 4.55 NOTE 3 8 9 0.30 4.5 16X B 0.19 4.3 0.1 C A B (0.15) TYP SEE DETAIL A 4X 0.166 MAX 2X 1.34 MAX NOTE 5 NOTE 5 THERMAL PAD 0.25 3.3 2.7 17 GAGE PLANE 1.2 MAX 0.15 0 - 8 0.05 0.75 0.50 DETAIL A 3.3 (1) TYPICAL 2.7 4214868/A 02/2017 PowerPAD is a trademark of Texas Instruments. NOTES: 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side. 4. Reference JEDEC registration MO-153. 5. Features may not be present. www.ti.com

EXAMPLE BOARD LAYOUT PWP0016A PowerPAD T M HTSSOP - 1.2 mm max height PLASTIC SMALL OUTLINE (3.4) NOTE 9 SOLDER MASK (3.3) DEFINED PAD 16X (1.5) SYMM SEE DETAILS 1 16 16X (0.45) (1.1) SYMM 17 TYP (3.3) (5) NOTE 9 14X (0.65) 8 9 ( 0.2) TYP VIA (1.1) TYP METAL COVERED (5.8) BY SOLDER MASK LAND PATTERN EXAMPLE EXPOSED METAL SHOWN SCALE:10X SOOPLEDNEINRG MASK METAL SMOELTDAELR U MNDAESRK SOOPLEDNEINRG MASK EXPOSED METAL EXPOSED METAL 0.05 MIN 0.05 MAX ALL AROUND ALL AROUND NON SOLDER MASK SOLDER MASK DEFINED DEFINED SOLDER MASK DETAILS PADS 1-16 4214868/A 02/2017 NOTES: (continued) 6. Publication IPC-7351 may have alternate designs. 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site. 8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 (www.ti.com/lit/slma002) and SLMA004 (www.ti.com/lit/slma004). 9. Size of metal pad may vary due to creepage requirement. www.ti.com

EXAMPLE STENCIL DESIGN PWP0016A PowerPAD T M HTSSOP - 1.2 mm max height PLASTIC SMALL OUTLINE (3.3) BASED ON 0.125 THICK 16X (1.5) STENCIL (R0.05) TYP 1 16 16X (0.45) SYMM 17 (3.3) BASED ON 0.125 THICK STENCIL 14X (0.65) 9 8 SYMM METAL COVERED BY SOLDER MASK SEE TABLE FOR DIFFERENT OPENINGS (5.8) FOR OTHER STENCIL THICKNESSES SOLDER PASTE EXAMPLE EXPOSED PAD 100% PRINTED SOLDER COVERAGE BY AREA SCALE:10X STENCIL SOLDER STENCIL THICKNESS OPENING 0.1 3.69 X 3.69 0.125 3.3 X 3.3 (SHOWN) 0.15 3.01 X 3.01 0.175 2.79 X 2.79 4214868/A 02/2017 NOTES: (continued) 10. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations. 11. Board assembly site may have different recommendations for stencil design. www.ti.com

IMPORTANTNOTICEANDDISCLAIMER TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS. These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources. TI’s products are provided subject to TI’s Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI’s provision of these resources does not expand or otherwise alter TI’s applicable warranties or warranty disclaimers for TI products. Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated

Datasheet下载

Datasheet下载