- 型号: JS28F128P30BF75A

- 制造商: Micron Technology Inc

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

JS28F128P30BF75A产品简介:

ICGOO电子元器件商城为您提供JS28F128P30BF75A由Micron Technology Inc设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 JS28F128P30BF75A价格参考¥询价-¥询价。Micron Technology IncJS28F128P30BF75A封装/规格:存储器, FLASH - NOR Memory IC 128Mb (8M x 16) Parallel 40MHz 75ns 56-TSOP。您可以下载JS28F128P30BF75A参考资料、Datasheet数据手册功能说明书,资料中有JS28F128P30BF75A 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC) |

| 描述 | IC FLASH 128MBIT 75NS 56TSOP |

| 产品分类 | |

| 品牌 | Micron Technology Inc |

| 数据手册 | |

| 产品图片 |

|

| 产品型号 | JS28F128P30BF75A |

| rohs | 无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | StrataFlash™ |

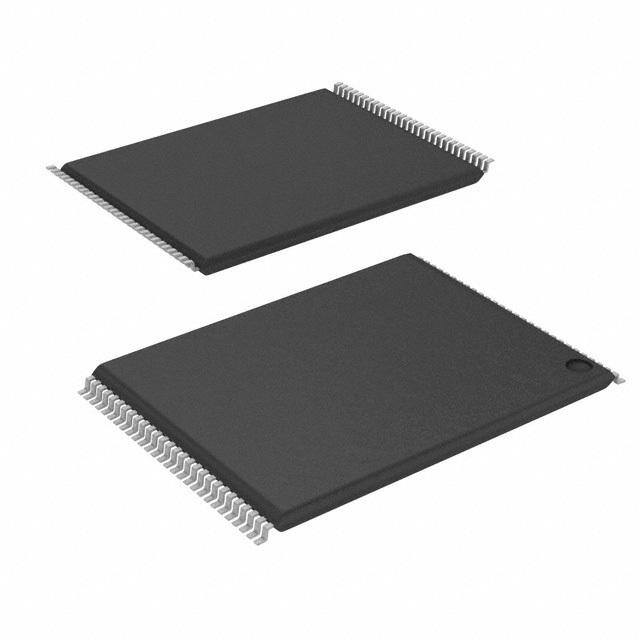

| 供应商器件封装 | 56-TSOP(14x20) |

| 包装 | 托盘 |

| 存储器类型 | FLASH - NOR |

| 存储容量 | 128M (8M x 16) |

| 封装/外壳 | 56-TFSOP(0.724",18.40mm 宽) |

| 工作温度 | -40°C ~ 85°C |

| 接口 | 并联 |

| 标准包装 | 576 |

| 格式-存储器 | 闪存 |

| 电压-电源 | 1.7 V ~ 2 V |

| 速度 | 75ns |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

® Numonyx Axcell™ P30-65nm Flash Memory 128-Mbit, 64-Mbit Single Bit per Cell (SBC) Datasheet Product Features (cid:132) High Performance: (cid:132) Enhanced Security: — 65ns initial access time for Easy BGA and — Absolute write protection: VPP = Vss QUAD+ — Power-transition erase/program lockout — 75ns initial access time for TSOP — Individual zero-latency block locking — 25ns 8-word asynchronous-page read mode — Individual block lock-down capability — 52MHz with zero WAIT states, 17ns clock-to- — Password Access feature data output synchronous-burst read mode — One-Time Programmable Register: — 4-, 8-, 16- and continuous-word options for — 64 OTP bits, programmed with unique burst mode information by Numonyx — 1.8V Low Power buffered programming at — 2112 OTP bits, available for customer 1.8MByte/s (Typ) using 256-word buffer programming — Buffered Enhanced Factory Programming at 3.2MByte/s (typ) using 256-word buffer (cid:132) Software: — 20µs (Typ) program suspend (cid:132) Architecture: — 20µs (Typ) erase suspend — Asymmetrically-blocked architecture — Basic Command Set and Extended Function — Four 32-KByte parameter blocks: top or Interface (EFI) Command Set compatible bottom configuration — Common Flash Interface capable — 128-KByte array blocks — Blank Check to verify an erased block (cid:132) Density and Packaging: — 56-Lead TSOP (128-Mbit, 64-Mbit) (cid:132) Voltage and Power: — 64-Ball Easy BGA (128-Mbit, 64-Mbit) — VCC (core) voltage: 1.7V – 2.0V — 88-Ball QUAD+ Package (128-Mbit) — VCCQ (I/O) voltage: 1.7V – 3.6V — 16-bit wide data bus — Standby current: 30µA(Typ)/55µA(Max) — Continuous synchronous read current: 23mA (cid:132) Quality and Reliability: (Typ)/28mA (Max) at 52MHz — JESD47E Compliant — Operating temperature: –40°C to +85°C — Minimum 100,000 erase cycles — 65nm process technology Datasheet Apr 2010 1 Order Number: 208033-02

LIegNal LFinesO andR DisMclaimAersTION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH NUMONYX™ PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN NUMONYX'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NUMONYX ASSUMES NO LIABILITY WHATSOEVER, AND NUMONYX DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF NUMONYX PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Numonyx products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications. Numonyx may make changes to specifications and product descriptions at any time, without notice. Numonyx, B.V. may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Numonyx reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. Contact your local Numonyx sales office or your distributor to obtain the latest specifications and before placing your product order. Copies of documents which have an order number and are referenced in this document, or other Numonyx literature may be obtained by visiting Numonyx's website at http://www.numonyx.com. Numonyx, the Numonyx logo, and Axcell are trademarks or registered trademarks of Numonyx , B.V. or its subsidiaries in other countries. *Other names and brands may be claimed as the property of others. Copyright © 2010, Numonyx, B.V., All Rights Reserved. Datasheet Apr 2010 2 Order Number: 208033-02

P30-65nm SBC Contents 1.0 Functional Description...............................................................................................5 1.1 Introduction.......................................................................................................5 1.2 Overview ...........................................................................................................5 1.3 Memory Map.......................................................................................................6 2.0 Package Information.................................................................................................7 2.1 56-Lead TSOP.....................................................................................................7 2.2 64-Ball Easy BGA Package....................................................................................8 2.3 QUAD+ SCSP Packages......................................................................................10 3.0 Pinouts/Ballouts .....................................................................................................11 4.0 Signals....................................................................................................................14 5.0 Bus Operations........................................................................................................16 5.1 Read - Asynchronous Mode.................................................................................16 5.2 Read - Synchronous Mode..................................................................................16 5.3 Write...............................................................................................................17 5.4 Output Disable..................................................................................................17 5.5 Standby...........................................................................................................17 5.6 Reset...............................................................................................................18 6.0 Command Set..........................................................................................................19 6.1 Device Command Codes.....................................................................................19 6.2 Device Command Bus Cycles..............................................................................20 7.0 Read Operation........................................................................................................22 7.1 Read Array.......................................................................................................22 7.2 Read Device Identifier........................................................................................22 7.3 Read CFI..........................................................................................................23 7.4 Read Status Register.........................................................................................23 7.5 Clear Status Register.........................................................................................23 8.0 Program Operation..................................................................................................24 8.1 Word Programming ...........................................................................................24 8.2 Buffered Programming.......................................................................................24 8.3 Buffered Enhanced Factory Programming..............................................................25 8.4 Program Suspend..............................................................................................27 8.5 Program Resume...............................................................................................28 8.6 Program Protection............................................................................................28 9.0 Erase Operation.......................................................................................................29 9.1 Block Erase......................................................................................................29 9.2 Blank Check.....................................................................................................29 9.3 Erase Suspend..................................................................................................30 9.4 Erase Resume...................................................................................................30 9.5 Erase Protection................................................................................................30 10.0 Security...................................................................................................................31 10.1 Block Locking....................................................................................................31 10.2 Selectable OTP Blocks........................................................................................33 10.3 Password Access...............................................................................................33 11.0 Register...................................................................................................................34 11.1 Status Register (SR)..........................................................................................34 11.2 Read Configuration Register (RCR)......................................................................34 Datasheet Apr 2010 3 Order Number: 208033-02

P30-65nm SBC 11.3 One-Time Programmable (OTP) Registers.............................................................40 12.0 Power and Reset Specifications ...............................................................................43 12.1 Power-Up and Power-Down.................................................................................43 12.2 Reset Specifications...........................................................................................43 12.3 Power Supply Decoupling....................................................................................44 13.0 Maximum Ratings and Operating Conditions............................................................45 13.1 Absolute Maximum Ratings.................................................................................45 13.2 Operating Conditions..........................................................................................45 14.0 Electrical Specifications...........................................................................................46 14.1 DC Current Characteristics..................................................................................46 14.2 DC Voltage Characteristics..................................................................................47 15.0 AC Characteristics....................................................................................................48 15.1 AC Test Conditions.............................................................................................48 15.2 Capacitance......................................................................................................49 15.3 AC Read Specifications ......................................................................................50 15.4 AC Write Specifications.......................................................................................54 15.5 Program and Erase Characteristics.......................................................................58 16.0 Ordering Information...............................................................................................59 A Supplemental Reference Information.......................................................................61 A.1 Common Flash Interface.....................................................................................61 A.2 Flowcharts........................................................................................................73 A.3 Write State Machine...........................................................................................83 B Conventions - Additional Documentation .................................................................87 B.1 Acronyms.........................................................................................................87 B.2 Definitions and Terms ........................................................................................87 C Revision History.......................................................................................................89 Datasheet Apr 2010 4 Order Number: 208033-02

P30-65nm SBC 1.0 Functional Description 1.1 Introduction This document provides information about the Numonyx® AxcellTM P30-65nm Single Bit per Cell (SBC) Flash memory and describes its features, operations, and specifications. P30-65nm SBC device is offered in 64-Mbit and 128-Mbit. Benefits include high-speed interface NOR device, and support for code and data storage. Features include high- performance synchronous-burst read mode, a dramatical improvement in buffer program time through larger buffer size, fast asynchronous access times, low power, flexible security options, and three industry-standard package choices. P30-65nm SBC device is manufactured using 65nm process technology. 1.2 Overview P30-65nm SBC device provides high performance on a 16-bit data bus. Individually erasable memory blocks are sized for optimum code and data storage. Upon initial power-up or return from reset, the device defaults to asynchronous page-mode read. Configuring the Read Configuration Register (RCR) enables synchronous burst-mode reads. In synchronous burst mode, output data is synchronized with a user-supplied clock signal. A WAIT signal provides easy CPU-to-flash memory synchronization. In addition to the enhanced architecture and interface, the device incorporates technology that enables fast buffer program and erase operations. The device features a 256-word buffer to enable optimum programming performance, which can improve system programming throughput time significantly to 1.8MByte/s. Designed for low-voltage systems, the P30-65nm SBC device supports read operations with VCC at 1.8V, and erase and program operations with VPP at 1.8V or 9.0V. Buffered Enhanced Factory Programming provides the fastest flash array programming performance with VPP at 9.0V, which increases factory throughput with 3.2Mbyte/s. With VPP at 1.8V, VCC and VPP can be tied together for a simple, ultra low power design. In addition to voltage flexibility, a dedicated VPP connection provides complete data protection when VPP ≤ V . PPLK The Command User Interface is the interface between the system processor and all internal operations of the device. An internal Write State Machine automatically executes the algorithms and timings necessary for block erase and program. A Status Register indicates erase or program completion and any errors that may have occurred. A device command sequence invokes program and erase automation. Each erase operation erases one block. The Erase Suspend feature allows system software to pause an erase cycle to read or program data in another block. Program Suspend allows system software to pause programming to read other locations. The OTP Register allows unique flash device identification that can be used to increase system security. The individual Block Lock feature provides zero-latency block locking and unlocking. The P30-65nm SBC device adds enhanced protection via Password Access; this new feature allows write and/or read access protection of user-defined blocks. In addition, the P30-65nm SBC device also has backward-compatible One-Time Programmable (OTP) permanent block locking security feature. Datasheet Apr 2010 5 Order Number:208033-02

P30-65nm SBC 1.3 Memory Map Figure 1: P30-65nm SBC Memory Map (64-Mbit and 128-Mbit Densities) A<23:1> 128-Mbit A<22:1> 64-Mbit 7F0000 –7FFFFF 64-Kword Block 130 3F0000–3FFFFF 64-Kword Block 66 Mbit 020000 –02FFFF 64-Kword Block 5 4-Mbit 128- 6 010000 –01FFFF 64-Kword Block 4 00C000–00FFFF 16-Kword Block 3 008000 –00BFFF 16-Kword Block 2 004000 –007FFF 16-Kword Block 1 000000 –003FFF 16-Kword Block 0 Bottom Boot Word Wide (x16) Mode A<23:1> 128-Mbit 7FC000– 7FFFFF 16-Kword Block 130 7F8000– 7FBFFF 16-Kword Block 129 7F4000– 7F7000 16-Kword Block 128 7F0000 – 7F3FFF 16-Kword Block 127 A<22:1> 64-Mbit 7E0000 – 7EFFFF 64-Kword Block 126 3FC000 – 3FFFFF 16-Kword Block 66 3F8000– 3FBFFF 16-Kword Block 65 3F4000– 3F7FFF 16-Kword Block 64 Mbit 3F0000– 3F3FFF 16-Kword Block 63 8- 3E0000– 3EFFFF 64-Kword Block 62 12 Mbit 64- 010000– 01FFFF 64-Kword Block 1 010000– 01FFFF 64-Kword Block 1 000000– 00FFFF 64-Kword Block 0 000000– 00FFFF 64-Kword Block 0 Top Boot Top Boot Word Wide (x16) Mode Word Wide (x16) Mode Note: A1 is the least significant address bit for TSOP and Easy BGA while A0 for the QUAD+ package. Unless otherwise indicated, for the purpose of brevity, this document will consolidate all discussions to A1 as the least significant Address bit. Datasheet Apr 2010 6 Order Number: 208033-02

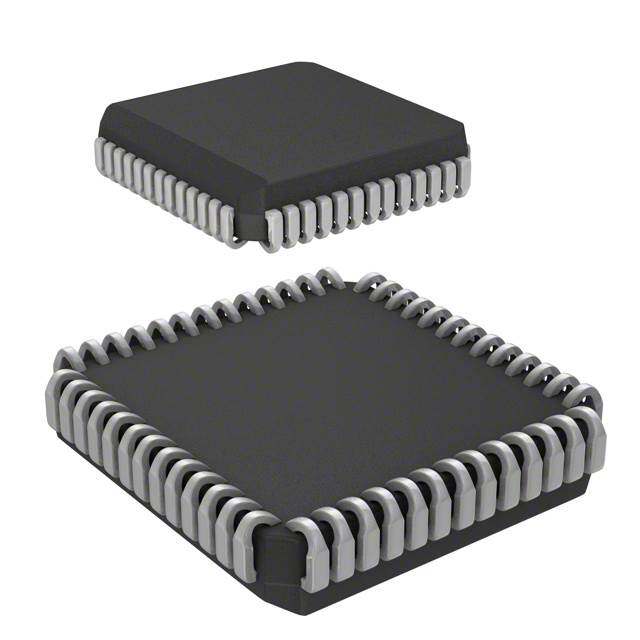

P30-65nm SBC 2.0 Package Information 2.1 56-Lead TSOP Figure 2: TSOP Mechanical Specifications Z See Notes 1 and 3 See Note 2 A2 Pin 1 e E See Detail B Y D1 A1 D Seating Plane See Detail A A Detail A Detail B C 0 b L Table 1: TSOP Package Dimensions (Sheet 1 of 2) Millimeters Inches Product Information Symbol Min Nom Max Min Nom Max Package Height A - - 1.200 - - 0.047 Standoff A1 0.050 - - 0.002 - - Package Body Thickness A2 0.965 0.995 1.025 0.038 0.039 0.040 Lead Width b 0.100 0.150 0.200 0.004 0.006 0.008 Lead Thickness C 0.100 0.150 0.200 0.004 0.006 0.008 Package Body Length D1 18.200 18.400 18.600 0.717 0.724 0.732 Package Body Width E 13.800 14.000 14.200 0.543 0.551 0.559 Lead Pitch e - 0.500 - - 0.0197 - Terminal Dimension D 19.800 20.00 20.200 0.780 0.787 0.795 Lead Tip Length L 0.500 0.600 0.700 0.020 0.024 0.028 Datasheet Apr 2010 7 Order Number:208033-02

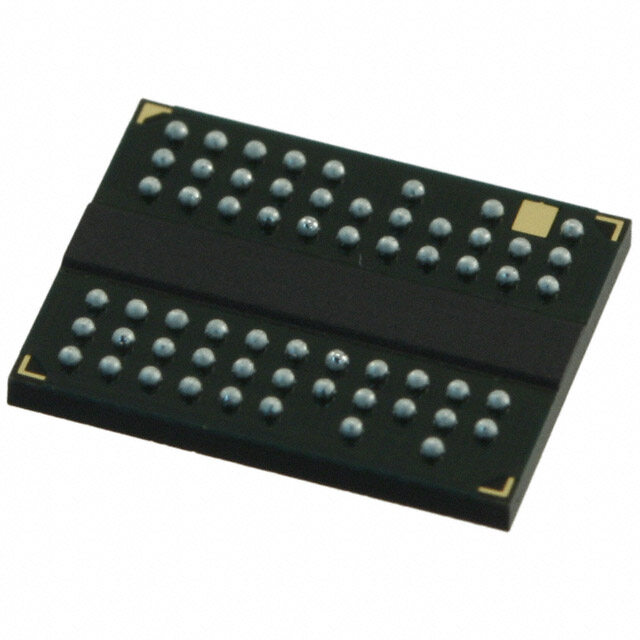

P30-65nm SBC Table 1: TSOP Package Dimensions (Sheet 2 of 2) Millimeters Inches Product Information Symbol Min Nom Max Min Nom Max Lead Count N - 56 - - 56 - Lead Tip Angle θ 0° 3° 5° 0° 3° 5° Seating Plane Coplanarity Y - - 0.100 - - 0.004 Lead to Package Offset Z 0.150 0.250 0.350 0.006 0.010 0.014 Notes: 1. One dimple on package denotes Pin 1. 2. If two dimples, then the larger dimple denotes Pin 1. 3. Pin 1 will always be in the upper left corner of the package, in reference to the product mark. 2.2 64-Ball Easy BGA Package Figure 3: Easy BGA Mechanical Specifications (10x13x1.2 mm) S1 Ball A1 Ball A1 Corner D Corner 1 2 3 4 5 6 7 8 8 7 6 5 4 3 2 1 S2 A A B B C C D D b E E E F F G G e H H Top View -Ball side down Bottom View -Ball Side Up A1 A2 A Seating Y Plane Note: Drawing not to scale Table 2: Easy BGA Package Dimensions for 10x13x1.2 mm (Sheet 1 of 2) Millimeters Inches Product Information Symbol Min Nom Max Min Nom Max Package Height A - - 1.200 - - 0.0472 Ball Height A1 0.250 - - 0.0098 - - Package Body Thickness A2 - 0.780 - - 0.0307 - Ball (Lead) Width b 0.310 0.410 0.510 0.0120 0.0160 0.0200 Package Body Width D 9.900 10.000 10.100 0.3898 0.3937 0.3976 Datasheet Apr 2010 8 Order Number: 208033-02

P30-65nm SBC Table 2: Easy BGA Package Dimensions for 10x13x1.2 mm (Sheet 2 of 2) Millimeters Inches Product Information Symbol Min Nom Max Min Nom Max Package Body Length E 12.900 13.000 13.100 0.5079 0.5118 0.5157 Pitch e - 1.000 - - 0.0394 - Ball (Lead) Count N - 64 - - 64 - Seating Plane Coplanarity Y - - 0.100 - - 0.0039 Corner to Ball A1 Distance Along D S1 1.400 1.500 1.600 0.0551 0.0591 0.0630 Corner to Ball A1 Distance Along E S2 2.900 3.000 3.100 0.1142 0.1181 0.1220 Note: Daisy Chain Evaluation Unit information is at Numonyx™ Flash Memory Packaging Technology http:// developer.Numonyx.com/design/flash/packtech. Datasheet Apr 2010 9 Order Number:208033-02

P30-65nm SBC 2.3 QUAD+ SCSP Packages Figure 4: 128-Mbit, 88-ball (80 active) QUAD+ SCSP Specifications (8x10x1.2 mm) A1 Index S Mark 1 1 2 3 4 5 6 7 8 8 7 6 5 4 3 2 1 S A A 2 B B C C D D E E F F D e G G H H J J K K L L M M b E Top View -Ball Bottom View -Ball Up Down A 2 A1 A Y Drawing not to scale. Millimeters Inches Dimensions Symbol Min Nom Max Min Nom Max Package Height A - - 1.200 - - 0.0472 Ball Height A1 0.200 - - 0.0079 - - Package Body Thickness A2 - 0.860 - - 0.0339 - Ball (Lead) Width b 0.325 0.375 0.425 0.0128 0.0148 0.0167 Package Body Width D 9.900 10.000 10.100 0.3898 0.3937 0.3976 Package Body Length E 7.900 8.000 8.100 0.3110 0.3150 0.3189 Pitch e - 0.800 - - 0.0315 - Ball (Lead) Count N - 88 - - 88 - Seating Plane Coplanarity Y - - 0.100 - - 0.0039 Corner to Ball A1 Distance Along E S1 1.100 1.200 1.300 0.0433 0.0472 0.0512 Corner to Ball A1 Distance Along D S2 0.500 0.600 0.700 0.0197 0.0236 0.0276 Datasheet Apr 2010 10 Order Number: 208033-02

P30-65nm SBC 3.0 Pinouts/Ballouts Figure 5: 56-Lead TSOP Pinout (64-Mbit and 128-Mbit Densities) A16 1 56 WAIT A15 2 55 A17 A14 3 54 DQ15 A13 4 53 DQ7 A12 5 52 DQ14 A11 6 51 DQ6 A10 7 50 DQ13 A9 8 49 DQ5 A23 9 48 DQ12 A22 10 47 DQ4 A21 11 46 ADV# VSS 12 45 CLK NC 13 56-Lead TSOP Pinout 44 RST# WE# 14 14 mm x 20 mm 43 VPP WP# 15 42 DQ11 A20 16 Top View 41 DQ3 A19 17 40 DQ10 A18 18 39 DQ2 A8 19 38 VCCQ A7 20 37 DQ9 A6 21 36 DQ1 A5 22 35 DQ8 A4 23 34 DQ0 A3 24 33 VCC A2 25 32 OE# RFU 26 31 VSS RFU 27 30 CE# VSS 28 29 A1 Notes: 1. A1 is the least significant address bit. 2. A23 is valid for 128-Mbit densities; otherwise, it is a no connect (NC). 3. A22 is valid for 64-Mbit densities and above; otherwise, it is a no connect (NC). 4. No Internal Connection on Pin 13; it may be driven or floated. For legacy 130nm designs, this pin can be tied to Vcc. 5. One dimple on package denotes Pin 1 which will always be in the upper left corner of the package, in reference to the product mark. Datasheet Apr 2010 11 Order Number:208033-02

P30-65nm SBC Figure 6: 64-Ball Easy BGA Ballout (64-Mbit and 128-Mbit Densities) 1 2 3 4 5 6 7 8 8 7 6 5 4 3 2 1 A A A1 A6 A8 VPP A13 VCC A18 A22 A22 A18 VCC A13 VPP A8 A6 A1 B B A2 VSS A9 CE# A14 RFU A19 RFU RFU A19 RFU A14 CE# A9 VSS A2 C C A3 A7 A10 A12 A15 WP# A20 A21 A21 A20 WP# A15 A12 A10 A7 A3 D D A4 A5 A11 RST#VCCQVCCQ A16 A17 A17 A16 VCCQVCCQRST# A11 A5 A4 E E DQ8 DQ1 DQ9 DQ3 DQ4 CLK DQ15 RFU RFU DQ15 CLK DQ4 DQ3 DQ9 DQ1 DQ8 F F RFU DQ0 DQ10DQ11DQ12 ADV# WAIT OE# OE# WAIT ADV#DQ12DQ11 DQ10 DQ0 RFU G G A23 RFU DQ2 VCCQ DQ5 DQ6 DQ14 WE# WE# DQ14 DQ6 DQ5 VCCQ DQ2 RFU A23 H H RFU VSS VCC VSS DQ13 VSS DQ7 RFU RFU DQ7 VSS DQ13 VSS VCC VSS RFU Easy BGA Easy BGA Top View-Ball side down Bottom View-Ball side up Notes: 1. A1 is the least significant address bit. 2. A23 is valid for 128-Mbit densities; otherwise, it is a no connect. 3. A22 is valid for 64-Mbit densities and above; otherwise, it is a no connect (NC). 4. One dimple on package denotes Pin 1 which will always be in the upper left corner of the package, in reference to the product mark. Datasheet Apr 2010 12 Order Number: 208033-02

P30-65nm SBC Figure 7: QUAD+ SCSP Ballout and Signals (128-Mbit) Pin 1 1 2 3 4 5 6 7 8 A DU DU Depop Depop Depop Depop DU DU A B A4 A18 A19 VSS VCC VCC A21 A11 B C A5 RFU RFU VSS RFU CLK A22 A12 C D A3 A17 RFU VPP RFU RFU A9 A13 D E A2 A7 RFU WP# ADV# A20 A10 A15 E F A1 A6 RFU RST# WE# A8 A14 A16 F G A0 DQ8 DQ2 DQ10 DQ5 DQ13 WAIT F2-CE# G H RFU DQ0 DQ1 DQ3 DQ12 DQ14 DQ7 F2-OE# H J RFU F1-OE# DQ9 DQ11 DQ4 DQ6 DQ15 VCCQ J K F1-CE# RFU RFU RFU RFU VCC VCCQ RFU K L VSS VSS VCCQ VCC VSS VSS VSS VSS L M DU DU Depop Depop Depop Depop DU DU M 1 2 3 4 5 6 7 8 Top View -Ball Side Down Control Signals De-Populated Ball Address Legends: Reserved for Future Use Data Do Not Use Power/Ground Notes: 1. A22 is valid for 128-Mbit densities; otherwise, it is a no connect (NC). 2. A21 is valid for 64-Mbit densities and above; otherwise, it is a no connect (NC). 3. F2-CE# and F2-OE# are no connect (NC) for all densities. 4. Unlike TSOP and Easy BGA, A0 is the least significant address bit for the QUAD+ package. Unless otherwise indicated, for the purpose of brevity, this document will consolidate all later discussions to A1 as the least significant Address bit. Datasheet Apr 2010 13 Order Number:208033-02

P30-65nm SBC 4.0 Signals Table 3: TSOP and Easy BGA Signal Descriptions Symbol Type Name and Function A[MAX:1] Input ADDRESS INPUTS: Device address inputs. 128-Mbit: A[23:1], 64-Mbit: A[22:1]. DATA INPUT/OUTPUTS: Inputs data and commands during write cycles; outputs data during Input/ DQ[15:0] reads of memory, Status Register, OTP Register, and Read Configuration Register. Data balls float Output when the CE# or OE# are deasserted. Data is internally latched during writes. ADDRESS VALID: Active low input. During synchronous read operations, addresses are latched on the rising edge of ADV#, or on the next valid CLK edge with ADV# low, whichever occurs first. ADV# Input In asynchronous mode, the address is latched when ADV# going high or continuously flows through if ADV# is held low. WARNING: Designs not using ADV# must tie it to VSS to allow addresses to flow through. CHIP ENABLE: Active low input. CE# low selects the associated flash memory die. When asserted, flash internal control logic, input buffers, decoders, and sense amplifiers are active. When CE# Input deasserted, the associated flash die is deselected, power is reduced to standby levels, data and WAIT outputs are placed in high-Z state. WARNING: Chip Enable must be high when device is not in use. CLOCK: Synchronizes the device with the system’s bus frequency in synchronous-read mode. During synchronous read operations, addresses are latched on the rising edge of ADV#, or on the CLK Input next valid CLK edge with ADV# low, whichever occurs first. WARNING: Designs not using CLK for synchronous read mode must tie it to VCCQ or VSS. OUTPUT ENABLE: Active low input. OE# low enables the device’s output data buffers during read OE# Input cycles. OE# high places the data outputs and WAIT in High-Z. RESET: Active low input. RST# resets internal automation and inhibits write operations. This RST# Input provides data protection during power transitions. RST# high enables normal operation. Exit from reset places the device in asynchronous read array mode. WAIT: Indicates data valid in synchronous array or non-array burst reads. RCR.10, (WT) determines its polarity when asserted. WAIT’s active output is VOL or VOH when CE# and OE# are VIL. WAIT is high-Z if CE# or OE# is VIH. WAIT Output • In synchronous array or non-array read modes, WAIT indicates in valid data when asserted and valid data when deasserted. • In asynchronous page mode, and all write modes, WAIT is deasserted. WRITE ENABLE: Active low input. WE# controls writes to the device. Address and data are latched WE# Input on the rising edge of WE#. WRITE PROTECT: Active low input. WP# low enables the lock-down mechanism. Blocks in lock- WP# Input down cannot be unlocked with the Unlock command. WP# high overrides the lock-down function enabling blocks to be erased or programmed using software commands. ERASE AND PROGRAM POWER: A valid voltage on this pin allows erasing or programming. Memory contents cannot be altered when VPP ≤ VPPLK. Block erase and program at invalid VPP voltages should not be attempted. Power/ Set VPP = VPPL for in-system program and erase operations. To accommodate resistor or diode drops VPP Input from the system supply, the VIH level of VPP can be as low as VPPL min. VPP must remain above VPPL min to perform in-system flash modification. VPP may be 0 V during read operations. VPPH can be applied to array blocks for 1000 cycles maximum and to parameter blocks for 2500. VPP can be connected to 9V for a cumulative total not to exceed 80 hours. Extended use of this pin at 9V may reduce block cycling capability. DEVICE CORE POWER SUPPLY: Core (logic) source voltage. Writes to the flash array are inhibited VCC Power when VCC ≤ VLKO. Operations at invalid VCC voltages should not be attempted. VCCQ Power OUTPUT POWER SUPPLY: Output-driver source voltage. VSS Power GROUND: Connect to system ground. Do not float any VSS connection. RESERVED FOR FUTURE USE: Reserved by Numonyx for future device functionality and RFU — enhancement. These should be treated in the same way as a Don’t Use (DU) signal. DU — DON’T USE: Do not connect to any other signal, or power supply; must be left floating. NC — NO CONNECT: No internal connection; can be driven or floated. Datasheet Apr 2010 14 Order Number: 208033-02

P30-65nm SBC Table 4: QUAD+ SCSP Signal Descriptions Symbol Type Name and Function ADDRESS INPUTS: Device address inputs. 128-Mbit: A[22:0]. A[MAX:0] Input Note: Unlike TSOP and Easy BGA, A0 is the least significant address bit for the QUAD+ package. Unless otherwise indicated, for the purpose of brevity, this document will consolidate all discussions to A1 as the least significant Address bit. DATA INPUT/OUTPUTS: Inputs data and commands during write cycles; outputs data during Input/ DQ[15:0] memory, Status Register, Protection Register, and Read Configuration Register reads. Data balls float Output when the CE# or OE# are deasserted. Data is internally latched during writes. ADDRESS VALID: Active low input. During synchronous read operations, addresses are latched on the rising edge of ADV#, or on the next valid CLK edge with ADV# low, whichever occurs first. ADV# Input In asynchronous mode, the address is latched when ADV# going high or continuously flows through if ADV# is held low. WARNING: Designs not using ADV# must tie it to VSS to allow addresses to flow through. Flash CHIP ENABLE: Active low input. F1-CE# low selects the associated flash memory die. When asserted, flash internal control logic, input buffers, decoders, and sense amplifiers are active. When F1-CE# Input deasserted, the associated flash die is deselected, power is reduced to standby levels, data and WAIT outputs are placed in high-Z state. WARNING: Chip enable must be driven high when device is not in use. CLOCK: Synchronizes the device with the system’s bus frequency in synchronous-read mode. During synchronous read operations, addresses are latched on the rising edge of ADV#, or on the CLK Input next valid CLK edge with ADV# low, whichever occurs first. WARNING: Designs not using CLK for synchronous read mode must tie it to VCCQ or VSS. OUTPUT ENABLE: Active low input. F1-OE# low enables the device’s output data buffers during F1-OE# Input read cycles. F1-OE# high places the data outputs and WAIT in High-Z. RESET: Active low input. RST# resets internal automation and inhibits write operations. This RST# Input provides data protection during power transitions. RST# high enables normal operation. Exit from reset places the device in asynchronous read array mode. WAIT: Indicates data valid in synchronous array or non-array burst reads. Read Configuration Register bit 10 (RCR.10, WT) determines its polarity when asserted. WAIT’s active output is VOL or VOH when F1-CE# and F1-OE# are VIL. WAIT is high-Z if F1-CE# or F1-OE# is VIH. WAIT Output • In synchronous array or non-array read modes, WAIT indicates invalid data when asserted and valid data when deasserted. • In asynchronous page mode, and all write modes, WAIT is deasserted. WRITE ENABLE: Active low input. WE# controls writes to the device. Address and data are latched WE# Input on the rising edge of WE#. WRITE PROTECT: Active low input. WP# low enables the lock-down mechanism. Blocks in lock- WP# Input down cannot be unlocked with the Unlock command. WP# high overrides the lock-down function enabling blocks to be erased or programmed using software commands. ERASE AND PROGRAM POWER: A valid voltage on this pin allows erasing or programming. Memory contents cannot be altered when VPP ≤ VPPLK. Block erase and program at invalid VPP voltages should not be attempted. Power/ Set VPP = VPPL for in-system program and erase operations. To accommodate resistor or diode drops VPP lnput from the system supply, the VIH level of VPP can be as low as VPPL min. VPP must remain above VPPL min to perform in-system flash modification. VPP may be 0 V during read operations. VPPH can be applied to main blocks for 1000 cycles maximum and to parameter blocks for 2500 cycles. VPP can be connected to 9V for a cumulative total not to exceed 80 hours. Extended use of this pin at 9V may reduce block cycling capability. DEVICE CORE POWER SUPPLY: Core (logic) source voltage. Writes to the flash array are inhibited VCC Power when VCC ≤ VLKO. Operations at invalid VCC voltages should not be attempted. VCCQ Power OUTPUT POWER SUPPLY: Output-driver source voltage. VSS Power GROUND: Connect to system ground. Do not float any VSS connection. RESERVED FOR FUTURE USE: Reserved by Numonyx for future device functionality and RFU — enhancement. These should be treated in the same way as a Do Not Use (DU) signal. DU — DO NOT USE: Do not connect to any other signal, or power supply; must be left floating. NC — NO CONNECT: No internal connection; can be driven or floated. Datasheet Apr 2010 15 Order Number:208033-02

P30-65nm SBC 5.0 Bus Operations CE# low and RST# high enable device read operations. The device internally decodes upper address inputs to determine the accessed block. ADV# low opens the internal address latches. OE# low activates the outputs and gates selected data onto the I/O bus. Bus cycles to/from the P30-65nm SBC device conform to standard microprocessor bus operations. Table 5, “Bus Operations Summary” summarizes the bus operations and the logic levels that must be applied to the device control signal inputs. Table 5: Bus Operations Summary Bus Operation RST# CLK ADV# CE# OE# WE# WAIT DQ[15:0] Notes Asynchronous VIH X L L L H Deasserted Output 2 Read Synchronous VIH Running L L L H Driven Output - Write VIH X L L H L High-Z Input 1,2 Output Disable VIH X X L H H High-Z High-Z 2 Standby VIH X X H X X High-Z High-Z 2 Reset VIL X X X X X High-Z High-Z 2,3 Notes: 1. Refer to the Table 7, “Command Bus Cycles” on page 21 for valid DQ[15:0] during a write operation. 2. X = Don’t Care (H or L). 3. RST# must be at VSS ± 0.2V to meet the maximum specified power-down current. 5.1 Read - Asynchronous Mode To perform an asynchronous page or single word read, an address is driven onto the address bus, and CE# is asserted. ADV# can be driven high to latch the address, or it must be held low throughout the read cycle. WE# and RST# must already have been deasserted. WAIT is set to a deasserted state during asynchronous page mode and single word mode as determined by RCR.10. CLK is not used for asynchronous page- mode reads, and is ignored. After OE# is asserted, the data is driven onto DQ[15:0] after an initial access time t or t delay. (See Table 25, “AC Read Specifications” AVQV GLQV on page 50). Note: If only asynchronous reads are to be performed, CLK should be tied to a valid V level, IH WAIT signal can be floated and ADV# must be tied to ground. In asynchronous page mode, eight data words are “sensed” simultaneously from the flash memory array and loaded into an internal page buffer. The buffer word corresponding to the initial address on the Address bus is driven onto DQ[15:0] after the initial access delay. The lowest three address bits determine which word of the 8-word page is output from the data buffer at any given time. Refer to the following waveforms for more detailed information:Figure 19, “Asynchronous Single-Word Read (ADV# Low)” on page 51, and Figure 20, “Asynchronous Single-Word Read (ADV# Latch)” on page 52, and Figure 21, “Asynchronous Page-Mode Read Timing” on page 52. 5.2 Read - Synchronous Mode To perform a synchronous burst read on array or non-array, an initial address is driven onto the address bus, and CE# is asserted. WE# and RST# must already have been deasserted. ADV# is asserted, and then deasserted to latch the address. Alternately, Datasheet Apr 2010 16 Order Number: 208033-02

P30-65nm SBC ADV# can remain asserted throughout the burst access, in which case the address is latched on the next valid CLK edge while ADV# is asserted. Once OE# is asserted, the the first word is driven onto DQ[15:0] on the next valid CLK edge after initial access latency delay (see Section 11.2.2, “Latency Count (RCR[13:11])” on page 36). Subsequent data is output on valid CLK edges following a minimum delay T (see CHQV Table 25, “AC Read Specifications” on page 50). However, for a synchronous non-array read, the same word of data will be output on successive clock edges until the burst length requirements are satisfied. The WAIT signal indicates data valid when the device is operating in synchronous mode (RCR.15=0). The WAIT signal is only “deasserted” when data is valid on the bus. When the device is operating in synchronous non-array read mode, such as read status, read ID, or read query, the WAIT signal is also “deasserted” when data is valid on the bus. WAIT behavior during synchronous non-array reads at the end of word line works correctly only on the first data access. Refer to the following waveforms for more detailed information: Figure 22, “Synchronous Single-Word Array or Non-array Read Timing” on page 53, and Figure 23, “Continuous Burst Read, showing an Output Delay Timing” on page 53, and Figure 24, “Synchronous Burst-Mode Four-Word Read Timing” on page 54. 5.3 Write To perform a write operation, both CE# and WE# are asserted while RST# and OE# are deasserted. During a write operation, address and data are latched on the rising edge of WE# or CE#, whichever occurs first. Table 7, “Command Bus Cycles” on page 21 shows the bus cycle sequence for each of the supported device commands, while Table 6, “Command Codes and Definitions” on page 19 describes each command. See Table 26, “AC Write Specifications” on page 54 for signal-timing details. When the device is operating in write operations, WAIT is set to a deasserted state as determined by RCR.10. Note: Write operations with invalid VCC and/or VPP voltages can produce spurious results and should not be attempted. 5.4 Output Disable When OE# is deasserted, device outputs DQ[15:0] are disabled and placed in a high- impedance (High-Z) state, WAIT is also placed in High-Z. 5.5 Standby When CE# is deasserted the device is deselected and placed in standby, substantially reducing power consumption. In standby, the data outputs are placed in High-Z, independent of the level placed on OE#. Standby current, I , is the average current CCS measured over any 5ms time interval, 5μs after CE# is deasserted. During standby, average current is measured over the same time interval 5μs after CE# is deasserted. When the device is deselected (while CE# is deasserted) during a program or erase operation, it continues to consume active power until the program or erase operation is completed. Datasheet Apr 2010 17 Order Number:208033-02

P30-65nm SBC 5.6 Reset As with any automated device, it is important to assert RST# when the system is reset. When the system comes out of reset, the system processor attempts to read from the flash memory if it is the system boot device. If a CPU reset occurs with no flash memory reset, improper CPU initialization may occur because the flash memory may be providing status information rather than array data. Flash memory devices from NumonyxTM allow proper CPU initialization following a system reset through the use of the RST# input. After initial power-up or reset, the device defaults to asynchronous Read Array mode, and the Status Register is set to 0x80. When RST# is driven low (RST# asserted), the flash device enters reset mode. Then all internal circuits are de-energized, and the output drivers are placed in High-Z. If RST# is asserted during a program or erase operation, the operation is terminated and the memory contents at the aborted location (for a program) or block (for an erase) are no longer valid. A device reset also clears the Status Register. See Table 18, “Power and Reset” on page 43 for RST# timing detail. When RST# is driven high (RST# deasserted), a minimum wait is required before the flash device is able to perform normal operations. Please consider T (R5) and PHQV T (W1) during system design. see Table 25, “AC Read Specifications” on page 50. PHWL and Section 26, “AC Write Specifications” on page 54. After this wake-up interval passes, normal operation is ready for execution. Datasheet Apr 2010 18 Order Number: 208033-02

P30-65nm SBC 6.0 Command Set 6.1 Device Command Codes The flash Command User Interface (CUI) provides access to device read, write, and erase operations. The CUI does not occupy an addressable memory location; it is part of the internal logic which allows the flash device to be controlled. The Write State Machine provides the management for its internal erase and program algorithms. Commands are written to the CUI to control flash device operations. Table 6, “Command Codes and Definitions” describes all valid command codes. For operations that involve multiple command cycles, the possibility exists that the subsequent command does not get issued in the proper sequence. When this happens, the CUI sets Status Register bits SR[5,4] to indicate a command sequence error. Table 6: Command Codes and Definitions (Sheet 1 of 2) Mode Code Device Mode Description 0xFF Read Array Places the device in Read Array mode. Array data is output on DQ[15:0]. Read Status Places the device in Read Status Register mode. The device enters this mode 0x70 Register after a program or erase command is issued. SR data is output on DQ[7:0]. Read Device ID Places device in Read Device Identifier mode. Subsequent reads output or Read 0x90 manufacturer/device codes, Configuration Register data, Block Lock status, Read Configuration or OTP Register data on DQ[15:0]. Register (RCR) Places the device in Read Query mode. Subsequent reads output Common 0x98 Read CFI Flash Interface (CFI) information on DQ[7:0]. Clear Status The WSM can only set SR error bits. The Clear Status Register command is 0x50 Register used to clear the SR error bits. First cycle of a 2-cycle programming command; prepares the CUI for a write operation. On the next write cycle, the address and data are latched and the WSM executes the programming algorithm at the addressed location. During Word Program program operations, the device responds only to Read Status Register and 0x40 Setup Program Suspend commands. CE# or OE# must be toggled to update the Status Register in asynchronous read. CE# or ADV# must be toggled to update the SR Data for synchronous Non-array reads. The Read Array command must be issued to read array data after programming has finished. This command loads a variable number of words up to the buffer size of 256 0xE8 Buffered Program Write words onto the program buffer. The confirm command is issued after the data streaming for writing into the Buffered Program 0xD0 buffer is done. This instructs the WSM to perform the Buffered Program Confirm algorithm, writing the data from the buffer to the flash memory array. First cycle of a 2-cycle command; initiates the BEFP mode. The CUI then 0x80 BEFP Setup waits for the BEFP Confirm command, 0xD0, that initiates the BEFP algorithm. All other commands are ignored when BEFP mode begins. If the previous command was BEFP Setup (0x80), the CUI latches the 0xD0 BEFP Confirm address and data, and prepares the device for BEFP mode. First cycle of a 2-cycle command; prepares the CUI for a block-erase 0x20 Block Erase Setup operation. The WSM performs the erase algorithm on the block addressed by the Erase Confirm command. If the first command was Block Erase Setup (0x20), the CUI latches the Erase address and data, and the WSM erases the addressed block. During block- erase operations, the device responds only to Read Status Register and Erase 0xD0 Block Erase Confirm Suspend commands. CE# or OE# must be toggled to update the Status Register in asynchronous read. CE# or ADV# must be toggled to update the SR Data for synchronous Non-array reads. Datasheet Apr 2010 19 Order Number:208033-02

P30-65nm SBC Table 6: Command Codes and Definitions (Sheet 2 of 2) Mode Code Device Mode Description This command issued to any device address initiates a suspend of the currently-executing program or block erase operation. The Status Register Program or Erase indicates successful suspend operation by setting either SR.2 (program 0xB0 Suspend suspended) or SR.6 (erase suspended), along with SR.7 (ready). The WSM Suspend remains in the suspend mode regardless of control signal states (except for RST# asserted). This command issued to any device address resumes the suspended program 0xD0 Suspend Resume or block-erase operation. First cycle of a 2-cycle command; prepares the CUI for block lock 0x60 Block Lock Setup configuration changes. If the previous command was Block Lock Setup (0x60), the addressed block 0x01 Block Lock is locked. If the previous command was Block Lock Setup (0x60), the addressed block 0xD0 Block Unlock is unlocked. If the addressed block is in a lock-down state, the operation has Protection no effect. If the previous command was Block Lock Setup (0x60), the addressed block 0x2F Block Lock-Down is locked down. First cycle of a 2-cycle command; prepares the device for a OTP Register or OTP Register or Lock Register program operation. The second cycle latches the register 0xC0 Lock Register address and data, and starts the programming algorithm to program data program setup into the OTP array. Read Configuration First cycle of a 2-cycle command; prepares the CUI for device read 0x60 Register Setup configuration. Configuration If the previous command was Read Configuration Register Setup (0x60), the Read Configuration CUI latches the address and writes A[16:1] to the Read Configuration 0x03 Register Register. Following a Configure RCR command, subsequent read operations access array data. First cycle of a 2-cycle command; initiates the Blank Check operation on a 0xBC Block Blank Check array block. Blank Check Block Blank Check Second cycle of blank check command sequence; it latches the block address 0xD0 Confirm and executes blank check on the array block. This command is used in extended function interface. first cycle of a multiple- cycle command second cycle is a Sub-Op-Code, the data written on third Extended Function EFI 0xEB cycle is one less than the word count; the allowable value on this cycle are 0 Interface through 511. The subsequent cycles load data words into the program buffer at a specified address until word count is achieved. 6.2 Device Command Bus Cycles Device operations are initiated by writing specific device commands to the CUI. See Table 7, “Command Bus Cycles” on page 21. Several commands are used to modify array data including Word Program and Block Erase commands. Writing either command to the CUI initiates a sequence of internally-timed functions that culminate in the completion of the requested task. However, the operation can be aborted by either asserting RST# or by issuing an appropriate suspend command. Datasheet Apr 2010 20 Order Number: 208033-02

P30-65nm SBC Table 7: Command Bus Cycles First Bus Cycle Second Bus Cycle Bus Mode Command Cycles Oper Addr(1) Data(2) Oper Addr(1) Data(2) Read Array 1 Write DnA 0xFF - - - Read Device Identifier ≥ 2 Write DnA 0x90 Read DBA + IA ID Read Read CFI ≥ 2 Write DnA 0x98 Read DBA + CFI-A CFI-D Read Status Register 2 Write DnA 0x70 Read DnA SRD Clear Status Register 1 Write DnA 0x50 - - - Word Program 2 Write WA 0x40 Write WA WD Buffered Program(3) > 2 Write WA 0xE8 Write WA N - 1 Program Buffered Enhanced Factory Program > 2 Write WA 0x80 Write WA 0xD0 (BEFP)(4) Erase Block Erase 2 Write BA 0x20 Write BA 0xD0 Program/Erase 1 Write DnA 0xB0 - - - Suspend Suspend Program/Erase 1 Write DnA 0xD0 - - - Resume Block Lock 2 Write BA 0x60 Write BA 0x01 Block Unlock 2 Write BA 0x60 Write BA 0xD0 Protection Block Lock-down 2 Write BA 0x60 Write BA 0x2F Program OTP Register 2 Write OTP-RA 0xC0 Write OTP-RA OTP-D Program Lock Register 2 Write LRA 0xC0 Write LRA LRD Configure Read Configuration 2 Write RCD 0x60 Write RCD 0x03 Configuration Register Blank Check Block Blank Check 2 Write BA 0xBC Write BA D0 Extended Function Sub-Op EFI Interface(5) >2 Write WA 0xEB Write WA code Notes: 1. First command cycle address should be the same as the operation’s target address. DBA = Device Base Address. DnA = Address within the device. IA = Identification code address offset. CFI-A = Read CFI address offset. WA = Word address of memory location to be written. BA = Address within the block. OTP-RA = OTP Register address. LRA = Lock Register address. RCD = Read Configuration Register data on A[16:1] for TSOP and BGA package; on A[15:0] for QUAD+ package. 2. ID = Identifier data. CFI-D = CFI data on DQ[15:0]. SRD = Status Register data. WD = Word data. N = Word count of data to be loaded into the write buffer. OTP-D = OTP Register data. LRD = Lock Register data. 3. The second cycle of the Buffered Program Command is the word count of the data to be loaded into the write buffer. This is followed by up to 256 words of data. Then the confirm command (0xD0) is issued, triggering the array programming operation. 4. The confirm command (0xD0) is followed by the buffer data. 5. The second cycle is a Sub-Op-Code, the data written on third cycle is N-1; 1 ≤ N ≤ 256. The subsequent cycles load data words into the program buffer at a specified address until word count is achieved. After the data words are loaded, the final cycle is the confirm cycle 0xD0). Datasheet Apr 2010 21 Order Number:208033-02

P30-65nm SBC 7.0 Read Operation The device can be in any of four read states: Read Array, Read Identifier, Read Status or Read Query. Upon power-up or after a reset, the device defaults to Read Array mode. To change the read state, the appropriate read command must be written to the device (see Section 6.2, “Device Command Bus Cycles” on page 20). The following sections describe read-mode operations in detail. In order to enable synchronous burst reads, the RCR must be configured. Please see Section 11.2, “Read Configuration Register (RCR)” on page 34 for RCR detail. Please refer to Section 5.1, “Read - Asynchronous Mode” on page 16 and Section 5.2, “Read - Synchronous Mode” on page 16 for bus operation detail. See Section 25, “AC Read Specifications” on page 50 for timing specification. 7.1 Read Array Following a device power-up or reset, the device is set to Read Array mode. However, to perform array reads after any other device operation (e.g. write operation), the Read Array command must be issued in order to read from the flash memory array. Please refer to Section 5.1, “Read - Asynchronous Mode” on page 16 and Section 5.2, “Read - Synchronous Mode” on page 16 for bus operation detail. See Section 25, “AC Read Specifications” on page 50 for timing specification. 7.2 Read Device Identifier The Read Device Identifier command instructs the device to output manufacturer code, device identifier code, block-lock status, OTP Register data, or Read Configuration Register data (see Section 6.2, “Device Command Bus Cycles” on page 20 for details on issuing the Read Device Identifier command). Table 8, “Device Identifier Information” on page 22 and Table 9, “Device ID codes” on page 23 show the address offsets and data values for this device. Table 8: Device Identifier Information (Sheet 1 of 2) Item Address(1,2) Data(x16) Manufacturer Code 0x00 0x89h Device ID Code 0x01 ID (See Table 9) Block Lock Configuration: Lock Bit: • Block Is Unlocked DQ0 = 0b0 • Block Is Locked BBA(1) + 0x02 DQ0 = 0b1 • Block Is not Locked-Down DQ1 = 0b0 • Block Is Locked-Down DQ1 = 0b1 Read Configuration Register 0x05 RCR Contents General Purpose Register(3) DBA(2) + 0x07 GPR data Lock Register 0 0x80 PR-LK0 64-bit Factory-Programmed OTP Register 0x81–0x84 Numonyx Factory OTP Register data 64-bit User-Programmable OTP Register 0x85–0x88 User OTP Register data Datasheet Apr 2010 22 Order Number: 208033-02

P30-65nm SBC Table 8: Device Identifier Information (Sheet 2 of 2) Item Address(1,2) Data(x16) Lock Register 1 0x89 PR-LK1 OTP Register lock data 128-bit User-Programmable OTP Registers 0x8A–0x109 User OTP Register data Notes: 1. BBA = Block Base Address. 2. DBA = Device base Address, Numonyx reserves other configuration address locations. 3. The GPR is used as read out register for Extended Function interface command. Table 9: Device ID codes ID Code Type Device Density Device Identifier Codes 64-Mbit 8817 Top Boot 128-Mbit 8818 64-Mbit 881A Bottom Boot 128-Mbit 881B 7.3 Read CFI The Read CFI command instructs the device to output Common Flash Interface data when read. See Figure 6.1, “Device Command Codes” on page 19. Section A.1, “Common Flash Interface” on page 61 shows CFI information and address offsets within the CFI database. 7.4 Read Status Register To read the Status Register, issue the Read Status Register command at any address. Status Register information is available to which the Read Status Register, Word Program, or Block Erase command was issued. SRD is automatically made available following a Word Program, Block Erase, or Block Lock command sequence. Reads from the device after any of these command sequences outputs the device’s status until another valid command is written (e.g. the Read Array command). The Status Register is read using single asynchronous-mode or synchronous burst mode reads. SRD is output on DQ[7:0], while 0x00 is output on DQ[15:8]. In asynchronous mode the falling edge of OE#, or CE# (whichever occurs first) updates and latches the Status Register contents. However, when reading the Status Register in synchronous burst mode, CE# or ADV# must be toggled to update SRD. The Device Ready Status bit (SR.7) provides overall status of the device. SR[6:1] present status and error information about the program, erase, suspend, VPP, and block-locked operations. See Table 12, “Status Register Description” on page 34 for the description of the Status Register. 7.5 Clear Status Register The Clear Status Register command clears the Status Register. It functions independent of VPP. The WSM sets and clears SR.7, but it sets bits SR[5:3,1] without clearing them. The Status Register should be cleared before starting a command sequence to avoid any ambiguity. A device reset also clears the Status Register. Datasheet Apr 2010 23 Order Number:208033-02

P30-65nm SBC 8.0 Program Operation The device supports three programming methods: Word Programming (40h/10h), Buffered Programming (E8h, D0h), and Buffered Enhanced Factory Programming (80h, D0h). The following sections describe device programming in detail. Successful programming requires the addressed block to be unlocked. If the block is locked down, WP# must be deasserted and the block must be unlocked before attempting to program the block. Attempting to program a locked block causes a program error (SR[4,1] set) and termination of the operation. See Section 10.0, “Security” on page 31 for details on locking and unlocking blocks. 8.1 Word Programming Word programming operations are initiated by writing the Word Program Setup command to the device. This is followed by a second write to the device with the address and data to be programmed. The device outputs Status Register data when read. See Figure 32, “Word Program Flowchart” on page 73. VPP must be above V , PPLK and within the specified V min/max values. PPL During programming, the WSM executes a sequence of internally-timed events that program the desired data bits at the addressed location, and verifies that the bits are sufficiently programmed. Programming the flash memory array changes “ones” to “zeros”. Memory array bits that are zeros can be changed to ones only by erasing the block. The Status Register can be examined for programming progress and errors by reading at any address. The device remains in the Read Status Register state until another command is written to the device. Status Register bit SR.7 indicates the programming status while the sequence executes. Commands that can be issued to the device during programming are Read Status Register, Read Device Identifier, Read CFI, and Read Array (this returns unknown data). When programming has finished, Status Register bit SR.4 (when set) indicates a programming failure. If SR.3 is set, the WSM could not perform the word programming operation because VPP was outside of its acceptable limits. If SR.1 is set, the word programming operation attempted to program a locked block, causing the operation to abort. Before issuing a new command, the Status Register contents should be examined and then cleared using the Clear Status Register command. Any valid command can follow, when word programming has completed. 8.2 Buffered Programming The device features a 256-word buffer to enable optimum programming performance. For Buffered Programming, data is first written to an on-chip write buffer. Then the buffer data is programmed into the flash memory array in buffer-size increments. This can improve system programming performance significantly over non-buffered programming. (see Figure 35, “Buffer Program Flowchart” on page 76). When the Buffered Programming Setup command is issued, Status Register information is updated and reflects the availability of the buffer. SR.7 indicates buffer availability: if set, the buffer is available; if cleared, the buffer is not available. Note: The device defaults to output SR data after the Buffered Programming Setup Command (E8h) is issued. CE# or OE# must be toggled to update Status Register. Don’t issue the Datasheet Apr 2010 24 Order Number: 208033-02

P30-65nm SBC Read SR command (70h), which would be interpreted by the internal state machines as Buffer Word Count. On the next write, a word count is written to the device at the buffer address. This tells the device how many data words will be written to the buffer, up to the maximum size of the buffer. On the next write, a device start address is given along with the first data to be written to the flash memory array. Subsequent writes provide additional device addresses and data. All data addresses must lie within the start address plus the word count. Optimum programming performance and lower power usage are obtained by aligning the starting address at the beginning of a 256-word boundary (A[8:1] = 0x00). Note: If a misaligned address range is issued during buffered programming, the program region must also be within an 256-word aligned boundary. After the last data is written to the buffer, the Buffered Programming Confirm command must be issued to the original block address. The WSM begins to program buffer contents to the flash memory array. If an error occurs while writing to the array, the device stops programming, and SR[7,4] are set, indicating a programming failure. When Buffered Programming has completed, additional buffer writes can be initiated by issuing another Buffered Programming Setup command and repeating the buffered program sequence. Buffered programming may be performed with VPP = V or V PPL PPH (see Section 13.2, “Operating Conditions” on page 45 for limitations when operating the device with VPP = V ). PPH If an attempt is made to program past an erase-block boundary using the Buffered Program command, the device aborts the operation. This generates a command sequence error, and SR[5,4] are set. If Buffered programming is attempted while VPP is at or below V , SR[4,3] are set. PPLK If any errors are detected that have set Status Register bits, the Status Register should be cleared using the Clear Status Register command. 8.3 Buffered Enhanced Factory Programming Buffered Enhanced Factory Programing (BEFP) speeds up the flash programming perforamnce. The enhanced programming algorithm used in BEFP eliminates traditional programming elements that drive up overhead in device programmer systems. BEFP consists of three phases: Setup, Program/Verify, and Exit (see Figure 37, “BEFP Flowchart” on page 78). It uses a write buffer to spread up the program performance across 256 data words. Verification occurs in the same phase as programming to accurately program the flash memory cell to the correct bit state. A single two-cycle command sequence programs the entire block of data. This enhancement eliminates three write cycles per buffer: two commands and the word count for each set of 256 data words. Host programmer bus cycles fill the device’s write buffer followed by a status check. SR.0 indicates when data from the buffer has been programmed into sequential flash memory array locations. Following the buffer-to-flash array programming sequence, the Write State Machine (WSM) increments internal addressing to automatically select the next 256-word array boundary. This aspect of BEFP saves host programming equipment the address-bus setup overhead. With adequate continuity testing, programming equipment can rely on the WSM’s internal verification to ensure that the device has programmed properly. This eliminates the external post-program verification and its associated overhead. Datasheet Apr 2010 25 Order Number:208033-02

P30-65nm SBC 8.3.1 BEFP Requirements and Considerations Table 10: BEFP Requirements Parameter/Issue Requirement Notes Case Temperature TC = 30°C ± 10°C - VCC Nominal Vcc - VPP Driven to VPPH - Setup and Confirm Target block must be unlocked before issuing the BEFP Setup and Confirm commands. - The first-word address (WA0) of the block to be programmed must be held constant Programming from the setup phase through all data streaming into the target block, until transition - to the exit phase is desired. Buffer Alignment WA0 must align with the start of an array buffer boundary. 1 Note: Word buffer boundaries in the array are determined by A[8:1] (0x00 through 0xFF). The alignment start point is A[8:1] = 0x000. Table 11: BEFP Considerations Parameter/Issue Requirement Notes Cycling For optimum performance, cycling must be limited below 50 erase cycles per block. 1 Programming blocks BEFP programs one block at a time; all buffer data must fall within a single block. 2 Suspend BEFP cannot be suspended. - Programming the flash Programming to the flash memory array can occur only when the buffer is full. 3 memory array Notes: 1. Some degradation in performance may occur is this limit is exceeded, but the internal algorithm continues to work properly. 2. If the internal address counter increments beyond the block’s maximum address, addressing wraps around to the beginning of the block. 3. If the number of words is less than 256, remaining locations must be filled with 0xFFFF. 8.3.2 BEFP Setup Phase After receiving the BEFP Setup and Confirm command sequence, Status Register bit SR.7 (Ready) is cleared, indicating that the WSM is busy with BEFP algorithm startup. A delay before checking SR.7 is required to allow the WSM enough time to perform all of its setups and checks (Block-Lock status, VPP level, etc.). If an error is detected, SR.4 is set and BEFP operation terminates. If the block was found to be locked, SR.1 is also set. SR.3 is set if the error occurred due to an incorrect VPP level. Note: Reading from the device after the BEFP Setup and Confirm command sequence outputs Status Register data. Do not issue the Read Status Register command; it will be interpreted as data to be loaded into the buffer. 8.3.3 BEFP Program/Verify Phase After the BEFP Setup Phase has completed, the host programming system must check SR[7,0] to determine the availability of the write buffer for data streaming. SR.7 cleared indicates the device is busy and the BEFP program/verify phase is activated. SR.0 indicates the write buffer is available. Datasheet Apr 2010 26 Order Number: 208033-02

P30-65nm SBC Two basic sequences repeat in this phase: loading of the write buffer, followed by buffer data programming to the array. For BEFP, the count value for buffer loading is always the maximum buffer size of 256 words. During the buffer-loading sequence, data is stored to sequential buffer locations starting at address 0x00. Programming of the buffer contents to the flash memory array starts as soon as the buffer is full. If the number of words is less than 256, the remaining buffer locations must be filled with 0xFFFF. Caution: The buffer must be completely filled for programming to occur. Supplying an address outside of the current block's range during a buffer-fill sequence causes the algorithm to exit immediately. Any data previously loaded into the buffer during the fill cycle is not programmed into the array. The starting address for data entry must be buffer size aligned, if not the BEFP algorithm will be aborted and the program fails and (SR.4) flag will be set. Data words from the write buffer are directed to sequential memory locations in the flash memory array; programming continues from where the previous buffer sequence ended. The host programming system must poll SR.0 to determine when the buffer program sequence completes. SR.0 cleared indicates that all buffer data has been transferred to the flash array; SR.0 set indicates that the buffer is not available yet for the next fill cycle. The host system may check full status for errors at any time, but it is only necessary on a block basis after BEFP exit. After the buffer fill cycle, no write cycles should be issued to the device until SR.0 = 0 and the device is ready for the next buffer fill. Note: Any spurious writes are ignored after a buffer fill operation and when internal program is proceeding. The host programming system continues the BEFP algorithm by providing the next group of data words to be written to the buffer. Alternatively, it can terminate this phase by changing the block address to one outside of the current block’s range. The Program/Verify phase concludes when the programmer writes to a different block address; data supplied must be 0xFFFF. Upon Program/Verify phase completion, the device enters the BEFP Exit phase. 8.3.4 BEFP Exit Phase When SR.7 is set, the device has returned to normal operating conditions. A full status check should be performed at this time to ensure the entire block programmed successfully. When exiting the BEFP algorithm with a block address change, the read mode will not change. After BEFP exit, any valid command can be issued to the device. 8.4 Program Suspend Issuing the Program Suspend command while programming suspends the programming operation. This allows data to be accessed from the device other than the one being programmed. The Program Suspend command can be issued to any device address. A program operation can be suspended to perform reads only. Additionally, a program operation that is running during an erase suspend can be suspended to perform a read operation (see Figure 36, “Program Suspend/Resume Flowchart” on page 77). When a programming operation is executing, issuing the Program Suspend command requests the WSM to suspend the programming algorithm at predetermined points. The device continues to output Status Register data after the Program Suspend command is issued. Programming is suspended when Status Register bits SR[7,2] are set. Suspend latency is specified in Section 15.5, “Program and Erase Characteristics” on page 58. Datasheet Apr 2010 27 Order Number:208033-02

P30-65nm SBC To read data from the device, the Read Array command must be issued. Read Array, Read Status Register, Read Device Identifier, Read CFI, and Program Resume are valid commands during a program suspend. During a program suspend, deasserting CE# places the device in standby, reducing active current. VPP must remain at its programming level, and WP# must remain unchanged while in program suspend. If RST# is asserted, the device is reset. 8.5 Program Resume The Resume command instructs the device to continue programming, and automatically clears Status Register bits SR[7,2]. This command can be written to any address. If error bits are set, the Status Register should be cleared before issuing the next instruction. RST# must remain deasserted (see Figure 33, “Program Suspend/ Resume Flowchart” on page 74). 8.6 Program Protection When VPP = V , absolute hardware write protection is provided for all device blocks. If IL VPP is at or below V , programming operations halt and SR.3 is set indicating a VPP- PPLK level error. Block Lock Registers are not affected by the voltage level on VPP; they may still be programmed and read, even if VPP is less than V . PPLK Figure 8: Example VPP Supply Connections VCC VCC VCC VCC V VPP PROT # VPP PP ≤ 10K Ω • Low-voltage Programming only • Factory Programming with V = V • Logic Control of Device Protection PP PPH • Complete write/Erase Protection when V ≤ V PP PPLK V V CC VCC CC VCC V =V VPP VPP PP PPH • Low Voltage Programming Only • Low Voltage and Factory Programming • Full Device Protection Unavailable Datasheet Apr 2010 28 Order Number: 208033-02

P30-65nm SBC 9.0 Erase Operation Flash erasing is performed on a block basis. An entire block is erased each time an erase command sequence is issued, and only one block is erased at a time. When a block is erased, all bits within that block read as logical ones. The following sections describe block erase operations in detail. 9.1 Block Erase Block erase operations are initiated by writing the Block Erase Setup command to the address of the block to be erased (see Section 6.2, “Device Command Bus Cycles” on page 20). Next, the Block Erase Confirm command is written to the address of the block to be erased. If the device is placed in standby (CE# deasserted) during an erase operation, the device completes the erase operation before entering standby. VPP must be above V and the block must be unlocked (see Figure 38, “Block Erase Flowchart” PPLK on page 79). During a block erase, the WSM executes a sequence of internally-timed events that conditions, erases, and verifies all bits within the block. Erasing the flash memory array changes “zeros” to “ones”. Memory block array data that are ones can be changed to zeros by programming block. The Status Register can be examined for block erase progress and errors by reading any address. The device remains in the Read Status Register state until another command is written. SR.0 indicates whether the addressed block is erasing. Status Register bit SR.7 is set upon erase completion. Status Register bit SR.7 indicates block erase status while the sequence executes. When the erase operation has finished, Status Register bit SR.5 indicates an erase failure if set. SR.3 set would indicate that the WSM could not perform the erase operation because VPP was outside of its acceptable limits. SR.1 set indicates that the erase operation attempted to erase a locked block, causing the operation to abort. Before issuing a new command, the Status Register contents should be examined and then cleared using the Clear Status Register command. Any valid command can follow once the block erase operation has completed. 9.2 Blank Check The Blank Check operation determines whether a specified array block is blank (i.e. completely erased). Without Blank Check, Block Erase would be the only other way to ensure a block is completely erased. Blank Check is especially useful in the case of erase operation interrupted by a power loss event. Blank check can apply to only one block at a time, and no operations other than Status Register Reads are allowed during Blank Check (e.g. reading array data, program, erase etc). Suspend and resume operations are not supported during Blank Check, nor is Blank Check supported during any suspended operations. Blank Check operations are initiated by writing the Block Blank Check command to the block address. Next, the Blank Check Confirm command is issued along with the same block address. When a successful command sequence is entered, the device automatically enters the Read Status State. The WSM then reads the entire specified block, and determines whether any bit in the block is programmed or over-erased. The Status Register can be examined for Blank Check progress and errors by reading any address within the block being accessed. During a blank check operation, the Status Register indicates a busy status (SR.7 = 0). Upon completion, the Status Datasheet Apr 2010 29 Order Number:208033-02

P30-65nm SBC Register indicates a ready status (SR.7 = 1). The Status Register should be checked for any errors, and then cleared. If the Blank Check operation fails, which means the block is not completely erased, the Status Register bit SR.5 will be set (“1”). CE# or OE# toggle (during polling) updates the Status Register. After examining the Status Register, it should be cleared by the Clear Status Register command before issuing a new command. The device remains in Status Register Mode until another command is written to the device. Any command can follow once the Blank Check command is complete. 9.3 Erase Suspend Issuing the Erase Suspend command while erasing suspends the block erase operation. This allows data to be accessed from memory locations other than the one being erased. The Erase Suspend command can be issued to any device address. A block erase operation can be suspended to perform a word or buffer program operation, or a read operation within any block except the block that is erase suspended (see Figure 34, “Erase Suspend/Resume Flowchart” on page 75). When a block erase operation is executing, issuing the Erase Suspend command requests the WSM to suspend the erase algorithm at predetermined points. The device continues to output Status Register data after the Erase Suspend command is issued. Block erase is suspended when Status Register bits SR[7,6] are set. Suspend latency is specified in Section 15.5, “Program and Erase Characteristics” on page 58. To read data from the device (other than an erase-suspended block), the Read Array command must be issued. During Erase Suspend, a Program command can be issued to any block other than the erase-suspended block. Block erase cannot resume until program operations initiated during erase suspend complete. Read Array, Read Status Register, Read Device Identifier, Read CFI, and Erase Resume are valid commands during Erase Suspend. Additionally, Clear Status Register, Program, Program Suspend, Block Lock, Block Unlock, and Block Lock-Down are valid commands during Erase Suspend. During an erase suspend, deasserting CE# places the device in standby, reducing active current. VPP must remain at a valid level, and WP# must remain unchanged while in erase suspend. If RST# is asserted, the device is reset. 9.4 Erase Resume The Erase Resume command instructs the device to continue erasing, and automatically clears SR[7,6]. This command can be written to any address. If Status Register error bits are set, the Status Register should be cleared before issuing the next instruction. RST# must remain deasserted. 9.5 Erase Protection When VPP = V , absolute hardware erase protection is provided for all device blocks. If IL VPP ≤ V , erase operations halt and SR.3 is set indicating a VPP-level error. PPLK Datasheet Apr 2010 30 Order Number: 208033-02