ICGOO在线商城 > 分立半导体产品 > 晶体管 - FET,MOSFET - 单 > IRF4905LPBF

- 型号: IRF4905LPBF

- 制造商: International Rectifier

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

IRF4905LPBF产品简介:

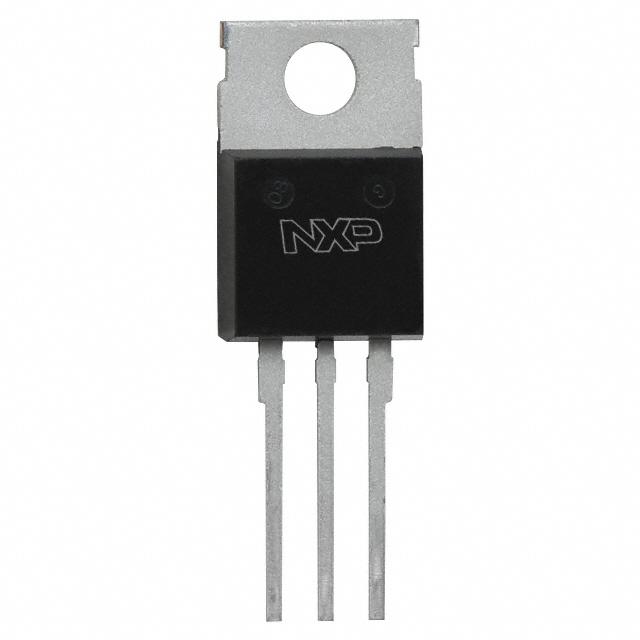

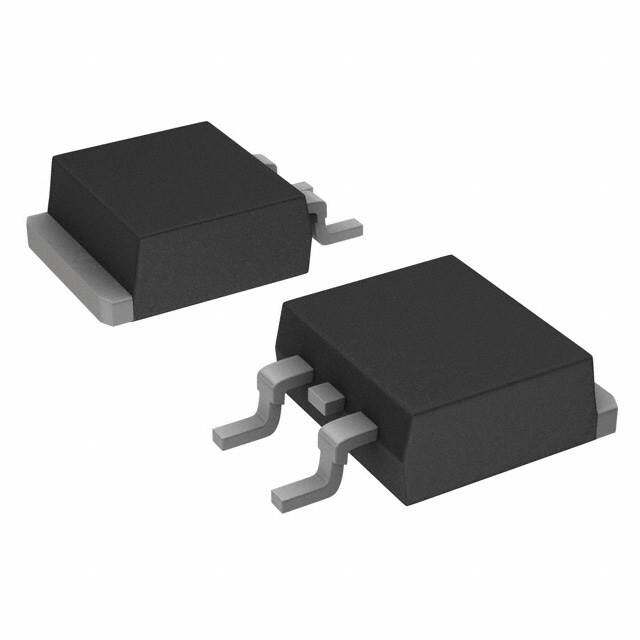

ICGOO电子元器件商城为您提供IRF4905LPBF由International Rectifier设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 IRF4905LPBF价格参考¥7.13-¥7.89。International RectifierIRF4905LPBF封装/规格:晶体管 - FET,MOSFET - 单, 通孔 P 沟道 55V 42A(Tc) 170W(Tc) TO-262。您可以下载IRF4905LPBF参考资料、Datasheet数据手册功能说明书,资料中有IRF4905LPBF 详细功能的应用电路图电压和使用方法及教程。

Infineon Technologies的IRF4905LPBF是一款P沟道增强型MOSFET(金属氧化物场效应晶体管),主要用于开关和功率管理应用。以下是其主要应用场景: 1. 电源管理系统 IRF4905LPBF常用于电源管理电路中,特别是在降压转换器、升压转换器和反相转换器等DC-DC转换器中。由于其低导通电阻(Rds(on))特性,能够在高电流条件下保持较低的功耗,从而提高系统的效率。 2. 负载切换 在负载切换应用中,IRF4905LPBF可以作为电子开关,控制负载的通断。例如,在汽车电子系统中,它可以用于控制车灯、风扇、电动座椅等设备的电源供应,确保在需要时能够快速响应并提供稳定的电流。 3. 电机驱动 该MOSFET适用于小型直流电机的驱动控制。通过PWM(脉宽调制)信号控制MOSFET的导通与关断,可以实现对电机速度和方向的精确控制。此外,它还可以用于电机的制动回路,帮助快速停止电机并回收能量。 4. 电池管理系统 在电池管理系统(BMS)中,IRF4905LPBF可用于电池充放电保护电路。当电池电压过高或过低时,MOSFET会切断充电或放电回路,防止电池损坏。它的低导通电阻有助于减少发热,延长电池寿命。 5. 通信设备 在通信设备中,IRF4905LPBF可用于电源调节和信号隔离。例如,在基站和路由器中,它可以帮助稳定供电电压,并防止不同模块之间的电气干扰。 6. 消费电子产品 在消费电子产品如智能手机、平板电脑和笔记本电脑中,IRF4905LPBF可用于电源管理单元(PMU),以优化电池使用时间和设备性能。它还可以用于USB接口的过流保护,防止外部设备对主机造成损害。 总结 IRF4905LPBF凭借其出色的开关特性和低导通电阻,广泛应用于各种电力电子设备中,尤其适合需要高效、可靠电源管理和负载控制的应用场景。

| 参数 | 数值 |

| 产品目录 | |

| 描述 | MOSFET P-CH 55V 42A TO-262MOSFET MOSFT PCh -55V -74A 20mOhm 120nC |

| 产品分类 | FET - 单分离式半导体 |

| FET功能 | 标准 |

| FET类型 | MOSFET P 通道,金属氧化物 |

| Id-ContinuousDrainCurrent | - 74 A |

| Id-连续漏极电流 | - 74 A |

| 品牌 | International Rectifier |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 晶体管,MOSFET,International Rectifier IRF4905LPBFHEXFET® |

| 数据手册 | |

| 产品型号 | IRF4905LPBF |

| PCN组件/产地 | |

| Pd-PowerDissipation | 200 W |

| Pd-功率耗散 | 200 W |

| Qg-GateCharge | 120 nC |

| Qg-栅极电荷 | 120 nC |

| RdsOn-Drain-SourceResistance | 20 mOhms |

| RdsOn-漏源导通电阻 | 20 mOhms |

| Vds-Drain-SourceBreakdownVoltage | - 55 V |

| Vds-漏源极击穿电压 | - 55 V |

| Vgs-Gate-SourceBreakdownVoltage | 20 V |

| Vgs-栅源极击穿电压 | 20 V |

| 不同Id时的Vgs(th)(最大值) | 4V @ 250µA |

| 不同Vds时的输入电容(Ciss) | 3500pF @ 25V |

| 不同Vgs时的栅极电荷(Qg) | 180nC @ 10V |

| 不同 Id、Vgs时的 RdsOn(最大值) | 20 毫欧 @ 42A,10V |

| 产品培训模块 | http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=26250 |

| 产品种类 | MOSFET |

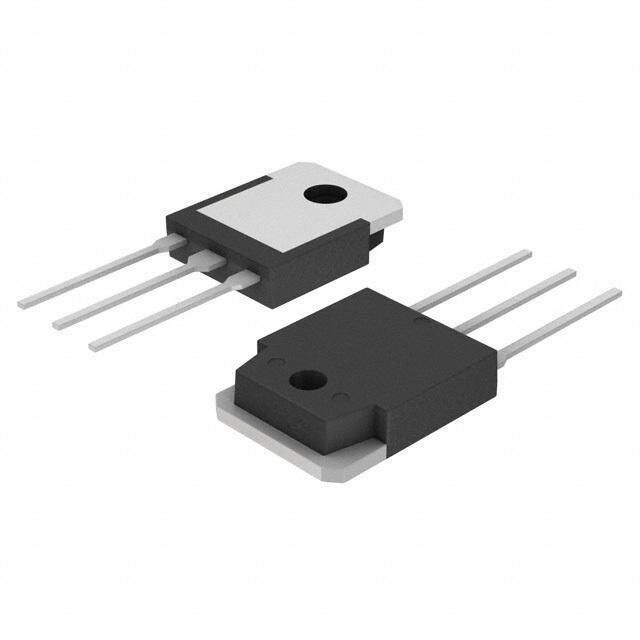

| 供应商器件封装 | TO-262 |

| 功率-最大值 | 170W |

| 功率耗散 | 200 W |

| 包装 | 管件 |

| 商标 | International Rectifier |

| 安装类型 | 通孔 |

| 安装风格 | Through Hole |

| 导通电阻 | 20 mOhms |

| 封装 | Tube |

| 封装/外壳 | TO-262-3,长引线,I²Pak,TO-262AA |

| 封装/箱体 | I2PAK-3 |

| 工厂包装数量 | 50 |

| 晶体管极性 | P-Channel |

| 栅极电荷Qg | 120 nC |

| 标准包装 | 50 |

| 汲极/源极击穿电压 | - 55 V |

| 漏极连续电流 | - 74 A |

| 漏源极电压(Vdss) | 55V |

| 电流-连续漏极(Id)(25°C时) | 42A (Tc) |

| 设计资源 | http://www.irf.com/product-info/models/saber/irf4905slpbf.sinhttp://www.irf.com/product-info/models/spice/irf4905slpbf.spi |

| 闸/源击穿电压 | 20 V |

.jpg)

PDF Datasheet 数据手册内容提取

PD - 97034 IRF4905SPbF IRF4905LPbF Features HEXFET® Power MOSFET (cid:79) Advanced Process Technology (cid:79) Ultra Low On-Resistance D VDSS = -55V (cid:79) 150°C Operating Temperature (cid:79) Fast Switching R = 20mΩ DS(on) (cid:79) Repetitive Avalanche Allowed up to Tjmax G (cid:79) Some Parameters Are Differrent from I = -42A IRF4905S D S (cid:79) Lead-Free Description D D Features of this design are a 150°C junction oper- ating temperature, fast switching speed and im- proved repetitive avalanche rating . These features S S combine to make this design an extremely efficient GD GD and reliable device for use in a wide variety of other D2Pak TO-262 applications. IRF4905SPbF IRF4905LPbF G D S Gate Drain Source Absolute Maximum Ratings Parameter Max. Units ID @ TC = 25°C Continuous Drain Current, VGS @ 10V (Silicon Limited) -70 ID @ TC = 100°CContinuous Drain Current, VGS @ 10V (Silicon Limited) -44 A ID @ TC = 25°C Continuous Drain Current, VGS @ 10V (Package Limited) -42 I Pulsed Drain Current (cid:0) -280 DM PD @TC = 25°C Power Dissipation 170 W Linear Derating Factor 1.3 W/°C VGS Gate-to-Source Voltage ± 20 V EAS (Thermally limited) Single Pulse Avalanche Energy(cid:1) 140 mJ E (Tested ) Single Pulse Avalanche Energy Tested Value (cid:2) 790 AS IAR Avalanche Current(cid:3)(cid:0) See Fig.12a, 12b, 15, 16 A EAR Repetitive Avalanche Energy (cid:4) mJ T Operating Junction and -55 to + 150 J TSTG Storage Temperature Range °C Soldering Temperature, for 10 seconds 300 (1.6mm from case ) Mounting Torque, 6-32 or M3 screw (cid:5) 10 lbf(cid:7)in (1.1N(cid:7)m) Thermal Resistance Parameter Typ. Max. Units R Junction-to-Case (cid:6) ––– 0.75 θJC R Junction-to-Ambient (PCB Mount, steady state) (cid:5)(cid:6) ––– 40 θJA www.irf.com 1 (cid:1)(cid:2)(cid:3)(cid:2)(cid:4)(cid:3)

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8)(cid:9)(cid:10) Electrical Characteristics @ T = 25°C (unless otherwise specified) J Parameter Min. Typ. Max. Units Conditions V(BR)DSS Drain-to-Source Breakdown Voltage -55 ––– ––– V VGS = 0V, ID = -250µA ∆V(BR)DSS/∆TJ Breakdown Voltage Temp. Coefficient ––– -0.054 ––– V/°C Reference to 25°C, ID = -1mA RDS(on) Static Drain-to-Source On-Resistance ––– ––– 20 mΩ VGS = -10V, ID = -42A (cid:2) VGS(th) Gate Threshold Voltage -2.0 ––– -4.0 V VDS = VGS, ID = -250µA gfs Forward Transconductance 19 ––– ––– S VDS = -25V, ID = -42A IDSS Drain-to-Source Leakage Current ––– ––– -25 µA VDS = -55V, VGS = 0V ––– ––– -200 VDS = -44V, VGS = 0V, TJ = 125°C IGSS Gate-to-Source Forward Leakage ––– ––– 100 nA VGS = -20V Gate-to-Source Reverse Leakage ––– ––– -100 VGS = 20V Qg Total Gate Charge ––– 120 180 ID = -42A Qgs Gate-to-Source Charge ––– 32 ––– nC VDS = -44V Qgd Gate-to-Drain ("Miller") Charge ––– 53 ––– VGS = -10V (cid:2) td(on) Turn-On Delay Time ––– 20 ––– VDD = -28V tr Rise Time ––– 99 ––– ID = -42A td(off) Turn-Off Delay Time ––– 51 ––– ns RG = 2.6 Ω tf Fall Time ––– 64 ––– VGS = -10V (cid:2) L Internal Source Inductance ––– 7.5 ––– nH Between lead, S and center of die contact Ciss Input Capacitance ––– 3500 ––– VGS = 0V Coss Output Capacitance ––– 1250 ––– VDS = -25V C Reverse Transfer Capacitance ––– 450 ––– pF ƒ = 1.0MHz rss Coss Output Capacitance ––– 4620 ––– VGS = 0V, VDS = -1.0V, ƒ = 1.0MHz Coss Output Capacitance ––– 940 ––– VGS = 0V, VDS = -44V, ƒ = 1.0MHz Coss eff. Effective Output Capacitance ––– 1530 ––– VGS = 0V, VDS = 0V to -44V (cid:3) Source-Drain Ratings and Characteristics Parameter Min. Typ. Max. Units Conditions I Continuous Source Current ––– ––– -42 MOSFET symbol S (Body Diode) A showing the I Pulsed Source Current ––– ––– -280 integral reverse SM (Body Diode)(cid:0)(cid:1) p-n junction diode. VSD Diode Forward Voltage ––– ––– -1.3 V TJ = 25°C, IS = -42A, VGS = 0V (cid:2) trr Reverse Recovery Time ––– 61 92 ns TJ = 25°C, IF = -42A, VDD = -28V Q Reverse Recovery Charge ––– 150 220 nC di/dt = -100A/µs (cid:2) rr ton Forward Turn-On Time Intrinsic turn-on time is negligible (turn-on is dominated by LS+LD) 2 www.irf.com

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8)(cid:9)(cid:10) 1000 1000 VGS VGS TOP -15V TOP -15V Aen()t ----8761...0000VVVV Aen()t ----8761...0000VVVV Curr 100 --55..50VV Curr 100 --55..50VV e BOTTOM -4.5V e BOTTOM -4.5V c c ur ur o o S S o- o- an-ti 10 an-ti 10 Dr Dr -4.5V , D , D -I -4.5V ≤ 60µs PULSE WIDTH -I ≤ 60µs PULSE WIDTH Tj = 25°C Tj = 150°C 1 1 0.1 1 10 100 1000 0.1 1 10 100 1000 -VDS, Drain-to-Source Voltage (V) -VDS, Drain-to-Source Voltage (V) Fig 1. Typical Output Characteristics Fig 2. Typical Output Characteristics 1000.0 40 TJ = 25°C TJ = 25°C )ent Α( 100.0 TJ = 150°C Snce() 30 Curr ucat Sueocr 10.0 nscond 20 TJ = 150°C no--t Tdar Dari 1.0 war , D For 10 -I VDS = -25V s, ≤ 60µs PULSE WIDTH Gf VDS = -10V 0.1 380µs PULSE WIDTH 3 4 5 6 7 8 9 10 11 12 13 14 0 0 20 40 60 80 -VGS, Gate-to-Source Voltage (V) -ID, Drain-to-Source Current (A) Fig 3. Typical Transfer Characteristics Fig 4. Typical Forward Transconductance Vs. Drain Current www.irf.com 3

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8)(cid:9)(cid:10) 7000 20 VGS = 0V, f = 1 MHZ 6000 CCirssss == CCggsd + Cgd, Cds SHORTED Ve() 16 ID= -42A VVDDSS== --2484VV F) 5000 Coss = Cds + Cgd oagtl VDS= -11V p V enc( 4000 Ciss uecr 12 a o paacti 3000 Seo--t 8 CC, 2000 Coss Gat, S G 4 V 1000 Crss - 0 0 0 40 80 120 160 200 1 10 100 -VDS, Drain-to-Source Voltage (V) QG Total Gate Charge (nC) Fig 5. Typical Capacitance Vs. Fig 6. Typical Gate Charge Vs. Drain-to-Source Voltage Gate-to-Source Voltage 1000.0 1000 OPERATION IN THIS AREA LIMITED BY RDS(on) A) A) Cuenrrt ( 100.0 TJ = 150°C Cuenrr(t 100 100µsec Danr i 10.0 eoucr 1msec se So- 10msec eevr an-ti 10 LIMITED BY PACKAGE R-I, SD 1.0 TJ = 25°C D-rI, D Tc = 25°C DC Tj = 150°C VGS = 0V Single Pulse 0.1 1 0.0 0.4 0.8 1.2 1.6 2.0 0 1 10 100 -VSD, Source-to-Drain Voltage (V) -VDS , Drain-toSource Voltage (V) Fig 7. Typical Source-Drain Diode Fig 8. Maximum Safe Operating Area Forward Voltage 4 www.irf.com

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8)(cid:9)(cid:10) 80 2.0 LIMITED BY PACKAGE ec ID = -42A n ast VGS = -10V si A) 60 Re n(t On 1.5 DCueanrr-r I, iD 24000 DSenoouac--rr t, iRDSon() mNoedazr)( li 1.0 0.5 25 50 75 100 125 150 -60 -40 -20 0 20 40 60 80 100 120 140 160 TC , Case Temperature (°C) TJ , Junction Temperature (°C) Fig 9. Maximum Drain Current Vs. Fig 10. Normalized On-Resistance Case Temperature Vs. Temperature 1 D = 0.50 ) C J 0.20 h Z t 0.1 0.10 mReponaess( l 0.01 000...000215 τJτJτ1Cτ1i= τi/RiR1R1 τ2τR22R2 Rτ33Rτ33 τCτR000i (...132°C176630/W548 ) 000τ...i 000(001se024c038)641871 er Ci τi/Ri h T Notes: SINGLE PULSE 1. Duty Factor D = t1/t2 ( THERMAL RESPONSE ) 2. Peak Tj = P dm x Zthjc + Tc 0.001 1E-006 1E-005 0.0001 0.001 0.01 0.1 t1 , Rectangular Pulse Duration (sec) Fig 11. Maximum Effective Transient Thermal Impedance, Junction-to-Case www.irf.com 5

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8)(cid:9)(cid:10) VDS L 600 R-2G0V IADS.U.T DRIVER VDDA megJy)r( 500 T O P -- 3I10D7AA tp 0.01Ω En BOTTOM -42A e 400 h c n a al v 300 A 15V e s ul P 200 e Fig 12a. Unclamped Inductive Test Circuit gl n IAS SiS, 100 A E 0 25 50 75 100 125 150 Starting TJ, Junction Temperature (°C) tp V(BR)DSS Fig 12c. Maximum Avalanche Energy Fig 12b. Unclamped Inductive Waveforms Vs. Drain Current QG (cid:1)(cid:2)(cid:3) 3.6 QGS QGD V) VG eg( a 3.2 otl V d Charge hol ID = -250µA Fig 13a. Basic Gate Charge Waveform es 2.8 SaCmuerreTnytpeReagsulDat.oUr.T. ehr t at G 12V .2µF 50KΩ Sh()t 2.4 .3µF G V - - D.U.T. +VDS 2.0 VGS -75 -50 -25 0 25 50 75 100 125 150 -3mA TJ , Temperature ( °C ) IG ID CurrentSamplingResistors Fig 13b. Gate Charge Test Circuit Fig 14. Threshold Voltage Vs. Temperature 6 www.irf.com

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8)(cid:9)(cid:10) 1000 Duty Cycle = Single Pulse A) 100 0.01 Allowed avalanche Current vs ne(t aasvsaulamncinhge ∆pTuj ls=e w2i5d°tCh, dutea vt o urr 0.05 avalanche losses. Note: In no Ce 10 0.10 case should Tj be allowed to h exceed Tjmax c n a al v A 1 0.1 1.0E-06 1.0E-05 1.0E-04 1.0E-03 1.0E-02 1.0E-01 tav (sec) Fig 15. Typical Avalanche Current Vs.Pulsewidth 160 Notes on Repetitive Avalanche Curves , Figures 15, 16: TOP Single Pulse (For further info, see AN-1005 at www.irf.com) BOTTOM 1% Duty Cycle 1. Avalanche failures assumption: J) ID = -42A Purely a thermal phenomenon and failure occurs at a my( 120 etevmerpye praatrut rtey pfaer. in excess of Tjmax. This is validated for g er 2. Safe operation in Avalanche is allowed as long asTjmax is n E not exceeded. e 3. Equation below based on circuit and waveforms shown in h 80 nc Figures 12a, 12b. aal 4. PD (ave) = Average power dissipation per single Av avalanche pulse. , R 40 5. BV = Rated breakdown voltage (1.3 factor accounts for A voltage increase during avalanche). E 6. I = Allowable avalanche current. av 7. ∆T = Allowable rise in junction temperature, not to exceed T (assumed as 25°C in Figure 15, 16). jmax 0 t Average time in avalanche. av = 25 50 75 100 125 150 D = Duty cycle in avalanche = t ·f av Starting TJ , Junction Temperature (°C) ZthJC(D, tav) = Transient thermal resistance, see figure 11) P = 1/2 ( 1.3·BV·I ) =(cid:1)(cid:1)T/ Z D (ave) av thJC Fig 16. Maximum Avalanche Energy I =2(cid:1)T/ [1.3·BV·Z ] av th Vs. Temperature E = P ·t AS (AR) D (ave) av www.irf.com 7

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8)(cid:9)(cid:10) Driver Gate Drive (cid:2)(cid:3)(cid:4)(cid:3)(cid:5)(cid:24)(cid:24) Period D = P.W. + P.W. Period (cid:24) (cid:1) (cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:2)(cid:6)(cid:7)(cid:8)(cid:9)(cid:10)(cid:11)(cid:5)(cid:6)(cid:7)(cid:1)(cid:11)(cid:12)(cid:13)(cid:2)(cid:14)(cid:15)(cid:3)(cid:9)(cid:6)(cid:2)(cid:11)(cid:12)(cid:13) VGS=10V • (cid:7)(cid:8)(cid:11)(cid:16)(cid:7)(cid:17)(cid:6)(cid:3)(cid:9)(cid:10)(cid:7)(cid:18)(cid:12)(cid:14)(cid:5)(cid:4)(cid:6)(cid:9)(cid:12)(cid:4)(cid:15) (cid:7)(cid:7) • (cid:19)(cid:3)(cid:11)(cid:5)(cid:12)(cid:14)(cid:7)(cid:20)(cid:21)(cid:9)(cid:12)(cid:15) - (cid:7)(cid:7)(cid:7)(cid:7) (cid:7)•(cid:7)(cid:7) (cid:7) (cid:1)(cid:8)(cid:11)(cid:5)(cid:16)(cid:3)(cid:3)(cid:7)(cid:15)(cid:8)(cid:12)(cid:15)(cid:6)(cid:9)(cid:7)(cid:24)(cid:22)(cid:3)(cid:9)(cid:9)(cid:23)(cid:12)(cid:15)(cid:13)(cid:7)(cid:25)(cid:18)(cid:11)(cid:12)(cid:3)(cid:14)(cid:26)(cid:5)(cid:15)(cid:4)(cid:6)(cid:3)(cid:9)(cid:12)(cid:4)(cid:15) D.U.T. ISDWaveform + (cid:3) Reverse (cid:2) Recovery Body Diode Forward - - + Current Currentdi/dt D.U.T. VDSWaveform Diode Recovery (cid:4) dv/dt VDD (cid:6) (cid:20)(cid:19) • (cid:14)(cid:28)(cid:29)(cid:14)(cid:6)(cid:7)(cid:4)(cid:11)(cid:12)(cid:6)(cid:3)(cid:11)(cid:21)(cid:21)(cid:15)(cid:14)(cid:7)(cid:30)(cid:10)(cid:7)(cid:31)(cid:1) (cid:27)(cid:27) Re-Applied • (cid:27)(cid:3)(cid:2)(cid:28)(cid:15)(cid:3)(cid:7)(cid:13)(cid:9)(cid:26)(cid:15)(cid:7)(cid:6)(cid:10) (cid:15)(cid:7)(cid:9)(cid:13)(cid:7)(cid:27)!"!(cid:24)! + Voltage Body Diode Forward Drop • (cid:18)(cid:2)(cid:3)(cid:7)(cid:4)(cid:11)(cid:12)(cid:6)(cid:3)(cid:11)(cid:21)(cid:21)(cid:15)(cid:14)(cid:7)(cid:30)(cid:10)(cid:7)(cid:27)(cid:5)(cid:6)(cid:10)(cid:7)#(cid:9)(cid:4)(cid:6)(cid:11)(cid:3)(cid:7)$(cid:27)$ - Inductor Curent • (cid:27)!"!(cid:24)!(cid:7)%(cid:7)(cid:27)(cid:15)(cid:28)(cid:2)(cid:4)(cid:15)(cid:7)"(cid:12)(cid:14)(cid:15)(cid:3)(cid:7)(cid:24)(cid:15)(cid:13)(cid:6) Ripple ≤ 5% ISD (cid:24)(cid:24)(cid:5)(cid:5)(cid:20)(cid:15)(cid:16)(cid:15)(cid:10)(cid:19)(cid:15)(cid:5)(cid:24)(cid:9)(cid:17)(cid:25)(cid:10)(cid:13)(cid:26)(cid:27)(cid:5)(cid:9)(cid:8)(cid:5)(cid:18)(cid:21)(cid:22)(cid:21)(cid:23)(cid:5)(cid:8)(cid:9)(cid:10)(cid:5)(cid:24)(cid:28)(cid:29)(cid:30)(cid:25)(cid:31)(cid:31)(cid:15)(cid:17) (cid:24)(cid:5)(cid:6) (cid:5)(cid:7)(cid:5)(cid:3)(cid:6)(cid:5)(cid:8)(cid:9)(cid:10)(cid:5)(cid:11)(cid:9)(cid:12)(cid:13)(cid:14)(cid:5)(cid:11)(cid:15)(cid:16)(cid:15)(cid:17)(cid:5)(cid:18)(cid:15)(cid:16)(cid:13)(cid:14)(cid:15)(cid:19) (cid:19)(cid:17) Fig 17. (cid:4)(cid:5)(cid:6)(cid:7)(cid:8)(cid:9)(cid:10)(cid:11)(cid:12)(cid:5)(cid:8)(cid:13)(cid:5)(cid:14)(cid:11)(cid:15)(cid:5)(cid:16)(cid:17)(cid:8)(cid:12)(cid:15)(cid:18)(cid:12)(cid:19)(cid:8)(cid:20)(cid:5)(cid:21)(cid:19)(cid:8)(cid:22)(cid:10)(cid:16)(cid:14)(cid:23)(cid:10)(cid:19)(cid:8)for P-Channel HEXFET(cid:1)(cid:8)Power MOSFETs (cid:20) (cid:27) (cid:6) (cid:27)(cid:17) (cid:6) (cid:19)(cid:17) (cid:18)(cid:21)(cid:22)(cid:21)(cid:23)(cid:21) (cid:20) (cid:19) - (cid:6) + (cid:27)(cid:27) (cid:6) (cid:19)(cid:17) (cid:20)(cid:5)(cid:21)(cid:13)(cid:15)(cid:7)&(cid:2)(cid:14)(cid:6)’(cid:7)≤ 1 ((cid:13) (cid:27)(cid:5)(cid:6)(cid:10)(cid:7)#(cid:9)(cid:4)(cid:6)(cid:11)(cid:3)(cid:7)≤ 0.1 % Fig 18a. Switching Time Test Circuit td(on) tr td(off) tf VGS 10% 90% VDS Fig 18b. Switching Time Waveforms 8 www.irf.com

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8)(cid:9)(cid:10) (cid:1)(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:2)(cid:3)(cid:16)(cid:4)(cid:3)(cid:11)(cid:17)(cid:5)(cid:18)(cid:19)(cid:7)(cid:20)(cid:9)(cid:10)(cid:17)(cid:5) (Dimensions are shown in millimeters (inches)) (cid:1)(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:2)(cid:3)(cid:6)(cid:7)(cid:5)(cid:8)(cid:3)(cid:6)(cid:4)(cid:9)(cid:10)(cid:11)(cid:5)(cid:12)(cid:10)(cid:13)(cid:14)(cid:6)(cid:15)(cid:3)(cid:7)(cid:9)(cid:14)(cid:10) THIS IS AN IRF530S WITH PART NUMBER LOT CODE 8024 INTERNATIONAL ASSEMBLED ON WW 02, 2000 RECTIFIER F530S IN THE ASSEMBLY LINE "L" LOGO DATE CODE pNoosteit:io "nP "i nind iacsasteesm "bLleya lidn-eFree" ASSEMBLY YEAR 0 = 2000 LOT CODE WEEK 02 LINE L OR PART NUMBER INTERNATIONAL RECTIFIER F530S LOGO DATE CODE P = DESIGNATES LEAD-FREE ASSEMBLY PRODUCT (OPTIONAL) LOT CODE YEAR 0 = 2000 WEEK 02 A = ASSEMBLY SITE CODE www.irf.com 9

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8)(cid:9)(cid:10) TO-262 Package Outline (Dimensions are shown in millimeters (inches)) (cid:1)(cid:1)(cid:1)(cid:1)(cid:1)IGBT 1- GATE 2- COLLECTOR 3- EMITTER 4- COLLECTOR TO-262 Part Marking Information EXAMPLE: THIS IS AN IRL3103L LOT CODE 1789 PART NUMBER INTERNATIONAL ASSEMBLED ON WW 19, 1997 RECTIFIER IN THE ASSEMBLY LINE "C" LOGO Note: "P" in assembly line DATE CODE position indicates "Lead-Free" ASSEMBLY YEAR 7 = 1997 LOT CODE WEEK 19 LINE C OR PART NUMBER INTERNATIONAL RECTIFIER LOGO DATE CODE P = DESIGNATES LEAD-FREE ASSEMBLY PRODUCT (OPTIONAL) LOT CODE YEAR 7 = 1997 WEEK 19 A = ASSEMBLY SITE CODE 10 www.irf.com

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8)(cid:9)(cid:10) (cid:1)(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:21)(cid:3)(cid:22)(cid:17)(cid:5)(cid:23)(cid:5)(cid:24)(cid:17)(cid:17)(cid:20)(cid:5)(cid:12)(cid:10)(cid:13)(cid:14)(cid:6)(cid:15)(cid:3)(cid:7)(cid:9)(cid:14)(cid:10) TRR 1.60 (.063) 1.50 (.059) 43..1900 ((..116513)) 11..6500 ((..006539)) 0.368 (.0145) 0.342 (.0135) FEED DIRECTION 1.85 (.073) 11.60 (.457) 1.65 (.065) 11.40 (.449) 1155..4222 ((..660091)) 2243..3900 ((..995471)) TRL 1.75 (.069) 10.90 (.429) 1.25 (.049) 10.70 (.421) 4.72 (.136) 16.10 (.634) 4.52 (.178) 15.90 (.626) FEED DIRECTION 13.50 (.532) 27.40 (1.079) 12.80 (.504) 23.90 (.941) 4 330.00 60.00 (2.362) (14.173) MIN. MAX. 30.40 (1.197) NOTES : MAX. 1. COMFORMS TO EIA-418. 26.40 (1.039) 4 2. CONTROLLING DIMENSION: MILLIMETER. 24.40 (.961) 34.. DINICMLEUNDSEIOSN F MLAENAGSEU RDEISDT @OR HTUIOBN. @ OUTER EDGE. 3 (cid:6)(cid:7)(cid:8)(cid:9)(cid:10)(cid:11) (cid:4)(cid:5)Repetitive rating; pulse width limited by (cid:5)(cid:1)Limited by TJmax , see Fig.12a, 12b, 15, 16 for typical repetitive max. junction temperature. (See fig. 11). avalanche performance. (cid:3) (cid:5)Limited by TJmax, starting TJ = 25°C, L = 0.16mH(cid:6)(cid:1)This value determined from sample failure population. 100% RG = 25Ω, IAS = -42A, VGS =-10V. Part not tested to this value in production. recommended for use above this value. (cid:7) This is applied to D2Pak, when mounted on 1" square PCB (FR- (cid:1) Pulse width ≤ 1.0ms; duty cycle ≤ 2%. 4 or G-10 Material). For recommended footprint and soldering (cid:2) Coss eff. is a fixed capacitance that gives the techniques refer to application note #AN-994. same charging time as Coss while VDS is rising (cid:8)(cid:5)(cid:5)(cid:20)θ(cid:7)(cid:13)(cid:19)(cid:5) (cid:15)(cid:25)(cid:19)!(cid:10)(cid:15)"(cid:5)(cid:25)(cid:26)(cid:5)(cid:23))(cid:5)(cid:25)##(cid:10)(cid:9)$(cid:13) (cid:25)(cid:26)(cid:15)(cid:17)(cid:27)(cid:5)%(cid:4)&(cid:29) from 0 to 80% VDSS . Data and specifications subject to change without notice. This product has been designed and qualified for the Industrial market. Qualification Standards can be found on IR’s Web site. IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105 TAC Fax: (310) 252-7903 Visit us at www.irf.com for sales contact information. 08/05 www.irf.com 11

Note: For the most current drawings please refer to the IR website at: http://www.irf.com/package/

Mouser Electronics Authorized Distributor Click to View Pricing, Inventory, Delivery & Lifecycle Information: I nfineon: IRF4905SPBF IRF4905LPBF IRF4905STRLPBF IRF4905STRRPBF

/IRF4905LPBF.jpg)

Datasheet下载

Datasheet下载