ICGOO在线商城 > IPB05N03LA

- 型号: IPB05N03LA

- 制造商: Infineon

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

IPB05N03LA产品简介:

ICGOO电子元器件商城为您提供IPB05N03LA由Infineon设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 提供IPB05N03LA价格参考以及InfineonIPB05N03LA封装/规格参数等产品信息。 你可以下载IPB05N03LA参考资料、Datasheet数据手册功能说明书, 资料中有IPB05N03LA详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | |

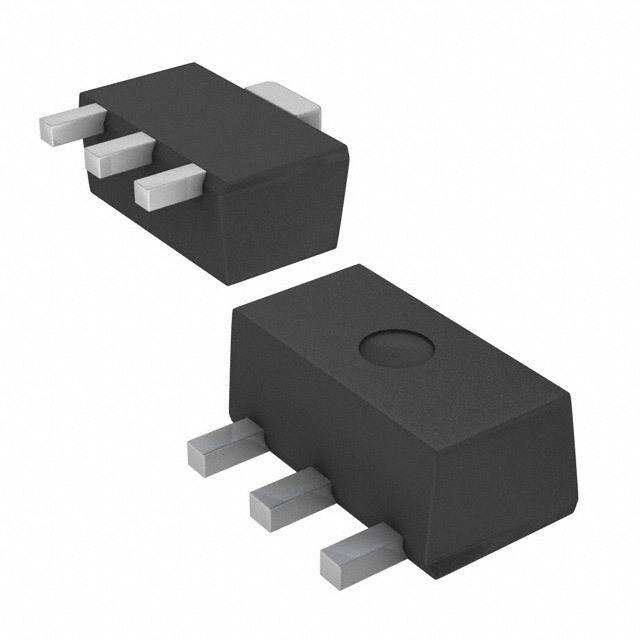

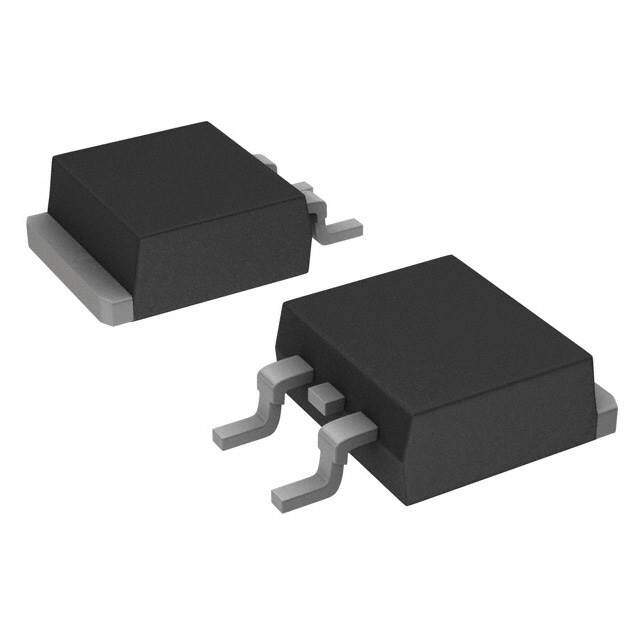

| 描述 | MOSFET N-CH 25V 80A D2PAK |

| 产品分类 | FET - 单 |

| FET功能 | 逻辑电平门 |

| FET类型 | MOSFET N 通道,金属氧化物 |

| 品牌 | Infineon Technologies |

| 数据手册 | http://www.infineon.com/dgdl/IPB05N03LA_Rev1.7_G.pdf?folderId=db3a304412b407950112b408e8c90004&fileId=db3a304412b407950112b42b51a844c4 |

| 产品图片 |

|

| 产品型号 | IPB05N03LA |

| PCN过时产品 | |

| rohs | 含铅 / 不符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | OptiMOS™ |

| 不同Id时的Vgs(th)(最大值) | 2V @ 50µA |

| 不同Vds时的输入电容(Ciss) | 3110pF @ 15V |

| 不同Vgs时的栅极电荷(Qg) | 25nC @ 5V |

| 不同 Id、Vgs时的 RdsOn(最大值) | 4.6 毫欧 @ 55A,10V |

| 产品目录页面 | |

| 供应商器件封装 | PG-TO263-3 |

| 其它名称 | IPB05N03LAINCT |

| 功率-最大值 | 94W |

| 包装 | 剪切带 (CT) |

| 安装类型 | 表面贴装 |

| 封装/外壳 | TO-263-3,D²Pak(2 引线+接片),TO-263AB |

| 标准包装 | 1 |

| 漏源极电压(Vdss) | 25V |

| 电流-连续漏极(Id)(25°C时) | 80A (Tc) |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

IPB05N03LA G OptiMOS®2 Power-Transistor Product Summary Features V 25 V DS • Ideal for high-frequency dc/dc converters R (SMD version) 4.6 mΩ DS(on),max • Qualified according to JEDEC1) for target application I 80 A D • N-channel - Logic level • Excellent gate charge x R product (FOM) DS(on) • Very low on-resistance R DS(on) PG-TO263 • Superior thermal resistance • 175 °C operating temperature • dv/dt rated • Pb-free lead plating; RoHS compliant Type Package Marking IPB05N03LA G PG-TO263 05N03LA Maximum ratings, at T=25 °C, unless otherwise specified j Parameter Symbol Conditions Value Unit Continuous drain current I T =25 °C2) 80 A D C T =100 °C 76 C Pulsed drain current I T =25 °C3) 385 D,pulse C Avalanche energy, single pulse E I =72 A, R =25 Ω 190 mJ AS D GS I =80 A, V =20 V, D DS Reverse diode dv/dt dv/dt di/dt=200 A/µs, 6 kV/µs T =175 °C j,max Gate source voltage4) VGS ±20 V Power dissipation P T =25 °C 94 W tot C Operating and storage temperature T, T -55 ... 175 °C j stg IEC climatic category; DIN IEC 68-1 55/175/56 1) J-STD20 and JESD22 Rev. 1. 7 page 1 2006-05-10

IPB05N03LA G Parameter Symbol Conditions Values Unit min. typ. max. Thermal characteristics Thermal resistance, junction - case R - - 1.6 K/W thJC SMD version, device on PCB R minimal footprint - - 62 thJA 6 cm2 cooling area5) - - 40 Electrical characteristics, at T=25 °C, unless otherwise specified j Static characteristics Drain-source breakdown voltage V V =0 V, I =1 mA 25 - - V (BR)DSS GS D Gate threshold voltage V V =V , I =50 µA 1.2 1.6 2 GS(th) DS GS D V =25 V, V =0 V, Zero gate voltage drain current I DS GS - 0.1 1 µA DSS T=25 °C j V =25 V, V =0 V, DS GS - 10 100 T=125 °C j Gate-source leakage current I V =20 V, V =0 V - 1 100 nA GSS GS DS V =4.5 V, I =55 A, Drain-source on-state resistance R GS D - 6.2 7.8 mΩ DS(on) SMD version V =10 V, I =55 A, GS D - 3.8 4.6 SMD version Gate resistance R - 1 - Ω G |V |>2|I |R , Transconductance g DS D DS(on)max 43 86 - S fs I =55 A D 2) Current is limited by bondwire; with an R =1.6 K/W the chip is able to carry 108 thJC 3) See figure 3 4) T =150 °C and duty cycle D<0.25 for j,max V <-5 V GS 5) Device on 40 mm x 40 mm x 1.5 mm epoxy PCB FR4 with 6 cm2 (one layer, 70 Rev. 1. 7 page 2 2006-05-10

IPB05N03LA G Parameter Symbol Conditions Values Unit min. typ. max. Dynamic characteristics Input capacitance C - 2413 3110 pF iss V =0 V, V =15 V, Output capacitance C GS DS - 921 1225 oss f=1 MHz Reverse transfer capacitance C - 112 167 rss Turn-on delay time t - 11 17 ns d(on) Rise time tr V =15 V, V =10 V, - 27 38 DD GS I =20 A, R =2.7 Ω Turn-off delay time t D G - 32 45 d(off) Fall time t - 4.6 6.9 f Gate Charge Characteristics6) Gate to source charge Q - 8.1 11 nC gs Gate charge at threshold Q - 3.9 5.0 g(th) Gate to drain charge Qgd V =15 V, I =40 A, - 5.3 8.0 DD D V =0 to 5 V Switching charge Q GS - 10 14 sw Gate charge total Q - 19 25 g Gate plateau voltage V - 3.4 - V plateau V =0.1 V, Gate charge total, sync. FET Q DS - 17 22 nC g(sync) V =0 to 5 V GS Output charge Q V =15 V, V =0 V - 20 27 oss DD GS Reverse Diode Diode continous forward current I - - 80 A S T =25 °C C Diode pulse current I - - 385 S,pulse V =0 V, I =80 A, Diode forward voltage V GS F - 0.97 1.2 V SD T=25 °C j V =15 V, I =I , Reverse recovery charge Q R F S - - 10 nC rr di /dt=400 A/µs F 6) See figure 16 for gate charge parameter definition Rev. 1. 7 page 3 2006-05-10

IPB05N03LA G 1 Power dissipation 2 Drain current P =f(T ) I =f(T ); V ≥10 V tot C D C GS 100 100 90 80 80 70 60 60 W] A] P [tot 50 I [D 40 40 30 20 20 10 0 0 0 50 100 150 200 0 50 100 150 200 T [°C] T [°C] C C 3 Safe operating area 4 Max. transient thermal impedance I =f(V ); T =25 °C; D=0 Z =f(t ) D DS C thJC p parameter: t parameter: D=t /T p p 1000 10 1 µs limited by on-state resistance 10 µs 1 0.5 100 0.2 100 µs W] 0.1 A] DC K/ [D [C 0.1 0.05 I 1 ms thJ 0.02 Z 0.01 single pulse 10 10 ms 0.01 1 0.001 0.1 1 10 100 010-6 100-5 100-4 10-03 10-20 10-1 0 100 1 V [V] t [s] DS p Rev. 1. 7 page 4 2006-05-10

IPB05N03LA G 5 Typ. output characteristics 6 Typ. drain-source on resistance I =f(V ); T=25 °C R =f(I ); T=25 °C D DS j DS(on) D j parameter: V parameter: V GS GS 140 25 10 V 4.5 V 3.2 V 3.5 V 3.8 V 4.1 V 120 3 V 20 4.1 V 100 ]Ω 15 80 m A] 3.8 V [ [D on) I 60 DS( R 10 3.5 V 4.5 V 40 5 3.2 V 10 V 20 3 V 2.8 V 0 0 0 1 2 3 0 20 40 60 80 100 120 140 V [V] I [A] DS D 7 Typ. transfer characteristics 8 Typ. forward transconductance I =f(V ); |V |>2|I |R g =f(I ); T=25 °C D GS DS D DS(on)max fs D j parameter: T j 160 120 140 100 120 80 100 A] S] [D 80 [fs 60 I g 60 40 40 20 20 175 °C 25 °C 0 0 0 1 2 3 4 5 0 20 40 60 80 V [V] I [A] GS D Rev. 1. 7 page 5 2006-05-10

IPB05N03LA G 9 Drain-source on-state resistance 10 Typ. gate threshold voltage R =f(T); I =55 A; V =10 V V =f(T); V =V DS(on) j D GS GS(th) j GS DS parameter: I D 10 2.5 9 8 2 7 500 µA m]Ω 6 98 % V] 1.5 R [DS(on) 45 typ V [GS(th) 1 50 µA 3 2 0.5 1 0 0 -60 -20 20 60 100 140 180 -60 -20 20 60 100 140 180 T [°C] T [°C] j j 11 Typ. Capacitances 12 Forward characteristics of reverse diode C=f(V ); V =0 V; f=1 MHz I =f(V ) DS GS F SD parameter: T j 10000 1000 Ciss 175 °C Coss 25 °C 1000 100 175°C 98% pF] A] [ [F C I Crss 100 10 25°C 98% 10 1 0 5 10 15 20 25 30 0.0 0.5 1.0 1.5 2.0 V [V] V [V] DS SD Rev. 1. 7 page 6 2006-05-10

IPB05N03LA G 13 Avalanche characteristics 14 Typ. gate charge I =f(t ); R =25 Ω V =f(Q ); I =40 A pulsed AS AV GS GS gate D parameter: T parameter: V j(start) DD 100 12 25 °C 100 °C 15 V 150 °C 10 5 V 20 V 8 A] V] [V 10 [S 6 A G I V 4 2 1 0 1 10 100 1000 0 10 20 30 40 t [µs] Q [nC] AV gate 15 Drain-source breakdown voltage 16 Gate charge waveforms V =f(T); I =1 mA BR(DSS) j D 29 V GS 28 Q g 27 26 V] [S) 25 S D BR( 24 V V gs(th) 23 22 21 Qg(th) Qsw Qgate Q Q 20 gs gd -60 -20 20 60 100 140 180 T [°C] j Rev. 1. 7 page 7 2006-05-10

IPB05N03LA G PG-TO263-3-2/TO263-3-5/TO263-3-22: Outlines Footprint Packaging Rev. 1. 7 page 8 2006-05-10

IPB05N03LA G Published by Infineon Technologies AG 81726 München, Germany © Infineon Technologies AG 2006. All Rights Reserved. Attention please! The information given in this data sheet shall in no event be regarded as a guarantee of conditions or characteristics (“Beschaffenheitsgarantie”). With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party. Information For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com). Warnings Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office. Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered. Rev. 1. 7 page 9 2006-05-10

Datasheet下载

Datasheet下载