ICGOO在线商城 > 分立半导体产品 > 晶体管 - FET,MOSFET - 单 > FDB070AN06A0

- 型号: FDB070AN06A0

- 制造商: Fairchild Semiconductor

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

FDB070AN06A0产品简介:

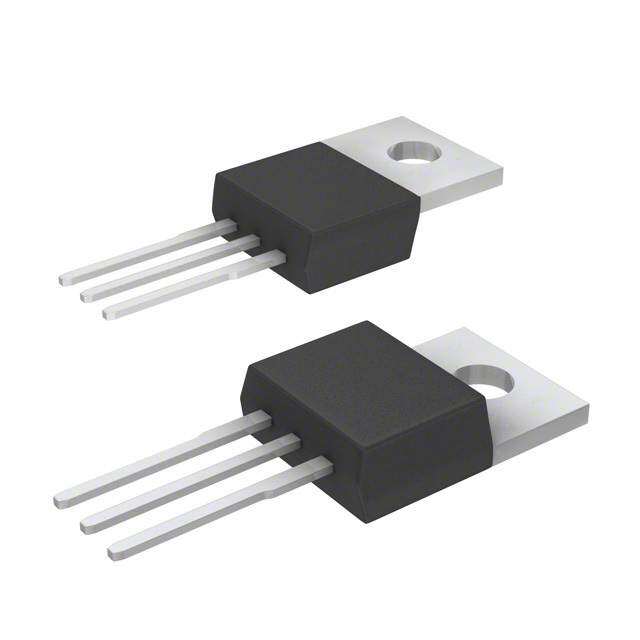

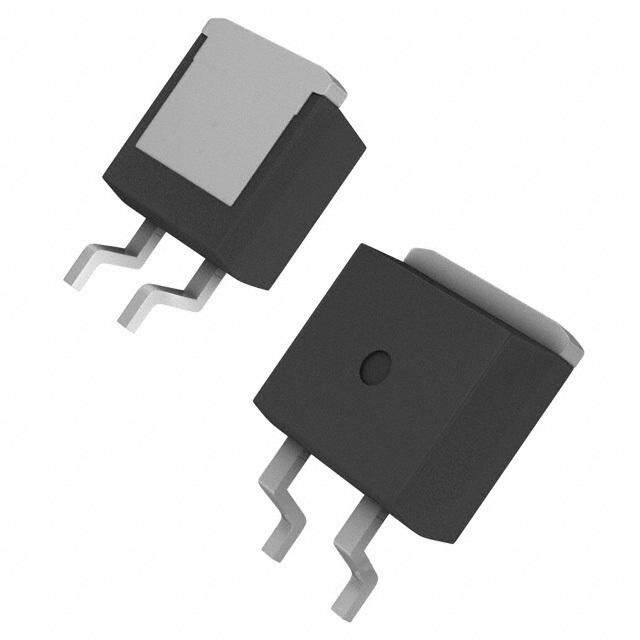

ICGOO电子元器件商城为您提供FDB070AN06A0由Fairchild Semiconductor设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 FDB070AN06A0价格参考。Fairchild SemiconductorFDB070AN06A0封装/规格:晶体管 - FET,MOSFET - 单, 表面贴装 N 沟道 60V 15A(Ta),80A(Tc) 175W(Tc) D²PAK。您可以下载FDB070AN06A0参考资料、Datasheet数据手册功能说明书,资料中有FDB070AN06A0 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | |

| ChannelMode | Enhancement |

| 描述 | MOSFET N-CH 60V 80A TO-263ABMOSFET N-Channel PT 6V 8A 7mOhm |

| 产品分类 | FET - 单分离式半导体 |

| FET功能 | 标准 |

| FET类型 | MOSFET N 通道,金属氧化物 |

| Id-ContinuousDrainCurrent | 80 A |

| Id-连续漏极电流 | 80 A |

| 品牌 | Fairchild Semiconductor |

| 产品手册 | |

| 产品图片 |

|

| rohs | RoHS 合规性豁免无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 晶体管,MOSFET,Fairchild Semiconductor FDB070AN06A0PowerTrench® |

| 数据手册 | |

| 产品型号 | FDB070AN06A0 |

| PCN封装 | |

| Pd-PowerDissipation | 175 W |

| Pd-功率耗散 | 175 W |

| RdsOn-Drain-SourceResistance | 6.1 mOhms |

| RdsOn-漏源导通电阻 | 6.1 mOhms |

| Vds-Drain-SourceBreakdownVoltage | 60 V |

| Vds-漏源极击穿电压 | 60 V |

| Vgs-Gate-SourceBreakdownVoltage | +/- 20 V |

| Vgs-栅源极击穿电压 | 20 V |

| 上升时间 | 159 ns |

| 下降时间 | 35 ns |

| 不同Id时的Vgs(th)(最大值) | 4V @ 250µA |

| 不同Vds时的输入电容(Ciss) | 3000pF @ 25V |

| 不同Vgs时的栅极电荷(Qg) | 66nC @ 10V |

| 不同 Id、Vgs时的 RdsOn(最大值) | 7 毫欧 @ 80A,10V |

| 产品培训模块 | http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=356 |

| 产品种类 | MOSFET |

| 供应商器件封装 | TO-263AB |

| 其它名称 | FDB070AN06A0-ND |

| 典型关闭延迟时间 | 27 ns |

| 功率-最大值 | 175W |

| 包装 | 带卷 (TR) |

| 单位重量 | 1.312 g |

| 商标 | Fairchild Semiconductor |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装 | Reel |

| 封装/外壳 | TO-263-3,D²Pak(2 引线+接片),TO-263AB |

| 封装/箱体 | D2PAK-2 |

| 工厂包装数量 | 800 |

| 晶体管极性 | N-Channel |

| 最大工作温度 | + 175 C |

| 最小工作温度 | - 55 C |

| 标准包装 | 800 |

| 漏源极电压(Vdss) | 60V |

| 电流-连续漏极(Id)(25°C时) | 15A (Ta), 80A (Tc) |

| 系列 | FDB070AN06A0 |

| 通道模式 | Enhancement |

| 配置 | Single |

| 零件号别名 | FDB070AN06A0_NL |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

Is Now Part of To learn more about ON Semiconductor, please visit our website at www.onsemi.com Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor’s system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (_), the underscore (_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at www.onsemi.com. Please email any questions regarding the system integration to Fairchild_questions@onsemi.com. ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor’s product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. “Typical” parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

F D B 0 October 2013 7 0 A FDB070AN06A0 N 0 ® 6 N-Channel PowerTrench MOSFET A 0 60 V, 80 A, 7 mΩ — Features Applications N - C • RDS(on) = 6.1 mΩ ( Typ.) @ VGS = 10 V, ID = 80 A • Synchronous Rectification for ATX / Server / Telecom PSU h a • Qg(tot) = 51 nC ( Typ.) @ VGS = 10 V • Battery Protection Circuit n n • Low Miller Charge • Motor Drives and Uninterruptible Power Supplies e l • Low Qrr Body Diode P o • UIS Capability (Single Pulse and Repetitive Pulse) w e r T Formerly developmental type 82567 r e n c D h ® M D O S F G E G S D2-PAK T S MOSFET Maximum Ratings TC = 25°C unless otherwise noted Symbol Parameter FDB070AN06A0 Unit V Drain to Source Voltage 60 V DSS V Gate to Source Voltage ±20 V GS Drain Current Continuous (T < 97oC, V = 10V) 80 A I C GS D Continuous (TA = 25oC, VGS = 10V, RθJA = 43oC/W) 15 A Pulsed Figure 4 A E Single Pulse Avalanche Energy (Note 1) 190 mJ AS Power dissipation 175 W P D Derate above 25oC 1.17 W/oC T , T Operating and Storage Temperature -55 to 175 oC J STG Thermal Characteristics RθJC Thermal Resistance Junction to Case, Max. 0.86 oC/W RθJA Thermal Resistance Junction to Ambient, Max. (Note 2) 62 oC/W RθJA Thermal Resistance Junction to Ambient, Max., 1in2 copper pad area 43 oC/W ©2003 Fairchild Semiconductor Corporation 1 www.fairchildsemi.com FDB070AN06A0 Rev. C2

F D Package Marking and Ordering Information B 0 Device Marking Device Package Reel Size Tape Width Quantity 7 FDB070AN06A0 FDB070AN06A0 D2-PAK 330 mm 24 mm 800 units 0 A N 0 6 Electrical Characteristics T = 25°C unless otherwise noted A C 0 Symbol Parameter Test Conditions Min Typ Max Unit — Off Characteristics N - B Drain to Source Breakdown Voltage I = 250µA, V = 0V 60 - - V C VDSS D GS h IDSS Zero Gate Voltage Drain Current VVDS == 50V0V T = 150oC -- -- 2150 µA an GS C n I Gate to Source Leakage Current V = ±20V - - ±100 nA e GSS GS l P On Characteristics o w V Gate to Source Threshold Voltage V = V , I = 250µA 2 - 4 V GS(TH) GS DS D e ID = 80A, VGS = 10V - 0.0061 0.007 rT rDS(ON) Drain to Source On Resistance ID = 80A, VGS = 10V, - 0.0127 0.015 Ω re T = 175oC n J c h Dynamic Characteristics ® M C Input Capacitance - 3000 - pF ISS V = 25V, V = 0V, O C Output Capacitance DS GS - 510 - pF OSS f = 1MHz S C Reverse Transfer Capacitance - 230 - pF F RSS E Qg(TOT) Total Gate Charge at 10V VGS = 0V to 10V 51 66 nC T Qg(TH) Threshold Gate Charge VGS = 0V to 2V VDD = 30V - 5.4 7 nC Q Gate to Source Gate Charge I = 80A - 17 - nC gs D Qgs2 Gate Charge Threshold to Plateau Ig = 1.0mA - 11.6 - nC Q Gate to Drain “Miller” Charge - 16 - nC gd Switching Characteristics (V = 10V) GS t Turn-On Time - - 256 ns ON t Turn-On Delay Time - 12 - ns d(ON) tr Rise Time VDD = 30V, ID = 80A - 159 - ns td(OFF) Turn-Off Delay Time VGS = 10V, RGS = 5.6Ω - 27 - ns t Fall Time - 35 - ns f t Turn-Off Time - - 93 ns OFF Drain-Source Diode Characteristics I = 80A - - 1.25 V V Source to Drain Diode Voltage SD SD I = 40A - - 1.0 V SD t Reverse Recovery Time I = 75A, dI /dt = 100A/µs - - 34 ns rr SD SD Q Reverse Recovered Charge I = 75A, dI /dt = 100A/µs - - 35 nC RR SD SD Notes: 1: Starting TJ = 25°C, L = 93µH, IAS = 64A. 2: Pulse width = 100s. ©2003 Fairchild Semiconductor Corporation 2 www.fairchildsemi.com FDB070AN06A0 Rev. C2

F D Typical Characteristics TC = 25°C unless otherwise noted B 0 1.2 120 70 CURRENT LIMITED A BY PACKAGE R 1.0 100 N PLIE A) 06 N MULTI 0.8 RRENT ( 80 A0 — O 0.6 U 60 WER DISSIPATI 00..24 I, DRAIN CD 2400 N-Cha O n P n 0 0 e l 0 25 50 75 100 125 150 175 25 50 75 100 125 150 175 P TC, CASE TEMPERATURE (oC) TC, CASE TEMPERATURE (oC) ow e Figure 1. Normalized Power Dissipation vs Figure 2. Maximum Continuous Drain Current vs r Ambient Temperature Case Temperature T r e n 2 c h DUTY CYCLE - DESCENDING ORDER ® 1 0.5 0.2 M 0.1 O E 0.05 S EDNC 0.02 F ORMALIZL IMPEDA 0.1 0.01 PDM ET NA Z, θJCHERM t1t2 T NOTES: DUTY FACTOR: D = t1/t2 SINGLE PULSE PEAK TJ = PDM x ZθJC x RθJC + TC 0.01 10-5 10-4 10-3 10-2 10-1 100 101 t, RECTANGULAR PULSE DURATION (s) Figure 3. Normalized Maximum Transient Thermal Impedance 2000 TC = 25oC FOR TEMPERATURES 1000 ABOVE 25oC DERATE PEAK A) CURRENT AS FOLLOWS: T ( RREN VGS = 10V I = I25 17155 -0 TC U C K A E P TRANSCONDUCTANCE , M MAY LIMIT CURRENT ID 100 IN THIS REGION 50 10-5 10-4 10-3 10-2 10-1 100 101 t, PULSE WIDTH (s) Figure 4. Peak Current Capability ©2003 Fairchild Semiconductor Corporation 3 www.fairchildsemi.com FDB070AN06A0 Rev. C2

F D Typical Characteristics TC = 25°C unless otherwise noted B 0 7 1000 500 If R = 0 0 10µs tIfA VR =≠ (0L)(IAS)/(1.3*RATED BVDSS - VDD) AN A) 100 100µs NT (A) 100 tAV = (L/R)ln[(IAS*R)/(1.3*RATED BVDSS - VDD) +1] 06 I, DRAIN CURRENT (D 110 OSLPIINMEGIARTLRAEETED IPA OBU NMYL AISrNDYE S TB(OHENIS) DC 10m1sms I, AVALANCHE CURREAS 10 STARTING TJ = 1S5T0AoCRTING TJ = 25oC A0 — N-Chan TJ = MAX RATED n TC = 25oC e 0.1 1 l 1 10 100 0.01 0.1 1 10 100 P VDS, DRAIN TO SOURCE VOLTAGE (V) tAV, TIME IN AVALANCHE (ms) o w Figure 5. Forward Bias Safe Operating Area NOTE: Refer to Fairchild Application Notes AN7514 and AN7515 e r Figure 6. Unclamped Inductive Switching T Capability r e n c h 160 160 PULSE DURATION = 80µs ® DVDUDT =Y 1C5YVCLE = 0.5% MAX VGS = 10V VGS = 7V MO A)120 A) 120 S ENT ( ENT ( FE RR RR VGS = 6V T CU 80 CU 80 N N I, DRAID 40 TJ = 25oC I, DRAID 40 PDUULTSYE C DYUCRLEA T=I O0 T.N5C %= = 8 M205AµosXC TJ = 175oC TJ = -55oC VGS = 5V 0 0 0 0.5 1.0 1.5 2.0 4.0 4.5 5.0 5.5 6.0 6.5 7.0 VGS, GATE TO SOURCE VOLTAGE (V) VDS, DRAIN TO SOURCE VOLTAGE (V) Figure 7. Transfer Characteristics Figure 8. Saturation Characteristics 16 2.5 Ω) PULSE DURATION = 80µs PULSE DURATION = 80µs m DUTY CYCLE = 0.5% MAX DUTY CYCLE = 0.5% MAX E( CE C 14 R N U 2.0 A O ON RESIST 12 VGS = 6V RAIN TO SSISTANCE1.5 RCE 10 ED DN RE OU LIZO S A AIN TO 8 VGS = 10V NORM 1.0 DR VGS = 10V, ID =80A 6 0.5 0 20 40 60 80 -80 -40 0 40 80 120 160 200 ID, DRAIN CURRENT (A) TJ, JUNCTION TEMPERATURE (oC) Figure 9. Drain to Source On Resistance vs Drain Figure 10. Normalized Drain to Source On Current Resistance vs Junction Temperature ©2003 Fairchild Semiconductor Corporation 4 www.fairchildsemi.com FDB070AN06A0 Rev. C2

F D Typical Characteristics TC = 25°C unless otherwise noted B 0 7 1.2 1.10 0 VGS = VDS, ID = 250µA ID = 250µA A CE N MALIZED GATEHOLD VOLTAGE 01..80 D DRAIN TO SOURDOWN VOLTAGE 11..0005 06A0 — N NORTHRES 0.6 MALIZEBREAK 0.95 -Ch OR a N n n 0.4 0.90 e l -80 -40 0 40 80 120 160 200 -80 -40 0 40 80 120 160 200 P TJ, JUNCTION TEMPERATURE (oC) TJ, JUNCTION TEMPERATURE (oC) o w Figure 11. Normalized Gate Threshold Voltage vs Figure 12. Normalized Drain to Source e r Junction Temperature Breakdown Voltage vs Junction Temperature T r e n 10000 10 c h VDD = 30V ® CISS = CGS + CGD AGE (V) 8 MO pF) OLT S NCE ( COSS ≅ CDS + CGD CE V 6 FE TA 1000 UR T CI O C, CAPA CRSS = CGD ATE TO S 4 WAVEFORMS IN VGS = 0V, f = 1MHz V, GGS2 DESCIIDDE ==N 81D05INAAG ORDER: 100 0 0.1 1 10 60 0 10 20 30 40 50 60 VDS, DRAIN TO SOURCE VOLTAGE (V) Qg, GATE CHARGE (nC) Figure 13. Capacitance vs Drain to Source Figure 14. Gate Charge Waveforms for Constant Voltage Gate Current ©2003 Fairchild Semiconductor Corporation 5 www.fairchildsemi.com FDB070AN06A0 Rev. C2

F D Test Circuits and Waveforms B 0 7 0 A VDS N BVDSS 0 6 L tP A VDS 0 VRAERQYU ItRP ETDO POEBATKA IINAS RG +VDD IAS VDD — N VGS - -C DUT h a tP n 0V IAS n 0.01Ω 0 el P tAV o w e Figure 15. Unclamped Energy Test Circuit Figure 16. Unclamped Energy Waveforms r T r e n c VDS h ® VDD Qg(TOT) M L VDS O VGS VGS = 10V S VGS + FE VDD Qgs2 T - DUT Ig(REF) VGS = 2V 0 Qg(TH) Qgs Qgd Ig(REF) 0 Figure 17. Gate Charge Test Circuit Figure 18. Gate Charge Waveforms VDS tON tOFF td(ON) td(OFF) RL tr tf VDS 90% 90% + VGS VDD 10% 10% - 0 DUT 90% RGS VGS 50% 50% PULSE WIDTH VGS 10% 0 Figure 19. Switching Time Test Circuit Figure 20. Switching Time Waveforms ©2003 Fairchild Semiconductor Corporation 6 www.fairchildsemi.com FDB070AN06A0 Rev. C2

F D Thermal Resistance vs. Mounting Pad Area B 0 The maximum rated junction temperature, TJM, and the 80 7 thermal resistance of the heat dissipating path determines RθJA = 26.51+ 19.84/(0.262+Area) EQ.2 0A the maximum allowable device power dissipation, P , in an DM N application. Therefore the application’s ambient RθJA = 26.51+ 128/(1.69+Area) EQ.3 0 temperature, TA (oC), and thermal resistance RθJA (oC/W) 6 must be reviewed to ensure that T is never exceeded. 60 A JM W) 0 Equation 1 mathematically represents the relationship and C/ serves as the basis for establishing the rating of the part. o(A — (T –T ) RθJ N PDM = -------J-R--M---θ---J----A----A----- (EQ. 1) 40 -Ch a n In using surface mount devices such as the TO-263 n package, the environment in which it is applied will have a 20 e l significant influence on the part’s current and maximum 0.1 1 10 P power dissipation ratings. Precise determination of PDM is (0.645) (6.45) (64.5) o complex and influenced by many factors: AREA, TOP COPPER AREA in2 (cm2) w Figure 21. Thermal Resistance vs Mounting e 1. Mounting pad area onto which the device is attached and Pad Area rT whether there is copper on one side or both sides of the r e board. n c 2. The number of copper layers and the thickness of the h board. ® M 3.The use of external heat sinks. O S 4.The use of thermal vias. F E 5.Air flow and board orientation. T 6. For non steady state applications, the pulse width, the duty cycle and the transient thermal response of the part, the board and the environment they are in. Fairchild provides thermal information to assist the designer’s preliminary application evaluation. Figure 21 defines the RθJA for the device as a function of the top copper (component side) area. This is for a horizontally positioned FR-4 board with 1oz copper after 1000 seconds of steady state power with no air flow. This graph provides the necessary information for calculation of the steady state junction temperature or power dissipation. Pulse applications can be evaluated using the Fairchild device Spice thermal model or manually utilizing the normalized maximum transient thermal impedance curve. Thermal resistances corresponding to other copper areas can be obtained from Figure 21 or by calculation using Equation 2 or 3. Equation 2 is used for copper area defined in inches square and equation 3 is for area in centimeters square. The area, in square inches or square centimeters is the top copper area including the gate and source pads. 19.84 RθJA = 26.51+(---0---.-2---6---2-----+-----A----r---e---a---)- (EQ. 2) Area in Inches Squared 128 RθJA = 26.51+(---1---.-6---9-----+-----A----r---e---a----) (EQ. 3) Area in Centimeters Squared ©2003 Fairchild Semiconductor Corporation 7 www.fairchildsemi.com FDB070AN06A0 Rev. C2

F PSPICE Electrical Model D B .SUBCKT FDB070AN06A0 2 1 3 ; rev March 2003 0 Ca 12 8 1.5e-9 7 0 Cb 15 14 1.5e-9 LDRAIN A Cin 6 8 2.9e-9 DPLCAP 5 DRAIN N 2 10 0 Dbody 7 5 DbodyMOD RLDRAIN 6 Dbreak 5 11 DbreakMOD 5R1SLC1 DBREAK A Dplcap 10 5 DplcapMOD RSLC2 + 0 551 ESLC 11 — Ebreak 11 7 17 18 62 - Eds 14 8 5 8 1 - 50 + N EEEEgsvvgttshe 16rme3 1ps 80 26 660 2 8861 111189 28 21 1 LGATE EVETSEGM+P68 E+VT18H9RE-S 2R1DR1A6IN EBMRWEAEKAK-1178 DBODY -Chan GATE RGATE + 18 - 6 n It 8 17 1 1 9 20 22 MMED el RLGATE MSTRO P LLdgraatein 12 95 41..80ee--99 CIN 8 7 LSOURCE SOU3RCE ow Lsource 3 7 3e-9 RSOURCE e RLSOURCE r T RLgate 1 9 48 S1A S2A r RRLLdsorauirnc e2 35 71 03 12 183 1143 15 17 RBREAK 18 en c S1B S2B RVTEMP h MMmstreod 1166 66 88 88 MMsmtreodMMOODD CA 13++ CB+ 14 IT -19 M® Mweak 16 21 8 8 MweakMOD EGS 68 EDS 58 + VBAT O S Rbreak 17 18 RbreakMOD 1 -- - 8 F Rdrain 50 16 RdrainMOD 1.3e-3 22 E Rgate 9 20 2.7 RVTHRES T RSLC1 5 51 RSLCMOD 1e-6 RSLC2 5 50 1e3 Rsource 8 7 RsourceMOD 3.1e-3 Rvthres 22 8 RvthresMOD 1 Rvtemp 18 19 RvtempMOD 1 S1a 6 12 13 8 S1AMOD S1b 13 12 13 8 S1BMOD S2a 6 15 14 13 S2AMOD S2b 13 15 14 13 S2BMOD Vbat 22 19 DC 1 ESLC 51 50 VALUE={(V(5,51)/ABS(V(5,51)))*(PWR(V(5,51)/(1e-6*250),10))} .MODEL DbodyMOD D (IS=7.6E-12 N=1.04 RS=2.2e-3 TRS1=2.7e-3 TRS2=2e-7 + CJO=1.6e-9 M=0.55 TT=5e-12 XTI=3.9) .MODEL DbreakMOD D (RS=8e-1 TRS1=5e-4 TRS2=-8.9e-6) .MODEL DplcapMOD D (CJO=1.05e-9 IS=1e-30 N=10 M=0.45) .MODEL MmedMOD NMOS (VTO=3.7 KP=10 IS=1e-30 N=10 TOX=1 L=1u W=1u RG=2.7) .MODEL MstroMOD NMOS (VTO=4.7 KP=100 IS=1e-30 N=10 TOX=1 L=1u W=1u) .MODEL MweakMOD NMOS (VTO=3.01 KP=0.03 IS=1e-30 N=10 TOX=1 L=1u W=1u RG=27 RS=0.1) .MODEL RbreakMOD RES (TC1=7.1e-4 TC2=-5.5e-7) .MODEL RdrainMOD RES (TC1=1.7e-2 TC2=4e-5) .MODEL RSLCMOD RES (TC1=3e-3 TC2=1e-5) .MODEL RsourceMOD RES (TC1=1e-3 TC2=1e-6) .MODEL RvthresMOD RES (TC1=-5.2e-3 TC2=-1.5e-5) .MODEL RvtempMOD RES (TC1=-3e-3 TC2=1.3e-6) .MODEL S1AMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-4 VOFF=-2) .MODEL S1BMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-2 VOFF=-4) .MODEL S2AMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-1.5 VOFF=0.5) .MODEL S2BMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=0.5 VOFF=-1.5) .ENDS Note: For further discussion of the PSPICE model, consult A New PSPICE Sub-Circuit for the Power MOSFET Featuring Global Temperature Options; IEEE Power Electronics Specialist Conference Records, 1991, written by William J. Hepp and C. Frank Wheatley. ©2003 Fairchild Semiconductor Corporation 8 www.fairchildsemi.com FDB070AN06A0 Rev. C2

F SABER Electrical Model D B 0 rev March 2003 7 template FDB070AN06A0 n2,n1,n3 0 electrical n2,n1,n3 A { N var i iscl 0 dp..model dbodymod = (isl=7.6e-12,nl=1.04,rs=2.2e-3,trs1=2.7e-3,trs2=2e-7,cjo=1.6e-9,m=0.55,tt=5e-12,xti=3.9) 6 A dp..model dbreakmod = (rs=8e-1,trs1=5e-4,trs2=-8.9e-6) 0 dp..model dplcapmod = (cjo=1.05e-9,isl=10e-30,nl=10,m=0.45) m..model mmedmod = (type=_n,vto=3.7,kp=10,is=1e-30, tox=1) — m..model mstrongmod = (type=_n,vto=4.7,kp=100,is=1e-30, tox=1) N m..model mweakmod = (type=_n,vto=3.01,kp=0.03,is=1e-30, tox=1,rs=0.1) LDRAIN - sw_vcsp..model s1amod = (ron=1e-5,roff=0.1,von=-4,voff=-2) DPLCAP 5 DRAIN C sw_vcsp..model s1bmod = (ron=1e-5,roff=0.1,von=-2,voff=-4) 2 h sw_vcsp..model s2amod = (ron=1e-5,roff=0.1,von=-1.5,voff=0.5) 10 a sw_vcsp..model s2bmod = (ron=1e-5,roff=0.1,von=0.5,voff=-1.5) RSLC1 RLDRAIN n n c.ca n12 n8 = 1.5e-9 51 RSLC2 e c.cb n15 n14 = 1.5e-9 l c.cin n6 n8 = 2.9e-9 ISCL P 50 DBREAK o dp.dbody n7 n5 = model=dbodymod - w ddpp..ddbprlceaapk nn150 n n151 == mmooddeell==ddpblrceaapkmmoodd ESG+68 EVTHRES RDR1A6IN 11 DBODY erT spe.ebreak n11 n7 n17 n18 = 62 LGATE EVTEMP + 189 - 21 MWEAK re ssppee..eedgss nn1143 nn88 nn56 nn88 == 11 GA1TE 9RGATE20+ 1282 - 6 MMED EBREAK+ nch spe.esg n6 n10 n6 n8 = 1 RLGATE MSTRO 1178 LSOURCE ® ssppee..eevvtthermeps nn260 n 2n16 nn1198 nn82 2= = 1 1 CIN 8 - 7 SOU3RCE MO RSOURCE S i.it n8 n17 = 1 RLSOURCE F S1A S2A l.lgate n1 n9 = 4.8e-9 12 13 14 15 17 RBREAK 18 ET 8 13 l.ldrain n2 n5 = 1.0e-9 l.lsource n3 n7 = 3e-9 S1B S2B RVTEMP CA 13 CB 19 res.rlgate n1 n9 = 48 ++ + 14 IT - rreess..rrlldsorauirnc en 2n 3n 5n 7= =1 03 EGS 68 EDS 58 + VBAT -- - 8 22 m.mmed n16 n6 n8 n8 = model=mmedmod, l=1u, w=1u RVTHRES m.mstrong n16 n6 n8 n8 = model=mstrongmod, l=1u, w=1u m.mweak n16 n21 n8 n8 = model=mweakmod, l=1u, w=1u res.rbreak n17 n18 = 1, tc1=7.1e-4,tc2=-5.5e-7 res.rdrain n50 n16 = 1.3e-3, tc1=1.7e-2,tc2=4e-5 res.rgate n9 n20 = 2.7 res.rslc1 n5 n51 = 1e-6, tc1=3e-3,tc2=1e-5 res.rslc2 n5 n50 = 1e3 res.rsource n8 n7 = 3.1e-3, tc1=1e-3,tc2=1e-6 res.rvthres n22 n8 = 1, tc1=-5.2e-3,tc2=-1.5e-5 res.rvtemp n18 n19 = 1, tc1=-3e-3,tc2=1.3e-6 sw_vcsp.s1a n6 n12 n13 n8 = model=s1amod sw_vcsp.s1b n13 n12 n13 n8 = model=s1bmod sw_vcsp.s2a n6 n15 n14 n13 = model=s2amod sw_vcsp.s2b n13 n15 n14 n13 = model=s2bmod v.vbat n22 n19 = dc=1 equations { i (n51->n50) +=iscl iscl: v(n51,n50) = ((v(n5,n51)/(1e-9+abs(v(n5,n51))))*((abs(v(n5,n51)*1e6/250))** 10)) } } ©2003 Fairchild Semiconductor Corporation 9 www.fairchildsemi.com FDB070AN06A0 Rev. C2

F SPICE Thermal Model D B th JUNCTION 0 REV 23 March 2003 7 0 A FDB070AN06A0T N CTHERM1 TH 6 3.5e-3 0 6 CTHERM2 6 5 1.7e-2 A CTHERM3 5 4 1.8e-2 RTHERM1 CTHERM1 0 CTHERM4 4 3 1.9e-2 — CTHERM5 3 2 4.7e-2 CTHERM6 2 TL 7e-2 N 6 - RTHERM1 TH 6 2e-2 C RTHERM2 6 5 7e-2 h a RTHERM3 5 4 1e-1 RTHERM2 CTHERM2 n RTHERM4 4 3 1.5e-1 n RTHERM5 3 2 1.6e-1 e RTHERM6 2 TL 1.85e-1 l P 5 o w SABER Thermal Model e r SABER thermal model FDB070AN06A0T RTHERM3 CTHERM3 T template thermal_model th tl re thermal_c th, tl n { c ctherm.ctherm1 th 6 =3.5e-3 4 h ® ctherm.ctherm2 6 5 =1.7e-2 ctherm.ctherm3 5 4 =1.8e-2 M ctherm.ctherm4 4 3 =1.9e-2 RTHERM4 CTHERM4 O ctherm.ctherm5 3 2 =4.7e-2 S ctherm.ctherm6 2 tl =7e-2 F E rtherm.rtherm1 th 6 =2e-2 3 T rtherm.rtherm2 6 5 =7e-2 rtherm.rtherm3 5 4 =1e-1 rtherm.rtherm4 4 3 =1.5e-1 RTHERM5 CTHERM5 rtherm.rtherm5 3 2 =1.6e-1 rtherm.rtherm6 2 tl =1.85e-1 } 2 RTHERM6 CTHERM6 tl CASE ©2003 Fairchild Semiconductor Corporation 10 www.fairchildsemi.com FDB070AN06A0 Rev. C2

F D Mechanical Dimensions B 0 7 2 0 TO-263 2L (D PAK) A N 0 6 A 0 — N - C h a n n e l P o w e r T r e n c h ® M O S F E T Figure 22. 2LD, TO263, Surface Mount Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specif- ically the warranty therein, which covers Fairchild products. Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings: http://www.fairchildsemi.com/package/packageDetails.html?id=PN_TT263-002 Dimension in Millimeters ©2003 Fairchild Semiconductor Corporation 11 www.fairchildsemi.com FDB070AN06A0 Rev. C2

F D B 0 7 0 A N 0 TRADEMARKS 6 The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not A 0 intended to be an exhaustive list of all such trademarks. — AccuPower™ F-PFS™ Sync-Lock™ BAiXtS-CiCA™P®* FGRloFbEaTl P®ower ResourceSM Powtm®erTrench® ®* N - Build it Now™ GreenBridge™ PowerXS™ TinyBoost® C CCoorreePPOLUWSE™R™ GGrreeeenn FFPPSS™™ e-Series™ PQrFoEgTra®mmable Active Droop™ TinyBuck® ha TinyCalc™ CCTRLO™SSVOLT™ GGmTOax™™ QQSui™et Series™ TinyLogic® nn Current Transfer Logic™ IntelliMAX™ RapidConfigure™ TINYOPTO™ e DEUXPEED® ISOPLANAR™ ™ TTiinnyyPPoWwMe™r™ Pl Dual Cool™ Marking Small Speakers Sound Louder EcoSPARK® and Better™ Saving our world, 1mW/W/kW at a time™ TTirnaynWSiiCre™™ ow EfficentMax™ MegaBuck™ SignalWise™ TriFault Detect™ e ESBC™ MICROCOUPLER™ SmartMax™ TRUECURRENT®* r ® MMiiccrrooPFEakT™™ SSMoluAtRioTn sS fToAr RYTou™r Success™ SerDes™ Tr Fairchild® MicroPak2™ SPM® en FFAaiCrcTh iQldu Sieet mSiecroiensd™uctor® MMiollteiorDnMrivaex™™ SSTupEeArLFTEHT™® UHC® ch FACT® mWSaver® SuperSOT™-3 Ultra FRFET™ ® FAST® OptoHiT™ SuperSOT™-6 UniFET™ M FastvCore™ OPTOLOGIC® SuperSOT™-8 VCX™ O FFPESTB™ench™ OPTOPLANAR® SSuynpcreFMETO™S® VVXoiSsl™utaaglMePalxu™s™ SF E T *Trademarks of System General Corporation, used under license by Fairchild Semiconductor. DISCLAIMER FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS. LIFE SUPPORT POLICY FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used here in: 1. Life support devices or systems are devices or systems which, (a) are 2. A critical component in any component of a life support, device, or intended for surgical implant into the body or (b) support or sustain life, system whose failure to perform can be reasonably expected to cause and (c) whose failure to perform when properly used in accordance with the failure of the life support device or system, or to affect its safety or instructions for use provided in the labeling, can be reasonably effectiveness. expected to result in a significant injury of the user. ANTI-COUNTERFEITING POLICY Fairchild Semiconductor Corporation’s Anti-Counterfeiting Policy. Fairchild’s Anti-Counterfeiting Policy is also stated on our external website, www.Fairchildsemi.com, under Sales Support. Counterfeiting of semiconductor parts is a growing problem in the industry. All manufactures of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed application, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild’s quality standards for handing and storage and provide access to Fairchild’s full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address and warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors. PRODUCT STATUS DEFINITIONS Definition of Terms Datasheet Identification Product Status Definition Datasheet contains the design specifications for product development. Specifications Advance Information Formative / In Design may change in any manner without notice. Datasheet contains preliminary data; supplementary data will be published at a later Preliminary First Production date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. Datasheet contains final specifications. Fairchild Semiconductor reserves the right to No Identification Needed Full Production make changes at any time without notice to improve the design. Datasheet contains specifications on a product that is discontinued by Fairchild Obsolete Not In Production Semiconductor. The datasheet is for reference information only. Rev. I66 ©2003 Fairchild Semiconductor Corporation 12 www.fairchildsemi.com FDB070AN06A0 Rev. C2

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor’s product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent−Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. “Typical” parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner. PUBLICATION ORDERING INFORMATION LITERATURE FULFILLMENT: N. American Technical Support: 800−282−9855 Toll Free ON Semiconductor Website: www.onsemi.com Literature Distribution Center for ON Semiconductor USA/Canada 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Europe, Middle East and Africa Technical Support: Order Literature: http://www.onsemi.com/orderlit Phone: 303−675−2175 or 800−344−3860 Toll Free USA/Canada Phone: 421 33 790 2910 Fax: 303−675−2176 or 800−344−3867 Toll Free USA/Canada Japan Customer Focus Center For additional information, please contact your local Email: orderlit@onsemi.com Phone: 81−3−5817−1050 Sales Representative © Semiconductor Components Industries, LLC www.onsemi.com www.onsemi.com 1

Mouser Electronics Authorized Distributor Click to View Pricing, Inventory, Delivery & Lifecycle Information: O N Semiconductor: FDB070AN06A0

Datasheet下载

Datasheet下载