ICGOO在线商城 > 开发板,套件,编程器 > 评估和演示板和套件 > EVAL-ADV7842-7511P

- 型号: EVAL-ADV7842-7511P

- 制造商: Analog

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

EVAL-ADV7842-7511P产品简介:

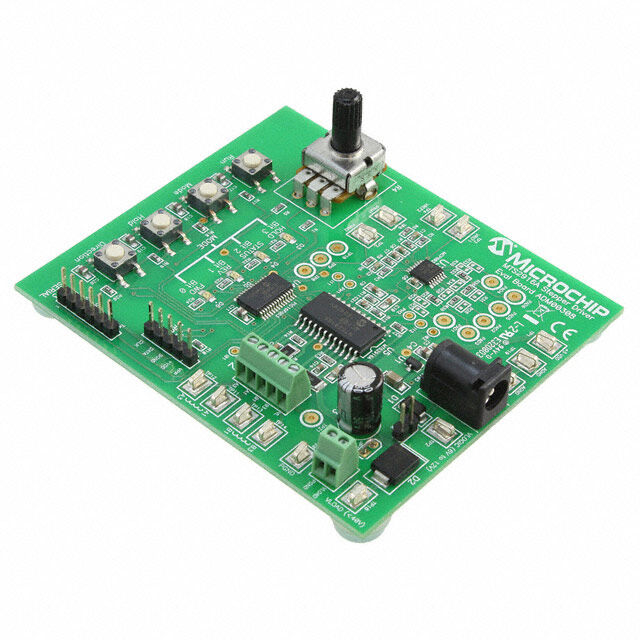

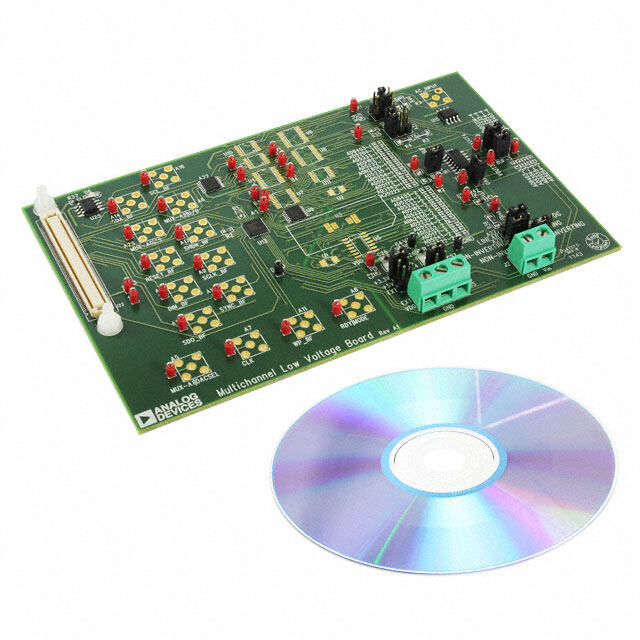

ICGOO电子元器件商城为您提供EVAL-ADV7842-7511P由Analog设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 EVAL-ADV7842-7511P价格参考。AnalogEVAL-ADV7842-7511P封装/规格:评估和演示板和套件, ADV7511, ADV7842 Video Decoder Video Evaluation Board。您可以下载EVAL-ADV7842-7511P参考资料、Datasheet数据手册功能说明书,资料中有EVAL-ADV7842-7511P 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 编程器,开发系统嵌入式解决方案 |

| 描述 | BOARD EVAL FOR ADV7842-7511P视频 IC 开发工具 EVAL-ADV7842-7511P |

| 产品分类 | |

| 品牌 | Analog Devices |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 模拟与数字IC开发工具,视频 IC 开发工具,Analog Devices EVAL-ADV7842-7511PAdvantiv®, Xpressview™ |

| 数据手册 | |

| 产品型号 | EVAL-ADV7842-7511P |

| 主要属性 | - |

| 主要用途 | 视频,视频解码器 |

| 产品 | Evaluation Boards |

| 产品种类 | 视频 IC 开发工具 |

| 使用的IC/零件 | ADV7511, ADV7842 |

| 其它名称 | EVALADV78427511P |

| 商标 | Analog Devices |

| 封装 | Bulk |

| 嵌入式 | 是,DSP |

| 工作电源电压 | 5 V |

| 工具用于评估 | ADV7842 |

| 工厂包装数量 | 1 |

| 所含物品 | 板 |

| 接口类型 | HDMI, RS-232, USB, Video |

| 描述/功能 | Evaluation board without HDCP support |

| 标准包装 | 1 |

| 用于 | ADV7842 |

| 类型 | HDMI Receiver/Video Decoder |

| 辅助属性 | - |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

内置12位、170 MHz视频/图形 数字化仪和3D梳状滤波解码器 的双通道HDMI快速切换接收器 ADV7842 特性 双通道HDMI® 1.4a快速切换接收器 垂直调峰和水平调峰滤波器 支持HDMI 稳定地同步提取质量不佳的视频源 支持3D电视 高级VBI数据分隔器 内容类型位 一般特性 兼容CEC 1.4 高度灵活的36位像素输出接口 扩展色度 针对HDMI和图形的内部EDID RAM 256引脚、17 mm × 17 mm BGA封装 支持双通道STDI(标准识别)功能 HDMI 225 MHz接收器 任意至任意、3 × 3色彩空间转换(CSC)矩阵 HDMI端口支持Xpressview快速切换 2个可编程中断请求输出引脚 支持3D视频格式,包括帧封装1080p 同步模拟处理和HDMI监控 24 Hz、720p 50 Hz、720p 60 Hz 应用 支持全色度,包括YCC601、Adobe RGB、Adobe YCC 601 高级电视 支持36/30位深色和24位色彩 等离子高清电视、液晶电视(支持高清电视) 支持HDCP 1.4、内置HDCP密钥 液晶/DLP®背投式高清电视 自适应HDMI均衡器 CRT高清电视、LCoS™高清电视 集成CEC控制器 AVR视频接收机 支持HDMI中继器 液晶/DLP前投式投影仪 各HDMI端口均支持5 V检测和热插拔 带个人录像机功能的高清电视机顶盒 支持HDMI音频,包括HBR和DSD 投影仪 高级静音特性 灵活的数字音频输出接口 功能框图 最多支持5个S/PDIF输出 SDRAM 最多支持4个I2S输出 SCART 视频/图形数字化仪 CVBS CVBS 48 4个170 MHz、12位ADC SCART RGB CVBS + CVBS ADC HS/VS 12通道模拟输入多路复用 SDP CVBS ADC SCART G CVBS FIELD/DE 525i/625i分量模拟输入 3DYC 支支针持持对577222500ppp///611200588p00ip分/支1量0持8逐0低p行分刷扫量新描高速清率电(2视4 Hz/25 Hz/30 Hz) SYDPb/YPPCSr INPUT MUX AADDCC SSCCAARRTT BR SS-CVCIADPRETO HDCSAL/TVKAS TPUT MUX FCHILSEK/LVDS/DE Y/G U YPbPr O 可对高达1600 × 1200 、60 Hz (UXGA)的RGB图形进行数字化 HDYPbPr 525p/625p FIELD/DE 36-BIT 处理 GRAPHICS Pb/B 720p/1080i CLK YCbCr/RGB RGB 1080p/ 支持SCART快速消隐 Pr/R UXGA DATA RGB 3D视频解码器 36 支持NTSC/PAL/SECAM色彩标准 HDMI 1 TMDS 4 I2S DDC DEEP S/PDIF X AUDIO N包T括SC帧/P同AL步 2的D/高3D级运时动基检校测正梳(T状BC滤)波器 HDMI 2 TDMDDCS HCDOMLIO RRx HDBSRD PUT MU OMUCTLPKUT 5 对于525i和625i,支持隔行转逐行 SWFAITSCTH MSCCLLKK OUT SCLK IF补偿滤波器 HKDEYCSP ADV7842 TPOROACUEDSIOSOR 08849-001 图1 Rev. B Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Tel: 781.329.4700 www.analog.com Trademarks and registered trademarks are the property of their respective owners. Fax: 781.461.3113 ©2010-2011 Analog Devices, Inc. All rights reserved. ADI中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI不对翻译中存在的差异或由此产生的错误负责。如需确认任何词语的准确性,请参考ADI提供 的最新英文版数据手册。

ADV7842 目录 特性..................................................................................................1 上电序列......................................................................................12 应用..................................................................................................1 关断序列......................................................................................12 功能框图.........................................................................................1 引脚配置和功能描述.....................................................................13 修订历史.........................................................................................2 功能概述..........................................................................................20 概述..................................................................................................3 HDMI接收器...............................................................................20 详细功能框图................................................................................4 模拟前端......................................................................................20 技术规格.........................................................................................5 标清处理器..................................................................................21 电气特性.....................................................................................5 分量处理器..................................................................................21 电源规格.....................................................................................6 其它特性......................................................................................22 模拟规格.....................................................................................8 外部存储器要求..............................................................................23 视频规格.....................................................................................8 单通道数据速率(SDR)...............................................................23 时序特性.....................................................................................9 双通道数据速率(DDR)..............................................................23 时序图.........................................................................................10 像素输入/输出格式化....................................................................24 绝对最大额定值............................................................................11 像素数据输出模式特性.............................................................24 封装散热性能............................................................................11 寄存器映射架构..............................................................................25 ESD警告.....................................................................................11 外形尺寸..........................................................................................26 电源时序控制................................................................................12 订购指南......................................................................................26 修订历史 2011年1月—修订版SpA至修订版B 更新了版本号..........................................................................通篇 更新了出版代码......................................................................28 2010年10月—修订版Sp0至修订版SpA 更改产品标题和特性部分....................................................1 更改表1的注释1......................................................................5 添加表5的注释1......................................................................9 更改表7的引脚C11描述........................................................14 更改表7的引脚N11描述和表7的引脚P11描述................18 2010年6月—修订版Sp0:初始版 Rev. B | Page 2 of 28

ADV7842 概述 高级音频功能,其中包括静音控制器,用于消除音频输出 ADV7842是一款高质量、单芯片、2:1多路复用HDMI™接 中的外来音频噪声。 收器和图形数字化仪,并集成多格式视频解码器。 该器件内置一个双路输入HDMI 1.4兼容型接收器,支持最 该多格式3D梳状滤波解码器支持将复合视频或S视频输入 高达1080p的所有高清电视格式,显示分辨率最高可达 信号形式的PAL、NTSC和SECAM标准信号转换为数字 UXGA(1600 × 1200,60 Hz)。 ITU-R BT.656格式。此外,ADV7842能够同时处理CVBS和 标清RGB信号,从而支持SCART和叠加功能。 ADV7842的两个输入HDMI端口均具有Xpressview™快速切 换功能。Xpressview技术使用ADI公司基于硬件的HDCP引 该器件内置一个主分量处理器(CP),可处理YPrPb和RGB 擎,软件开销极小,任意HDMI输入端口可在不到1秒的时 分量格式,包括RGB图形。CP还处理来自HDMI接收器的 间内快速完成切换。 视频信号。ADV7842支持双路HDMI和模拟输入模式,因 此允许在ADC和HDMI之间快速切换。 ADV7842不仅支持最高达1080p36位深色的所有高清电视 格式,而且支持所有强制性HDMI 1.4 3D电视格式。 它支持将RGB/YPbPr分量视频信号解码为数字YCbCr或 RGB像素输出流。支持的分量视频包括525i、625i、525p、 它还集成一个HDMI v1.4 CEC控制器,支持能力发现和控 625p、720p、1080i、1080p和1250i等标准,以及许多其它 制(CDC)特性。 SMPTE和高清标准。 ADV7842具有一个灵活的音频输出端口,用于输出从 ADV7842支持图形数字化,能够对VGA至UXGA速率的 HDMI流解码的音频数据。它支持多种HDMI音频格式, RGB图形信号进行数字化处理,将其转换为数字RGB或 包括超级音频光盘(SACD,通过DSD)和HBR等。 YCbCr像素输出流。一个图形端口配有内部EDID。 各HDMI端口具有专用的5 V检测和热插拔置位引脚。该 ADV7842采用先进的CMOS工艺制造,提供17mm×17 HDMI接收器还集成一个均衡器,可确保该接口在最长30 mm、256引脚、BGA表贴封装,符合RoHS标准;额定温 米的电缆条件下具有鲁棒的工作性能。HDMI接收器具有 度范围为-10℃至+70℃。 Rev. B | Page 3 of 28

ADV7842 详细功能框图 L 200-94880 C S _ X T P0TO P11 P12TO P23 P24TO P35 LLCHS/CS VS/FIELDFIELD/DESYNC_OUT TTX_SDA/T INT1INT2 AP0AP1 AP2AP3AP4AP5 SCLK MCLK 2 2 2 1 1 1 RETTAMROF TUPTUO OEDIV RETTAMROF TUPTUO OIDUA R STANDARD DEFINITION PROCESSOR (SDP) 2D COMB3D COMBDDR/SDR-SDRAM INTERFACETBC VERTICALSTANDARDDECIMATIONAUTODECTIONFILTERSPEAKING HORIZONTALMACROVISIONCOLOR SPACEPEAKINGDETECTIONCONVERSION INTERLACEFASTBLANKCTIANDLTITO PROGRESSIVEOVERLAYCONVERSIONCONTROL DIGITAL PROCESSING BLOCK COMPONENT PROCESSORSYNC EXTRACT(ESDP)SYNC SOURCEAV CODESTANDARDAND POLARITYINSERTIONIDENTIFICATIONDETECT CP CSCANDDECIMATIONMACROVISIONANDFILTERSCGMS DETECTION GAINDIGITALOFFSETPROGRAM-CONTROLFINE CLAMPADDERMABLEDELAY ACTIVE PEAKNOISEANDAND HSYNC DEPTHCALIBRATION ANCILLARYVSIDATADECODER2FAST ICFORMATTERINTERFACEINTERRUPT2CICONTROLLEREADBACK VIDEO DATA PROCESSOR AUDIOPROCESSOR E (A) (B) (C) (D) XUM (A)(B)(C) ACKET/OFRAMEMORY PNFM I 12 12 12 12 S, VS/FIELD ONTROL OLAND DATA DEEP COLORCONVERSION 4:2:2TO 4:4:4CONVERSION FILTER PACKETPROCESSOR C C R HS/ ONT XUM + C0 C1 C2 C3 C EDOCED IMDH + KCOLB D D D D GNIHCTIWS TSAF A A A A N E D O C M ANALOG FRONT EN CLAMP 12-CHANNELCLAMPINPUTMATRIXCLAMP CLAMP LLC GENERATION SYNC PROCESSINGAND CLOCK GENERATI TRI-LEVELSLICER 2C CONTROL INTERFAI AVLINKCONTROLLER CEC CONTROLLER 5V DETECTAND HPACONTROLLER EDID/HDCPREPEATEREEPROCONTROLLER HDCPPLLBLOCK EQUAL-SAMPLERIZER EQUAL-SAMPLERIZER T S C B b B 125678 4 LA K C AB LL ±± ±±± ±±± AOU CVB Y SCART RG YPrP RG SYNCSYNCHS_IN1/TRIVS_IN1/TRIHS_IN2/TRIVS_IN2/TRI TRI1TO TRI SCSD AVLIN CE RXA_5V/HPA_RXB_5V/HPA_ SDA/DDCA_SCSDA/DDCB_SC RXA_CRXB_C RXA_0RXA_1RXA_2 RXB_0RXB_1RXB_2 __ AB CC DD DD 图2. 详细功能框图 Rev. B | Page 4 of 28

ADV7842 技术规格 AVDD = 1.8 V ± 5%,CVDD = 1.8 V ± 5%,DVDD = 1.8 V ± 5%,PVDD = 1.8 V ± 5%,DVDDIO = 3.3 V ±5%,TVDD = 3.3 V ± 5% ,VDD_SDRAM = 3.2 V至3.4 V(SDR),VDD_SDRAM = 2.35 V至2.65 V (DDR)。除非另有说明,T 至T = −10°C至+70°C。 MIN MAX 电气特性 表1 参数 符号 测试条件/注释 最小值 典型值 最大值 单位 静态性能 分辨率(每个ADC) N 12 位 积分非线性 INL 27 MHz (12位水平) −3.0 至 +8.0 LSB 54 MHz (12位水平) −3.0 至 +8.0 LSB 74.25 MHz (12位水平) −4.0 至 +7.0 LSB 108 MHz (11位水平) −3.5 至 +8.0 LSB 170 MHz (9位水平) −0.7 至 +1.5 LSB 微分非线性 DNL 27 MHz (12位水平) −0.7 至 +0.8 LSB 54 MHz (12位水平) −0.7 至 +0.8 LSB 75 MHz (12位水平) −0.7 至 +0.8 LSB 108 MHz (11位水平) −0.7 至 +0.8 LSB 170 MHz (9位水平) −0.6 至 +0.5 LSB 数字输入 输入高电压 V XTALN和XTALP引脚 1.2 V IH 输入低电压 V XTALN和XTALP引脚 0.4 V IL 其它数字引脚 V 2 V IH 其它数字引脚 V 0.8 V IL RESET引脚 输入电流 I ±60 µA IN EP_MISO引脚 ±60 µA SPDIF_IN引脚 ±60 µA TEST4引脚 ±60 µA TEST6引脚 ±60 µA 其它数字引脚 ±10 µA 输入电容 C 10 pF IN 数字输入(5 V耐压)1 输入高电压 V 2.6 V IH 输入低电压 V 0.8 V IL 输入电流 I −82 +82 µA IN 数字输出 输出高电压 V 2.4 V OH 输出低电压 V 0.4 V OL 高阻抗漏电流 I 10 µA LEAK 输出电容 C 20 pF OUT 1 下列引脚均兼容5 V电压:HS_IN1/TRI5、HS_IN2/TRI7、VS_IN1/TRI6、VS_IN2/TRI8、RXA_5V、RXB_5V、DDCA_SCL、DDCA_SDA、DDCB_SCL和DDCB_SDA 。 Rev. B | Page 5 of 28

ADV7842 电源规格 表2 参数 符号 最小值典型值最大值 单位 测试条件/注释 电源要求 数字内核电源 VDD 1.75 1.8 1.85 V 数字I/O电源 DVDDIO 3.14 3.3 3.46 V SDRAM电源 VDD_SDRAM 3.2 3.3 3.4 V SDR存储器 VDD_SDRAM 2.35 2.5 2.65 V DDR存储器 PLL电源 PVDD 1.71 1.8 1.89 V 模拟电源 AVDD 1.71 1.8 1.89 V 端子电源 TVDD 3.14 3.3 3.46 V 比较器电源 CVDD 1.71 1.8 1.89 V 功耗1,2,3 数字内核电源电流 IVDD 155 220 mA 模拟1080p采样速率148 MHz 148 196 mA RGB图形采样速率162 MHz 285 343 mA RGB图形采样速率162 MHz,同步模式且使能两个背景端口 163 176 mA HDMI 1080p:12位深色 216 273 mA HDMI 1080p:12位深色,同步模式且使能两个背景端口 194 230 mA CVBS处理 332 378 mA CVBS处理,同步模式且使能两个背景端口 57 72 mA SD 576i分量处理 197 224 mA SD 576i分量处理,同步模式且使能两个背景端口 270 289 mA SCART处理 404 435 mA SCART处理,同步模式且使能两个背景端口 数字I/O电源电流 I 51 109 mA 模拟1080p采样速率148 MHz DVDDIO 41 129 mA RGB图形采样速率162 MHz 45 117 mA RGB图形采样速率162 MHz,同步模式且使能两个背景端口 27 32 mA HDMI 1080p:12位深色 22 150 mA HDMI 1080p:12位深色,同步模式且使能两个背景端口 9 11 mA CVBS处理 10 11 mA CVBS处理,同步模式且使能两个背景端口 8 11 mA SD 576i分量处理 8 11 mA SD 576i分量处理,同步模式且使能两个背景端口 10 11 mA SCART处理 10 12 mA SCART处理,同步模式且使能两个背景端口 Rev. B | Page 6 of 28

ADV7842 参数 符号 最小值典型值 最大值 单位 测试条件/注释 PLL电源电流 I 28 30 mA 模拟1080p采样速率148 MHz PVDD 25 27 mA RGB图形采样速率162 MHz 25 28 mA RGB图形采样速率162 MHz,同步模式且使能两个背景端口 35 36 mA HDMI 1080p:12位深色 35 38 mA HDMI 1080p:12位深色,同步模式且使能两个背景端口 34 37 mA CVBS处理 35 37 mA CVBS处理,同步模式且使能两个背景端口 22 24 mA SD 576i分量处理 22 24 mA SD 576i分量处理,同步模式且使能两个背景端口 34 37 mA SCART处理 35 37 mA SCART处理,同步模式且使能两个背景端口 模拟电源电流 IAVDD 279 295 mA 模拟1080p采样速率148 MHz 281 297 mA RGB图形采样速率162 MHz 285 301 mA RGB图形采样速率162 MHz,同步模式且使能两个背景端口 0.1 0.3 mA HDMI 1080p:12位深色 0.1 0.3 mA HDMI 1080p:12位深色,同步模式且使能两个背景端口 85 89 mA CVBS处理 86 91 mA CVBS处理,同步模式且使能两个背景端口 267 281 mA SD 576i分量处理 270 285 mA SD 576i分量处理,同步模式且使能两个背景端口 283 294 mA SCART处理 286 301 SCART处理,同步模式且使能两个背景端口 端子电源电流4 ITVDD 85 95 mA 连接一个端口 120 135 mA 连接两个端口 比较器电源电流 I 120 130 mA HDMI 1080p:12位深色 CVDD 220 250 mA HDMI 1080p:12位深色,同步模式且使能两个背景端口 存储器接口电源电流 I 28 35 mA CVBS输入采样速率54 MHz VDD_SDRAM 关断电流5 I 0.1 mA DVDDIO I 2.6 mA VDD_SDRAM I 10 mA VDD I 0.1 mA AVDD I 0.5 mA CVDD I 1.1 mA TVDD I 1.7 mA PVDD 上电时间 t 25 ms PWRUP 1 所有电流最大值均通过特性保证来辅助进行电源设计。 2 典型功耗值会与标称电源电压水平、SMPTE条形视频图案和室温一同记录。 3 功耗最大值会与最大额定电源电压水平、MoireX视频图案和最大额定温度一同记录。 4 端子电源包括片外消耗的TVDD电流。 5 通过将位POWER_DOWN设为高电平即可进入关断模式。 Rev. B | Page 7 of 28

ADV7842 模拟规格 表3 参数 测试条件/注释 最小 值 典型 值 最大 值 单位 箝位电路1 输入阻抗 箝位断开 10 MΩ 模拟(AIN1 − AIN12) ADC中间电平(CML) 0.91 V ADC满量程电平 CML + 0.55 V ADC零电平 CML − 0.55 V ADC动态范围 1.1 V 箝位电平(锁定时) 分量输入,Y信号 CML − 0.12 V 分量输入,Pr信号 CML V 分量输入,Pb信号 CML V PC RGB输入(R、G、B信号) CML − 0.12 V CVBS输入 CML − 0.205 V SCART RGB输入(R、G、B信号) CML − 0.205 V S视频输入(Y信号) CML − 0.205 V S视频输入(C信号) CML V 大箝位源电流 仅SDP 0.3 mA 大箝位吸电流 仅SDP 0.4 mA 小箝位源电流 仅SDP 9 小箝位吸电流 仅SDP 8 1 特定于100 nF的外部箝位电容。 视频规格 表4 参数 符号 测试条件/注释 最小值 典型值 最大值 单位 非线性规格 差分相位 DP CVBS输入(5步调制) 0.6 度 差分增益 DG CVBS输入(5步调制) 0.8 % 亮度非线性 LNL CVBS输入(5步调制) 0.9 % 噪声规格 27 MHz LLC时测量 未加权SNR 亮度斜坡 63 dB 未加权SNR 亮度平场 64 dB 模拟前端串扰 60 dB 锁定时间规格(SDP) 水平锁定范围 ±5 % 垂直锁定范围 40 70 Hz 副载波锁定范围 f ±0.8 kHz SC 色彩锁定时间 60 行 同步深度范围1 20 200 % 色同步范围 1 200 % 垂直锁定时间 300 ms 水平锁定时间 100 行 色度规格(SDP) 色度幅度误差 0.9 % 色度相位误差 0.3 度 色度亮度交调 0.3 % 1 标称同步深度为300 mV(100%同步深度范围)。 Rev. B | Page 8 of 28

ADV7842 时序特性 数据和I2C时2 序特性 表5 参数1 符号 测试条件/注释 最小 值 典型 值 最大值 单位 时钟和晶振 晶振频率,XTAL 28.63636 MHz 晶振频率稳定性 ±50 ppm 水平同步输入频率 10 110 kHz LLC频率范围 12.825 170 MHz I2C端口 SCL频率 400 kHz SCL最短脉冲宽度(高电平) t1 600 ns SCL最短脉冲宽度(低电平) t2 1.3 µs 起始条件保持时间 t 600 ns 3 起始条件建立时间 t 600 ns 4 SDA建立时间 t 100 ns 5 SCL和SDA上升时间 t 1000 ns 6 SCL和SDA下降时间 t 300 ns 7 结束条件建立时间 t 0.6 µs 8 TTX I2C端口 SCL频率 3.4 MHz SCL最短脉冲宽度(高电平) t1 60 ns SCL最短脉冲宽度(低电平) t2 160 ns 起始条件保持时间 t 160 ns 3 起始条件建立时间 t 160 ns 4 SDA建立时间 t 10 ns 5 SCL和SDA上升时间 t 10 80 ns 6 SCL和SDA下降时间 t 10 80 ns 7 结束条件建立时间 t 160 ns 8 复位特性 复位脉冲宽度 5 ms 时钟输出 LLC传号空号比 t:t 45:55 55:45 % 占空比 9 10 数据和控制输出2 数据输出转换时间SDR (SDP) t11 有效数据结束至负时钟沿 2.9 4.6 ns 数据输出转换时间SDR (SDP) t12 负时钟沿至有效数据开始 0.2 0.6 ns 数据输出转换时间SDR (CP) t 有效数据结束至负时钟沿 1.5 2.2 ns 13 数据输出转换时间SDR (CP) t 负时钟沿至有效数据开始 0.1 0.3 ns 14 I2S端口,主机模式 SCLK传号空号比 t15:t16 45:55 55:45 % 占空比 LRCLK数据转换时间 t17 有效数据结束至负SCLK沿 10 ns LRCLK数据转换时间 t18 负SCLK沿至有效数据开始 10 ns I2Sx数据转换时间 t 有效数据结束至负SCLK沿 5 ns 19 I2Sx数据转换时间 t 负SCLK沿至有效数据开始 5 ns 20 1 通过特性保证。 2 输出时钟上的DLL模块旁路。 Rev. B | Page 9 of 28

ADV7842 时序图 t3 t5 t3 SDA t6 t1 SCL t2 t7 t4 t8 08849-003 图3. I2C时序 t9 t10 LLC t11 t12 VSP/0FITEOLDP,3F5I,EHLSD/C/DSE, 08849-004 图4. 像素端口和控制SDR输出时序(SDP) t9 t10 LLC t13 t14 P0 THOS P/C35S,, VFSIE/FLIDE/LDDE, 08849-005 图5. 像素端口和控制SDR输出时序(CP) t15 SCLK t16 t17 LRCLK t18 I2Sx t19 LEFT-JUSTIFIED MODE MSB MSB – 1 t20 t19 I2Sx I2S MODE MSB MSB – 1 I2Sx t20 t19 RIGHT-JUSTIFIED MODE MSB LSB t20 NOTES 123... TLI2HRSECx LSAKUR FIESF SIAXI G SxNI GRANELAFSEL AR ACSCC TCEOES SS0S,I BI1BL, LE2E, VA VINAIAD A A3P P1E5 NT PODI INNA.GP4 P PININ NSA.MES. 08849-006 图6. I2S时序 Rev. B | Page 10 of 28

ADV7842 绝对最大额定值 封装散热性能 为了降低使用ADV7842时的能耗水平,建议用户关闭该器 表6 件的不用部分。 参数 额定值 AVDD至GND 2.2 V 由于PCB金属存在差异,因而PCB导热率并不完全一致, VDD至GND 2.2 V 不同PCB的θ 值可能不同。 PVDD至GND 2.2 V JA DVDDIO至GND 4.0 V 最有效的测量解决方案是使用封装表面温度来估算芯片温 VDD_SDRAM至GND 4.0 V 度,这样可消除与θ 值相关的变化。 CVDD至GND 2.2 V JA TVDD至GND 4.0 V 结温不得超过125℃的最大值(T )。下式利用封装的实测 JMAX AVDD至PVDD −0.3 V 至 +0.3 V 表面温度计算结温,仅适用于待测器件(DUT)不使用散热 AVDD至VDD −0.3 V 至 +0.3 V 器的情况: TVDD至CVDD −0.3 V 至 +2.2 V DVDDIO至VDD_SDRAM −0.3 V 至 +3.3 V T T ψ ×W J S JT TOTAL VDD_SDRAM至AVDD −0.3 V 至 +2 V 其中: VDD_SDRAM至VDD −0.3 V 至 +2 V 数字输入电压至GND −0.3 V 至 DVDDIO + 0.3 V TS是封装表面温度(°C)。 数5 V字耐输压出数电字压输至入G至NGDND1 5−.05. 3V V 至 DVDDIO + 0.3 V ψ JT = 0.5°C/W(对于256引脚BGA封装)。 模拟输入至GND −0.3 V 至 AVDD + 0.3 V XTALN和XTALP至GND −0.3 V 至 PVDD + 0.3 V 最大结温 125°C (T ) J MAX 其中: 存储温度范围 −65°C 至 +150°C 红外回流焊(20秒) 260°C 0.4反映TVDD功率(器件自身所耗)的40%。 1下列输入为3.3 V输入电压,但均兼容5 V电压:HS_IN1/TRI5、HS_IN2/ TRI7、VS_IN1/TRI6、VS_IN2/TRI8、DDCA_SCL、DDCA_SDA、DDCB_ SC 当输出像素时钟大于74 MHz时A = 0.5。 L和DDCB_SDA。 当输出像素时钟小于或等于74 MHz时A = 0.75。 注意,超出上述绝对最大额定值可能会导致器件永久性损 坏。这只是额定最值,不表示在这些条件下或者在任何其 ESD警告 它超出本技术规范操作章节中所示规格的条件下,器件能 ESD(静电放电)敏感器件。 够正常工作。长期在绝对最大额定值条件下工作会影响器 带电器件和电路板可能会在没有察觉的情况下放 件的可靠性。 电。尽管本产品具有专利或专有保护电路,但在 遇到高能量ESD时,器件可能会损坏。因此,应 当采取适当的ESD防范措施,以避免器件性能下 降或功能丧失。 Rev. B | Page 11 of 28

ADV7842 电源时序控制 上电序列- 注释 电源上电期间,复位应保持低电平。 ADV7842的推荐上电序列如下: • 3.3 V电源应最先上电。 1. 3.3 V电源 • 2.5 V电源应在3.3 V电源建立之后但在1.8 V电源之前上电。 2. 2.5 V电源(仅适用于使用DDR存储器时) • 1.8 V电源应最后上电。 3. 1.8 V电源 ADV7842还可以通过同时置位所有电源来上电。 这种情况下,各电源都正在建立,因此必须确保低额定电源 电压水平不超过高额定电源电压水平。 3.3V 3.3V SUPPLIES 关断序列 2.5V 2.5V SUPPLIES (IF ANY) 只要高额定电源电压不低于低电源电压,ADV7842电源可以 同时解除置位。 V) Y ( L P 1.8V SUPPLIES P 1.8V U S R E W O P 3P.O3VW SEURP-UPPLIES 2P.O5VW SEURP-UPPLIES 1P.O8VW SEURP-UPPLIES 08849-009 图7. 推荐上电序列 Rev. B | Page 12 of 28

ADV7842 引脚配置和功能描述 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 A GND P3 P1 P0 TVDD RXB_2– RXB_1– RXB_0– RXB_C– GND RXA_2– RXA_1– RXA_0– RXA_C– TVDD GND A B P5 P4 P2 SYNC_OUT TVDD RXB_2+ RXB_1+ RXB_0+ RXB_C+ GND RXA_2+ RXA_1+ RXA_0+ RXA_C+ TVDD XTALP B C P7 P6 VS/FIELD HS/CS GND HPA_B HPA_A RXB_5V RXA_5V PWRDN1 TEST8 CVDD CVDD CVDD GND XTALN C D P9 P8 EP_MISO FIELD/DE GND CEC DDCB_SDA DDCB_SCL DDCA_SDA DDCA_SCL RTERM CVDD VGA_SCL VGA_SDA PVDD PVDD D E GND P10 EP_CS EP_MOSI GND GND GND GND GND GND CVDD CVDD HS_IN2/TRI7VS_IN2/TRI8 REFP REFN E F P12 P11 EP_SCK TTX_SCL DVDDIO GND GND GND GND GND GND AVDD AIN12 AIN11 TRI4 TRI3 F G P14 P13 TTX_SDA MCLK DVDDIO GND GND GND GND GND GND AVDD AIN10 SYNC4 AIN9 AIN8 G H P16 P15 AP0 AP5 DVDDIO GND GND GND GND GND GND AVDD TRI1 TRI2 AIN7 SYNC3 H J P18 P17 SCLK AP4 DVDDIO GND VDD GND GND GND GND AVDD AIN6 AIN4 SYNC2 GND J K P20 P19 AP3 AP1 DVDDIO VDD VDD VDD VDD GND GND AVDD AIN5 VS_IN1/TRI6 AIN2 AIN3 K L P22 P21 SCL AP2 DVDDIO VDD VDD VDD VDD GND GND AVDD AOUT HS_IN1/TRI5 AIN1 SYNC1 L M GND P23 SDA INT1 DVDDIO VDD_SDRAM VDD_SDRAM VDD_SDRAM VDD_SDRAM VDD_SDRAM GND GND GND GND GND GND M N LLC P24 INT2 TEST4 RESET TEST6 SDRAM_A8 SDRAM_A4 SDRAM_A0 SDRAM_CS SDRAM_LDQS SDRAM_DQ4 SDRAM_DQ15 SDRAM_DQ11 SDRAM_CK SDRAM_CKE N P P25 P26 TEST5 AVLINK TEST7 SDRAM_A11 SDRAM_A7 SDRAM_A3SDRAM_A10 SDRAM_RAS SDRAM_DQ7 SDRAM_DQ3 SDRAM_VREF SDRAM_DQ12SDRAM_UDQS SDRAM_CK P R P27 P28 P30 P32 P34 SDRAM_A9 SDRAM_A6 SDRAM_A2SDRAM_BA1 SDRAM_CAS SDRAM_DQ6 SDRAM_DQ2 SDRAM_DQ0 SDRAM_DQ13 SDRAM_DQ9 SDRAM_DQ8 R T GN1D P229 P331 P433 P535 GN6D SDRA7M_A5 SDRA8M_A1SDRA9M_BA0SDRA1M0_WE SDRA1M1_DQ5 G1N2D SDRA1M3_DQ1 SDRA1M4_DQ14 SDRA1M5_DQ10 G1N6D T 08849-007 图8 引脚配置(顶视图) Rev. B | Page 13 of 28

ADV7842 表7. 引脚功能描述 引脚 编号 引脚名称 类型 描述 A1 GND 地 地。 A2 P3 数字视频输出 视频像素输出端口。 A3 P1 数字视频输出 视频像素输出端口。 A4 P0 数字视频输出 视频像素输出端口。 A5 TVDD 电源 端子电源电压(3.3 V)。 A6 RXB_2− HDMI输入 HDMI接口中端口B的数字输入通道2 (-)。 A7 RXB_1− HDMI输入 HDMI接口中端口B的数字输入通道1 (-)。 A8 RXB_0− HDMI输入 HDMI接口中端口B的数字输入通道0 (-)。 A9 RXB_C− HDMI输入 HDMI接口中端口B的数字输入时钟(-)。 A10 GND 地 地。 A11 RXA_2− HDMI输入 HDMI接口中端口A的数字输入通道2 (-)。 A12 RXA_1− HDMI输入 HDMI接口中端口A的数字输入通道1 (-)。 A13 RXA_0− HDMI输入 HDMI接口中端口A的数字输入通道0 (-)。 A14 RXA_C− HDMI输入 HDMI接口中端口A的数字输入时钟(-)。 A15 TVDD 电源 端子电源电压(3.3 V)。 A16 GND 地 地。 B1 P5 数字视频输出 视频像素输出端口。 B2 P4 数字视频输出 视频像素输出端口。 B3 P2 数字视频输出 视频像素输出端口。 B4 SYNC_OUT 其它数字 分隔同步输出 B5 TVDD 电源 端子电源电压(3.3 V)。 B6 RXB_2+ HDMI输入 HDMI接口中端口B的数字输入通道2 (+)。 B7 RXB_1+ HDMI输入 HDMI接口中端口B的数字输入通道1 (+)。 B8 RXB_0+ HDMI输入 HDMI接口中端口B的数字输入通道0 (+)。 B9 RXB_C+ HDMI输入 HDMI接口中端口B的数字输入时钟(+)。 地。 B10 GND 地 B11 RXA_2+ HDMI输入 HDMI接口中端口A的数字输入通道2 (+)。 HDMI接口中端口A的数字输入通道1 (+)。 B12 RXA_1+ HDMI输入 HDMI接口中端口A的数字输入通道0 (+)。 B13 RXA_0+ HDMI输入 HDMI接口中端口A的数字输入时钟(+)。 B14 RXA_C+ HDMI输入 端子电源电压(3.3 V)。 B15 TVDD 电源 为ADV7842提供时钟的28.63636 MHz晶振或外部1.8V、28.63636 MHz时 B16 XTALP 其它模拟 钟振荡器源的输入引脚。 C1 P7 数字视频输出 视频像素输出端口。 C2 P6 数字视频输出 视频像素输出端口。 C3 VS/FIELD 数字视频输出 垂直同步/场同步。VS是CP和HDMI处理器中的垂直同步输出信号。FIELD 是所有隔行视频模式下的场同步输出信号。可为此引脚配置VS或FIELD。 C4 HS/CS 数字视频输出 水平同步/复合同步。HS是CP和HDMI处理器中的水平同步输出信号。CS (复合同步)信号是同时包含水平和垂直同步脉冲的单个信号。可为此 引脚配置HS或CS。 C5 GND Grou地 地。 C6 HPA_B 其它数字 HDMI端口B的热插拔信号输出。 C7 HPA_A 其它数字 HDMI端口A的热插拔信号输出。 C8 RXB_5V HDMI输入 HDMI接口中端口B的5 V检测引脚。 C9 RXA_5V HDMI输入 HDMI接口中端口A的5 V检测引脚。 C10 PWRDN1 其它数字 控制ADV7842的上电。应连接到3.3 V I/O电源来为ADV7842上电。 C11 TEST8 测试引脚 T此引脚通过4.7 kΩ电阻连接到地。 C12 CVDD 电源 比较器电源(1.8 V)。 C13 CVDD 电源 比较器电源(1.8 V)。 C14 CVDD 电源 比较器电源(1.8 V)。 Rev. B | Page 14 of 28

ADV7842 引脚 编号 引脚名称 类型 描述 C15 GND 地 地。 C16 XTALN 其它模拟 28.63636 MHz晶振的输入引脚。 D1 P9 数字视频输出 视频像素输出端口。 视频像素输出端口。 D2 P8 数字视频输出 外部EDID接口的SPI主机输入/从机输出。 D3 EP_MISO 数字输入 数据使能(DE)。DE是指示有效像素数据的信号。所有隔行视频模式下的场 D4 FIELD/DE 其它数字 同步输出信号(FIELD)。可为此引脚配置DE或FIELD。 D5 GND 地 地。 D6 CEC 数字输入/输出 消费电子控制通道。 D7 DDCB_SDA 数字输入/输出 HDCP从机串行数据端口B。DDCB_SDA是兼容5 V电压的3.3 V输入/输出。 D8 DDCB_SCL 数字输入 HDCP从机串行时钟端口B。DDCB_SCL是兼容5 V电压的3.3 V输入。 D9 DDCA_SDA 数字输入/输出 HDCP从机串行数据端口A。DDCA_SDA是兼容5 V电压的3.3 V输入/输出。 D10 DDCA_SCL 数字输入 HDCP从机串行时钟端口A。DDCA_SCL是兼容5 V电压的3.3 V输入。 D11 RTERM 其它模拟 设置内部端接电阻。应在此引脚和GND之间连接500电阻。 D12 CVDD 电源 比较器电源(1.8 V)。 D13 VGA_SCL 其它数字 VGA的DDC端口串行时钟输入 D14 VGA_SDA 其它数字 VGA的DDC端口串行数据输入/输出 D15 PVDD 电源 PLL电源(1.8 V)。 D16 PVDD 电源 PLL电源(1.8 V)。 E1 GND 地 地。 E2 P10 数字视频输出 视频像素输出端口。 E3 EP_CS 数字输出 外部EDID接口的SPI片选信号。 E4 EP_MOSI 数字输出 外部EDID接口的SPI主机输出/从机输入。 地 地。 E5 GND 地 地。 E6 GND 地 地。 E7 GND 地 地。 E8 GND 地 地。 E9 GND 地 地。 E10 GND 电源 比较器电源(1.8 V)。 E11 CVDD 电源 比较器电源(1.8 V)。 E12 CVDD 其它模拟 图形端口2上的HS (HS_IN2)。HS输入信号用于5线时序模式。SCART或D E13 HS_IN2/TRI7 端子连接器上的Trilevel/Bilevel输入(TRI7)。(可通过I2C选择。) E14 VS_IN2/TRI8 其它模拟 图形端口2上的VS (VS_IN2)。VS输入信号用于5线时序模式。SCART或D 端子连接器上的Trilevel/Bilevel输入(TRI8)。(可通过I2C选择。) E15 REFP 其它模拟 内部基准电压输出。 E16 REFN 其它模拟 内部基准电压输出。 F1 P12 数字视频输出 视频像素输出端口。 F2 P11 数字视频输出 视频像素输出端口。 F3 EP_SCK 数字输出 外部EDID接口的SPI时钟信号。 F4 TTX_SCL 其它数字 用于Teletext数据提取的快速I2C接口。TTX_SCL用作I2C端口串行时钟输入。 F5 DVDDIO 电源 数字I/O电源电压(3.3 V)。 F6 GND 地 地。 F7 GND 地 地。 F8 GND 地 地。 F9 GND 地 地。 F10 GND 地 地。 F11 GND 地 地。 F12 AVDD 电源 模拟电源电压(1.8 V)。 Rev. B | Page 15 of 28

ADV7842 引脚 编号 引脚名称 类型 描述 F13 AIN12 模拟视频输入 模拟视频输入通道。 F14 AIN11 模拟视频输入 模拟视频输入通道。 F15 TRI4 其它模拟 SCART或D类连接器上的Trilevel或Bilevel输入。(可通过I2C选择。) F16 TRI3 其它模拟 SCART或D类连接器上的Trilevel或Bilevel输入。(可通过I2C选择。) G1 P14 数字视频输出 视频像素输出端口。 G2 P13 数字视频输出 视频像素输出端口。 G3 TTX_SDA 其它数字 用于Teletext数据提取的快速I2C接口。TTX_SDA用作I2C端口串行数据输入/输出引脚。 G4 MCLK 其它 音频主机时钟输出。 G5 DVDDIO 电源 数字I/O电源电压(3.3 V)。 G6 GND 地 地。 G7 GND 地 地。 G8 GND 地 地。 G9 GND 地 地。 G10 GND 地 地。 G11 GND 地 地。 G12 AVDD 电源 模拟电源电压(1.8 V)。 G13 AIN10 模拟视频输入 模拟视频输入通道。 G14 SYNC4 其它模拟 这是嵌入式同步模式下使用的绿同步或亮度同步输入(SOG/SOY)。用户可配置。 G15 AIN9 模拟视频输入 模拟视频输入通道。 G16 AIN8 模拟视频输入 模拟视频输入通道。 H1 P16 数字视频输出 视频像素输出端口。 H2 P15 数字视频输出 视频像素输出端口。 H3 AP0 其它 音频输出引脚。 H4 AP5 其它 音频输出引脚。 H5 DVDDIO 电源 数字I/O电源电压(3.3 V)。 H6 GND 地 地。 H7 GND 地 地。 H8 GND 地 地。 H9 GND 地 地。 H10 GND 地 地。 H11 GND 地 地。 H12 AVDD 电源 模拟电源电压(1.8 V)。 H13 TRI1 其它模拟 SCART或D类连接器上的Trilevel或Bilevel输入。(可通过I2C选择。) H14 TRI2 其它模拟 SCART或D类连接器上的Trilevel或Bilevel输入。(可通过I2C选择。) 模拟视频输入 模拟视频输入通道。 H15 AIN7 其它模拟 这是嵌入式同步模式下使用的绿同步或亮度同步输入(SOG/SOY)。用户可配置。 H16 SYNC3 J1 P18 数字视频输出 视频像素输出端口。 J2 P17 数字视频输出 视频像素输出端口。 J3 SCLK 其它数字 音频串行时钟输出。 J4 AP4 其它 音频输出引脚。 J5 DVDDIO 电源 数字I/O电源电压(3.3 V)。 J6 GND 地 地。 J7 VDD 电源 数字内核电源电压(1.8 V)。 J8 GND 地 地。 J9 GND 地 地。 J10 GND 地 地。 J11 GND 地 地。 J12 AVDD 电源 模拟电源电压(1.8 V)。 J13 AIN6 模拟视频输入 模拟视频输入通道。 Rev. B | Page 16 of 28

ADV7842 引脚 编号 引脚名称 类型 描述 J14 AIN4 模拟视频输入 模拟视频输入通道。 J15 SYNC2 其它模拟 这是嵌入式同步模式下使用的绿同步或亮度同步输入(SOG/SOY)。用户可配置。 地。 J16 GND 地 地。 K1 P20 数字视频输出 视频像素输出端口。 K2 P19 数字视频输出 视频像素输出端口。 K3 AP3 其它 音频输出引脚。 K4 AP1 其它 音频输出引脚。 K5 DVDDIO 电源 数字I/O电源电压(3.3 V)。 K6 VDD 电源 数字内核电源电压(1.8 V)。 K7 VDD 电源 数字内核电源电压(1.8 V)。 K8 VDD 电源 数字内核电源电压(1.8 V)。 K9 VDD 电源 数字内核电源电压(1.8 V)。 K10 GND 地 地。 K11 GND 地 地。 K12 AVDD 电源 模拟电源电压(1.8 V)。 K13 AIN5 模拟视频输入 模拟视频输入通道。 K14 VS_IN1/TRI6 其它模拟 图形端口1上的VS (VS_IN1)。VS输入信号用于5线时序模式。S-CART或D端子连接 器上的Trilevel/Bilevel输入(TRI6)。(可通过I2C选择。) K15 AIN2 模拟视频输入 模拟视频输入通道。 K16 AIN3 模拟视频输入 模拟视频输入通道。 L1 P22 数字视频输出 视频像素输出端口。 L2 P21 数字视频输出 视频像素输出端口。 L3 SCL 其它数字 I2C端口串行时钟输入。SCL是控制端口的时钟线。 L4 AP2 其它 音频输出引脚。 L5 DVDDIO 电源 数字I/O电源电压(3.3 V)。 L6 VDD 电源 数字内核电源电压(1.8 V)。 L7 VDD 电源 数字内核电源电压(1.8 V)。 L8 VDD 电源 数字内核电源电压(1.8 V)。 L9 VDD 电源 数字内核电源电压(1.8 V)。 L10 GND 地 地。 L11 GND 地 地。 L12 AVDD 电源 模拟电源电压(1.8 V)。 L13 AOUT 模拟监控输出 模拟监控输出。 L14 HS_IN1/TRI5 其它模拟 图形端口1上的HS (HS_IN1)。HS输入信号用于5线时序模式。SCART或D端子连接器 上的Trilevel/Bilevel输入(TRI5)。(可通过I2C选择。) L15 AIN1 模拟视频输入 模拟视频输入通道。 L16 SYNC1 其它模拟 这是嵌入式同步模式下使用的绿同步或亮度同步输入(SOG/SOY)。用户可配置。 M1 GND 地 地。 M2 P23 数字视频输出 视频像素输出端口。 M3 SDA 其它数字 I2C端口串行数据输入/输出引脚。SDA是控制端口的数据线。 M4 INT1 其它数字 中断。此引脚可以是低电平有效或高电平有效。状态位变化时即会触发此引脚。 触发中断的事件由用户控制。 M5 DVDDIO 电源 数字I/O电源电压(3.3 V)。 M6 VDD_SDRAM 电源 外部存储器接口数字输入/输出电源(DDR 2.5 V或SDR 3.3 V)。 M7 VDD_SDRAM 电源 外部存储器接口数字输入/输出电源(DDR 2.5 V或SDR 3.3 V)。 M8 VDD_SDRAM 电源 外部存储器接口数字输入/输出电源(DDR 2.5 V或SDR 3.3 V)。 M9 VDD_SDRAM 电源 外部存储器接口数字输入/输出电源(DDR 2.5 V或SDR 3.3 V)。 M10 VDD_SDRAM 电源 外部存储器接口数字输入/输出电源(DDR 2.5 V或SDR 3.3 V)。 M11 GND 地 地。 Rev. B | Page 17 of 28

ADV7842 引脚 编号 引脚名称 类型 描述 M12 GND 地 地。 M13 GND 地 地。 M14 GND 地 地。 M15 GND 地 地。 M16 GND 地 地。 N1 LLC 数字视频输出 像素数据的行锁定输出时钟。 N2 P24 数字视频输出 视频像素输出端口。 N3 INT2 其它数字 中断。此引脚可以是低电平有效或高电平有效。状态位变化时即会触发此引 脚。触发中断的事件由用户控制。 N4 TEST4 测试 连接此引脚到地。 N5 RESET 其它数字 系统复位输入。低电平有效。复位ADV7842电路需要最短5 ms的低电平复位脉冲。 N6 TEST6 测试 此引脚保持悬空。 N7 SDRAM_A8 SDRAM接口 地址输出。与外部RAM地址行接口。 N8 SDRAM_A4 SDRAM接口 地址输出。与外部RAM地址行接口。 N9 SDRAM_A0 SDRAM接口 地址输出。与外部RAM地址行接口。 N10 SDRAM_CS SDRAM接口 片选。SDRAM_CS使能和禁用RAM上的命令解码器。传至外部SDRAM的四个命令信号之一。 N11 SDRAM_LDQS SDRAM接口 低位数据选通引脚。数据选通引脚用于RAM接口。当从外部存储器读取数据时,这是 输入端,而向外部存储器写入数据时,这是输出端。从外部存储器读取时实现边沿对 齐,而向外部存储器写入时则集中。SDRAM_LDQS对应于SDRAM_DQ7至SDRAM_DQ0 上的数据。 N12 SDRAM_DQ4 SDRAM接口 数据总线。与外部RAM 16位数据总线接口。 N13 SDRAM_DQ15 SDRAM接口 数据总线。与外部RAM 16位数据总线接口。 N14 SDRAM_DQ11 SDRAM接口 数据总线。与外部RAM 16位数据总线接口。 N15 SDRAM_CK SDRAM接口 差分时钟输出。传送至RAM的所有地址和控制输出信号应当在SDRAM_CK的正边沿和 SDRAM_CK的负边沿上采样。 N16 SDRAM_CKE SDRAM接口 时钟使能。此引脚用作外部RAM时钟信号的使能引脚。 P1 P25 数字视频输出 视频像素输出端口。 P2 P26 数字视频输出 视频像素输出端口。 P3 TEST5 测试 连接此引脚到地。 P4 AVLINK 数字输入/输出 数字SCART控制通道。 P5 TEST7 测试 此引脚保持悬空。 P6 SDRAM_A11 SDRAM接口 地址输出。与外部RAM地址行接口。 P7 SDRAM_A7 SDRAM接口 地址输出。与外部RAM地址行接口。 P8 SDRAM_A3 SDRAM接口 地址输出。与外部RAM地址行接口。 P9 SDRAM_A10 SDRAM接口 地址输出。与外部RAM地址行接口。 P10 SDRAM_RAS SDRAM接口 行地址选择命令信号。传至外部SDRAM的四个命令信号之一。 P11 SDRAM_DQ7 SDRAM接口 数据总线。与外部RAM 16位数据总线接口。 P12 SDRAM_DQ3 SDRAM接口 DDR SDRAM接口的1.25 V基准电压源或SDR SDRAM接口的1.65 V基准电压源。 P13 SDRAM_VREF SDRAM接口 数据总线。与外部RAM 16位数据总线接口。 P14 SDRAM_DQ12 SDRAM接口 高位数据选通引脚。数据选通引脚用于RAM接口。当从外部存储器读取数据 P15 SDRAM_UDQS SDRAM接口 时,这是输入端,而向外部存储器写入数据时,这是输出端。从外部存储器 读取时实现边沿对齐,而向外部存储器写入时则集中。SDRAM_UDQS对应于 SDRAM_DQ15至SDRAM_DQ8上的数据。 P16 SDRAM_CK SDRAM接口 差分时钟输出。传送至RAM的所有地址和控制输出信号应当在SDRAM_CK的 正边沿和SDRAM_CK的负边沿上采样。 . R1 P27 数字视频输出 视频像素输出端口。 R2 P28 数字视频输出 视频像素输出端口。 R3 P30 数字视频输出 视频像素输出端口。 R4 P32 数字视频输出 视频像素输出端口。 Rev. B | Page 18 of 28

ADV7842 引脚 编号 引脚名称 类型 描述 R5 P34 数字视频输出 视频像素输出端口。 R6 SDRAM_A9 SDRAM接口 地址输出。与外部RAM地址行接口。 R7 SDRAM_A6 SDRAM接口 地址输出。与外部RAM地址行接口。 R8 SDRAM_A2 SDRAM接口 地址输出。与外部RAM地址行接口。 R9 SDRAM_BA1 SDRAM接口 空白地址输出。与外部RAM空白地址行接口。 R10 SDRAM_CAS SDRAM接口 列地址选择命令信号。传至外部SDRAM的四个命令信号之一。 R11 SDRAM_DQ6 SDRAM接口 数据总线。与外部RAM 16位数据总线接口。 R12 SDRAM_DQ2 SDRAM接口 数据总线。与外部RAM 16位数据总线接口。 R13 SDRAM_DQ0 SDRAM接口 数据总线。与外部RAM 16位数据总线接口。 R14 SDRAM_DQ13 SDRAM接口 数据总线。与外部RAM 16位数据总线接口。 R15 SDRAM_DQ9 SDRAM接口 数据总线。与外部RAM 16位数据总线接口。 R16 SDRAM_DQ8 SDRAM接口 数据总线。与外部RAM 16位数据总线接口。 T1 GND 地 地。 T2 P29 数字视频输出 视频像素输出端口。 T3 P31 数字视频输出 视频像素输出端口。 T4 P33 数字视频输出 视频像素输出端口。 T5 P35 数字视频输出 视频像素输出端口。 T6 GND 地 地。 T7 SDRAM_A5 SDRAM接口 地址输出。与外部RAM地址行接口。 T8 SDRAM_A1 SDRAM接口 地址输出。与外部RAM地址行接口。 T9 SDRAM_BA0 SDRAM接口 空白地址输出。与外部RAM空白地址行接口。 T10 SDRAM_WE SDRAM接口 写入使能输出命令信号。传至外部SDRAM的四个命令信号之一。 T11 SDRAM_DQ5 SDRAM接口 数据总线。与外部RAM 16位数据总线接口。 T12 GND 地 地。 T13 SDRAM_DQ1 SDRAM接口 数据总线。与外部RAM 16位数据总线接口。 T14 SDRAM_DQ14 SDRAM接口 数据总线。与外部RAM 16位数据总线接口。 T15 SDRAM_DQ10 SDRAM接口 数据总线。与外部RAM 16位数据总线接口。 T16 GND 地 地。 Rev. B | Page 19 of 28

ADV7842 功能概述 HDMI接收器 模拟前端 ADV7842前端集成2:1多路复用HDMI 1.4接收器,后者采用 ADV7842模拟前端包括4个170 MHz、12位ADC,用来对模 Xpressview快速切换技术并支持3D电视等HDMI 1.4特性。 拟视频信号进行数字化处理,然后将信号施加于标清处理 该器件基于ADI公司现有HDMI设备的特性组合,并支持 器(SDP)或分量处理器(CP)。模拟前端使用差分通道连接 最高达12位、1080p深色的高清电视格式和最高达UXGA 各ADC,确保混合信号应用能够实现高性能。模拟前端还 (1600 × 1200,60 Hz)的所有显示分辨率。Xpressview快速切 包括一个12通道输入多路复用器,支持将多个视频信号施 换技术使用ADI公司基于硬件的HDCP引擎,软件开销极 加于ADV7842,而无需外部多路复用器。 小,两个输入端口之间可在不到1秒的时间内快速完成切 电流和电压箝位控制环路确保消除视频信号中的所有直流 换。 失调。各ADC前置钳位电路,确保视频信号始终在转换器 增加HDCP 1.4功能后,ADV7842还能接收加密视频内容。 的处理范围之内。 该器件的HDMI接口能够按照HDCP 1.4协议的规定,对视 当解码复合和S视频输入时,ADC配置为最高8倍过采样模 频接收机进行身份验证,在接收机端解密编码数据,以及 式。对于分量525i、625i、525p和625p视频源,则执行4倍 在传输期间更新身份验证信息。此外还支持中继器。 过采样。对所有其它视频标准执行1倍过采样。视频信号 该HDMI接收器能够主动均衡HDMI数据信号,以便补偿 过采样可降低外部抗混叠滤波器的成本和复杂度,并提高 HDMI和DVI布线固有的高频损耗,特别是当电缆较长且 信噪比(SNR)。 频率较高时。该器件能为最长30米的电缆提供均衡处理, 各ADC前置可选的内部可编程带宽抗混叠滤波器。这些滤 因此即使在最高HDMI数据速率下,它也能实现鲁棒的接 波器可用于对视频信号进行带宽限制,从而移除带外杂散 收性能。 噪声。 该HDMI接收器具有高级音频功能。它最多可针对八个通 ADV7842支持对CVBS和RGB标清信号进行同步处理,以 道提供多通道I2S音频支持。此外,它支持与每个通道进行 实现SCART兼容和叠加功能。在I2C寄存器的控制下, 6-DSD通道接口,从而承载SACD上所传输音频信号的1位 CVBS和RGB输入组合可以混合输出。 过采样表示。ADV7842还可以接收HBR音频数据包流并通 模拟前端特性包括: 过HBR接口以符合IEC60958标准的SPDIF格式形式输出。 • 4个170 MHz、NSV、12位ADC支持真12位视频解码 • 12通道模拟输入多路复用器支持多个视频源连接,而无 该接收器内置一个静音控制器,它能检测多种可能导致音 需外部多路复用器 频输出中出现外来音频噪声的条件。一旦检测到这些条 • 4个电流和电压箝位控制环路确保消除视频信号中的所有 件,就可以调节(rampe)音频数据来实现静音,从而防止发 直流失调 出咔嚓声或爆音。 • CVBS上的SCART功能和SD RGB叠加由快速空白输入控制 • 可通过TRI1-TRI8输入检测SCART源切换 HDMI接收器特性包括: • 4个可编程抗混叠滤波器 • 2:1多路复用HDMI接收器 • 支持HDMI 1.4 3D,DVI 1.0 • 225 MHz HDMI接收器 • 集成均衡器 • 背景端口上还支持高带宽数字内容保护(HDCP 1.4) • 内部储存HDCP密钥 • 支持36/30位深色 • 支持PCM、HBR、DSD音频数据包 • 支持中继器 • 内部E-EDID RAM • 各HDMI端口均具有热插拔输出引脚 • CEC控制器 Rev. B | Page 20 of 28

ADV7842 标清处理器 SDP可解码复合和S视频格式的许多基带视频信号。SDP支 • 内部彩条测试图案 持的视频标准包括PAL、PAL 60、PAL M、PAL N、PAL • 帧同步的高级TBC确保非标准输入的标称时钟和数据 • 对于525i和625i格式,支持隔行转逐行,从而可以直接 NC、NTSC M/J、NTSC 4.43和SECAM。ADV7842可自动检 驱动HDMI Tx器件 测视频标准,并进行相应处理。 • 色彩控制包括色调、亮度、饱和度和对比度 SDP具有一个3D时间梳状滤波器和一个5线式自适应2D梳 分量处理器 状滤波器,可在解码复合视频信号时提供出色的色度和亮 ADV7842的CP部分可以对任何色彩空间的广泛复合视频格 度分离。这种自适应滤波器根据视频标准和信号质量自动 式进行解码和数字化处理。CP支持的分量视频标准包括 调整处理模式,无需用户干预。SDP还有一个IF滤波器模 525i、625i、525p、625p、720p、1080i、1080p、1250i、最 块,可补偿调谐器SAW滤波器所导致的高频色度频谱衰 高达UXGA 60 Hz的VGA以及其它标准。 减。SDP有专门的亮度和色度参数来控制亮度、对比度、 模拟前端和CP部分之间放置任意至任意、3 × 3 CSC矩阵, 饱和度和色调。 从而支持YPbPr转RGB和RGB转YCbCr。利用色彩空间转换 ADV7842采用自适应数字线路长度跟踪(ADLLT™)专利算法 器可以实施色彩空间的许多其它标准。 实现,可跟踪VCR等视频源的视频线路长度变化。ADLLT CP部分具有一个检测电路,可以检测525i、625i、525p和 使ADV7842能够跟踪和解码质量不佳的视频源(如VCR)和 625p标准的Macrovision编码YPbPr信号。它能够稳定地支 高噪声源(如调谐器输出、VCD播放器和便携式摄像机)。 持此类信号的解码。CGMS数据的VBI提取由ADV7842的 帧TBC确保解码器和下游器件之间可实现稳定的时钟同 CP部分执行,支持隔行、逐行和高清扫描速率。提取的数 步。 据可通过I2C接口回读。 SDP还包含亮度瞬态改善(LTI)模块和色度瞬态改善(CTI)模 CP特性包括: 块。这些模块可以提高亮度和色度转换的边沿速率,使视 • 支持525i、625i、525p、625p、720p、1080i、1080p和许 多其它高清电视格式 频图像更清晰。SDP具有一个Macrovision®检测电路,可实 • 支持720p 24 Hz/25 Hz格式 现I型、II型和III型Macrovision保护级别。该解码器还能够 • 手动调整,包括增益(对比度)、失调(亮度)、色调 稳定地支持所有Macrovision信号输入。 和饱和度调整 • 支持带嵌入式同步、复合同步或独立HS和VS的模拟分量 SDP特性包括: YPbPr和RGB视频格式 • 高级自适应3D梳状滤波器(采用外部DDR或SDR SDRAM • 任意至任意、3 × 3 CSC矩阵支持YCbCr转RGB和RGB转Y 存储器) CbCr,且具有完全可编程或预编程配置 • 用于NTSC和PAL的自适应2D 5线式梳状滤波器可为复合视 • 同步源极性检测器(SSPD)确定输入信号伴随的同步信号的 频提供出色的色度和亮度分离 来源和极性 • 全自动检测和自动切换所有全球标准(PAL、NTSC和SEC • Macrovision版权保护功能适用于分量格式(525i、625i、 AM) 525p和625p) • 白色峰值模式下的自动增益控制确保始终以完整视频处理 • 无视频输入或视频失锁时,自由输出模式提供稳定的时序 范围处理视频 • 支持对非标准视频源进行任意像素采样 • 专有架构支持锁定较弱、高噪声且不稳定的视频源,如V • 170 MHz转换速率支持高达1600 × 1200、60 Hz的RGB输入 CR和调谐器等 分辨率 • IF滤波器模块补偿调谐器SAW滤波器所导致的高频亮度衰 • STDI模块支持标准识别 减 • RGB可作为色彩空间转换成YCbCr并抽取成4:2:2格式,从 • LTI和CTI 实现以视频为中心的后端IC接口 • 垂直和水平可编程亮度调峰滤波器 • CVBS和S视频模式支持8倍过采样(108 MHz) • 线路锁定时钟(LLC)输出 • 无视频输入或视频失锁时,自由输出模式提供稳定的时序 Rev. B | Page 21 of 28

ADV7842 提供数据使能 (DE)输出信号,以便直接连到 其它特性 HDMI/DVI Tx IC ADV7842提供位置、极性及宽度可编程的HS、VS、FIELD 32相位DLL支持最佳像素时钟采样 和DE输出信号和两个I2C主机端口接口(控制和VBI)。它具 有两个可编程中断请求输出引脚INT1和INT2。它还具有多 SSPD模块自动检测同步源和极性 个低功耗模式和一个完全关断模式。ADV7842提供17 mm 对比度、亮度、色调和饱和度控制 × 17 mm、BGA封装,符合RoHS标准;额定温度范围为− 图形模式的自动或手动箝位和增益控制 10°C至+70°C。 欲了解有关ADV7842的详细产品信息,请联系ADI公司当 地代理商。 Rev. B | Page 22 of 28

ADV7842 外部存储器要求 ADV7842采用外部SDRAM作为3D梳状滤波器和帧同步 双通道数据速率(DDR) 器。它支持SDR或DDR SD RAM。 ADV7842可采用DDR外部存储器来同时提供3D梳状滤波器 单通道数据速率(SDR) 和帧同步器操作。 ADV7842可采用SDR外部存储器来提供3D梳状滤波器或帧 最低存储器要求为128 Mb DDR SDRAM。所需存储器架构 同步器操作,但不能同时提供。 为四个2 Mb × 16 (8M16)存储库,且CL为2.5时速度等级为 最低存储器要求为64 Mb SDR SDRAM。所需存储器架构为 133 MHz。此配置推荐推荐使用22 Ω串联端接电阻。 四个1 Mb × 16 (4M16)存储库,且CAS延迟(CL)为3时速度 与ADV7842兼容的推荐 DDR存储器包括三星公司的 等级为133 MH。此配置推荐使用22 Ω串联端接电阻。 K4H561638J-LCB3、美光科技公司的MT46V16M16P-6T和 与ADV7842兼容的推荐 SDR存储器包括 Winbond 海力士公司的H5DU1262GTR-E3C。 W9864G6PH-7。 Rev. B | Page 23 of 28

ADV7842 像素输入/输出格式化 ADV7842的输出部分非常灵活。像素输出总线最高支持36 像素数据输出模式特性 位4:4:4。像素数据支持单通道和双通道两种数据速率模 输出像素端口包括下列特性: 式。在SDR模式下,可以实现16/20/24位4:2:2或24/30/36位 • 8/10/12位ITU-R BT.656 4:2:2,带嵌入式事件码和/或 4:4:4输出。在DDR模式下,像素输出端口可配置为8/10/12 HS、VS、FIELD输出信号 位4:2:2模式或24/30/36位4:4:4模式。此外还支持总线旋转和 总线反转。所有输出模式均通过I2C控制进行控制。 • SDR 16/20/24/30/36位,带嵌入式时间码和/或HS/CS与 VS/FIELD引脚时序 • DDR 8/10/12位4:2:2,带嵌入式时间码和/或HS、VS、 FIELD输出信号 • DDR 24/30/36位4:4:4,带嵌入式时间码和/或HS、VS、 FIELD输出信号 注意,根据特性DDR模式最高支持54 MHz。 Rev. B | Page 24 of 28

ADV7842 寄存器映射架构 ADV7842的寄存器通过一个双线式串行(I2C兼容型)接口控 有其他映射地址必须进行编程;这样就确保系统上不会出 制。该器件具有12个映射。IO映射具有静态I2C地址。所 现寻址冲突。图9显示了寄存器映射架构。 表8 寄存器映射名称 默认地址 可编程地址 可以对地址进行编程的位置 IO映射 0x40 不可编程 不适用 CP映射 0x00 可编程 IO映射,寄存器0xFD SDP映射 0x00 可编程 IO映射,寄存器0xF1 SDP_IO映射 0x00 可编程 IO映射,寄存器0xF2 VDP映射 0x00 可编程 IO映射,寄存器0xFE AVLINK映射 0x00 可编程 IO映射,寄存器0xF3 CEC映射 0x00 可编程 IO映射,寄存器0xF4 HDMI映射 0x00 可编程 IO映射,寄存器0xFB EDID映射 0x00 可编程 IO映射,寄存器0xFA 中继器映射 0x00 可编程 IO映射,寄存器0xF9 AFE,DPLL映射 0x00 可编程 IO映射,寄存器0xF8 InfoFrame映射 0x00 可编程 IO映射,寄存器0xF5 IO CP SDP SDP_IO VDP AVLINK CEC MAP MAP MAP MAP MAP MAP MAP SLAVE SLAVE SLAVE SLAVE SLAVE SLAVE SLAVE ADDRESS: ADDRESS: ADDRESS: ADDRESS: ADDRESS: ADDRESS: ADDRESS: 0x40 PROGRAMMABLE PROGRAMMABLE PROGRAMMABLE PROGRAMMABLE PROGRAMMABLE PROGRAMMABLE SCL SDA SLAVE SLAVE SLAVE SLAVE SLAVE ADDRESS: ADDRESS: ADDRESS: ADDRESS: ADDRESS: PROGRAMMABLE PROGRAMMABLE PROGRAMMABLE PROGRAMMABLE PROGRAMMABLE HDMI EDID REPEATER AFE, DPLL INFOFRAME MAP MAP MAP MAP MAP 08849-008 图9. 寄存器映射架构 Rev. B | Page 25 of 28

ADV7842 外形尺寸 17.20 A1 BALL CORNER 17.00 SQ 16.80 16151413121110987654 32 1 A B C BALL A1 D CORNER E 15.00 F BSC SQ G H J K L M 1.00 N BSC P R T TOP VIEW BOTTOM VIEW DETAIL A DETAIL A 1.10 MAX 1.70 MAX 0.25 MIN 0.30 MIN 0.70 0.60 COPLANARITY 0.20 SEATING 0.50 PLANE BALL DIAMETER COMPLIANT TO JEDEC STANDARDS MO-192-AAF-1 022007-A 图10. 256引脚CSP_BGA封装 (BC-256-3) 尺寸单位:mm 订购指南 型号1 注释 温度范围 封装描述 封装选项 ADV7842KBCZ-5 2, 3 −10°C 至 +70°C 256引脚CSP_BGA封装 BC-256-3 BC-256-3 ADV7842KBCZ-5P 2, 4, 5 −10°C 至 +70°C 256引脚CSP_BGA封装 BC-256-3 BC-256-3 EVAL-ADV7842EB1Z 3, 6, 7 前端评估板 EVAL-ADV7842EB2Z 5, 6, 8 前端评估板 1 Z = 符合RoHS标准的器件。 2 速度等级:5 = 170 MHz。 3 此器件利用内部HDCP密钥进行编程。要购买任何带有内部HDCP密钥的器件,客户必须具有HDCP采用者身份(授权要求请咨询Digital Content Protection,LLC)。 4 HDCP功能:P = 无HDCP功能(专业版)。 5 针对非HDCP加密应用的专业版。购买者无需具有HDCP采用者身份。 6 为了处理ADV7842数字输出并实现视频输出,同时需要一个ATV母板。通过HDMI发送器和视频编码器评估性能时,ATV视频输出板是可选的。 7 ATV视频评估平台的前端板,安装有ADV7842KBCZ-5解码器。 8 ATV视频评估平台的前端板,安装有ADV7842KBCZ-5P解码器。 Rev. B | Page 26 of 28

ADV7842 注释 Rev. B | Page 27 of 28

ADV7842 注释 I2C指最初由Philips Semiconductors(现为NXP Semiconductors)开发的一种通信协议。 HDMI、HDMI商标和High-Definition Multimedia Interface是HDMI Licensing LLC公司在美国及其他国家的商标或注册商标。 ©2010-2011 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D08849sc-0-7/11(B) Rev. B | Page 28 of 28

Datasheet下载

Datasheet下载