ICGOO在线商城 > 开发板,套件,编程器 > 评估和演示板和套件 > EVAL-ADV7181CLQEBZ

- 型号: EVAL-ADV7181CLQEBZ

- 制造商: Analog

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

EVAL-ADV7181CLQEBZ产品简介:

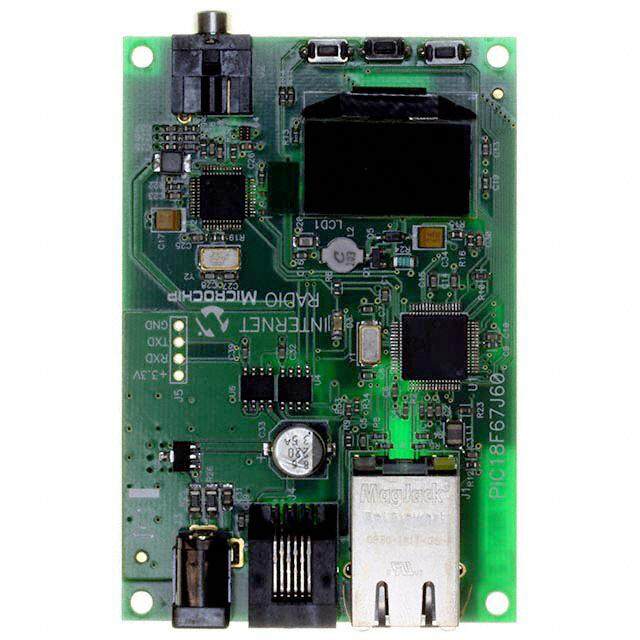

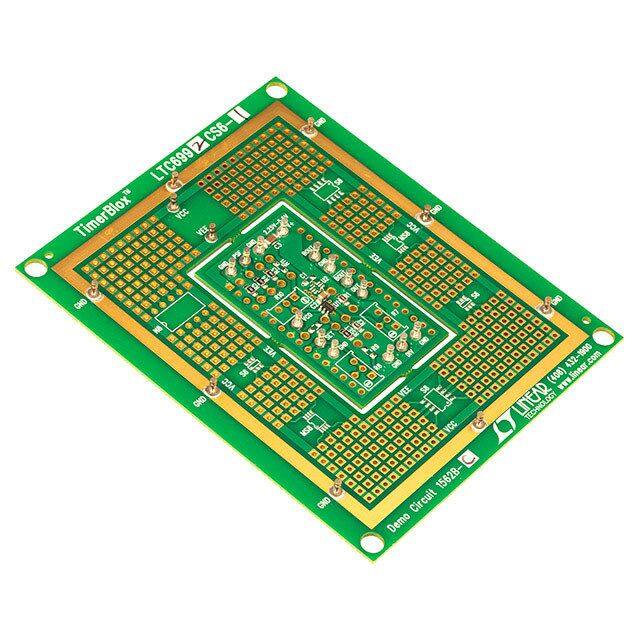

ICGOO电子元器件商城为您提供EVAL-ADV7181CLQEBZ由Analog设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 EVAL-ADV7181CLQEBZ价格参考。AnalogEVAL-ADV7181CLQEBZ封装/规格:评估和演示板和套件, ADV7181CLQ Video Decoder Video Evaluation Board。您可以下载EVAL-ADV7181CLQEBZ参考资料、Datasheet数据手册功能说明书,资料中有EVAL-ADV7181CLQEBZ 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 编程器,开发系统嵌入式解决方案 |

| 描述 | BOARD EVAL FOR ADV7181CLQ视频 IC 开发工具 EVAL BRD ADV7181C |

| 产品分类 | |

| 品牌 | Analog Devices |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 模拟与数字IC开发工具,视频 IC 开发工具,Analog Devices EVAL-ADV7181CLQEBZ- |

| 数据手册 | |

| 产品型号 | EVAL-ADV7181CLQEBZ |

| 主要属性 | - |

| 主要用途 | 视频,视频解码器 |

| 产品 | Evaluation Boards |

| 产品种类 | 视频 IC 开发工具 |

| 使用的IC/零件 | ADV7181CLQ |

| 其它名称 | EVALADV7181CLQEBZ |

| 商标 | Analog Devices |

| 封装 | Bulk |

| 嵌入式 | - |

| 工作电源电压 | 7 V |

| 工具用于评估 | ADV7181C |

| 工厂包装数量 | 1 |

| 所含物品 | 板 |

| 接口类型 | HDMI, USB, Video |

| 标准包装 | 1 |

| 用于 | ADV7181C |

| 类型 | Video Encoder |

| 系列 | ADV7181C |

| 辅助属性 | - |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

10位、集成式、多格式 标清电视/高清电视 视频解码器和RGB图形数字化仪 ADV7181C 产品特性 概述 四个10位ADC,采样速率最高可达110 MHz ADV7181C是一款高质量、单芯片、多格式视频解码器和 6个模拟输入通道 图形数字化仪。这款多格式解码器支持将复合视频或S视 支持SCART快速消隐 频形式的PAL、NTSC和SECAM标准信号转换为数字ITU-R 内部抗混叠滤波器 支持NTSC、PAL、SECAM色彩标准 BT.656格式。它还支持将RGB/YPrPb分量视频信号解码为 支持525p/625p分量逐行扫描 数字YCrCb或RGB像素输出流。支持的分量视频包括 支持720p/1080i分量高清电视 525i、625i、525p、625p、720p、1080i等标准,以及许多 可对最高达1024 × 768、70 Hz (XGA)的RGB图形进行数字化 其它高清和SMPTE标准。该器件也支持图形数字化,能够 处理 对VGA至XGA速率的RGB图形信号进行数字化处理,将其 3 × 3颜色空间转换矩阵 转换为数字DDR RGB或YCrCb像素输出流。此外能够同时 工业温度范围:−40°C至+85°C 12位4:4:4 DDR、8/10/16/20位SDR像素输出接口 处理CVBS和标清RGB信号,从而支持SCART和叠加功 可编程中断请求输出引脚 能。这些信号的混合由快速消隐引脚控制。 小尺寸封装 ADV7181C主要包含两个处理部分。第一部分为标清处理 引脚数量减少 器(SDP),可处理所有类型的PAL、NTSC和SECAM信号。 适用于视频和图形的单前端 VBI数据分隔器(包括图文电视) 第二部分为分量处理器(CP),可处理YPrPb和RGB分量格 通过汽车应用认证 式,包括RGB图形。 应用 注意,ADV7181C具有独特的软件和硬件配置要求。更多 车载娱乐设备 信息参见本数据手册的第19页。 高清电视 液晶/DLP投影仪 带个人录像机功能的高清电视机顶盒 支持逐行扫描输入的DVD刻录机 AVR接收机 Rev. E Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other O ne Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Tel: 781.329.4700 www.analog.com Trademarks and registered trademarks are the property of their respective owners. Fax: 781.461.3113 ©2008–2012Analog Devices, Inc. All rights reserved. ADI中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI不对翻译中存在的差异或由此产生的错误负责。如需确认任何词语的准确性,请参考ADI提供 的最新英文版数据手册。

ADV7181C 目录 特性..................................................................................................1 CP像素数据输出模式...........................................................12 应用..................................................................................................1 复合和S视频处理..................................................................12 概述..................................................................................................1 分量视频处理.........................................................................13 修订历史.........................................................................................2 RGB图形处理.........................................................................13 功能框图.........................................................................................3 通用特性..................................................................................13 技术规格.........................................................................................4 详细说明.......................................................................................14 电气特性....................................................................................4 模拟前端..................................................................................14 视频规格....................................................................................5 标清处理器(SDP)...................................................................14 时序特性....................................................................................6 分量处理器(CP).....................................................................14 模拟规格....................................................................................8 模拟输入多路复用................................................................15 绝对最大额定值............................................................................9 像素输出格式化..........................................................................17 封装热性能...............................................................................9 外部环路滤波器元件建议........................................................18 热规格........................................................................................9 典型连接图...................................................................................19 ESD警告.....................................................................................9 外形尺寸.......................................................................................20 引脚配置和功能描述.................................................................10 订购指南..................................................................................20 功能详解.......................................................................................12 汽车应用级产品.....................................................................20 模拟前端..................................................................................12 SDP像素数据输出模式........................................................12 修订历史 2012年8月—修订版D至修订版E 更改SDP像素数据输出模式部分............................................12 更改表3..........................................................................................6 更改RGB图形处理部分.............................................................13 更改图6.........................................................................................10 更改分量处理器(CP)部分.........................................................14 更改模拟输入多路复用部分....................................................15 2012年12月-修订版C至修订版D 更改特性和概述部分...................................................................1 2009年4月—修订版A至修订版B 增加“典型连接图”部分的文字................................................19 更改封装热性能部分...................................................................8 增加“汽车应用级产品”部分.....................................................20 更改引脚配置和功能描述部分.................................................9 删除LFCSP_VQ封装..................................................................19 2009年12月—修订版B至修订版C 更改“订购指南”...........................................................................19 更改产品名称、特性部分和概述部分....................................1 更改图1...........................................................................................3 2009年1月——修订版0至修订版A 更改表1的电源要求参数.............................................................4 更改表1的模拟电源电流参数....................................................4 更改表3的系统时钟和晶振参数以及注释3............................6 更改封装热性能部分...................................................................8 删除表3的注释3;重新排序......................................................6 删除热规格部分............................................................................8 增加时序图部分............................................................................7 增加引脚65(EPAD)....................................................................10 将“AVDD = 3.1.5 V至3.45 V”改为 更改模拟输入多路复用部分....................................................15 “AVDD = 3.15 V至3.45 V”...........................................................8 更改“订购指南”...........................................................................20 更改封装热性能............................................................................9 2008年8月—版本0:初始版 增加热规格部分............................................................................9 Rev. E | Page 2 of 20

ADV7181C 功能框图 100-31570 PIXELDATA P19TOP10 P9TOP0 HS/CS VS FIELD/DE LLC SFL/SYNCOUT INT 0 0 1 1 RETTAMROF DNA OFIF TUPTUO 20 20 ERY FASTBLANKOVERLAYCONTROLANDAV CODEINSERTION AV CODEINSERTION V CO Y Cr Cb Y Cr Cb E ON PROCESSOR DARDVBI DATA RTECTION LUMALUMA2D COMBRESAMPLE(5H MAX) RESAMPLECONTROL CHROMACHROMA2D COMBRESAMPLE(4H MAX) T PROCESSOR CGMS DATAEXTRACTION OFFSETCONTROL DARD DEFINITI STANAUTODE LUMAFILTER SYNCEXTRACT CHROMAFILTER COMPONEN MACROVISIONDETECTION GAINCONTROL N A T N S ON K MACROVISIDETECTIO BS/Y FSCRECOVERY CHROMADEMOD ACTIVE PEAANDAGC DIGITALFINECLAMP V C VBS C Cr Cb 10 10 10 C EN CO PASI 0 0 0 0 SR 1 1 1 1 RE DATAREPROCESSOR DECIMATIONANDOWNSAMPLINGFILTERS COLO CONV P D 0 0 0 0 1 1 1 1 0 1 2 3 C C C C D D D D A A A A A D C ANTI-CLAMPALIASFILTER ANTI-CLAMPALIASINPUTFILTERMUX ANTI-CLAMPALIASFILTER ANTI-CLAMPALIASFILTER SERIAL INTERFACECONTROLAND VBI DAT SYNC PROCESSINGANCLOCK GENERATION SSPDSTDI XTALXTAL1 1 ADV718 A6IN1TO6AIN CVBSS-VIDEOYPrPbSCART–B + CVBS)HICS RGB FB SCLK SDATA ALSB HS_IN/CS_INVS_IN OG/SOY GP S RA (R G 图1. Rev. E | Page 3 of 20

ADV7181C 技术规格 电气特性 AVDD = 3.15 V至3.45 V,DVDD = 1.65 V至2.0 V,DVDDIO = 3.0 V至3.6 V,PVDD = 1.71 V至1.89 V,标称输入范围1.6 V。 除非另有说明,T 至T = −40°C至+85°C。 MIN MAX 表1. 参数1, 2 符号 测试条件 最小 值典型 值 最大 值 单位 静态性能3, 4 分辨率(每个ADC) N 10 位 积分非线性 积分 非线性(INL) BSL 27 MHz(10位水平) ±0.6 ±2.5 LSB BSL 54 MHz(10位水平) −0.6/+0.7 LSB BSL 74 MHz(10位水平) ±1.4 LSB BSL 110 MHz(8位水平) ±0.9 LSB 差分非线性 差分 非线性(DNL)误差: 27 MHz(10位水平) −0.2/+0.25 −0.99/+2.5 LSB 54 MHz(10位水平) −0.2/+0.25 LSB 74 MHz(10位水平) ±0.9 LSB 110 MHz(8位水平) −0.2/+1.5 LSB 数字输入5 高输入电压6 V 2 V IH HS_IN、VS_IN低电平触发模式 0.7 V 低输入电压7 V 0.8 V IL HS_IN、VS_IN低电平触发模式 0.3 V 输入电流 I −10 +10 µA IN 输入电容5 C 10 pF IN 数字输出 高输出电压8 V I = 0.4 mA 2.4 V OH SOURCE 低输出电压8 V I = 3.2 mA 0.4 V OL SINK 高阻抗漏电流 I 引脚1 60 µA LEAK 所有其他输出引脚 10 µA 输出电容5 C 20 pF OUT 电源要求5 数字内核电源 DVDD 1.65 1.8 2 V 数字I/O电源 DVDDIO 3.0 3.3 3.6 V PLL电源 PVDD 1.71 1.8 1.89 V 模拟电源 AVDD 3.15 3.3 3.45 V 数字内核电源电流 IDVDD CVBS输入采样速率54 MHz 105 mA 图形RGB采样速率75 MHz 90 mA SCART RGB FB采样速率54 MHz 106 mA 数字I/O电源电流 IDVDDIO CVBS输入采样速率54 MHz 4 mA 图形RGB采样速率75 MHz 38 mA PLL电源电流 IPVDD CVBS输入采样速率54 MHz 11 mA 图形RGB采样速率75 MHz 12 mA 模拟电源电流9 IAVDD CVBS输入采样速率54 MHz 99 mA 图形RGB采样速率75 MHz 166 mA SCART RGB FB采样速率54 MHz 200 mA 掉电电流 IPWRDN 2.25 mA 绿色省电模式 IPWRDNG 同步旁路功能 16 mA 上电时间 TPWRUP 20 ms 1 在此范围内保证最大值和最小值性能规格。 2 所有规格均是利用ADI公司推荐的编程脚本获得。 3 所有ADC线性测试的输入范围均为满量程− 12.5%至零量程+ 12.5%。 4 INL和DNL最大值是在器件配置为分量视频输入的条件下获得。 5 通过特性保证。 6 为在引脚22上获得规定的V 电平,需将值0x04写入寄存器0x13 (WO)。如果将值0x00写入寄存器0x13,则引脚22上的V 为1.2 V。 IH IH 7 为在引脚22上获得规定的V 电平,需将值0x04写入寄存器0x13 (WO)。如果将值0x00写入寄存器0x13,则引脚22上的V 为0.4 V。 IL IL 8 V 和V 电平是使用寄存器子地址0xF4中的默认驱动强度值(0xD5)而获得。 OH OL 9 仅测量CVBS电流时,ADC0上电。仅测量RGB电流时,ADC0、ADC1和ADC2上电。测量SCART FB电流时,所有ADC均上电。 Rev. E | Page 4 of 20

ADV7181C 视频规格 AVDD = 3.15 V至3.45 V,DVDD = 1.65 V至2.0 V,DVDDIO = 3.0 V至3.6 V,PVDD = 1.71 V至1.89 V。除非另有说明, T 至T = −40°C至+85°C。 MIN MAX 表2. 参数1, 2 符号 测试条件 最小 值 典型 值 最大 值 单位 非线性规格 差分相位 DP CVBS输入,5步调制 0.5 度 差分增益 DG CVBS输入,5步调制 0.5 % 亮度非线性 LNL CVBS输入,5步 0.5 % 噪声规格 未加权SNR 亮度斜坡 54 56 dB 未加权SNR 亮度平场 58 60 dB 模拟前端串扰 60 dB 锁定时间规格 水平锁定范围 −5 +5 % 垂直锁定范围 40 70 Hz f 副载波锁定范围 ±1.3 kHz SC 色彩锁定时间 60 行 同步深度范围3 20 200 % 色同步范围 5 200 % 垂直锁定时间 2 场 水平锁定时间 100 行 色度规格 色调精度 HUE 1 度 色彩饱和精度 CL_AC 1 % 色彩AGC范围 5 400 % 色度幅度误差 0.5 % 色度相位误差 0.4 度 色度亮度交调 0.2 % 亮度规格 亮度精度 CVBS,1 V输入 1 % 亮度对比度精度 CVBS,1 V输入 1 % 1 在此范围内保证最大值和最小值性能规格。 2 通过特性保证。 3 标称同步深度为300 mV(100%同步深度范围)。 Rev. E | Page 5 of 20

ADV7181C 时序特性 AVDD = 3.15 V至3.45 V,DVDD = 1.65 V至2.0 V,DVDDIO = 3.0 V至3.6 V,PVDD = 1.71 V至1.89 V。除非另有说明, T 至T = −40°C至+85°C。 MIN MAX 表3. 参数1, 2 符号 测试条件 最小 值 典型值 最大值 单位 系统时钟和晶振 晶振标称频率 28.63636 MHz 晶振频率稳定性 ±50 ppm 水平同步输入频率 14.8 110 kHz LLC频率范围 12.825 110 MHz I2C端口3 SCLK频率 400 kHz SCLK最短脉冲宽度(高电平) t 0.6 µs 1 SCLK最短脉冲宽度(低电平) t 1.3 µs 2 保持时间(起始条件) t 0.6 µs 3 建立时间(起始条件) t 0.6 µs 4 SDA建立时间 t 100 ns 5 SCLK和SDA上升时间 t 300 ns 6 SCLK和SDA下降时间 t 300 ns 7 停止条件的建立时间 t 0.6 µs 8 复位特性 复位脉冲宽度 5 ms 时钟输出 LLC传号空号比 t:t 45:55 55:45 %占空比 9 10 数据和控制输出 数据输出转换时间SDR(SDP)4 t 负时钟沿至有效数据 3.6 ns 11 开始 数据输出转换时间SDR(SDP)4 t 有效数据结束至负时 2.4 ns 12 钟沿 数据输出转换时间SDR(CP)5 t 有效数据结束至负时 2.8 ns 13 钟沿 数据输出转换时间SDR(CP)5 t 负时钟沿至有效数据 0.1 ns 14 开始 数据输出转换时间DDR(CP)5, 6 t 正时钟沿至有效数据 1.9 ns 15 结束 数据输出转换时间DDR(CP)5, 6 t 有效数据起始至正时 1.7 ns 16 钟沿 数据输出转换时间DDR(CP)5, 6 t 负时钟沿至有效数据 1.4 ns 17 结束 数据输出转换时间DDR(CP)5, 6 t 有效数据起始至负时 1.7 ns 18 钟沿 1 在此范围内保证最大值和最小值性能规格。 2 通过特性保证。 3 TTL输入值为0 V至3 V,上升/下降时间 ≤3 ns,在10%与90%点之间测量。 4 SDP时序数值是使用寄存器子地址0xF4中的默认驱动强度值(0xD5)而获得。 5 CP时序数值是使用寄存器子地址0xF4中的最大驱动强度值(0x3F)而获得。 6 通过特性保证,最高75 MHz像素时钟。 Rev. E | Page 6 of 20

ADV7181C 时序图 t3 t5 t3 SDATA t6 t1 SCLK t2 t7 t4 t8 07513-103 图2. I2C时序 t9 t10 LLC t11 t12 P0 STFOL P/S1FY9I,NE VCLS_D,O/ DHUEST,, 07513-104 图3. 像素端口和控制SDR输出时序(SD内核) t9 t10 LLC t13 t14 P0TO P19 07513-105 图4. 像素端口和控制SDR输出时序(CP内核) LLC t16 t18 t15 t17 P0TO P19 05340-006 图5. 像素端口和控制DDR输出时序(CP内核) Rev. E | Page 7 of 20

ADV7181C 模拟规格 AVDD = 3.15 V至3.45 V,DVDD = 1.65 V至2.0 V,DVDDIO = 3.0 V至3.6 V,PVDD = 1.71 V至1.89 V。除非另有说明, T 至T = −40°C至+85°C。建议模拟输入视频信号范围:0.5 V至1.6 V,典型值1 V p-p。 MIN MAX 表4. 参数1, 2 测试条件 最小值 典型 值 最大 值 单位 箝位电路 外部箝位电容 0.1 µF 输入阻抗;引脚34(FB)除外 箝位断开 10 MΩ 引脚34(FB)的输入阻抗 20 kΩ CML 1.86 V ADC满量程电平 CML + 0.8 V ADC零电平 CML − 0.8 V ADC动态范围 1.6 V 箝位电平(锁定时) CVBS输入 CML – 0.292 V SCART RGB输入(R、G、B信号) CML – 0.4 V S视频输入(Y信号) CML – 0.292 V S视频输入(C信号) CML – 0 V 分量输入(Y、Pr、Pb信号) CML – 0.3 V PC RGB输入(R、G、B信号) CML – 0.3 V 大箝位源电流 仅SDP 0.75 mA 大箝位吸电流 仅SDP 0.9 mA 小箝位源电流 仅SDP 17 µA 小箝位吸电流 仅SDP 17 µA 1 在此范围内保证最大值和最小值性能规格。 2 通过特性保证。 Rev. E | Page 8 of 20

ADV7181C 绝对最大额定值 封装散热性能 表5. 为了降低器件功耗,请关断所有不用的ADC。 参数 额定值 AVDD至AGND 4 V 针对下列高电流模式,必须使用推荐的脚本:SCART、 DVDD至DGND 2.2 V 720p、1080i和所有RGB图形标准。使用推荐的脚本可确保 PVDD至AGND 2.2 V 热性能正常。这些脚本可向本地现场应用工程师索取。 DVDDIO至DGND 4 V DVDDIO至AVDD −0.3 V至+0.3 V 结温必须始终低于最大结温(T )125°C。结温可以通过下 J MAX PVDD至DVDD −0.3 V至+0.3 V 式计算: DVDDIO至PVDD −0.3 V至+2 V T = T + (θ × W ) DVDDIO至DVDD −0.3 V至+2 V J A MAX JA MAX AVDD至PVDD −0.3 V至+2 V 其中: AVDD至DVDD −0.3 V至+2 V T = 85°C. A MAX 数字输入电压至DGND DGND − 0.3 V至 θ = 45.5°C/W. JA DVDDIO + 0.3 V W = ((AVDD × IAVDD) + (DVDD × IDVDD) + MAX 数字输出电压至DGND DGND − 0.3 V至 (DVDDIO × IDVDDIO) + (PVDD × IPVDD)). DVDDIO + 0.3 V 热规格 模拟输入至AGND AGND − 0.3 V至 AVDD + 0.3 V 表6. 工作温度范围 −40°C至+85°C 参数 测试条件 值 最大结温(T ) 125°C J MAX 结壳热阻θ 带实体接地层的4层PCB 典型值 存储温度范围 −65°C至+150°C JC 9.2°C/W 红外回流焊(20秒) 260°C 结至环境热阻θ 带实体接地层的4层PCB 典型值 JA 注意,超出上述绝对最大额定值可能会导致器件永久性 (静止空气) 45.5°C/W 损坏。这只是额定最值,并不能以这些条件或者在任何其 它超出本技术规范操作章节中所示规格的条件下,推断器 ESD警告 件能否正常工作。长期在绝对最大额定值条件下工作会影 ESD(静电放电)敏感器件。 响器件的可靠性。 带电器件和电路板可能会在没有察觉的情况下放电。 尽管本产品具有专利或专有保护电路,但在遇到高 能量ESD时,器件可能会损坏。因此,应当采取适当 的ESD防范措施,以避免器件性能下降或功能丧失。 Rev. E | Page 9 of 20

ADV7181C 引脚配置和功能描述 N _I E S Y D C O VS FIELD/ P16 P17 P18 P19 DVDD DGND HS_IN/ VS_IN SCLK SDATA ALSB RESET SOG/S A6IN 64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 INT 1 48 AIN5 HS/CS 2 PIN 1 47 AIN4 DGND 3 46 AIN3 DVDDIO 4 45 NC P15 5 44 CAPC2 P14 6 43 AGND P13 7 42 CML ADV7181C P12 8 41 REFOUT SFL/SYNC_OUT 9 TOP VIEW 40 AVDD (Not to Scale) DGND 10 39 CAPY2 DVDDIO 11 38 CAPY1 P11 12 37 AGND P10 13 36 AIN2 P9 14 35 AIN1 P8 15 34 FB P7 16 33 NC 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 6 5 4 C 1 L D D 3 2 1 0 N F D D P P P LL XTAL XTA DVD DGN P P P P RDW ELP PVD AGN W P N1.ONTCE =S NO CONNECT. DO NOT CONNECT TO THIS PIN. 07513-002 图6. 引脚配置 表7. 引脚功能描述 引脚编号 引脚名称 类型1 描述 1 INT O 中断。此引脚可以是低电平有效或高电平有效。SDP/CP状态位改变就会触 发此引脚。触发中断的事件集由用户控制。 2 HS/CS O HS:水平同步输出 信号(SDP和CP模式)。 CS:数字复合同步信号(CP模式)。 3, 10, 24, 57 DGND G 数字地。 4, 11 DVDDIO P 数字I/O电源电压(3.3 V)。 28至25、19至12、8至5、 P0至P19 O 视频像素输出端口。输出配置模式参见表10。 62至59 9 SFL/SYNC_OUT O SFL:副载波频率锁定。该引脚包含一个串行输出流,可以在该解码器连到 任何ADI数字视频编码器时锁定副载波频率。 SYNC_OUT:分隔同步输出信号,仅在CP模式下可用。 20 LLC O 行锁定输出时钟。该引脚用于像素数据(12.825 MHz至110 MHz范围)。 21 XTAL1 O 该引脚应连到28.63636 MHz晶振;如果ADV7181C使用外部3.3 V、28.63636 MHz 时钟振荡器源,则该引脚应保持不连接状态。晶振模式下,晶振必须为基 频晶体。 22 XTAL I 28.63636 MHz晶振的输入引脚,也可以用为ADV7181C提供时钟的外部3.3 V、 28.63636 MHz时钟振荡器源过驱。 23, 58 DVDD P 数字内核电源电压(1.8 V)。 29 PWRDWN I 该引脚为逻辑0时,ADV7181C进入关断模式。 30 ELPF O 必须将推荐的外部环路滤波器连接到此ELPF引脚。 31 PVDD P PLL电源(1.8 V)。 32, 37, 43 AGND G 模拟地。 Rev. E | Page 10 of 20

ADV7181C 引脚编号 引脚名称 类型1 描述 33, 45 NC 不连接。这些引脚不在内部互连。 34 FB I 快速开关叠加输入。该引脚切换CVBS与RGB模拟信号。 35, 36, 46, 47, 48, 49 A 1至A 6 I 模拟视频输入通道。 IN IN 38, 39 CAPY1, CAPY2 I ADC电容网络。用于该引脚的推荐电容网络参见图9。 40 AVDD P 模拟电源电压(3.3 V)。 41 REFOUT O 内部基准电压输出。用于该引脚的推荐电容网络参见图9。 42 CML O 内部ADC的共模电平引脚(CML)。用于该引脚的推荐电容网络参见图9。 44 CAPC2 I ADC电容网络。用于该引脚的推荐电容网络参见图9。 50 SOG/SOY I 绿同步/亮度同步输入。用于嵌入式同步模式。 51 RESET I 系统复位输入,低电平有效。ADV7181C电路复位需要最短5 ms的低电平复位 脉冲。 52 ALSB I 该引脚选择ADV7181C控制端口和VBI回读端口的I2C地址。ALSB设为逻 辑0时,可设置控制端口0x40写操作的地址和VBI端口0x21的回读地 址。ALSB设为逻辑1时,可设置控制端口0x42写操作的地址和VBI端口 0x23的回读地址。 53 SDATA I/O I2C端口串行数据输入/输出引脚。 54 SCLK I I2C端口串行时钟输入。最大时钟速率为400 kHz。 55 VS_IN I VS输入信号。用于5线定时模式下的CP模式。 56 HS_IN/CS_IN I 该引脚可在CP模式下配置为数字HS输入信号或数字CS输入信号,用于 提取5线或4线RGB模式中的时序。 63 FIELD/DE O 场同步输出信号(所有隔行视频模式)。CP模式下,该引脚也可用作数据 使能信号(DE),允许直接连接到HDMI/DVI Tx IC。 64 VS O 垂直同步输出信号(SDP和CP模式)。 1 G = 接地,I = 输入,O = 输出,I/O = 输入/输出,P = 电源。 Rev. E | Page 11 of 20

ADV7181C 功能详解 复合和S视频处理 模拟前端 模拟前端部分包括4个高质量10位 ADC,6个模拟输入通道 复合和S视频处理特性支持NTSCVBS和S视频形式的C 多路复用器可以连接多个视频源,无需外部多路复用器。 M/J、NTSC 4.43、PAL B/D/I/G/H、PAL60、PAL M、PAL N和 它还包括: SECAM(B、D、G、K和L)标准,用于NTSC和PAL的超级 自适应、2D、5线梳状滤波器可为复合视频提供出色的色 • 4个电流和电压箝位控制环路,确保消除视频信号中的 度和亮度分离。它还能完全自动地检测和切换所有全球标 所有直流失调。 准(PAL、NTSC和SECAM),白色峰值模式下的自动增益控 • SCART功能和CVBS的SD RGB叠加功能,这些功能由快 制功能可确保始终以完整视频处理范围处理视频。其它特 速消隐输入控制。 性包括: • 4个内部抗混叠滤波器,用于消除标清输入视频信号的 带外噪声。 • 自适应数字线路长度跟踪(ADLLT™) • 专有架构支持锁定较弱、高噪声且不稳定的视频源,如 SDP像素数据输出模式 VCR和调谐器等 SDP像素数据输出模式如下: • IF滤波器模块补偿调谐器SAW滤波器所导致的高频亮度 • 8/10位ITU-R BT.656 4:2:2 YCrCb,带嵌入式时间码和/或 衰减 HS、VS、FIELD • 色度瞬态改善(CTI) • 16/20位YCrCb,带嵌入式时间码和/或HS、VS、FIELD • 亮度数字降噪(DNR) • 色彩控制功能包括色调、亮度、饱和度、对比度和Cr、 CP像素数据输出模式 Cb控制 CP像素数据输出模式包括单通道数据速率(SDR)和双通道 • 经过认证的Macrovision®版权保护检测功能适用于复合 数据速率(DDR),如下所示: 和S视频,支持所有全球格式(PAL/NTSC/SECAM) • SDR 8-/10位 4:2:2 YCrCb,支持525i、625i • CVBS、S视频和YUV模式支持4倍过采样(54 MHz) • SDR 16-/20位 4:2:2 YCrCb,支持所有标准 • 行锁定时钟输出(LLC) • DDR 8-/10位 4:2:2 YCrCb,支持所有标准 • 支持宽银幕检测 • DDR 12位 4:4:4 RGB,支持图形输入 • 无视频输入时,自由输出模式提供稳定的时序 • 垂直消隐间隔数据处理器,包括图文电视、视频编程系 统(VPS)、垂直间隔时间码(VITC)、字幕信息(CC)和扩 展数据服务(EDS)、宽屏幕信令(WSS)、版权生成管理系 统(CGMS)、兼容GemStar™ 1×/2×电子节目指南 • 由28.63636 MHz单晶振提供时钟 • 副载波频率锁定(SFL)输出用于下游视频编码器 • 差分增益典型值0.5% • 差分相位典型值0.5° Rev. E | Page 12 of 20

ADV7181C 分量视频处理 通用特性 分量视频处理支持525i、625i、525p、625p、720p、1080i ADV7181C的通用特性包括具有可编程位置、极性和宽度 及其它许多高清电视格式,同时支持自动增益(对比度)和 的HS/CS、VS和FIELD/DE输出信号,以及用于提示 失调(亮度)调整以及手动调整控制。分量视频处理支持的 SDP/CP状态变化的可编程中断请求输出引脚INT。其它特 其它特性包括: 性包括: • 带嵌入式同步或带独立HS、VS或CS的模拟分量 • 低功耗:1.8 V数字内核、3.3 V模拟和数字I/O、低功耗 YpbPr/RGB视频格式 关断模式及绿色PC模式 • 色彩空间转换矩阵,支持YCrCb转DDR RGB和RGB转 • 工业温度范围:−40°C至+85°C YCrCb • 64引脚、10 mm × 10 mm无铅LQFP封装 • 标准识别(STDI)支持系统级分量格式检测 • 3.3 V ADC提供增强的动态范围和性能 • 同步源极性检测器(SSPD)确定输入视频伴随的同步信号 的来源和极性 • 经过认证的Macrovision版权保护功能适用于分量格式 (525i、625i、525p和625p) • 无视频输入时,自由输出模式提供稳定的时序 • 支持对非标准视频源进行任意像素采样 RGB图形处理 RGB图形处理提供110 MSPS转换速率,支持最高达1024 × 768、70 Hz (UXGA)的RGB输入分辨率、图形模式的自动或 手动钳位和增益控制、对比度和亮度控制。其他特性包括: • 32相位DLL支持最佳像素时钟采样 • SSPD模块自动检测同步源和极性 • STDI模块支持标准识别 • RGB可通过色彩空间转换变为YcbCr,并通过降采样变 为4:2:2格式,以便与以视频为中心的后端IC接口 • 提供数据使能(DE)输出信号,以便直接连到HDMI/DVI Tx IC • 支持对非标准视频源进行任意像素采样 • 12位DDR格式支持RGB图形 Rev. E | Page 13 of 20

ADV7181C 详细说明 模拟前端 SDP可以处理各种VBI数据服务,例如:图文电视、字幕 信息(CC)、宽屏幕信令(WSS)、视频编程系统(VPS)、垂直 ADV7181C模拟前端包括4个10位 ADC,用来对模拟视频 间隔时间码(VITC)、版权生成管理系统(CGMS)、GemStar 信号进行数字化处理,然后将信号提供给SDP或CP。模拟 1×/2×和扩展数据服务(XDS)。ADV7181C SDP部分具有一个 前端使用差分通道连接各ADC,确保混合信号应用能够实 Macrovision 7.1检测电路,可检测I型、II型和III型保护级。 现高性能。 该解码器还能够稳定地支持所有Macrovision信号输入。 模拟前端还包括一个6通道输入多路复用器,支持将多个 视频信号施加于ADV7181C。各ADC前置电流和电压钳位 分量处理器(CP) 电路,确保视频信号始终在转换器的处理范围之内。下游 CP部分可以对任何色彩空间的广泛复合视频格式进行解码 的CP或SDP中的数字精密钳位电路对视频信号执行精密 和数字化处理。CP支持的分量视频标准包括525i、625i、 钳位。 525p、625p、720p、1080i、最高达XGA 70 Hz的图形以及许 多其它标准。 各ADC前置可选的抗混叠滤波器。这些滤波器可用来限制 标清视频信号的带宽,从而消除带外杂散噪声。 ADV7181C的CP部分含有一个AGC模块。无嵌入式同步 时,可以手动设置视频增益。AGC部分后接一个数字钳位 当解码复合和S视频输入时,ADC配置为4倍过采样模式; 电路,以确保将视频信号钳位于正确的消隐电平。CP的自 对于525i、625i、525p和625p视频源,则执行2×过采样。 动调整功能包括增益(对比度)和失调(亮度)调整,另外也 对所有其它视频标准执行1倍过采样。视频信号过采样可 支持手动调整控制。 降低外部抗混叠滤波器的成本和复杂度,并提高信噪比 (SNR)。 CP支持固定模式图形RGB转分量输出。 ADV7181C支持对CVBS和RGB标清信号进行同步处理,以 模拟前端和CP部分之间有一个色彩空间转换矩阵,支持 实现SCART兼容和叠加功能。在I2C寄存器和快速消隐引 YPrPb转DDR RGB和RGB转YCrCb。利用色彩空间转换器 脚的控制下,CVBS和RGB输入组合可以混合输出。 可以实施色彩空间的许多其它标准。 标清处理器(SDP) CP的输出部分非常灵活。它可以配置为SDR模式,每个时 钟周期提供一个数据包;或者配置为DDR模式,在时钟的 SDP部分可解码复合、S视频和YUV格式的许多基带视频信 上升沿和下降沿提供数据。SDR模式下,可以实现20位 号。SDP支持的视频标准包括PAL B/D/I/G/H、PAL60、 4:2:2格式。这些模式提供HS/CS、VS和FIELD/DE(如适用) PAL M、PAL N、NTSC M/J、NTSC 4.43和SECAM B/D/G/ 时序参考信号。在DDR模式下,ADV7181C可以提供具有 K/L。ADV7181C自动检测视频标准,并进行相应处理。 相应时序信号的8位 4:2:2 YCrCb或12位 4:4:4 RGB像素输出 SDP具有一个5线式超级自适应2D梳状滤波器,可在解码 接口。 复合视频信号时提供出色的色度和亮度分离。这种自适应 CP部分具有一个检测电路,可以检测525i、625i、525p和 滤波器根据视频标准和信号质量自动调整处理模式,无需 625p标准的Macrovision编码YPrPb信号。它能够稳定地支 用户干预。SDP还有一个IF滤波器模块,可补偿调谐器 持此类信号的解码。 SAW滤波器所导致的高频亮度频谱衰减。 分量数据的VBI提取由ADV7181C的CP部分执行,支持隔行、 SDP有专门的亮度和色度参数来控制亮度、对比度、饱和 逐行和高清扫描速率。提取的数据可通过I2C接口回读。 度和色调。 ADV7181C采用专利ADLLT算法来跟踪VCR等视频源的变 化的视频行长。ADLLT使ADV7181C能够跟踪和解码质量 不佳的视频源,如VCR、调谐器输出、VCD播放器和便携 式摄像机的高噪声源等。SDP还含有一个色度瞬态改变 (CTI)处理器,它可以提高色度转换的边沿速率,使视频图 像更清晰。 Rev. E | Page 14 of 20

ADV7181C 模拟输入多路复用 ADV7181C集成一个模拟多路复用部分,允许多个视频信号源连接到该解码器。图7显示了ADV7181C输入多路复用部分的 整体结构。 1 2 3 4 5 6 N N N N N N ADC_SW_MAN_EN AI AI AI AI AI AI 1 ADC0_SW[3:0] AIN1 AIN2 AIN3 AIN4 ADC0 AIN5 AIN6 1 ADC1_SW[3:0] AIN3 AIN4 AIN5 AIN6 ADC1 1 ADC2_SW[3:0] AIN2 AIN4 AIN5 AIN6 ADC2 1 ADC3_SW[3:0] AIN4 ADC3 07513-003 图7. 内部引脚连接 Rev. E | Page 15 of 20

ADV7181C 对于ADV7181C,建议使用表8所示的ADC映射。 表8. ADC映射建议 模式 ADC映射要求 AIN通道 内核 配置1 CVBS ADC0 CVBS = A 1 SD INSEL[3:0] = 0000 IN SDM_SEL[1:0] = 00 PRIM_MODE[3:0] = 0000 VID_STD[3:0] = 0010 YC/YC自动 Y = ADC0 Y = A 2 SD INSEL[3:0] = 0000 IN C = ADC1 C = A 3 SDM_SEL[1:0] = 11 IN PRIM_MODE[3:0] = 0000 VID_STD[3:0] = 0010 分量YUV Y = ADC0 Y = A 6 SD INSEL[3:0] = 1001 IN U = ADC2 U = A 4 SDM_SEL[1:0] = 00 IN V = ADC1 V = A 5 PRIM_MODE[3:0] = 0000 IN VID_STD[3:0] = 0010 分量YUV Y = ADC0 Y = A 6 CP INSEL[3:0] = 0000 IN U = ADC2 U = A 4 SDM_SEL[1:0] = 00 IN V = ADC1 V = A 5 PRIM_MODE[3:0] = 0000 IN VID_STD[3:0] = 1010 SCART RGB CBVS = ADC0 CVBS = A 2 SD INSEL[3:0] = 0000 IN G = ADC1 G = A 6 SDM_SEL[1:0] = 00 IN B = ADC3 B = A 4 PRIM_MODE[3:0] = 0000 IN R = ADC2 R = A 5 VID_STD[3:0] = 0010 IN 图形 G = ADC0 G = A 6 CP INSEL[3:0] = 0000 IN RGB模式 B = ADC2 B = A 4 SDM_SEL[1:0] = 00 IN R = ADC1 R = A 5 PRIM_MODE[3:0] = 0001 IN VID_STD[3:0] = 1100 1 以正确格式对后续模块进行格式化的配置。 表9. 所有ADC的手动多路复用设置 ADC_SWITCH_MAN置1 ADC0_SW_SEL[3:0] ADC0 连接 ADC1_SW_SEL[3:0] ADC1 连接 ADC2_SW_SEL[3:0] ADC2 连接 ADC3_SW_SEL[3:0] ADC3连接 0001 A 1 0001 不适 用 0001 不适 用 0001 不适 用 IN 0010 A 2 0010 不适 用 0010 A 2 0010 不适 用 IN IN 0100 A 4 0100 A 4 0100 A 4 0100 A 4 IN IN IN IN 0101 A 5 0101 A 5 0101 A 5 0101 不适 用 IN IN IN 0110 A 6 0110 A 6 0110 A 6 0110 不适 用 IN IN IN 1100 A 3 1100 A 3 1100 不适 用 1100 不适 用 IN IN 必须直接控制ADV7181C的模拟输入多路复用,这种方式 表9列出了下列情况的ADC映射配置: 称为手动输入多路复用。ADC_SWITCH_MAN位设为1可 • ADC_SW_MAN_EN,手动输入多路复用使能,IO映 激活手动多路复用(见表9)。它只影响ADC之前的模拟开 射,地址C4[7] 关。INSEL、SDM_SEL、PRIM_MODE和VID_STD仍然要 • ADC0_SW[3:0],ADC0多路复用配置,IO映射,地址 求进行设置,以便后续模块以正确的格式处理视频数据。 C3[3:0] 并非每个输入引脚都能连接到任何ADC。IC内部的模拟信 • ADC1_SW[3:0],ADC1多路复用配置,IO映射,地址 号路由对通道连接做出了一些限制。表9概要显示了芯片 C3[7:4] 之内的路由能力。4个多路复用部分可以通过保留的控制 • ADC2_SW[3:0],ADC2多路复用配置,IO映射,地址 信号总线ADC0_SW[3:0]/ADC1_SW[3:0]/ADC2_SW C4[3:0] [3:0]/ADC3_SW[3:0]进行控制。 • ADC3_SW[3:0],ADC3多路复用配置,IO映射,地址F3 [7:4] Rev. E | Page 16 of 20

ADV7181C 像素输出格式化 表10. 像素输出格式 处理器、格式和模式 像素端口引脚P[19:0] 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 视频输出8位 SDP YCrCb[7:0] 4:2:2 视频输出10位 SDP YCrCb[9:0] 4:2:2 视频输出16位 SDP Y[7:0] CrCb[7:0] 4:2:2 视频输出20位 SDP Y[9:0] CrCb[7:0] 4:2:2 视频输出12位 D71 D61 D51 D41 D31 D21 D11 D01 D111 D101 D91 D81 CP 4:4:4 B[7]↑ B[6]↑ B[5]↑ B[4]↑ B[3]↑ B[2]↑ B[1]↑ B[0]↑ G[3]↑ G[2]↑ G[1]↑ G[0]↑ RGB DDR R[3]↓ R[2]↓ R[1]↓ R[0]↓ G[7]↓ G[6]↓ G[5]↓ G[4]↓ R[7]↓ R[6]↓ R[5]↓ R[4]↓ 视频输出16位 CP CHA[7:0](例如,Y[7:0]) CHB/C[7:0](例如,Cr/Cb[7:0]) 4:2:2 视频输出20位 CP CHA[9:0](例如,Y[9:0]) CHB/C[9:0](例如,Cr/Cb[9:0]) 4:2:2 1 ↑表示数据在LLC的上升沿提供,↓表示数据在LLC的下降沿提供。 Rev. E | Page 17 of 20

ADV7181C 推荐外部环路滤波器元件 ELPF引脚的外部环路滤波器元件应尽可能靠近相应的引 脚。图8给出了元件建议值。 ELPF 30 1.69kΩ 10nF 82nF PVDD = 1.8V 07513-004 图8. ELPF元件 Rev. E | Page 18 of 20

ADV7181C 典型连接图 500-31570 图9. 典型连接 欲获得最新软件配置文件,请访问中文技术论坛视频社区的ADV7181C设计支持文件网页。 Rev. E | Page 19 of 20

ADV7181C 外形尺寸 12.20 0.75 12.00 SQ 0.60 1.60 11.80 0.45 MAX 64 49 1 48 PIN 1 10.20 TOP VIEW 10.00 SQ (PINS DOWN) 9.80 1.45 0.20 1.40 0.09 1.35 7° 3.5° 0.15 0° 16 33 0.05 SPELAANTIENG 0.08 17 32 COPLANARITY VIEW A 0.27 0.50 BSC 0.22 VIEW A LEAD PITCH 0.17 ROTATED 90° CCW COMPLIANTTO JEDEC STANDARDS MS-026-BCD 051706-A 图10. 64引脚薄型四方扁平封装[LQFP] (ST-64-2) 尺寸单位:mm 订购指南 型号1, 2 温度范围 封装描述 封装选项 ADV7181CBSTZ −40°C至+85°C 64引脚 LQFP ST-64-2 ADV7181CBSTZ-REEL −40°C至+85°C 64引脚 LQFP ST-64-2 ADV7181CWBSTZ −40°C至+85°C 64引脚 LQFP ST-64-2 ADV7181CWBSTZ-REEL −40°C至+85°C 64引脚 LQFP ST-64-2 EVAL-ADV7181CLQEBZ LQFP评估板 1 Z = 符合RoHS标准的器件。 2 W = 通过汽车应用认证。 汽车应用级产品 ADV7181CW生产工艺受到严格控制,以提供满足汽车应用的质量和可靠性要求。请注意,车用型号的技术规格可能不同 于商用型号;因此,设计人员应仔细阅读本数据手册的技术规格部分。只有显示为汽车应用级的产品才能用于汽车应用。 欲了解特定产品的订购信息并获得这些型号的汽车可靠性报告,请联系当地ADI客户代表。 I2C指最初由Philips Semiconductors(现为NXP Semiconductors)开发的一种通信协议。 ©2008–2012 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D07513sc-0-8/12(E) Rev. E | Page 20 of 20

Datasheet下载

Datasheet下载