ICGOO在线商城 > 集成电路(IC) > 数据采集 - 数模转换器 > DAC8311IDCKT

- 型号: DAC8311IDCKT

- 制造商: Texas Instruments

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

DAC8311IDCKT产品简介:

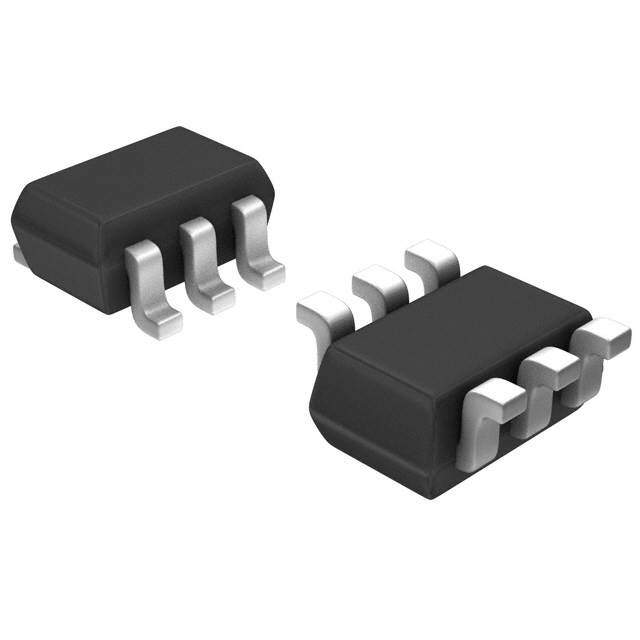

ICGOO电子元器件商城为您提供DAC8311IDCKT由Texas Instruments设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 DAC8311IDCKT价格参考。Texas InstrumentsDAC8311IDCKT封装/规格:数据采集 - 数模转换器, 14 位 数模转换器 1 SC-70-6。您可以下载DAC8311IDCKT参考资料、Datasheet数据手册功能说明书,资料中有DAC8311IDCKT 详细功能的应用电路图电压和使用方法及教程。

DAC8311IDCKT 是由 Texas Instruments(德州仪器)推出的一款 16 位缓冲电压输出数模转换器(DAC)。它属于数据采集系统中的数模转换器类别,广泛应用于需要高精度和低功耗的场景。以下是 DAC8311 的主要应用场景: 1. 工业自动化与控制 - 在工业控制系统中,DAC8311 可用于将数字信号转换为模拟信号,以驱动执行器、阀门或电机控制器。 - 它能够精确生成控制信号,适用于温度调节、压力控制和流量监测等场景。 2. 测试与测量设备 - DAC8311 的高分辨率和低功耗特性使其适合于测试与测量设备,如信号发生器、示波器校准工具和精密测量仪器。 - 它可以生成高精度的模拟波形,用于校准或仿真真实世界信号。 3. 医疗设备 - 在医疗领域,DAC8311 可用于医疗成像设备、监护仪和其他需要高精度信号生成的设备。 - 例如,它可以用于生成刺激信号,驱动超声波探头或心电图设备中的信号调理电路。 4. 通信系统 - 在通信系统中,DAC8311 能够生成精确的模拟信号,用于调制解调器、滤波器或其他射频(RF)前端模块。 - 它的低功耗设计有助于延长电池供电设备的使用寿命。 5. 消费电子 - 在一些高端消费电子产品中,DAC8311 可用于音频信号处理、可穿戴设备的传感器信号生成等领域。 - 其紧凑的封装形式和低功耗特性非常适合便携式设备。 6. 汽车电子 - 在汽车电子系统中,DAC8311 可用于发动机控制单元(ECU)、车载信息娱乐系统以及高级驾驶辅助系统(ADAS)中的信号生成。 - 它能够提供稳定的模拟输出,确保系统的可靠性和精度。 特性总结 - 高精度:16 位分辨率,适合对精度要求较高的应用。 - 低功耗:适合电池供电或对能耗敏感的设备。 - 宽工作电压范围:支持多种电源环境,适应性强。 - 小型封装:便于集成到空间受限的设计中。 综上所述,DAC8311IDCKT 广泛应用于需要高精度、低功耗和稳定性能的场景,是工业、医疗、通信和消费电子领域的理想选择。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC)半导体 |

| 描述 | IC DAC 14BIT 1CH V-OUT SC70-6数模转换器- DAC 14bit Sgl Ch 80uA 1.8V-5.5V DAC |

| 产品分类 | |

| 品牌 | Texas Instruments |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 数据转换器IC,数模转换器- DAC,Texas Instruments DAC8311IDCKT- |

| 数据手册 | |

| 产品型号 | DAC8311IDCKT |

| PCN设计/规格 | |

| 产品培训模块 | http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=13240 |

| 产品种类 | 数模转换器- DAC |

| 位数 | 14 |

| 供应商器件封装 | SC-70-6 |

| 其它名称 | 296-23760-6 |

| 分辨率 | 14 bit |

| 制造商产品页 | http://www.ti.com/general/docs/suppproductinfo.tsp?distId=10&orderablePartNumber=DAC8311IDCKT |

| 包装 | Digi-Reel® |

| 商标 | Texas Instruments |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装 | Reel |

| 封装/外壳 | 6-TSSOP,SC-88,SOT-363 |

| 封装/箱体 | SC-70-6 |

| 工作温度 | -40°C ~ 125°C |

| 工厂包装数量 | 250 |

| 建立时间 | 6µs |

| 接口类型 | Serial (SPI) |

| 数据接口 | 串行 |

| 最大工作温度 | + 125 C |

| 最小工作温度 | - 40 C |

| 标准包装 | 1 |

| 电压参考 | Supply |

| 电压源 | 单电源 |

| 电源电压-最大 | 5.5 V |

| 电源电压-最小 | 1.8 V |

| 积分非线性 | +/- 4 LSB |

| 稳定时间 | 6 us |

| 系列 | DAC8311 |

| 结构 | String |

| 转换器数 | 1 |

| 转换器数量 | 1 |

| 输出数和类型 | 1 电压,单极1 电压,双极 |

| 输出类型 | Voltage Buffered |

| 采样率(每秒) | * |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

Product Sample & Technical Tools & Support & Folder Buy Documents Software Community DAC8311,DAC8411 SBAS439C–AUGUST2008–REVISEDJULY2015 DAC8x11 2-V to 5.5-V, 80-μA, 14- and 16-Bit, Low-Power, Single-Channel, Digital-to-Analog Converters in SC70 Package 1 Features 3 Description • RelativeAccuracy: The DAC8311 (14-bit) and DAC8411 (16-bit) devices 1 are low-power, single-channel, voltage output digital- – 1LSBINL(DAC8311:14-bit) to-analog converters (DAC). They provide excellent – 4LSBINL(DAC8411:16-bit) linearity and minimize undesired code-to-code • microPowerOperation:80μAat2V transient voltages while offering an easy upgrade path within a pin-compatible family. All devices use a • Power-Down:0.5 μAat5V,0.1 μAat2V versatile, 3-wire serial interface that operates at clock • WidePowerSupply:2Vto5.5V rates of up to 50 MHz and is compatible with • Power-OnResettoZeroScale standard SPI™, QSPI™, Microwire, and digital signal processor(DSP)interfaces. • StraightBinaryDataFormat • LowPowerSerialInterfaceWithSchmitt- All devices use an external power supply as a TriggeredInputs:Upto50MHz reference voltage to set the output range. The devices incorporate a power-on reset (POR) circuit • On-ChipOutputBufferAmplifier,Rail-to-Rail that ensures the DAC output powers up at 0 V and Operation remains there until a valid write to the device occurs. • SYNCInterruptFacility The DAC8311 and DAC8411 contain a power-down • ExtendedTemperatureRange–40°Cto125°C feature, accessed over the serial interface, that reduces current consumption of the device to 0.1 μA • Pin-CompatibleFamilyinaTiny,6-PinSC70 at 2 V in power down mode. The low power Package consumption of these devices in normal operation makes it ideally suited for portable, battery-operated 2 Applications equipment. The power consumption is 0.55 mW at 5 • Portable,Battery-Poweredinstruments V,reducingto2.5μWinpower-downmode. • ProcessControls These devices are pin-compatible with the DAC5311, • DigitalGainandOffsetAdjustment DAC6311, and DAC7311, offering an easy upgrade path from 8-, 10-, and 12-bit resolution to 14- and 16- • ProgrammableVoltageandCurrentSources bit. All devices are available in a small, 6-pin, SC70 package. This package offers a flexible, pin- SimplifiedSchematic compatible, and functionally-compatible drop-in AV GND solution within the family over an extended DD temperaturerangeof –40°Cto125°C. Power-On Reset DeviceInformation(1) PARTNUMBER PACKAGE BODYSIZE(NOM) REF(+) ReDgAisCter 14-/16-Bit DAC OBuutfpfeurt VOUT DAC8311 SC70(6) 2.00mm×1.25mm DAC8411 (1) For all available packages, see the orderable addendum at theendofthedatasheet. Input Control Power-Down Logic Control Logic Resistor Network SYNC SCLK D IN 1 An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectualpropertymattersandotherimportantdisclaimers.PRODUCTIONDATA.

DAC8311,DAC8411 SBAS439C–AUGUST2008–REVISEDJULY2015 www.ti.com Table of Contents 1 Features.................................................................. 1 8.3 FeatureDescription.................................................22 2 Applications........................................................... 1 8.4 DeviceFunctionalModes........................................24 3 Description............................................................. 1 8.5 Programming...........................................................25 4 RevisionHistory..................................................... 2 9 ApplicationandImplementation........................ 27 9.1 ApplicationInformation............................................27 5 DeviceComparison............................................... 3 9.2 TypicalApplications................................................28 6 PinConfigurationandFunctions......................... 3 10 PowerSupplyRecommendations..................... 31 7 Specifications......................................................... 4 11 Layout................................................................... 32 7.1 AbsoluteMaximumRatings......................................4 11.1 LayoutGuidelines.................................................32 7.2 ESDRatings..............................................................4 11.2 LayoutExample....................................................32 7.3 RecommendedOperatingConditions.......................4 12 DeviceandDocumentationSupport................. 33 7.4 ThermalInformation..................................................4 7.5 ElectricalCharacteristics...........................................5 12.1 RelatedLinks........................................................33 7.6 TimingRequirements:14-Bit ...................................7 12.2 CommunityResources..........................................33 7.7 TimingRequirements:16-Bit....................................7 12.3 Trademarks...........................................................33 7.8 TypicalCharacteristics..............................................9 12.4 ElectrostaticDischargeCaution............................33 12.5 Glossary................................................................33 8 DetailedDescription............................................ 22 13 Mechanical,Packaging,andOrderable 8.1 Overview.................................................................22 Information........................................................... 33 8.2 FunctionalBlockDiagram.......................................22 4 Revision History NOTE:Pagenumbersforpreviousrevisionsmaydifferfrompagenumbersinthecurrentversion. ChangesfromRevisionB(May2013)toRevisionC Page • AddedESDRatingstable,FeatureDescriptionsection,DeviceFunctionalModes,ApplicationandImplementation section,PowerSupplyRecommendationssection,Layoutsection,DeviceandDocumentationSupportsection,and Mechanical,Packaging,andOrderableInformationsection ................................................................................................. 1 ChangesfromRevisionA(August,2011)toRevisionB Page • Changedall1.8Vto2.0Vthroughoutdatasheet................................................................................................................... 1 • Deleted1.8-VTypicalCharacteristicssection........................................................................................................................ 9 • ChangedX-axisforFigure35............................................................................................................................................... 13 • ChangedX-axisforFigure36............................................................................................................................................... 13 ChangesfromOriginal(August,2008)toRevisionA Page • Changedspecificationsandtestconditionsforinputlowvoltageparameter......................................................................... 6 • Changedspecificationsandtestconditionsforinputhighvoltageparameter....................................................................... 6 2 SubmitDocumentationFeedback Copyright©2008–2015,TexasInstrumentsIncorporated ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 www.ti.com SBAS439C–AUGUST2008–REVISEDJULY2015 5 Device Comparison Table1.RelatedDevices RELATEDDEVICES 16-BIT 14-BIT 12-BIT 10-BIT 8-BIT PinandFunction DAC8411 DAC8311 DAC7311 DAC6311 DAC5311 Compatible Table2.PackageInformation MAXIMUMDIFFERENTIAL PRODUCT MAXIMUMRELATIVEACCURACY(LSB) NONLINEARITY(LSB) DAC8411 ±8 ±2 DAC8311 ±4 ±1 6 Pin Configuration and Functions DCKPackage 6-PinSC70 TopView SYNC 1 6 V OUT SCLK 2 5 GND D 3 4 AV /V IN DD REF PinFunctions PIN I/O DESCRIPTION NAME NO. AV /V 4 I PowerSupplyInput,+2Vto+5.5V. DD REF SerialDataInput.Dataisclockedintothe24-bit(DAC8411)or16-bit(DAC8311)inputshift D 3 I IN registeronthefallingedgeoftheserialclockinput. GND 5 — Groundreferencepointforallcircuitryonthepart. SCLK 2 I SerialClockInput.Datacanbetransferredatratesupto50MHz. Level-triggeredcontrolinput(activelow).Thisistheframesychronizationsignalfortheinput data.WhenSYNCgoeslow,itenablestheinputshiftregisteranddataaretransferredinonthe fallingedgesofthefollowingclocks.TheDACisupdatedfollowingthe24th(DAC8411)or16th SYNC 1 I (DAC8311)clockcycle,unlessSYNCistakenhighbeforethisedge,inwhichcasetherising edgeofSYNCactsasaninterruptandthewritesequenceisignoredbytheDAC8x11.Referto theDAC8311andDAC8411SYNCInterruptsectionsformoredetails. V 6 O AnalogoutputvoltagefromDAC.Theoutputamplifierhasrail-to-railoperation. OUT Copyright©2008–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback 3 ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 SBAS439C–AUGUST2008–REVISEDJULY2015 www.ti.com 7 Specifications 7.1 Absolute Maximum Ratings overoperatingfree-airtemperaturerange(unlessotherwisenoted)(1) MIN MAX UNIT AV toGND –0.3 6 V DD Voltage DigitalinputvoltagetoGND –0.3 AV +0.3 V DD V toGND –0.3 AV +0.3 V OUT DD Junction,T max 150 °C J Temperature Storage,T –65 150 °C stg (1) StressesbeyondthoselistedunderAbsoluteMaximumRatingsmaycausepermanentdamagetothedevice.Thesearestressratings only,whichdonotimplyfunctionaloperationofthedeviceattheseoranyotherconditionsbeyondthoseindicatedunderRecommended OperatingConditions.Exposuretoabsolute-maximum-ratedconditionsforextendedperiodsmayaffectdevicereliability. 7.2 ESD Ratings VALUE UNIT Human-bodymodel(HBM),perANSI/ESDA/JEDECJS-001(1) ±1000 V(ESD) Electrostaticdischarge Charged-devicemodel(CDM),perJEDECspecificationJESD22- V C101(2) ±500 (1) JEDECdocumentJEP155statesthat500-VHBMallowssafemanufacturingwithastandardESDcontrolprocess. (2) JEDECdocumentJEP157statesthat250-VCDMallowssafemanufacturingwithastandardESDcontrolprocess. 7.3 Recommended Operating Conditions overoperatingfree-airtemperaturerange(unlessotherwisenoted) MIN NOM MAX UNIT T Operatingtemperature –40 +125 °C A AV Supplyvoltage 2.0 +5.5 V DD 7.4 Thermal Information DAC8x11 THERMALMETRIC(1) DCK(SC70) UNIT 6PINS R Junction-to-ambientthermalresistance 216.4 °C/W θJA R Junction-to-case(top)thermalresistance 52.1 °C/W θJC(top) R Junction-to-boardthermalresistance 65.9 °C/W θJB ψ Junction-to-topcharacterizationparameter 1.3 °C/W JT ψ Junction-to-boardcharacterizationparameter 65.2 °C/W JB R Junction-to-case(bottom)thermalresistance N/A °C/W θJC(bot) (1) Formoreinformationabouttraditionalandnewthermalmetrics,seetheSemiconductorandICPackageThermalMetricsapplication report,SPRA953. 4 SubmitDocumentationFeedback Copyright©2008–2015,TexasInstrumentsIncorporated ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 www.ti.com SBAS439C–AUGUST2008–REVISEDJULY2015 7.5 Electrical Characteristics atAV =2Vto5.5V,R =2kΩtoGND,andC =200pFtoGND,andT =–40°Cto+125°Cunlessotherwisenoted. DD L L A DAC8411,DAC8311 PARAMETER TESTCONDITIONS UNIT MIN TYP MAX STATICPERFORMANCE(1) Resolution 16 Bits Measuredbythelinepassing 3.6Vto5V ±4 ±8 Relativeaccuracy LSB DAC8411 throughcodes485and64714 2Vto3.6V ±4 ±12 Differential ±0.5 ±2 LSB nonlinearity Resolution 14 Bits Measuredbythelinepassingthroughcodes120and Relativeaccuracy ±1 ±4 LSB DAC8311 16200 Differential ±0.125 ±1 LSB nonlinearity Offseterror Measuredbythelinepassingthroughtwocodes(2) ±0.05 ±4 mV Offseterrordrift 3 μV/°C Zerocodeerror AllzerosloadedtotheDACregister 0.2 mV Full-scaleerror AllonesloadedtoDACregister 0.04 0.2 %ofFSR Gainerror 0.05 ±0.15 %ofFSR AVDD=5V ±0.5 ppmof Gaintemperaturecoefficient AV =2V ±1.5 FSR/°C DD OUTPUTCHARACTERISTICS Outputvoltagerange 0 AV V DD R =2kΩ,C =200pF,AV =5V, L L DD 6 10 μs Outputvoltagesettlingtime(3) 1/4scaleto3/4scale R =2MΩ,C =470pF 12 μs L L Slewrate 0.7 V/μs R =∞ 470 pF L Capacitiveloadstability R =2kΩ 1000 pF L Codechangeglitchimpulse 1LSBchangearoundmajorcarry 0.5 nV-s Digitalfeedthrough 0.5 nV-s Power-onglitchimpulse R =2kΩ,C =200pF,AV =5V 17 mV L L DD DCoutputimpedance 0.5 Ω AV =5V 50 mA DD Short-circuitcurrent AV =3V 20 mA DD Power-uptime Comingoutofpower-downmode 50 μs ACPERFORMANCE SNR 88 dB THD TA=25°C,BW=20kHz,16-bitlevel,AVDD=5V, –66 dB f =1kHz,1st19harmonicsremovedforSNR OUT SFDR calculation 66 dB SINAD 66 dB T =25°C,atzero-scaleinput, A 17 nV/√Hz f =1kHz,AV =5V DACoutputnoisedensity(4) OUT DD T =25°C,atmid-codeinput, A 110 nV/√Hz f =1kHz,AV =5V OUT DD DACoutputnoise(5) TA=25°C,atmid-codeinput, 3 μV 0.1Hzto10Hz,AV =5V pp DD (1) Linearitycalculatedusingareducedcoderangeof485to64714for16-bit,and120to16200for14-bit,outputunloaded. (2) Straightlinepassingthroughcodes485and64714for16-bit,and120and16200for14-bit,outputunloaded. (3) Specifiedbydesignandcharacterization,notproductiontested. (4) Formoredetails,seeFigure33. (5) Formoredetails,seeFigure34. Copyright©2008–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback 5 ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 SBAS439C–AUGUST2008–REVISEDJULY2015 www.ti.com Electrical Characteristics (continued) atAV =2Vto5.5V,R =2kΩtoGND,andC =200pFtoGND,andT =–40°Cto+125°Cunlessotherwisenoted. DD L L A DAC8411,DAC8311 PARAMETER TESTCONDITIONS UNIT MIN TYP MAX LOGICINPUTS(3) Inputcurrent ±1 μA AV =2.7Vto5.5V 0.3×AV V DD DD V L,inputlowvoltage IN AV =2Vto2.7V 0.1×AV V DD DD AV =2.7Vto5.5V 0.7×AV V DD DD V H,inputhighvoltage IN AV =2Vto2.7V 0.9×AV V DD DD Pincapacitance 1.5 3 pF POWERREQUIREMENTS AV 2 5.5 V DD AV =3.6Vto5.5V 110 160 DD V H=AV andV L= Normalmode GINND,atmDidD-scalecINode(6) AVDD=2.7Vto3.6V 95 150 μA AV =2Vto2.7V 80 140 DD I DD AV =3.6Vto5.5V 0.5 3.5 DD Allpower-down V H=AV andV L= mode GINND,atmDidD-scalecINode(6) AVDD=2.7Vto3.6V 0.4 3.0 μA AV =2Vto2.7V 0.1 2.0 DD AV =3.6Vto5.5V 0.55 0.88 DD V H=AV andV L= Normalmode GINND,atmDidD-scalecINode(6) AVDD=2.7Vto3.6V 0.25 0.54 mW Power AVDD=2Vto2.7V 0.14 0.38 dissipation AV =3.6Vto5.5V 2.50 19.2 DD Allpower-down V H=AV andV L= mode GINND,atmDidD-scalecINode(6) AVDD=2.7Vto3.6V 1.08 10.8 μW AV =2Vto2.7V 0.72 8.1 DD (6) Formoredetails,seeFigure14andFigure55. 6 SubmitDocumentationFeedback Copyright©2008–2015,TexasInstrumentsIncorporated ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 www.ti.com SBAS439C–AUGUST2008–REVISEDJULY2015 7.6 Timing Requirements: 14-Bit Allspecificationsat–40°Cto125°C,andAV =2Vto5.5V,unlessotherwisenoted.(1) (2) DD PARAMETER TESTCONDITIONS MIN TYP MAX UNIT AV =2.0Vto3.6V 20 DD f Serialclockfrequency MHz (SCLK) AV =3.6Vto5.5V 50 DD AV =2Vto3.6V 50 DD t SCLKcycletime ns 1 AV =3.6Vto5.5V 20 DD AV =2Vto3.6V 25 DD t SCLKhightime ns 2 AV =3.6Vto5.5V 10 DD AV =2Vto3.6V 25 DD t SCLKlowtime ns 3 AV =3.6Vto5.5V 10 DD AV =2Vto3.6V 0 DD t SYNCtoSCLKrisingedgesetuptime ns 4 AV =3.6Vto5.5V 0 DD AV =2Vto3.6V 5 DD t Datasetuptime ns 5 AV =3.6Vto5.5V 5 DD AV =2Vto3.6V 4.5 DD t Dataholdtime ns 6 AV =3.6Vto5.5V 4.5 DD AV =2Vto3.6V 0 DD t SCLKfallingedgetoSYNCrisingedge ns 7 AV =3.6Vto5.5V 0 DD AV =2Vto3.6V 50 DD t MinimumSYNChightime ns 8 AV =3.6Vto5.5V 20 DD AV =2Vto3.6V 100 DD t 16thSCLKfallingedgetoSYNCfallingedge ns 9 AV =3.6Vto5.5V 100 DD SYNCrisingedgeto16thSCLKfallingedge AVDD=2Vto3.6V 15 t ns 10 (forsuccessfulSYNCinterrupt) AV =3.6Vto5.5V 15 DD (1) Allinputsignalsarespecifiedwitht =t =3ns(10%to90%ofAV )andtimedfromavoltagelevelof(V +V )/2. R F DD IL IH (2) SeeFigure1timingdiagram. 7.7 Timing Requirements: 16-Bit Allspecificationsat–40°Cto125°C,andAV =2Vto5.5V,unlessotherwisenoted.(1) (2) DD PARAMETER TESTCONDITIONS MIN TYP MAX UNIT AV =2.0Vto3.6V 20 DD f(SCLK) Serialclockfrequency MHz AV =3.6Vto5.5V 50 DD AV =2Vto3.6V 50 DD t SCLKcycletime ns 1 AV =3.6Vto5.5V 20 DD AV =2Vto3.6V 25 DD t SCLKhightime ns 2 AV =3.6Vto5.5V 10 DD AV =2Vto3.6V 25 DD t SCLKlowtime ns 3 AV =3.6Vto5.5V 10 DD AV =2Vto3.6V 0 DD t SYNCtoSCLKrisingedgesetuptime ns 4 AV =3.6Vto5.5V 0 DD AV =2Vto3.6V 5 DD t Datasetuptime ns 5 AV =3.6Vto5.5V 5 DD AV =2Vto3.6V 4.5 DD t Dataholdtime ns 6 AV =3.6Vto5.5V 4.5 DD AV =2Vto3.6V 0 DD t SCLKfallingedgetoSYNCrisingedge ns 7 AV =3.6Vto5.5V 0 DD (1) Allinputsignalsarespecifiedwitht =t =3ns(10%to90%ofAV )andtimedfromavoltagelevelof(V +V )/2. R F DD IL IH (2) SeeFigure2timingdiagram. Copyright©2008–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback 7 ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 SBAS439C–AUGUST2008–REVISEDJULY2015 www.ti.com Timing Requirements: 16-Bit (continued) Allspecificationsat–40°Cto125°C,andAV =2Vto5.5V,unlessotherwisenoted.(1)(2) DD PARAMETER TESTCONDITIONS MIN TYP MAX UNIT AV =2Vto3.6V 50 DD t MinimumSYNChightime ns 8 AV =3.6Vto5.5V 20 DD AV =2Vto3.6V 100 DD t 24thSCLKfallingedgetoSYNCfallingedge ns 9 AV =3.6Vto5.5V 100 DD SYNCrisingedgeto24thSCLKfallingedge AVDD=2Vto3.6V 15 t ns 10 (forsuccessfulSYNCinterrupt) AV =3.6Vto5.5V 15 DD t t 1 9 SCLK 1 16 t8 t t3 t2 t7 4 SYNC t t 10 6 t 5 D DB15 DB0 DB15 IN Figure1. SerialWriteOperation:14-Bit(DAC8311) t t 1 9 SCLK 1 24 t8 t t3 t2 t7 4 SYNC t t 10 6 t 5 D DB23 DB0 DB23 IN Figure2. SerialWriteOperation:16-Bit(DAC8411) 8 SubmitDocumentationFeedback Copyright©2008–2015,TexasInstrumentsIncorporated ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 www.ti.com SBAS439C–AUGUST2008–REVISEDJULY2015 7.8 Typical Characteristics 7.8.1 TypicalCharacteristics:AV =5V DD atT =25°C,AV =5V,andDACloadedwithmid-scalecode,unlessotherwisenoted. A DD 6 2 4 AVDD= 5V AVDD= 5V B) 2 B) 1 S S L 0 L 0 E ( -2 E ( L -4 L -1 -6 -2 1.0 0.2 B) 0.5 B) 0.1 S S E (L 0 E (L 0 DL -0.5 DL -0.1 -1.0 -0.2 0 8192 16384 24576 32768 40960 49152 57344 65536 0 2048 4096 6144 8192 10240 12288 14336 16384 Digital Input Code Digital Input Code Figure3. DAC841116-BitLinearityErrorandDifferential Figure4. DAC831114-BitLinearityErrorandDifferential LinearityErrorvsCode(–40°C) LinearityErrorvsCode(–40°C) 6 2 4 AVDD= 5V AVDD= 5V B) 2 B) 1 S S L 0 L 0 E ( -2 E ( L -4 L -1 -6 -2 1.0 0.2 B) 0.5 B) 0.1 S S E (L 0 E (L 0 DL -0.5 DL -0.1 -1.0 -0.2 0 8192 16384 24576 32768 40960 49152 57344 65536 0 2048 4096 6144 8192 10240 12288 14336 16384 Digital Input Code Digital Input Code Figure5. DAC841116-BitLinearityErrorandDifferential Figure6. DAC831114-BitLinearityErrorandDifferential LinearityErrorvsCode(25°C) LinearityErrorvsCode(25°C) 6 2 4 AVDD= 5V AVDD= 5V B) 2 B) 1 S S L 0 L 0 E ( -2 E ( L -4 L -1 -6 -2 1.0 0.2 DLE (LSB) -00..505 DLE (LSB) -00..101 -1.0 -0.2 0 8192 16384 24576 32768 40960 49152 57344 65536 0 2048 4096 6144 8192 10240 12288 14336 16384 Digital Input Code Digital Input Code Figure7. DAC841116-BitLinearityErrorandDifferential Figure8. DAC831114-BitLinearityErrorandDifferential LinearityErrorvsCode(125°C) LinearityErrorvsCode(125°C) Copyright©2008–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback 9 ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 SBAS439C–AUGUST2008–REVISEDJULY2015 www.ti.com Typical Characteristics: AV = 5 V (continued) DD atT =25°C,AV =5V,andDACloadedwithmid-scalecode,unlessotherwisenoted. A DD 0.4 5.5 AV = 5V DD 5.0 ode Error (mV) 00..32 utput Voltage (V) 44..50 C O o- g 3.5 Zer 0.1 nalo A 3.0 AV = 5V DD DAC Loaded with FFFFh 0 2.5 -40 -25 -10 5 20 35 50 65 80 95 110 125 0 2 4 6 8 10 Temperature (°C) I (mA) SOURCE Figure9.Zero-CodeErrorvsTemperature Figure10.SourceCurrentatPositiveRail 0.6 0.6 AVDD= 5V AVDD= 5V DAC Loaded with 0000h 0.4 V) Error (mV) 0.20 put Voltage ( 0.4 Offset -0.2 og Out 0.2 al n -0.4 A -0.6 0 -40 -25 -10 5 20 35 50 65 80 95 110 125 0 2 4 6 8 10 Temperature (°C) I (mA) SINK Figure11.OffsetErrorvsTemperature Figure12.SinkCurrentatNegativeRail 0.06 120 AVDD= 5V AVDD= 5.5V 0.04 A) mV) 0.02 mnt ( 100 ale Error ( 0 pply Curre c u ull-S -0.02 er-S 80 F w o -0.04 P -0.06 60 -40 -25 -10 5 20 35 50 65 80 95 110 125 0 8192 16384 24576 32768 40960 49152 57344 65536 Temperature (°C) Digital Input Code Figure13.Full-ScaleErrorvsTemperature Figure14.Power-SupplyCurrentvsDigitalInputCode 10 SubmitDocumentationFeedback Copyright©2008–2015,TexasInstrumentsIncorporated ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 www.ti.com SBAS439C–AUGUST2008–REVISEDJULY2015 Typical Characteristics: AV = 5 V (continued) DD atT =25°C,AV =5V,andDACloadedwithmid-scalecode,unlessotherwisenoted. A DD 140 1.6 AV = 5V AV = 5V DD DD A) my Current ( 113200 Current (mA) 10..28 ower-Suppl 110 Quiescent 0.4 P 100 0 -40 -25 -10 5 20 35 50 65 80 95 110 125 -40 -25 -10 5 20 35 50 65 80 95 110 125 Temperature (°C) Temperature (°C) Figure15.Power-SupplyCurrentvsTemperature Figure16.Power-DownCurrentvsTemperature 2000 50 SYNC Input (all other digital inputs = GND) AVDD= 5.5V 45 A) 40 m 1500 nt ( Sweep from 35 upply Curre 1000 Sweep from 0V to 5.5V Occurrences 322050 S er- 5.5V to 0V 15 ow 500 10 P 5 0 0 0 4 8 2 6 0 4 8 2 6 0 4 8 2 6 0 0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 8 8 8 9 9 10 10 10 11 11 12 12 12 13 13 14 VLOGIC(V) IDD(mA) Figure17.Power-SupplyCurrentvsLogicInputVoltage Figure18.Power-SupplyCurrentHistogram -40 94 AVDD= 5V, fS= 225kSPS, THD AVDD= 5V, -50 -M1edaBs uFrSeRm eDnigt iBtaaln Idnwpuidt,th = 20kHz 92 f-S1=d B2 2F5SkRS PDSig,ital Input, Measurement Bandwidth = 20kHz -60 D (dB) -70 2nd Harmonic R (dB) 90 H N T S 88 -80 3rd Harmonic -90 86 -100 84 0 1 2 3 4 5 0 1 2 3 4 5 f (kHz) f (kHz) OUT OUT Figure19.TotalHarmonicDistortionvsOutputFrequency Figure20.Signal-to-NoiseRatiovsOutputFrequency Copyright©2008–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback 11 ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 SBAS439C–AUGUST2008–REVISEDJULY2015 www.ti.com Typical Characteristics: AV = 5 V (continued) DD atT =25°C,AV =5V,andDACloadedwithmid-scalecode,unlessotherwisenoted. A DD 0 AV = 5V, DD 20 fOUT= 1kHz, fS= 225kSPS, Measurement Bandwidth = 20kHz -40 v) di n (dB) -60 m500V/ ai -80 ( G UT O -100 V -120 AV = 5V DD Clock Feedthrough Impulse ~0.5nV-s -140 0 5 10 15 20 Time (500ns/div) Frequency (kHz) Figure21.PowerSpectralDensity Figure22.ClockFeedthrough5V,2mHz,Midscale AV = 5V AV = 5V DD DD From Code: 7FFFh From Code: 8000h v) To Code: 8000h v) To Code: 7FFFh di di V/ V/ m m 0 0 0 0 1 1 ( ( UT UT O O V V Clock Clock Feedthrough Glitch Impulse Feedthrough Glitch Impulse ~0.5nV-s < 0.5nV-s ~0.5nV-s < 0.5nV-s Time (5ms/div) Time (5ms/div) Figure23.GlitchEnergy5V,16-Bit,1LSBStep,Rising Figure24.GlitchEnergy5V,16-Bit,1LSBStep,Falling Edge Edge AV = 5V DD From Code: 2001h v) v) To Code: 2000h di di V/ V/ m m 0 0 0 0 1 1 ( ( UT Glitch Impulse UT VO < 0.5nV-s VO Clock Clock Feedthrough Feedthrough AVDD= 5V ~0.5nV-s ~0.5nV-s From Code: 2000h Glitch Impulse To Code: 2001h < 0.5nV-s Time (5ms/div) Time (5ms/div) Figure25.GlitchEnergy5V,14-Bit,1LSBStep,Rising Figure26.GlitchEnergy5V,14-Bit,1LSBStep,Falling Edge Edge 12 SubmitDocumentationFeedback Copyright©2008–2015,TexasInstrumentsIncorporated ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 www.ti.com SBAS439C–AUGUST2008–REVISEDJULY2015 Typical Characteristics: AV = 5 V (continued) DD atT =25°C,AV =5V,andDACloadedwithmid-scalecode,unlessotherwisenoted. A DD AV = 5V AV = 5V DD DD From Code: 0000h From Code: FFFFh To Code: FFFFh To Code: 0000h Rising Edge 1V/div Zoomed Rising Edge Falling Edge Zoomed Falling Edge 100mV/div 1V/div 100mV/div Trigger Pulse 5V/div Trigger Pulse 5V/div Time (2ms/div) Time (2ms/div) Figure27.Full-ScaleSettlingTime5-VRisingEdge Figure28.Full-ScaleSettlingTime5-VFallingEdge Falling AV = 5V DD Edge From Code: C000h 1V/div To Code: 4000h Rising Edge Zoomed Rising Edge Zoomed Falling Edge 1V/div 100mV/div 100mV/div Trigger AVDD= 5V Trigger Pulse From Code: 4000h Pulse 5V/div To Code: C000h 5V/div Time (2ms/div) Time (2ms/div) Figure29.Half-ScaleSettlingTime5-VRisingEdge Figure30.Half-ScaleSettlingTime5-VFallingEdge AV = 5V v) v) DAC = ZerDoD Scale V/di V/di Load = 200pF || 10kW 2 2 ( ( D D D D V V A AV = 5V A DD DAC = Zero Scale Load = 200pF || 10kW v) 17mV v) di di V/ V/ m m 0 0 2 2 ( ( UT UT O O V V Time (5ms/div) Time (10ms/div) Figure31.Power-OnResetto0VPower-OnGlitch Figure32.Power-OffGlitch Copyright©2008–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback 13 ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 SBAS439C–AUGUST2008–REVISEDJULY2015 www.ti.com Typical Characteristics: AV = 5 V (continued) DD atT =25°C,AV =5V,andDACloadedwithmid-scalecode,unlessotherwisenoted. A DD 300 AVDD= 5V DAVADCD == M5Vid,scale, No Load 250 Ö)Hz 200 V/div) e (nV/ 150 Midscale (1mSE Nois 100 VNOI 3mV Full Scale Zero Scale PP 50 0 10 100 1k 10k 100k Time (2s/div) Frequency (Hz) Figure33.DACOutputNoiseDensityvsFrequency Figure34.DACOutputNoise0.1Hzto10HzBandwidth 120 0.4 AV = 2.0V to 5.5V AV = 2.0V to 5.5V DD DD A) 110 y Current (m 100 Current (A)m 00..32 ower-Suppl 9800 Quiescent 0.1 P 70 0 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 AV (V) AV (V) DD DD Figure35.Power-SupplyCurrentvsPower-SupplyVoltage Figure36.Power-DownCurrentvsPower-SupplyVoltage 14 SubmitDocumentationFeedback Copyright©2008–2015,TexasInstrumentsIncorporated ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 www.ti.com SBAS439C–AUGUST2008–REVISEDJULY2015 7.8.2 TypicalCharacteristics:AV =3.6V DD atT =25°C,andAV =3.6V,unlessotherwisenoted. A DD 100 140 AVDD= 3.6V AVDD= 3.6V 130 A) 90 A) m m nt ( nt ( 120 e e urr 80 urr C C y y 110 pl pl up 70 up er-S er-S 100 w w Po 60 Po 90 50 80 0 8192 16384 24576 32768 40960 49152 57344 65536 -40 -25 -10 5 20 35 50 65 80 95 110 125 Digital Input Code Temperature (°C) Figure37.Power-SupplyCurrentvsDigitalInputCode Figure38.Power-SupplyCurrentvsTemperature 1200 1.2 SYNC Input (all other digital inputs = GND) AV = 3.6V DD A) m 900 A) Current ( S0Vw etoe p3 .f6roVm urrent (m 0.8 y 600 C ower-Suppl 300 Quiescent 0.4 P Sweep from 3.6V to 0V 0 0 0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 -40 -25 -10 5 20 35 50 65 80 95 110 125 VLOGIC(V) Temperature (°C) Figure39.Power-SupplyCurrentvsLogicInputVoltage Figure40.Power-DownCurrentvsTemperature 3.7 0.6 AV = 3.6V DD DAC Loaded with 0000h 3.5 V) V) e ( e ( ag 3.3 ag 0.4 olt olt V V ut 3.1 ut p p ut ut O O g 2.9 g 0.2 o o al al n n A 2.7 A AV = 3.6V DD DAC Loaded with FFFFh 2.5 0 0 2 4 6 8 10 0 2 4 6 8 10 I (mA) I (mA) SOURCE SINK Figure41.SourceCurrentatPositiveRail Figure42.SinkCurrentatNegativeRail Copyright©2008–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback 15 ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 SBAS439C–AUGUST2008–REVISEDJULY2015 www.ti.com Typical Characteristics: AV = 3.6 V (continued) DD atT =25°C,andAV =3.6V,unlessotherwisenoted. A DD 50 AV = 3.6V DD 45 40 35 s e 30 c n urre 25 cc 20 O 15 10 5 0 0 4 8 2 6 0 4 8 2 6 0 4 8 2 6 0 7 7 7 8 8 9 9 9 0 0 1 1 1 2 2 3 1 1 1 1 1 1 1 1 I (mA) DD Figure43.Power-SupplyCurrentHistogram 7.8.3 TypicalCharacteristics:AV =2.7V DD atT =25°C,andAV =2.7V,unlessotherwisenoted. A DD 6 2 4 AVDD= 2.7V AVDD= 2.7V B) 2 B) 1 S S L 0 L 0 LE ( -2 LE ( -1 -4 -6 -2 1.0 0.2 B) 0.5 B) 0.1 S S E (L 0 E (L 0 DL -0.5 DL -0.1 -1.0 -0.2 0 8192 16384 24576 32768 40960 49152 57344 65536 0 2048 4096 6144 8192 10240 12288 14336 16384 Digital Input Code Digital Input Code Figure44. DAC841116-BitLinearityErrorandDifferential Figure45. DAC831114-BitLinearityErrorandDifferential LinearityErrorvsCode(–40°C) LinearityErrorvsCode(–40°C) 16 SubmitDocumentationFeedback Copyright©2008–2015,TexasInstrumentsIncorporated ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 www.ti.com SBAS439C–AUGUST2008–REVISEDJULY2015 Typical Characteristics: AV = 2.7 V (continued) DD atT =25°C,andAV =2.7V,unlessotherwisenoted. A DD 6 2 4 AVDD= 2.7V AVDD= 2.7V B) 2 B) 1 S S L 0 L 0 LE ( -2 LE ( -1 -4 -6 -2 1.0 0.2 B) 0.5 B) 0.1 S S E (L 0 E (L 0 DL -0.5 DL -0.1 -1.0 -0.2 0 8192 16384 24576 32768 40960 49152 57344 65536 0 2048 4096 6144 8192 10240 12288 14336 16384 Digital Input Code Digital Input Code Figure46. DAC841116-BitLinearityErrorandDifferential Figure47. DAC831114-BitLinearityErrorandDifferential LinearityErrorvsCode(25°C) LinearityErrorvsCode(25°C) 6 2 4 AVDD= 2.7V AVDD= 2.7V B) 2 B) 1 S S L 0 L 0 LE ( -2 LE ( -1 -4 -6 -2 1.0 0.2 B) 0.5 B) 0.1 S S E (L 0 E (L 0 DL -0.5 DL -0.1 -1.0 -0.2 0 8192 16384 24576 32768 40960 49152 57344 65536 0 2048 4096 6144 8192 10240 12288 14336 16384 Digital Input Code Digital Input Code Figure48. DAC841116-BitLinearityErrorandDifferential Figure49. DAC831114-BitLinearityErrorandDifferential LinearityErrorvsCode(125°C) LinearityErrorvsCode(125°C) 0.4 2.8 AV = 2.7V DD mV) 0.3 ge (V) 2.6 ode Error ( 0.2 utput Volta 2.4 C O o- g Zer 0.1 nalo 2.2 A AV = 2.7V DD DAC Loaded with FFFFh 0 2.0 -40 -25 -10 5 20 35 50 65 80 95 110 125 0 2 4 6 8 10 Temperature (°C) I (mA) SOURCE Figure50.Zero-CodeErrorvsTemperature Figure51.SourceCurrentatPositiveRail Copyright©2008–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback 17 ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 SBAS439C–AUGUST2008–REVISEDJULY2015 www.ti.com Typical Characteristics: AV = 2.7 V (continued) DD atT =25°C,andAV =2.7V,unlessotherwisenoted. A DD 0.6 0.6 AVDD= 2.7V AVDD= 2.7V DAC Loaded with 0000h 0.4 V) Error (mV) 0.20 put Voltage ( 0.4 Offset -0.2 og Out 0.2 al n -0.4 A -0.6 0 -40 -25 -10 5 20 35 50 65 80 95 110 125 0 2 4 6 8 10 Temperature (°C) I (mA) SINK Figure52.OffsetErrorvsTemperature Figure53.SinkCurrentatNegativeRail 0.06 100 AVDD= 2.7V AVDD= 2.7V 0.04 A) 90 mV) 0.02 mnt ( cale Error ( 0 upply Curre 8700 ull-S -0.02 er-S F w -0.04 Po 60 -0.06 50 -40 -25 -10 5 20 35 50 65 80 95 110 125 0 8192 16384 24576 32768 40960 49152 57344 65536 Temperature (°C) Digital Input Code Figure54.Full-ScaleErrorvsTemperature Figure55.Power-SupplyCurrentvsDigitalInputCode 120 1.0 AV = 2.7V AV = 2.7V DD DD A) 110 0.8 mCurrent ( 100 urrent (mA) 0.6 y C Power-Suppl 9800 Quiescent 00..42 70 0 -40 -25 -10 5 20 35 50 65 80 95 110 125 -40 -25 -10 5 20 35 50 65 80 95 110 125 Temperature (°C) Temperature (°C) Figure56.Power-SupplyCurrentvsTemperature Figure57.Power-DownCurrentvsTemperature 18 SubmitDocumentationFeedback Copyright©2008–2015,TexasInstrumentsIncorporated ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 www.ti.com SBAS439C–AUGUST2008–REVISEDJULY2015 Typical Characteristics: AV = 2.7 V (continued) DD atT =25°C,andAV =2.7V,unlessotherwisenoted. A DD 800 50 SYNC Input (all other digital inputs = GND) AVDD= 2.7V 45 A) 40 m 600 nt ( 35 ply Curre 400 S0Vw etoe p2 .f7roVm urrences 3205 er-Sup S2.w7eVe tpo f0roVm Occ 2105 w 200 o 10 P 5 0 0 0 0.5 1.0 1.5 2.0 2.5 3.0 60 64 68 72 76 80 84 88 92 96 00 04 1 1 VLOGIC(V) IDD(mA) Figure58.Power-SupplyCurrentvsLogicInputVoltage Figure59.Power-SupplyCurrentHistogram -20 88 AV = 2.7V, f = 225kSPS, AV = 2.7V, f = 225kSPS, DD S DD S -1dB FSR Digital Input, -1dB FSR Digital Input, Measurement Bandwidth = 20kHz Measurement Bandwidth = 20kHz -40 THD 86 B) B) D (d -60 R (d 84 H N T S 2nd Harmonic -80 82 3rd Harmonic -100 80 0 1 2 3 4 5 0 1 2 3 4 5 f (kHz) f (kHz) OUT OUT Figure60.TotalHarmonicDistortionvsOutputFrequency Figure61.Signal-to-NoiseRatiovsOutputFrequency 0 AV = 2.7V, DD 20 fOUT= 1kHz, fS= 225kSPS, Measurement Bandwidth = 20kHz -40 v) di n (dB) -60 m500V/ ai -80 ( G UT O -100 V -120 AV = 2.7V DD Clock Feedthrough Impulse ~0.4nV-s -140 0 5 10 15 20 Time (5ms/div) Frequency (kHz) Figure62.PowerSpectralDensity Figure63.ClockFeedthrough2.7V,20mHz,Midscale Copyright©2008–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback 19 ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 SBAS439C–AUGUST2008–REVISEDJULY2015 www.ti.com Typical Characteristics: AV = 2.7 V (continued) DD atT =25°C,andAV =2.7V,unlessotherwisenoted. A DD AV = 2.7V AV = 2.7V DD DD From Code: 7FFFh From Code: 8000h To Code: 8000h To Code: 7FFFh v) v) di di V/ V/ m m 0 0 0 0 1 1 ( ( UT Glitch Impulse UT VO Clock < 0.3nV-s VO Clock Glitch Impulse Feedthrough Feedthrough < 0.3nV-s ~0.4nV-s ~0.4nV-s Time (5ms/div) Time (5ms/div) Figure64.GlitchEnergy2.7V,16-Bit,1LSBStep,Rising Figure65.GlitchEnergy2.7V,16-Bit,1LSBStep,Falling Edge Edge AV = 2.7V AV = 2.7V DD DD From Code: 2000h From Code: 2001h To Code: 2001h To Code: 2000h v) v) di di V/ V/ m m 0 0 0 0 1 1 ( ( UT Glitch Impulse UT VO < 0.3nV-s VO Clock Clock Feedthrough Glitch Impulse Feedthrough ~0.4nV-s < 0.3nV-s ~0.4nV-s Time (5ms/div) Time (5ms/div) Figure66.GlitchEnergy2.7V,14-Bit,1LSBStep,Rising Figure67.GlitchEnergy2.7V,14-Bit,1LSBStep,Falling Edge Edge AV = 2.7V AV = 2.7V DD DD From Code: 0000h From Code: FFFFh To Code: FFFFh To Code: 0000h Falling Edge Rising Edge 1V/div 1V/div Zoomed Rising Edge Zoomed Falling Edge 100mV/div 100mV/div Trigger Pulse 2.7V/div Trigger Pulse 2.7V/div Time (2ms/div) Time (2ms/div) Figure68.Full-ScaleSettlingTime2.7VRisingEdge Figure69.Full-ScaleSettlingTime2.7VFallingEdge 20 SubmitDocumentationFeedback Copyright©2008–2015,TexasInstrumentsIncorporated ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 www.ti.com SBAS439C–AUGUST2008–REVISEDJULY2015 Typical Characteristics: AV = 2.7 V (continued) DD atT =25°C,andAV =2.7V,unlessotherwisenoted. A DD AV = 2.7V AV = 2.7V DD DD From Code: 4000h From Code: C000h To Code: C000h To Code: 4000h Falling Edge Rising 1V/div Edge 1V/div Zoomed Rising Edge Trigger 100mV/div Pulse Trigger 2.7V/div Zoomed Falling Edge Pulse 100mV/div 2.7V/div Time (2ms/div) Time (2ms/div) Figure70.Half-ScaleSettlingTime2.7VRisingEdge Figure71.Half-ScaleSettlingTime2.7VFallingEdge AV = 2.7V v) v) DAC = ZDeDro Scale V/di V/di Load = 200pF || 10kW 1 1 ( ( D D D D V V A AV = 2.7V A DD DAC = Zero Scale Load = 200pF || 10kW v) 17mV v) di di V/ V/ m m 0 0 2 2 ( ( UT UT O O V V Time (5ms/div) Time (10ms/div) Figure72.Power-OnResetto0-VPower-OnGlitch Figure73.Power-OffGlitch Copyright©2008–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback 21 ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 SBAS439C–AUGUST2008–REVISEDJULY2015 www.ti.com 8 Detailed Description 8.1 Overview The DAC8x11 family of devices are low-power, single-channel, voltage output DACs. These devices are monotonic by design, provide excellent linearity, and minimize undesired code-to-code transient voltages while offering an easy upgrade path within a pin-compatible family. All devices use a versatile, 3-wire serial interface that operates at clock rates of up to 50 MHz and is compatible with standard SPI, QSPI, Microwire, and digital signalprocessor(DSP)interfaces. 8.2 Functional Block Diagram AV GND DD Power-On Reset REF(+) ReDgAisCter 14-/16-Bit DAC OBuutfpfeurt VOUT Input Control Power-Down Logic Control Logic Resistor Network SYNC SCLK D IN 8.3 Feature Description 8.3.1 DACSection The DAC8311 and DAC8411 are fabricated using Texas Instruments' proprietary HPA07 process technology. The architecture consists of a string DAC followed by an output buffer amplifier. Because there is no reference input pin, the power supply (AV ) acts as the reference. Figure 74 shows a block diagram of the DAC DD architecture. AV DD REF (+) DAC Register Resistor String V OUT Output Amplifier GND Figure74. DAC8x11Architecture TheinputcodingtotheDAC8311andDAC8411isstraightbinary,sotheidealoutputvoltageisgivenby: D V = AV ´ OUT DD 2n where • n=resolutioninbits;either14(DAC8311)or16(DAC8411). • D=decimalequivalentofthebinarycodethatisloadedtotheDACregister;itrangesfrom0to16,383forthe 14-bitDAC8311,or0to65,535forthe16-bitDAC8411. 22 SubmitDocumentationFeedback Copyright©2008–2015,TexasInstrumentsIncorporated ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 www.ti.com SBAS439C–AUGUST2008–REVISEDJULY2015 Feature Description (continued) 8.3.2 ResistorString The resistor string section is shown in Figure 75. It is simply a string of resistors, each of value R. The code loaded into the DAC register determines at which node on the string the voltage is tapped off to be fed into the output amplifier by closing one of the switches connecting the string to the amplifier. The resistor string architectureisinherentlymonotonic. V REF R DIVIDER V REF 2 R To Output R Amplifier R R Figure75. ResistorString 8.3.3 OutputAmplifier The output buffer amplifier is capable of generating rail-to-rail voltages on its output which gives an output range of 0V to AV . The output amplifier is capable of driving a load of 2 kΩ in parallel with 1000 pF to GND. The DD source and sink capabilities of the output amplifier can be seen in the Typical Characteristics section for each device.Theslewrateis0.7V/μswithahalf-scalesettlingtimeoftypically6 μswiththeoutputunloaded. 8.3.4 Power-OnResettoZero-Scale The DAC8x11 contains a power-on reset circuit that controls the output voltage during power up. On power up, theDACregisterisfilledwithzerosandtheoutputvoltageis0V.TheDACregisterremainsthatwayuntilavalid write sequence is made to the DAC. This design is useful in applications where it is important to know the state oftheoutputoftheDACwhileitisintheprocessofpoweringup. The occurring power-on glitch impulse is only a few mV (typically, 17 mV; see Figure 31, Figure 72, or Figure31). Copyright©2008–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback 23 ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 SBAS439C–AUGUST2008–REVISEDJULY2015 www.ti.com 8.4 Device Functional Modes 8.4.1 Power-DownModes The DAC8x11 contains four separate modes of operation. These modes are programmable by setting two bits (PD1 and PD0) in the control register. Table 3 shows how the state of the bits corresponds to the mode of operationofthedevice. Table3.ModesofOperationfortheDAC8x11 PD1 PD0 OPERATINGMODE NORMALMODE 0 0 NormalOperation POWER-DOWNMODES 0 1 Output1kΩtoGND 1 0 Output100kΩtoGND 1 1 High-Z Whenbothbitsaresetto0,thedeviceworksnormallywithastandardpowerconsumptionoftypically80 μAat2 V. However, for the three power-down modes, the typical supply current falls to 0.5 μA at 5 V, 0.4 μA at 3 V, and 0.1 μA at 2.0 V. Not only does the supply current fall, but the output stage is also internally switched from the output of the amplifier to a resistor network of known values. The advantage of this architecture is that the output impedance of the part is known while the part is in power-down mode. There are three different options. The output is connected internally to GND either through a 1-kΩ resistor or a 100-kΩ resistor, or is left open-circuited (High-Z).SeeFigure76fortheoutputstage. Amplifier Resistor V String DAC OUT Power-down Resistor Circuitry Network Figure76. OutputStageDuringPower-Down All linear circuitry is shut down when the power-down mode is activated. However, the contents of the DAC register are unaffected when in power-down. The time to exit power-down is typically 50 μs for AV = 5 V and DD AV =3V.SeetheTypicalCharacteristics:AV =5Vforeachdeviceformoreinformation. DD DD 24 SubmitDocumentationFeedback Copyright©2008–2015,TexasInstrumentsIncorporated ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 www.ti.com SBAS439C–AUGUST2008–REVISEDJULY2015 8.5 Programming 8.5.1 DAC8311SerialInterface The DAC8311 has a 3-wire serial interface (SYNC, SCLK, and DIN) compatible with SPI, QSPI, and Microwire interfacestandards,aswellasmostDSPs.SeeFigure1 foranexampleofatypicalwritesequence. 8.5.1.1 DAC8311InputShiftRegister The input shift register is 16 bits wide, as shown in Figure 77. The first two bits (PD0 and PD1) are reserved control bits that set the desired mode of operation (normal mode or any one of three power-down modes) as indicatedinTable3. The write sequence begins by bringing the SYNC line low. Data from the DIN line are clocked into the 16-bit shift register on each falling edge of SCLK. The serial clock frequency can be as high as 50 MHz, making the DAC8311 compatible with high-speed DSPs. On the 16th falling edge of the serial clock, the last data bit is clockedinandtheprogrammedfunctionisexecuted. At this point, the SYNC line may be kept low or brought high. In either case, it must be brought high for a minimum of 20 ns before the next write sequence so that a falling edge of SYNC can initiate the next write sequence. 8.5.1.2 DAC8311SYNCInterrupt In a normal write sequence, the SYNC line is kept low for at least 16 falling edges of SCLK and the DAC is updated on the 16th falling edge. However, bringing SYNC high before the 16th falling edge acts as an interrupt to the write sequence. The shift register is reset and the write sequence is seen as invalid. Neither an update of theDACregistercontentsorachangeintheoperatingmodeoccurs,asshowninFigure78. Figure77. DAC8311DataInputRegister DB15 DB14 DB0 PD1 PD0 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset CLK SYNC DIN DB15 DB0 DB15 DB0 Invalid Write Sequence: Valid Write Sequence: SYNCHIGH before 16th Falling Edge Output Updates on 16th Falling Edge Figure78. DAC8311SYNCInterruptFacility 8.5.2 DAC8411SerialInterface The DAC8411 has a 3-wire serial interface (SYNC, SCLK, and DIN) compatible with SPI, QSPI, and Microwire interfacestandards,aswellasmostDSPs.SeetheFigure1 foranexampleofatypicalwritesequence. 8.5.2.1 DAC8411InputShiftRegister The input shift register is 24 bits wide, as shown in Figure 79. The first two bits are reserved control bits (PD0 and PD1) that set the desired mode of operation (normal mode or any one of three power-down modes) as indicatedinTable3.Thelastsixbitsare don'tcare. The write sequence begins by bringing the SYNC line low. Data from the DIN line are clocked into the 24-bit shift register on each falling edge of SCLK. The serial clock frequency can be as high as 50 MHz, making the DAC8411 compatible with high-speed DSPs. On the 18th falling edge of the serial clock, the last data bit is clockedinandtheprogrammedfunctionisexecuted.Thelastsixbitsare don'tcare. Copyright©2008–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback 25 ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 SBAS439C–AUGUST2008–REVISEDJULY2015 www.ti.com At this point, the SYNC line may be kept low or brought high. In either case, it must be brought high for a minimum of 20 ns before the next write sequence so that a falling edge of SYNC can initiate the next write sequence.Aspreviouslymentioned,itmustbebroughthighagainbeforethenextwritesequence. TheSYNClinemaybebroughthighafterthe18thbitisclockedinbecausethelastsixbitsare don'tcare. 8.5.2.2 DAC8411SYNCInterrupt In a normal write sequence, the SYNC line is kept low for 24 falling edges of SCLK and the DAC is updated on the 18th falling edge, ignoring the last six don't care bits. However, bringing SYNC high before the 18th falling edge acts as an interrupt to the write sequence. The shift register is reset and the write sequence is seen as invalid. Neither an update of the DAC register contents or a change in the operating mode occurs, as shown in Figure80. Figure79. DAC8411DataInputRegister DB23 PD1 PD0 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 DB7 DB6 DB5 D1 D0 X X X X X X LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset 18th Falling Edge 18th/24th Falling Edge CLK 18 24 18 24 SYNC DIN DB23 DB6 DB5 DB0 DB23 DB6 DB5 DB0 Invalid/Interrupted Write Sequence: Valid Write Sequence: Output/Mode Does Not Updateon the 18th Falling Edge Output/Mode Updateson the 18th or 24th Falling Edge Figure80. DAC8411SYNCInterruptFacility 26 SubmitDocumentationFeedback Copyright©2008–2015,TexasInstrumentsIncorporated ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 www.ti.com SBAS439C–AUGUST2008–REVISEDJULY2015 9 Application and Implementation NOTE Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validateandtesttheirdesignimplementationtoconfirmsystemfunctionality. 9.1 Application Information 9.1.1 MicroprocessorInterfacing 9.1.1.1 DAC8x11to8051Interface Figure 81 shows a serial interface between the DAC8x11 and a typical 8051-type microcontroller. The setup for theinterfaceisasfollows:TXDofthe8051drivesSCLKoftheDAC8x11,whileRXDdrivestheserialdatalineof thepart.TheSYNCsignalisderivedfromabitprogrammablepinontheport.Inthiscase,portlineP3.3isused. When data are to be transmitted to the DAC8x11, P3.3 is taken low. The 8051 transmits data only in 8-bit bytes; thus, only eight falling clock edges occur in the transmit cycle. To load data to the DAC, P3.3 remains low after the first eight bits are transmitted, and a second write cycle is initiated to transmit the second byte of data. P3.3 is taken high following the completion of this cycle. The 8051 outputs the serial data in a format which has the LSB first. The DAC8x11 requires its data with the MSB as the first bit received. Therefore, the 8051 transmit routinemusttakethisrequirementintoaccount,and mirrorthedataasneeded. 80C51/80L51(1) DAC8x11(1) P3.3 SYNC TXD SCLK RXD DIN NOTE: (1) Additional pins omitted for clarity. Figure81. DAC8x11to80C51/80l51Interfaces 9.1.1.2 DAC8x11toMicrowireInterface Figure 82 shows an interface between the DAC8x11 and any Microwire-compatible device. Serial data are shifted out on the falling edge of the serial clock and are clocked into the DAC8x11 on the rising edge of the SK signal. Microwire DAC8x11(1) CS SYNC SK SCLK SO D IN NOTE:(1)Additionalpinsomittedforclarity. Figure82. DAC8x11toMicrowireInterface Copyright©2008–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback 27 ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 SBAS439C–AUGUST2008–REVISEDJULY2015 www.ti.com Application Information (continued) 9.1.1.3 DAC8x11to68HC11Interface Figure 83 shows a serial interface between the DAC8x11 and the 68HC11 microcontroller. SCK of the 68HC11 drives the SCLK of the DAC8x11, while the MOSI output drives the serial data line of the DAC. The SYNC signal isderivedfromaportline(PC7),similartowhatwasdoneforthe8051. 68HC11(1) DAC8x11(1) PC7 SYNC SCK SCLK MOSI D IN NOTE: (1) Additional pins omitted for clarity. Figure83. DAC8X11to68HC11Interface The68HC11shouldbeconfiguredsothatitsCPOLbitisa'0'anditsCPHAbitisa'1'.Thisconfigurationcauses data appearing on the MOSI output to be valid on the falling edge of SCK. When data are being transmitted to the DAC, the SYNC line is taken low (PC7). Serial data from the 68HC11 are transmitted in 8-bit bytes with only eight falling clock edges occurring in the transmit cycle. Data are transmitted MSB first. In order to load data to the DAC8x11, PC7 is held low after the first eight bits are transferred, and a second serial write operation is performedtotheDAC;PC7istakenhighattheendofthisprocedure. 9.2 Typical Applications 9.2.1 LoopPoweredTransmitter Thedescribedlooppoweredtransmittercanaccuratelysourcecurrentsfrom4mAto20mA. V REG Regulator V+ R5 122.15 kΩ V /V REG REF R 2 + 30.542 kΩ U1 Q1 OPA317 R 60.4Ω 6 4.32 kΩ R R 26.7Ω 3 4 Return Figure84. LoopPoweredTransmitterSchematic 9.2.1.1 DesignRequirements The transmitter has only two external input terminals; a supply connection and a ground (or return) connection. The transmitter communicates back to the host, typically a PLC analog input module, by precisely controlling the magnitude of the return current. In order to conform to the 4-mA to 20-mA communication standards, the completetransmittermustconsumelessthan4mAofcurrent. 28 SubmitDocumentationFeedback Copyright©2008–2015,TexasInstrumentsIncorporated ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 www.ti.com SBAS439C–AUGUST2008–REVISEDJULY2015 Typical Applications (continued) The complete design of this circuit is outlined in TIPD158, Low Cost Loop-Powered 4-20mA Transmitter EMC/EMI Tested Reference Design. The design is expected to be low-cost and deliver immunity to the IEC61000-4 suite of tests with minimum impact on the accuracy of the system. Reference design TIPD158 includesthedesigngoals,simulatedresults,andmeasuredperformance. 9.2.1.2 DetailedDesignProcedure Amplifier U1 uses negative feedback to make sure that the potentials at the inverting (V–) and noninverting (V+) input terminals are equal. In this configuration, V– is directly tied to the local GND; therefore, the potential at the noninverting input terminal is driven to local ground. Thus, the voltage difference across R is the DAC output 2 voltage (VOUT), and the voltage difference across R is the regulator voltage (VREG). These voltage differences 5 causecurrentstoflowthroughR andR ,asillustratedinFigure85. 2 5 V REG Regulator V+ V /R REG 2 R 5 VREG/VREF R V+ 2 DAC V + OUT U1 Q1 V /R 0A DAC 1 iloop R V– 6 iq i1 R3R4 i2 iout Return Figure85. VoltagetoCurrentConversion ThecurrentsfromR andR sumintoi (definedinEquation1),andi flowsthroughR . 2 5 1 1 3 V V i DAC (cid:14) REG 1 R R 2 5 (1) Amplifier U2 drives the base of Q1, the NPN bipolar junction transistor (BJT), to allow current to flow through R 4 so that the voltage drops across R and R remain equal. This design keeps the inverting and noninverting 3 4 terminals at the same potential. A small part of the current through R is sourced by the quiescent current of all 4 of the components used in the transmitter design (regulator, amplifier, and DAC). The voltage drops across R 3 andR areequal;therefore,different-sizedresistorscausedifferentcurrentflowthrougheachresistor.Usethese 4 different-sizedresistorstoapplygaintothecurrentflowthroughR bycontrollingtheratioofresistorR toR ,as 4 3 4 showninEquation2: V(cid:14) i ˜R 1 3 i ˜R 9± L ˜5 Ÿ L 1 3 2 4 2 R 9(cid:14) 9± 4 (2) The current gain in the circuit helps allow a majority of the output current to come directly from the loop through Q1 instead of from the voltage-to-current converter. This current gain, in addition to the low-power components, keeps the current consumption of the voltage-to-current converter low. Currents i and i sum to form output 1 2 currenti ,asshowninEquation3: out V V R §V V · §V V · § R · i i (cid:14)i DAC (cid:14) REG (cid:14) 3 ˜¨ DAC (cid:14) REG¸ ¨ DAC (cid:14) REG¸˜¨1(cid:14) 3 ¸ out 1 2 R2 R5 R4 © R2 R5 ¹ © R2 R5 ¹ © R4¹ (3) Copyright©2008–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback 29 ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 SBAS439C–AUGUST2008–REVISEDJULY2015 www.ti.com Typical Applications (continued) The complete transfer function, arranged as a function of input code, is shown in Equation 4. The remaining sectionsdividethiscircuitintoblocksforsimplifieddiscussion. § V ˜Code V · § R · iout(cid:11)Code(cid:12) ¨¨©2RReEsoGlution ˜R2 (cid:14) RRE5G¸¸¹˜¨©1(cid:14) R34 ¸¹ (4) Resistor R is included to reduce the gain of transistor Q1, and therefore, reduce the closed-loop gain of the 6 voltage-to-currentconverterforastabledesign.SizeresistorsR ,R ,R ,andR basedonthefull-scalerangeof 2 3 4 5 theDAC,regulatorvoltage,andthedesiredcurrentoutputrangeofthedesign. 9.2.1.3 ApplicationCurves Figure 86 shows the measured transfer function of the circuit. Figure 87 shows the total unadjusted error (TUE) ofthecircuit,stayingbelow0.15%FSR. 20 0.20 0.15 16 R) 0.10 OutputCurrent(mA)128 OutputCurrentTUE(%FS--0000....10000505 -0.15 4 -0.20 0 1024 2048 3072 4096 0 1024 2048 3072 4096 DACCode DACCode Figure86.OutputCurrentvsCode Figure87.CurrentTotalUnadjustedErrorvsCode 9.2.2 UsingtheREF5050asaPowerSupplyfortheDAC8x11 As a result of the extremely low supply current required by the DAC8x11, an alternative option is to use a REF5050 5 V precision voltage reference to supply the required voltage to the part, as shown in Figure 88. This option is especially useful if the power supply is too noisy or if the system supply voltages are at some value other than 5 V. The REF5050 outputs a steady supply voltage for the DAC8x11. If the REF5050 is used, the current needed to supply DAC8x11 is typically 110 μA at 5V, with no load on the output of the DAC. When the DAC output is loaded, the REF5050 also needs to supply the current to the load. The total current required (with a5-kΩ loadontheDACoutput)is: 110μA+(5V/5kΩ)=1.11mA The load regulation of the REF5050 is typically 0.002%/mA, resulting in an error of 90 μV for the 1.1 -mA current drawnfromit.Thisvaluecorrespondstoa1.1LSBerrorat16bit(DAC8411). +5.5V +5V REF5050 1mF 110mA SYNC Three-Wire VOUT= 0V to 5V Serial SCLK DAC8x11 Interface D IN Figure88. REF5050asPowerSupplytoDAC8x11 30 SubmitDocumentationFeedback Copyright©2008–2015,TexasInstrumentsIncorporated ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 www.ti.com SBAS439C–AUGUST2008–REVISEDJULY2015 Typical Applications (continued) For other power-supply voltages, alternative references such as the REF3030 (3 V), REF3033 (3.3 V), or REF3220 (2.048 V) are recommended. For a full list of available voltage references from TI, see TI web site at www.ti.com. 9.2.3 BipolarOperationUsingtheDAC8x11 The DAC8x11 has been designed for single-supply operation but a bipolar output range is also possible using the circuit in Figure 89. The circuit shown gives an output voltage range of ±5V. Rail-to-rail operation at the amplifier output is achievable using an OPA211, OPA340, or OPA703 as the output amplifier. For a full list of availableoperationalamplifiersfromTI,seeTIwebsiteatwww.ti.com Theoutputvoltageforanyinputcodecanbecalculatedasfollows: é æ D ö æR +R ö æR öù VO = êêëAVDD´çè2n÷ø´çè 1R1 2÷ø-AVDD´çèR21÷øúúû where • n=resolutioninbits;either14(DAC8311)or16(DAC8411). • D=theinputcodeindecimal;either0to16,383(DAC8311)or0to65,535(DAC8411). (5) WithAV =5V,R =R =10kΩ: DD 1 2 VO(cid:3)(cid:4)102(cid:1)n D(cid:5)(cid:2)5V (6) The resulting output voltage range is ±5V. Code 000h corresponds to a –5-V output and FFFFh (16-bit level) correspondingtoa5-Voutput. +5V R2 10kW +5.5V R 1 10kW OPA211 VOUT ±5V AV DAC8x11 DD 10mF 0.1mF - 5.5V Three-Wire Serial Interface Figure89. BipolarOperationWiththeDAC8x11 10 Power Supply Recommendations The DAC8x11 is designed to operate with a unipolar analog power supply ranging from 2 V to 5.5 V on the AV DD pin. The AV pin supplies power to the digital and analog circuits (including the resistor string) inside the DAC. DD The current consumption of this pin is specified in the Electrical Characteristics table. Use a 1-μF to 10-μF capacitorinparallelwitha0.1-μFbypasscapacitoronthispintoremovehigh-frequencynoise. Copyright©2008–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback 31 ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 SBAS439C–AUGUST2008–REVISEDJULY2015 www.ti.com 11 Layout 11.1 Layout Guidelines A precision analog component requires careful layout, adequate bypassing, and clean, well-regulated power supplies. The DAC8x11 offers single-supply operation; it will often be used in close proximity with digital logic, microcontrollers, microprocessors, and digital signal processors. The more digital logic present in the design and thehighertheswitchingspeed,themoredifficultitwillbetoachievegoodperformancefromtheconverter. BecauseofthesinglegroundpinoftheDAC8x11,allreturncurrents,includingdigitalandanalogreturncurrents, must flow through the GND pin. Ideally, GND would be connected directly to an analog ground plane. This plane would be separate from the ground connection for the digital components until they were connected at the power entrypointofthesystem. The power applied to AV should be well-regulated and low-noise. Switching power supplies and dc/dc DD converters often have high-frequency glitches or spikes riding on the output voltage. In addition, digital components can create similar high-frequency spikes as the internal logic switches state. This noise can easily couple into the DAC output voltage through various paths between the power connections and analog output. ThisconditionisparticularlytruefortheDAC8x11,asthepowersupplyisalsothereferencevoltagefortheDAC. As with the GND connection, AV should be connected to a 5 V power supply plane or trace that is separate DD from the connection for digital logic until they are connected at the power entry point. In addition, TI strongly recommends the 1 μF to 1 μF and 0.1 μF bypass capacitors. In some situations, additional bypassing may be required, such as a 100 μF electrolytic capacitor or even a Pi filter made up of inductors and capacitors—all designedtoessentiallylow-passfilterthe5Vsupply,removingthehigh-frequencynoise. 11.2 Layout Example U1 Analog IO Bypass Digital IO Capacitors Figure90. RecommendedLayout 32 SubmitDocumentationFeedback Copyright©2008–2015,TexasInstrumentsIncorporated ProductFolderLinks:DAC8311 DAC8411

DAC8311,DAC8411 www.ti.com SBAS439C–AUGUST2008–REVISEDJULY2015 12 Device and Documentation Support 12.1 Related Links The table below lists quick access links. Categories include technical documents, support and community resources,toolsandsoftware,andquickaccesstosampleorbuy. Table4.RelatedLinks TECHNICAL TOOLS& SUPPORT& PARTS PRODUCTFOLDER SAMPLE&BUY DOCUMENTS SOFTWARE COMMUNITY DAC8311 Clickhere Clickhere Clickhere Clickhere Clickhere DAC8411 Clickhere Clickhere Clickhere Clickhere Clickhere 12.2 Community Resources The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use. TIE2E™OnlineCommunity TI'sEngineer-to-Engineer(E2E)Community.Createdtofostercollaboration amongengineers.Ate2e.ti.com,youcanaskquestions,shareknowledge,exploreideasandhelp solveproblemswithfellowengineers. DesignSupport TI'sDesignSupport QuicklyfindhelpfulE2Eforumsalongwithdesignsupporttoolsand contactinformationfortechnicalsupport. 12.3 Trademarks E2EisatrademarkofTexasInstruments. SPI,QSPIaretrademarksofMotorola,Inc. Allothertrademarksarethepropertyoftheirrespectiveowners. 12.4 Electrostatic Discharge Caution Thesedeviceshavelimitedbuilt-inESDprotection.Theleadsshouldbeshortedtogetherorthedeviceplacedinconductivefoam duringstorageorhandlingtopreventelectrostaticdamagetotheMOSgates. 12.5 Glossary SLYZ022—TIGlossary. Thisglossarylistsandexplainsterms,acronyms,anddefinitions. 13 Mechanical, Packaging, and Orderable Information The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of thisdocument.Forbrowser-basedversionsofthisdatasheet,refertotheleft-handnavigation. Copyright©2008–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback 33 ProductFolderLinks:DAC8311 DAC8411

PACKAGE OPTION ADDENDUM www.ti.com 6-Feb-2020 PACKAGING INFORMATION Orderable Device Status Package Type Package Pins Package Eco Plan Lead/Ball Finish MSL Peak Temp Op Temp (°C) Device Marking Samples (1) Drawing Qty (2) (6) (3) (4/5) DAC8311IDCKR ACTIVE SC70 DCK 6 3000 Green (RoHS NIPDAU Level-2-260C-UNLIM -40 to 125 D83 & no Sb/Br) DAC8311IDCKT ACTIVE SC70 DCK 6 250 Green (RoHS NIPDAU Level-2-260C-UNLIM -40 to 125 D83 & no Sb/Br) DAC8411IDCKR ACTIVE SC70 DCK 6 3000 Green (RoHS NIPDAU Level-2-260C-UNLIM -40 to 125 D84 & no Sb/Br) DAC8411IDCKT ACTIVE SC70 DCK 6 250 Green (RoHS NIPDAU Level-2-260C-UNLIM -40 to 125 D84 & no Sb/Br) DAC8411IDCKTG4 ACTIVE SC70 DCK 6 250 Green (RoHS NIPDAU Level-2-260C-UNLIM -40 to 125 D84 & no Sb/Br) (1) The marketing status values are defined as follows: ACTIVE: Product device recommended for new designs. LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect. NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design. PREVIEW: Device has been announced but is not in production. Samples may or may not be available. OBSOLETE: TI has discontinued the production of the device. (2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free". RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption. Green: TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement. (3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature. (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device. (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device. (6) Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width. Addendum-Page 1

PACKAGE OPTION ADDENDUM www.ti.com 6-Feb-2020 Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release. In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis. Addendum-Page 2

PACKAGE MATERIALS INFORMATION www.ti.com 29-Sep-2019 TAPE AND REEL INFORMATION *Alldimensionsarenominal Device Package Package Pins SPQ Reel Reel A0 B0 K0 P1 W Pin1 Type Drawing Diameter Width (mm) (mm) (mm) (mm) (mm) Quadrant (mm) W1(mm) DAC8311IDCKR SC70 DCK 6 3000 180.0 8.4 2.2 2.5 1.2 4.0 8.0 Q3 DAC8311IDCKT SC70 DCK 6 250 180.0 8.4 2.2 2.5 1.2 4.0 8.0 Q3 DAC8411IDCKR SC70 DCK 6 3000 180.0 8.4 2.2 2.5 1.2 4.0 8.0 Q3 DAC8411IDCKT SC70 DCK 6 250 180.0 8.4 2.2 2.5 1.2 4.0 8.0 Q3 PackMaterials-Page1

PACKAGE MATERIALS INFORMATION www.ti.com 29-Sep-2019 *Alldimensionsarenominal Device PackageType PackageDrawing Pins SPQ Length(mm) Width(mm) Height(mm) DAC8311IDCKR SC70 DCK 6 3000 195.0 200.0 45.0 DAC8311IDCKT SC70 DCK 6 250 195.0 200.0 45.0 DAC8411IDCKR SC70 DCK 6 3000 195.0 200.0 45.0 DAC8411IDCKT SC70 DCK 6 250 195.0 200.0 45.0 PackMaterials-Page2

None

None

IMPORTANTNOTICEANDDISCLAIMER TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS. These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources. TI’s products are provided subject to TI’s Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI’s provision of these resources does not expand or otherwise alter TI’s applicable warranties or warranty disclaimers for TI products. Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated

Datasheet下载

Datasheet下载