ICGOO在线商城 > 开发板,套件,编程器 > 评估板 - 嵌入式 - MCU,DSP > CY8CKIT-050B

- 型号: CY8CKIT-050B

- 制造商: Cypress Semiconductor

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

CY8CKIT-050B产品简介:

ICGOO电子元器件商城为您提供CY8CKIT-050B由Cypress Semiconductor设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 CY8CKIT-050B价格参考。Cypress SemiconductorCY8CKIT-050B封装/规格:评估板 - 嵌入式 - MCU,DSP, CY8C5868AXI-LP035 PSOC® 5LP MCU 32-Bit ARM® Cortex®-M3 Embedded Evaluation Board。您可以下载CY8CKIT-050B参考资料、Datasheet数据手册功能说明书,资料中有CY8CKIT-050B 详细功能的应用电路图电压和使用方法及教程。

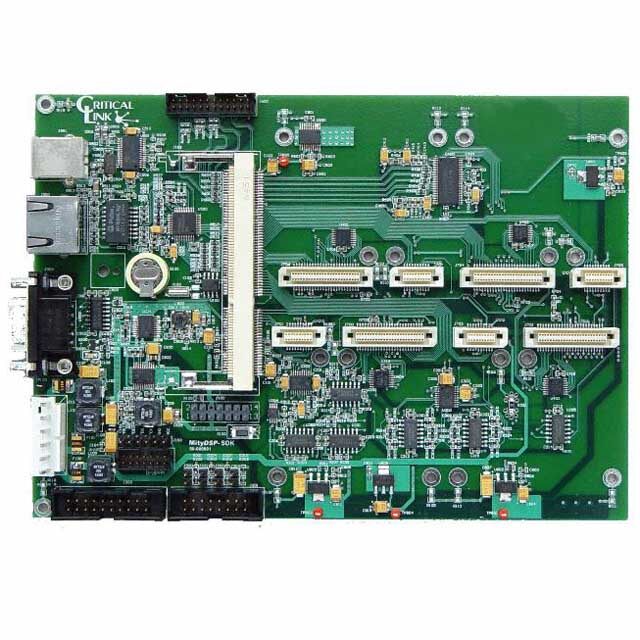

CY8CKIT-050B 是 Cypress Semiconductor Corp. 生产的一款评估板,专为嵌入式系统中的微控制器单元 (MCU) 和数字信号处理器 (DSP) 应用而设计。它基于 PSoC 5LP 系列,集成了高性能 ARM Cortex-M3 内核和可编程模拟及数字模块,适用于多种应用场景。 应用场景: 1. 智能家居与物联网 (IoT): CY8CKIT-050B 可用于开发智能家居设备,如智能灯控、温控器、传感器节点等。其低功耗特性使其适合长时间运行的 IoT 设备,内置的无线连接选项(通过外接模块)支持 Wi-Fi 和蓝牙功能,便于实现远程控制和数据传输。 2. 工业自动化: 在工业环境中,该评估板可用于开发实时控制系统、电机控制、传感器接口等。PSoC 5LP 的高集成度和可编程性使得它可以灵活配置,满足不同工业应用的需求,例如 PLC 控制、HMI(人机界面)开发等。 3. 消费电子: 适用于各种消费电子产品,如手持设备、穿戴式设备等。其丰富的 I/O 接口和强大的处理能力可以支持复杂的用户界面和多媒体功能。此外,CY8CKIT-050B 支持触摸感应技术,非常适合开发触控屏设备或按键替代方案。 4. 医疗设备: 在医疗领域,该评估板可用于开发便携式医疗设备,如心率监测仪、血糖仪等。其低功耗和高精度的模拟前端有助于提高测量准确性,同时支持多种通信协议,方便数据上传至云端或移动设备。 5. 汽车电子: CY8CKIT-050B 还适用于汽车电子系统的开发,如车载信息娱乐系统、车身控制模块(BCM)、传感器接口等。其强大的处理能力和丰富的外设接口使其能够应对复杂的汽车环境需求。 总之,CY8CKIT-050B 是一款多功能的评估板,适用于广泛的嵌入式系统开发,尤其在需要高性能、低功耗和高度集成的应用中表现出色。开发者可以通过该平台快速原型设计和验证概念,加速产品上市时间。

| 参数 | 数值 |

| 产品目录 | 编程器,开发系统嵌入式解决方案 |

| 描述 | KIT DEV PSOC 5LP开发板和工具包 - ARM PSoC 5LP Development Kit |

| 产品分类 | 评估板 - 嵌入式 - MCU, DSP工程工具 |

| 品牌 | Cypress Semiconductor Corp |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 嵌入式开发工具,嵌入式处理器开发套件,开发板和工具包 - ARM,Cypress Semiconductor CY8CKIT-050BPSOC® 5LP |

| 数据手册 | |

| 产品型号 | CY8CKIT-050B |

| 产品 | Development Kits |

| 产品种类 | 开发板和工具包 - ARM |

| 其它名称 | 428-3184 |

| 内容 | 板,电缆,LCD |

| 商标 | Cypress Semiconductor |

| 安装类型 | 固定 |

| 封装 | Bulk |

| 工作电源电压 | 9 V/12 V |

| 工具用于评估 | PSoC 5LP |

| 平台 | - |

| 接口类型 | RS-232, USB |

| 操作系统 | - |

| 板类型 | 评估平台 |

| 标准包装 | 1 |

| 核心 | ARM Cortex M3 |

| 核心处理器 | ARM® Cortex®-M3 |

| 类型 | MCU 32-位 |

| 系列 | CY8CKIT-050 |

| 设计资源 | http://www.cypress.com/?docID=41843 |

| 配套使用产品/相关产品 | CY8C5868AXI-LP035 |

PDF Datasheet 数据手册内容提取

CY8CKIT-050 PSoC® 5LP Development Kit Guide Doc. # 001-65816 Rev. *J Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 http://www.cypress.com

Copyrights Copyrights © Cypress Semiconductor Corporation, 2011-2018. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC (“Cypress”). This document, including any software or firmware included or ref- erenced in this document (“Software”), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as spe- cifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organi- zation, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resell- ers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress’s patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Soft- ware is prohibited. TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PUR- POSE. No computing device can be absolutely secure. Therefore, despite security measures implemented in Cypress hard- ware or software products, Cypress does not assume any liability arising out of any security breach, such as unauthorized access to or use of a Cypress product. In addition, the products described in these materials may contain design defects or errors known as errata which may cause the product to deviate from published specifications. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference pur- poses. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or autho- rized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgi- cal implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage (“Unintended Uses”). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products. Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F- RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respec- tive owners. CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 2

Contents 1. Introduction 5 1.1 Kit Contents.................................................................................................................5 1.2 PSoC Creator..............................................................................................................5 1.3 Additional Learning Resources....................................................................................6 1.3.1 Beginner Resources.........................................................................................6 1.3.2 Engineers Looking for More.............................................................................6 1.3.3 Learning from Peers.........................................................................................6 1.3.4 More Code Examples.......................................................................................6 1.4 Documentation Conventions........................................................................................8 2. Getting Started 9 2.1 DVD Installation...........................................................................................................9 2.2 Install Hardware.........................................................................................................10 2.3 Install Software..........................................................................................................10 2.4 Uninstall Software......................................................................................................10 2.5 Verify Kit Version.......................................................................................................10 3. Kit Operation 11 3.1 Programming PSoC 5LP Device...............................................................................11 4. Hardware 15 4.1 System Block Diagram..............................................................................................15 4.2 Functional Description...............................................................................................16 4.2.1 Power Supply.................................................................................................16 4.2.1.1 Power Supply Jumper Settings........................................................17 4.2.1.2 Grounding Scheme..........................................................................18 4.2.1.3 Low-Power Functionality..................................................................18 4.2.1.4 AC/DC Adaptor Specifications.........................................................19 4.2.1.5 Battery Specifications......................................................................19 4.2.2 Programming Interface...................................................................................19 4.2.2.1 Onboard Programming Interface.....................................................20 4.2.2.2 JTAG/SWD Programming................................................................20 4.2.3 USB Communication......................................................................................21 4.2.4 Boost Convertor.............................................................................................22 4.2.5 32-kHz and 24-MHz Crystal...........................................................................22 4.2.6 Protection Circuit............................................................................................22 4.2.6.1 Functional Description.....................................................................23 4.2.7 PSoC 5LP Development Kit Expansion Ports................................................24 4.2.7.1 Port D...............................................................................................24 4.2.7.2 Port E...............................................................................................26 4.2.8 RS-232 Interface............................................................................................27 4.2.9 Prototyping Area............................................................................................27 CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 3

Contents 4.2.10 Character LCD...............................................................................................28 4.2.11 CapSense Sensors........................................................................................29 5. Code Examples 31 5.1 Introduction................................................................................................................31 5.1.1 Programming the Code Examples.................................................................31 5.2 Project: VoltageDisplay_SAR_ADC...........................................................................32 5.2.1 Project Description.........................................................................................32 5.2.2 Hardware Connections...................................................................................32 5.2.3 SAR ADC Configuration.................................................................................32 5.2.4 Verify Output..................................................................................................33 5.3 Project: VoltageDisplay_DelSigADC.........................................................................33 5.3.1 Project Description.........................................................................................33 5.3.2 Hardware Connections...................................................................................33 5.3.3 DelSig ADC Configuration..............................................................................34 5.3.4 Verify Output..................................................................................................35 5.4 Project: IntensityLED.................................................................................................36 5.4.1 Project Description.........................................................................................36 5.4.2 Hardware Connections...................................................................................36 5.4.3 Verify Output..................................................................................................36 5.5 Project: LowPowerDemo...........................................................................................36 5.5.1 Project Description.........................................................................................36 5.5.2 Hardware Connections...................................................................................36 5.5.3 Verify Output..................................................................................................37 5.6 Project: CapSense.....................................................................................................38 5.6.1 Project Description.........................................................................................38 5.6.2 Hardware Connections...................................................................................38 5.6.3 Verify Output..................................................................................................38 5.7 Project: ADC_DAC....................................................................................................39 5.7.1 Project Description.........................................................................................39 5.7.2 Hardware Connections...................................................................................39 5.7.3 Verify Output..................................................................................................39 A. Appendix 41 A.1 Schematic..................................................................................................................41 A.2 Board Layout.............................................................................................................47 A.2.1 PDC-09356 Top.............................................................................................47 A.2.2 PDC-09356 Power.........................................................................................48 A.2.3 PDC-09356 Ground.......................................................................................49 A.2.4 PDC-09356 Bottom........................................................................................50 A.3 Bill of Materials (BOM)...............................................................................................51 A.4 Pin Assignment Table................................................................................................56 Revision History 60 Document Revision History ..............................................................................................................60 CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 4

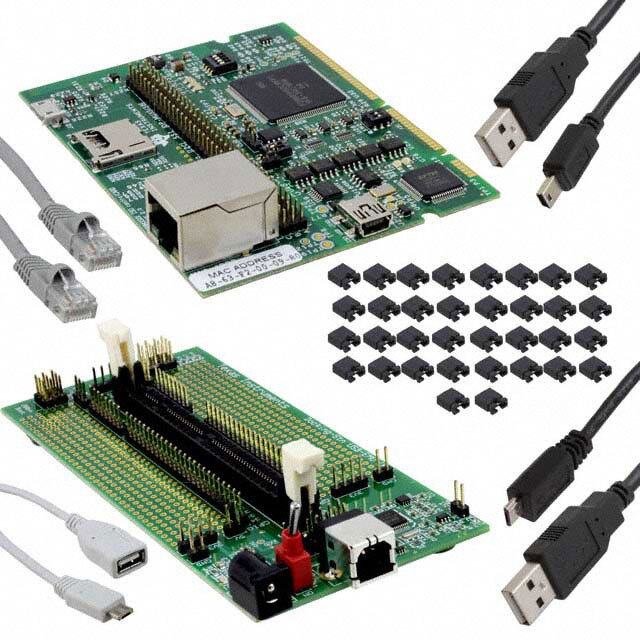

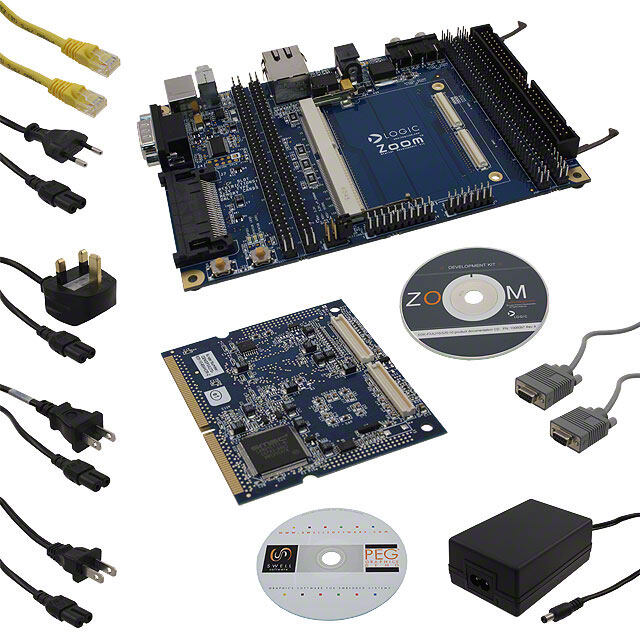

1. Introduction Thank you for your interest in the CY8CKIT-050 PSoC® 5LP Development Kit. This kit allows you to develop precision analog and low-power designs using PSoC 5LP. You can design your own projects with PSoC Creator™ or alter the sample projects provided with this kit. The CY8CKIT-050 PSoC 5LP Development Kit is based on the PSoC5LP family of devices. PSoC5LP is a Programmable System-on-Chip™ platform for 8-bit, 16-bit, and 32-bit applications. It combines precision analog and digital logic with a high-performance CPU. With PSoC, you can create the exact combination of peripherals and integrated proprietary IP to meet your application requirements. 1.1 Kit Contents The PSoC 5LP Development Kit contains: ■ Development board ■ Kit DVD ■ Quick start guide ■ USB A to mini-B cable ■ 3.3-V LCD module ■ Jumper wires and jumper shunts Inspect the contents of the kit; if you find any part missing, contact your nearest Cypress sales office for help. 1.2 PSoC Creator Cypress's PSoC Creator software is a state-of-the-art, easy-to-use integrated development environment (IDE) that introduces a hardware and software design environment based on classic schematic entry and revolutionary embedded design methodology. With PSoC Creator, you can: ■ Create and share user-defined, custom peripherals using hierarchical schematic design. ■ Automatically place and route select components and integrate simple glue logic, normally located in discrete muxes. ■ Trade off hardware and software design considerations allowing you to focus on what matters and getting to market faster. PSoC Creator also enables you to tap into an entire tools ecosystem with integrated compiler tool chains, RTOS solutions, and production programmers to support both PSoC 3 and PSoC 5LP. CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 5

Introduction 1.3 Additional Learning Resources Visit http://www.cypress.com/go/psoc5 for additional learning resources in the form of datasheets, application notes, and technical reference manual. 1.3.1 Beginner Resources AN77759 - Getting Started with PSoC 5 PSoC Creator Training 1.3.2 Engineers Looking for More AN54460 - PSoC 3, PSoC 4, and PSoC 5LP Interrupts AN52705 - PSoC 3 and PSoC 5LP - Getting Started with DMA AN52701 - PSoC 3 and PSoC 5LP - Getting Started with Controller Area Network (CAN) AN54439 - PSoC 3 and PSoC 5LP External Crystal Oscillators AN52927 - PSoC 3 and PSoC 5LP - Segment LCD Direct Drive Cypress continually strives to provide the best support. Click here to view a growing list of application notes for PSoC 3, PSoC 4, and PSoC 5LP. 1.3.3 Learning from Peers Cypress Developer Community Forums 1.3.4 More Code Examples PSoC Creator provides several example projects that make code development fast and easy. To access these example projects, click on Find Example Project… under the Example and Kits sec- tion in the Start Page of PSoC Creator or navigate to File > Open > Example Project… Figure 1-1. Find Example Project CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 6

Introduction The Find Example Project section has various filters that help you locate the most relevant project. PSoC Creator provides several starter designs. These designs highlight features that are unique to PSoC devices. They allow you to create a design with various components, instead of creating an empty design; the code is also provided. To use a starter design for your project, navigate to File > New > Project and select the design required. Figure 1-2. New Project The example projects and starter designs are designed for the CY8CKIT-001 PSoC Development Kit. However, these projects can be converted for use with the CY8CKIT-030 PSoC 3 Development Kit or CY8CKIT-050 PSoC 5LP Development Kit by following the procedure in the knowledge base article Migrating Project from CY8CKIT-001 to CY8CKIT-030 or CY8CKIT-050. CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 7

Introduction 1.4 Documentation Conventions Table 1-1. Document Conventions for Guides Convention Usage Displays file locations, user entered text, and source code: Courier New C:\ ...cd\icc\ Displays file names and reference documentation: Italics Read about the sourcefile.hex file in the PSoC Designer User Guide. Displays keyboard commands in procedures: [Bracketed, Bold] [Enter] or [Ctrl] [C] Represents menu paths: File > Open File > Open > New Project Displays commands, menu paths, and icon names in procedures: Bold Click the File icon and then click Open. Displays an equation: Times New Roman 2 + 2 = 4 Text in gray boxes Describes cautions or unique functionality of the product. CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 8

2. Getting Started This chapter describes how to install and configure the PSoC 5LP Development Kit. Kit Operationchapter on page11 describes the kit operation. It explains how to program a PSoC 5LP device with PSoC Programmer and use the kit with the help of a code example. To reprogram the PSoC device with PSoC Creator, see the installation instructions for PSoC Creator. Hardwarechapter on page15 details the hardware operation. Code Exampleschapter on page31 provides instructions to create a simple code example. The Appendix on page41 provides the Schematic on page41 and Bill of Materials (BOM) on page51 associated with the PSoC 5LP Development Kit. 2.1 DVD Installation Follow these steps to install the PSoC 5LP Development Kit software: 1. Insert the kit DVD into the DVD drive of your PC. The DVD is designed to auto-run and the kit menu appears. Figure 2-1. Kit Menu Note If auto-run does not execute, double-click cyautorun.exe on the root directory of the DVD. CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 9

Getting Started Figure 2-2. DVD Root Directory After the installation is complete, the kit contents are available at the following location: <Install_Directory>\Cypress\PSoC 5LP Development Kit\<version> 2.2 Install Hardware No hardware installation is required for this kit. 2.3 Install Software When installing the PSoC 5LP Development Kit, the installer checks if your system has the required software. These include PSoC Creator, PSoC Programmer, Windows Installer, .NET, and Keil Com- plier. If these applications are not installed, the installer installs them in your PC before installing the kit. If Acrobat Reader application is not installed in your PC, then the installer provides the link to install the same and this does not prevent kit installation. Note that Adobe reader is required to view the kit documents. Install the following software from the kit DVD: ■ PSoC Creator 3.0 or later ■ PSoC Programmer 3.19.1 or later Note When installing PSoC Programmer, select Typical on the Installation Type page. ■ Code examples (provided in the Firmware folder) 2.4 Uninstall Software The software can be uninstalled using one of the following methods: ■ Go to Start > Control Panel > Add or Remove Programs; select the Remove button. ■ Go to Start > All Programs > Cypress > Cypress Update Manager > Cypress Update Man- ager; select the Uninstall button. ■ Insert the installation DVD and click Install PSoC 5LP Development Kit button. In the CyIn- staller for PSoC 5LP Development Kit 2.1 window, select Remove from the Installation Type drop-down menu. Follow the instructions to uninstall. 2.5 Verify Kit Version To know the kit revision, look for the white sticker on the bottom left, on the reverse of the kit box. If the revision reads CY8CKIT-050B, then, you own the latest version. To upgrade CY8CKIT-050/CY8CKIT-050A to CY8CKIT-050B, you can purchase our latest kits at http://www.cypress.com/go/CY8CKIT-050. CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 10

3. Kit Operation The code examples in the PSoC5LP Development Kit help you develop precision analog applications using the PSoC 5LP family of devices. The board also has hooks to enable low-power measurements for low-power application development and evaluation. 3.1 Programming PSoC 5LP Device The default programming interface for the board is a USB-based onboard programming interface. To program the device, plug the USB cable to the programming USB connector J1, as shown in Figure3-1. Figure 3-1. Connect USB Cable to J1 CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 11

Kit Operation When plugged in, the board enumerates as DVKProg5. After enumeration, initiate, build, and then program using PSoC Creator. When using onboard programming, it is not necessary to power the board from the 12-V or 9-V DC supply or a battery. You can use the USB power to the programming section. If the board is already powered from another source, plugging in the programming USB does not damage the board. The PSoC 5LP device on the board can also be programmed using a MiniProg3 (CY8CKIT-002). To use MiniProg3 for programming, use the connector J3 on the board, as shown in Figure3-2. Note The MiniProg3 (CY8CKIT-002) is not part of the PSoC 5LP Development Kit contents. It can be purchased from the Cypress Online Store. Figure 3-2. Connect MiniProg3 CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 12

Kit Operation With the MiniProg3, programming is similar to the onboard programmer; however, the setup enumerates as a MiniProg3. The Select Debug Target window may be displayed, as shown in the following figure. Figure 3-3. Select Debug Target Click Port Acquire. The window appears as follows. Click Connect to start programming. CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 13

Kit Operation Figure 3-4. Click Connect CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 14

4. Hardware 4.1 System Block Diagram The PSoC 5LP Development Kit has the following sections: ■ Power supply system ■ Programming interface ■ USB communications ■ Boost convertor ■ PSoC 5LP and related circuitry ■ 32-kHz crystal ■ 24-MHz crystal ■ Port E (analog performance port) and port D (CapSense® or generic port) ■ RS-232 communications interface ■ Prototyping area ■ Character LCD interface ■ CapSense buttons and sliders Note P0[2] is connected to the SAR bypass capacitor C40, which can be selected by shorting jumper J43. P0[4] is connected to the SAR bypass capacitor C55, which can be selected by shorting jumper J44. CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 15

Hardware Figure 4-1. PSoC 5LP Development Kit Details Communication USB Boost Converter 10-Pin JTAG/SWD/SWO Power Adapter 9-V Battery Input Debug and Prog Header On-board Programming USB 32-kHz Crystal 10- Pin MiniTrace Connector 24-MHz Crystal Port D( CapSense/ Miscellaneous Port E Port) (Analog Por)t Reset Button Variable Resistor/ Potentiometer CapSense RS-232 Interface Character LCD Interface Prototyping Area (Contact points in a row are Switches/LEDs electrically con.n ected. Rows on the left and right of the notch are isolated) 4.2 Functional Description 4.2.1 Power Supply The power supply system on this board is versatile; input supply can be from the following sources: ■ 9-V or 12-V wall wart supply using connector J4 ■ 9-V battery connector using connectors BH1 and BH2 ■ USB power from communications section using connector J2 ■ USB power from the onboard programming section using connector J1 ■ Power from JTAG/SWD programming interface using connector J3 ■ Power through boost convertor that uses the input test points VBAT and GND CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 16

Hardware The board power domain has five rails: ■ Vin rail: This is where the input of the onboard regulators are connected. This domain is powered through protection diodes. ■ 5-V rail: This is the output of the 5-V regulator U2. The rail has a fixed 5-V output regardless of jumper settings. The voltage in this rail can be less than 5V only when the board is powered by the USB. This 5-V rail powers the circuits that require fixed 5-V supply. ■ 3.3-V rail: This is the output of the 3.3-V regulator U4. This rail remains 3.3V regardless of jumper settings or power source changes. It powers the circuits requiring fixed 3.3-V supply such as the onboard programming section. ■ Vddd rail: This rail provides power to the digital supply for the PSoC device. It can be derived from either the 5-V or 3.3-V rail. The selection is made using J10 (3-pin jumper). ■ Vdda rail: This rail provides power to the analog supply of the PSoC device. It is the output of a low-noise regulator U1. The regulator is a variable output voltage and can be either 3.3 V or 5 V. This is done by changing the position on J11 (3-pin jumper). The following block diagram shows the structure of the power system on the board. Figure 4-2. Power System Structure USB 3.3 V 5 V Programming USB Vin Communication 3.3-V Regulator Power Vddd Vddd Selection (J10) 9-V Battery 5 V 5-V Regulator 12-V/9-V Wall Vdda Vdda wart 5-V/3.3-V Analog Selection Regulator (J11) 4.2.1.1 Power Supply Jumper Settings Figure 4-3. Jumper Settings CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 17

Hardware Two jumpers govern the power rails on the board. J10 is responsible for the selection of Vddd (digital power) and J11 selects the VADJ of Vdda (analog power). The jumper settings for each power scheme are as follows. Powering Scheme Jumper Settings Vdda = 5V, Vddd = 5V J10 in 5-V setting and J11 in 5-V setting. Vdda = 3.3V, Vddd = 3.3V J10 in 3.3-V setting and J11 in 3.3-V setting. Vdda= 5V, Vddd = 3.3V J10 in 3.3-V setting and J11 in 5-V setting. Can be achieved, but is an invalid condition because the PSoC 5LP silicon Vdda=3.3V, Vddd=5V performance cannot be guaranteed. Warning: ■ The PSoC device performance is guaranteed when Vdda is greater than or equal to Vddd. Fail- ure to meet this condition can have implications on the silicon performance. ■ The power supply of the I/Os, Vddio, is connected to Vddd. Therefore, any input voltage to the PSoC I/Os must not exceed the Vddd. ■ When USB power is used, ensure a 3.3-V setting on both analog and digital supplies. This is because the 5-V rail of the USB power is not accurate and is not recommended. If you require 5- V operation, it is recommended to use an external power supply adapter or a 9-V battery. ■ If separate analog and digital power supplies are used, the analog supply ramp rate may be slower than that of the digital supply. This may cause I/Os to be in an indeterminate state until the power supplies stabilize. 4.2.1.2 Grounding Scheme The board design considers analog designs as major target applications. Therefore, the grounding scheme in the board is unique to ensure precision analog performance. The board has three types of ground: ■ GND - This is the universal ground where all the regulators are referred. Both Vssd and Vssa connect to this ground through a star connection. ■ Vssd - This is the digital ground and covers the digital circuitry on the board, such as RS-232 and LCD. ■ Vssa - This is the analog ground and covers the grounding for analog circuitry present on the board, such as the reference block. When creating custom circuitry in the prototyping area provided on the board, remember to use the Vssa for the sensitive analog circuits and Vssd for the digital ones. Port E on the board is the designated analog expansion connector. This connector brings out ports0, 3, and 4, which are the best performing analog ports on PSoC3 and PSoC5 devices. Port E has two types of grounds. One is the analog ground (GND_A in the silkscreen, Vssa in the schematic), which connects directly to the analog ground on the board. The other ground, known as GND, is used for the digital and high-current circuitry on the expansion board. This differentiation on the connector grounds helps the expansion board designer to separate the analog and digital ground on any high-precision analog boards being designed for port E. 4.2.1.3 Low-Power Functionality The kit also facilitates application development, which requires low power consumption. Low-power functions require a power measurement capability, also available in this kit. CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 18

Hardware The analog supply is connected to the device through the 0- resistor (R23). By removing this resistor and connecting an ammeter in series using the test points, Vdda_p and Vdda, you can measure the analog power used by the system. The digital supply can be monitored by removing the connection on jumper J10 and connecting an ammeter in place of the short. This allows to measure the digital power used by the system. The board provides the ability to measure analog and digital power separately. To measure power at a single point, rather than at analog and digital separately, remove resistor R23 to disconnect the analog regulator from powering the Vdda and short Vdda and Vddd through R30. The net power can now be measured at jumper J10 similar to the digital power measurement. To switch repeatedly between R23 and R30, moving around the 0- resistors can be discomforting. Hence, a J38 (unpopulated) is provided to populate a male 3-pin header and have a shorting jumper in the place of R23/R30. While measuring device power, make the following changes in the board to avoid leakage through other components that are connected to the device power rails. ■ Disconnect the RS-232 power by disconnecting R58. An additional jumper capability is available as J37 if you populate it with a 2-pin male header. ■ Disconnect the potentiometer by disconnecting J30. ■ Ground the boost pins if boost operation is not used by populating R1, R28, and R29. Also make sure R25 and R31 are not populated. 4.2.1.4 AC/DC Adaptor Specifications Use adaptors with the following specifications: ■ Input voltage: 100 to 240 VAC, 50 Hz to 60Hz, 1A ■ Output voltage: 12VDC, 1A ■ Power output: 12W ■ Polarization: Positive center ■ Certification: CE certified Some recommended part numbers include EPSA120100U-P5P-EJ (CUI Inc.) and LTE12W-S2 (Li Tone Electronics Co. Ltd). 4.2.1.5 Battery Specifications Use batteries with the following specifications: ■ Battery size: 6LR61 (9 V) ■ Output voltage: 9VDC ■ Type: Non-rechargeable alkaline consumer batteries ■ RoHS status: RoHS compliant ■ Lead free status: Pb-free Some recommended part numbers include 6LR61XWA/1SB (Panasonic), MN1604 (Duracell), and 6LR61 (Energizer). 4.2.2 Programming Interface This kit allows programming in two modes: ■ Using the onboard programming interface ■ Using the JTAG/SWD programming interface with a MiniProg3 CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 19

Hardware 4.2.2.1 Onboard Programming Interface The onboard programmer interfaces with your PC through a USB connector, as shown in Figure4-4. Figure 4-4. Onboard Programming Interface When the USB programming is plugged into the PC, it enumerates as DVKProg5 and you can use the normal programming interface from PSoC Creator to program this board through the onboard programmer. Pins P1[0] and P1[1] are connected to the onboard programmer. If you are using the onboard programmer, these pins should not be used for any other function. A 0- resistor R9 is provided on the board to disconnect power to the onboard programmer. 4.2.2.2 JTAG/SWD Programming Apart from the onboard programming interface, the board also provides the option of using the MiniProg3. This interface is much faster than the onboard program interface. The JTAG/SWD programming is done through the 10-pin connector, J3. CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 20

Hardware Figure 4-5. JTAG/SWD Programming The JTAG/SWD programming using J3 requires the MiniProg3 programmer, which can be purchased from http://www.cypress.com/go/CY8CKIT-002. Note While using MiniProg3, only the Reset mode is supported with this kit. 4.2.3 USB Communication The board has a USB communications interface that uses the connector, as shown in Figure4-6. The USB connector connects to the D+ and D– lines on the PSoC to enable development of USB applications using the board. This USB interface can also supply power to the board, as discussed in Power Supply on page16. Figure 4-6. USB Interface CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 21

Hardware 4.2.4 Boost Convertor The PSoC 5LP device has the unique capability of working from a voltage supply as low as 0.5V. This is possible using the boost convertor. The boost convertor uses an external inductor and a diode. These components are prepopulated on the board. Figure4-7 shows the boost convertor. To enable the boost convertor functionality, make the following hardware changes on the board. ■ Populate resistors R25, R27 (populated by default), R29, and R31 with 0- resistors. Note See the Bill of Materials (BOM) on page51 for the manufacturer part number. ■ Ensure that R1 and R28 are not populated After making these changes, you can configure the project to create a boost convertor-based design. The input power supply to the boost convertor must be provided through the test points marked Vbat and GND. Figure 4-7. Boost Converter 4.2.5 32-kHz and 24-MHz Crystal PSoC 5LP has an on-chip real time clock (RTC), which can function in sleep. This requires an external 32-kHz crystal, which is provided on the board to facilitate RTC-based designs. The PSoC 5LP also has an external MHz crystal option in applications where the IMO tolerance is not satisfactory. In these applications, the board has a 24-MHz crystal to provide an accurate main oscillator. 4.2.6 Protection Circuit A reverse-voltage and over-voltage protection circuit is added to the expansion port on the 5-V and 3.3-V lines. The protection circuit consists of two P-channel MOSFET on the power line, allowing the current to flow from input to output depending on the voltages applied at the external board connector. Figure4-8 and Figure4-9 are protection circuits placed between EBK and the onboard components on the 5-V and 3.3-V lines. CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 22

Hardware Figure 4-8. Schematic for Protection Circuit on 5-V Power Line Figure 4-9. Schematic for Protection Circuit on 3.3-V Power Line 4.2.6.1 Functional Description The protection circuit will protect from a maximum over-voltage or reverse-voltage of 12 V. The cut- off voltage on the 5-V line is 5.7 V and on the 3.3-V line is 3.6V. This means, if you apply more than this voltage level from the external board connector side, the p-MOS Q5 will turn off, thus protecting PSoC and other onboard components. The current consumption of these protection circuits is less than 6mA. When voltage from the external connector is between 1.8V and 3.3V, the p-MOS Q4 conducts. Because the voltage across R16 is less than the threshold voltage (Vth) of p-MOS Q6, it will turn off and the p-MOS Q5 conducts, allowing voltage supply to the DVK. When the external power supply exceeds 3.3V, the p-MOS Q5 starts conducting. This eventually turns off p-MOS Q6 at 3.6V, protecting the DVK from over-voltage. When a reverse voltage is applied across the protection circuit from the external connector side, Q4 P-MOS will turn off, thus protecting the components on the board from reverse voltage. CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 23

Hardware If you are using the regulator power supply from the board to power the external modules, both the P-MOS Q4 and Q5 will always be in the On state, allowing the flow of current with a maximum of 22mV drop across the circuit when the current consumed by the external module is 150mA. Note The working of protection circuit on the 3.3-V and 5-V lines is as described. For the purpose of explanation, the annotation of 3.3-V protection circuitry (Figure4-9) is used. 4.2.7 PSoC 5LP Development Kit Expansion Ports The PSoC 5LP Development Kit has two expansion ports, port D and port E, each with their own unique features. 4.2.7.1 Port D This is the miscellaneous port designed to handle CapSense-based application boards and digital application boards. The signal routing to this port adheres to the stringent requirements needed to provide good performance CapSense. This port can also be used for other functions and expansion board kits (EBKs). This port is not designed for precision analog performance. The pins on the port are functionally compatible to port B of the PSoC Development Kit. Any project made to function on port B of the PSoC Development Kit can be easily ported over to port D on this board. A caveat to this is that there is no opamp available on this port; therefore, opamp-based designs are not recommended for use on this port. The following figure shows the pin mapping for the port. CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 24

Hardware Figure 4-10. Port D CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 25

Hardware 4.2.7.2 Port E This is the analog port on the kit and has special layout considerations. It also brings out all analog resources such as dedicated opamps to a single connect. Therefore, this port is ideal for precision analog design development. This port is functionally compatible to port A of the PSoC Development Kit and it is easy to port an application developed on port A. This port has two types of grounds, CGND1 and CGND2. The two grounds are connected to the GND on the board, but are provided for expansion boards designed for analog performance. The expansion boards have an analog and digital ground. The two grounds on this port help to keep it distinct even on this board until it reaches the GND plane. Figure 4-11. Port E CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 26

Hardware 4.2.8 RS-232 Interface The board has an RS-232 transceiver for designs using RS-232 (UART). The RS-232 section power can be disconnected through a single resistor R58. This is useful for low-power designs. Figure 4-12. RS-232 Interface 4.2.9 Prototyping Area The prototyping area on the board has two complete ports of the device for simple custom circuit development. The ports in the area are port 0 and port 3, which bring out the four dedicated opamp pins on the device. Therefore, these ports can be used with the prototyping area to create simple yet elegant analog designs. It also brings SIOs such as port 12[4], port 12[5], port 12[6], and port 12[7] and GPIOs such as port P6[0] and port P6[6]. Power and ground connections are available close to the prototyping space for convenience. The area also has four LEDs and two switches for applications development. The two switches on the board are hard-wired to port 15[5] and port 6[1]. Two LEDs out of the four are hard-wired to port 6[2] and port 6[3] and the other two are brought out on pads closer to the prototyping area. CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 27

Hardware Figure 4-13. Prototyping Area This area also comprises of a potentiometer to be used for analog system development work. The potentiometer connects from Vdda, which is a noise-free supply and is hence capable of being used for low-noise analog applications. The potentiometer output is available on P6[5] and VR on header P6 in the prototyping area. 4.2.10 Character LCD The kit has a character LCD module, which goes into the character LCD header, P8. The LCD runs on a 3.3-V supply and can function regardless of the voltage on which PSoC is powered. A 0- resistor setting is available on the LCD section (R71/72), making it possible to convert it to a 3.3-V LCD. CAUTION When the resistor is shifted to support a 5-V LCD module, plugging in a 3.3-V LCD mod- ule into the board can damage the LCD module. Figure 4-14. Pin 1 Indication CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 28

Hardware Figure 4-15. LCD Connected on P8 Connector 4.2.11 CapSense Sensors The board layout considers the special requirements for CapSense. It has two CapSense buttons and a five-element CapSense slider. The CapSense buttons are connected to pins P5[6] and P5[5]. The slider elements are connected to pins P5[0:4]. The Cmod (modulation capacitor) is connected to pin P6[4] and an optional Rb (bleeder resistor) is available on P15[4]. CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 29

Hardware Figure 4-16. CapSense Sensors CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 30

5. Code Examples 5.1 Introduction All the code examples of this kit are for CY8C5868AXI-LP035 device. To access code examples described in this section, open the PSoC Creator Start Page. For additional code examples, visit http://www.cypress.com. Figure 5-1. PSoC Creator Start Page 5.1.1 Programming the Code Examples Follow these steps to open and program code examples: 1. Click on a code example from Kits on the PSoC Creator Start Page. 2. Create a folder in the desired location and click OK. 3. The project opens in PSoC Creator and is saved to that folder. 4. Build the code example to generate the hex file. 5. To program, connect the board to a computer using the USB cable connected to port J1, as described in Onboard Programming Interface on page20. The board is detected as DVKProg5 6. Click Debug > Program. 7. The programming window opens up. If the silicon is not yet acquired, select the DVKProg5 and click on the Connect button. 8. The silicon is acquired and is shown in a tree structure below the DVKProg5. 9. Click OK to exit the window and start programming. CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 31

Code Examples 5.2 Project: VoltageDisplay_SAR_ADC 5.2.1 Project Description This example code measures an analog voltage controlled by the potentiometer. The code uses the internal SAR ADC configured for a 12-bit operation; the ADC range is 0 to Vdda. The results are dis- played on the character LCD module. Note The PSoC 5LP Development Kit is factory-programmed with this example. 5.2.2 Hardware Connections The example requires the character LCD on P8. Because it uses the potentiometer, the jumper POT_PWR should be in place. This connects the potentiometer to the Vdda. 5.2.3 SAR ADC Configuration To view or configure the SAR ADC component, double-click the component in the TopDesign.cysch file. Figure 5-2. SAR ADC Configuration The SAR ADC is configured as follows: ■ Free-running mode of operation is selected because the ADC scans only one channel continu- ously. ■ Conversion rate is set to 100 ksps. The code waits for each sample, processes it, and displays the result on the LCD. ■ Range is set to Vssa to Vdda in single-ended mode because the potentiometer output is a single- ended signal that can go from 0 to Vdda. Therefore, at 12-bit resolution, the ADC will resolve in steps of Vdda/212. CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 32

Code Examples ■ Voltage reference should be set to Vdda/2 supply voltage when input range is set to ‘Vssa to Vdda’. It is set to 1.65 V here, because by default, Vdda jumper setting on the board is set to 3.3V. If J11 is changed to select 5 V, then this parameter should be changed to 2.5 V accordingly. 5.2.4 Verify Output Build and program the code example, and reset the device. The LCD shows the voltage reading cor- responding to the voltage on the potentiometer. Figure5-3 demonstrates the functionality. When you turn the potentiometer, the voltage value changes. You can also verify the voltage on the potentiom- eter using a precision multimeter. Note The potentiometer connects to a differential ADC, which works in single-ended mode. This means the ADC input is measured against internal Vssa. Any offset in the measurement can be pos- itive or negative. This can result in a small offset voltage even when the potentiometer is zero. Figure 5-3. Voltage Display using SAR ADC 5.3 Project: VoltageDisplay_DelSigADC 5.3.1 Project Description This example code measures a simple analog voltage controlled by the potentiometer. The code uses the internal Del-Sig ADC configured for a 20-bit operation; the ADC range is 0 to Vdda. The voltage measurement resolution is in microvolts. The results are displayed on the character LCD module. 5.3.2 Hardware Connections The example requires the character LCD on P8. Because it uses the potentiometer, the jumper POT_PWR should be in place. This connects the potentiometer to the Vdda. Move jumper J10 and J11 to position 2-3, this will set Vdda to 5 V. CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 33

Code Examples 5.3.3 DelSig ADC Configuration To view or configure the Delsig ADC component, double-click the component in the TopDe- sign.cysch file. Figure 5-4. Delta-Sigma ADC Configuration To configure the Del-Sig ADC: ■ Select the continuous mode of operation because the ADC scans only one channel. ■ Set the conversion rate to 187 samples/sec, which is the maximum sample rate possible at 20-bit resolution. ■ Set the range from Vssa to Vdda in single-ended mode because the potentiometer output is a single-ended signal that can go from 0 to Vdda. Therefore, at 20-bit resolution, the ADC will resolve in steps of Vdda/220. Note Internal Vdda/3 reference option is not available in the current PSoC5LP silicon. In this proj- ect, Vdda = 5V. The project will not work if Vdda = 3.3V, because it needs Vdda/3 reference for Del- Sig ADC. To set Vdda to 5V, in the VoltageDisplay_DelSigADC.cydwr window of PSoC Creator, click on the System tab, go to the Operating Conditions option. Set Vdda to 5V. CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 34

Code Examples Figure 5-5. Operating Conditions Option 5.3.4 Verify Output Build and program the code example, and reset the device. The LCD shows the voltage reading corresponding to the voltage on the potentiometer. Figure5-6 demonstrates the functionality. When you turn the potentiometer, the voltage value changes. You can also verify the voltage on the potentiometer using a precision multimeter. Notes ■ The potentiometer connects to a differential ADC, which works in single-ended mode. This means the ADC input is measured against internal Vssa. Any offset in the measurement can be positive or negative. This can result in a small offset voltage even when the potentiometer is zero. Move jumper J10 and J11 back to position 1-2 after verifying the output. ■ The LCD displays negative voltages when the POT is at 0th position. Figure 5-6. Voltage Display using Del-Sig ADC CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 35

Code Examples 5.4 Project: IntensityLED 5.4.1 Project Description This example code uses a pulse-width modulator (PWM) to illuminate an LED. When the pulse width of the PWM varies, the LED brightness changes. By continuously varying the pulse width of the PWM, the example code makes an LED go from low brightness to a high brightness and back. 5.4.2 Hardware Connections No hardware connections are required for this project, because all the connections are hard-wired to specific pins on the board. 5.4.3 Verify Output When the example code is built and programmed into the device, reset the device by pressing the Reset button or power cycling the board. The project output is LED3 glowing with a brightness control that changes with time (see Figure5-7). Note If the CY8CKIT-050 is programmed with any other code example involving LCD display prior to programming the IntensityLED.hex file, the LCD display continues to display the output of previous project as the LCD component is not handled in the IntensityLED project. The LCD display gets cleared by power cycling the board. Figure 5-7. Verify Output - Code Example 5.5 Project: LowPowerDemo 5.5.1 Project Description This code example demonstrates the low-power functionality of PSoC 5LP. The project implements an RTC based code, which goes to sleep and wakes up on the basis of switch inputs. The RTC uses an accurate 32-kHz clock generated using the external crystal provided on the board. When there is a key press, the device is put to sleep while the RTC is kept active. 5.5.2 Hardware Connections The project requires a 3.3V LCD to view the time display. No extra connections are required for project functionality. To make low-power measurements using this project, implement the changes proposed in Low-Power Functionality on page18. CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 36

Code Examples 5.5.3 Verify Output In normal operation, the project displays the time starting from 00:00:00 when SW2 is pressed. Normal mode is indicated by LED3 in ON state. When you press the SW2 button again, the device is put to sleep. Sleep mode is indicated by LED3 in OFF state. If an ammeter is connected to measure the system current (see Low-Power Functionality on page18 for details), a system current of less than 2 µA is displayed. The device wakes up when SW2 is pressed again and displays the time on the LCD. The following figures show the output display. Figure 5-8. PSoC 5LP in Active Mode Figure 5-9. PSoC 5LP in Sleep Mode CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 37

Code Examples 5.6 Project: CapSense 5.6.1 Project Description This code example provides a platform to build CapSense-based projects using PSoC 5LP. The example uses two CapSense buttons and one five-element slider provided on the board. Each capacitive sensor on the board is scanned using the Cypress CSD algorithm. The buttons are pre- tuned in the example code to take care of factors such as board parasitic. 5.6.2 Hardware Connections This project uses the LCD for display; therefore, ensure that it is plugged into the port. No specific hardware connections are required for this project because all connections are hard-wired on the board. 5.6.3 Verify Output Build and program the code example, and reset the device. The LCD displays the status of the two buttons as On/Off. The LCD also shows the slider touch position as a percentage. When you touch a button, the LCD displays ON; when you remove the finger from the button, the LCD displays OFF. When the slider is touched, the corresponding finger position is displayed as a percentage on the LCD. Figure 5-10. CapSense Slider CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 38

Code Examples Figure 5-11. CapSense Button 5.7 Project: ADC_DAC 5.7.1 Project Description This project demonstrates sine wave generation by using an 8-bit DAC and DMA. The sine wave period is based on the current value of the ADC value of the potentiometer. The firmware reads the voltage output by the board potentiometer and displays the raw counts on the LCD. An 8-bit DAC outputs a table generated sine wave to an LED using DMA at a frequency proportional to the ADC count. 5.7.2 Hardware Connections For this example, the character LCD must be installed on P8. The example uses the potentiometer; therefore, the jumper POT_PWR should also be in place. This jumper connects the potentiometer to the Vdda. 5.7.3 Verify Output Build and program the code example, and reset the device to view the ADC output displayed on the LCD. LED4 is an AC signal output whose period is based on the ADC. Turning the potentiometer results in LCD value change. This also results in change in the period of the sine wave fed into LED4. When the potentiometer changes, the blinking rate of LED4 changes. CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 39

Code Examples Figure 5-12. ADC Output CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 40

A. Appendix A.1 Schematic NO LOAD Power Supply TTPP44RREEDD V5.0 5.0V/1A LDO +9V/+12V, 1A DD33SSSS1122--EE33//6611TT VIN UU22 AAPP11111177DD5500GG RR2244 1 2 DD--6644 1 3 TTOO--225522 2 2 00880055 1 PPOOJJ44WWEERR JJAACCKK PP23--55GND D-64D-6421 E3/61TE3/61TDD44 CC3344221166++11G00N DuuFFdd 1166vvVIN 1GNDGVNDOUT 10 uFd 16v10 uFd 16vCC1144V3322S1166SD++ ZZTTNEEPPORR33 OOLRROEEADDD2V3.3 9V Battery SS12-SS12- V5.0 ZZEERRRR22OO66 08050805 Terminals LLMM11111177MMPPXX--33..33 3 SSOOTTV--222233IN VOUT 2 1 BBHH22 PPPOOOSSS123 123 33221166++C1C10022 uuFFdd 1166vv 1 UUG44ND TAB 4 33221166++C1C10011 55uuFFdd 1166vv VDDA JJ3333 VDDA_P 3.3V/0.8A LDO 2 1 RED BBAATT 99VV FFEEMMAA2LLEE GND 5V/3G.ND3V/0.5A LDO VSSD ZZEERRRR22OO33 08050805 1 VDDDVDDA JJ3388 BBHH11 99VV BBAATTNNN 99EEEVVGGG MM123AALLEE13 33221166++1100CC uu55FFdd 1166vv 85 UUIn11NSHDNLLTT117766S33CCESSON88SUET 124 2200440000..CC1111 uu77FFdd0603060312RR33..11112266KK0603060312 R3R3..11V773344DKKDA_P 331221166++10 uFd 16v10 uFd 16vCC1133 123NO 123LOAD GND DD1D2 Byp V3 GNGNGN SENSE EL3 VSSA 367 V5.0 1 S VDDA VDDD RR1111 VDDD Note:2 Lo0Z0Z88a00EE55dRRRR 33OOR003N0O 1 wLhOeAnD either GND 080508051233R3R30011 55oohhmm V080508052SSA11KK 32SENSE1SEL3V3 V352.0V13.3 Analog and Digital regulator required 2 321 321 2 RR008855005577 1 08050805 DD55ED GreenED Green JJ1111 JJ1100 VSSB GND VSSD VSSA NOZZ EELRROAOOD 1 LL NFootre 5:V: J11-3 to J11-2, J10-3 to J10-2 VSSD For 3.3V: J11-2 to J11-1, J10-2 to J10-1 VSSD VSSA For 5V Analog,3.3V Digital: J11-3 to J11-2, J10-2 to J10-1 Note: Load R25, R29 and R31 for operating the device on Boost Internal Boost Regulator VDDA VDDD VBAT Ind VBAT 08050805 RR2299 RR2255 RR3311 RRTTEEPPDD22 LL11 NO LOSSAOOTTDD22D3366 NO LOAD08050805 08050805 NO LOAD 1 RR2277 2 Vboost 2222 770u0u3322HH ZZHHCCSS ZZEERROO55008800 NO RRLO11AD08050805 00440022 CC00..3311 uuFFdd11221100 C21C21220066 VVuuFFdd BBLLTTAAPPCC11KK 2222 11uu00FFVVCCdd221122221100 00440022 CC00..221133 uuFFdd N08050805ORR L22O88AD GND GND GND GND VSSB Note: Load R1,R28 and Un-Load R27 for low power application CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 41

Appendix JJ4444 VCCd VCCa 1 2 12 1 1 VDDD VDDD CC5555 1 JJ4411 1 JJ4422 VCCd 0066003311..00 uuFFdd 11 PPIINN HHDDRR 11 PPIINN HHDDRR CC4422 CC4411 VSSA NO LOAD NO LOAD ZZEERRRR447O7O 06030603 00660033 11..00 uuFFdd 00440022 00..11 uuFFdd C1C1..440044 uuFFdd VDDD VDDA 11 PPIINN HHDDRR 11N PPO IIJNJNL22 1OHH55ADDDRR1 00440022 C0C0..441133 uuFFdd VSSD P2[4]P2[3]P2[2]P2[1]P2[0]P15[5]P15[4]P6[3]P6[2]P6[1]P6[0] P4[7]P4[6]P4[5]P4[4]P4[3]P4[2]P0[7]P0[6]P0[5]P0[4] 00660033 VSSD 11 PP1IINN1 HHDDJJRR112211 PP1IINN1 HHDDJJRR88 JJNO LOAD226611VSSD NO LOAD NO LOAD VBUS2 0 VDDA VSSD UU77 10999897969594939291908988878685848382818079787776 JJ2222 1 P15[4] 243210543210ddd7654327654 1 Rbleed RR88 NO LOAD DDioP2_P2_P2_P2_P2_P15_P15_P6_P6_P6_P6_VDDVSSVCCP4_P4_P4_P4_P4_P4_P0_P0_P0_P0_ 11N PPO IINNL OHHADDDRR ZZEERRRR339O9O 06030603 11..55KK V RR3388 P2[5] 1 75 22..22KK P2[6] 2 P2_5 VDDio0 74 P0[3] JJ4433 NO LOAD R3R3KK22 Cmod2200 pFd2200 pFd060306030012880055 CC3399 Ind PPPPPPP2116666[22[75[[[[[674]45]]]]]] 11345678901 PPPPPPPPVS2211666622______S__674567b45 II22CC00__SSCDLA,, SSIIOO CCYY88CC55886688AAXXII--LLPP003355 TTQQFFPP110000 SSIIOO__PPVPPPPPP11S00004422S________d32321010 777766666321098765 PPPPPPP10140402[2[[[[01102[[2]3]]]]]] 00V..D11 DuuFFAddV0044S0022SCCA4400 0066003312 VC1C1S12..5500S44 AuuFFdd Vboost 12 Ind VDDa 64 VBAT 13 Vboost VSSa 63 VCCa 14 Vbat VCCa 62 CC3377 CC3366 CC3388 /XRES 15 VSSd NC8 61 P5[0] 16 XRES NC7 60 00660033 11..00 uuFFdd0044002200..11 uuFFdd 0044002200..11 uuFFdd VSSB VSSD PPP555[[[123]]] 111789 PPP555___012 NNNCCC654 555987 VSSA NOTT PPLO55AD SSWWSPDDW1[CI2OOK] 22220123 PPPP5111____3012 SIO, I2C1_SDA PPP111N552C___3321 55556543 PP1122[[01]] 3322..7766YY8822KKHHzz XXTTAALL VSSD TDI 24 P1_3 SIO, I2C1_SCL P12_0 52 P3[7] 1 2 P1[5] 25 PP11__45 VDDio1P1_6P1_7P12_6_SIOP12_7_SIOP5_4P5_5P5_6P5_7P15_6 DPP15_7 DMVDDdVSSdVCCdNC1NC2P15_0P15_1P3_0P3_1P3_2P3_3P3_4P3_5VDDio3 PP33__76 51 P3[6] 1 CC322554V5SSA1 CC2277 VDDD 26272829303132333435363738394041424344454647484950 JJ1166 002660033 2222 ppFFdd 002660033 2222 ppFFdd 1 1 NO LOAD RR3366 06030603 P1[6]P1[7]P12[6]P12[7]P5[4]P5[5]P5[6]P5[7]DP_PDM_P P3[0]P3[1]P3[2]P3[3]P3[4]P3[5] 11 PPIINN HHDDRR VSSA VDDA VSSA ZZEERROO 11 PPIIJNJN11 1HH88DDRR1 CC3344 R33R3322E22E2206030603R3222ER3222E06030603 VCCd 22 11 22YY4433 MMHHzz CCrryyssttaall 06030603RRZZEE3355RROO NO LOAD 00440022 00..11 uuFFdd 11 VDDD DPDM CC3311 CC3300 CC2266 00440022 2222 ppFFdd 00440022 2222 ppFFdd 00440022 00..11 uuFFdd VSSD CC2299 CC3333 11..00 uuFFdd00660033 00440022 00..11 uuFFdd CC00..331155 uuFFdd VSSA VSSA 00440022 Note: VSSD VSSD PSoC 5 Place De-Caps near to the Chip CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 42

Appendix CC77 CC1188 CC1122 CC2200 CC2211 CC1100 PLACE ONE CAP PER EACH VCC ON U5. 00440022 00..11 uuFFdd 00440022 00..11 uuFFdd 00440022 00..11 uuFFdd 00440022 00..11 uuFFdd 00440022 00..11 uuFFdd 00440022 00..11 uuFFdd SS12-E3/61TSS12-E3/61TDD88VD-64D-6421VBUS1INSS12-E3/61TSS12-E3/61TDD22VD-64D-6421VBUS15.0 000603060312440022 11RR11C0C000%%11..00111144KK99 uuFF3Vdd3_FX1200P440022 PCC26C26LL....112233AO11 VVuuCSFFddEE CT00441O00221 U AC0C05..N1111-66 3Duu FF ACddN1D6 GCUNL5DO-7S.E11VCC132VCC2V08050805123.317VCC3RZRZ27EE99VCC443RRVCC5OO55VCC6 5XTALIN32244YY2 11MMHHzz14XTALOUT GND 00440022 VCC00S..11S11D uuFFddVDDDVSSD J5J5330013579MMIILL KKEE1YY24680EEDD SSMMDD SWDSSS/T/XWWWDSRIDDOWECISOVK/JTAG 68CCS1S37988S2S4001..00UUV11GBSS22 00uuD822NBB44UD0004020402FFI44M R1R1DDPSMMLLddJJ20033CC11II00VNN00KK1CII0012354 NC1CBB//2SSNNNC23 88UUNC388--7--33D9D9SSSSGGOONC4D-64D-64II21NVCCOONDBDIICCUD10D10GSSD-64D-64S21NJJND1CO99D AL3D11D11LV1D-64D-6421O3A_564DF1XG1NRR112D0011DPKKD77+-0402040204020402TTGR2R23VVTTN..V66--22VVD2231KKT0022_PRRF040204022X12PR2R2..5522KK 411542331456389421290137 WSSADDCRRRCCCIAFVVCDLTTTMPDDECAKLLLAGND1CCLALSYYILKN012OUCCE01KEAGND2///U//SFFFUT12SSUS#LLLTLLPAAARW#GGGDRABCCCGND1YY77GND2CC6688GND30011GND433UUAA55GND5--5566GND6LLTTXXCCCPPPAAP45AP//FFPP6PAPPPPPPPII/AARESERVEDA7PPPPPPPPPPFFPDDDDDDA/102DDOOBBBBBBBBKF2345673///0123456701//////nnLTAAS/FFFFFFW//////////IIAEDDLFFFFFFFFFFNNDDDDDDGNODDDDDDDDRRUDDTT111111DDE012345672018901234510 333333413122222244444555456789083901234556789012 SSS/XWWWRDDEOSCIOK 1TTVV11 1206030603R31R319%9%22KKV11BUS1 VDDDVSSD J5J544001357900MMIILL KKEE11YY246800EEDD- SSPMMIDDN TRACEPPPPP 22222[[[[H543[67]]]]E]ADER 2 610 1241 26285356 57 14 FIRMWARE UPDATE 06030603RR2222 FX2LP Programmer GND RUCOSEBQM UBPIALRICAEKNDVC FOEOL.RTAGE 1 61612%2%KK GND GND JJ5500 P0[0]P0[1]P0[2]P0[3]P0[4]P0[5]P0[6]P0[7] P3[0]P3[1]P3[2]P3[3]P3[4]P3[5]P3[6]P3[7] Prototype Area SSWW11 87654321 87654321 /XRES 1A 2A 87654321 87654321 1B 2B PP44 PP33 SSWW PPUUSSHHBBUUTTTTOONN RREECCPP 88XX11 RREECCPP 88XX11 VDDD BBrreeaaddbbooaarrdd LED1 2 LLEEDD11 1 1RR6622 333300 oo2hhmm 1JJ551 NO LOAD VSSD VDDA12 JJ12RR33005566 P6[5] LED2 2LLLLEEEELLLLDDDDEEEE RRRRDD0000DD88880000eeee33225555dddd 1 1RRRR66660011 3333555500003333888800000000 oooo2hhhhmmmm 11 PPIINN HHDDRR VDDA Note: Un-Load R48 - R54 to disconnect Capacitive Sensors P6[2] 2 1 1 2 PP66 N ohtieg:h3 PLp611or[N500aeO]KKdc2 iLRsRRO5iA556oD55 n11f 00oaKK1rnalogVSS10 uFd 16v10 uFd 16vAP1332251166[5++]CC4455P116BA[3]SSWW332LLLLEEEE22LLDDDDABEE RRRR0000DD88880000eeee445555dddd 1 P61[RR155]99 335555000033888800000011 BAoo2VhhSmmSSSWWD22 22AB 12345678 12345678 PLLE6E[DD52]1 V5.0 V3.3 RR44060306031P5[0]99ZEROZERORR55060306032P5[1]00ZEROZERORR06030603355P5[2]11ZEROZERORR55060306034P5[3]22ZEROZERORR55060306035P5[4]33ZEROZERO 06030603P5[5] RZRZEE55RR44OO 06030603P5[6] RZRZEE44RR88OO SSWW PPUUSSHHBBUUTTTTOONN SSWW PPUUSSHHBBUUTTTTOONN VSSA VSSD 1 CCSSBB11 1 CCSSBB22 CCaappSSeennssee LLiinneeaarr SSlliiddeerr 55 SSeegg VSSD VSSD 11 PPIINN HHDDRR11 PPIINN HHDDRR 11 PPIINN HHDDRR CCSSSS11 CCaappSSeennssee CCaappSSeennssee JJ2277 1 JJ3355 1 JJ2288 1 NO LOAD1JJ33166 NO LOAD1JJ771 VDDD 1JJ11144 NO LOADVDDA1JJ661 NO LOAD 1 VSSA 1 VSSA 1 CapSense Button and Slider VSSD11 PPIINN HHDDRR VSSA11 PPIINN HHDDRR 11 PPIINN HHDDRR 11 PPIINN HHDDRR VSSD VDDD VDDD VDDA JJ3322 JJ3344 P6[6]P6[0]P12[7]P12[6]P12[5]P12[4] 1 1 1 1 87654321 1 1 1 1 VSSD 87654321 JJ2299 JJ3311 VSSA VSSD PP99RREECCPP 88XX11 CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 43

Appendix GND CGND1 Use Separate Track Expansion Connectors PP11 for CGND1 to GND P3[6] 2 1 P3[7] PP22 P3[4] 4 2 1 3 P3[5] P1[6] 2 1 P1[7] JJ2233 1 PP33[[20]] 1680 468 357 579 PP33[[31]] JJ1155 PTSDW1[I2D]IO 468 246 135 357 SSPWW1[5DO]CK 1 P0[6] 12 10 9 11 P0[7] 1 10 8 7 9 NO LOAD P0[4] 14 12 11 13 P0[5] 1 P2[6] 12 10 9 11 P2[7] JJ2200 1 PP00[[20]] 112680 111468 111357 111579 PP00[[31]] NO JJL11O99AD PPP222[[[420]]] 111468 111246 111135 111357 PPP222[[[315]]] 1 P4[6] 22 20 19 21 P4[7] 1 20 18 17 19 NO JJ11L77OAD1 PPP444[[[420]]] 22234680 22222468 22221357 22223579 PPP444[[[315]]] NO JJ22L111OAD PPPP5555[[[[6024]]]] 22222468 22220246 12229135 22221357 PPPP5555[[[[7531]]]] 1 P12[2] 32 30 29 31 P12[3] 1 30 28 27 29 JJ11N33O LOAD SCL PV152.0[0] 333468 333246 333135 333357 PV132.3[1]SDA VSSA JJ22N44O L1OAD SCLPP1122[[02]] 333246 333024 233913 333135 PPV11322.3[[13]]SDA 1 1 40 3480 3379 39 VIN 1 1 V5.0 3480 3368 3357 3379 VIN NO LOAD 2200xx22 RREECCPP RRAA NO LOAD 40 39 CGND1 2200xx22 RREECCPP RRAA VSSD Port E (Analog EBK Connector) Port D (Misc Connector) CGND1 VSSD VDDA JJ3399 NO LOAD VREF 1 RR7733 2 P0[3] 1 ZZEERROO55008800 UU66 LLMM44114400NO LOAD 1 NO LOAD 2 6 VREF 1 RR3344 2 1 RR3377 2 P3[2] VIN VREF CC2244 ZZEERROO55008800 ZZEERROO55008800 3 EN NDND1ND2ND3NC 5 00660033 N11O..00 LuuOFFAddD 10 uFd 16v10 uFd 16v33221166++CC2288 0044002200CC..1133 22uuFFdd GGGG VSSA VSSA 1478 Voltage Reference VSSA CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 44

Appendix LCD Display Note: Load R72 for 5V operation, Load R71 for 3.3V operation RR6677 VLCD 1100KKNO LOAD V5.0 VLCD V3.3 3 1 VIN TT V5.0 SS12-E3/61TSS12-E3/61TDD771 SS12-E3/61SS12-E3/61DD111 RRPP27788N22O0088 0055LO00AEED 1 RR277110088005500EE 1 00440022 CC00V..5511S33 SuuDFFdd 2 D-64D-64 D-64D-64 GVGVNCNCDCDC 12 1 2 1 2 6S17S2VBDUMSJJ22 123 2 VBUS2VBUS22 DDMP LLCCDD RR//nnVREDVREDWWOSN0OSN0 34567 1100KKRR330066660099 11RR00660088 oohhmm33006600VSSD S3S4 GNDIDDP 54 D14D141 D12D121 D13D131 MMOODDUULLEE DDDDDD123123 8910 111111000000KKKKKK 00440022 RRRRRR444444220011 PP22[[01]] UUSSBB MMIINNII BB DD44 11 00440022 P2[2] 89 D-64D-642 D-64D-642 D-64D-642 DDDDDD567567 111234 11110000KKKK 0000444400002222 RRRR44443344 PP22[[34]] 110000KK RR44 USB MinB AA 1156 11110000KKKK 00440022 RRRR44445566 P2[5] 1 22004400 2 LLCCDD HHEEAADDEERR WW//OO BBAACCKKLLIIKKGGHHTT 0000444400002222 P2[6] CC99 0004020402..0011 uuFFdd VLCD VSSD VSSD RR7700 NO LOAD55008800 Note: Un-Load R58 to disconnect RS-232 Power VDDD JJ3377 12 NO LOAD 1 12 2 d 16vd 16v33221166 ++ CC4488 CC4477 RR5588 55008800 0 uF0 uF CC4466 00440022 00..11 uuFFdd 0044002200..11 uuFFdd PP77 1100 oohhmm 11 10 UU88 16 59 4 C2+ CC C1+ 1 VSSD 4 VSSD CC5511 V CC5500 8 RTS 3 RX 00440022 00..11 uuFFdd 00440022 00..11 uuFFdd 7 CTS 26 TX 5 C2- C1- 3 RR6644 ZZEERROO SERIAL_TX 1 TX 14 11 RX 13 TR1OUT TR1IN 12 RR6633 33006600110000 oohhmm DDBB99 FFEEMMAALLEE RX1IN RX1OUT 1 2 SERIAL_RX 11 RR6655 55008800110000 oohhmm RCTTSS 78 TR2OUT TR2IN 190 1 2 SERIAL_RTS RX2IN RX2OUT 55008800 RR6666 ZZEERROO SERIAL_CTS 33006600 SSEERRIIAALL__TRXX PP155 CC4499 2 V+ GND V- 6 CC5522 SSEERRIIAALL__CRTTSS 234 00440022 00..11 uuFFddMMAAXX33223322CCDDRR15 00440022 00..11 uuFFdd 44xx11 RREECCPP RS 232 VSSD CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 45

Appendix RR7744 ZZEERROO NO LOAD RR7755 ZZEERROO NO LOAD 55008800 55008800 V5.0_EXTQQ11 PPMMOOSS(( DDMMPP33009988LL--77)) V5.0 V3.3_EXTQQ44 PPMMOOSS(( DDMMPP33009988LL--77)) V3.3 RR77 QQ33 RR1166 QQ55 PMOS( DMP3098L-7)PMOS( DMP3098L-7) =4.3V(PTZTE254,SOD-106)=4.3V(PTZTE254,SOD-106) 2222DD0011 oo55hhmm PPQQMM22OOSS(( DDMMPP33009988LL--R1R177KK11)) 00oohhmm PMOS( DMP3098L-7)PMOS( DMP3098L-7) Vz=1.8V(BZT52C2V0-7-F)Vz=1.8V(BZT52C2V0-7-F) 44DD44112266 oohhmm PPQQMM66OOSS(( DDMMPP33009988LL--77R1R1))KK11 88oohhmm VzVz Protection Circuits CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 46

Appendix A.2 Board Layout A.2.1 PDC-09356 Top CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 47

Appendix A.2.2 PDC-09356 Power CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 48

Appendix A.2.3 PDC-09356 Ground CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 49

Appendix A.2.4 PDC-09356 Bottom CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 50

Appendix A.3 Bill of Materials (BOM) Item Qty Reference Value Description Manufacturer Manufacturer Part No. PCB Cypress PDC-09356 BATTERY HOLDER 9V Male Keystone Elec- 1 1 BH1 BAT 9V MALE 593 PC MT tronics BATTERY HOLDER 9V Keystone Elec- 2 1 BH2 BAT 9V FEMALE 594 Female PC MT tronics C2, C4, C5, C13, CAP 10UF 16V TANTALUM 3 9 C14, C15, C28, 10 uFd 16v AVX TAJA106K016R 10% 3216 C45, C46 CAP CER 22UF 10V 10% X5R 4 2 C6, C22 22 uFd Kemet C1210C226K8PACTU 1210 C7, C10, C12, C16, C17, C18, C19, C20, C21, C26, C32, C33, C34, C35, C36, CAP .1UF 16V CERAMIC Y5V Panasonic - 5 29 0.1 uFd ECJ-0EF1C104Z C38, C40, C41, 0402 ECG C43, C47, C48, C49, C50, C51, C52, C53, C1, C3, C23 CAP 10000PF 16V CERAMIC Panasonic - 6 2 C8, C9 0.01 uFd ECJ-0EB1C103K 0402 SMD ECG CAP CER 2.2UF 6.3V 20% Panasonic - 7 1 C11 2.2 uFd ECJ-0EB0J225M X5R 0402 ECG C29, C37, C42, CAP CERAMIC 1.0UF 25V 8 4 1.0 uFd Taiyo Yuden TMK107BJ105KA-T C44 X5R 0603 10% CAP, CER, 22 pF, 50V, 5%, Panasonic - 9 2 C25, C27 22pF ECJ-0EC1H220J COG, 0603, SMD ECG SMD/SMT 0805 2200pF GRM2165C1H222JA0 10 1 C39 2200 pFd Murata 50volts C0G 5% 1D CAP CERAMIC 1.0UF 25V 11 2 C54, C55 1.0 uFd Taiyo Yuden TMK107BJ105KA-T X5R 0603 10% D1, D2, D3, D4, DIODE SCHOTTKY 20V 1A Vishay/General 12 6 SS12-E3/61T SS12-E3/61T D7, D8 SMA Semiconductor LED GREEN CLEAR 0805 Chicago Minia- 13 1 D5 LED Green CMD17-21VGC/TR8 SMD ture DIODE SCHOTTKY 40V 1.0A 14 1 D6 ZHCS Zetex ZHCS1000TA SOT23-3 D9, D10, D11, SUPPRESSOR ESD 5VDC 15 6 ESD diode Bourns Inc. CG0603MLC-05LE D12, D13, D14 0603 SMD DIODE ZENER 4.3V 1W SOD- Rohm Semicon- 16 1 D15 4.3V zener diode PTZTE254.3B 106 ductor DIODE ZENER 2V 500MW 17 1 D16 2.0V Zener Diode Diodes Inc BZT52C2V0-7-F SOD-123 CONN USB MINI B SMT 18 2 J1,J2 USB MINI B TYCO 1734035-2 RIGHT ANGLE 50MIL KEYED CONN HEADER 10 PIN 50MIL 19 2 J3, J40 Samtec FTSH-105-01-L-DV-K SMD KEYED SMD CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 51

Appendix Item Qty Reference Value Description Manufacturer Manufacturer Part No. CONN JACK POWER 2.1mm 20 1 J4 POWER JACK P-5 CUI PJ-102A PCB RA 21 1 J50 Breadboard BREADBOARD 17x5x2 3M 923273-I TP1, J26, J27, BLACK TEST TEST POINT PC MINI .040"D Keystone 22 5 5001 J35, J28 POINT Black Electronics LED1, LED2, Rohm 23 4 LED Red LED RED CLEAR 0805 SMD SML-210LTT86 LED3, LED4 Semiconductor INDUCTOR SHIELD PWR SLF7032T-220MR96- 24 1 L1 22 uH TDK Corporation 22UH 7032 2-PF CONN FMALE 40POS DL .100 Sullins Electron- 25 2 P1,P2 20x2 RECP RA PPPC202LJBN-RC R/A GOLD ics Corp. CONN DB9 FMALE VERT 26 1 P7 DB9 FEMALE Norcomp Inc. 191-009-223R001 PRESSFIT SLD LCD HEADER W/ CONN RECEPT 16POS .100 27 1 P8 Tyco Electronics 1-534237-4 O BACKLIGHT VERT AU 28 4 P3, P4, P6, P9 RECP 8X1 CONN RECT 8POS .100 VERT 3M 929850-01-08-RA P-MOS, 30V 3.8A Q1, Q2, Q3, Q4, MOSFET P-CH 30V 3.8A 29 6 SOT23 in Protec- Diodes Inc DMP3098L-7 Q5, Q6 SOT23-3 tion circuit RES 220 OHM 1/ ERJ- 30 1 R7 10W 1% 0603 Panasonic - ECG YES 3EKF2200V SMD RES 442 OHM 1/ ERJ- 31 1 R16 10W 1% 0603 Panasonic - ECG YES 3EKF4420V SMD RES 100K OHM 1/16W 5% Panasonic - 32 2 R3, R4 100K ERJ-2GEJ104X 0402 SMD ECG R9, R23, R24, RES 0.0 OHM 1/10W 5% 0805 33 6 ZERO Panasonic-ECG ERJ-6GEY0R00V R26, R27, R71 SMD RES 2.2K OHM 1/16W 5% Panasonic - 34 2 R5, R6 2.2K ERJ-2GEJ222X 0402 SMD ECG RES 1.0K OHM 1/8W 5% 0805 Panasonic - 35 3 R11, R10, R18 1K ERJ-6GEYJ102V SMD ECG RES 3.16K OHM 1/10W .5% 36 1 R12 3.16K Yageo RT0603DRD073K16L 0603 SMD RES 3.74K OHM 1/10W 1% Panasonic - 37 1 R13 3.74K ERJ-3EKF3741V 0603 SMD ECG RES 100K OHM 1/10W 1% 38 1 R14 100K Yageo RC0603FR-07100KL 0603 SMD R15, R59, R60, RES 330 OHM 1/10W 5% 0805 Panasonic - 39 5 330 ohm ERJ-6GEYJ331V R61, R62 SMD ECG R17, R40, R41, RES 10K OHM 1/16W 5% Stackpole Elec- RMCF 1/16S 10K 5% 40 8 R42, R43, R44, 10K 0402 SMD tronics Inc R R45, R46 R35, R36, R39, R47, R48, R49, RES ZERO OHM 1/16W 5% Panasonic - 41 13 R50, R51, R52, ZERO ERJ-3GEY0R00V 0603 SMD ECG R53, R54, R64, R66 CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 52

Appendix Item Qty Reference Value Description Manufacturer Manufacturer Part No. RES 22 OHM 1/16W 1% 0603 Panasonic - 42 2 R32, R33 22E ERJ-3EKF22R0V SMD ECG RES 100 OHM 1/8W 5% 0805 43 2 R63, R65 100 ohm Rohm MCR10EZHJ101 SMD POT 10K OHM 1/8W CARB CTS Electro- 44 1 R56 POT 10K 296UD103B1N VERTICAL components RES 10 OHM 1/8W 5% 0805 Stackpole Elec- 45 1 R58 10E RMCF 1/10 10 5% R SMD tronics Inc RES 100 OHM 1/16W 5% 0603 Panasonic - 46 1 R68 100 ohm ERJ-3GEYJ101V SMD ECG RES 10K OHM 1/16W 5% Panasonic - 47 1 R69 10K ERJ-3GEYJ103V 0603 SMD ECG SW LT SWITCH 6MM 160GF Panasonic - 48 3 SW1, SW2, SW3 EVQ-Q2P02W PUSHBUTTON H=2.5MM SMD ECG IC LDO REG LOW NOISE ADJ Linear 49 1 U1 LT1763CS8 LT1763CS8#PBF 8-SOIC Technology IC REG LDO 1.0A 5.0V TO- 50 1 U2 AP1117D50G Diodes Inc AP1117D50G-13 252 IC EEPROM 128BIT 400KHZ Microchip 51 1 U3 24LC00/SN 24LC00/SN 8SOIC Technology IC REG 3.3V 800MA LDO National LM1117IMP-3.3/ 52 1 U4 LM1117MPX-3.3 SOT-223 Semiconductor NOPB IC, FX2 HIGH-SPEED USB CY7C68013A- Cypress CY7C68013A- 53 1 U5 PERIPHERAL CONTROLLER 56LTXC Semiconductor 56LTXC QFN56 CY8C5868AXI- Cypress 54 1 U7 PSoC 5 Mixed-Signal Array CY8C5868AXI-LP035 LP035 TQFP100 Semiconductor IC 3-5.5V LINE DRVR/RCVR Texas 55 1 U8 MAX3232CDR MAX3232IDR 16-SOIC Insturments CER RESONATOR 24.0 MHz 56 1 Y1 24 MHz Murata CSTCW24M0X53-R0 SMD CRYSTAL 32.768 KHZ CYL Citizen America CFS308- 57 1 Y2 32.768KHz XTAL 12.5PF CFS308 Corporation 32.768KDZF-UB CRYSTAL 24.000MHZ 20PF 58 1 Y3 24 MHz Crystal ECS Inc ECS-240-20-5PX-TR SMD TEST POINT PC MINI .040"D Keystone 59 3 J8, J33, TP2 RED TEST POINT 5000 RED Electronics RES 2.2KOHM 1/16W Panasonic - 60 1 R38 2.2K ERA-V27J222V 2700PPM 5%0603 ECG CONN HEADER VERT SGL 61 2 J10, J11 3p_jumper 3M 961103-6404-AR 3POS GOLD CONN HEADER VERT SGL 62 3 J30, J43, J44 2p_jumper 3M 961102-6404-AR 2POS GOLD 3.3V LCD Module 3.3V LCD Module 16POS w/16 63 1 NA 16POS w/16 pin Lumex LCM-S01602DTR/A-3 pin header installed header installed CONN HEADER VERT SGL 64 1 NA 16 pin header 3M 961116-6404-AR 16POS GOLD RES 39.0K OHM 1/10W 1% Rohm 65 1 R21 39K MCR03EZPFX3902 0603 SMD Semiconductor CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 53

Appendix Item Qty Reference Value Description Manufacturer Manufacturer Part No. RES 62.0K OHM 1/10W 1% Rohm 66 1 R22 62K MCR03EZPFX6202 0603 SMD Semiconductor CAP, CER, 22 pF, 50V, 5%, Panasonic - 67 2 C30, C31 22pF ECJ-1VC1H220J COG, 0603, SMD ECG CONN RECEPT 4POS .100 68 1 P5 4x1 RECP 3M 929850-01-04-RA VERT GOLD J31, J32, J29, CONN RECEPT 4POS .100 69 1 4x1 RECP 3M 929850-01-04-RA J34 VERT GOLD No Load Components CAP CERAMIC 1.0UF 25V 70 1 C24 1.0 uFd Taiyo Yuden TMK107BJ105KA-T X5R 0603 10% J5, J6, J12, J14, J18, J22, J25, TEST POINT PC MINI .040"D Keystone Elec- 71 11 RED 5000 TP3, TP4, J16, RED tronics J39 TEST POINT PC MINI .040"D Keystone Elec- 72 2 J7,J36 BLACK 5001 Black tronics TEST POINT PC MINI .040"D Keystone Elec- 73 1 TP5 WHITE 5002 WHITE tronics POT 10K OHM 1/4" SQ CERM 74 1 R67 10K Bourns Inc. 3362P-1-103LF SL ST R30, R34, R57, R72, R25, R31, RES 0.0 OHM 1/10W 5% 0805 75 12 ZERO Panasonic-ECG ERJ-6GEY0R00V R70, R37, R29, SMD R73, R74, R75 TRIMPOT 10K OHM 4MM TOP 76 1 R55 10K Bourns Inc. 3214W-1-103E ADJ SMD RES ZERO OHM 1/10W 5% Panasonic - 77 2 R1, R28 ZERO ERJ-3GEY0R00V 0603 SMD ECG IC REF PREC VOLT National Semi- LM4140ACM-1.0/ 78 1 U6 LM4140 MICROPWR 8-SOIC conductor NOPB RES 1.5KOHM 1/10W Panasonic - 79 1 R8 1.5K ERA-S15J152V 1500PPM 5%0805 ECG RES 1/10W 3K OHM 0.1% Stackpole 80 1 R2 3K RNC 20 T9 3K 0.1% R 0805 Electronics Inc CONN HEADER VERT SGL 81 1 J38 3p_jumper 3M 961103-6404-AR 3POS GOLD CONN HEADER VERT SGL 82 1 J37 2p_jumper 3M 961102-6404-AR 2POS GOLD 83 2 CSB1,CSB2 CapSense CapSense Button Cypress CapSense Linear 84 1 CSS1 CapSense Slider Cypress Slider 5 Seg J9, J13, J15, J17, J19, J20, J21, 85 11 PADS PADS J23, J24, J41, J42 86 2 TV1, TV2 PADS PADS Install On Bottom of PCB As Close To Corners As Possible 87 5 BUMPER CLEAR .500X.23" Richco Plastic RBS-3R SQUARE Co CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 54

Appendix Item Qty Reference Value Description Manufacturer Manufacturer Part No. Special Jumper Installation Instructions 88 1 J30 Install jumper Rectangular Connectors Kobiconn 151-8030-E across pins 1 MINI JUMPER GF 13.5 and 2 CLOSE TYPE BLACK 89 2 J10, J11 Install jumper Rectangular Connectors Kobiconn 151-8030-E across pins 1 MINI JUMPER GF 13.5 and 2 CLOSE TYPE BLACK External Assembly 90 2 Install 3.3V label 3.3V label as per assembly spec 91 2 4-40 X 5 +13 Spacer and nut for RS232 Brass Spacer Connector P7 Stud with Nut CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 55

Appendix A.4 Pin Assignment Table Port Pin Pin Name Description 71 P0[0] Connected to pin 18 on port E 72 P0[1] Connected to pin 17 on port E 1. Connected to pin 16 on port E 73 P0[2] 2. Connected to SAR bypass capacitor C54 that can be selected by shorting jumper J43 Connected to two points: 74 P0[3] 1. Voltage reference chip* Port 0 2. Connected to pin 15 on port E 1. Connected to pin 14 on port E 76 P0[4] 2. Connected to SAR bypass capacitor C55 that can be selected by shorting jumper J44 77 P0[5] Connected to pin 13 on port E 78 P0[6] Connected to pin 12 on port E 79 P0[7] Connected to pin 11 on port E Connected to three points: 1. Connected to pin 2 on programming header J3 20 P1[0] 2. Connected to pin 45 on U5 3. Connected to pin 8 (SWDIO) on port D Connected to three points: 1. Connected to pin 4 on programming header 21 P1[1] 2. Connected to pin 56 on U5 3. Connected to pin 7 (SWDCK) on port D 22 P1[2] Connected to pin 6 on port D Connected to three points: Port 1 1. Connected to pin 6 on programming header 23 P1[3] 2. Connected to pin 47 on U5 3. Connected to pin 5 (SWO) on port D Connected to two points: 24 P1[4] 1. Connected to pin 8 on programming header 2. Connected to pin 4 (TDI) on port D 25 P1[5] Connected to pin 3 on port D 27 P1[6] Connected to pin 2 on port D 28 P1[7] Connected to pin 1 on port D CY8CKIT-050 PSoC® 5LP Development Kit Guide, Doc. # 001-65816 Rev. *J 56