ICGOO在线商城 > ATSAMD20G14A-AUT

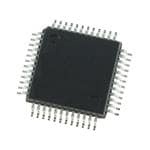

- 型号: ATSAMD20G14A-AUT

- 制造商: Atmel

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

ATSAMD20G14A-AUT产品简介:

ICGOO电子元器件商城为您提供ATSAMD20G14A-AUT由Atmel设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 提供ATSAMD20G14A-AUT价格参考以及AtmelATSAMD20G14A-AUT封装/规格参数等产品信息。 你可以下载ATSAMD20G14A-AUT参考资料、Datasheet数据手册功能说明书, 资料中有ATSAMD20G14A-AUT详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC) |

| 描述 | IC MCU 32BIT 16KB FLASH 48TQFP |

| EEPROM容量 | - |

| 产品分类 | |

| I/O数 | 38 |

| 品牌 | Atmel |

| 数据手册 | |

| 产品图片 |

|

| 产品型号 | ATSAMD20G14A-AUT |

| RAM容量 | 2K x 8 |

| rohs | 无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | SAM D20G |

| 产品培训模块 | http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=26162http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=26159http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=26180 |

| 供应商器件封装 | * |

| 其它名称 | ATSAMD20G14A-AUTDKR |

| 包装 | Digi-Reel® |

| 外设 | 欠压检测/复位,POR,WDT |

| 封装/外壳 | 48-TQFP |

| 工作温度 | -40°C ~ 85°C |

| 振荡器类型 | 内部 |

| 数据转换器 | A/D 14x12b, D/A 1x10b |

| 标准包装 | 1 |

| 核心处理器 | ARM® Cortex®-M0+ |

| 核心尺寸 | 32-位 |

| 电压-电源(Vcc/Vdd) | 1.62 V ~ 3.6 V |

| 程序存储器类型 | 闪存 |

| 程序存储容量 | 16KB(16K x 8) |

| 连接性 | I²C, SPI, UART/USART |

| 速度 | 48MHz |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

SMART ARM-Based Microcontrollers SAM D20E / SAM D20G / SAM D20J Summary DATASHEET SUMMARY Introduction Atmel® | SMART™ SAM D20 is a series of low-power microcontrollers using the 32-bit ARM® Cortex®-M0+ processor, and ranging from 32- to 64-pins with up to 256KB Flash and 32KB of SRAM. The SAM D20 devices operate at a maximum frequency of 48MHz and reach 2.46 CoreMark®/MHz. They are designed for simple and intuitive migration with identical peripheral modules, hex compatible code, identical linear address map and pin compatible migration paths between all devices in the product series. All devices include intelligent and flexible peripherals, Atmel Event System for inter-peripheral signaling, and support for capacitive touch button, slider and wheel user interfaces. Features • Processor – ARM Cortex-M0+ CPU running at up to 48MHz • Single-cycle hardware multiplier • Memories – 16/32/64/128/256KB in-system self-programmable Flash – 2/4/8/16/32KB SRAM Memory • System – Power-on reset (POR) and brown-out detection (BOD) – Internal and external clock options with 48MHz Digital Frequency Locked Loop (DFLL48M) – External Interrupt Controller (EIC) – 16 external interrupts – One non-maskable interrupt – Two-pin Serial Wire Debug (SWD) programming, test and debugging interface • Low Power – Idle and standby sleep modes This is a summary document. A – SleepWalking peripherals complete document is available on our Web site at • Peripherals www.atmel.com – 8-channel Event System Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

– Up to five 16-bit Timer/Counters (TC), configurable as either: • One 16-bit TC with two compare/capture channels • One 8-bit TC with two compare/capture channels • One 32-bit TC with two compare/capture channels, by using two TCs – 32-bit Real Time Counter (RTC) with clock/calendar function – Watchdog Timer (WDT) – CRC-32 generator – Up to six Serial Communication Interfaces (SERCOM), each configurable to operate as either: • USART with full-duplex and single-wire half-duplex configuration • Inter-Integrated Circuit (I2C) up to 400kHz • Serial Peripheral Interface (SPI) – One 12-bit, 350ksps Analog-to-Digital Converter (ADC) with up to 20 channels • Differential and single-ended input • 1/2x to 16x programmable gain stage • Automatic offset and gain error compensation • Oversampling and decimation in hardware to support 13-, 14-, 15- or 16-bit resolution – 10-bit, 350ksps Digital-to-Analog Converter (DAC) – Two Analog Comparators (AC) with window compare function – Peripheral Touch Controller (PTC) • 256-Channel capacitive touch and proximity sensing • I/O – Up to 52 programmable I/O pins • Packages – 64-pin TQFP, QFN – 64-ball UFBGA – 48-pin TQFP, QFN – 45-ball WLCSP – 32-pin TQFP, QFN • Operating Voltage – 1.62V – 3.63V • Power Consumption – Down to 70µA/MHz in active mode – Down to 8µA running the Peripheral Touch Controller Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 2 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Table of Contents Introduction......................................................................................................................1 Features..........................................................................................................................1 1. Description.................................................................................................................4 2. Configuration Summary.............................................................................................5 3. Ordering Information..................................................................................................6 3.1. SAM D20E....................................................................................................................................6 3.2. SAM D20G...................................................................................................................................8 3.3. SAM D20J....................................................................................................................................9 3.4. Device Identification....................................................................................................................11 4. Block Diagram.........................................................................................................13 5. Pinout.......................................................................................................................14 5.1. SAM D20J..................................................................................................................................14 5.2. SAM D20G.................................................................................................................................16 5.3. SAM D20E..................................................................................................................................18 6. Product Mapping......................................................................................................19 7. Processor And Architecture.....................................................................................20 7.1. Cortex M0+ Processor................................................................................................................20 7.2. Nested Vector Interrupt Controller..............................................................................................21 7.3. Micro Trace Buffer......................................................................................................................23 7.4. High-Speed Bus System............................................................................................................24 7.5. AHB-APB Bridge........................................................................................................................24 7.6. PAC - Peripheral Access Controller............................................................................................25 7.7. Register Description...................................................................................................................26 8. Packaging Information.............................................................................................39 8.1. Thermal Considerations.............................................................................................................39 8.2. Package Drawings......................................................................................................................40 8.3. Soldering Profile.........................................................................................................................50

1. Description The Atmel® | SMART™ SAM D20 is a series of low-power microcontrollers using the 32-bit ARM® Cortex®- M0+ processor, and ranging from 32- to 64-pins with up to 256KB Flash and 32KB of SRAM. The SAM D20 devices operate at a maximum frequency of 48MHz and reach 2.46 CoreMark/MHz. They are designed for simple and intuitive migration with identical peripheral modules, hex compatible code, identical linear address map and pin compatible migration paths between all devices in the product series. All devices include intelligent and flexible peripherals, Atmel Event System for inter-peripheral signaling, and support for capacitive touch button, slider and wheel user interfaces. The SAM D20 devices provide the following features: In-system programmable Flash, eight-channel Event System, programmable interrupt controller, up to 52 programmable I/O pins, 32-bit real-time clock and calendar, up to eight 16-bit Timer/Counters (TC) . The timer/counters can be configured to perform frequency and waveform generation, accurate program execution timing or input capture with time and frequency measurement of digital signals. The TCs can operate in 8- or 16-bit mode, selected TCs can be cascaded to form a 32-bit TC. The series provide up to six Serial Communication Modules (SERCOM) that each can be configured to act as an USART, UART, SPI, I2C up to 400kHz, up to twenty-channel 350ksps 12-bit ADC with programmable gain and optional oversampling and decimation supporting up to 16-bit resolution, one 10-bit 350ksps DAC, two analog comparators with window mode, Peripheral Touch Controller supporting up to 256 buttons, sliders, wheels and proximity sensing; programmable Watchdog Timer, brown-out detector and power-on reset and two-pin Serial Wire Debug (SWD) program and debug interface. All devices have accurate and low-power external and internal oscillators. All oscillators can be used as a source for the system clock. Different clock domains can be independently configured to run at different frequencies, enabling power saving by running each peripheral at its optimal clock frequency, and thus maintaining a high CPU frequency while reducing power consumption. The SAM D20 devices have two software-selectable sleep modes, idle and standby. In idle mode the CPU is stopped while all other functions can be kept running. In standby all clocks and functions are stopped expect those selected to continue running. The device supports SleepWalking. This feature allows the peripheral to wake up from sleep based on predefined conditions, and thus allows the CPU to wake up only when needed, e.g. when a threshold is crossed or a result is ready. The Event System supports synchronous and asynchronous events, allowing peripherals to receive, react to and send events even in standby mode. The Flash program memory can be reprogrammed in-system through the SWD interface. The same interface can be used for non-intrusive on-chip debug of application code. A boot loader running in the device can use any communication interface to download and upgrade the application program in the Flash memory. The SAM D20 devices are supported with a full suite of program and system development tools, including C compilers, macro assemblers, program debugger/simulators, programmers and evaluation kits. Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 4 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

2. Configuration Summary SAM D20J SAM D20G SAM D20E Pins 64 48 32 General Purpose I/O-pins (GPIOs) 52 38 26 Flash 256/128/64/32KB 256/128/64/32KB 256/128/64/32KB SRAM 32/16/8/4/2KB 32/16/8/4/2KB 32/16/8/4/2KB Timer Counter (TC) instances 8 6 6 Waveform output channels per TC instance 2 2 2 Serial Communication Interface (SERCOM) 6 6 4 instances Analog-to-Digital Converter (ADC) channels 20 14 10 Analog Comparators (AC) 2 2 2 Digital-to-Analog Converter (DAC) channels 1 1 1 Real-Time Counter (RTC) Yes Yes Yes RTC alarms 1 1 1 RTC compare values One 32-bit value or One 32-bit value or One 32-bit value or two 16-bit values two 16-bit values two 16-bit values External Interrupt lines 16 16 16 Peripheral Touch Controller (PTC) X and Y lines 16x16 12x10 10x6 Maximum CPU frequency 48MHz Packages QFN QFN QFN TQFP TQFP TQFP UFBGA WLCSP Oscillators 32.768kHz crystal oscillator (XOSC32K) 0.4-32MHz crystal oscillator (XOSC) 32.768kHz internal oscillator (OSC32K) 32KHz ultra-low-power internal oscillator (OSCULP32K) 8MHz high-accuracy internal oscillator (OSC8M) 48MHz Digital Frequency Locked Loop (DFLL48M) Event System channels 8 8 8 SW Debug Interface Yes Yes Yes Watchdog Timer (WDT) Yes Yes Yes Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 5 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

3. Ordering Information SSAAMMDD 2200 EE 1144 AA -- MM UU TT PPrroodduucctt FFaammiillyy PPaacckkaaggee CCaarrrriieerr SSAAMMDD == GGeenneerraall PPuurrppoossee MMiiccrrooccoonnttrroolllleerr NNoo cchhaarraacctteerr == TTrraayy ((DDeeffaauulltt)) TT == TTaappee aanndd RReeeell PPrroodduucctt SSeerriieess 2200 == CCoorrtteexx MM00++ CCPPUU,, BBaassiicc FFeeaattuurree SSeett PPaacckkaaggee GGrraaddee Pin Count UU == --4400 -- 8855CC MMaattttee SSnn PPllaattiinngg OO D = 25 Pins NN == --4400 -- 110055CC MMaattttee SSnn PPllaattiinngg OO E = 32 Pins G = 48 Pins PPaacckkaaggee TTyyppee J = 64 Pins FFllaasshh MMeemmoorryy DDeennssiittyy AA == TTQQFFPP 1188 == 225566KKBB MM == QQFFNN 1177 == 112288KKBB CC == UUFFBBGGAA 1166 == 6644KKBB UU == WWLLCCSSPP 1155 == 3322KKBB 1144 == 1166KKBB DDeevviiccee VVaarriiaanntt AA == DDeeffaauulltt VVaarriiaanntt 3.1. SAM D20E Ordering Code FLASH (bytes) SRAM (bytes) Package Carrier Type ATSAMD20E14A-AU 16K 2K TQFP32 Tray ATSAMD20E14A-AUT Tape & Reel ATSAMD20E14A-AN Tray ATSAMD20E14A-ANT Tape & Reel ATSAMD20E14A-MU QFN32 Tray ATSAMD20E14A-MUT Tape & Reel ATSAMD20E14A-MN Tray ATSAMD20E14A-MNT Tape & Reel Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 6 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Ordering Code FLASH (bytes) SRAM (bytes) Package Carrier Type ATSAMD20E15A-AU 32K 4K TQFP32 Tray ATSAMD20E15A-AUT Tape & Reel ATSAMD20E15A-AN Tray ATSAMD20E15A-ANT Tape & Reel ATSAMD20E15A-MU QFN32 Tray ATSAMD20E15A-MUT Tape & Reel ATSAMD20E15A-MN Tray ATSAMD20E15A-MNT Tape & Reel ATSAMD20E16A-AU 64K 8K TQFP32 Tray ATSAMD20E16A-AUT Tape & Reel ATSAMD20E16A-AN Tray ATSAMD20E16A-AFT Tape & Reel ATSAMD20E16A-MU QFN32 Tray ATSAMD20E16A-MUT Tape & Reel ATSAMD20E16A-MN Tray ATSAMD20E16A-MNT Tape & Reel ATSAMD20E17A-AU 128K 16K TQFP32 Tray ATSAMD20E17A-AUT Tape & Reel ATSAMD20E17A-AN Tray ATSAMD20E17A-ANT Tape & Reel ATSAMD20E17A-MU QFN32 Tray ATSAMD20E17A-MUT Tape & Reel ATSAMD20E17A-MN Tray ATSAMD20E17A-MNT Tape & Reel ATSAMD20E18A-AU 256K 32K TQFP32 Tray ATSAMD20E18A-AUT Tape & Reel ATSAMD20E18A-AN Tray ATSAMD20E18A-AFT Tape & Reel ATSAMD20E18A-MU QFN32 Tray ATSAMD20E18A-MUT Tape & Reel ATSAMD20E18A-MN Tray ATSAMD20E18A-MNT Tape & Reel Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 7 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

3.2. SAM D20G Ordering Code FLASH (bytes) SRAM (bytes) Package Carrier Type ATSAMD20G14A-AU 16K 2K TQFP32 Tray ATSAMD20G14A-AUT Tape & Reel ATSAMD20G14A-AN Tray ATSAMD20G14A-ANT Tape & Reel ATSAMD20G14A-MU QFN32 Tray ATSAMD20G14A-MUT Tape & Reel ATSAMD20G14A-MN Tray ATSAMD20G14A-MNT Tape & Reel ATSAMD20G15A-AU 32K 4K TQFP48 Tray ATSAMD20G15A-AUT Tape & Reel ATSAMD20G15A-AN Tray ATSAMD20G15A-ANT Tape & Reel ATSAMD20G15A-MU QFN48 Tray ATSAMD20G15A-MUT Tape & Reel ATSAMD20G15A-MN Tray ATSAMD20G15A-MNT Tape & Reel ATSAMD20G16A-AU 64K 8K TQFP48 Tray ATSAMD20G16A-AUT Tape & Reel ATSAMD20G16A-AN Tray ATSAMD20G16A-ANT Tape & Reel ATSAMD20G16A-MU QFN48 Tray ATSAMD20G16A-MUT Tape & Reel ATSAMD20G16A-MN Tray ATSAMD20G16A-MNT Tape & Reel Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 8 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Ordering Code FLASH (bytes) SRAM (bytes) Package Carrier Type ATSAMD20G17A-AU 128K 16K TQFP48 Tray ATSAMD20G17A-AUT Tape & Reel ATSAMD20G17A-AN Tray ATSAMD20G17A-ANT Tape & Reel ATSAMD20G17A-MU QFN48 Tray ATSAMD20G17A-MUT Tape & Reel ATSAMD20G17A-MN Tray ATSAMD20G17A-MNT Tape & Reel ATSAMD20G17A-UUT WLCSP45 Tape & Reel ATSAMD20G18A-AU 256K 32K TQFP48 Tray ATSAMD20G18A-AUT Tape & Reel ATSAMD20G18A-AN Tray ATSAMD20G18A-ANT Tape & Reel ATSAMD20G18A-MU QFN48 Tray ATSAMD20G18A-MUT Tape & Reel ATSAMD20G18A-MN Tray ATSAMD20G18A-MNT Tape & Reel ATSAMD20G18A-UUT WLCSP45 Tape & Reel 3.3. SAM D20J Ordering Code FLASH (bytes) SRAM (bytes) Package Carrier Type ATSAMD20J14A-AU 16K 2K TQFP64 Tray ATSAMD20J14A-AUT Tape & Reel ATSAMD20J14A-AN Tray ATSAMD20J14A-ANT Tape & Reel ATSAMD20J14A-MU QFN64 Tray ATSAMD20J14A-MUT Tape & Reel ATSAMD20J14A-MN Tray ATSAMD20J14A-MNT Tape & Reel Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 9 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Ordering Code FLASH (bytes) SRAM (bytes) Package Carrier Type ATSAMD20J15A-AU 32K 4K TQFP64 Tray ATSAMD20J15A-AUT Tape & Reel ATSAMD20J15A-AN Tray ATSAMD20J15A-ANT Tape & Reel ATSAMD20J15A-MU QFN64 Tray ATSAMD20J15A-MUT Tape & Reel ATSAMD20J15A-MN Tray ATSAMD20J15A-MNT Tape & Reel ATSAMD20J16A-AU 64K 8K TQFP64 Tray ATSAMD20J16A-AUT Tape & Reel ATSAMD20J16A-AN Tray ATSAMD20J16A-ANT Tape & Reel ATSAMD20J16A-MU QFN64 Tray ATSAMD20J16A-MUT Tape & Reel ATSAMD20J16A-MN Tray ATSAMD20J16A-MNT Tape & Reel ATSAMD20J16A-CU UFBGA64 Tray ATSAMD20J16A-CUT Tape & Reel ATSAMD20J17A-AU 128K 16K TQFP64 Tray ATSAMD20J17A-AUT Tape & Reel ATSAMD20J17A-AN Tray ATSAMD20J17A-ANT Tape & Reel ATSAMD20J17A-MU QFN64 Tray ATSAMD20J17A-MUT Tape & Reel ATSAMD20J17A-MN Tray ATSAMD20J17A-MNT Tape & Reel ATSAMD20J17A-CU UFBGA64 Tray ATSAMD20J17A-CUT Tape & Reel Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 10 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Ordering Code FLASH (bytes) SRAM (bytes) Package Carrier Type ATSAMD20J18A-AU 256K 32K TQFP64 Tray ATSAMD20J18A-AUT Tape & Reel ATSAMD20J18A-AN Tray ATSAMD20J18A-ANT Tape & Reel ATSAMD20J18A-MU QFN64 Tray ATSAMD20J18A-MUT Tape & Reel ATSAMD20J18A-MN Tray ATSAMD20J18A-MNT Tape & Reel ATSAMD20J18A-CU UFBGA64 Tray ATSAMD20J18A-CUT Tape & Reel 3.4. Device Identification The DSU - Device Service Unit peripheral provides the Device Selection bits in the Device Identification register (DID.DEVSEL) in order to identify the device by software. The device variants have a reset value of DID=0x1001drxx, with the LSB identifying the die number ('d'), the die revision ('r') and the device selection ('xx'). Table 3-1. Device Identification Values Device Variant DID.DEVSEL Device ID (DID) SAMD20J18C 0x00 0x10001300 SAMD20J18A 0x00 0x10001300 SAMD20J17A 0x01 0x10001301 SAMD20J16A 0x02 0x10001302 SAMD20J15A 0x03 0x10001303 SAMD20J14A 0x04 0x10001304 SAMD20G18A 0x05 0x10001305 SAMD20G17A 0x06 0x10001306 SAMD20G16A 0x07 0x10001307 SAMD20G15A 0x08 0x10001308 SAMD20G14A 0x09 0x10001309 SAMD20E18A 0x0A 0x1000130A SAMD20E17A 0x0B 0x1000130B SAMD20E16A 0x0C 0x1000130C SAMD20E15A 0x0D 0x1000130D Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 11 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Device Variant DID.DEVSEL Device ID (DID) SAMD20E14A 0x0E 0x1000130E Reserved 0x0F SAMD20G18U 0x10 0x10001310 SAMD20G17U 0x11 0x10001311 Reserved 0x12 - 0xFF Note: The device variant (last letter of the ordering number) is independent of the die revision (DSU.DID.REVISION): The device variant denotes functional differences, whereas the die revision marks evolution of the die. The device variant denotes functional differences, whereas the die revision marks evolution of the die. Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 12 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

4. Block Diagram IOBUS 256/128/64/32/16KB ARM CORTEX-M0+ NVM SWCLK SERIAL PROCESSOR NVM SWDIO WIRE Fmax 48MHz CONTROLLER Cache DEVICE SERVICE UNIT M M S 32/16/8/4/2KB RAM HIGH SPEED BUS MATRIX SRAM PERIPHERAL S CONTROLLER ACCESS CONTROLLER S S S AHB-APB AHB-APB AHB-APB BRIDGE B BRIDGE A BRIDGE C PERIPHERAL PERIPHERAL ACCESS CONTROLLER ACCESS CONTROLLER SYSTEM CONTROLLER ORT BOD33 VREF 6 6 x xS SEERRCCOOMM PIN[3:0] P OSCULP32K XIN32 XOUT32 XOSC32K OSC32K OSC8M M 8 x TIMER COUNTER WO[1:0] E 8 x Timer Counter XIN T (See Note1) XOUT XOSC DFLL48M YS S T POWER MANAGER EN AIN[19:0] EV ADC VREFA RT CLOCK VREFB PO CONTROLLER RESET SLEEP AIN[3:0] RESET CONTROLLER CONTROLLER 2 ANALOG COMPARATORS CMP1:0] GENERIC CLOCK GCLK_IO[7:0] CONTROLLER VOUT DAC REAL TIME VREFA COUNTER WATCHDOG PERIPHERAL X[15:0] TIMER TOUCH EXTINT[15:0] EXTERNAL INTERRUPT CONTROLLER Y[15:0] NMI CONTROLLER Note: 1. Some products have different number of SERCOM instances, Timer/Counter instances, PTC signals and ADC signals. Refer to Peripherals Configuration Summary for details. Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 13 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

5. Pinout 5.1. SAM D20J 5.1.1. QFN64 / TQFP64 E R O N T 0302010031303130DIDCD28SE272322 BBBBBBAADDNAEABB PPPPPPPPVVGPRPPP 4321098765432109 6666655555555554 48 VDDIO PA00 1 47 GND PA01 2 46 PA25 PA02 3 45 PA24 PA03 4 PB04 5 44 PA23 43 PA22 PB05 6 42 PA21 GNDANA 7 41 PA20 VDDANA 8 40 PB17 PB06 9 39 PB16 PB07 10 38 PA19 PB08 11 37 PA18 PB09 12 36 PA17 PA04 13 35 PA16 PA05 14 34 VDDIO PA06 15 33 GND PA07 16 7890123456789012 1112222222222333 8901OD0123452345 PA0PA0PA1PA1DDIGNPB1PB1PB1PB1PB1PB1PA1PA1PA1PA1 V DIGITAL PIN ANALOG PIN OSCILLATOR GROUND INPUT SUPPLY REGULATED OUTPUT SUPPLY RESET PIN Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 14 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

5.1.2. UFBGA64 Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 15 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

5.2. SAM D20G 5.2.1. QFN48 / TQFP48 E R O N T 03023130DIDCD28 SE272322 BBAADDNA EABB PPPPVVGP RPPP 876543210987 444444444333 PA00 1 36 VDDIO PA01 2 35 GND PA02 3 34 PA25 PA03 4 33 PA24 GNDANA 5 32 PA23 VDDANA 6 31 PA22 PB08 7 30 PA21 PB09 8 29 PA20 PA04 9 28 PA19 PA05 10 27 PA18 PA06 11 26 PA17 PA07 12 25 PA16 345678901234 111111122222 8901OD012345 0011IN111111 PAPAPAPADDGPBPBPAPAPAPA V DIGITAL PIN ANALOG PIN OSCILLATOR GROUND INPUT SUPPLY REGULATED OUTPUT SUPPLY RESET PIN Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 16 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

5.2.2. WLCSP45 A Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 17 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

5.3. SAM D20E 5.3.1. QFN32 / TQFP32 E R O N T 3130DIDCD28 SE27 AADDNA EA PPVVGP RP 21098765 33322222 PA00 1 24 PA25 PA01 2 23 PA24 PA02 3 22 PA23 PA03 4 21 PA22 PA04 5 20 PA19 PA05 6 19 PA18 PA06 7 18 PA17 PA07 8 17 PA16 90123456 1111111 AD890145 NN001111 DAGPAPAPAPAPAPA D DIGITAL PIN V ANALOG PIN OSCILLATOR GROUND INPUT SUPPLY REGULATED OUTPUT SUPPLY RESET PIN Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 18 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

6. Product Mapping Figure 6-1. Product Mapping Global Memory Space Code 0x00000000 0x00000000 Code Internal flash 0x20000000 0x00040000 Reserved SRAM 0x1FFFFFFF SRAM 0x20008000 0x20000000 Undefined AHB-APB Bridge C Internal SRAM 0x42000000 PAC2 0x40000000 0x20008000 0x42000400 Peripherals EVSYS Peripherals 0x42000800 0x43000000 0x40000000 SERCOM0 Reserved AHB-APB 0x42000C00 Bridge A SERCOM1 0x60000000 0x41000000 0x42001000 SERCOM2 AHB-APB Undefined Bridge B 0x42001400 SERCOM3 0x60000200 0x42000000 0x42001800 Reserved AHB-APB SERCOM4 0xE0000000 Bridge C 0x42001C00 0x42FFFFFF SERCOM5 System 0x42002000 0xFFFFFFFF TC0 System 0x42002400 0xE0000000 TC1 Reserved 0x42002800 0xE000E000 TC2 SCS 0x42002C00 0xE000F000 TC3 Reserved AHB-APB Bridge A 0x42003000 0xE00FF000 TC4 ROM Table 0x40000000 0x42003400 PAC0 0xE0100000 TC5 Reserved 0x40000400 0xFFFFFFFF 0x42003800 PM TC6 0x40000800 AHB-APB Bridge B 0x42003C00 SYSCTRL TC7 0x40000C00 0x41000000 0x42004000 GCLK PAC1 ADC 0x40001000 0x41002000 0x42004400 WDT DSU AC 0x40001400 0x41004000 0x42004800 RTC NVMCTRL DAC 0x40001800 0x41004400 0x42004C00 EIC PORT PTC 0x40001C00 0x41004800 0x42005000 Reserved Reserved Reserved 0x40FFFFFF 0x41FFFFFF 0x42FFFFFF This figure represents the full configuration of the SAM D20 device with maximum flash and SRAM capabilities and a full set of peripherals. Refer to the Configuration Summary for details. Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 19 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

7. Processor And Architecture 7.1. Cortex M0+ Processor The SAM D20 implements the ARM® Cortex®-M0+ processor, based on the ARMv6 Architecture and Thumb®-2 ISA. The Cortex M0+ is 100% instruction set compatible with its predecessor, the Cortex-M0 core, and upward compatible to Cortex-M3 and M4 cores. The ARM Cortex-M0+ implemented is revision r0p1. For more information refer to http://www.arm.com. 7.1.1. Cortex M0+ Configuration Table 7-1. Cortex M0+ Configuration Features Configurable option Device configuration Interrupts External interrupts 0-32 28 Data endianness Little-endian or big-endian Little-endian SysTick timer Present or absent Present Number of watchpoint comparators 0, 1, 2 2 Number of breakpoint comparators 0, 1, 2, 3, 4 4 Halting debug support Present or absent Present Multiplier Fast or small Fast (single cycle) Single-cycle I/O port Present or absent Present Wake-up interrupt controller Supported or not supported Not supported Vector Table Offset Register Present or absent Present Unprivileged/Privileged support Present or absent Absent(1) Memory Protection Unit Not present or 8-region Not present Reset all registers Present or absent Absent Instruction fetch width 16-bit only or mostly 32-bit 32-bit Note: 1. All software run in privileged mode only. The ARM Cortex-M0+ core has two bus interfaces: • Single 32-bit AMBA-3 AHB-Lite system interface that provides connections to peripherals and all system memory, which includes flash and RAM. • Single 32-bit I/O port bus interfacing to the PORT with 1-cycle loads and stores. 7.1.2. Cortex-M0+ Peripherals • System Control Space (SCS) – The processor provides debug through registers in the SCS. Refer to the Cortex-M0+ Technical Reference Manual for details (www.arm.com). • System Timer (SysTick) Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 20 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

– The System Timer is a 24-bit timer that extends the functionality of both the processor and the NVIC. Refer to the Cortex-M0+ Technical Reference Manual for details (www.arm.com). • Nested Vectored Interrupt Controller (NVIC) – External interrupt signals connect to the NVIC, and the NVIC prioritizes the interrupts. Software can set the priority of each interrupt. The NVIC and the Cortex-M0+ processor core are closely coupled, providing low latency interrupt processing and efficient processing of late arriving interrupts. Refer to Nested Vector Interrupt Controller and the Cortex-M0+ Technical Reference Manual for details (www.arm.com). • System Control Block (SCB) – The System Control Block provides system implementation information, and system control. This includes configuration, control, and reporting of the system exceptions. Refer to the Cortex-M0+ Devices Generic User Guide for details (www.arm.com). • Micro Trace Buffer (MTB) – The CoreSight MTB-M0+ (MTB) provides a simple execution trace capability to the Cortex- M0+ processor. Refer to section Micro Trace Buffer and the CoreSight MTB-M0+ Technical Reference Manual for details (www.arm.com). 7.1.3. Cortex-M0+ Address Map Table 7-2. Cortex-M0+ Address Map Address Peripheral 0xE000E000 System Control Space (SCS) 0xE000E010 System Timer (SysTick) 0xE000E100 Nested Vectored Interrupt Controller (NVIC) 0xE000ED00 System Control Block (SCB) 0x41006000 (see also Product Mapping) Micro Trace Buffer (MTB) 7.1.4. I/O Interface 7.1.4.1. Overview Because accesses to the AMBA® AHB-Lite™ and the single cycle I/O interface can be made concurrently, the Cortex-M0+ processor can fetch the next instructions while accessing the I/Os. This enables single cycle I/O accesses to be sustained for as long as needed. Refer to CPU Local Bus for more information. 7.1.4.2. Description Direct access to PORT registers. 7.2. Nested Vector Interrupt Controller 7.2.1. Overview The Nested Vectored Interrupt Controller (NVIC) in the SAM D20 supports 32 interrupt lines with four different priority levels. For more details, refer to the Cortex-M0+ Technical Reference Manual (www.arm.com). 7.2.2. Interrupt Line Mapping Each of the 28 interrupt lines is connected to one peripheral instance, as shown in the table below. Each peripheral can have one or more interrupt flags, located in the peripheral’s Interrupt Flag Status and Clear Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 21 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

(INTFLAG) register. The interrupt flag is set when the interrupt condition occurs. Each interrupt in the peripheral can be individually enabled by writing a one to the corresponding bit in the peripheral’s Interrupt Enable Set (INTENSET) register, and disabled by writing a one to the corresponding bit in the peripheral’s Interrupt Enable Clear (INTENCLR) register. An interrupt request is generated from the peripheral when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt requests for one peripheral are ORed together on system level, generating one interrupt request for each peripheral. An interrupt request will set the corresponding interrupt pending bit in the NVIC interrupt pending registers (SETPEND/CLRPEND bits in ISPR/ICPR). For the NVIC to activate the interrupt, it must be enabled in the NVIC interrupt enable register (SETENA/CLRENA bits in ISER/ICER). The NVIC interrupt priority registers IPR0-IPR7 provide a priority field for each interrupt. Table 7-3. Interrupt Line Mapping Peripheral Source NVIC Line EIC NMI – External Interrupt Controller NMI PM – Power Manager 0 SYSCTRL – System Control 1 WDT – Watchdog Timer 2 RTC – Real Time Counter 3 EIC – External Interrupt Controller 4 NVMCTRL – Non-Volatile Memory Controller 5 EVSYS – Event System 6 SERCOM0 – Serial Communication Interface 0 7 SERCOM1 – Serial Communication Interface 1 8 SERCOM2 – Serial Communication Interface 2 9 SERCOM3 – Serial Communication Interface 3 10 SERCOM4 – Serial Communication Interface 4 11 SERCOM5 – Serial Communication Interface 5 12 TC0 – Timer Counter 0 13 TC1 – Timer Counter 1 14 TC2 – Timer Counter 2 15 TC3 – Timer Counter 3 16 TC4 – Timer Counter 4 17 TC5 – Timer Counter 5 18 TC6 – Timer Counter 6 19 TC7 – Timer Counter 7 20 ADC – Analog-to-Digital Converter 21 AC – Analog Comparator 22 Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 22 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Peripheral Source NVIC Line DAC – Digital-to-Analog Converter 23 PTC – Peripheral Touch Controller 24 7.3. Micro Trace Buffer 7.3.1. Features • Program flow tracing for the Cortex-M0+ processor • MTB SRAM can be used for both trace and general purpose storage by the processor • The position and size of the trace buffer in SRAM is configurable by software • CoreSight compliant 7.3.2. Overview When enabled, the MTB records changes in program flow, reported by the Cortex-M0+ processor over the execution trace interface shared between the Cortex-M0+ processor and the CoreSight MTB-M0+. This information is stored as trace packets in the SRAM by the MTB. An off-chip debugger can extract the trace information using the Debug Access Port to read the trace information from the SRAM. The debugger can then reconstruct the program flow from this information. The MTB simultaneously stores trace information into the SRAM, and gives the processor access to the SRAM. The MTB ensures that trace write accesses have priority over processor accesses. The execution trace packet consists of a pair of 32-bit words that the MTB generates when it detects the processor PC value changes non-sequentially. A non-sequential PC change can occur during branch instructions or during exception entry. See the CoreSight MTB-M0+ Technical Reference Manual for more details on the MTB execution trace packet format. Tracing is enabled when the MASTER.EN bit in the Master Trace Control Register is 1. There are various ways to set the bit to 1 to start tracing, or to 0 to stop tracing. See the CoreSight Cortex-M0+ Technical Reference Manual for more details on the Trace start and stop and for a detailed description of the MTB’s MASTER register. The MTB can be programmed to stop tracing automatically when the memory fills to a specified watermark level or to start or stop tracing by writing directly to the MASTER.EN bit. If the watermark mechanism is not being used and the trace buffer overflows, then the buffer wraps around overwriting previous trace packets. The base address of the MTB registers is 0x41006000; this address is also written in the CoreSight ROM Table. The offset of each register from the base address is fixed and as defined by the CoreSight MTB- M0+ Technical Reference Manual. The MTB has 4 programmable registers to control the behavior of the trace features: • POSITION: Contains the trace write pointer and the wrap bit, • MASTER: Contains the main trace enable bit and other trace control fields, • FLOW: Contains the WATERMARK address and the AUTOSTOP and AUTOHALT control bits, • BASE: Indicates where the SRAM is located in the processor memory map. This register is provided to enable auto discovery of the MTB SRAM location, by a debug agent. See the CoreSight MTB-M0+ Technical Reference Manual for a detailed description of these registers. Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 23 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

7.4. High-Speed Bus System 7.4.1. Features High-Speed Bus Matrix has the following features: • Symmetric crossbar bus switch implementation • Allows concurrent accesses from different masters to different slaves • 32-bit data bus • Operation at a one-to-one clock frequency with the bus masters 7.4.2. Configuration Table 7-4. Bus Matrix Masters Bus Matrix Masters Master ID CM0+ - Cortex M0+ Processor 0 DSU - Device Service Unit 1 Table 7-5. Bus Matrix Slaves Bus Matrix Slaves Slave ID Internal Flash Memory 0 AHB-APB Bridge A 1 AHB-APB Bridge B 2 AHB-APB Bridge C 3 7.5. AHB-APB Bridge The AHB-APB bridge is an AHB slave, providing an interface between the high-speed AHB domain and the low-power APB domain. It is used to provide access to the programmable control registers of peripherals (see Product Mapping). AHB-APB bridge is based on AMBA APB Protocol Specification V2.0 (ref. as APB4) including: • Wait state support • Error reporting • Transaction protection • Sparse data transfer (byte, half-word and word) Additional enhancements: • Address and data cycles merged into a single cycle • Sparse data transfer also apply to read access to operate the AHB-APB bridge, the clock (CLK_HPBx_AHB) must be enabled. See PM – Power Manager for details. Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 24 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Figure 7-1. APB Write Access. T0 T1 T2 T3 T0 T1 T2 T3 T4 T5 PCLK PCLK PADDR Addr 1 PADDR Addr 1 PWRITE PWRITE PSEL PSEL PENABLE PENABLE PWDATA Data 1 PWDATA Data 1 PREADY PREADY No wait states Wait states Figure 7-2. APB Read Access. T0 T1 T2 T3 T0 T1 T2 T3 T4 T5 PCLK PCLK PADDR Addr 1 PADDR Addr 1 PWRITE PWRITE PSEL PSEL PENABLE PENABLE PRDATA Data 1 PRDATA Data 1 PREADY PREADY No wait states Wait states Related Links Product Mapping on page 19 7.6. PAC - Peripheral Access Controller 7.6.1. Overview There is one PAC associated with each AHB-APB bridge. The PAC can provide write protection for registers of each peripheral connected on the same bridge. The PAC peripheral bus clock (CLK_PACx_APB) can be enabled and disabled in the Power Manager. CLK_PAC0_APB and CLK_PAC1_APB are enabled are reset. CLK_PAC2_APB is disabled at reset. Refer to PM – Power Manager for details. The PAC will continue to operate in any sleep mode where the selected clock source is running. Write-protection does not apply for debugger access. When the debugger makes an access to a peripheral, write-protection is ignored so that the debugger can update the register. Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 25 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Write-protect registers allow the user to disable a selected peripheral’s write-protection without doing a read-modify-write operation. These registers are mapped into two I/O memory locations, one for clearing and one for setting the register bits. Writing a one to a bit in the Write Protect Clear register (WPCLR) will clear the corresponding bit in both registers (WPCLR and WPSET) and disable the write-protection for the corresponding peripheral, while writing a one to a bit in the Write Protect Set (WPSET) register will set the corresponding bit in both registers (WPCLR and WPSET) and enable the write-protection for the corresponding peripheral. Both registers (WPCLR and WPSET) will return the same value when read. If a peripheral is write-protected, and if a write access is performed, data will not be written, and the peripheral will return an access error (CPU exception). The PAC also offers a safety feature for correct program execution, with a CPU exception generated on double write-protection or double unprotection of a peripheral. If a peripheral n is write-protected and a write to one in WPSET[n] is detected, the PAC returns an error. This can be used to ensure that the application follows the intended program flow by always following a write-protect with an unprotect, and vice versa. However, in applications where a write-protected peripheral is used in several contexts, e.g., interrupts, care should be taken so that either the interrupt can not happen while the main application or other interrupt levels manipulate the write-protection status, or when the interrupt handler needs to unprotect the peripheral, based on the current protection status, by reading WPSET. 7.7. Register Description Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32- bit register, and the 8-bit halves of a 16-bit register can be accessed directly. Refer to the Product Mapping for PAC locations. Related Links Product Mapping on page 19 7.7.1. PAC0 Register Description Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 26 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

7.7.1.1. Write Protect Clear Name: WPCLR Offset: 0x00 Reset: 0x000000 Property:– Bit 31 30 29 28 27 26 25 24 Access Reset Bit 23 22 21 20 19 18 17 16 Access Reset Bit 15 14 13 12 11 10 9 8 Access Reset Bit 7 6 5 4 3 2 1 0 EIC RTC WDT GCLK SYSCTRL PM Access R/W R/W R/W R/W R/W R/W Reset 0 0 0 0 0 0 Bit 6 – EIC Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 5 – RTC Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 4 – WDT Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 27 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 3 – GCLK Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 2 – SYSCTRL Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 1 – PM Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 28 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

7.7.1.2. Write Protect Set Name: WPSET Offset: 0x04 Reset: 0x000000 Property:– Bit 31 30 29 28 27 26 25 24 Access Reset Bit 23 22 21 20 19 18 17 16 Access Reset Bit 15 14 13 12 11 10 9 8 Access Reset Bit 7 6 5 4 3 2 1 0 EIC RTC WDT GCLK SYSCTRL PM Access R/W R/W R/W R/W R/W R/W Reset 0 0 0 0 0 0 Bit 6 – EIC Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 5 – RTC Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 4 – WDT Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 29 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 3 – GCLK Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 2 – SYSCTRL Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 1 – PM Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. 7.7.2. PAC1 Register Description Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 30 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

7.7.2.1. Write Protect Clear Name: WPCLR Offset: 0x00 Reset: 0x000002 Property:– Bit 31 30 29 28 27 26 25 24 Access Reset Bit 23 22 21 20 19 18 17 16 Access Reset Bit 15 14 13 12 11 10 9 8 Access Reset Bit 7 6 5 4 3 2 1 0 MTB PORT NVMCTRL DSU Access R/W R/W R/W R/W Reset 0 0 0 1 Bit 6 – MTB Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 3 – PORT Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 2 – NVMCTRL Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 31 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 1 – DSU Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 32 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

7.7.2.2. Write Protect Set Name: WPSET Offset: 0x04 Reset: 0x000002 Property:– Bit 31 30 29 28 27 26 25 24 Access Reset Bit 23 22 21 20 19 18 17 16 Access Reset Bit 15 14 13 12 11 10 9 8 Access Reset Bit 7 6 5 4 3 2 1 0 MTB PORT NVMCTRL DSU Access R/W R/W R/W R/W Reset 0 0 0 1 Bit 6 – MTB Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 3 – PORT Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 2 – NVMCTRL Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 33 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 1 – DSU Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. 7.7.3. PAC2 Register Description Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 34 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

7.7.3.1. Write Protect Clear Name: WPCLR Offset: 0x00 Reset: 0x00800000 Property:– Bit 31 30 29 28 27 26 25 24 Access Reset Bit 23 22 21 20 19 18 17 16 PTC DAC AC ADC Access R/W R/W R/W R/W Reset 0 0 0 0 Bit 15 14 13 12 11 10 9 8 TC7 TC6 TC5 TC4 TC3 TC2 TC1 TC0 Access R/W R/W R/W R/W R/W R/W R/W R/W Reset 0 0 0 0 0 0 0 0 Bit 7 6 5 4 3 2 1 0 SERCOM5 SERCOM4 SERCOM3 SERCOM2 SERCOM1 SERCOM0 EVSYS Access R/W R/W R/W R/W R/W R/W R/W Reset 0 0 0 0 0 0 0 Bit 19 – PTC Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 18 – DAC Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 17 – AC Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 35 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 16 – ADC Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bits 15,14,13,12,11,10,9,8 – TCx Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bits 7,6,5,4,3,2 – SERCOMx Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 1 – EVSYS Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 36 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

7.7.3.2. Write Protect Set Name: WPSET Offset: 0x04 Reset: 0x00800000 Property:– Bit 31 30 29 28 27 26 25 24 Access Reset Bit 23 22 21 20 19 18 17 16 PTC DAC AC ADC Access R/W R/W R/W R/W Reset 0 0 0 0 Bit 15 14 13 12 11 10 9 8 TC7 TC6 TC5 TC4 TC3 TC2 TC1 TC0 Access R/W R/W R/W R/W R/W R/W R/W R/W Reset 0 0 0 0 0 0 0 0 Bit 7 6 5 4 3 2 1 0 SERCOM5 SERCOM4 SERCOM3 SERCOM2 SERCOM1 SERCOM0 EVSYS Access R/W R/W R/W R/W R/W R/W R/W Reset 0 0 0 0 0 0 0 Bit 19 – PTC Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 18 – DAC Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 17 – AC Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 37 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 16 – ADC Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bits 15,14,13,12,11,10,9,8 – TCx Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bits 7,6,5,4,3,2 – SERCOMx Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Bit 1 – EVSYS Writing a zero to these bits has no effect. Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals. Value Description 0 Write-protection is disabled. 1 Write-protection is enabled. Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 38 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

8. Packaging Information 8.1. Thermal Considerations Related Links Junction Temperature on page 39 8.1.1. Thermal Resistance Data The following table summarizes the thermal resistance data depending on the package. Table 8-1. Thermal Resistance Data Package Type θ θ JA JC 32-pin TQFP 68.0°C/W 25.8°C/W 48-pin TQFP 78.8°C/W 12.3°C/W 64-pin TQFP 66.7°C/W 11.9°C/W 32-pin QFN 37.2°C/W 13.1°C/W 48-pin QFN 33.0°C/W 11.4°C/W 64-pin QFN 33.5°C/W 11.2°C/W 64-ball UFBGA 67.4°C/W 12.4°C/W 45-ball WLCSP 37.0°C/W 0.36°C/W 8.1.2. Junction Temperature The average chip-junction temperature, T , in °C can be obtained from the following: J 1. T = T + (P x θ ) J A D JA 2. T = T + (P x (θ + θ )) J A D HEATSINK JC where: • θ = Package thermal resistance, Junction-to-ambient (°C/W), see Thermal Resistance Data JA • θ = Package thermal resistance, Junction-to-case thermal resistance (°C/W), see Thermal JC Resistance Data • θ = Thermal resistance (°C/W) specification of the external cooling device HEATSINK • P = Device power consumption (W) D • T = Ambient temperature (°C) A From the first equation, the user can derive the estimated lifetime of the chip and decide if a cooling device is necessary or not. If a cooling device is to be fitted on the chip, the second equation should be used to compute the resulting average chip-junction temperature T in °C. J Related Links Thermal Considerations on page 39 Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 39 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

8.2. Package Drawings 8.2.1. 64 pin TQFP Table 8-2. Device and Package Maximum Weight 300 mg Table 8-3. Package Characteristics Moisture Sensitivity Level MSL3 Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 40 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Table 8-4. Package Reference JEDEC Drawing Reference MS-026 JESD97 Classification E3 8.2.2. 64 pin QFN Note: The exposed die attach pad is not connected electrically inside the device. Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 41 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Table 8-5. Device and Package Maximum Weight 200 mg Table 8-6. Package Charateristics Moisture Sensitivity Level MSL3 Table 8-7. Package Reference JEDEC Drawing Reference MO-220 JESD97 Classification E3 8.2.3. 64-ball UFBGA Table 8-8. Device and Package Maximum Weight 27.4 mg Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 42 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Table 8-9. Package Characteristics Moisture Sensitivity Level MSL3 Table 8-10. Package Reference JEDEC Drawing Reference MO-220 JESD97 Classification E8 8.2.4. 48 pin TQFP Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 43 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Table 8-11. Device and Package Maximum Weight 140 mg Table 8-12. Package Characteristics Moisture Sensitivity Level MSL3 Table 8-13. Package Reference JEDEC Drawing Reference MS-026 JESD97 Classification E3 Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 44 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

8.2.5. 48 pin QFN Note: The exposed die attach pad is not connected electrically inside the device. Table 8-14. Device and Package Maximum Weight 140 mg Table 8-15. Package Characteristics Moisture Sensitivity Level MSL3 Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 45 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Table 8-16. Package Reference JEDEC Drawing Reference MO-220 JESD97 Classification E3 8.2.6. 45-ball WLCSP Table 8-17. Device and Package Maximum Weight 7.3 mg Table 8-18. Package Characteristics Moisture Sensitivity Level MSL1 Table 8-19. Package Reference JEDEC Drawing Reference MO-220 JESD97 Classification E1 Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 46 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

8.2.7. 32 pin TQFP Table 8-20. Device and Package Maximum Weight 100 mg Table 8-21. Package Charateristics Moisture Sensitivity Level MSL3 Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 47 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Table 8-22. Package Reference JEDEC Drawing Reference MS-026 JESD97 Classification E3 8.2.8. 32 pin QFN Note: The exposed die attach pad is connected inside the device to GND and GNDANA. Table 8-23. Device and Package Maximum Weight 90 mg Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 48 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Table 8-24. Package Characteristics Moisture Sensitivity Level MSL3 Table 8-25. Package Reference JEDEC Drawing Reference MO-220 JESD97 Classification E3 8.2.9. 35 ball WLCSP Table 8-26. Device and Package Maximum Weight 6.2 mg Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 49 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Table 8-27. Package Characteristics Moisture Sensitivity Level MSL1 Table 8-28. Package Reference JEDEC Drawing Reference MO-220 JESD97 Classification E1 8.3. Soldering Profile The following table gives the recommended soldering profile from J-STD-20. Table 8-29. Profile Feature Green Package Average Ramp-up Rate (217°C to peak) 3°C/s max. Preheat Temperature 175°C ±25°C 150-200°C Time Maintained Above 217°C 60-150s Time within 5°C of Actual Peak Temperature 30s Peak Temperature Range 260°C Ramp-down Rate 6°C/s max. Time 25°C to Peak Temperature 8 minutes max. A maximum of three reflow passes is allowed per component. Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 50 Atmel-42129P-SAM D20_Datasheet_Summary-09/2016

Atmel Corporation 1600 Technology Drive, San Jose, CA 95110 USA T: (+1)(408) 441.0311 F: (+1)(408) 436.4200 | www.atmel.com © 2016 Atmel Corporation. / Rev.: Atmel-42129P-SAM D20_Datasheet_Summary-09/2016 Atmel®, Atmel logo and combinations thereof, Enabling Unlimited Possibilities®, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. ARM®, ARM Connected® logo, and others are the registered trademarks or trademarks of ARM Ltd. Other terms and product names may be trademarks of others. DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life. SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death (“Safety-Critical Applications”) without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.

Mouser Electronics Authorized Distributor Click to View Pricing, Inventory, Delivery & Lifecycle Information: M icrochip: ATSAMD20G14A-MU ATSAMD20J15A-AU ATSAMD20E15A-AU ATSAMD20G18A-MU ATSAMD20E15A-MU ATSAMD20J14A-MU ATSAMD20G17A-MU ATSAMD20G15A-AU ATSAMD20J15A-MU ATSAMD20E17A-AU ATSAMD20E17A-MU ATSAMD20G16A-MU ATSAMD20J18A-MU ATSAMD20G14A-AU ATSAMD20E16A-MU ATSAMD20J17A-MU ATSAMD20J14A-AU ATSAMD20J18A-AU ATSAMD20G15A-MU ATSAMD20G17A-AU ATSAMD20E14A-AU ATSAMD20E14A-MU ATSAMD20E16A-AU ATSAMD20G16A-AU ATSAMD20J16A-MU ATSAMD20J16A-AU ATSAMD20G18A-AU ATSAMD20G17A-AUT ATSAMD20G14A-MUT ATSAMD20G15A-MUT ATSAMD20J14A-MUT ATSAMD20E14A-MUT ATSAMD20J15A-MUT ATSAMD20G18A-MUT ATSAMD20J15A-AUT ATSAMD20J17A-MUT ATSAMD20E15A-MUT ATSAMD20E15A-AUT ATSAMD20G16A-AUT ATSAMD20J18A-AUT ATSAMD20J18A-MUT ATSAMD20E16A-MUT ATSAMD20G15A-AUT ATSAMD20J17A-AUT ATSAMD20G14A-AUT ATSAMD20J14A-AUT ATSAMD20G16A-MUT ATSAMD20J16A-MUT ATSAMD20E17A-AUT ATSAMD20G18A-AUT ATSAMD20G17A-MUT ATSAMD20E14A-AUT ATSAMD20E16A-AUT ATSAMD20E17A-MUT ATSAMD20J16A-AUT ATSAMD20J15B-AU ATSAMD20E14B-MUT ATSAMD20G16B-MNT ATSAMD20J15B-MUT ATSAMD20G16B-ANT ATSAMD20E14B-MU ATSAMD20J16B-MUT ATSAMD20E15B-AU ATSAMD20G14B-AU ATSAMD20E15B-MUT ATSAMD20G15B-AUT ATSAMD20E16B-MNT ATSAMD20G14B-MU ATSAMD20G14B-AUT ATSAMD20E16B-AU ATSAMD20G14B-MUT ATSAMD20E14B-AUT ATSAMD20J16B-MNT ATSAMD20J14B-MUT ATSAMD20J14B-MU ATSAMD20J16B-MN ATSAMD20G16B-AU ATSAMD20G16B-MN ATSAMD20G16B-AN ATSAMD20G15B-MU ATSAMD20J16B-AN ATSAMD20G16B-AUT ATSAMD20G16B-MU ATSAMD20J14B-AUT ATSAMD20G15B-AU ATSAMD20E14B-AU ATSAMD20E16B-MUT ATSAMD20E16B-AN ATSAMD20J15B-AUT ATSAMD20J16B-AU ATSAMD20E16B-AUT ATSAMD20E16B-MU ATSAMD20J14B-AU ATSAMD20J16B-MU ATSAMD20J15B-MU ATSAMD20G15B-MUT ATSAMD20E16B-ANT ATSAMD20G16B-MUT ATSAMD20E15B-AUT ATSAMD20J16B-AUT

Datasheet下载

Datasheet下载