ICGOO在线商城 > 集成电路(IC) > 嵌入式 - CPLD(复杂可编程逻辑器件) > ATF1500A-10JU

- 型号: ATF1500A-10JU

- 制造商: Atmel

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

ATF1500A-10JU产品简介:

ICGOO电子元器件商城为您提供ATF1500A-10JU由Atmel设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 ATF1500A-10JU价格参考。AtmelATF1500A-10JU封装/规格:嵌入式 - CPLD(复杂可编程逻辑器件), 。您可以下载ATF1500A-10JU参考资料、Datasheet数据手册功能说明书,资料中有ATF1500A-10JU 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC)半导体 |

| 描述 | IC CPLD 32MC 10NS 44PLCCCPLD - 复杂可编程逻辑器件 CPLD 32 MACROCELL CMPTBLE w/F1500 |

| 产品分类 | |

| I/O数 | 32 |

| 品牌 | Atmel |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 嵌入式处理器和控制器,CPLD - 复杂可编程逻辑器件,Atmel ATF1500A-10JUATF15xx |

| 数据手册 | |

| 产品型号 | ATF1500A-10JU |

| 产品 | ATF1500A |

| 产品种类 | CPLD - 复杂可编程逻辑器件 |

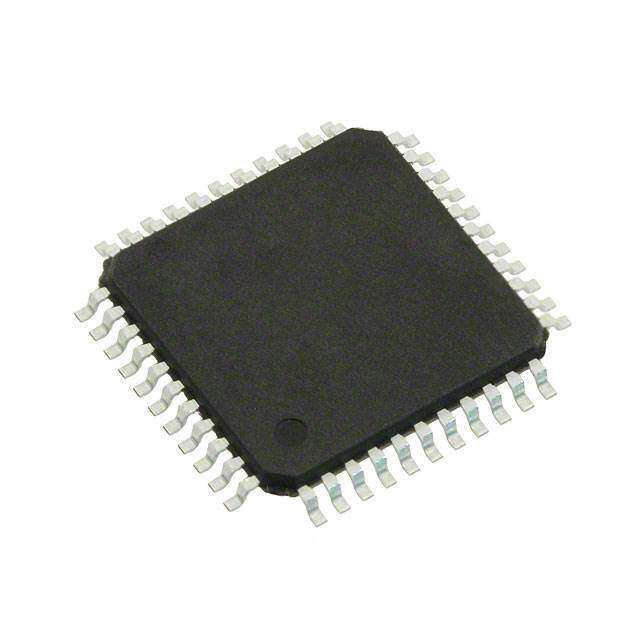

| 供应商器件封装 | 44-PLCC |

| 其它名称 | ATF1500A10JU |

| 包装 | 管件 |

| 可编程类型 | 系统内可编程(最少 100 次编程/擦除循环) |

| 商标 | Atmel |

| 大电池数量 | 32 |

| 存储类型 | Flash |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 宏单元数 | 32 |

| 封装/外壳 | 44-LCC(J 形引线) |

| 封装/箱体 | PLCC-44 |

| 工作温度 | -40°C ~ 85°C |

| 工作电源电压 | 5 V |

| 工厂包装数量 | 27 |

| 延迟时间 | 10 ns |

| 延迟时间tpd(1)最大值 | 10.0ns |

| 最大工作温度 | + 85 C |

| 最大工作频率 | 125 MHz |

| 最小工作温度 | - 40 C |

| 栅极数 | - |

| 栅极数量 | 1000 |

| 标准包装 | 27 |

| 每个宏指令的积项数 | 40 |

| 电源电压-内部 | 4.5 V ~ 5.5 V |

| 电源电压-最大 | 5.5 V |

| 电源电压-最小 | 4.5 V |

| 输入/输出端数量 | 32 |

| 逻辑元件/块数 | - |

| 逻辑数组块数量——LAB | - |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

Features • High-density, High-performance Electrically-erasable Complex Programmable Logic Device – 44-pin, 32 I/O CPLD – 7.5 ns Maximum Pin-to-pin Delay – Registered Operation Up to 125 MHz – Fully Connected Input and Feedback Logic Array – Backward Compatibility with ATF1500/L Software and Hardware (cid:127) Flexible Logic Macrocell – D/T/Latch Configurable Flip-flops – Global and Individual Register Control Signals High- – Global and Individual Output Enable – Programmable Output Slew Rate performance (cid:127) Advanced Power Management Features – Automatic 3 mA Standby (ATF1500AL) EPLD – Pin-controlled 10 mA Standby Mode – Programmable Pin-keeper Inputs and I/Os (cid:127) Available in Commercial and Industrial Temperature Ranges (cid:127) Available in 44-lead PLCC and TQFP Packages ATF1500A (cid:127) Advanced Flash Technology – 100% Tested ATF1500AL – Completely Reprogrammable – 100 Program/Erase Cycles – 20 Year Data Retention – 2000V ESD Protection – 200 mA Latch-up Immunity (cid:127) Supported by Popular third-arty Tools (cid:127) Security Fuse Feature (cid:127) Pin-compatible with the Most Commonly Used Devices (cid:127) Green (Pb/Halide-fee/RoHS Compliant) Package Options Description The ATF1500A is a high-performance, high-density complex PLD. Built on an advanced Flash technology, it has maximum pin-to-pin delays of 7.5 ns and supports sequential logic operation at speeds up to 125 MHz. With 32 logic macrocells and up to 36 inputs, it easily integrates logic from several TTL, SSI, MSI and classic PLDs. The ATF1500A’s global input and feedback architecture simplifies logic placement and eliminates pinout changes due to design changes. Pin Configurations (continued) Pin PLCC TQFP Name Function Top View Top View CLK Clock I Logic Inputs I/OI/OI/O/PDVCCOE2/IGCLR/IOE1/ICLK/IGNDI/OI/O I/OI/OI/O/PDVCCOE2/IGCLR/IOE1/ICLK/IGNDI/OI/O I/O BBui-fdfeirresctional I/O 7654321444342414039 I/O I/O 1 4443424140393837363534 33 I/O I/O 8 38 I/O I/O 2 32 I/O I/O 9 37 I/O I/O 3 31 I/O Register Reset GND 10 36 I/O GND 4 30 I/O GCLR (active low) II//OO 1112 3354 VI/OCC II//OO 56 2298 VI/OCC I/O 13 33 I/O I/O 7 27 I/O OE1, Output Enable I/O 14 32 I/O I/O 8 26 I/O VCC 15 31 I/O VCC 9 25 I/O OE2 (active low) I/O 16 30 GND I/O 10 24 GND VCC +5V Supply I/O 17181920212223242526272829 I/O I/O 11 23 I/O OOOODCOOOOO 1213141516171819202122 PD Power-down I/I/I/I/GNVCI/I/I/I/I/ I/OI/OI/OI/OGNDVCCI/OI/OI/OI/OI/O Rev. 0759F–6/05 (active high) 1

Functional Logic Diagram(1) Note: 1. Arrows connecting macrocells indicate direction and groupings of CASIN/CASOUT data flow. The ATF1500A has 32 bi-directional I/O pins and four dedi- Each of the 32 logic macrocells generates a buried feed- cated input pins. Each dedicated input pin can also serve back, which goes to the global bus. Each input and I/O pin as a global control signal: register clock, register reset or also feeds into the global bus. Because of this global bus- output enable. Each of these control signals can be ing, each of these signals is always available to all 32 mac- selected for use individually within each macrocell. rocells in the device. ATF1500A(L) 2

ATF1500A(L) Each macrocell also generates a foldback logic term, which Each output also has individual slew rate control. This may goes to a regional bus. All signals within a regional bus are be used to reduce system noise by slowing down outputs connected to all 16 macrocells within the region. that do not need to operate at maximum speed. Outputs Cascade logic between macrocells in the ATF1500A allows default to slow switching, and may be specified as fast fast, efficient generation of complex logic functions. The switching in the design file. ATF1500A contains four such logic chains, each capable of creating sum term logic with a fan-in of up to 40 product Design Software Support terms. ATF1500A designs are supported by several third-party tools. Automated fitters allow logic synthesis using a variety Bus-friendly Pin-keeper Input and I/O’s of high-level description languages and formats. All Input and I/O pins on the ATF1500A have programma- ble “pin-keeper” circuits. If activated, when any pin is driven Input Diagram high or low and then subsequently left floating, it will stay at that previous high or low level. V CC This circuitry prevents unused Input and I/O lines from floating to intermediate voltage levels, which causes unnecessary power consumption and system noise. The keeper circuits eliminate the need for external pull-up resis- INPUT tors and eliminate their DC power consumption. 100K Pin-keeper circuits can be disabled. Programming is con- trolled in the logic design file. Once the pin-keeper circuits ESD PROTECTION are disabled, normal termination procedures are required CIRCUIT PROGRAMMABLE for unused inputs and I/Os. OPTION I/O Diagram Speed/Power Management The ATF1500A has several built-in speed and power man- V CC agement features. The ATF1500A contains circuitry that automatically puts the device into a low-power standby OE mode when no logic transitions are occurring. This not only reduces power consumption during inactive periods, but DATA I/O also provides proportional power savings for most applica- tions running at system speeds below 10 MHz. V All ATF1500As also have an optional pin-controlled power- CC down mode. In this mode, current drops to below 10 mA. When the power-down option is selected, the PD pin is used to power-down the part. The power-down option is selected in the design source file. When enabled, the 100K device goes into power-down when the PD pin is high. In the power-down mode, all internal logic signals are latched and held, as are any enabled outputs. All pin transitions are ignored until the PD is brought low. When the power-down PROGRAMMABLE OPTION feature is enabled, the PD cannot be used as a logic input or output. However, the PD pin’s macrocell may still be used to generate buried foldback and cascade logicsignals. 3

ATF1500A(L) Macrocell ATF1500A Macrocell The ATF1500A macrocell is flexible enough to support routed to the OR gate, creating a five input AND/OR sum highly-complex logic functions operating at high speed. The term. With the addition of the CASIN from neighboring macrocell consists of five sections: product terms and prod- macrocells, this can be expanded to as many as 40 product uct term select multiplexer, OR/XOR/CASCADE logic, a terms with little small additional delay. flip-flop, output select and enable, and logic array inputs. The macrocell’s XOR gate allows efficient implementation Product Terms and Select Mux of compare and arithmetic functions. One input to the XOR comes from the OR sum term. The other XOR input can be Each ATF1500A macrocell has five product terms. Each a product term or a fixed high or low level. For combinato- product term receives as its inputs all signals from both the rial outputs, the fixed level input allows output polarity global bus and regional bus. selection. For registered functions, the fixed levels allow De The product term select multiplexer (PTMUX) allocates the Morgan minimization of the product terms. The XOR gate is five product terms as needed to the macrocell logic gates also used to emulate T-type flip-flops. and control signals. The PTMUX programming is deter- mined by the design compiler that selects the optimum Flip-flop macrocell configuration. The ATF1500A’s flip-flop has very flexible data and control functions. The data input can come from either the XOR OR/XOR/CASCADE Logic gate or from a separate product term. Selecting the sepa- The ATF1500A macrocell’s OR/XOR/CASCADE logic rate product term allows creation of a buried registered structure is designed to efficiently support all types of logic. feedback within a combinatorial output macrocell. Within a single macrocell, all the product terms can be ATF1500A(L) 4

ATF1500A(L) In addition to D, T, JK and SR operation, the flip-flop can The output enable multiplexer (MOE) controls the output also be configured as a flow-through latch. In this mode, enable signals. Any buffer can be permanently enabled for data passes through when the clock is high and is latched simple output operation. Buffers can also be permanently when the clock is low. disabled to allow use of the pin as an input. In this configu- The clock itself can be either the global CLK pin or an indi- ration all the macrocell resources are still available, includ- vidual product term. The flip-flop changes state on the ing the buried feedback, expander and CASCADE logic. clock’s rising edge. When the CLK pin is used as the clock, The output enable for each macrocell can also be selected one of the macrocell product terms can be selected as a as either of the two OE pins or as an individual product clock enable. When the clock enable function is active and term. the enable signal (product term) is low, all clock edges are Global/Regional Busses ignored. The global bus contains all Input and I/O pin signals as well The flip-flop’s asynchronous reset signal (AR) can be either as the buried feedback signal from all 32 macrocells. the pin global clear (GCLR), a product term, or always off. Together with the complement of each signal, this provides AR can also be a logic OR of GCLR with a product term. a 68-bit bus as input to every product term. Having the The asynchronous preset (AP) can be a product term or entire global bus available to each macrocell eliminates always off. any potential routing problems. With this architecture Output Select and Enable designs can be modified without requiring pinout changes. The ATF1500A macrocell output can be selected as regis- Each macrocell also generates a foldback product term. tered or combinatorial. When the output is registered, the This signal goes to the regional bus, and is available to 16 same registered signal is fed back internally to the global macrocells. The foldback is an inverse polarity of one of the bus. When the output is combinatorial, the buried feedback macrocell’s product terms. The 16 foldback terms in each can be either the same combinatorial signal or it can be the region allow generation of high fan-in sum terms (up to 21 register output if the separate product term is chosen as product terms) with little additional delay. the flip-flop input. 5

Absolute Maximum Ratings* Temperature Under Bias..................................-40°C to +85°C *NOTICE: Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent dam- Storage Temperature.....................................-65°C to +150°C age to the device. This is a stress rating only and functional operation of the device at these or any Voltage on Any Pin with other conditions beyond those indicated in the Respect to Ground.........................................-2.0V to +7.0V(1) operational sections of this specification is not implied. Exposure to absolute maximum rating Voltage on Input Pins conditions for extended periods may affect device with Respect to Ground reliability. During Programming.....................................-2.0V to +14.0V(1) Note: 1. Minimum voltage is -0.6V DC, which may under- shoot to -2.0V for pulses of less than 20 ns. Max- Programming Voltage with imum output pin voltage is V + 0.75V DC, CC Respect to Ground.......................................-2.0V to +14.0V(1) which may overshoot to 5.25V for pulses of less than 20 ns. DC and AC Operating Conditions Commercial Industrial Operating Temperature (ambient) 0°C - 70°C -40°C - 85°C V Power Supply 5V ± 5% 5V ± 10% CC DC Characteristics Symbol Parameter Condition Min Typ Max Units Input or I/O I 0 ≤ V ≤ V (Max) -10 µA IL Low Leakage Current IN IL Input or I/O I V , Min ≤ V ≤ V 10 µA IH High Leakage Current IH IN CC Com. 70 mA ATF1500A Power Supply Current, V = Max, Ind. 100 mA I (1) CC CC1 Standby VIN = 0, VCC Com. 3 mA ATF1500AL Ind. 5 mA Power Supply Current, V = Max, I Pin-Controlled Power CC 2 10 mA CC2 V = 0, V Down Mode IN CC Output Short Circuit I V = 0.5V -130 mA OS Current OUT V , Min < V V Input Low Voltage CC CC -0.5 0.8 V IL < V , Max CC V Input High Voltage 2.0 V + 1 V IH CC V Output Low Voltage V = Min I = 12 mA 0.45 V OL CC OL I = -4 mA 2.4 V OH V Output High Voltage V = Min OH CC I = -0.2 mA V - 0.2 V OH CC Note: 1. All I parameters measured with outputs open, and a 16-bit loadable, up/down counter programmed into each region. CC ATF1500A(L) 6

ATF1500A(L) AC Waveforms Register AC Characteristics, Input Pin Clock -7 -10 -12 -15 -20 -25 Symbol Parameter Min Max Min Max Min Max Min Max Min Max Min Max Units t (1) Clock to Output 4.5 2 5 2 6 2 8 2 9 2 9 ns COS t Clock to Feedback 2 2 2 2 2 2 ns CFS t I, I/O Setup Time 6 8 10 11 14 16 ns SIS Feedback Setup t 6 8 10 11 12 13 ns SFS Time Input, I/O, Feedback t 0 0 0 0 0 0 ns HS Hold Time t Clock Period 6 8 9 10 11 12 ns PS t Clock Width 3 4 4.5 5 5.5 6 ns WS External Feedback 95 76.9 62.5 52.6 43 40 MHz 1/(t + t ) SIS COS f Internal Feedback MAXS 125 100 83.3 76.9 71 66 MHz 1/(t + t ) SFS CFS No Feedback 1/(t ) 166.7 125 111 100 91 83 MHz PS Reset Pin Recovery t 2 3 3 4 5 5 ns RPRS Time Reset Term t 6 9 10 12 13 14 ns RTRS Recovery Time Note: 1. For slow slew outputs, add t . SSO 7

Register AC Characteristics, Product Term Clock -7 -10 -12 -15 -20 -25 Symbol Parameter Min Max Min Max Min Max Min Max Min Max Min Max Units t (1) Clock to Output 7.5 10 12 15 18 20 ns COA t Clock to Feedback 5 7 7 9 12 15 ns CFA t I, I/O Setup Time 3 3 4 4 8 10 ns SIA Feedback Setup t 3 3 4 4 12 15 ns SFA Time Input, I/O, Feedback t 2 3 4 4 5 5 ns HA Hold Time t Clock Period 6 8 10 12 24 30 ns PA t Clock Width 3 4 5 6 12 15 ns WA External Feedback 95.2 76.9 62.5 52.6 38 33.3 MHz 1/(t + t ) SIA COA f Internal Feedback MAXA 125 100 90.9 76.9 41.7 33.3 MHz 1/(t + t ) SFA CFA No Feedback 1/(t ) 166.7 125 100 83.3 41.7 33.3 MHz PA Reset Pin Recovery t 0 0 0 0 0 0 ns RPRA Time Reset Term t 4 5 6 6 7 8 ns RTRA Recovery Time Note: 1. For slow slew outputs, add t . SSO ATF1500A(L) 8

ATF1500A(L) AC Characteristics -7 -10 -12 -15 -20 -25 Symbol Parameter Min Max Min Max Min Max Min Max Min Max Min Max Units I, I/O or FB to t (1) Non-Registered 2 7.5 3 10 3 12 3 15 3 20 3 25 ns PD Output t I, I/O to Feedback 5 7 8 9 12 14 ns PD2 Feedback to t (1) Non-Registered 2 7.5 3 10 3 12 3 15 3 20 3 25 ns PD3 Output Feedback to t 5 7 8 9 12 14 ns PD4 Feedback OE Term to Output t (1) 2 7.5 3 10 3 12 3 15 3 20 3 25 ns EA Enable OE Term to Output t 2 7.5 2 10 2 12 2 15 2 20 2 25 ns ER Disable OE Pin to Output t (1) 2 5.5 2 7 2 8 2 9 2 10 2 11 ns PZX Enable OE Pin to Output t 1.5 5.5 1..5 7 1.5 8 1.5 9 1.5 10 1.5 11 ns PXZ Disable t Preset to Feedback 6 9 9 12 18 20 ns PF Preset to Registered t (1) 8.5 12 14 20 23 25 ns PO Output Reset Pin to t 3 4 3 5 5.5 6 ns RPF Feedback Reset Pin to t (1) 5.5 7 8 11 13 15 ns RPO Registered Output Reset Term to t 6 9 9 12 15 20 ns RTF Feedback Reset Term to t (1) 8.5 12 14 20 23 25 ns RTO Registered Output t Cascade Logic Delay 0.8 0.8 1 1 1.5 1.5 ns CAS Slow Slew Output t 3 3 3 4 4 4 ns SSO Adder t Foldback Term Delay 4 5 7 8 10 12 ns FLD Note: 1. For slow slew outputs, add t . SSO 9

Power Down AC Characteristics -7 -10 -12 -15 -20 -25 Symbol Parameter Min Max Min Max Min Max Min Max Min Max Min Max Units Valid I, I/O Before t 7 10 12 15 20 25 ns IVDH PD High Valid OE(2) t 7 10 12 15 20 25 ns GVDH Before PD High Valid Clock(2) t 7 10 12 15 20 25 ns CVDH Before PD High Input Don't Care t 15 20 22 25 30 35 ns DHIX After PD High OE Don't Care t 15 20 22 25 30 35 ns DHGX After PD High Clock Don't Care t 15 20 22 25 30 35 ns DHCX After PD High PD Low to Valid I, t 1 1 1 1 1 1 µs DLIV I/O PD Low to Valid t 1 1 1 1 1 1 µs DLGV OE(2) PD Low to Valid t 1 1 1 1 1 1 µs DLCV Clock(2) PD Low to Valid t (1) 1 1 1 1 1 1 µs DLOV Output Notes: 1. For slow slew outputs, add t . SSO 2. Pin or Product Term. Input Test Waveforms and Output Test Load Measurement Levels 3.0V AC AC DRIVING 1.5V MEASUREMENT LEVELS LEVEL 0.0V tr, tf ≤ 1.5 ns Pin Capacitance f = 1 MHz, T = 25°C(1) Typ Max Units Conditions C 4.5 5.5 pF V = 0V IN IN C 3.5 4.5 pF V = 0V OUT OUT Note: 1. Typical values for nominal supply voltage. This parameter is only sampled and is not 100% tested. ATF1500A(L) 10

ATF1500A(L) Power-up Reset when vectors are run by any approved programmers. The preload mode is enabled by raising an input pin to a high The ATF1500A’s registers are designed to reset during voltage level. Contact Atmel PLD Applications for PRE- power-up. At a point delayed slightly from V crossing CC LOAD pin assignments, timing and voltage requirements. V , all registers will be reset to the low state. As a result, RST the registered output state will always be low on power-up. This feature is critical for state machine initialization. How- ever, due to the asynchronous nature of reset and the uncertainty of how V actually rises in the system, the fol- CC lowing conditions are required: 1. The V rise must be monotonic, from below 0.7 volt, CC 2. After reset occurs, all input and feedback setup times must be met before driving the clock signal high, and 3. Signals from which clocks are derived must remain sta- ble during t . PR Power-down Mode The ATF1500A includes an optional pin-controlled power- Parameter Description Typ Max Units down feature. When this mode is enabled, the PD pin acts as the power down pin. When the PD pin is high, the device t Power-up 2 10 µs supply current is reduced to less than 10 mA. During PR Reset Time power-down, all output data and internal logic states are Power-up latched and held. Therefore, all registered and combinato- V Reset 3.8 4.5 V RST rial output data remain valid. Any outputs that were in a Voltage high-Z state at the onset of power-down will remain at high-Z. During power-down, all input signals except the Output Slew Rate Control power-down pin are blocked. Input and I/O hold latches remain active to ensure that pins do not float to indetermi- Each ATF1500A macrocell contains a configuration bit for nate levels, further reducing system power. The power- each I/O to control its output slew rate. This allows selected down pin feature is enabled in the logic design file. Designs data paths to operate at maximum throughput while reduc- using the power-down pin may not use the PD pin logic ing system noise from outputs that are not speed-critical. array input. However, all other PD pin macrocell resources Outputs default to slow edges, and may be individually set may still be used, including the buried feedback and fold- to fast in the design file. Output transition times for outputs back product term array inputs. configured as “slow” have a t delay adder. SSO Register Preload Security Fuse Usage The ATF1500A’s registers are provided with circuitry to A single fuse is provided to prevent unauthorized copying allow loading of each register with either a high or a low. of the ATF1500A fuse patterns. Once programmed, fuse This feature will simplify testing since any state can be verify and preload are prohibited. However, the 160-bit forced into the registers to control test sequencing. A User Signature remains accessible. JEDEC file with preload is generated when a source file The security fuse should be programmed last, as its effect with preload vectors is compiled. Once downloaded, the is immediate. JEDEC file preload sequence will be done automatically 11

NORMALIZED SUPPLY CURRENT SUPPLY CURRENT vs. INPUT FREQUENCY vs. FREQUENCY ATF1500A (Vcc = 5V, TA = 25˚C) ATF1500AL (VCC = 5V, TA = 25˚C) ICC ICC mA NORMALIZED SUPPLY CURRENT vs. SUPPLY VOLTAGE NORMALIZED SUPPLY CURRENT ATF1500 (TA = 25˚C) vs. AMBIENT TEMPERATURE ATF1500 (V = 5V) CC I CC I mA CC OUTPUT SOURCE CURRENT vs. SUPPLY VOLTAGE (V = 2.4V, TA = 25˚C) OUTPUT SINK SURRENT OH vs. SUPPLY VOLTAGE (TA = 25˚C, V = 0.45V) OL I OH I mA OL OUTPUT SOURCE CURRENT OUTPUT SOURCE CURRENT vs. OUTPUT VOLTAGE (V = 2.4V, TA = 25˚C) OH vs. OUTPUT VOLTAGE (V = 5V, TA = 25˚C) CC IOH mA IOH mA ATF1500A(L) 12

ATF1500A(L) OUTPUT SINK CURRENT NORMALIZED t PD vs. OUTPUT VOLTAGE (VCC = 5V, TA = 25˚C) vs. AMBIENT TEMPERATURE (VCC = 5V) IOL mA t PD INPUT CLAMP CURRENT vs. INPUT VOLTAGE NORMALIZED t COS vs. AMBIENT TEMPERATURE (V = 5V) CC t COS INPUT CURRENT vs. INPUT VOLTAGE (V = 5V, TA = 25˚C) CC NORMALIZED t COA vs. AMBIENT TEMPERATURE (V = 5V) CC t COA NORMALIZED t COS vs. SUPPLY VOLTAGE (TA = 25˚C) t COS 13

NORMALIZED t NORMALIZED t SIS SIS vs. SUPPLY VOLTAGE (TA = 25˚C) vs. AMBIENT TEMPERATURE (V = 5V) CC t t SIS SIS NORMALIZED t SIA NORMALIZED tSIA vs. AMBIENT TEMPERATURE (V = 5V) vs. SUPPLY VOLTAGE (TA = 25˚C) CC t SIA t SIA ATF1500A(L) 14

ATF1500A(L) Ordering Information Standard Package Options t t f PD COS MAX (ns) (ns) (MHz) Ordering Code Package Operation Range ATF1500A-7AC 44A Commercial 7.5 4.5 95 ATF1500A-7JC 44J (0°C to 70°C) ATF1500A-10AC 44A Commercial ATF1500A-10JC 44J (0°C to 70°C) 10 5 76.9 ATF1500A-10AI 44A Industrial 44J (-40°C to 85°C) ATF1500A-10JI ATF1500A-12AC 44A Commercial ATF1500A-12JC 44J (0°C to 70°C) 12 6 62.5 ATF1500A-12AI 44A Industrial ATF1500A-12JI 44J (-40°C to 85°C) ATF1500A-15AC 44A Commercial 44J (0°C to 70°C) ATF1500A-15JC 15 8 52.6 ATF1500A-15AI 44A Industrial ATF1500A-15JI 44J (-40°C to 85°C) ATF1500AL-20AC 44A Commercial ATF1500AL-20JC 44J (0°C to 70°C) 20 9 40 ATF1500AL-20AI 44A Industrial ATF1500AL-20JI 44J (-40°C to 85°C) Note: 1. The last time buy date is Sept. 30, 2005 for shaded parts. The replacements for fast-speed grade is the ATF1502AS (pin compatible). For others, suggested replacements are available in Green packages. 2. The ATF1500AL-25AC, -25AI, -25JC and -25JI were obsoleted in August 1999. The replacement was the ATF1500AL-20. Using “C” Product for Industrial To use commercial product for Industrial temperature ranges, down-grade one speed grade from the “I” to the “C” device (7ns “C” = 10 ns “I”) and de-rate power by 30%. Green Package Options (Pb/Halide-free/RoHS Compliant) t t f PD COS MAX (ns) (ns) (MHz) Ordering Code Package Operation Range ATF1500A-10AU 44A Industrial 10 5 76.9 ATF1500A-10JU 44J (-40°C to 85°C) ATF1500AL-20AU 44A Industrial 20 9 40 ATF1500AL-20JU 44J (-40°C to 85°C) Package Type 44A 44-lead, Thin Plastic Gull Wing Quad Flatpack (TQFP) 44J 44-lead, Plastic J-leaded Chip Carrier (PLCC) 15

Packaging Information 44A – TQFP PIN 1 B PIN 1 IDENTIFIER e E1 E D1 D C 0˚~7˚ A1 A2 A L COMMON DIMENSIONS (Unit of Measure = mm) SYMBOL MIN NOM MAX NOTE A – – 1.20 A1 0.05 – 0.15 A2 0.95 1.00 1.05 D 11.75 12.00 12.25 D1 9.90 10.00 10.10 Note 2 E 11.75 12.00 12.25 Notes: 1.This package conforms to JEDEC reference MS-026, Variation ACB. E1 9.90 10.00 10.10 Note 2 2.Dimensions D1 and E1 do not include mold protrusion. Allowable protrusion is 0.25 mm per side. Dimensions D1 and E1 are maximum B 0.30 – 0.45 plastic body size dimensions including mold mismatch. C 0.09 – 0.20 3. Lead coplanarity is 0.10 mm maximum. L 0.45 – 0.75 e 0.80 TYP 10/5/2001 TITLE DRAWING NO. REV. 2325 Orchard Parkway 44A, 44-lead, 10 x 10 mm Body Size, 1.0 mm Body Thickness, San Jose, CA 95131 44A B R 0.8 mm Lead Pitch, Thin Profile Plastic Quad Flat Package (TQFP) ATF1500A(L) 16

ATF1500A(L) 44J – PLCC 1.14(0.045) X 45˚ 1.14(0.045) X 45˚ PIN NO. 1 0.318(0.0125) IDENTIFIER 0.191(0.0075) E1 E B1 D2/E2 B e A2 D1 A1 D A 0.51(0.020)MAX 45˚ MAX (3X) COMMON DIMENSIONS (Unit of Measure = mm) SYMBOL MIN NOM MAX NOTE A 4.191 – 4.572 A1 2.286 – 3.048 A2 0.508 – – D 17.399 – 17.653 D1 16.510 – 16.662 Note 2 E 17.399 – 17.653 Notes: 1.This package conforms to JEDEC reference MS-018, Variation AC. E1 16.510 – 16.662 Note 2 2.Dimensions D1 and E1 do not include mold protrusion. Allowable protrusion is .010"(0.254 mm) per side. Dimension D1 D2/E2 14.986 – 16.002 and E1 include mold mismatch and are measured at the extreme B 0.660 – 0.813 material condition at the upper or lower parting line. 3. Lead coplanarity is 0.004" (0.102 mm) maximum. B1 0.330 – 0.533 e 1.270 TYP 10/04/01 TITLE DRAWING NO. REV. 2325 Orchard Parkway 44J, 44-lead, Plastic J-leaded Chip Carrier (PLCC) San Jose, CA 95131 44J B R 17

Revision History Revision Comments 0759F Green package options added. ATF1500A(L) 18

Atmel Corporation Atmel Operations 2325 Orchard Parkway Memory RF/Automotive San Jose, CA 95131, USA 2325 Orchard Parkway Theresienstrasse 2 Tel: 1(408) 441-0311 San Jose, CA 95131, USA Postfach 3535 Fax: 1(408) 487-2600 Tel: 1(408) 441-0311 74025 Heilbronn, Germany Fax: 1(408) 436-4314 Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340 Regional Headquarters Microcontrollers Europe 2325 Orchard Parkway 1150 East Cheyenne Mtn. Blvd. Atmel Sarl San Jose, CA 95131, USA Colorado Springs, CO 80906, USA Route des Arsenaux 41 Tel: 1(408) 441-0311 Tel: 1(719) 576-3300 Case Postale 80 Fax: 1(408) 436-4314 Fax: 1(719) 540-1759 CH-1705 Fribourg La Chantrerie Biometrics/Imaging/Hi-Rel MPU/ Switzerland BP 70602 High Speed Converters/RF Datacom Tel: (41) 26-426-5555 44306 Nantes Cedex 3, France Avenue de Rochepleine Fax: (41) 26-426-5500 Tel: (33) 2-40-18-18-18 BP 123 Asia Fax: (33) 2-40-18-19-60 38521 Saint-Egreve Cedex, France Room 1219 Tel: (33) 4-76-58-30-00 Chinachem Golden Plaza ASIC/ASSP/Smart Cards Fax: (33) 4-76-58-34-80 Zone Industrielle 77 Mody Road Tsimshatsui 13106 Rousset Cedex, France East Kowloon Tel: (33) 4-42-53-60-00 Hong Kong Fax: (33) 4-42-53-60-01 Tel: (852) 2721-9778 Fax: (852) 2722-1369 1150 East Cheyenne Mtn. Blvd. Japan Colorado Springs, CO 80906, USA 9F, Tonetsu Shinkawa Bldg. Tel: 1(719) 576-3300 1-24-8 Shinkawa Fax: 1(719) 540-1759 Chuo-ku, Tokyo 104-0033 Japan Scottish Enterprise Technology Park Tel: (81) 3-3523-3551 Maxwell Building Fax: (81) 3-3523-7581 East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743 Literature Requests www.atmel.com/literature Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise,to any intellectualproperty right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI- TIONS OF SALE LOCATED ON ATMEL’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN- TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representationsor warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustainlife. ® ® © Atmel Corporation 2005. All rights reserved. Atmel , logo and combinations thereof, Everywhere You Are and others, are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others. Printed on recycled paper. 0759F–6/05/xM

Mouser Electronics Authorized Distributor Click to View Pricing, Inventory, Delivery & Lifecycle Information: M icrochip: ATF1500AL-20JU ATF1500A-10AU ATF1500A-10JU ATF1500AL-20AU

Datasheet下载

Datasheet下载

.jpg)