ICGOO在线商城 > 开发板,套件,编程器 > 评估板 - 运算放大器 > ARD00354

- 型号: ARD00354

- 制造商: Microchip

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

ARD00354产品简介:

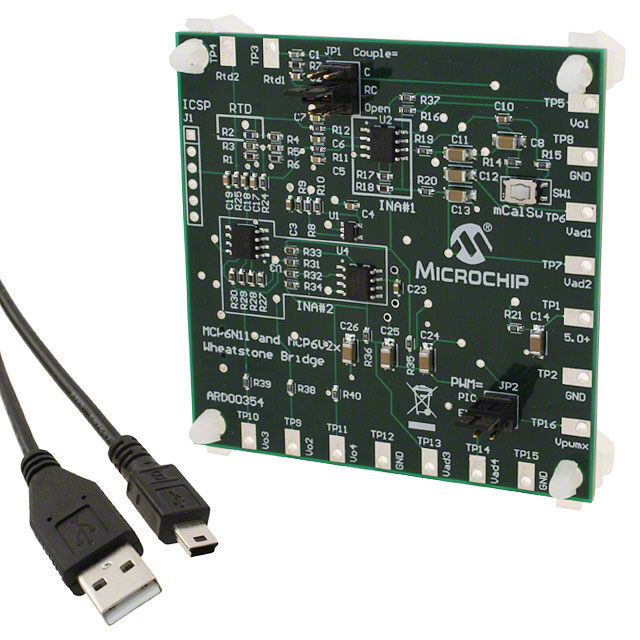

ICGOO电子元器件商城为您提供ARD00354由Microchip设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 ARD00354价格参考。MicrochipARD00354封装/规格:评估板 - 运算放大器, MCP6N11, MCP6001, MCP6V26, MCP6V27, PIC18F2553 1 - Single Channels per IC Instrumentation Amplifier Evaluation Board。您可以下载ARD00354参考资料、Datasheet数据手册功能说明书,资料中有ARD00354 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| -3db带宽 | - |

| 产品目录 | 编程器,开发系统嵌入式解决方案 |

| 描述 | BOARD REF DESIGN MCP6N11/MCP6V2X放大器 IC 开发工具 MCP6N11 Wheatstone Bridge Ref Design |

| 产品分类 | |

| 品牌 | Microchip Technology |

| 产品手册 | http://www.microchip.com/stellent/idcplg?IdcService=SS_GET_PAGE&nodeId=1406&dDocName=en556317 |

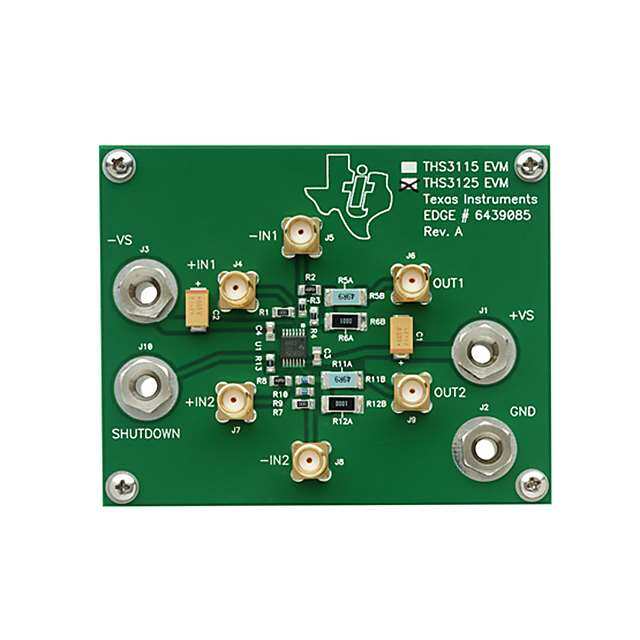

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 模拟与数字IC开发工具,放大器 IC 开发工具,Microchip Technology ARD00354- |

| 数据手册 | http://www.microchip.com/mymicrochip/filehandler.aspx?ddocname=en555932 |

| 产品型号 | ARD00354 |

| 产品 | Development Tools |

| 产品种类 | 放大器 IC 开发工具 |

| 使用的IC/零件 | MCP6N11,MCP6001,MCP6V26,MCP6V27,PIC18F2553 |

| 压摆率 | - |

| 商标 | Microchip Technology |

| 工作温度 | -40°C ~ 125°C |

| 工具用于评估 | MCP6N11, MCP6001, MCP6V26, MCP6V27, PIC18F2553 |

| 所含物品 | 板,线缆 |

| 接口类型 | USB |

| 描述/功能 | This board demonstrates the performance of Microchip's MCP6N11 instrumentation amplifier (INA) and a traditional three op amp INA using Microchip's MCP6V26 and MCP6V27 auto-zeroed op amps |

| 放大器类型 | 仪表 |

| 板类型 | 完全填充 |

| 标准包装 | 1 |

| 每IC通道数 | 1 - 单 |

| 电压-电源,单/双 (±) | - |

| 电流-电源(主IC) | 800µA |

| 电流-输出/通道 | 30mA |

| 类型 | Instrumentation Amplifiers |

| 输出类型 | 满摆幅 |

PDF Datasheet 数据手册内容提取

MCP6N11 500 kHz, 800 µA Instrumentation Amplifier Features Description • Rail-to-Rail Input and Output Microchip Technology Inc. offers the single MCP6N11 • Gain Set by 2 External Resistors instrumentation amplifier (INA) with Enable/VOS Cali- bration pin (EN/CAL) and several minimum gain • Minimum Gain (G ) Options: MIN options. It is optimized for single-supply operation with 1, 2, 5, 10 or 100V/V rail-to-rail input (no common mode crossover distor- • Common Mode Rejection Ratio (CMRR): 115dB tion) and output performance. (typical, G =100) MIN Two external resistors set the gain, minimizing gain • Power Supply Rejection Ratio (PSRR): 112dB error and drift-over temperature. The reference voltage (typical, G =100) MIN (V ) shifts the output voltage (V ). • Bandwidth: 500kHz (typical, Gain=G ) REF OUT MIN The supply voltage range (1.8V to 5.5V) is low enough • Supply Current: 800μA/channel (typical) to support many portable applications. All devices are • Single Channel fully specified from -40°C to +125°C. • Enable/V Calibration pin: (EN/CAL) OS These parts have five minimum gain options (1, 2, 5, 10 • Power Supply: 1.8V to 5.5V and 100V/V). This allows the user to optimize the input • Extended Temperature Range: -40°C to +125°C offset voltage and input noise for different applications. Typical Applications Typical Application Circuit • High Side Current Sensor V BAT • Wheatstone Bridge Sensors 10Ω I +1.8V • Difference Amplifier with Level Shifting VDD DD to U • Power Control Loops 1 +5.5V MCP6N11 V Design Aids OUT R F • Microchip Advanced Part Selector (MAPS) V 200kΩ FG • Demonstration Board R • Application Notes G 10kΩ V REF Block Diagram Package Types VOUT VDD VSS MCP6N11 MCP6N11 V R OUT M4 I SOIC 2×3TDFN* R 4 F V FG VFG 1 8 EN/CAL VFG 1 8 EN/CAL VREFRG VREF GM2 I2 I1Σ I3 VVIIMP 23 76 VVDODUT VVIIMP 23 E9P 76 VVDODUT VIP V GM3 VSS 4 5 VREF VSS 4 5 VREF IP G M1 V * Includes Exposed Thermal Pad (EP); see Table3-1. V TR IM V IM LowPower POR V Calibration OS EN/CAL © 2011 Microchip Technology Inc. DS25073A-page 1

MCP6N11 Minimum Gain Options Table1 shows key specifications that differentiate between the different minimum gain (G ) options. MIN See Section1.0 “Electrical Characteristics”, Section6.0 “Packaging Information” and Product Identification System for further information on G . MIN TABLE 1: KEY DIFFERENTIATING SPECIFICATIONS E e G V ∆V /∆T CMRR (dB) PSRR V GBWP ni ni MIN OS OS A DMH (µV ) (nV/√Hz) Part No. (V/V) (±mV) (±µV/°C) Min. (dB) (V) (MHz) P-P Nom. Nom. Nom. Max. Typ. V =5.5V Min. Max. Nom. DD (f=0.1 to 10Hz) (f=10kHz) MCP6N11-001 1 3.0 90 70 62 2.70 0.50 570 950 MCP6N11-002 2 2.0 45 78 68 1.35 1.0 285 475 MCP6N11-005 5 0.85 18 80 75 0.54 2.5 114 190 MCP6N11-010 10 0.50 9.0 81 81 0.27 5.0 57 95 MCP6N11-100 100 0.35 2.7 88 86 0.027 35 18 35 DS25073A-page 2 © 2011 Microchip Technology Inc.

MCP6N11 1.0 ELECTRICAL †Notice: Stresses above those listed under “Absolute CHARACTERISTICS Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other 1.1 Absolute Maximum Ratings † conditions above those indicated in the operational listings of this specification is not implied. Exposure to V –V .......................................................................6.5V DD SS maximum rating conditions for extended periods may Current at Input Pins†† ...............................................±2mA affect device reliability. Analog Inputs (V and V )†† .....V –1.0V to V +1.0V IP IM SS DD ††See Section4.2.1.2 “Input Voltage Limits” and All Other Inputs and Outputs .........V –0.3V to V +0.3V SS DD Section4.2.1.3 “Input Current Limits”. Difference Input Voltage.......................................|V –V | DD SS Output Short Circuit Current ................................Continuous Current at Output and Supply Pins ............................±30mA Storage Temperature ...................................-65°C to +150°C Max. Junction Temperature ........................................+150°C ESD protection on all pins (HBM, CDM, MM).≥2kV,1.5kV,300V 1.2 Specifications TABLE 1-1: DC ELECTRICAL SPECIFICATIONS Electrical Characteristics: Unless otherwise indicated, T =+25°C, V =1.8V to 5.5V, V = GND, EN/CAL=V , A DD SS DD V =V /2, V =0V, V =V /2, V =V /2, R =10kΩ to V and G =G ; see Figure1-6 and Figure1-7. CM DD DM REF DD L DD L L DM MIN Parameters Sym Min Typ Max Units G Conditions MIN Input Offset Input Offset Voltage, V -3.0 — +3.0 mV 1 (Note2) OS Calibrated -2.0 — +2.0 mV 2 -0.85 — +0.85 mV 5 -0.50 — +0.50 mV 10 -0.35 — +0.35 mV 100 Input Offset Voltage V — 0.36 — mV 1 OSTRM Trim Step — 0.21 — mV 2 — 0.077 — mV 5 — 0.045 — mV 10 — 0.014 — mV 100 Input Offset Voltage ΔV /ΔT — ±90/G — µV/°C 1 to 10 T = -40°C to +125°C OS A MIN A Drift — ±2.7 — µV/°C 100 (Note3) Power Supply PSRR 62 82 — dB 1 Rejection Ratio 68 88 — dB 2 75 96 — dB 5 81 102 — dB 10 86 112 — dB 100 Note 1: V = (V + V ) / 2, V = (V – V ) and G = 1 + R /R . CM IP IM DM IP IM DM F G 2: The V spec limits include 1/f noise effects. OS 3: This is the input offset drift without V re-calibration; toggle EN/CAL to minimize this effect. OS 4: These specs apply to both the V , V input pair (use V ) and to the V , V input pair (V takes V ’s place). IP IM CM REF FG REF CM 5: This spec applies to the V , V , V and V pins individually. IP IM REF FG 6: Figure2-11 and Figure2-19 show the V and V variation over temperature. IVR DMR 7: See Section1.5 “Explanation of DC Error Specs”. © 2011 Microchip Technology Inc. DS25073A-page 3

MCP6N11 TABLE 1-1: DC ELECTRICAL SPECIFICATIONS (CONTINUED) Electrical Characteristics: Unless otherwise indicated, T =+25°C, V =1.8V to 5.5V, V = GND, EN/CAL=V , A DD SS DD V =V /2, V =0V, V =V /2, V =V /2, R =10kΩ to V and G =G ; see Figure1-6 and Figure1-7. CM DD DM REF DD L DD L L DM MIN Parameters Sym Min Typ Max Units G Conditions MIN Input Current and Impedance (Note4) Input Bias Current I — 10 — pA all B Across Temperature — 80 — pA T = +85°C A Across Temperature 0 2 5 nA T = +125°C A Input Offset Current I — ±1 — pA OS Across Temperature — ±5 — pA T = +85°C A Across Temperature -1 ±0.05 +1 nA T = +125°C A Common Mode Input Z — 1013||6 — Ω||pF CM Impedance Differential Input Z — 1013||3 — Ω||pF DIFF Impedance Input Common Mode Voltage (V or V ) (Note4) CM REF Input Voltage Range V — — V −0.2 V all (Note5, Note6) IVL SS V V +0.15 — — V IVH DD Common Mode CMRR 62 79 — dB 1 V = V to V , CM IVL IVH Rejection Ratio 69 87 — dB 2 VDD=1.8V 75 101 — dB 5 79 107 — dB 10 86 119 — dB 100 70 94 — dB 1 V = V to V , CM IVL IVH 78 100 — dB 2 VDD=5.5V 80 108 — dB 5 81 114 — dB 10 88 115 — dB 100 Common Mode INL -1000 ±115 +1000 ppm 1 V = V to V , CM CM IVL IVH Non-Linearity -570 ±27 +570 ppm 2 VDM=0V, V =1.8V (Note7) -230 ±11 +230 ppm 5 DD -125 ±6 +125 ppm 10 -50 ±2 +50 ppm 100 -400 ±42 +400 ppm 1 V = V to V , CM IVL IVH -220 ±10 +220 ppm 2 VDM=0V, V =5.5V (Note7) -100 ±4 +100 ppm 5 DD -50 ±2 +50 ppm 10 -30 ±1 +30 ppm 100 Note 1: V = (V + V ) / 2, V = (V – V ) and G = 1 + R /R . CM IP IM DM IP IM DM F G 2: The V spec limits include 1/f noise effects. OS 3: This is the input offset drift without V re-calibration; toggle EN/CAL to minimize this effect. OS 4: These specs apply to both the V , V input pair (use V ) and to the V , V input pair (V takes V ’s place). IP IM CM REF FG REF CM 5: This spec applies to the V , V , V and V pins individually. IP IM REF FG 6: Figure2-11 and Figure2-19 show the V and V variation over temperature. IVR DMR 7: See Section1.5 “Explanation of DC Error Specs”. DS25073A-page 4 © 2011 Microchip Technology Inc.

MCP6N11 TABLE 1-1: DC ELECTRICAL SPECIFICATIONS (CONTINUED) Electrical Characteristics: Unless otherwise indicated, T =+25°C, V =1.8V to 5.5V, V = GND, EN/CAL=V , A DD SS DD V =V /2, V =0V, V =V /2, V =V /2, R =10kΩ to V and G =G ; see Figure1-6 and Figure1-7. CM DD DM REF DD L DD L L DM MIN Parameters Sym Min Typ Max Units G Conditions MIN Input Differential Mode Voltage (V ) (Note4) DM Differential Input V -2.7/G — — V all V = (V –G V )/2 DML MIN REF DD DM DM Voltage Range V — — +2.7/G V (Note6) DMH MIN Differential Gain Error g -1 ±0.13 +1 % V = V to V , E DM DML DMH Differential Gain Drift Δg /ΔT — ±0.0006 — %/°C V = (V –G V )/2 E A REF DD DM DM Differential INL -500 ±30 +500 ppm 1 (Note7) DM Non-Linearity -800 ±40 +800 ppm 2, 5 -2000 ±100 +2000 ppm 10, 100 DC Open-Loop Gain A 61 84 — dB 1 V =1.8V, OL DD 68 90 — dB 2 V =0.2V to 1.6V OUT 76 98 — dB 5 78 104 — dB 10 86 116 — dB 100 70 94 — dB 1 V =5.5V, DD 77 100 — dB 2 V =0.2V to 5.3V OUT 84 108 — dB 5 90 114 — dB 10 97 125 — dB 100 Output Minimum Output V — — V +15 mV all V =-V /(2G ), OL SS DM DD DM Voltage Swing V =1.8V, DD V = V /2–1V REF DD — — V +25 mV V =-V /(2G ), SS DM DD DM V =5.5V, DD V = V /2–1V REF DD Maximum Output V V −15 — — mV V =V /(2G ), OH DD DM DD DM Voltage Swing V =1.8V, DD V = V /2+1V REF DD V −25 — — mV V =V /(2G ), DD DM DD DM V =5.5V, DD V = V /2+1V REF DD Output Short Circuit I — ±8 — mA V = 1.8V SC DD Current — ±30 — mA V = 5.5V DD Power Supply Supply Voltage V 1.8 — 5.5 V all DD Quiescent Current I 0.5 0.8 1.1 mA I = 0 Q O per Amplifier POR Trip Voltage V 1.1 1.4 — V PRL V — 1.4 1.7 V PRH Note 1: V = (V + V ) / 2, V = (V – V ) and G = 1 + R /R . CM IP IM DM IP IM DM F G 2: The V spec limits include 1/f noise effects. OS 3: This is the input offset drift without V re-calibration; toggle EN/CAL to minimize this effect. OS 4: These specs apply to both the V , V input pair (use V ) and to the V , V input pair (V takes V ’s place). IP IM CM REF FG REF CM 5: This spec applies to the V , V , V and V pins individually. IP IM REF FG 6: Figure2-11 and Figure2-19 show the V and V variation over temperature. IVR DMR 7: See Section1.5 “Explanation of DC Error Specs”. © 2011 Microchip Technology Inc. DS25073A-page 5

MCP6N11 TABLE 1-2: AC ELECTRICAL SPECIFICATIONS Electrical Characteristics: Unless otherwise indicated, T =25°C, V =1.8V to 5.5V, V = GND, A DD SS EN/CAL=V , V =V /2, V =0V, V =V /2, V =V /2, R =10kΩ to V , C =60 pF and G =G ; DD CM DD DM REF DD L DD L L L DM MIN see Figure1-6 and Figure1-7. Parameters Sym Min Typ Max Units G Conditions MIN AC Response Gain Bandwidth GBWP — 0.50G — MHz 1 to 10 MIN Product — 35 — MHz 100 Phase Margin PM — 70 — ° all Open-Loop Output R — 0.9 — kΩ 1 to 10 OL Impedance — 0.6 — kΩ 100 Power Supply PSRR — 94 — dB all f<10kHz Rejection Ratio Common Mode CMRR — 104 — dB 1 to 10 f<10kHz Rejection Ratio — 94 — dB 100 f<10kHz Step Response Slew Rate SR — 3 — V/µs 1 to 10 V =1.8V DD — 9 — V/µs V =5.5V DD — 2 — V/µs 100 V =1.8V DD — 6 — V/µs V =5.5V DD Overdrive Recovery, t — 10 — µs all V =V –1V (or V +1V) to V /2, IRC CM SS DD DD Input Common Mode G V =±0.1V, 90% of V change DM DM OUT Overdrive Recovery, t — 5 — µs V =V –(0.5V)/G IRD DM DML MIN Input Differential (or V +(0.5V)/G ) to 0V, DMH MIN Mode V =(V –G V )/2, REF DD DM DM 90% of V change OUT Overdrive Recovery, t — 8 — µs G =2G , G V =0.5V to 0V, OR DM MIN DM DM DD Output V =0.75V (or 0.25V ), REF DD DD 90% of V change OUT Noise Input Noise Voltage E — 570/G — µV 1 to 10 f = 0.1Hz to 10Hz ni MIN P-P — 18 — µV 100 P-P Input Noise Voltage e — 950/G — nV/√Hz 1 to 10 f = 100kHz ni MIN Density — 35 — nV/√Hz 100 Input Current Noise i — 1 — fA/√Hz all f = 1kHz ni Density DS25073A-page 6 © 2011 Microchip Technology Inc.

MCP6N11 TABLE 1-3: DIGITAL ELECTRICAL SPECIFICATIONS Electrical Characteristics: Unless otherwise indicated, T =25°C, V =1.8V to 5.5V, V = GND, EN/CAL=V , A DD SS DD V = V /2, V =0V, V =V /2, V =V /2, R =10kΩ to V , C =60 pF and G =G ; CM DD DM REF DD L DD L L L DM MIN see Figure1-6 and Figure1-7. Parameters Sym Min Typ Max Units G Conditions MIN EN/CAL Low Specifications EN/CAL Logic V V — 0.2V V all IL SS DD Threshold, Low EN/CAL Input Current, I — -0.1 — nA EN/CAL = 0V ENL Low GND Current I -7 -2.5 — µA EN/CAL = 0V, V =5.5V SS DD Amplifier Output Leakage I — 10 — nA EN/CAL = 0V O(LEAK) EN/CAL High Specifications EN/CAL Logic V 0.8V V V all IH DD DD Threshold, High EN/CAL Input Current, I — -0.01 — nA EN/CAL = V ENH DD High EN/CAL Dynamic Specifications EN/CAL Input Hysteresis V — 0.2 — V all HYST EN/CAL Low to Amplifier t — 3 10 µs EN/CAL = 0.2V to V = 0.1(V /2), OFF DD OUT DD Output High-Z Turn-off V G = 1V, V =0V DM DM L Time EN/CAL High to t 12 20 28 ms EN/CAL = 0.8V to V = 0.9(V /2), ON DD OUT DD Amplifier Output V G = 1V, V =0V DM DM L On Time EN/CAL Low to t 100 — — µs Minimum time before externally ENLH EN/CAL High low time releasing EN/CAL (Note1) Amplifier On to t — 100 — µs ENOL EN/CAL Low Setup Time POR Dynamic Specifications V ↓ to Output Off t — 10 — µs all V =0V, V =1.8V to DD PHL L DD V –0.1V step, PRL 90% of V change OUT VDD ↑ to Output On tPLH 140 250 360 ms VL=0V, VDD=0V to VPRH+0.1V step, 90% of V change OUT Note 1: For design guidance only; not tested. TABLE 1-4: TEMPERATURE SPECIFICATIONS Electrical Characteristics: Unless otherwise indicated, all limits are specified for: V =1.8V to 5.5V, V =GND. DD SS Parameters Sym Min Typ Max Units Conditions Temperature Ranges Specified Temperature Range T -40 — +125 °C A Operating Temperature Range T -40 — +125 °C (Note1) A Storage Temperature Range T -65 — +150 °C A Thermal Package Resistances Thermal Resistance, 8L-SOIC θ — 150 — °C/W JA Thermal Resistance, 8L-TDFN (2×3) θ — 53 — °C/W JA Note 1: Operation must not cause T to exceed the Absolute Maximum Junction Temperature specification (+150°C). J © 2011 Microchip Technology Inc. DS25073A-page 7

MCP6N11 1.3 Timing Diagrams t ENLH ±(1V)/G DM EN/CAL V DM t t ENOL OFF t V ON CM V High-Z OUT t IRC FIGURE 1-5: EN/CAL Timing Diagram. V OUT FIGURE 1-1: Common Mode Input Overdrive Recovery Timing Diagram. V /2 DD V CM V DM t IRD V OUT FIGURE 1-2: Differential Mode Input Overdrive Recovery Timing Diagram. V /2 DD V CM V DM t OR V OUT FIGURE 1-3: Output Overdrive Recovery Timing Diagram. 1.8V V +0.1V V –0.1V PRH PRL VDD 0V t PHL t PLH V High-Z OUT FIGURE 1-4: POR Timing Diagram. DS25073A-page 8 © 2011 Microchip Technology Inc.

MCP6N11 1.4 DC Test Circuits 1.4.2 DIFFERENTIAL GAIN TEST CIRCUIT Figure1-7 is used for testing the INA’s differential gain 1.4.1 INPUT OFFSET TEST CIRCUIT error, non-linearity and input voltage range (g , INL , E DM Figure1-6 is used for testing the INA’s input offset V and V ; see Section1.5.3 “Differential Gain DML DMH errors and input voltage range (V , V and V ; see Error and Non-linearity”). R and R are 0.01% for E IVL IVH F G Section1.5.1 “Input Offset Related Errors” and accurate gain error measurements. Section1.5.2 “Input Offset Common Mode Non- linearity”). U is part of a control loop that forces V 2 OUT V to equal V ; U can be set to any bias point. DD CNT 1 V L VDD VCM+VDM/2 2.2µF V R V 2.2µF L 1kΩ L CM 100nF 100nF V OUT U RL VOUT 1 1kΩ MCP6N11 RF 6.34kΩ 1kΩ 0.01% + U1 1kΩ 100nF VM MCP6N11 V –V /2 V RG – V CM DM FG 0.01% 6.34kΩ REF R G U2 VREF MCP6H01 63.4kΩ FIGURE 1-7: Test Circuit for Differential R F Mode. R CNT The output voltages are (where V is the sum of input 12.7kΩ 63.4kΩ E offset errors and g is the gain error): V E M C 100nF CNT V EQUATION 1-2: 10nF CNT G = 1+R ⁄R FIGURE 1-6: Test Circuit for Common DM F G Mode (Input Offset). VOUT = VREF+GDM(1+gE)(VDM+VE) V = V –V When MCP6N11 is in its normal range of operation, the M OUT REF = G (1+g )(V +V ) DC output voltages are (where VE is the sum of input DM E DM E offset errors and g is the gain error): E To keep V , V and V within their ranges, set: REF FG OUT EQUATION 1-1: EQUATION 1-3: G = 1+R ⁄R DM F G V = V V = (V –G V )⁄2 OUT CNT REF DD DM DM V = V +G (1+g )V M REF DM E E Table1-6 shows the recommended R and R . They F G produce a 10kΩ load; V can usually be left open. Table1-5 gives the recommended R and R values L F G for different G options. MIN TABLE 1-6: SELECTING R AND R F G TABLE 1-5: SELECTING RF AND RG GMIN RF RG GDM (V/V) (Ω) (Ω) (V/V) G R R G G V BW MIN F G DM DM OS Nom. Nom. Nom. Nom. (V/V) (Ω) (Ω) (V/V) (±V) (kHz) Nom. Nom. Nom. Nom. Max. Nom. 1 0 Open 1.000 1 100k 499 201.4 0.60 2.5 2 4.99k 4.99k 2.000 2 0.40 5.0 5 8.06k 2.00k 5.030 5 100k 100 1001 0.85 2.5 10 9.09k 1.00k 10.09 10 0.50 5.0 100 10.0k 100 101.0 100 0.35 35 © 2011 Microchip Technology Inc. DS25073A-page 9

MCP6N11 1.5 Explanation of DC Error Specs Based on the measured V data, we obtain the E following linear fit: 1.5.1 INPUT OFFSET RELATED ERRORS EQUATION 1-6: The input offset error (V ) is extracted from input offset E measurements (see Section1.4.1 “Input Offset Test V –V ⁄2 CM DD Circuit”), based on Equation1-1: V = V +----------------------------------- E_LIN OS CMRR Where: EQUATION 1-4: V = V OS 2 V = ----V----M-----–-----V----R---E---F----- --------1--------- = ------V----3----–-----V----1------- E G (1+g ) CMRR V –V DM E IVH IVL V has several terms, which assume a linear response The remaining error (ΔV ) is described by the Common E E to changes in V , V , V , V and T (all of which Mode Non-Linearity spec: DD SS CM OUT A are in their specified ranges): EQUATION 1-7: EQUATION 1-5: maxΔV E INL = ------------------------------ V = V +Δ-----V---D----D-----–----Δ-----V----S--S-+-Δ-----V---C----M----+Δ-----V----R---E---F-- CM VIVH–VIVL E OS PSRR CMRR CMRR Where: ΔVOUT ΔVOS ΔVE = VE–VE_LIN +-----------------+ΔT ⋅------------- A A ΔT OL A Where: The same common mode behavior applies to VE when V is swept, instead of V , since both input stages PSRR, CMRR and A are in units of V/V REF CM OL are designed the same: ΔT is in units of °C A V =0 EQUATION 1-8: DM V –V ⁄2 REF DD Equation1-2 shows how V affects V . V = V +------------------------------------- E OUT E_LIN OS CMRR maxΔV 1.5.2 INPUT OFFSET COMMON MODE E INL = ------------------------------ NON-LINEARITY CM VIVH–VIVL The input offset error (V ) changes non-linearly with E VCM. Figure1-8 shows VE vs. VCM, as well as a linear 1.5.3 DIFFERENTIAL GAIN ERROR AND fit line (VE_LIN) based on VOS and CMRR. The op amp NON-LINEARITY is in standard conditions (ΔV =0, V =0, etc.). OUT DM The differential errors are extracted from differential V is swept from V to V . The test circuit is in CM IVL IVH gain measurements (see Section1.4.2 “Differential Section1.4.1 “Input Offset Test Circuit” and V is E Gain Test Circuit”), based on Equation1-2. These calculated using Equation1-4. errors are the differential gain error (g ) and the input E offset error (V , which changes non-linearly with V ): E DM V , V (V) E E_LIN VE_LIN EQUATION 1-9: V3 VE GDM = 1+RF⁄RG V2 VM = GDM(1+gE)(VDM+VE) These errors are adjusted for the expected output, then referred back to the input, giving the differential input V1 error (VED) as a function of VDM: ΔV E V (V) EQUATION 1-10: CM V V /2 V IVL DD IVH V M V = ------------–V FIGURE 1-8: Input Offset Error vs. ED G DM DM Common Mode Input Voltage. DS25073A-page 10 © 2011 Microchip Technology Inc.

MCP6N11 Figure1-9 shows V vs. V , as well as a linear fit ED DM line (V ) based on V and g . The op amp is in ED_LIN E E standard conditions (ΔV =0, etc.). V is swept OUT DM from V to V . DML DMH V , V (V) ED ED_LIN V ED_LIN V3 VED V 2 V 1 ΔV ED V (V) DM V 0 V DML DMH FIGURE 1-9: Differential Input Error vs. Differential Input Voltage. Based on the measured V data, we obtain the ED following linear fit: EQUATION 1-11: V = (1+g )V +g V ED_LIN E E E DM Where: V –V 3 1 g = -----------------------------------–1 E V –V DMH DML V 2 V = ---------------- E 1+g E Note that the V value measured here is not as E accurate as the one obtained in Section1.5.1 “Input Offset Related Errors”. The remaining error (ΔV ) is described by the ED Differential Mode Non-Linearity spec: EQUATION 1-12: maxΔV ED INL = ----------------------------------- DM V –V DMH DML Where: ΔV = V –V ED ED ED_LIN © 2011 Microchip Technology Inc. DS25073A-page 11

MCP6N11 NOTES: DS25073A-page 12 © 2011 Microchip Technology Inc.

MCP6N11 2.0 TYPICAL PERFORMANCE CURVES Note: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range. Note: Unless otherwise indicated, T = +25°C, V = 1.8V to 5.5V, V = GND, EN/CAL=V , V = V /2, V =0V, A DD SS DD CM DD DM V =V /2, V =V /2, R = 10kΩ to V , C = 60pF and G = G ; see Figure1-6 and Figure1-7. REF DD L DD L L L DM MIN 2.1 DC Voltages and Currents 35% 25% esrrencef Occutage ofercent323211100500505%%%%%%%% R3TTV3AADT0DO==S+ a12m.58°pVCl easnd 5.5V GGGMMMIIINNN=== 221ttoo1100 cescurrencof Occentage Perce2115005%%%% N3GVR3DToM0DO INV=SO= a5S 1m.R5 tppVeol- ec1sa0libration PP 0% 0% 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0-2.0 6-1.6 2-1.2 8-0.8 4-0.4 00.0 40.4 80.8 21.2 61.6 02.0 6- 5-No4-4rma3-lize2-2d Inp1-ut Offs1et Vo22ltag3e D44rift;5 6 Normalized Input Offset Voltage; G V (mV) G ((cid:2)V /(cid:2)T) (μV/°C) MIN OS MIN OS A FIGURE 2-1: Normalized Input Offset FIGURE 2-3: Normalized Input Offset Voltage, with G =1 to 10. Voltage Drift, with G =1 to 10. MIN MIN 14% 18% srrenceu111202%%% 3GTVR3ADTMM0DOII=NN=S+= a12 1m.580°pV0Cl easnd 5.5V cescurrenccc111624%%% N3GVR3DToM0DO INV=SO= a5S 1m.R50ppVe0l-ecsalibration c O10% f Octage ofnt 864%%% of entage ce 84684%%%%% ce er 2% PerP 22%% P 00%% 0 0 0 0 0 0 0 0 0 0 0 0 0 0% 20 00 80 60 40 20 20 40 60 80 00 20 -18-16-14-12-10-8-6-4-2024681012141618 1-1 1-1No-rma-lize-d Inp-ut Offset Voltage Drift;11 11 Normalized Input Offset Voltage; G V (mV) G ((cid:2)V /(cid:2)T) (μV/°C) MIN OS MIN OS A FIGURE 2-2: Normalized Input Offset FIGURE 2-4: Normalized Input Offset Voltage, with G =100. Voltage Drift, with G =100. MIN MIN © 2011 Microchip Technology Inc. DS25073A-page 13

MCP6N11 Note: Unless otherwise indicated, T = +25°C, V = 1.8V to 5.5V, V = GND, EN/CAL=V , V = V /2, V =0V, A DD SS DD CM DD DM V =V /2, V =V /2, R = 10kΩ to V , C = 60pF and G = G ; see Figure1-6 and Figure1-7. REF DD L DD L L L DM MIN 2.5 10 Voltage; 12..50 Voltage; 68 RRVGCeTMMpIONr==e Vs 1eD0nD0tative Part set V) 1.0 set V) 4 Off(m 0.5 Off(m 2 put VOS 0.0 put VOS 0 dd InGGMIN-0.5 -40°C dd InGGMIN -2 ze -1.0 +25°C ze -4 mali -1.5 ++18255°°CC RVCeMpr=e VseSSntative Part mali -6 -+4205°°CC or -2.0 GMIN= 1 to 10 or -8 +85°C N RTO N +125°C -2.5 -10 0 5 0 5 0 5 0 5 0 5 0 5 0 5 0 5 0 5 0 5 0 5 0 5 0 5 0 5 0. 0. 1. 1. 2. 2. 3. 3. 4. 4. 5. 5. 6. 6. 0. 0. 1. 1. 2. 2. 3. 3. 4. 4. 5. 5. 6. 6. Power Supply Voltage Power Supply Voltage FIGURE 2-5: Normalized Input Offset FIGURE 2-8: Normalized Input Offset Voltage vs. Power Supply Voltage, with Voltage vs. Power Supply Voltage, with V =0V and G =1 to 10. V =V and G =100. CM MIN CM DD MIN 25 2.0 age;et Voltat Offsed InputmalizedNorm(mV)GVGSMINO---1122111-50000505050 1-4288255505°°°°°CCCCC RVGRCCTeMMMpOINr==e sV 1eSS0nSS0tative Part d Input Offset Voltage;NormalizedGV(mV)GMINOS---0011011.......0505550 VDD= 1.8V RRGeTMpIONr=eVs D1eD nto=ta 15t0.i5vVe Part -25 -2.0 0 5 0 5 0 5 0 5 0 5 0 5 0 5 0. 0. 1. 1. 2. 2. 3. 3. 4. 4. 5. 5. 6. 6. 0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 Power Supply Voltage Output Voltage (V) FIGURE 2-6: Normalized Input Offset FIGURE 2-9: Normalized Input Offset Voltage vs. Power Supply Voltage, with Voltage vs. Output Voltage, with G =1 to 10. MIN V =0V and G =100. CM MIN 1.2 6 e; 1.0 Representative Part e; 5 Representative Part Voltag 00..68 RVGCTMMION== V 1D tDo 10 Voltag 34 VDD= 1.8V RGTMION= 100 d Input Offset dGV(mV)GMINOS---000000.....024442 -+++42810552°5°°CCC°C d Input Offset dGV(mV)GMINOS--210122 VDD= 5.5V e e aliz -0.6 aliz -3 m -0.8 m -4 Nor -1.0 Nor -5 -1.2 -6 0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 6.0 6.5 0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 Power Supply Voltage Output Voltage (V) FIGURE 2-7: Normalized Input Offset FIGURE 2-10: Normalized Input Offset Voltage vs. Power Supply Voltage, with Voltage vs. Output Voltage, with G =100. MIN V =V and G =1 to 10. CM DD MIN DS25073A-page 14 © 2011 Microchip Technology Inc.

MCP6N11 Note: Unless otherwise indicated, T = +25°C, V = 1.8V to 5.5V, V = GND, EN/CAL=V , V = V /2, V =0V, A DD SS DD CM DD DM V =V /2, V =V /2, R = 10kΩ to V , C = 60pF and G = G ; see Figure1-6 and Figure1-7. REF DD L DD L L L DM MIN 0.5 2.0 omadroo 00..43 VIVH–VDD 1 Wafer Lot Voltage; 11..05 RVRGDeTMDpIONr==e 5s 1.e5 ntVota 1t0ive Part HeangeHtage Raut VoltnpV)(V----0000000000........0212022134 VVDDDDDD== 15V..85IVVVL–VSS ormalizedd Input Offset GV(mV)GMINOS---01100.....05550 ++++1-8824250555°°°°CCCC I N -0.5 -2.0 -50 -25 0 25 50 75 100 125 5 0 5 0 5 0 5 0 5 0 5 0 5 0 0. 0. 0. 1. 1. 2. 2. 3. 3. 4. 4. 5. 5. 6. Ambient Temperature (°C) - Input Common Mode Voltage (V) FIGURE 2-11: Input Common Mode FIGURE 2-14: Normalized Input Offset Voltage Headroom vs. Ambient Temperature. Voltage vs. Common Mode Voltage, with V =5.5V and G =1 to 10. DD MIN 2.0 15 Voltage; 11..05 RVRGDeTMDpIONr==e 1s 1.e8 ntVota 1t0ive Part Voltage; 10 RVRGDeTMDpIONr==e 5s 1.e50nV0tative Part Offset (mV) 0.5 Offset (mV) 5 ut OS 0.0 ut OS 0 pV pV d IndGGMIN-0.5 d IndGGMIN --55 alize -1.0 ++18255°°CC alize ++18255°°CC orm -1.5 +-2450°°CC orm -10 +-2405°°CC N N -2.0 -15 -0.5 0.0 0.5 1.0 1.5 2.0 2.5 0.5 0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 6.0 Input Common Mode Voltage (V) - Input Common Mode Voltage (V) FIGURE 2-12: Normalized Input Offset FIGURE 2-15: Normalized Input Offset Voltage vs. Common Mode Voltage, with Voltage vs. Common Mode Voltage, with V =1.8V and G =1 to 10. V =5.5V and G =100. DD MIN DD MIN 15 110 d Input Offset Voltage;NormalizedGV(mV)GMINOS--111--0505550 +++1-82425550°°°°CCCC RVRGDeTMDpIONr==e 1s 1.e80nV0tative Part PSRR;MRR,Pized CMNormalNB)G(dBSRR / GG, PSRR / GCMMINMIN1100989988776665055050505050 CGGGMMMMIIINNNRR== 211/ ,Gto11M 00I1N000, VDD= 1.8V: CGGGMMMMIIINNNRR== 111/ 0Gtt0ooMPPGGI11NSS00MM, RRIIVNNDRR==D //11=GG 0 t50oMM. 5IINN1V::0: -0.5 0.0 0.5 1.0 1.5 2.0 2.5 -50 -25 0 25 50 75 100 125 Input Common Mode Voltage (V) Ambient Temperature (°C) FIGURE 2-13: Normalized Input Offset FIGURE 2-16: Normalized CMRR and Voltage vs. Common Mode Voltage, with PSRR vs. Ambient Temperature. V =1.8V and G =100. DD MIN © 2011 Microchip Technology Inc. DS25073A-page 15

MCP6N11 Note: Unless otherwise indicated, T = +25°C, V = 1.8V to 5.5V, V = GND, EN/CAL=V , V = V /2, V =0V, A DD SS DD CM DD DM V =V /2, V =V /2, R = 10kΩ to V , C = 60pF and G = G ; see Figure1-6 and Figure1-7. REF DD L DD L L L DM MIN 110 5 ain;oop GaOpen-Lod DC OmalizedNorm)(dB)A/ GAMINOLM110098998877650550505055 VVDDDD== 51..58VV GGGMMIINN=== 111 00t00o 10 ized Differential InputNormalror; GV(mV)ErrMINED-----21012345432 RRVGEeTMDpION=r=e (s V1eOnUtTa–tivVeRV EPDFVaD)/rDG=tD D5=M. 51–V.8VVDM 60 -5 -4 -3 -2 -1 0 1 2 3 4 5 -50 -25 0 25 50 75 100 125 Normalized Differential Input Voltage; Ambient Temperature (°C) G V (V) MIN DM FIGURE 2-17: Normalized DC Open-Loop FIGURE 2-20: Normalized Differential Input Gain vs. Ambient Temperature. Error vs. Differential Voltage, with G =1. MIN 6.0 5 (V)oltagetput VoOut544533422312..........005505055000 VIM= RV-0DDe.DD2p0r=eVGGG 5sDDD.eMMM5nVV==tIaM 11 t i=00 v 001 eV DPDa+rt 0.15V puttial Inpifferentized DimalmV)V(ror; GErrMINEDM---4230121032 RVVGREETeMDDpOIN=r=e((s VV2e OOntUUotTTa 1–t0ivVV0eRR EEPFFa))//rGGtDDMM–VVDDMM 1.0 NorN -44 0.5 -5 0.0 --55 --44 --33 --22 --11 00 11 22 33 44 55 0 5 0 5 0 5 0 5 0 5 0 5 0 5 0 5 1. 0. 0. 0. 1. 1. 2. 2. 3. 3. 4. 4. 5. 5. 6. 6. Normalized Differential Input Voltage; - - Non-inverting Input Voltage; VIP(V) GMINVDM(V) FIGURE 2-18: The MCP6N11 Shows No FIGURE 2-21: Normalized Differential Input Phase Reversal vs. Common Mode Voltage. Error vs. Differential Voltage, with G =2to100. MIN 4.0 5.5 1 Wafer Lot Representative Part utial InpufferentiDifV)V(Ve; GVgeDMHMIN3333333......0846240 GRTMOINVDMH= -GMINVDML Voltage (V)233445......505050 VVDRDEF== 5 (.V5DVD–GDMVDM)/2 ed Ran2.8 put 2.0 zormalizNooltageVo2222....4602 NVDoMteH:= F mori nGimMINum= 1o,f plot value and VDD tOut0011....0505 GGGGGMMMMMIIIIINNNNN===== 11125000 -50 -25 0 25 50 75 100 125 -7 -6 -5 -4 -3 -2 -1 0 1 2 3 4 5 6 7 Axis Title Differential Input Voltage (V) FIGURE 2-19: Normalized Differential FIGURE 2-22: The MCP6N11 Shows No Mode Voltage Range vs. Ambient Temperature. Phase Reversal vs. Differential Voltage, with V =5.5V. DD DS25073A-page 16 © 2011 Microchip Technology Inc.

MCP6N11 Note: Unless otherwise indicated, T = +25°C, V = 1.8V to 5.5V, V = GND, EN/CAL=V , V = V /2, V =0V, A DD SS DD CM DD DM V =V /2, V =V /2, R = 10kΩ to V , C = 60pF and G = G ; see Figure1-6 and Figure1-7. REF DD L DD L L L DM MIN 1.E1-008n 2.5 s (A) VVDCDM== 5V.D5DV s (nA) 12..50 RTVADeDp=r= +e 51s.2e55nV°tCative Part nt1.E-019n nt Curre Curre 01..50 IB Offset 1.E10-100p IB Offset -00..05 IOS s, as s, as-11.00 ut Bi1.E1-101p | IOS| ut Bi-1.5 np np-2.0 I I 1.E-112p -2.5 25 45 65 85 105 125 0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 6.0 Ambient Temperature (°C) Common Mode Input Voltage (V) FIGURE 2-23: Input Bias and Offset FIGURE 2-26: Input Bias and Offset Currents vs. Ambient Temperature, with Currents vs. Common Mode Input Voltage, with V =+5.5V. T =+125°C. DD A 1.E-10m3 1000 A)1.E10-004μ mV)m Magnitude (111...1EEE01---000001765nμμ +125°C oom (HeadroH 110000 VVDD==11.88VV VDD= 5.5V urrent Cu111..EEE1--000011899nnn ++--48240055°°°CCC ltageVo VDD–VOH VVOL–VVSS ut 1.1E0-100p ut p p In1.E1-101p Out 1.E-112p 1100 -1.0 -0.9 -0.8 -0.7 -0.6 -0.5 -0.4 -0.3 -0.2 -0.1 0.0 0.1 1 10 Input Voltage (V) Output Current Magnitude (mA) FIGURE 2-24: Input Bias Current vs. FIGURE 2-27: Output Voltage Headroom Input Voltage (below V ). vs. Output Current. SS 100 10 pA) 80 RTAep=r +e8s5e°nCtative Part 9 nts ( 60 VDD= 5.5V mV) 8 VDD–VOH et Curre 24000 IB (droomd 75675 VDD= 5.5V Offs -20 IOS Hea 4 s, as -40 ut pu 3 VDD= 1.8V ut Bi -60 Out 2 np -80 1 I-100 00 VOL–VSS 0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 6.0 -50 -25 0 25 50 75 100 125 Common Mode Input Voltage (V) Ambient Temperature (°C) FIGURE 2-25: Input Bias and Offset FIGURE 2-28: Output Voltage Headroom Currents vs. Common Mode Input Voltage, with vs. Ambient Temperature. T =+85°C. A © 2011 Microchip Technology Inc. DS25073A-page 17

MCP6N11 Note: Unless otherwise indicated, T = +25°C, V = 1.8V to 5.5V, V = GND, EN/CAL=V , V = V /2, V =0V, A DD SS DD CM DD DM V =V /2, V =V /2, R = 10kΩ to V , C = 60pF and G = G ; see Figure1-6 and Figure1-7. REF DD L DD L L L DM MIN 50 1100 A) m 40 1000 ort Circuit Current (Sho--12312000000 +++-41820255°5°°CCC°C μA)urrent (ply CuSup 896745300000000000000 VDD= 1.8V VDD= 5.5V ut -30 200 p ut-40 100 O -50 0 0 5 0 5 0 5 0 5 0 5 0 5 0 5 5 0 5 0 5 0 5 0 5 0 5 0 5 0 0. 0. 1. 1. 2. 2. 3. 3. 4. 4. 5. 5. 6. 6. 0. 0. 0. 1. 1. 2. 2. 3. 3. 4. 4. 5. 5. 6. Power Supply Voltage (V) - Common Mode Input Voltage (V) FIGURE 2-29: Output Short Circuit Current FIGURE 2-31: Supply Current vs. Common vs. Power Supply Voltage. Mode Input Voltage. 1100 1000 900 A) 800 μ nt ( 700 urre 600 +125°C ply Cp 450000 ++-44820055°°°CCC u 300 S 200 100 0 0 5 0 5 0 5 0 5 0 5 0 5 0 5 0. 0. 1. 1. 2. 2. 3. 3. 4. 4. 5. 5. 6. 6. Power Supply Voltage (V) FIGURE 2-30: Supply Current vs. Power Supply Voltage. DS25073A-page 18 © 2011 Microchip Technology Inc.

MCP6N11 Note: Unless otherwise indicated, T = +25°C, V = 1.8V to 5.5V, V = GND, EN/CAL=V , V = V /2, V =0V, A DD SS DD CM DD DM V =V /2, V =V /2, R = 10kΩ to V , C = 60pF and G = G ; see Figure1-6 and Figure1-7. REF DD L DD L L L DM MIN 2.2 Frequency Response 100 0.50 150 90 VDD= 5.5V 0.45 140 80 hwith)MHz)0.40 130 CMRR (dB) 45671230000000 GGMGGGGIMNIMMMMN=IIIINNNN= 1=== 10 112500 ndain Banized GaNormaliN(WP/Gt; GBWroductPNMIN000000000.......110323232055005555 GGMGGGMINMMMMIN=IIIINNNN= 1=== 01 00125 GGBBWWPMPP 11119178612020000000000°)argin (hase MaPh 0 0.00 50 1.E1+k03 1.1E0+k04 11.E0+00k5 1.E1M+06 -50 -25 0 25 50 75 100 125 Frequency (Hz) Ambient Temperature (°C) FIGURE 2-32: CMRR vs. Frequency. FIGURE 2-35: Normalized Gain Bandwidth Product and Phase Margin vs. Ambient Temperature. 120 1.E+1004k 110 VDD= 5.5V e c 100 nan d 90 e 8800 mpm1.E+013k GGDDMM//GGMMIINN= 1100 GMMIINN= 1 to 10 dB) 70 ut I R (PSRR 645634000000 GMIN= 1 tpop OutLoo11.EE)((cid:3)++1100002200 GMIN= 100 GMIN= 2 d- 2120000 GGMGMINMMIN=IINN= 1= 01 005 seClos11.EE++00111100 GDM/GMIN= 1 1.E1+k03 1.1E0+k04 11.E0+00k5 1.E1M+06 1.E1+k03 1.1E0+k04 11.E0+00k5 1.E1M+06 1.1E0+M07 Frequency (Hz) Frequency (Hz) FIGURE 2-33: PSRR vs. Frequency. FIGURE 2-36: Closed-Loop Output Impedance vs. Frequency. 120 -60 7 nop Gaio(dB)NN106860000 (cid:2)AOL/GMIN ----91112055000nop Gaio(°) B)6565 GGMMIINN=GGDDMM==== 1 01125 GGMDIMN=== 251000 pen-Lod OpA/Gde;AOLMI 2420000 | AOL/GMIN| ---122284110000pen-Lod Op/Ge; AOLMINO king (dPeak43 GGMDIMN== 12=00 00100 zeormalizNotuMagnitM ---426000 GGGGGMMMMINIIINNN===== 1 55012 ---323073000zeormalizNoasPha n Gai21 = 500 -80 GMIN= 100 -360 00 11.E0+k4 11.0E0+k5 1.1EM+6 11.E0M+7 11.E0p+1 11.0E0+p2 1.1En+3 Frequency (Hz) Normalized Capacitive Load; C(G /G ) (F) L MIN DM FIGURE 2-34: Normalized Open-Loop FIGURE 2-37: Gain Peaking vs. Gain vs. Frequency. Normalized Capacitive Load. © 2011 Microchip Technology Inc. DS25073A-page 19

MCP6N11 Note: Unless otherwise indicated, T = +25°C, V = 1.8V to 5.5V, V = GND, EN/CAL=V , V = V /2, V =0V, A DD SS DD CM DD DM V =V /2, V =V /2, R = 10kΩ to V , C = 60pF and G = G ; see Figure1-6 and Figure1-7. REF DD L DD L L L DM MIN 2.3 Noise 1010m0 0.5 age e Voltaut Noiseed InpurmalizeNor/(cid:4)Hz)e(V/ty; GDensitNniMI1101101110000001μμμ GGGGGMMMMMINIIIINNNN==== 1 05221 GMIN= 100 RTO Noise;nputNalized INorma)t) (mV)Ge(tGMINni----00000000000.........20431201324 RGRTeMMpOIINNr=es 1e ntota 1t0ive Part ASanmalppolge NRPaBteW = =4 0S.P1 SHz 1000.1n -0.5 10.E.1-1 1.E1+01.E10+111.E0+021.1Ek+31.1E0+k411.0E0+k51.1EM+6 0 5 10 15 20 25 30 35 Frequency (Hz) Time (min) FIGURE 2-38: Normalized Input Noise FIGURE 2-41: Normalized Input Noise Voltage Density vs. Frequency. Voltage vs. Time, with G =1 to 10. MIN 14 2.0 Representative Part Analog NPBW = 0.1 Hz eVoltagNoise Input malized m(cid:4)Hz)e(μV/(cid:4); Geensity;DeniMIN11120286242 GGGGGGGMMMMMMIIIIIINNNNNNf======= = 1212511 10000000 Hz VVDDDD== 15..85VV Noise;nputNalized INorma)t) (mV)Ge(tGMINni---111000011.......500550505 GRTMMOIINN= 100 Sampple Rate = 4 SPS or RTO N 0 -2.0 5 0 5 0 5 0 5 0 5 0 5 0 5 0 0. 0. 0. 1. 1. 2. 2. 3. 3. 4. 4. 5. 5. 6. 0 5 10 15 20 25 30 35 - Common Mode Input Voltage (V) Time (min) FIGURE 2-39: Normalized Input Noise FIGURE 2-42: Normalized Input Noise Voltage Density vs. Input Common Mode Voltage vs. Time, with G =100. MIN Voltage, with f=100Hz. 4.0 eg 33.55 a VoltNoise nput (cid:4)Hz)e(μV/(cid:4)GeniMIN32212....00550 GGGGGMMMMMMIIIIIINNNNNN===== 52111000 VVDDDD== 15..85VV Id ; y; malizemensitDe 010..505 f = 10 kHz or RTO N 0.0 5 0 5 0 5 0 5 0 5 0 5 0 5 0 0. 0. 0. 1. 1. 2. 2. 3. 3. 4. 4. 5. 5. 6. - Common Mode Input Voltage (V) FIGURE 2-40: Normalized Input Noise Voltage Density vs. Input Common Mode Voltage, with f=10kHz. DS25073A-page 20 © 2011 Microchip Technology Inc.

MCP6N11 Note: Unless otherwise indicated, T = +25°C, V = 1.8V to 5.5V, V = GND, EN/CAL=V , V = V /2, V =0V, A DD SS DD CM DD DM V =V /2, V =V /2, R = 10kΩ to V , C = 60pF and G = G ; see Figure1-6 and Figure1-7. REF DD L DD L L L DM MIN 2.4 Time Response 10 VDD= 5.5V g )div) GRFDM+ =R GGM=I N10 k(cid:3) inSw VDD= 5.5V V/ e mm g 10 olta e (Voltag GGGMMMIIINNN=== 111 0tt0oo 1100 t VOutpu)(V-PP 11 VDD= 1.8V GMIGN=MI N1 =to 1 0100 ut m p u ut m OO xix a M 00 0 2 4 6 8 10 12 14 16 18 20 11.E0+k4 11.E00+k5 1.1EM+6 Time (μs) Frequency (Hz) FIGURE 2-43: Small Signal Step FIGURE 2-46: Maximum Output Voltage Response. Swing vs. Frequency. 5.5 1000 )mV/div)e (10 mVoltageOutput VO5443322110..........0050505055 GGMMIINN== 11 0t0o 10 VGRDFDDDMM+= =R 5GG.5MM=VII NN10 k(cid:3) geVoltagn Mode ommonput CoInps)t(μsovery;ve RecoverdrivOvIRC 1100110000 GDMVDM= ±1V VDD=G 1M.I8NV= 10GMIN= 1V0DD0DD= 5.5V 00..00 1 GMIN= 1 0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 1 10 100 Time (μs) Normalized Gain; GDM/GMIN FIGURE 2-44: Large Signal Step FIGURE 2-47: Common Mode Input Response. Overdrive Recovery Time vs. Normalized Gain. 10 1000 98 ageVoltas)(μsRD s)te (V/μsew RatSle 7567453 GGGMMIINN== 1110tt0o1100 VVVDDDD=== 551..855VVV e al ModeerentiaDiffetovery;ve RecodrivI 1100110000 VDD= 1.8V VVDDDD=55..55VV 21 put npverOv GMING=M I1N0= 100 0 I 1 GMIN= 1 -50 -25 0 25 50 75 100 125 1 10 100 Ambient Temperature (°C) Normalized Gain; GDM/GMIN FIGURE 2-45: Slew Rate vs. Ambient FIGURE 2-48: Differential Input Overdrive Temperature. Recovery Time vs. Normalized Gain. © 2011 Microchip Technology Inc. DS25073A-page 21

MCP6N11 Note: Unless otherwise indicated, T = +25°C, V = 1.8V to 5.5V, V = GND, EN/CAL=V , V = V /2, V =0V, A DD SS DD CM DD DM V =V /2, V =V /2, R = 10kΩ to V , C = 60pF and G = G ; see Figure1-6 and Figure1-7. REF DD L DD L L L DM MIN 1000 4 very; GVRDEMF== 20G.7M5INVDD V) 33 VDD= 5.5V VIP verdrive Recot(μs)OR 100 VDD= 1.8VVDD= 5.5V GMIN= 1G0MIN= 1 ges (Voltagput 2010 VVOOUUTT,, GGMMIINN== 1100 t Ou 1100 OutO-1 Outp GMIN= 100 nput,n-2 I-3 1 -4 VIM 1 10 100 0 10 20 30 40 50 60 70 80 90 100 Normalized Gain; GDM/GMIN Time (μs) FIGURE 2-49: Output Overdrive Recovery FIGURE 2-51: The MCP6N11 Shows No Time vs. Normalized Gain. Phase Reversal vs. Differential Input Overdrive, with V =5.5V. DD 6 ututpu 55 VCM VGGf =DDDD MM1VV=0DD 5kMM.H5=zV+00..11VV , Ode,V) 4 Mos ( 3 nege mmout CoVoltaV 21 VVVOOUUTT,, GGGMMIINN== 11100 pp 00 n I -1 0 10 20 30 40 50 60 70 80 90 100 Time (μs) FIGURE 2-50: The MCP6N11 Shows No Phase Reversal vs. Common Mode Input Overdrive, with V =5.5V. DD DS25073A-page 22 © 2011 Microchip Technology Inc.

MCP6N11 Note: Unless otherwise indicated, T = +25°C, V = 1.8V to 5.5V, V = GND, EN/CAL=V , V = V /2, V =0V, A DD SS DD CM DD DM V =V /2, V =V /2, R = 10kΩ to V , C = 60pF and G = G ; see Figure1-6 and Figure1-7. REF DD L DD L L L DM MIN 2.5 Enable/Calibration and POR Responses 2.0 30 , Output Voltage (V)L0011111.......6802468 VVDLD== 0 1V.8V CaSlibtarrattsion turInNsA on turInNsA off ms); t(mn Time;urn OnTON212111550050 VVDDDD== 51..58VV A0.4 L N/C0.2 EN/CAL VOUT CA 55 E0.0 /EN/ -0.2 0 0 10 20 30 40 50 60 70 80 90 100 -50 -25 0 25 50 75 100 125 Time (ms) Ambient Temperature (°C) FIGURE 2-52: EN/CAL and Output Voltage FIGURE 2-55: EN/CAL Turn On Time vs. vs. Time, with V =1.8V. Ambient Temperature. DD 6.0 1.8 V)55..05 VVDLD== 0 5V.5V e (V)e 1.6 VL= 0V , Output Voltage (L2233441.......0505055 CaSlibtarrattsion turInNsA on turInNsA off VoltagutputVply, Oup 11011000......28406428 VDD VOUT OOnn A u EN/C001...050 EN/CAL VOUT er Sowe 00..20 OOffff Calibrating OOffff P -0.5 -0.2 0 10 20 30 40 50 60 70 80 90 100 0.0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0 Time (ms) Time (s) FIGURE 2-53: EN/CAL and Output Voltage FIGURE 2-56: Power Supply On and Off vs. Time, with V =5.5V and Output Voltage vs. Time. DD 0.60 1.7 0.18 0.55 1.6 0.16 0.50 s (V)si00..4450 VDD= 5.5V es (V)11..45 00..1124s (V) stereAL HysA000000....323232050500 Trip Voltag1111...1231 VPRH–VVPPRRHL 0000...01008066R HysteresiR C R O EN/000...111050 VDD= 1.8V PO1.0 0.04P 0.05 0.9 VPRL 0.02 0.00 0.8 0.00 -50 -25 0 25 50 75 100 125 -50 -25 0 25 50 75 100 125 Ambient Temperature (°C) Ambient Temperature (°C) FIGURE 2-57: POR Trip Voltages and FIGURE 2-54: EN/CAL Hysteresis vs. Hysteresis vs. Temperature. Ambient Temperature. © 2011 Microchip Technology Inc. DS25073A-page 23

MCP6N11 Note: Unless otherwise indicated, T = +25°C, V = 1.8V to 5.5V, V = GND, EN/CAL=V , V = V /2, V =0V, A DD SS DD CM DD DM V =V /2, V =V /2, R = 10kΩ to V , C = 60pF and G = G ; see Figure1-6 and Figure1-7. REF DD L DD L L L DM MIN 0.0 1.E10-007n ent;e EN/CAL = 0V A)A EVNDDDD/C=A 5L.5 =V 0V y CurrSupplyowerSμA)I(μSS---011...505 rent (ge Curreakag111...EEE110---001010890nnp ++18255°°CC PP LL ativeeg -2.0 ++++188225555°°°CCCC utputOu1.E1-101p +2255°°CC N -40°C -2.5 1.E-1112pp 0.00.51.01.52.02.53.03.54.04.55.05.56.06.5 0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 6.0 Power Supply Voltage (V) Output Voltage (V) FIGURE 2-58: Quiescent Current in FIGURE 2-59: Output Leakage Current vs. Shutdown vs. Power Supply Voltage. Output Voltage. DS25073A-page 24 © 2011 Microchip Technology Inc.

MCP6N11 3.0 PIN DESCRIPTIONS Descriptions of the pins are listed in Table3-1. TABLE 3-1: PIN FUNCTION TABLE MCP6N11 Symbol Description SOIC TDFN 1 1 V Feedback Input FG 2 2 V Inverting Input IM 3 3 V Non-inverting Input IP 4 4 V Negative Power Supply SS 5 5 V Reference Input REF 6 6 V Output OUT 7 7 V Positive Power Supply DD 8 8 EN/CAL Enable/V Calibrate Digital Input OS — 9 EP Exposed Thermal Pad (EP); must be connected to V SS 3.1 Analog Signal Inputs 3.5 Power Supply Pins The non-inverting and inverting inputs (V , and V ) The positive power supply (V ) is 1.8V to 5.5V higher IP IM DD are high-impedance CMOS inputs with low bias than the negative power supply (V ). For normal SS currents. operation, the other pins are between V and V . SS DD Typically, these parts are used in a single (positive) 3.2 Analog Feedback Input supply configuration. In this case, V is connected to SS ground and V is connected to the supply; V will The analog feedback input (V ) is the inverting input DD DD FG need bypass capacitors. of the second input stage. The external feedback components (R and R ) are connected to this pin. It is F G 3.6 Digital Enable and V Calibration a high-impedance CMOS input with low bias current. OS Input 3.3 Analog Reference Input This input (EN/CAL) is a CMOS, Schmitt-triggered The analog reference input (VREF) is the non-inverting input that controls the active, low power and VOS input of the second input stage; it shifts V to its calibration modes of operation. When this pin goes low, OUT desired range. The external gain resistor (R ) is the part is placed into a low power mode and the output G connected to this pin. It is a high-impedance CMOS is high-Z. When this pin goes high, the amplifier’s input input with low bias current. offset voltage is corrected by the calibration circuitry, then the output is re-connected to the V pin, which OUT becomes low impedance, and the part resumes normal 3.4 Analog Output operation. The analog output (V ) is a low-impedance voltage OUT output. It represents the differential input voltage 3.7 Exposed Thermal Pad (EP) (V =V –V ), with gain G and is shifted by DM IP IM DM V . The external feedback resistor (R ) is connected There is an internal connection between the Exposed REF F to this pin. Thermal Pad (EP) and the VSS pin; they must be connected to the same potential on the Printed Circuit Board (PCB). This pad can be connected to a PCB ground plane to provide a larger heat sink. This improves the package thermal resistance (θ ). JA © 2011 Microchip Technology Inc. DS25073A-page 25

MCP6N11 NOTES: DS25073A-page 26 © 2011 Microchip Technology Inc.

MCP6N11 4.0 APPLICATIONS The input offset voltage (V ) is corrected by the OS voltage V . Each time a V Calibration event occurs, TR OS The MCP6N11 instrumentation amplifier (INA) is V is updated to the best value (at that moment). TR manufactured using Microchip’s state of the art CMOS These events are triggered by either powering up process. It is low cost, low power and high speed, (monitored by the POR) or by toggling the EN/CAL pin making it ideal for battery-powered applications. high. The current out of G (I ) is constant and very M3 3 small (assumed to be zero in the following discussion). 4.1 Basic Performance The input signal is applied to G . Equation4-2 shows M1 the relationships between the input voltages (V and 4.1.1 STANDARD CIRCUIT IP V ) and the common mode and differential voltages IM Figure4-1 shows the standard circuit configuration for (V and V ). CM DM these INAs. When the inputs and output are in their specified ranges, the output voltage is approximately: EQUATION 4-2: EQUATION 4-1: V = V +V ⁄2 IP CM DM V ≈V +G V V = V –V ⁄2 OUT REF DM DM IM CM DM Where: V = (V +V )⁄2 CM IP IM GDM=1+RF/RG VDM = VIP–VIM The negative feedback loop includes G , R , R and VDD U1 R . These blocks set the DC open-loopM g2ainM (4A F) and G OL MCP6N11 the nominal differential gain (G ): V DM IP V OUT EQUATION 4-3: VIM VFG RF A = G R OL M2 M4 G = 1+R ⁄R DM F G R G V ≈ REF A is very high, so I is very small and I + I 0. This OL 4 1 2 FIGURE 4-1: Standard Circuit. makes the differential inputs to G and G equal in M1 M2 magnitude and opposite in polarity. Ideally, this gives: For normal operation, keep: • VIP, VIM, VREF and VFG between VIVL and VIVH EQUATION 4-4: • V – V (i.e., V ) between V and V IP IM DM DML DMH (V –V ) = V • V between V and V FG REF DM OUT OL OH V = V G +V OUT DM DM REF 4.1.2 ARCHITECTURE Figure4-2 shows the block diagram for these INAs. For an ideal part, changing VCM, VSS or VDD produces no change in V . V shifts V as needed. OUT REF OUT The different G options change G , G and the MIN M1 M2 VOUT VDD VSS internal compensation capacitor. This results in the V R performance trade-offs shown in Table1. OUT M4 I R 4 F V FG V RG VREF GM2 I2 Σ I3 REF I 1 V G IP V M3 IP G M1 V V TR IM V IM LowPower POR V Calibration OS EN/CAL FIGURE 4-2: MCP6N11 Block Diagram. © 2011 Microchip Technology Inc. DS25073A-page 27

MCP6N11 4.1.3 DC ERRORS EQUATION 4-6: Section1.5 “Explanation of DC Error Specs” I ⎛ OS⎞ defines some of the DC error specifications. These ΔV = –I R = –I –-------- R IP BP IP ⎝ B 2 ⎠ IP errors are internal to the INA, and can be summarized I as follows: ΔV = –I R = ⎛–I +---O---S--⎞R IM BM IM ⎝ B 2 ⎠ IM ΔV +ΔV EQUATION 4-5: IP IM ΔV = --------------------------------- CM 2 V = V +G (1+g )(V +ΔV ) OUT REF DM E DM ED R +R –I –R +R +GDM(1+gE)(VE+ΔVE) = –IB⎝⎛----I--P------2--------I--M---⎠⎞ +-----2-O----S-⎝⎛--------I--P---2----------I--M---⎠⎞ Where: ΔV = ΔV –ΔV DM IP IM ΔV –ΔV ΔV ΔV V = V +--------D----D------------------S--S-+----------C---M----+---------R---E---F-- I E OS PSRR CMRR CMRR = I (–R +R )–---O---S--(R +R ) B IP IM 2 IP IM ΔV ΔV +---------O---U----T-+ΔT ⋅--------O----S- ΔV A A ΔT ΔV = G ⎛ΔV +---------C----M----⎞ OL A OUT DM⎝ DM CMRR⎠ ΔV ≤INL (V –V ) ED DM DMH DML Where: ΔV ≤INL (V –V ) E CM IVH IVL CMRR is in units of V/V Where: PSRR, CMRR and A are in units of V/V The best design results when R and R are equal OL IP IM and small: ΔT is in units of °C A EQUATION 4-7: The non-linearity specs (INL and INL ) describe CM DM errors that are non-linear functions of VCM and VDM, ΔVOUT≈GDMΔVDM respectively. They give the maximum excursion from ≈G (±2I ε –I )R linear response over the entire common mode and DM B RTOL OS IP Where: differential ranges. R =R The input bias current and offset current specs (I and IP IM B I ), together with a circuit’s external input resistances, ε =tolerance of R and R OS RTOL IP IM give an additional DC error. Figure4-3 shows the resistors that set the DC bias point. The resistors at the feedback input (R , R and R ) R F G and its input bias currents (I and I ) give the BR BF following changes in the INA’s bias voltages: IBP R VDD U1 IP V MCP6N11 EQUATION 4-8: IP V OUT I VIM IBF RF ΔVREF = –IBRRR = ⎝⎛–IB2–---O--2-S---2-⎠⎞RR R I IM ΔV ≈ΔV , due to high A BM V FG REF OL FG I R ΔV ≈I (R –G R )+---O---S---2-(R +G R ) R IBR RG OUT B2 F DM R 2 F DM R Where: V REF I meets the I spec, but is not equal to I B2 B B FIGURE 4-3: DC Bias Resistors. I meets the I spec, but is not equal to I OS2 OS OS The resistors at the main input (R and R ) and its IP IM input bias currents (I and I ) give the following BP BM changes in the INA’s bias voltages: The best design results when GDMRR and RF are equal and small: EQUATION 4-9: ΔV ≈(±(2I ε +I ))R OUT B2 RTOL OS2 F Where: G R =R DM R F ε =tolerance of R , R and R RTOL R F G DS25073A-page 28 © 2011 Microchip Technology Inc.

MCP6N11 4.1.4 AC PERFORMANCE 4.2 Functional Blocks The bandwidth of these amplifiers depends on G DM 4.2.1 RAIL-TO-RAIL INPUTS and G : MIN Each input stage uses one PMOS differential pair at the EQUATION 4-10: input. The output of each differential pair is processed using current mode circuitry. The inputs show no f f ≈--G----B---W-----P- crossover distortion vs. common mode voltage. BW G DM With this topology, the inputs (V and V ) operate IP IM ≈(0.50 MHz)(G ⁄G ), G =1, …,10 MIN DM MIN normally down to V –0.2V and up to V +0.15V at SS DD ≈(0.35 MHz)(G ⁄G ), G =100 room temperature (see Figure2-11). The input offset MIN DM MIN Where: voltage (VOS) is measured at VCM=VSS–0.2V and V +0.15V (at +25°C), to ensure proper operation. f =-3dBbandwidth DD BW f =Gainbandwidthproduct 4.2.1.1 Phase Reversal GBWP The input devices are designed to not exhibit phase The bandwidth at the maximum output swing is called inversion when the input pins exceed the supply the Full Power Bandwidth (f ). It is limited by the FPBW voltages. Figures2-18 and2-50 show an input voltage Slew Rate (SR) for many amplifiers, but is close to f BW exceeding both supplies with no phase inversion. for these parts: The input devices also do not exhibit phase inversion when the differential input voltage exceeds its limits; EQUATION 4-11: see Figures2-22 and2-51. SR fFPBW≈π----V------ 4.2.1.2 Input Voltage Limits O ≈f , for these parts In order to prevent damage and/or improper operation BW Where: of these amplifiers, the circuit must limit the voltages at the input pins (see Section1.1 “Absolute Maximum V =Maximumoutputvoltageswing O Ratings†”). This requirement is independent of the ≈VOH–VOL current limits discussed later on. The ESD protection on the inputs can be depicted as CMRR is constant from DC to about 1kHz. shown in Figure4-4. This structure was chosen to protect the input transistors against many (but not all) 4.1.5 NOISE PERFORMANCE overvoltage conditions, and to minimize input bias As shown in Figures2-41 and2-42, the 1/f noise current (I ). B causes an apparent wander in the DC output voltage. Changing the measurement time or bandwidth has little effect on this noise. Bond V DD Pad We recommend re-calibrating V periodically, to OS reduce 1/f noise wander. For example, V could be OS re-calibrated at least once every 15 minutes; more often when temperature or V change significantly. Bond Input Bond DD V V IP Pad Stage Pad IM of INAInput Bond V SS Pad FIGURE 4-4: Simplified Analog Input ESD Structures. © 2011 Microchip Technology Inc. DS25073A-page 29

MCP6N11 The input ESD diodes clamp the inputs when they try It is also possible to connect the diodes to the left of the to go more than one diode drop below V . They also resistor R and R . In this case, the currents through SS 1 2 clamp any voltages that go too far above V ; their the diodes D and D need to be limited by some other DD 1 2 breakdown voltage is high enough to allow normal mechanism. The resistors then serve as in-rush current operation, but not low enough to protect against slow limiters; the DC current into the input pins (V and V ) IP IM overvoltage (beyond V ) events. Very fast ESD should be very small. DD events (that meet the spec) are limited so that damage A significant amount of current can flow out of the does not occur. inputs (through the ESD diodes) when the common In some applications, it may be necessary to prevent mode voltage (V ) is below ground (V ); see CM SS excessive voltages from reaching the op amp inputs. Figure2-25. Figure4-5 shows one approach to protecting these inputs. D and D may be small signal silicon diodes, 4.2.1.4 Input Voltage Ranges 1 2 Schottky diodes for lower clamping voltages or diode- Figure4-7 shows possible input voltage values connected FETs for low leakage. (V =0V). Lines with a slope of +1 have constant V SS DM (e.g., the V =0 line). Lines with a slope of -1 have DM constant V (e.g., the V =V /2 line). V CM CM DD DD For normal operation, V and V must be kept within IP IM D U1 the region surrounded by the thick blue lines. The 1 MCP6N11 horizontal and vertical blue lines show the limits on the V 1 individual inputs. The blue lines with a slope of +1 show D2 the limits on VDM; the larger GMIN is, the closer they are to the V =0 line. V DM 2 The input voltage range specs (V and V ) change IVL IVH with the supply voltages (V and V , respectively). FIGURE 4-5: Protecting the Analog Inputs SS DD The differential input range specs (V and V ) Against High Voltages. DML DMH change with minimum gain (G ). Temperature also MIN affects these specs. 4.2.1.3 Input Current Limits To take full advantage of V and V , set V In order to prevent damage and/or improper operation DML DMH REF (see Figure1-6 and Figure1-7) so that the output of these amplifiers, the circuit must limit the currents (V ) is centered between the supplies (V and into the input pins (see Section1.1 “Absolute Maxi- OUT SS V ). mum Ratings†”). This requirement is independent of DD the voltage limits previously discussed. Figure4-6 shows one approach to protecting these VIP inputs. The resistors R1 and R2 limit the possible VIVH current in or out of the input pins (and into D1 and D2). VDD The diode currents will dump onto VDD. V DMH = M V V D DD V C M= U V V D1 M1CP6N11 =0 DD/2 1 R1 D V DM V DMH 2 = V M 2 V D VIM R2 0 V IVL V –min(V ,V ) min(R ,R )> SS 1 2 V0 V V 1 2 2mA IV D IV L D H max(V ,V )–V 1 2 DD min(R1,R2)> 2mA FIGURE 4-7: Input Voltage Ranges. FIGURE 4-6: Protecting the Analog Inputs Against High Currents. DS25073A-page 30 © 2011 Microchip Technology Inc.

MCP6N11 4.2.2 ENABLE/V CALIBRATION 4.3 Applications Tips OS (EN/CAL) 4.3.1 MINIMUM STABLE GAIN These parts have a Normal mode, a Low Power mode and a V Calibration mode. There are different options for different Minimum Stable OS Gains (1, 2, 5, 10 and 100V/V; see Table1-1). The When the EN/CAL pin is high and the internal POR differential gain (G ) needs to be greater than or (with delay) indicates that power is good, the part DM equal to G in order to maintain stability. operates in its Normal mode. MIN Picking a part with higher G has the advantages of When the EN/CAL pin is low, the part operates in its MIN lower Input Noise Voltage Density (e ), lower Input Low Power mode. The quiescent current (at V ) drops ni SS Offset Voltage (V ) and increased Gain Bandwidth to -2.5µA (typical), the amplifier output is put into a OS Product (GBWP); see Table1. The Differential Input high-impedance state. Signals at the input pins can Voltage Range (V ) is lower for higher G , but the feed through to the output pin. DMR MIN output voltage range would limit V anyway, when DMR When the EN/CAL pin goes high and the internal POR G ≥2. DM (with delay) indicates that power is good, the amplifier internally corrects its input offset voltage (V ) with the 4.3.2 CAPACITIVE LOADS OS internal common mode voltage at mid-supply (V /2) DD Driving large capacitive loads can cause stability and the output tri-stated (after t ). Once V Calibra- OFF OS problems for amplifiers. As the load capacitance tion is completed, the amplifier is enabled and normal increases, the feedback loop’s phase margin operation resumes. decreases, and the closed-loop bandwidth is reduced. The EN/CAL pin does not operate normally when left This produces gain peaking in the frequency response, floating. Either drive it with a logic output, or tie it high with overshoot and ringing in the step response. Lower so that the part is always on. gains (G ) exhibit greater sensitivity to capacitive DM loads. 4.2.3 POR WITH DELAY When driving large capacitive loads with these The internal POR makes sure that the input offset instrumentation amps (e.g., >100pF), a small series voltage (VOS) is calibrated whenever the supply resistor at the output (RISO in Figure4-8) improves the voltage goes from low voltage (<VPRL) to high voltage feedback loop’s phase margin (stability) by making the (>VPRH). This prevents corruption of the VOS trim reg- output load resistive at higher frequencies. The isters after a low-power event. bandwidth will be generally lower than the bandwidth After the POR goes high, the internal circuitry adds a with no capacitive load. fixed delay (t ), before telling the V Calibration PLH OS circuitry (see Figure4-2) to start. If the EN/CAL pin is VDD U1 toggled during this time, the fixed delay is restarted MCP6N11 (takes an additional time t ). PLH V R 1 ISO V 4.2.4 PARITY DETECTOR OUT A parity error detector monitors the memory contents V2 V RF CL FG for any corruption. In the rare event that a parity error is detected (e.g., corruption from an alpha particle), a R POR event is automatically triggered. This will cause G the input offset voltage to be re-corrected, and the op VREF amp will not return to normal operation for a period of FIGURE 4-8: Output Resistor, R time (the POR turn on time, t ). ISO PLH stabilizes large capacitive loads. 4.2.5 RAIL-TO-RAIL OUTPUT Figure4-9 gives recommended R values for ISO The Minimum Output Voltage (V ) and Maximum different capacitive loads and gains. The x-axis is the OL Output Voltage (VOH) specs describe the widest output normalized load capacitance (CLGMIN/GDM), where swing that can be achieved under the specified load GDM is the circuit’s differential gain (1+RF/RG) and conditions. GMIN is the minimum stable gain. The output can also be limited when V or V exceeds IP IM V or V , or when V exceeds V or V . IVL IVH DM DML DMH © 2011 Microchip Technology Inc. DS25073A-page 31

MCP6N11 In this data sheet, R +R =10kΩ for most gains (0Ω F G 1.E+100k4 for G =1); see Table1-6. This choice gives good DM Phase Margin. In general, R (Figure4-10) needs to (cid:5)) F ( meet the following limits to maintain stability: O RIS ed EQUATION 4-12: d1.E+10k3 n e m For G =1: m DM oo c R = 0 Re GMIN= 1 to 10 F GMIN= 100 1.E+10002 For G >1: 11.E00-1p0 1.E1n-09 1.1E0-n08 11.E00-0n7 1.E1μ-06 DM Normalized Load Capacitance; 2 CL GMIN/GDM(F) R <-------α-----G----D----M---------- FIGURE 4-9: Recommended R Values F 2πf C ISO GBWP G for Capacitive Loads. Where: After selecting R for your circuit, double check the α≤0.25 ISO resulting frequency response peaking and step G ≥G DM MIN response overshoot on the bench. Modify R ’s value ISO f =GainBandwidthProduct until the response is reasonable. GBWP C =C +C +(PCBstraycapacitance) G DM CM 4.3.3 GAIN RESISTORS Figure4-10 shows a simple gain circuit with the INA’s 4.3.4 SUPPLY BYPASS input capacitances at the feedback inputs (V and REF With these INAs, the power supply pin (V for single V ). These capacitances interact with R and R to DD FG G F supply) should have a local bypass capacitor (i.e., modify the gain at high frequencies. The equivalent 0.01µF to 0.1µF) within 2mm for good high frequency capacitance acting in parallel to R is C =C +C G G DM CM performance. Surface mount, multilayer ceramic plus any board capacitance in parallel to R . C will G G capacitors, or their equivalent, should be used. cause an increase in G at high frequencies, which DM reduces the phase margin of the feedback loop (i.e., These INAs require a bulk capacitor (i.e., 1.0µF or reduce the feedback loop's stability). larger) within 100mm, to provide large, slow currents. This bulk capacitor can be shared with other nearby analog parts as long as crosstalk through the supplies V DD U does not prove to be a problem. 1 V MCP6N11 1 V OUT V2 RF V FG C CCM CDM CM RG V REF FIGURE 4-10: Simple Gain Circuit with Parasitic Capacitances. DS25073A-page 32 © 2011 Microchip Technology Inc.

MCP6N11 4.4 Typical Applications 4.4.3 HIGH SIDE CURRENT DETECTOR Figure4-13 shows the MCP6N11 INA used as to detect 4.4.1 HIGH INPUT IMPEDANCE and amplify the high side current in a battery powered DIFFERENCE AMPLIFIER design. The INA gain is set at 21V/V, so V changes OUT Figure4-11 shows the MCP6N11 used as a difference 210mV for every 1mA of IDD current. The best GMIN amplifier. The inputs are high impedance and give good option to pick would be a gain of 10 (MCP6N11-010). CMRR performance. V BAT VDD U1 VDD 10Ω IDD +1t.o8V V MCP6N11 U1 +5.5V IP V MCP6N11 OUT V VIM V RF RF OUT FG V 200kΩ FG R G R G V 10kΩ REF V REF FIGURE 4-11: Difference Amplifier. (V –V ) BAT DD 4.4.2 DIFFERENCE AMPLIFIER FOR IDD= (10Ω) VERY LARGE COMMON MODE (V –V ) SIGNALS = OUT REF (10Ω)(21.0V/V) Figure4-12 shows the MCP6N11 INA used as a difference amplifier for signals with a very large FIGURE 4-13: High Side Current Detector. common mode component. The input resistor dividers (R and R ) ensure that the voltages at the INA’s inputs 4.4.4 WHEATSTONE BRIDGE 1 2 are within their range of normal operation. The Figure4-14 shows the MCP6N11 single capacitors C1, with the parasitic capacitances C2 (the instrumentation amp used to condition the signal from resistors’ parasitic capacitance plus the INA’s input a Wheatstone bridge (e.g., strain gage). The overall common mode capacitance, CCM), set the same INA gain is set at 201V/V. The best GMIN option to pick, division ratio, so that high-frequency signals (e.g., a for this gain, is 100V/V (MCP6N11-100). step in voltage) have the same gain. Select the INA gain to compensate for R and R ’s attenuation. Select 1 2 R1 and R2’s tolerances for good CMRR. VDD R1 R2 RW1 RW2 U1 V MCP6N11 1 C1 C2 RW2 RW1 VOUT R V F DD U 1 V 200kΩ FG MCP6N11 R V G OUT 1kΩ R V F REF V FG FIGURE 4-14: Wheatstone Bridge C1 C2 RG Amplifier. V 2 V R R REF 1 2 FIGURE 4-12: Difference Amplifier with Very Large Common Mode Component. © 2011 Microchip Technology Inc. DS25073A-page 33

MCP6N11 NOTES: DS25073A-page 34 © 2011 Microchip Technology Inc.

MCP6N11 5.0 DESIGN AIDS Microchip provides the basic design aids needed for the MCP6N11 instrumentation amplifiers. 5.1 Microchip Advanced Part Selector (MAPS) MAPS is a software tool that helps efficiently identify Microchip devices that fit a particular design requirement. Available at no cost from the Microchip website at www.microchip.com/maps, the MAPS is an overall selection tool for Microchip’s product portfolio that includes Analog, Memory, MCUs and DSCs. Using this tool, a customer can define a filter to sort features for a parametric search of devices and export side-by-side technical comparison reports. Helpful links are also provided for Data sheets, Purchase and Sampling of Microchip parts. 5.2 Analog Demonstration Board Microchip offers a broad spectrum of Analog Demonstration and Evaluation Boards that are designed to help customers achieve faster time tomarket. For a complete listing of these boards andtheir corresponding user’s guides and technical information, visit the Microchip web site at www.microchip.com/analog tools. 5.3 Application Notes The following Microchip Application Notes are available on the Microchip web site at www.microchip. com/appnotes and are recommended as supplemental reference resources. • AN884: “Driving Capacitive Loads With Op Amps”, DS00884 • AN990: “Analog Sensor Conditioning Circuits – AnOverview”, DS00990 • AN1228: “Op Amp Precision Design: Random Noise”, DS01228 Some of these application notes, and others, are listed in the design guide: • “Signal Chain Design Guide”, DS21825 © 2011 Microchip Technology Inc. DS25073A-page 35

MCP6N11 NOTES: DS25073A-page 36 © 2011 Microchip Technology Inc.

MCP6N11 6.0 PACKAGING INFORMATION 6.1 Package Marking Information 8-Lead SOIC (150 mil) (MCP6N11) Example 6N11001E SN^e^3 1121 256 NNN Note: The example is for a MCP6N11-001 part. 8-Lead TDFN (2×3) (MCP6N11) Example Device Code MCP6N11-001 AAQ MCP6N11-002 AAR AAQ 121 MCP6N11-005 AAS 25 MCP6N11-010 AAT MCP6N11-100 AAU Note: Applies to 8-Lead 2x3 TDFN Legend: XX...X Customer-specific information Y Year code (last digit of calendar year) YY Year code (last 2 digits of calendar year) WW Week code (week of January 1 is week ‘01’) NNN Alphanumeric traceability code e3 Pb-free JEDEC designator for Matte Tin (Sn) * This package is Pb-free. The Pb-free JEDEC designator ( e 3 ) can be found on the outer packaging for this package. Note: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information. © 2011 Microchip Technology Inc. DS25073A-page 37

MCP6N11 Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging DS25073A-page 38 © 2011 Microchip Technology Inc.

MCP6N11 Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging © 2011 Microchip Technology Inc. DS25073A-page 39

MCP6N11 (cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8)(cid:9)(cid:10)(cid:6)(cid:11)(cid:12)(cid:13)(cid:14)(cid:8)(cid:15)(cid:16)(cid:6)(cid:10)(cid:10)(cid:8)(cid:17)(cid:18)(cid:12)(cid:10)(cid:13)(cid:19)(cid:5)(cid:8)(cid:20)(cid:15)(cid:21)(cid:22)(cid:8)(cid:23)(cid:8)(cid:21)(cid:6)(cid:24)(cid:24)(cid:25)(cid:26)(cid:27)(cid:8)(cid:28)(cid:29)(cid:30)(cid:31)(cid:8)(cid:16)(cid:16)(cid:8) (cid:25)(cid:7)!(cid:8)"(cid:15)(cid:17)#$% (cid:21)(cid:25)(cid:12)(cid:5)& (cid:30)(cid:10)(cid:9)(cid:2)(cid:31)(cid:11)(cid:14)(cid:2)!(cid:10)"(cid:31)(cid:2)(cid:8)#(cid:9)(cid:9)(cid:14)(cid:15)(cid:31)(cid:2)(cid:12)(cid:28)(cid:8)$(cid:28)(cid:17)(cid:14)(cid:2)%(cid:9)(cid:28)&(cid:7)(cid:15)(cid:17)"’(cid:2)(cid:12)(cid:16)(cid:14)(cid:28)"(cid:14)(cid:2)"(cid:14)(cid:14)(cid:2)(cid:31)(cid:11)(cid:14)(cid:2)(cid:6)(cid:7)(cid:8)(cid:9)(cid:10)(cid:8)(cid:11)(cid:7)(cid:12)(cid:2)((cid:28)(cid:8)$(cid:28)(cid:17)(cid:7)(cid:15)(cid:17)(cid:2)(cid:22)(cid:12)(cid:14)(cid:8)(cid:7))(cid:7)(cid:8)(cid:28)(cid:31)(cid:7)(cid:10)(cid:15)(cid:2)(cid:16)(cid:10)(cid:8)(cid:28)(cid:31)(cid:14)%(cid:2)(cid:28)(cid:31)(cid:2) (cid:11)(cid:31)(cid:31)(cid:12)*++&&&(cid:20)!(cid:7)(cid:8)(cid:9)(cid:10)(cid:8)(cid:11)(cid:7)(cid:12)(cid:20)(cid:8)(cid:10)!+(cid:12)(cid:28)(cid:8)$(cid:28)(cid:17)(cid:7)(cid:15)(cid:17) DS25073A-page 40 © 2011 Microchip Technology Inc.

MCP6N11 Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging © 2011 Microchip Technology Inc. DS25073A-page 41

MCP6N11 Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging DS25073A-page 42 © 2011 Microchip Technology Inc.

MCP6N11 (cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8)(cid:9)(cid:10)(cid:6)(cid:11)(cid:12)(cid:13)(cid:14)(cid:8)’(cid:18)(cid:6)(cid:10)(cid:8)((cid:10)(cid:6)(cid:12)(cid:27)(cid:8)(cid:21)(cid:25)(cid:8)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8)(cid:9)(cid:6)(cid:14))(cid:6)*(cid:5)(cid:8)(cid:20)+(cid:21)(cid:22)(cid:8)(cid:23)(cid:8),-(cid:28)-(cid:31)(cid:29)./(cid:8)(cid:16)(cid:16)(cid:8) (cid:25)(cid:7)!(cid:8)"0’((cid:21)% (cid:21)(cid:25)(cid:12)(cid:5)& (cid:30)(cid:10)(cid:9)(cid:2)(cid:31)(cid:11)(cid:14)(cid:2)!(cid:10)"(cid:31)(cid:2)(cid:8)#(cid:9)(cid:9)(cid:14)(cid:15)(cid:31)(cid:2)(cid:12)(cid:28)(cid:8)$(cid:28)(cid:17)(cid:14)(cid:2)%(cid:9)(cid:28)&(cid:7)(cid:15)(cid:17)"’(cid:2)(cid:12)(cid:16)(cid:14)(cid:28)"(cid:14)(cid:2)"(cid:14)(cid:14)(cid:2)(cid:31)(cid:11)(cid:14)(cid:2)(cid:6)(cid:7)(cid:8)(cid:9)(cid:10)(cid:8)(cid:11)(cid:7)(cid:12)(cid:2)((cid:28)(cid:8)$(cid:28)(cid:17)(cid:7)(cid:15)(cid:17)(cid:2)(cid:22)(cid:12)(cid:14)(cid:8)(cid:7))(cid:7)(cid:8)(cid:28)(cid:31)(cid:7)(cid:10)(cid:15)(cid:2)(cid:16)(cid:10)(cid:8)(cid:28)(cid:31)(cid:14)%(cid:2)(cid:28)(cid:31)(cid:2) (cid:11)(cid:31)(cid:31)(cid:12)*++&&&(cid:20)!(cid:7)(cid:8)(cid:9)(cid:10)(cid:8)(cid:11)(cid:7)(cid:12)(cid:20)(cid:8)(cid:10)!+(cid:12)(cid:28)(cid:8)$(cid:28)(cid:17)(cid:7)(cid:15)(cid:17) © 2011 Microchip Technology Inc. DS25073A-page 43

MCP6N11 NOTES: DS25073A-page 44 © 2011 Microchip Technology Inc.

MCP6N11 APPENDIX A: REVISION HISTORY Revision A (October 2011) • Original Release of this Document. © 2011 Microchip Technology Inc. DS25073A-page 45

MCP6N11 NOTES: DS25073A-page 46 © 2011 Microchip Technology Inc.

MCP6N11 PRODUCT IDENTIFICATION SYSTEM To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office. PART NO. –X X /XX Examples: Device Gain Temperature Package a) MCP6N11T-001E/MNY: Tape and Reel, Option Range Minimum gain = 1, Extended temperature, 8LD 2×3TDFN. b) MCP6N11-002E/SN: Minimum gain = 2, Device: MCP6N11 Single Instrumentation Amplifier Extended temperature, MCP6N11T Single Instrumentation Amplifier 8LD SOIC. (Tape and Reel) Gain Option: 001 = Minimum gain of 1V/V 002 = Minimum gain of 2V/V 005 = Minimum gain of 5V/V 010 = Minimum gain of 10V/V 100 = Minimum gain of 100V/V Temperature Range: E = -40°C to +125°C Package: MNY = 2×3TDFN, 8-lead * SN = Plastic SOIC (150mil Body), 8-lead *Y = nickel palladium gold manufacturing designator. Only available on the TDFN package. © 2011 Microchip Technology Inc. DS25073A-page 47

MCP6N11 NOTES: DS25073A-page 48 © 2011 Microchip Technology Inc.

Note the following details of the code protection feature on Microchip devices: • Microchip products meet the specification contained in their particular Microchip Data Sheet. • Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions. • There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip’s Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property. • Microchip is willing to work with the customer who is concerned about the integrity of their code. • Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as “unbreakable.” Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip’s code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act. Information contained in this publication regarding device Trademarks applications and the like is provided only for your convenience The Microchip name and logo, the Microchip logo, dsPIC, and may be superseded by updates. It is your responsibility to KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, ensure that your application meets with your specifications. PIC32 logo, rfPIC and UNI/O are registered trademarks of MICROCHIP MAKES NO REPRESENTATIONS OR Microchip Technology Incorporated in the U.S.A. and other WARRANTIES OF ANY KIND WHETHER EXPRESS OR countries. IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, INCLUDING BUT NOT LIMITED TO ITS CONDITION, MXDEV, MXLAB, SEEVAL and The Embedded Control QUALITY, PERFORMANCE, MERCHANTABILITY OR Solutions Company are registered trademarks of Microchip FITNESS FOR PURPOSE. Microchip disclaims all liability Technology Incorporated in the U.S.A. arising from this information and its use. Use of Microchip Analog-for-the-Digital Age, Application Maestro, chipKIT, devices in life support and/or safety applications is entirely at chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, the buyer’s risk, and the buyer agrees to defend, indemnify and dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, hold harmless Microchip from any and all damages, claims, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, suits, or expenses resulting from such use. No licenses are Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, conveyed, implicitly or otherwise, under any Microchip MPLINK, mTouch, Omniscient Code Generation, PICC, intellectual property rights. PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. SQTP is a service mark of Microchip Technology Incorporated in the U.S.A. All other trademarks mentioned herein are property of their respective companies. © 2011, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved. Printed on recycled paper. ISBN: 978-1-61341-685-3 Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company’s quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip’s quality system for the design and manufacture of development systems is ISO 9001:2000 certified. © 2011 Microchip Technology Inc. DS25073A-page 49

Worldwide Sales and Service AMERICAS ASIA/PACIFIC ASIA/PACIFIC EUROPE Corporate Office Asia Pacific Office India - Bangalore Austria - Wels 2355 West Chandler Blvd. Suites 3707-14, 37th Floor Tel: 91-80-3090-4444 Tel: 43-7242-2244-39 Chandler, AZ 85224-6199 Tower 6, The Gateway Fax: 91-80-3090-4123 Fax: 43-7242-2244-393 Tel: 480-792-7200 Harbour City, Kowloon India - New Delhi Denmark - Copenhagen Fax: 480-792-7277 Hong Kong Tel: 91-11-4160-8631 Tel: 45-4450-2828 Technical Support: Tel: 852-2401-1200 Fax: 91-11-4160-8632 Fax: 45-4485-2829 http://www.microchip.com/ support Fax: 852-2401-3431 India - Pune France - Paris Web Address: Australia - Sydney Tel: 91-20-2566-1512 Tel: 33-1-69-53-63-20 www.microchip.com Tel: 61-2-9868-6733 Fax: 91-20-2566-1513 Fax: 33-1-69-30-90-79 Atlanta Fax: 61-2-9868-6755 Japan - Yokohama Germany - Munich Duluth, GA China - Beijing Tel: 81-45-471- 6166 Tel: 49-89-627-144-0 Tel: 86-10-8569-7000 Fax: 49-89-627-144-44 Tel: 678-957-9614 Fax: 81-45-471-6122 Fax: 678-957-1455 Fax: 86-10-8528-2104 Korea - Daegu Italy - Milan Boston China - Chengdu Tel: 82-53-744-4301 Tel: 39-0331-742611 Westborough, MA Tel: 86-28-8665-5511 Fax: 82-53-744-4302 Fax: 39-0331-466781 Tel: 774-760-0087 Fax: 86-28-8665-7889 Korea - Seoul Netherlands - Drunen Fax: 774-760-0088 China - Chongqing Tel: 82-2-554-7200 Tel: 31-416-690399 Chicago Tel: 86-23-8980-9588 Fax: 82-2-558-5932 or Fax: 31-416-690340 Itasca, IL Fax: 86-23-8980-9500 82-2-558-5934 Spain - Madrid Tel: 630-285-0071 China - Hangzhou Malaysia - Kuala Lumpur Tel: 34-91-708-08-90 Fax: 630-285-0075 Tel: 86-571-2819-3187 Tel: 60-3-6201-9857 Fax: 34-91-708-08-91 Cleveland Fax: 86-571-2819-3189 Fax: 60-3-6201-9859 UK - Wokingham Independence, OH China - Hong Kong SAR Malaysia - Penang Tel: 44-118-921-5869 Tel: 216-447-0464 Tel: 852-2401-1200 Tel: 60-4-227-8870 Fax: 44-118-921-5820 Fax: 216-447-0643 Fax: 852-2401-3431 Fax: 60-4-227-4068 Dallas China - Nanjing Philippines - Manila Addison, TX Tel: 86-25-8473-2460 Tel: 63-2-634-9065 Tel: 972-818-7423 Fax: 86-25-8473-2470 Fax: 63-2-634-9069 Fax: 972-818-2924 China - Qingdao Singapore Detroit Tel: 86-532-8502-7355 Tel: 65-6334-8870 Farmington Hills, MI Fax: 86-532-8502-7205 Fax: 65-6334-8850 Tel: 248-538-2250 Fax: 248-538-2260 China - Shanghai Taiwan - Hsin Chu Tel: 86-21-5407-5533 Tel: 886-3-5778-366 Indianapolis Fax: 86-21-5407-5066 Fax: 886-3-5770-955 Noblesville, IN Tel: 317-773-8323 China - Shenyang Taiwan - Kaohsiung Fax: 317-773-5453 Tel: 86-24-2334-2829 Tel: 886-7-536-4818 Fax: 86-24-2334-2393 Fax: 886-7-330-9305 Los Angeles Mission Viejo, CA China - Shenzhen Taiwan - Taipei Tel: 86-755-8203-2660 Tel: 886-2-2500-6610 Tel: 949-462-9523 Fax: 949-462-9608 Fax: 86-755-8203-1760 Fax: 886-2-2508-0102 China - Wuhan Thailand - Bangkok Santa Clara Santa Clara, CA Tel: 86-27-5980-5300 Tel: 66-2-694-1351 Tel: 408-961-6444 Fax: 86-27-5980-5118 Fax: 66-2-694-1350 Fax: 408-961-6445 China - Xian Tel: 86-29-8833-7252 Toronto Mississauga, Ontario, Fax: 86-29-8833-7256 Canada China - Xiamen Tel: 905-673-0699 Tel: 86-592-2388138 Fax: 905-673-6509 Fax: 86-592-2388130 China - Zhuhai Tel: 86-756-3210040 08/02/11 Fax: 86-756-3210049 DS25073A-page 50 © 2011 Microchip Technology Inc.

Datasheet下载

Datasheet下载