ICGOO在线商城 > 分立半导体产品 > 晶体管 - FET,MOSFET - 单 > AOT9N50

- 型号: AOT9N50

- 制造商: ALPHA&OMEGA

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

AOT9N50产品简介:

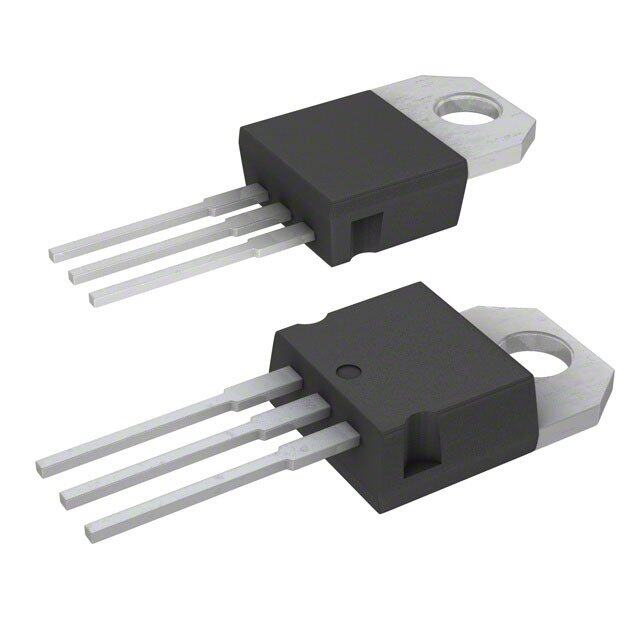

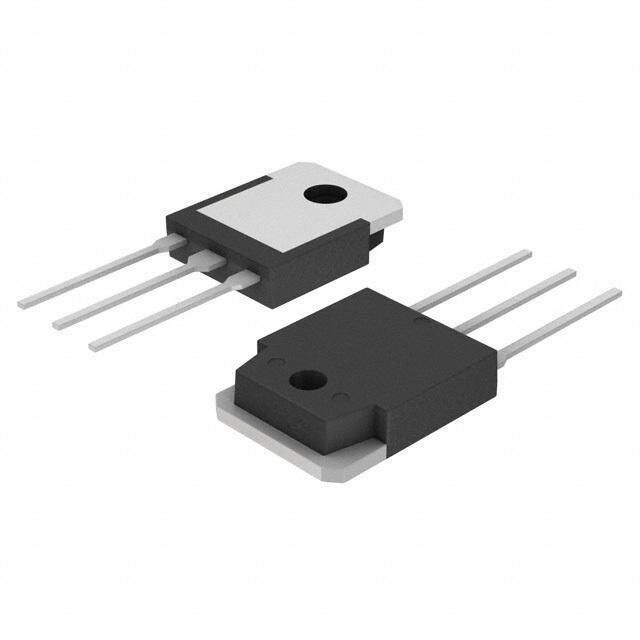

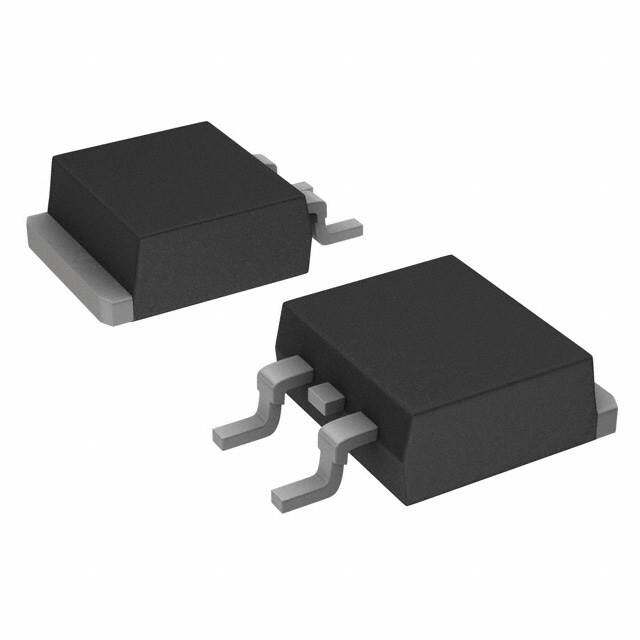

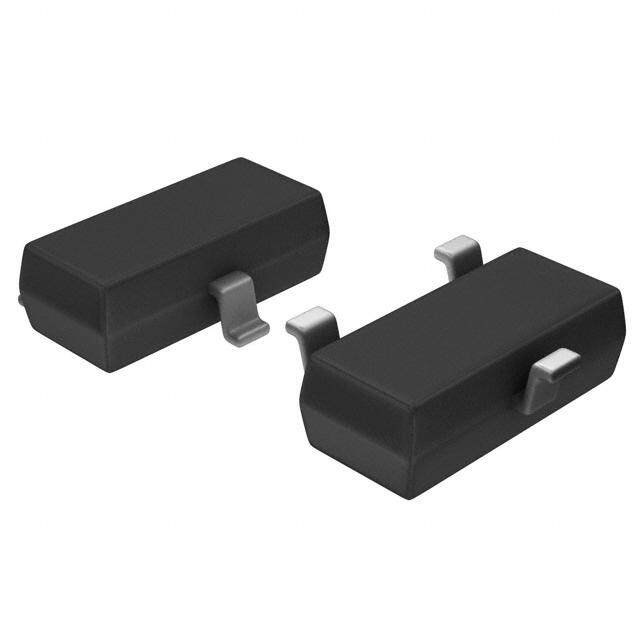

ICGOO电子元器件商城为您提供AOT9N50由ALPHA&OMEGA设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 AOT9N50价格参考。ALPHA&OMEGAAOT9N50封装/规格:晶体管 - FET,MOSFET - 单, 通孔 N 沟道 500V 9A(Tc) 192W(Tc) TO-220。您可以下载AOT9N50参考资料、Datasheet数据手册功能说明书,资料中有AOT9N50 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | |

| 描述 | MOSFET N-CH 500V 9A TO-220 |

| 产品分类 | FET - 单 |

| FET功能 | 标准 |

| FET类型 | MOSFET N 通道,金属氧化物 |

| 品牌 | Alpha & Omega Semiconductor Inc |

| 数据手册 | |

| 产品图片 |

|

| 产品型号 | AOT9N50 |

| rohs | 无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | - |

| 不同Id时的Vgs(th)(最大值) | 4.5V @ 250µA |

| 不同Vds时的输入电容(Ciss) | 1042pF @ 25V |

| 不同Vgs时的栅极电荷(Qg) | 28nC @ 10V |

| 不同 Id、Vgs时的 RdsOn(最大值) | 850 毫欧 @ 4.5A,10V |

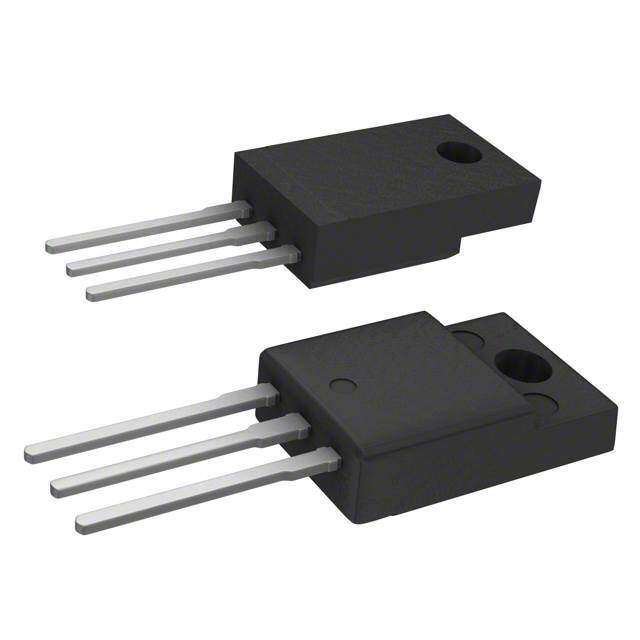

| 供应商器件封装 | TO-220 |

| 其它名称 | 785-1172-5 |

| 功率-最大值 | 192W |

| 包装 | 管件 |

| 安装类型 | 通孔 |

| 封装/外壳 | TO-220-3 |

| 标准包装 | 1,000 |

| 漏源极电压(Vdss) | 500V |

| 电流-连续漏极(Id)(25°C时) | 9A (Tc) |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

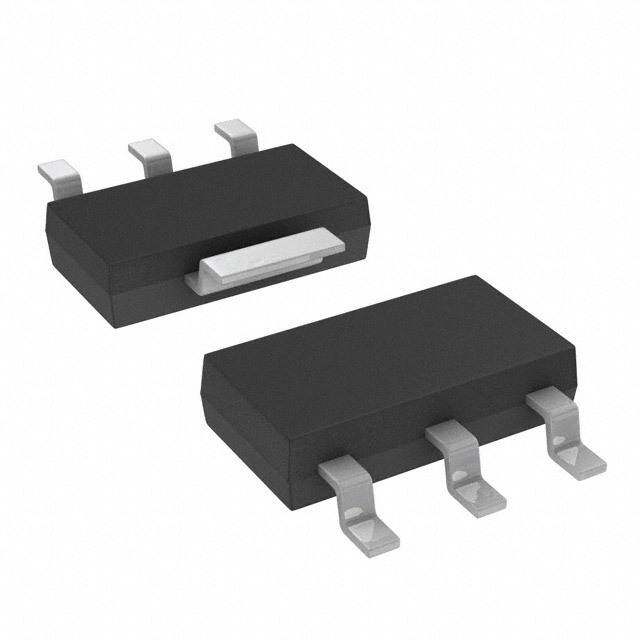

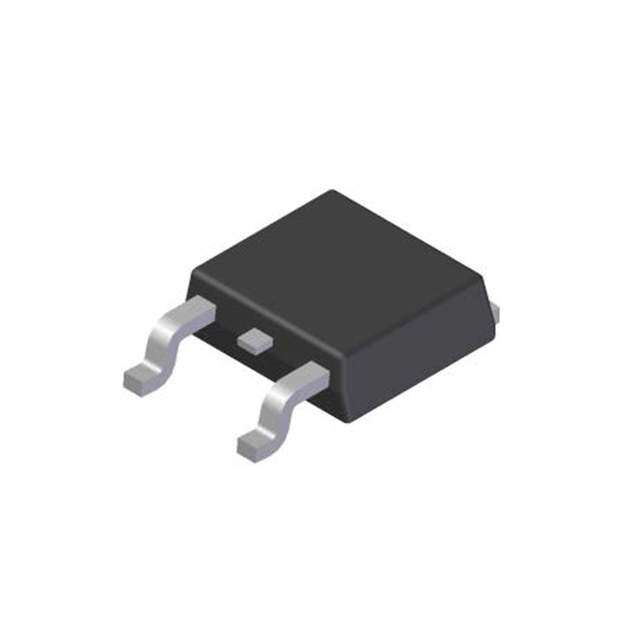

AOT9N50/AOTF9N50 500V, 9A N-Channel MOSFET General Description Product Summary The AOT9N50 & AOTF9N50 have been fabricated using VDS 600V@150℃ an advanced high voltage MOSFET process that is I (at V =10V) 9A D GS designed to deliver high levels of performance and R (at V =10V) < 0.85W robustness in popular AC-DC applications. DS(ON) GS By providing low R , C and C along with DS(on) iss rss guaranteed avalanche capability these parts can be adopted quickly into new and existing offline power supply designs. 100% UIS Tested 100% R Tested g For Halogen Free add "L" suffix to part number: AOT9N50L & AOTF9N50L TO-220 Top View TO-220F D G G G D D S S S Absolute Maximum Ratings T =25°C unless otherwise noted A Parameter Symbol AOT9N50 AOTF9N50 Units Drain-Source Voltage V 500 V DS Gate-Source Voltage V ±30 V GS Continuous Drain TC=25°C I 9 9* Current T =100°C D 6.0 6* A C Pulsed Drain Current C I 30 DM Avalanche Current C I 3.2 A AR Repetitive avalanche energy C E 154 mJ AR Single plused avalanche energy G E 307 mJ AS Peak diode recovery dv/dt dv/dt 5 V/ns T =25°C 192 38.5 W C P Power Dissipation B Derate above 25oC D 1.5 0.3 W/ oC Junction and Storage Temperature Range T, T -55 to 150 °C J STG Maximum lead temperature for soldering purpose, 1/8" from case for 5 seconds TL 300 °C Thermal Characteristics Parameter Symbol AOT9N50 AOTF9N50 Units Maximum Junction-to-Ambient A,D RqJA 65 65 °C/W Maximum Case-to-sink A RqCS 0.5 -- °C/W Maximum Junction-to-Case RqJC 0.65 3.25 °C/W * Drain current limited by maximum junction temperature. Rev3: July 2010 www.aosmd.com Page 1 of 6

AOT9N50/AOTF9N50 Electrical Characteristics (T=25°C unless otherwise noted) J Symbol Parameter Conditions Min Typ Max Units STATIC PARAMETERS I =250µA, V =0V, T=25°C 500 BV Drain-Source Breakdown Voltage D GS J DSS I =250µA, V =0V, T=150°C 600 V D GS J BV Breakdown Voltage Temperature /∆TDJSS Coefficient ID=250µA, VGS=0V 0.56 V/ oC V =500V, V =0V 1 IDSS Zero Gate Voltage Drain Current VDS=400V, TG=S125°C 10 m A DS J I Gate-Body leakage current V =0V, V =±30V ±100 nA GSS DS GS V Gate Threshold Voltage V =5V I =250m A 3.4 4 4.5 V GS(th) DS D R Static Drain-Source On-Resistance V =10V, I =4.5A 0.66 0.85 W DS(ON) GS D g Forward Transconductance V =40V, I =4.5A 10 S FS DS D V Diode Forward Voltage I =1A,V =0V 0.74 1 V SD S GS I Maximum Body-Diode Continuous Current 9 A S I Maximum Body-Diode Pulsed Current 30 A SM DYNAMIC PARAMETERS C Input Capacitance 694 868 1042 pF iss C Output Capacitance V =0V, V =25V, f=1MHz 74 93 112 pF oss GS DS C Reverse Transfer Capacitance 6.2 7.8 9.4 pF rss R Gate resistance V =0V, V =0V, f=1MHz 2 4 6 W g GS DS SWITCHING PARAMETERS Q Total Gate Charge 15 23.6 28 nC g Q Gate Source Charge V =10V, V =400V, I =9A 4 5.2 6.2 nC gs GS DS D Q Gate Drain Charge 8.5 10.6 12.7 nC gd t Turn-On DelayTime 19.5 ns D(on) t Turn-On Rise Time V =10V, V =250V, I =9A, 47 ns r GS DS D tD(off) Turn-Off DelayTime RG=25W 51.5 ns t Turn-Off Fall Time 38.5 ns f trr Body Diode Reverse Recovery Time IF=9A,dI/dt=100A/m s,VDS=100V 195 248 300 ns Qrr Body Diode Reverse Recovery Charge IF=9A,dI/dt=100A/m s,VDS=100V 2.5 3.5 4.5 m C A. The value of R qJA is measured with the device in a still air environment with T A =25°C. B. The power dissipation P is based on T =150°C, using junction-to-case thermal resistance, and is more useful in setting the upper D J(MAX) dissipation limit for cases where additional heatsinking is used. C. Repetitive rating, pulse width limited by junction temperature T =150°C, Ratings are based on low frequency and duty cycles to keep initial T J(MAX) J =25°C. D. The R qJA is the sum of the thermal impedence from junction to case R qJC and case to ambient. E. The static characteristics in Figures 1 to 6 are obtained using <300 m s pulses, duty cycle 0.5% max. F. These curves are based on the junction-to-case thermal impedence which is measured with the device mounted to a large heatsink, assuming a maximum junction temperature of T =150°C. The SOA curve provides a single pulse rating. J(MAX) G. L=60mH, I =3.2A, V =150V, R =25Ω, Starting T=25°C AS DD G J THIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN, FUNCTIONS AND RELIABILITY WITHOUT NOTICE. Rev3: July 2010 www.aosmd.com Page 2 of 6

AOT9N50/AOTF9N50 TYPICAL ELECTRICAL AND THERMAL CHARACTERISTICS 18 100 10V -55°C V =40V 15 DS 6.5V 12 10 6V I (A)D 9 I(A)D 125°C 6 1 V =5.5V GS 25°C 3 0 0.1 0 5 10 15 20 25 30 2 4 6 8 10 VDS (Volts) VGS(Volts) Fig 1: On-Region Characteristics Figure 2: Transfer Characteristics 2.0 3 e 2.5 V =10V 1.5 stanc 2 IDG=S4.5A ) si WR (DS(ON) 1.0 d On-Re 1.5 e z 0.5 VGS=10V mali 1 or N 0.5 0.0 0 4 8 12 16 20 0 -100 -50 0 50 100 150 200 I (A) D Temperature (°C) Figure 3: On-Resistance vs. Drain Current and Gate Figure 4: On-Resistance vs. Junction Temperature Voltage 1.2 1.0E+02 1.0E+01 d) 1.1 1.0E+4000 e z 125°C mali A) 1.0E-01 Nor 1 I (S 1.0E-02 25°C V (DSS 1.0E-03 B 0.9 1.0E-04 1.0E-05 0.8 0.0 0.2 0.4 0.6 0.8 1.0 -100 -50 0 50 100 150 200 V (Volts) T (°C) SD J Figure 6: Body-Diode Characteristics (Note E) Figure 5:Break Down vs. Junction Temperature Rev3: July 2010 www.aosmd.com Page 3 of 6

AOT9N50/AOTF9N50 TYPICAL ELECTRICAL AND THERMAL CHARACTERISTICS 15 10000 VDS=400V Ciss I =9A 12 D 1000 F) p C olts) 9 nce ( oss V a 100 (S cit VG 6 pa a C 10 3 C rss 0 1 0 5 10 15 20 25 30 35 0.1 1 10 100 Qg (nC) VDS (Volts) Figure 7: Gate-Charge Characteristics Figure 8: Capacitance Characteristics 100 100 10m s 10 RDS(ON) 10 RDS(ON) 10m s limited limited mps) 1 11m00sm s mps) 1 11m00sm s A A I (D 10ms I (D 10ms DC DC 0.1s 0.1 TJ(Max)=150°C 0.1 TJ(Max)=150°C 1s TC=25°C TC=25°C 0.01 0.01 1 10 100 1000 1 10 100 1000 VDS (Volts) VDS (Volts) Figure 9: Maximum Forward Biased Safe Figure 10: Maximum Forward Biased Safe Operating Operating Area for AOT9N50 (Note F) Area for AOTF9N50 (Note F) 10 8 A) (D g I 6 n ati nt r 4 e urr C 2 0 0 25 50 75 100 125 150 T (°C) CASE Figure 11: Current De-rating (Note B) Rev3: July 2010 www.aosmd.com Page 4 of 6

AOT9N50/AOTF9N50 TYPICAL ELECTRICAL AND THERMAL CHARACTERISTICS 10 D=T /T on In descending order ent TJ,PK=TC+PDM.ZqJC.RqJC D=0.5, 0.3, 0.1, 0.05, 0.02, 0.01, single pulse nsi nce 1 RqJC=0.65°C/W Tra sta d si e e maliz mal R 0.1 PD NorJCTher0.01 Ton T Zq Single Pulse 0.001 0.00001 0.0001 0.001 0.01 0.1 1 10 100 Pulse Width (s) Figure 12: Normalized Maximum Transient Thermal Impedance for AOT9N50 (Note F) 10 D=T /T In descending order on ent TJ,PK=TC+PDM.ZqJC.RqJC D=0.5, 0.3, 0.1, 0.05, 0.02, 0.01, single pulse nsi nce 1 RqJC=3.25°C/W Tra sta d si e e z R 0.1 mali mal PD Nor her CT 0.01 T J on Zq T Single Pulse 0.001 0.00001 0.0001 0.001 0.01 0.1 1 10 100 Pulse Width (s) Figure 13: Normalized Maximum Transient Thermal Impedance for AOTF9N50 (Note F) Rev3: July 2010 www.aosmd.com Page 5 of 6

AOT9N50/AOTF9N50 Gate Charge Test Circuit & Waveform Vgs Qg + 10V + VDC Qgs Qgd - Vds VDC - DUT Vgs Ig Charge Resistive Switching Test Circuit & Waveforms RL Vds Vds 90% + Vgs DUT Vdd VDC Rg - 10% Vgs Vgs td(on) tr td(off) tf ton toff Unclamped Inductive Switching (UIS) Test Circuit & Waveforms L 2 Vds E A R= 1/2 LI AR BVDSS Id Vds + Vgs Vgs VDC Vdd IAR Rg - Id DUT Vgs Vgs Diode Recovery Test Circuit & Waveforms Vds + Q r r = - Idt DUT Vgs Vds - L Isd I t Isd F dI/dt rr + I Vgs VDC Vdd RM Vdd - Vds Ig Rev3: July 2010 www.aosmd.com Page 6 of 6

Datasheet下载

Datasheet下载