ICGOO在线商城 > 传感器,变送器 > 运动传感器 - 加速计 > ADXL362BCCZ-R2

- 型号: ADXL362BCCZ-R2

- 制造商: Analog

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

ADXL362BCCZ-R2产品简介:

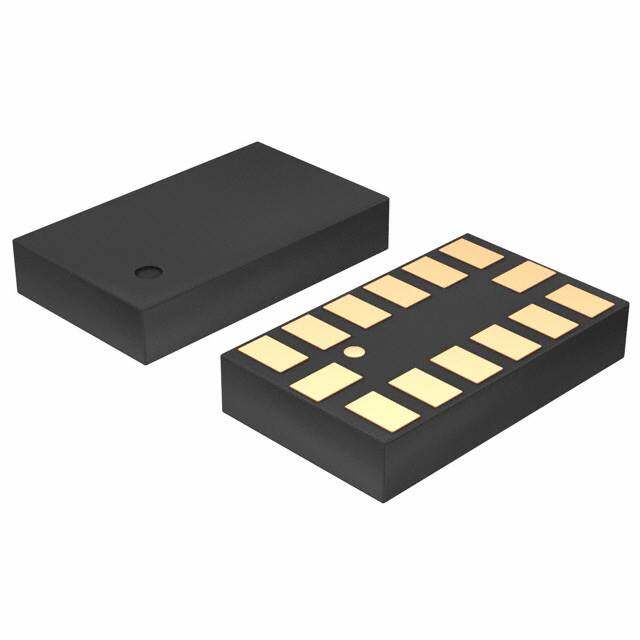

ICGOO电子元器件商城为您提供ADXL362BCCZ-R2由Analog设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 ADXL362BCCZ-R2价格参考。AnalogADXL362BCCZ-R2封装/规格:运动传感器 - 加速计, Accelerometer X, Y, Z Axis ±2g, 4g, 8g 6.25Hz ~ 400Hz 16-LGA (3x3.25)。您可以下载ADXL362BCCZ-R2参考资料、Datasheet数据手册功能说明书,资料中有ADXL362BCCZ-R2 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | |

| 描述 | IC ACCEL DIG LO PWR 3AX 16LGA加速计 Micropower 3-Axis Digital Output MEMS |

| 产品分类 | 加速计运动与定位传感器 |

| 品牌 | Analog Devices Inc |

| 产品手册 | |

| 产品图片 |

|

| rohs | RoHS 合规性豁免无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 加速计,Analog Devices ADXL362BCCZ-R2- |

| 数据手册 | |

| 产品型号 | ADXL362BCCZ-R2 |

| 产品种类 | 加速计 |

| 传感轴 | Triple |

| 供应商器件封装 | 16-LGA (3x3.25) |

| 其它名称 | ADXL362BCCZ-R2-ND |

| 分辨率 | 12 bit |

| 加速 | 5000 g |

| 加速度范围 | ±2g, 4g, 8g |

| 商标 | Analog Devices |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装 | Reel |

| 封装/外壳 | 16-TFLGA |

| 封装/箱体 | LGA-16 |

| 工厂包装数量 | 250 |

| 带宽 | 50Hz |

| 接口 | 串行 |

| 数字输出-位数 | 12 bit |

| 数字输出-总线接口 | SPI |

| 最大工作温度 | + 85 C |

| 最小工作温度 | - 40 C |

| 标准包装 | 250 |

| 灵敏度 | 1000LSB/g,500LSB/g,250LSB/g |

| 特色产品 | http://www.digikey.cn/product-highlights/cn/zh/analog-devices-adxl362-mems-accelerometer/3334 |

| 电压-电源 | 1.6 V ~ 3.5 V |

| 电源电压-最大 | 3.5 V |

| 电源电压-最小 | 1.6 V |

| 电源电流 | 1.8 uA |

| 系列 | ADXL362 |

| 视频文件 | http://www.digikey.cn/classic/video.aspx?PlayerID=1364138032001&width=640&height=505&videoID=2245193160001http://www.digikey.cn/classic/video.aspx?PlayerID=1364138032001&width=640&height=505&videoID=2245193171001http://www.digikey.cn/classic/video.aspx?PlayerID=1364138032001&width=640&height=505&videoID=2245193161001http://www.digikey.cn/classic/video.aspx?PlayerID=1364138032001&width=640&height=505&videoID=2245193172001 |

| 轴 | X,Y,Z |

| 输出类型 | SPI |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

Micropower, 3-Axis, ±2 g/±4 g/±8 g Digital Output MEMS Accelerometer Data Sheet ADXL362 FEATURES GENERAL DESCRIPTION Ultralow power The ADXL362 is an ultralow power, 3-axis MEMS accelerometer Power can be derived from coin cell battery that consumes less than 2 µA at a 100 Hz output data rate and 1.8 µA at 100 Hz ODR, 2.0 V supply 270 nA when in motion triggered wake-up mode. Unlike 3.0 µA at 400 Hz ODR, 2.0 V supply accelerometers that use power duty cycling to achieve low power 270 nA motion activated wake-up mode consumption, the ADXL362 does not alias input signals by 10 nA standby current undersampling; it samples the full bandwidth of the sensor at all High resolution: 1 mg/LSB data rates. Built-in features for system-level power savings: The ADXL362 always provides 12-bit output resolution; 8-bit Adjustable threshold sleep/wake modes for motion formatted data is also provided for more efficient single-byte activation transfers when a lower resolution is sufficient. Measurement Autonomous interrupt processing, without need for ranges of ±2 g, ±4 g, and ±8 g are available, with a resolution of microcontroller intervention, to allow the rest of the 1 mg/LSB on the ±2 g range. For applications where a noise level system to be turned off completely lower than the normal 550 µg/√Hz of the ADXL362 is desired, Deep embedded FIFO minimizes host processor load either of two lower noise modes (down to 175 µg/√Hz typical) Awake state output enables implementation of can be selected at minimal increase in supply current. standalone, motion activated switch Low noise down to 175 µg/√Hz In addition to its ultralow power consumption, the ADXL362 Wide supply and I/O voltage ranges: 1.6 V to 3.5 V has many features to enable true system level power reduction. Operates off 1.8 V to 3.3 V rails It includes a deep multimode output FIFO, a built-in micropower Acceleration sample synchronization via external trigger temperature sensor, and several activity detection modes including On-chip temperature sensor adjustable threshold sleep and wake-up operation that can run SPI digital interface as low as 270 nA at a 6 Hz (approximate) measurement rate. A Measurement ranges selectable via SPI command pin output is provided to directly control an external switch when Small and thin 3 mm × 3.25 mm × 1.06 mm package activity is detected, if desired. In addition, the ADXL362 has provisions for external control of sampling time and/or an APPLICATIONS external clock. Hearing aids The ADXL362 operates on a wide 1.6 V to 3.5 V supply range, Home healthcare devices and can interface, if necessary, to a host operating on a separate, Motion enabled power save switches lower supply voltage. The ADXL362 is available in a 3 mm × Wireless sensors 3.25 mm × 1.06 mm package. Motion enabled metering devices FUNCTIONAL BLOCK DIAGRAM VS VDDI/O INT1 3-AXIS INT2 SMENESMOSR 1A2-DBCIT DLIOGGITIACL, MOSI FIFO, MISO AND SPI CS SCLK AXIS ANTIALIASING DEMODULATORS FILTERS TEMPERATURE ADXL362 SENSOR GND 10776-001 Figure 1. Rev. E Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Tel: 781.329.4700 ©2012–2016 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. Technical Support www.analog.com

ADXL362 Data Sheet TABLE OF CONTENTS Features .............................................................................................. 1 Device ID Register ..................................................................... 24 Applications ....................................................................................... 1 Device ID: 0x1D Register .......................................................... 24 General Description ......................................................................... 1 Part ID: 0xF2 Register ................................................................ 24 Functional Block Diagram .............................................................. 1 Silicon Revision ID Register ..................................................... 24 Revision History ............................................................................... 3 X-Axis Data (8 MSB) Register .................................................. 24 Specifications ..................................................................................... 4 Y-Axis Data (8 MSB) Register .................................................. 24 Absolute Maximum Ratings ............................................................ 6 Z-Axis Data (8 MSB) Register .................................................. 24 Thermal Resistance ...................................................................... 6 Status Register ............................................................................. 25 Package Information .................................................................... 6 FIFO Entries Registers ............................................................... 26 Recommended Soldering Profile ............................................... 6 X-Axis Data Registers ................................................................ 26 ESD Caution .................................................................................. 6 Y-Axis Data Registers ................................................................ 26 Pin Configuration and Function Descriptions ............................. 7 Z-Axis Data Registers ................................................................ 26 Typical Performance Characteristics ............................................. 8 Temperature Data Registers ...................................................... 26 Theory of Operation ...................................................................... 13 Soft Reset Register ...................................................................... 26 Mechanical Device Operation .................................................. 13 Activity Threshold Registers ..................................................... 27 Operating Modes ........................................................................ 13 Activity Time Register ............................................................... 27 Selectable Measurement Ranges ............................................... 13 Inactivity Threshold Registers .................................................. 27 Selectable Output Data Rates .................................................... 13 Inactivity Time Registers ........................................................... 27 Power/Noise Tradeoff ................................................................ 14 Activity/Inactivity Control Register ........................................ 29 Power Savings Features .................................................................. 15 FIFO Control Register ............................................................... 30 Ultralow Power Consumption in All Modes .......................... 15 FIFO Samples Register .............................................................. 31 Motion Detection ....................................................................... 15 INT1/INT2 Function Map Registers ....................................... 31 FIFO ............................................................................................. 17 Filter Control Register ............................................................... 33 Communications ........................................................................ 17 Power Control Register.............................................................. 34 Additional Features ........................................................................ 18 Self Test Register ......................................................................... 35 Free Fall Detection ..................................................................... 18 Applications Information .............................................................. 36 External Clock ............................................................................ 18 Application Examples ................................................................ 36 Synchronized Data Sampling .................................................... 18 Power............................................................................................ 37 Self Test ........................................................................................ 18 FIFO Modes ................................................................................ 38 User Register Protection ............................................................ 18 Interrupts ..................................................................................... 39 Temperature Sensor ................................................................... 18 Using Synchronized Data Sampling ........................................ 40 Serial Communications ................................................................. 19 Using an External Clock ............................................................ 41 SPI Commands ........................................................................... 19 Using Self Test ............................................................................. 41 Multibyte Transfers .................................................................... 19 Operation at Voltages Other Than 2.0 V ................................ 41 Invalid Addresses and Address Folding .................................. 19 Mechanical Considerations for Mounting .............................. 41 Latency Restrictions ................................................................... 19 Axes of Acceleration Sensitivity ............................................... 42 Invalid Commands ..................................................................... 19 Layout and Design Recommendations ................................... 42 Register Map .................................................................................... 23 Outline Dimensions ....................................................................... 43 Register Details ............................................................................... 24 Ordering Guide .......................................................................... 43 Rev. E | Page 2 of 43

Data Sheet ADXL362 REVISION HISTORY 11/2016—Rev. D to Rev. E 2/2013—Rev. A to Rev. B Changes to Endnote 3, Table 1 ........................................................ 5 Change to Figure 7 ............................................................................ 8 Changes to Using Self Test Section and Table 22 Title ............... 41 Changes to Figure 11, Figure 12, and Figure 13 ............................ 9 Changes to Table 7 and Table 8 ..................................................... 14 11/2015—Rev. C to Rev. D Changes to Figure 31 ...................................................................... 16 Change to Sensor Resonant Frequency Parameter, Table 1 ......... 4 Change to Table 10 .......................................................................... 22 Added Endnote 4, Table 1 ................................................................ 4 Change to Bit 6, Table 12 ................................................................ 25 Changes to Figure 10 ........................................................................ 8 Changes to Inactivity Time Registers Section ............................. 28 Changes to Selectable Measurement Ranges Section ................ 13 Change to LINK/LOOP Bit, Table 13 ........................................... 29 Changes to Bus Keepers Section ................................................... 17 Change to ODR Bit, Table 17 ......................................................... 33 Changes to Figure 36 to Figure 40 ................................................ 20 Changes to Figure 43, Figure 44, and Figure 45 .......................... 36 Changes to Figure 41 and Figure 42 ............................................. 21 Changes to Start-up Routine Section, Figure 46, and Changes to Table 10 ........................................................................ 22 Figure 47 ........................................................................................... 37 Change to Start-Up Routine Section ............................................ 37 Change to Figure 52 ........................................................................ 42 Change to Table 22 .......................................................................... 41 Updated Outline Dimensions ........................................................ 43 9/2012—Rev. 0 to Rev. A Moved Revision History Section..................................................... 3 12/2014—Rev. B to Rev. C Changes to Linking Activity and Inactivity Detection Section; Changes to Table 1 ............................................................................ 4 Added Figure 31, Figure 32, and Figure 33, Renumbered Changes to Figure 14 and Figure 15 ............................................... 9 Sequentially ...................................................................................... 16 Change to Serial Communications Section ................................. 19 Change to Table 13 .......................................................................... 29 Change to Table 10 .......................................................................... 22 Changes to Figure 44 ...................................................................... 36 Changes to Soft Reset Register Section ........................................ 26 Moved Power Supply Decoupling Section ................................... 37 Changes to Example: Implementing Free Fall Detection Added Power Section, Power Supply Requirements Section, and Section .............................................................................................. 37 Figure 47 ........................................................................................... 37 Changes to Using Self Test Section and Table 22 ........................ 41 Updated Outline Dimensions........................................................ 43 Changes to Figure 51 ...................................................................... 42 Changes to Ordering Guide ........................................................... 43 Updated Outline Dimensions ........................................................ 43 8/2012—Revision 0: Initial Version Rev. E | Page 3 of 43

ADXL362 Data Sheet SPECIFICATIONS T = 25°C, V = 2.0 V, V = 2.0 V, 100 Hz ODR, HALF_BW = 0, ±2 g range, acceleration = 0 g, default settings for other registers, A S DD I/O unless otherwise noted.1 Table 1. Parameter Test Conditions/Comments Min Typ Max Unit SENSOR INPUT Each axis Measurement Range User selectable ±2, ±4, ±8 g Nonlinearity Percentage of full scale ±0.5 % Sensor Resonant Frequency 3000 Hz Cross Axis Sensitivity2 ±1.5 % OUTPUT RESOLUTION Each axis All g Ranges 12 Bits SENSITIVITY Each axis Sensitivity Calibration Error ±10 % Sensitivity at X , Y , Z 2 g range 1 mg/LSB OUT OUT OUT 4 g range 2 mg/LSB 8 g range 4 mg/LSB Scale Factor at X , Y , Z 2 g range 1000 LSB/g OUT OUT OUT 4 g range 500 LSB/g 8 g range 250 LSB/g Sensitivity Change Due to Temperature3 −40°C to +85°C 0.05 %/°C 0 g OFFSET Each axis 0 g Output4 X , Y −150 ±35 +150 mg OUT OUT Z −250 ±50 +250 mg OUT 0 g Offset vs. Temperature3 Normal Operation X , Y ±0.5 mg/°C OUT OUT Z ±0.6 mg/°C OUT Low Noise Mode and Ultralow Noise X , Y , Z ±0.35 mg/°C OUT OUT OUT Mode NOISE PERFORMANCE Noise Density Normal Operation X , Y 550 µg/√Hz OUT OUT Z 920 µg/√Hz OUT Low Noise Mode X , Y 400 µg/√Hz OUT OUT Z 550 µg/√Hz OUT Ultralow Noise Mode X , Y 250 µg/√Hz OUT OUT Z 350 µg/√Hz OUT V = 3.5 V; X , Y 175 µg/√Hz S OUT OUT V = 3.5 V; Z 250 µg/√Hz S OUT BANDWIDTH Low Pass (Antialiasing) Filter, −3 dB HALF_BW = 0 ODR/2 Hz Corner HALF_BW = 1 ODR/4 Hz Output Data Rate (ODR) User selectable in 8 steps 12.5 400 Hz SELF TEST Output Change5 X 230 550 870 mg OUT Y −870 −550 −230 mg OUT Z 270 535 800 mg OUT POWER SUPPLY Operating Voltage Range (V) 1.6 2.0 3.5 V S I/O Voltage Range (V ) 1.6 2.0 V V DD I/O S Rev. E | Page 4 of 43

Data Sheet ADXL362 Parameter Test Conditions/Comments Min Typ Max Unit Supply Current Measurement Mode 100 Hz ODR (50 Hz bandwidth)6 Normal Operation 1.8 µA Low Noise Mode 3.3 µA Ultralow Noise Mode 13 µA Wake-Up Mode 0.27 µA Standby 0.01 µA Power Supply Rejection Ratio (PSRR) C = 1.0 µF, R = 100 Ω, C = 1.1 µF, input S S IO is 100 mV sine wave on V S Input Frequency 100 Hz to 1 kHz −13 dB Input Frequency 1 kHz to 250 kHz −20 dB Turn-On Time 100 Hz ODR (50 Hz bandwidth) Power-Up to Standby 5 ms Measurement Mode Instruction to 4/ODR Valid Data TEMPERATURE SENSOR Bias Average @ 25°C 350 LSB Standard Deviation 290 LSB Sensitivity Average 0.065 °C/LSB Standard Deviation 0.0025 °C/LSB Sensitivity Repeatability ±0.5 °C Resolution 12 Bits ENVIRONMENTAL Operating Temperature Range −40 +85 °C 1 All minimum and maximum specifications are guaranteed. Typical specifications may not be guaranteed. 2 Cross axis sensitivity is defined as coupling between any two axes. 3 −40°C to +25°C or +25°C to +85°C. 4 Different supplies and measurement range cause different offset. 5 Self test change is defined as the output change in g when self test is asserted. Different supplies cause different self test changes. These limits apply to the specific test conditions stated in Table 1. For variations over the full Vs supply range, see Table 22. 6 Refer to Figure 30 for current consumption at other bandwidth settings. Rev. E | Page 5 of 43

ADXL362 Data Sheet ABSOLUTE MAXIMUM RATINGS Table 2. RECOMMENDED SOLDERING PROFILE Parameter Rating Figure 3 and Table 5 provide details about the recommended Acceleration (Any Axis, Unpowered) 5000 g soldering profile. Acceleration (Any Axis, Powered) 5000 g CRITICALZONE VS −0.3 V to +3.6 V TP tP TLTOTP VDD I/O −0.3 V to +3.6 V RAMP-UP AOlul tOptuhte Srh Poinrts- Circuit Duration −In0d.3e fVin tiote V S URETL TSMAX tL T A (Any Pin to Ground) R ESD 2000 V (HBM) MPE TSMIN E Short Term Maximum Temperature T PREtHSEAT RAMP-DOWN Four Hours 150°C One Minute 260°C TTeemmppeerraattuurree RRaannggee ((PStoowraegreed) ) −−5500°°CC ttoo ++115500°°CC t25°CTOPEAK TIME 10776-003 Figure 3. Recommended Soldering Profile Stresses at or above those listed under Absolute Maximum Table 5. Recommended Soldering Profile Ratings may cause permanent damage to the product. This is a Condition stress rating only; functional operation of the product at these Profile Feature Sn63/Pb37 Pb-Free or any other conditions above those indicated in the operational Average Ramp Rate (TL to TP) 3°C/sec max 3°C/sec max section of this specification is not implied. Operation beyond Preheat the maximum operating conditions for extended periods may Minimum Temperature (TSMIN) 100°C 150°C affect product reliability. Maximum Temperature (TSMAX) 150°C 200°C Time (T to T )(t) 60 sec to 120 sec 60 sec to 180 sec SMIN SMAX S THERMAL RESISTANCE T to T Ramp-Up Rate 3°C/sec max 3°C/sec max SMAX L Time Maintained Above Table 3. Package Characteristics Liquidous (T) L Package Type θ θ Device Weight JA JC Liquidous Temperature (T) 183°C 217°C L 16-Terminal LGA 150°C/W 85°C/W 18 mg Time (t) 60 sec to 150 sec 60 sec to 150 sec L Peak Temperature (T) 240 + 0/−5°C 260 + 0/−5°C P PACKAGE INFORMATION Time Within 5°C of Actual 10 sec to 30 sec 20 sec to 40 sec Peak Temperature (t) Figure 2 and Table 4 provide details about the package branding P Ramp-Down Rate 6°C/sec max 6°C/sec max for the ADXL362. For a complete listing of product availability, Time 25°C to Peak 6 minutes max 8 minutes max see the Ordering Guide section. Temperature ESD CAUTION • 3 6 2 B # y w w v v v v 10776-002 Figure 2. Product Information on Package (Top View) Table 4. Package Branding Information Branding Key Field Description ●362B Pin 1 indicator and device identifier #yww Pb-free designator (#) and date code vvvv Factory lot code Rev. E | Page 6 of 43

Data Sheet ADXL362 PIN CONFIGURATION AND FUNCTION DESCRIPTIONS D NG CN VS 16 15 14 VDDI/O 1 13 GND NC 2 12 GND ADXL362 RESERVED 3 TOP VIEW 11 INT1 (Not to Scale) SCLK 4 10 RESERVED RESERVED 5 9 INT2 6 7 8 SIO OS SC M IM N1 . O NINTCET E=S RNNOA CLLOYN NCEOCNTN. ETCHTISE DP.IN IS NOT 10776-004 Figure 4. Pin Configuration (Top View) Table 6. Pin Function Descriptions Pin No. Mnemonic Description 1 V Supply Voltage for Digital I/O. DD I/O 2 NC No Connect. Not internally connected. 3 Reserved Reserved. Can be left unconnected or connected to GND. 4 SCLK SPI Communications Clock. 5 Reserved Reserved. Can be left unconnected or connected to GND. 6 MOSI Master Output, Slave Input. SPI serial data input. 7 MISO Master Input, Slave Output. SPI serial data output. 8 CS SPI Chip Select, Active Low. Must be low during SPI communications. 9 INT2 Interrupt 2 Output. INT2 also serves as an input for synchronized sampling. 10 Reserved Reserved. Can be left unconnected, or connected to GND. 11 INT1 Interrupt 1 Output. INT1 also serves as an input for external clocking. 12 GND Ground. This pin must be grounded. 13 GND Ground. This pin must be grounded. 14 V Supply Voltage. S 15 NC No Connect. Not internally connected. 16 GND Ground. This pin must be grounded. Rev. E | Page 7 of 43

ADXL362 Data Sheet TYPICAL PERFORMANCE CHARACTERISTICS 25 40 35 %) N (%) 20 ON ( 30 O TI POPULATI 15 F POPULA 2250 NT OF 10 AGE O 15 PERCE 5 ERCENT 10 P 5 0–80–70–60–50–40–3Z0E–2R0O–1g0 OF0FS1E0T 2(m0g3)0 40 50 60 70 80 10776-005 0 930 950 970 99S0EN1S01IT0IV1I0T3Y0 (m10g5/L0S1B0)70 1090 1110 1130 10776-008 Figure 5. X-Axis Zero g Offset at 25°C, VS = 2 V Figure 8. X-Axis Sensitivity at 25°C, VS = 2 V, ±2 g Range 30 50 45 25 %) N (%) ON ( 40 O TI 35 PULATI 20 OPULA 30 PO 15 F P 25 CENT OF 10 NTAGE O 2105 PER 5 PERCE 10 5 0 –80–70–60–50–40–3Z0E–2R0O–1g0 OF0FS1E0T 2(m0g3)0 40 50 60 70 80 10776-006 0 930 950 970 99S0EN1S01IT0IV1I0T3Y0 (m10g5/L0S1B0)70 1090 1110 1130 10776-009 Figure 6. Y-Axis Zero g Offset at 25°C, VS = 2 V Figure 9. Y-Axis Sensitivity at 25°C, VS = 2 V, ±2 g Range 20 18 18 16 %) N (%) 16 ON ( 14 O 14 TI ULATI 12 PULA 12 P O 10 T OF PO 108 GE OF P 8 N A CE 6 NT 6 R E E C P 4 R 4 E P 2 2 0–170 –140 –110 –Z80ERO– g50OFF–S2E0T (m1g0) 40 70 100 10776-007 0975 990 1005 102S0E1N0S3I5TIV1I0T5Y0 (m1g06/L5SB1)080 1095 1110 1125 10776-010 Figure 7. Z-Axis Zero g Offset at 25°C, VS = 2 V Figure 10. Z-Axis Sensitivity at 25°C, VS = 2 V, ±2 g Range Rev. E | Page 8 of 43

Data Sheet ADXL362 25 150 %) 20 100 N ( O TI ULA 15 mg) 50 P ( O T P U T OF 10 OUTP 0 N E C R E P 5 –50 0–1.0ZE–0R.O8 g– O0.F6FS–E0T.4 TE–M0.P2ERA0TURE0 .C2OEF0.F4ICIE0N.6T (m0g./8°C)1.0 10776-011 –100–60 –40 –20 TE0MPERA20TURE (4°0C) 60 80 100 10776-014 Figure 11. X-Axis Zero g Offset Temperature Coefficient, VS = 2 V Figure 14. X-Axis Zero g Offset vs. Temperature— 16 Parts Soldered to PCB, ODR = 100 Hz, VS = 2 V 35 150 30 %) 100 ON ( 25 TI T OF POPULA 1250 OUTPUT (mg) 500 N E C 10 R PE –50 5 0–1.0ZE–0R.O8g– O0.F6FS–E0T.4 TE–M0P.2ERA0TURE0 .C2OEF0F.4ICIE0N.6T (m0g./8°C)1.0 10776-012 –100–60 –40 –20 TE0MPERA20TURE (4°0C) 60 80 100 10776-015 Figure 12. Y-Axis Zero g Offset Temperature Coefficient, VS = 2 V Figure 15. Y-Axis Zero g Offset vs. Temperature— 16 Parts Soldered to PCB, ODR = 100 Hz, VS = 2 V 25 150 %) 20 100 N ( O TI A UL 15 mg) 50 OP T ( P U F P NT O 10 OUT 0 E C R E P 5 –50 0–0.5–Z0E.R3O– 0g.1 OF0F.1SE0T. 3TE0M.5PER0.A7TU0R.9E C1O.1EF1F.I3CIE1N.5T (m1.g7/°C1).9 10776-013 –100–60 –40 –20 TE0MPERA2T0URE (4°C0) 60 80 100 10776-016 Figure 13. Z-Axis Zero g Offset Temperature Coefficient, VS = 2 V Figure 16. Z-Axis Zero g Offset vs. Temperature— 16 Parts Soldered to PCB, ODR = 100 Hz, VS = 2 V Rev. E | Page 9 of 43

ADXL362 Data Sheet 10 40 %) 8 35 N FROM 25°C ( 246 ULATION (%) 2350 O P ATI 0 PO 20 Y DEVI –2 NT OF 15 SITIVIT ––64 PERCE 10 N SE –8 5 –10–60 –40 –20 TE0MPERA2T0URE(4°C0) 60 80 100 10776-017 0 450 475 500 52S5ELF5 5T0ES5T7 D5EL6T0A0 (m6g2)5 650 675 700 10776-020 Figure 17. X-Axis Sensitivity Deviation from 25°C vs. Temperature— Figure 20. X-Axis Self Test Response at 25°C, VS = 2 V 16 Parts Soldered to PCB, ODR = 100 Hz, VS = 2 V 10 40 %) 8 35 N FROM 25°C ( 246 ULATION (%) 2350 O P ATI 0 PO 20 VI F Y DE –2 NT O 15 VIT –4 CE SITI –6 PER 10 N E S –8 5 –10–60 –40 –20 TE0MPERA2T0URE(4°C0) 60 80 100 10776-018 0 –700 –675 –650 –6S25EL–F6 0T0ES–T5 7D5EL–T5A5 0(m–g5)25 –500 –475 –450 10776-021 Figure 18. Y-Axis Sensitivity Deviation from 25°C vs. Temperature— Figure 21. Y-Axis Self Test Response at 25°C, VS = 2 V 16 Parts Soldered to PCB, ODR = 100 Hz, VS = 2 V 10 40 %) 8 35 N FROM25°C ( 246 ULATION (%) 2350 O P ATI 0 PO 20 VI F Y DE –2 NT O 15 VIT –4 CE NSITI –6 PER 10 E S –8 5 –10–60 –40 –20 TE0MPERA2T0URE (4°C0) 60 80 100 10776-019 0 350 375 400 425 S45E0LF4 T75ES5T0 D0E5L2T5A (5m5g0)575 600 625 650 10776-022 Figure 19. Z-Axis Sensitivity Deviation from 25°C vs. Temperature— Figure 22. Z-Axis Self Test Response at 25°C, VS = 2 V 16 Parts Soldered to PCB, ODR = 100 Hz, VS = 2 V Rev. E | Page 10 of 43

Data Sheet ADXL362 35 70 30 60 %) %) PERCENT OF POPULATION ( 11220505 PERCENT OF POPULATION ( 23450000 5 10 0 1.50 1.55 1.60C1U.6R5R1E.N70T C1.O75NS1U.8M0PT1.I8O5N1(µ.9A0)1.95 2.00 2.05 10776-023 0 50 100 CU15R0RENT2 0C0ONSU2M50PTION30(0nA) 350 400 10776-026 Figure 23. Current Consumption at 25°C, Normal Mode, Figure 26. Current Consumption at 25°C, Wake-Up Mode, VS = 2 V ODR = 100 Hz, VS = 2 V 30 12 25 10 %) %) N ( N ( O O TI 20 TI 8 A A L L U U P P PO 15 PO 6 F F O O T T EN 10 EN 4 C C R R E E P P 5 2 0 2.7 2.8 2.9 C3U.0RRE3.N1T C3O.2NS3U.M3PT3I.O4N(3µ.5A) 3.6 3.7 3.8 10776-024 0–200 TE0MPERA2T0U0RE SE4N0S0OR BI6A0S0AT 258°C00 (LSB)1000 10776-027 Figure 24. Current Consumption at 25°C, Low Noise Mode, Figure 27. Temperature Sensor Response at 25°C, VS = 2 V ODR = 100 Hz, VS = 2 V 35 40 30 35 %) %) ON ( 25 ON ( 30 TI TI A A 25 L L U 20 U P P PO PO 20 OF 15 OF T T 15 N N E E C 10 C ER ER 10 P P 5 5 0 8 9 C1U0RREN11T CON1S2UMP1T3ION(µ1A4) 15 16 10776-025 0 14.41T4E.6M1P4E.8RA15T.U0R1E5 .S2E1N5S.4O1R5 .S6C1A5L.8E 1F6A.0CT1O6.R2 (1L6S.4B1/°6C.6) 16.8 10776-028 Figure 25. Current Consumption at 25°C, Ultralow Noise Mode, Figure 28. Temperature Sensor Scale Factor, VS = 2 V ODR = 100 Hz, VS = 2 V Rev. E | Page 11 of 43

ADXL362 Data Sheet 30 25 %) N ( O TI 20 A L U P PO 15 F O T EN 10 C R E P 5 0–20 –C1L6OC–K1 2FRE–Q8UEN–C4Y DE0VIATIO4N FRO8M ID1E2AL (%16) 20 10776-029 Figure 29. Clock Frequency Deviation from Ideal at 25°C, VS = 2 V Rev. E | Page 12 of 43

Data Sheet ADXL362 THEORY OF OPERATION The ADXL362 is a complete 3-axis acceleration measurement Wake-Up Mode system that operates at extremely low power consumption levels. Wake-up mode is ideal for simple detection of the presence or It measures both dynamic acceleration, resulting from motion or absence of motion at extremely low power consumption (270 nA shock, and static acceleration, such as tilt. Acceleration is reported at a 2.0 V supply voltage). Wake-up mode is useful particularly for digitally and the device communicates via the SPI protocol. Built- implementation of a motion activated on/off switch, allowing the in digital logic enables autonomous operation and implements rest of the system to be powered down until activity is detected. functionality that enhances system level power savings. Wake-up mode reduces current consumption to a very low level MECHANICAL DEVICE OPERATION by measuring acceleration only about six times per second to The moving component of the sensor is a polysilicon surface- determine whether motion is present. If motion is detected, the micromachined structure that is built on top of a silicon wafer. accelerometer can respond autonomously in the following ways: Polysilicon springs suspend the structure over the surface of the • Switch into full bandwidth measurement mode wafer and provide a resistance against acceleration forces. • Signal an interrupt to a microcontroller Deflection of the structure is measured using differential • Wake up downstream circuitry, depending on the capacitors that consist of independent fixed plates and plates configuration attached to the moving mass. Acceleration deflects the structure • In wake-up mode, all accelerometer features are available and unbalances the differential capacitor, resulting in a sensor with the exception of the activity timer. All registers can be output whose amplitude is proportional to acceleration. Phase accessed, and real-time data can be read and/or stored in sensitive demodulation determines the magnitude and polarity the FIFO. of the acceleration. Standby OPERATING MODES Placing the ADXL362 in standby suspends measurement and The ADXL362 has two operating modes: measurement mode for reduces current consumption to 10 nA (typical). Pending continuous, wide bandwidth sensing; and wake-up mode for interrupts and data are preserved and no new interrupts are limited bandwidth activity detection. In addition, measurement can generated. be suspended altogether by placing the device in standby. The ADXL362 powers up in standby with all sensor functions Measurement Mode turned off. Measurement mode is the normal operating mode of the SELECTABLE MEASUREMENT RANGES ADXL362. In this mode, acceleration data is read continuously The ADXL362 has selectable measurement ranges of ±2 g, ±4 g, and the accelerometer consumes less than 3 µA (typical) across and ±8 g. Acceleration samples are always converted by a 12-bit its entire range of output data rates of up to 400 Hz using a 2.0 V ADC; therefore, sensitivity scales with g range. Ranges and supply. All features described in this datasheet are available corresponding sensitivity values are listed in Table 1. Data can when operating the ADXL362 in this mode. temporarily not represent maximum gees while overranging The ability to continuously output data from the minimum but no damage is caused to the accelerometer when acceleration 12.5 Hz to the maximum 400 Hz data rate while still delivering exceeds the corresponding range maximum. Table 2 lists the less than 3 µA (typical) of current consumption is what defines absolute maximum ratings for acceleration, indicating the the ADXL362 as an ultralow power accelerometer. Other accel- acceleration level that can cause permanent damage to the device. erometers derive low current by using a specific low power mode SELECTABLE OUTPUT DATA RATES that power cycles acceleration sensing. The result is a small effective bandwidth in the low power modes and undersampling The ADXL362 can report acceleration data at various data rates of input data; therefore, unwanted aliasing can occur. Under- ranging from 12.5 Hz to 400 Hz. The internal low-pass filter pole is sampling and aliasing do not occur with the ADXL362 because automatically set to ¼ or ½ the selected ODR (based on the it continuously samples the full bandwidth of its sensor at all HALF_BW setting) to ensure the Nyquist sampling criterion is data rates. met and no aliasing occurs. Rev. E | Page 13 of 43

ADXL362 Data Sheet Current consumption varies somewhat with output data rate as POWER/NOISE TRADEOFF shown in Figure 30, remaining below 5.0 µA over the entire The ADXL362 offers a few options for decreasing noise at the range of data rates and operating voltages. expense of only a small increase in current consumption. 6 VS = 1.6V The noise performance of the ADXL362 in normal operation, VS = 2.0V VS = 2.5V typically 7 LSB rms at 100 Hz bandwidth, is adequate for most 5 VS = 3.0V A) VS = 3.5V applications, depending upon bandwidth and the desired reso- µ N ( lution. For cases where lower noise is needed, the ADXL362 O 4 PTI provides two lower noise operating modes that trade reduced M NSU 3 noise for a somewhat higher current consumption. O T C Table 7 lists the current consumption and noise densities obtained N E 2 for normal operation and the two lower noise modes at a typical R R U 2.0 V supply. C 1 Table 7. Noise and Current Consumption: Normal Operation, 00 100 OUTPUT DA20TA0 RATE (Hz) 300 400 10776-030 OLoDwR N =o 1is0e0 M Hozd e, and Ultralow Noise Mode at VS = 2.0 V, Noise Current Figure 30. Current Consumption vs. Output Data Rate at Several (µg/√Hz) Consumption (µA) Supply Voltages Mode Typical Typical Antialiasing Normal Operation 550 1.8 The analog-to-digital converter (ADC) of the ADXL362 samples Low Noise 400 3.3 at the (user selected) output data rate. In the absence of anti- Ultralow Noise 250 13 aliasing filtering, it aliases any input signals whose frequency is more than half the data rate. To mitigate this, a two-pole low- Operating the ADXL362 at a higher supply voltage also decreases pass filter is provided at the input of the ADC. noise. Table 8 lists the current consumption and noise densities obtained for normal operation and the two lower noise modes The user can set this antialiasing filter to a bandwidth that is at ½ at the highest recommended supply, 3.3 V. the data rate or ¼ the data rate. Setting the antialiasing filter pole to ½ of the output data rate provides less aggressive antialiasing Table 8. Noise and Current Consumption: Normal Operation, filtering, but maximizes bandwidth and is adequate for most Low Noise Mode, and Ultralow Noise Mode at V = 3.3 V, S applications. Setting the pole to ¼ of the data rate reduces ODR = 100 Hz bandwidth for a given data rate, but provides more aggressive Noise Current antialiasing. (µg/√Hz) Consumption (µA) The antialiasing filter of the ADXL362 defaults to the more Mode Typical Typical conservative setting, where bandwidth is set to one-fourth the Normal Operation 380 2.7 output data rate. Low Noise 280 4.5 Ultralow Noise 175 15 Rev. E | Page 14 of 43

Data Sheet ADXL362 POWER SAVINGS FEATURES Designed for the most power conscious applications, the ADXL362 In many applications, it is advantageous for activity detection to includes several features (as described in this section) for enabling be based not on an absolute threshold, but on a deviation from power savings at the system level, as well as at the device level. a reference point or orientation. This is particularly useful because it removes the effect on activity detection of the static 1 g imposed ULTRALOW POWER CONSUMPTION IN ALL by gravity. When an accelerometer is stationary, its output can MODES reach 1 g, even when it is not moving. In absolute activity, when At the device level, the most obvious power saving feature of the the threshold is set to less than 1 g, activity is immediately detected ADXL362 is its ultralow current consumption in all configurations. in this case. The ADXL362 consumes between 1.1 μA (typical) and 5 μA In the referenced configuration, activity is detected when (typical) across all data rates up to 400 Hz and all supply voltages acceleration samples are at least a user set amount above an up to 3.5 V (see Figure 30). An even lower power, 270 nA (typical) internally defined reference for the user defined amount of time, motion triggered wake-up mode is provided for simple motion as described in Equation 1. detection applications that require a power consumption lower than 1 μA. ABS(Acceleration − Reference) > Threshold (1) At these current levels, the accelerometer consumes less power Consequently, activity is detected only when the acceleration in full operation than the standby currents of many other system has deviated sufficiently from the initial orientation. The components, and is, therefore, optimal for applications that require reference for activity detection is calculated when activity continuous acceleration monitoring and very long battery life. detection is engaged in the following scenarios: Because the accelerometer is always on, it can act as a motion When the activity function is turned on and measurement activation switch. The accelerometer signals to the rest of the mode is engaged; system when to turn on, thereby managing power at the If link mode is enabled: when inactivity is detected and system level. activity detection begins; or As important as its low operating current, the 10 nA (typical) If link mode is not enabled: when activity is detected and standby current of the ADXL362 contributes to a much longer activity detection repeats. battery life in applications that spend most of their time in a The referenced configuration results in a very sensitive activity sleep state and wake up via an external trigger. detection that detects even the most subtle motion events. MOTION DETECTION Fewer False Positives The ADXL362 features built-in logic that detects activity Ideally, the intent of activity detection is to wake up a system only (presence of acceleration above a threshold) and inactivity (lack when motion is intentional, ignoring noise or small, unintentional of acceleration above a threshold). Activity and inactivity events movements. In addition to being sensitive to subtle motion events, can be used as triggers to manage the accelerometer mode of the ADXL362 activity detection algorithm is designed to be operation, trigger an interrupt to a host processor, and/or robust in filtering out undesired triggers. autonomously drive a motion switch. The ADXL362 activity detection functionality includes a timer Detection of an activity or inactivity event is indicated in the to filter out unwanted motion and ensure that only sustained status register and can be configured to generate an interrupt. motion is recognized as activity. The duration of this timer, as In addition, the activity status of the device, that is, whether it is well as the acceleration threshold, are user adjustable from one moving or stationary, is indicated by the AWAKE bit, described sample (that is, no timer) to up to 20 seconds of motion. in the Using the AWAKE Bit section. Note that the activity timer is operational in measurement mode Activity and inactivity detection can be used when the accel- only. In wake-up mode, one-sample activity detection is used. erometer is in either measurement mode or wake-up mode. Inactivity Detection Activity Detection An inactivity event is detected when acceleration remains below An activity event is detected when acceleration remains above a a specified threshold for a specified time. Inactivity detection is specified threshold for a specified time period. also configurable as referenced or absolute. Referenced and Absolute Configurations When using absolute inactivity detection, acceleration samples Activity detection can be configured as referenced or absolute. are compared to a user set threshold for the user set time to When using absolute activity detection, acceleration samples are determine the absence of motion. Inactivity is detected when compared to a user set threshold to determine whether motion enough consecutive samples are all below the threshold. The is present. For example, if a threshold of 0.5 g is set and the absolute configuration of inactivity must be used for acceleration on the z-axis is 1 g for longer than the user defined implementing free fall detection. activity time, the activity status asserts. Rev. E | Page 15 of 43

ADXL362 Data Sheet When using referenced inactivity detection, inactivity is detected WAIT FOR WAIT FOR when acceleration samples are within a user specified amount ACTIVITY PROCESSOR TO EVENT CLEAR INTERRUPT of an internally defined reference (as described by Equation 2) for a user defined amount of time. AWAKE = 1 INACTIVITY ABS(Acceleration − Reference) < Threshold (2) INTERRUPT TRIGGERS Referenced inactivity, like referenced activity, is particularly ACTIVITY useful for eliminating the effects of the static acceleration due to INTERRUPT TRIGGERS gravity. With absolute inactivity, if the inactivity threshold is set AWAKE = 1 lower than 1 g, a device resting motionless may never detect inactivity. With referenced inactivity, the same device under the WAIT FOR WAIT FOR PROCESSOR TO INACTIVITY same configuration detects inactivity. CLEAR INTERRUPT EVENT The inactivity timer can be set to anywhere from 2.5 ms (a single saat m12p.5le H azt 4O0D0 RH) zo Of iDnaRc)ti vtoit ya.l Am oresqt u9i0re mmiennutt feosr ( i6n5a,c5t3iv5i tsya dmeptelec-s N1 . O TATHREEES ANWOTA KLEIN BKIETD D.EFAULTS TO 1 WHEN ACTIVITY AND INACTIVITY 10776-131 Figure 31. Flowchart Illustrating Activity and Inactivity Operation in Default Mode tion is that for whatever period of time the inactivity timer has been configured, the accelerometer detects inactivity only when In linked mode, each interrupt must be serviced by a host it has been stationary for that amount of time. processor before the next interrupt is enabled. For example, if the accelerometer has been configured for Linked mode operation is illustrated in the flowchart in Figure 32. 90 minutes, the accelerometer detects inactivity when it has WAIT FOR WAIT FOR AWAKE = 0 INACTIVITY been stationary for 90 minutes. The wide range of timer settings ACTIVITY PROCESSOR TO INTERRUPT EVENT CLEAR INTERRUP means that in applications where power conservation is critical, the system can be put to sleep after very short periods of inactivity. In applications where continuous operation is critical, the system stays on for as long as any motion is present. AWAKE = 1 WAIT FOR WAIT FOR Linking Activity and Inactivity Detection INATCETRIVRIUTYPT CPLERAORC EINSTSEORRR TUOPT INAECVTEINVTITY 10776-132 Figure 32. Flowchart Illustrating Activity and Inactivity Operation in Linked Mode The activity and inactivity detection functions can be used concurrently and processed manually by a host processor, or Loop Mode they can be configured to interact in several other ways, as In loop mode, motion detection operates as described in the follows. Linked Mode section, but interrupts do not need to be serviced Default Mode by a host processor. This configuration simplifies the implemen- The user must enable the activity and inactivity functions because tation of commonly used motion detection and enhances power these functions are not automatically enabled by default. After savings by reducing the amount of power used in bus communi- the user enables the activity and inactivity functions, the ADXL362 cation. exhibits the following behavior when it enters default mode: Both Loop mode operation is illustrated in the flowchart in Figure 33. activity and inactivity detection remain enabled and all interrupts AWAKE = 1 must be serviced by a host processor; that is, a processor must read each interrupt before it is cleared and can be used again. Loop mode operation is illustrated in the flowchart in Figure 32. WAIT FOR WAIT FOR ACTIVITY INACTIVITY EVENT EVENT Linked Mode In linked mode, activity and inactivity detection are linked to each other such that only one of the functions is enabled at any AWAKE = 0 10776-133 given time. As soon as activity is detected, the device is assumed Figure 33. Flowchart Illustrating Activity and Inactivity Operation in Loop Mode to be moving (or awake) and stops looking for activity; rather, Autosleep inactivity is expected as the next event. Therefore, only inactivity detection operates. When in linked or loop mode, enabling autosleep causes the device to enter wake-up mode autonomously (see the Wake-Up Similarly, when inactivity is detected, the device is assumed to Mode section) when inactivity is detected, and to reenter be stationary (or asleep). Thus, activity is expected as the next measurement mode when activity is detected. event; therefore, only activity detection operates. The autosleep configuration is active only if linked or loop modes are enabled. In the default mode, the autosleep setting is ignored. Rev. E | Page 16 of 43

Data Sheet ADXL362 Using the AWAKE Bit COMMUNICATIONS The AWAKE bit is a status bit that indicates whether the ADXL362 SPI Instructions is awake or asleep. The device is awake when it has experienced The digital interface of the ADXL362 is implemented with an activity condition, and it is asleep when it has experienced an system level power savings in mind. The following features inactivity condition. enhance power savings: The awake signal can be mapped to the INT1 or INT2 pin, • Burst reads and writes reduce the number of SPI allowing the pin to serve as a status output to connect or dis- communication cycles required to configure the device connect power to downstream circuitry based on the awake and retrieve data. status of the accelerometer. Used in conjunction with loop • Concurrent operation of activity and inactivity detection mode, this configuration implements a trivial, autonomous enables “set it and forget it” operation. Loop mode further motion activated switch, as shown in Figure 43. reduces communications power by enabling the clearing of If the turn-on time of downstream circuitry can be tolerated, interrupts without processor intervention. this motion switch configuration can save significant system • The FIFO is implemented such that consecutive samples level power by eliminating the standby current consumption of can be read continuously via a multibyte read of unlimited the remainder of the application. This standby current can often length; thus, one read FIFO instruction can clear the entire exceed the full operating current of the ADXL362. contents of the FIFO. In many other accelerometers, each FIFO read instruction retrieves a single sample only. In addition, the ADXL362 FIFO construction allows the use of direct memory The ADXL362 includes a deep 512-sample first in, first out (FIFO) access (DMA) to read the FIFO contents. buffer. The FIFO provides benefits primarily in two ways, as follows. Bus Keepers System Level Power Savings The ADXL362 includes bus keepers on all pins that can be configured as digital inputs: MOSI, SCLK, CS, INT1, and INT2. Appropriate use of the FIFO enables system level power savings Bus keepers prevent tristate bus lines from floating when nothing by enabling the host processor to sleep for extended periods of is driving them, thus preventing through current in any gate time while the accelerometer autonomously collects data. Alter- inputs that are on the bus. natively, using the FIFO to collect data can unburden the host while it tends to other tasks. MSB Registers Data Recording/Event Context Acceleration and temperature measurements are converted to 12-bit values and transmitted via SPI using two registers per The FIFO can be used in a triggered mode to record all data measurement. To read a full sample set of 3-axis acceleration leading up to an activity detection event, thereby providing con- data, six registers must be read. text for the event. In the case of a system that identifies impact events, for example, the accelerometer can keep the entire system Many applications do not require the accuracy that 12-bit data off while it stores acceleration data in its FIFO and looks for an provides and prefer, instead, to save system level power. The MSB activity event. When the impact event occurs, data that was registers XDATA, YDATA, and ZDATA enable this tradeoff. collected prior to the event is frozen in the FIFO. The accel- These registers contain the eight MSBs of the x-, y-, and z-axis erometer can then wake the rest of the system and transfer this acceleration data; reading them effectively provides 8-bit accel- data to the host processor, thereby providing context for the eration values. Importantly, only three (consecutive) registers must impact event. be read to retrieve a full data set, significantly reducing the time during which the SPI bus is active and drawing current. Generally, the more context available, the more intelligent decisions a system can achieve, making a deep FIFO especially 12-bit and 8-bit data are available simultaneously so that both useful. The ADXL362 FIFO can store up to more than 13 seconds data formats can be used in a single application, depending on of data, providing a clear picture of events prior to an activity the needs of the application at a given time. For example, the pro- trigger. cessor can read 12-bit data when higher resolution is required, and switch to 8-bit data (simply by reading a different set of registers) All FIFO modes of operation, as well as the structure of the FIFO when application requirements change. and instructions for retrieving data from it, are described in further detail in the FIFO Modes section of this data sheet. Rev. E | Page 17 of 43

ADXL362 Data Sheet ADDITIONAL FEATURES FREE FALL DETECTION SYNCHRONIZED DATA SAMPLING Many digital output accelerometers include a built-in free fall For applications that require a precisely timed acceleration detection feature. In the ADXL362, this function can be imple- measurement, the ADXL362 features an option to synchronize mented using the inactivity interrupt. Refer to the Applications acceleration sampling to an external trigger. Information section for more details, including suggested SELF TEST threshold and timing values. The ADXL362 incorporates a self test feature that effectively EXTERNAL CLOCK tests its mechanical and electronic systems simultaneously. The ADXL362 has a built-in 51.2 kHz (typical) clock that, by When the self test function is invoked, an electrostatic force is default, serves as the time base for internal operations. applied to the mechanical sensor. This electrostatic force moves the mechanical sensing element in the same manner as acceleration, ODR and bandwidth scale proportionally with the clock. The and it is additive to the acceleration experienced by the device. ADXL362 provides a discrete number of options for ODR, such This added electrostatic force results in an output change on all as 100 Hz, 50 Hz, 25 Hz, and so forth, in factors of 2, (see the three axes. Filter Control Register section for a complete listing). To achieve data rates other than those provided, an external clock can be USER REGISTER PROTECTION used at the appropriate clock frequency. The output data rate The ADXL362 includes user register protection for single event scales with the clock frequency, as shown in Equation 3. upsets (SEUs). An SEU is a change of state caused by ions or f electromagnetic radiation striking a sensitive node in a micro- ODR =ODR × (3) ACTUAL SELECTED 51.2kHz electronic device. The state change is a result of the free charge created by ionization in or close to an important node of a logic For example, to achieve an 80 Hz ODR, select the 100 Hz ODR element (for example, a memory bit). The SEU, itself, is not con- setting and provide a clock frequency that is 80% of nominal, or sidered permanently damaging to transistor or circuit functionality, 41.0 kHz. but it can create erroneous register values. The ADXL362 registers The ADXL362 can operate with external clock frequencies that are protected from SEU are Register 0x20 to Register 0x2E. ranging from the nominal 51.2 kHz down to 25.6 kHz to allow SEU protection is implemented via a 99-bit error correcting the user to achieve any desired output data rate. (Hamming-type) code that detects both single- and double-bit Alternatively, an external clock can improve clock frequency errors. The check bits are recomputed any time a write to any of accuracy. The distribution of clock frequencies among a sampling the protected registers occurs. At any time, if the stored version of >1000 parts has a standard deviation of approximately 3%. To of the check bits is not in agreement with the current check bit achieve tighter tolerances, a more accurate clock can be calculation, the ERR_USER_REGS status bit is set. provided externally. The SEU bit in the status register is set on power-up prior to Bandwidth automatically scales to ½ or ¼ of the ODR (based device configuration; it clears upon the first register write to on the HALF_BW setting), and this ratio is preserved, regardless that device. of clock frequency. Power consumption also scales with clock TEMPERATURE SENSOR frequency: higher clock rates increase power consumption. The ADXL362 includes an integrated temperature sensor that Figure 34 shows how power consumption varies with clock rate. can monitor internal system temperature or improve the tempera- 3.0 ture stability of the device via calibration. For example, acceleration outputs vary with temperature at a rate of ±0.5 mg/°C (typical), 2.5 A) but the relationship to temperature is repeatable and can be µ N ( calibrated. O 2.0 TI MP To use the temperature sensor to monitor absolute temperature, U NS 1.5 it is recommended that its initial bias (its output at some known O C temperature) is measured and calibrated. T N E 1.0 R R U C 0.5 VS = 1.6V VS = 2.0V VS = 3.5V 043 44 E4X5TERN4A6L CLO47CK FR4E8QUEN49CY (kH50z) 51 52 10776-031 Figure 34. Current Consumption vs. External Clock Rate Rev. E | Page 18 of 43

Data Sheet ADXL362 SERIAL COMMUNICATIONS The ADXL362 communicates via a 4-wire SPI and operates as a It is recommended that an even number of bytes be read (using slave. Ignore data that is transmitted from the ADXL362 to the a multibyte transaction) because each sample consists of two master device during writes to the ADXL362. bytes: 2 bits of axis information and 14 bits of data. If an odd number of bytes is read, it is assumed that the desired data was As shown in Figure 36 to Figure 40, the MISO pin is in a high read; therefore, the second half of the last sample is discarded so impedance state, held by a bus keeper, except when the ADXL362 a read from the FIFO always starts on a properly aligned even- is sending read data (to conserve bus power). byte boundary. Data is presented least significant byte first, Wire the ADXL362 for SPI communication as shown in the followed by the most significant byte. connection diagram in Figure 35. The recommended SPI clock MULTIBYTE TRANSFERS speeds are 1 MHz to 8 MHz, with 12 pF maximum loading. Multibyte transfers, also known as burst transfers, are supported The SPI timing scheme follows CPHA = CPOL = 0. for all SPI commands: register read, register write, and FIFO read For correct operation of the device, the logic thresholds and commands. It is recommended that data be read using multibyte timing parameters in Table 9 and Table 10 must be met at all transfers to ensure that a concurrent and complete set of x-, y-, times. Refer to Figure 41 and Figure 42 for visual diagrams of and z-acceleration (and temperature, where applicable) data is read. the timing parameters. The FIFO runs on the serial port clock during FIFO reads and ADXL362 PROCESSOR can sustain bursting at the SPI clock rate as long as the SPI clock CS DOUT is 1 MHz or faster. MOSI DOUT Register Read/Write Auto-Increment MISO DIN A register read or write command begins with the address specified SCLK DOUT 10776-032 itnh et htrea cnosmferm. Taon da vaonidd aaudtdor-eisnsc wrermapepnitns gf oarn eda scihd ea dedffietciotsn oalf breyated iinng Figure 35. 4-Wire SPI Connection Diagram registers multiple times, the auto-increment halts at the invalid SPI COMMANDS Register Address 63 (0x3F). The SPI port uses a multibyte structure wherein the first byte is INVALID ADDRESSES AND ADDRESS FOLDING a command. The ADXL362 command set is The ADXL362 has a 6-bit address bus, mapping only 64 registers in • 0x0A: write register the possible 256 register address space. The addresses do not fold to • 0x0B: read register repeat the registers at addresses above 64. Attempted access to • 0x0D: read FIFO register addresses above 64 are mapped to the invalid register at 63 (0x3F) and have no functional effect. Read and Write Register Commands Address 0x00 to Address 0x2E are for customer access, as The command structure for the read register and write register described in the register map. Address 0x2F to Address 0x3F are commands is as follows (see Figure 36 and Figure 37): reserved for factory use. </CS down> <command byte (0x0A or 0x0B)> <address LATENCY RESTRICTIONS byte> <data byte> <additional data bytes for multi-byte> … Reading any of the data registers (0x08 to 0x0A or 0x0E to </CS up> 0x15) clears the data ready interrupt. There can be as much as The read and write register commands support multibyte an 80 µs delay from reading a register to the clearing of the data (burst) read/write access. The waveform diagrams for multi- ready interrupt. byte read and write commands are shown in Figure 38 and Other register reads, register writes, and FIFO reads have no Figure 39. latency restrictions. Read FIFO Command INVALID COMMANDS Reading from the FIFO buffer is a command structure that does Commands other than 0x0A, 0x0B, and 0x0D have no effect. not have an address. The MISO output remains in a high impedance state, and the </CS down> <command byte (0x0D)> <data byte> <data bus keeper holds the MISO line at its last value. byte> … </CS up> Rev. E | Page 19 of 43

ADXL362 Data Sheet CS 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 SCLK INSTRUCTION 888-BBBBIIIITTTT AADDDDDDDDDRREESSSSSSSSS MOSI 000 000 00 000 111 0000 111 11 77777777 66666666 55555555 44444444 33333333 22222222 111111 00000000 MISO 7 6 5 DA4TA O3UT 2 1 0 10776-239 Figure 36. Register Read CS 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 SCLK INSTRUCTION 88-BBBBBBIIIITT AAAAADDDDDDRRRREEEEESSSSSS DATA BYTE MOSI 0 0 0 0 1 0 1 0 77777 666666 5555555 444444 3333333 2222222 1111 00 7 6 5 4 3 2 1 0 MISO HIGH IMPEDANCE 10776-240 Figure 37. Register Write (Receive Instruction Only) CS 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 SCLK INSTRUCTION 8-BIT ADDRESS MOSI 0 0 0 0 1 0 1 1 7 6 5 4 3 2 1 0 OUTPUT BYTE 1 OUTPUT BYTE n MISO 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 10776-241 Figure 38. Burst Read CS 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 SCLK INSTRUCTION 8-BIT ADDRESS DATA BYTE 1 DATA BYTE n MOSI 0 0 0 0 1 0 1 0 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 MISO HIGH IMPEDANCE 10776-242 Figure 39. Burst Write (Receive Instruction Only) CS 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 SCLK INSTRUCTION MOSI 0 0 0 0 1 1 0 1 OUTPUT BYTE 1 OUTPUT BYTE n MISO 7777 6666 5555 4444 3333 2222 111 00 7 6 5 4 3 2 1 0 10776-243 Figure 40. FIFO Read Rev. E | Page 20 of 43

Data Sheet ADXL362 tCSD CS CSS tCSH tCLE SCLK tSU tHD MOSI MSB IN LSB IN MISO HIGH IMPEDANCE 10776-244 Figure 41. Timing Diagram for SPI Receive Instructions CS tHIGH tLOW tCSH SCLK DON’T CARE MISO tV tDIS MOSI MSB OUT LSB OUT 10776-245 Figure 42. Timing Diagram for SPI Send Instructions (Shaded Portions of Figure 36, Figure 38, and Figure 40) Table 9. SPI Digital Input/Output Limit1 Parameter Test Conditions/Comments Min Max Unit Digital Input Low Level Input Voltage (V ) 0.3 × V V IL DD I/O High Level Input Voltage (V ) 0.7 × V V IH DD I/O Low Level Input Current (I ) V = V 0.1 µA IL IN DD I/O High Level Input Current (I ) V = 0 V −0.1 µA IH IN Digital Output Low Level Output Voltage (V ) I = 10 mA 0.2 × V V OL OL DD I/O High Level Output Voltage (V ) I = −4 mA 0.8 × V V OH OH DD I/O Low Level Output Current (I ) V = V 10 mA OL OL OL, max High Level Output Current (I ) V = V −4 mA OH OH OH, min 1 Limits based on characterization results, not production tested. Rev. E | Page 21 of 43

ADXL362 Data Sheet Table 10. SPI Timing (T = 25°C, V = 2.0 V, V = 2.0 V) A S DDI/O Limit1, 2 Parameter Min Max Unit Description f 3 2.4 8000 kHz Clock Frequency CLK CSS 100 ns CS Setup Time tCSH 20 ns CS Hold Time tCSD 20 ns CS Disable Time t 20 ns Data Setup Time SU t 20 ns Data Hold Time HD t 50 ns Clock High Time HIGH t 50 ns Clock Low Time LOW t 25 ns Clock Enable Time CLE t 0 35 ns Output Valid from Clock Low V t 0 25 ns Output Disable Time DIS 1 Limits based on design targets; not production tested. 2 The timing values are measured corresponding to the input thresholds (VIL and VIH) given in Table 9. 3 The minimum limit is only necessary when using FIFO. Rev. E | Page 22 of 43

Data Sheet ADXL362 REGISTER MAP Table 11. Register Summary Reg Name Bits Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 ResetRW 0x00 DEVID_AD [7:0] DEVID_AD[7:0] 0xAD R 0x01 DEVID_MST [7:0] DEVID_MST[7:0] 0x1D R 0x02 PARTID [7:0] PARTID[7:0] 0xF2 R 0x03 REVID [7:0] REVID[7:0] 0x01 R 0x08 XDATA [7:0] XDATA[7:0] 0x00 R 0x09 YDATA [7:0] YDATA[7:0] 0x00 R 0x0A ZDATA [7:0] ZDATA[7:0] 0x00 R 0x0B STATUS [7:0] ERR_USER_ AWAKE INACT ACT FIFO_OVER- FIFO_WATER- FIFO_READY DATA_READY 0x40 R REGS RUN MARK 0x0C FIFO_ENTRIES_L [7:0] FIFO_ENTRIES_L[7:0] 0x00 R 0x0D FIFO_ENTRIES_H [7:0] UNUSED FIFO_ENTRIES_H[1:0] 0x00 R 0x0E XDATA_L [7:0] XDATA_L[7:0] 0x00 R 0x0F XDATA_H [7:0] SX XDATA_H[3:0] 0x00 R 0x10 YDATA_L [7:0] YDATA_L[7:0] 0x00 R 0x11 YDATA_H [7:0] SX YDATA_H[3:0] 0x00 R 0x12 ZDATA_L [7:0] ZDATA_L[7:0] 0x00 R 0x13 ZDATA_H [7:0] SX ZDATA_H[3:0] 0x00 R 0x14 TEMP_L [7:0] TEMP_L[7:0] 0x00 R 0x15 TEMP_H [7:0] SX TEMP_H[3:0] 0x00 R 0x16 Reserved [7:0] Reserved[7:0] 0x00 R 0x17 Reserved [7:0] Reserved[7:0] 0x00 R 0x1F SOFT_RESET [7:0] SOFT_RESET[7:0] 0x00 W 0x20 THRESH_ACT_L [7:0] THRESH_ACT_L[7:0] 0x00 RW 0x21 THRESH_ACT_H [7:0] UNUSED THRESH_ACT_H[2:0] 0x00 RW 0x22 TIME_ACT [7:0] TIME_ACT[7:0] 0x00 RW 0x23 THRESH_INACT_L [7:0] THRESH_INACT_L[7:0] 0x00 RW 0x24 THRESH_INACT_H [7:0] UNUSED THRESH_INACT_H[2:0] 0x00 RW 0x25 TIME_INACT_L [7:0] TIME_INACT_L[7:0] 0x00 RW 0x26 TIME_INACT_H [7:0] TIME_INACT_H[7:0] 0x00 RW 0x27 ACT_INACT_CTL [7:0] RES LINKLOOP INACT_REF INACT_EN ACT_REF ACT_EN 0x00 RW 0x28 FIFO_CONTROL [7:0] UNUSED AH FIFO_TEMP FIFO_MODE 0x00 RW 0x29 FIFO_SAMPLES [7:0] FIFO_SAMPLES[7:0] 0x80 RW 0x2A INTMAP1 [7:0] INT_LOW AWAKE INACT ACT FIFO_OVER- FIFO_WATER- FIFO_READY DATA_READY 0x00 RW RUN MARK 0x2B INTMAP2 [7:0] INT_LOW AWAKE INACT ACT FIFO_OVER- FIFO_WATER- FIFO_READY DATA_READY 0x00 RW RUN MARK 0x2C FILTER_CTL [7:0] RANGE RES HALF_BW EXT_SAMPLE ODR 0x13 RW 0x2D POWER_CTL [7:0] RES EXT_CLK LOW_NOISE WAKEUP AUTOSLEEP MEASURE 0x00 RW 0x2E SELF_TEST [7:0] UNUSED ST 0x00 RW Rev. E | Page 23 of 43

ADXL362 Data Sheet REGISTER DETAILS This section describes the functions of the ADXL362 registers. X-AXIS DATA (8 MSB) REGISTER The ADXL362 powers up with default register values in the as Address: 0x08, Reset: 0x00, Name: XDATA shown in the Reset column of Table 11 in the Register Map section. This register holds the eight most significant bits of the x-axis acceleration data. This limited resolution data register is used in Note that any changes to the registers before the POWER_CTL power conscious applications where eight bits of data are sufficient: register (Register 0x00 to Register 0x2C) must be made with the energy can be conserved by reading only one byte of data per device in standby. If changes are made while the ADXL362 is in axis, rather than two. measurement mode, they can be effective for only part of a measurement. DEVICE ID REGISTER Address: 0x00, Reset: 0xAD, Name: DEVID_AD Y-AXIS DATA (8 MSB) REGISTER This register contains the Analog Devices device ID, 0xAD. Address: 0x09, Reset: 0x00, Name: YDATA This register holds the eight most significant bits of the y-axis acceleration data. This limited resolution data register is used in power conscious applications where eight bits of data are sufficient: DEVICE ID: 0x1D REGISTER energy can be conserved by reading only one byte of data per Address: 0x01, Reset: 0x1D, Name: DEVID_MST axis, rather than two. This register contains the Analog Devices MEMS device ID, 0x1D. Z-AXIS DATA (8 MSB) REGISTER Address: 0x0A, Reset: 0x00, Name: ZDATA PART ID: 0xF2 REGISTER This register holds the eight most significant bits of the z-axis Address: 0x02, Reset: 0xF2, Name: PARTID acceleration data. This limited resolution data register is used in power conscious applications where eight bits of data are sufficient: This register contains the device ID, 0xF2 (362 octal). energy can be conserved by reading only one byte of data per axis, rather than two. SILICON REVISION ID REGISTER Address: 0x03, Reset: 0x01, Name: REVID This register contains the product revision ID, beginning with 0x01 and incrementing for each subsequent revision. Rev. E | Page 24 of 43

Data Sheet ADXL362 STATUS REGISTER Address: 0x0B, Reset: 0x40, Name: STATUS This register includes the following bits that describe various conditions of the ADXL362. Table 12. Bit Descriptions for STATUS Bits Bit Name Settings Description Reset Access 7 ERR_USER_REGS SEU Error Detect. 1 indicates one of two conditions: either an SEU event, 0x0 R such as an alpha particle of a power glitch, has disturbed a user register setting or the ADXL362 is not configured. This bit is high upon both startup and soft reset, and resets as soon as any register write commands are performed. 6 AWAKE Indicates whether the accelerometer is in an active (AWAKE = 1) or 0x1 R inactive (AWAKE = 0) state, based on the activity and inactivity functionality. To enable autosleep, activity and inactivity detection must be in linked mode or loop mode (LINK/LOOP bits in the ACT_INACT_CTL register); otherwise, this bit defaults to 1 and must be ignored. 5 INACT Inactivity. 1 indicates that the inactivity detection function has detected 0x0 R an inactivity or a free fall condition. 4 ACT Activity. 1 indicates that the activity detection function has detected an 0x0 R overthreshold condition. 3 FIFO_OVERRUN FIFO Overrun. 1 indicates that the FIFO has overrun or overflowed, such 0x0 R that new data replaces unread data. See the Using FIFO Interrupts section for details. 2 FIFO_WATERMARK FIFO Watermark. 1 indicates that the FIFO contains at least the desired 0x0 R number of samples, as set in the FIFO_SAMPLES register. See the Using FIFO Interrupts section for details. 1 FIFO_READY FIFO Ready. 1 indicates that there is at least one sample available in the 0x0 R FIFO output buffer. See the Using FIFO Interrupts section for details. 0 DATA_READY Data Ready. 1 indicates that a new valid sample is available to be read. 0x0 R This bit clears when a FIFO read is performed. See the Data Ready Interrupt section for more details. Rev. E | Page 25 of 43

ADXL362 Data Sheet FIFO ENTRIES REGISTERS Z-AXIS DATA REGISTERS These registers indicate the number of valid data samples These two registers contain the sign extended (SX) z-axis present in the FIFO buffer. This number ranges from 0 to 512 acceleration data. ZDATA_L contains the eight LSBs, and or 0x00 to 0x200. FIFO_ENTRIES_L contains the least significant ZDATA_H contains the four MSBs of the 12-bit value. byte. FIFO_ENTRIES_H contains the two most significant bits. The sign extension bits (B[15:12], denoted as SX in the Bits[15:10] of FIFO_ENTRIES_H are unused (represented as X ZDATA_H bit map that follows) have the same value as the = don’t care). MSB (B11). Address: 0x0C, Reset: 0x00, Name: FIFO_ENTRIES_L Address: 0x12, Reset: 0x00, Name: ZDATA_L Address: 0x0D, Reset: 0x00, Name: FIFO_ENTRIES_H Address: 0x13, Reset: 0x00, Name: ZDATA_H X-AXIS DATA REGISTERS TEMPERATURE DATA REGISTERS These two registers contain the sign extended (SX) x-axis These two registers contain the sign extended (SX) tempera- acceleration data. XDATA_L contains the eight least significant ture sensor output data. TEMP_L contains the eight LSBs, and bits (LSBs), and XDATA_H contains the four most significant TEMP_H contains the four MSBs of the 12-bit value. The value is bits (MSBs) of the 12-bit value. sign extended; therefore, Bits[B15:B12] of TEMP_H are all 0s or The sign extension bits (B[15:12], denoted as SX in the all 1s, based on the value of Bit B11. XDATA_H bit map that follows) have the same value as the The sign extension bits (B[15:12], denoted as SX in the TEMP_H MSB (B11). bit map that follows) have the same value as the MSB (B11). Address: 0x0E, Reset: 0x00, Name: XDATA_L Address: 0x14, Reset: 0x00, Name: TEMP_L Address: 0x0F, Reset: 0x00, Name: XDATA_H Address: 0x15, Reset: 0x00, Name: TEMP_H Y-AXIS DATA REGISTERS SOFT RESET REGISTER These two registers contain the sign extended (SX) y-axis Address: 0x1F, Reset: 0x00, Name: SOFT_RESET acceleration data. YDATA_L contains the eight LSBs and Writing Code 0x52 (representing the letter, R, in ASCII or YDATA_H contains the four MSBs of the 12-bit value. unicode) to this register immediately resets the ADXL362. All The sign extension bits (B[15:12], denoted as SX in the register settings are cleared, and the sensor is placed in standby. YDATA_H bit map that follows) have the same value as the Interrupt pins are configured to a high output impedance mode MSB (B11). and held to a valid state by bus keepers. Address: 0x10, Reset: 0x00, Name: YDATA_L This is a write-only register. If read, data in it is always 0x00. A latency of approximately 0.5 ms is required after soft reset. Address: 0x11, Reset: 0x00, Name: YDATA_H Rev. E | Page 26 of 43

Data Sheet ADXL362 ACTIVITY THRESHOLD REGISTERS When the accelerometer is in wake-up mode, the TIME_ACT value is ignored and activity is detected based on a single To detect activity, the ADXL362 compares the absolute value of acceleration sample. the 12-bit (signed) acceleration data with the 11-bit (unsigned) THRESH_ACT value. See the Motion Detection section for more information on activity detection. The term, THRESH_ACT, refers to an 11-bit unsigned value com- INACTIVITY THRESHOLD REGISTERS prising the THRESH_ACT_L register, which holds its eight LSBs; and the THRESH_ACT_H register, which holds its three MSBs. To detect inactivity, the absolute value of the 12-bit acceleration data is compared with the 11-bit (unsigned) THRESH_INACT THRESH_ACT is set in codes; the value in g depends on the value. See the Motion Detection section for more information. measurement range setting that is selected. The term, THRESH_INACT, refers to an 11-bit unsigned value THRESH_ACT [g] = THRESH_ACT [codes]/Sensitivity comprised of the THRESH_INACT_L registers, which holds its [codes per g] eight LSBs and the THRESH_INACT_H register, which holds Address: 0x20, Reset: 0x00, Name: THRESH_ACT_L its three MSBs. This 11-bit unsigned value sets the threshold for inactivity detection. This value is set in codes; the value (in g) depends on the measurement range setting selected: Address: 0x21, Reset: 0x00, Name: THRESH_ACT_H THRESH_INACT [g] = THRESH_INACT [codes]/Sensitivity [codes per g] Address: 0x23, Reset: 0x00, Name: THRESH_INACT_L ACTIVITY TIME REGISTER Address: 0x22, Reset: 0x00, Name: TIME_ACT The activity timer implements a robust activity detection that Address: 0x24, Reset: 0x00, Name: THRESH_INACT_H minimizes false positive motion triggers. When the timer is used, only sustained motion can trigger activity detection. Refer to the Fewer False Positives section for additional information. The value in this register sets the number of consecutive INACTIVITY TIME REGISTERS samples that must have at least one axis greater than the activity The 16-bit value in these registers sets the number of consecu- threshold (set by THRESH_ACT) for an activity event to be tive samples that must have all axes lower than the inactivity detected. threshold (set by THRESH_INACT) for an inactivity event to The time (in seconds) is given by the following equation: be detected. Time = TIME_ACT/ODR The TIME_INACT_L register holds the eight LSBs and the where: TIME_INACT_H register holds the eight MSBs of the 16-bit TIME_ACT is the value set in this register. TIME_INACT value. ODR is the output data rate set in the FILTER_CTL register The time in seconds can be calculated as (Address 0x2C). Time = TIME_INACT/ODR Setting the activity time to 0x00 has the same result as setting where: this time to 0x01: Activity is detected when a single acceleration TIME_INACT is the 16-bit value set by the TIME_INACT_L reg- sample has at least one axis greater than the activity threshold ister (eight LSBs) and the TIME_INACT_H register (eight MSBs). (THRESH_ACT). ODR is the output data rate set in the FILTER_CTL register (Address 0x2C). Rev. E | Page 27 of 43

ADXL362 Data Sheet The 16-bit value allows for long inactivity detection times. The Address: 0x25, Reset: 0x00, Name: TIME_INACT_L maximum value is 0xFFFF or 65,535 samples. At the lowest output data rate, 12.5 Hz, this equates to almost 90 minutes. In this con- figuration, the accelerometer must be stationary for 90 minutes before putting its system to sleep. Address: 0x26, Reset: 0x00, Name: TIME_INACT_H Setting the inactivity time to 0x00 has the same result as setting this time to 0x01: Inactivity is detected when a single acceleration sample has all axes lower than the inactivity threshold (THRESH_INACT). Rev. E | Page 28 of 43

Data Sheet ADXL362 ACTIVITY/INACTIVITY CONTROL REGISTER Address: 0x27, Reset: 0x00, Name: ACT_INACT_CTL Table 13. Bit Descriptions for ACT_INACT_CTL Bits Bit Name Settings Description Reset Access [7:6] UNUSED Unused Bits. 0x0 RW [5:4] LINK/LOOP X0 Default Mode. 0x0 RW Activity and inactivity detection are both enabled, and their interrupts (if mapped) must be acknowledged by the host processor by reading the STATUS register. Autosleep is disabled in this mode. Use this mode for free fall detection applications. 01 Linked Mode. Activity and inactivity detection are linked sequentially such that only one is enabled at a time. Their interrupts (if mapped) must be acknowledged by the host processor by reading the STATUS register. 11 Loop Mode. Activity and inactivity detection are linked sequentially such that only one is enabled at a time, and their interrupts are internally acknowledged (do not need to be serviced by the host processor). To use either linked or looped mode, both ACT_EN (Bit 0) and INACT_EN (Bit 2) must be set to 1; otherwise, the default mode is used. For additional information, refer to the Linking Activity and Inactivity Detection section. 3 INACT_REF Referenced/Absolute Inactivity Select. 0x0 RW 1 = inactivity detection function operates in referenced mode. 0= inactivity detection function operates in absolute mode. 2 INACT_EN Inactivity Enable. 0x0 RW 1 = enables the inactivity (underthreshold) functionality. 1 ACT_REF Referenced/Absolute Activity Select. 0x0 RW 1 = activity detection function operates in referenced mode. 0 = activity detection function operates in absolute mode. 0 ACT_EN Activity Enable. 0x0 RW 1 = enables the activity (overthreshold) functionality. Rev. E | Page 29 of 43

ADXL362 Data Sheet FIFO CONTROL REGISTER Address: 0x28, Reset: 0x00, Name: FIFO_CONTROL Table 14. Bit Descriptions for FIFO_CONTROL Bits Bit Name Settings Description Reset Access [7:4] UNUSED Unused Bits. 0x0 RW 3 AH Above Half. 0x0 RW This bit is the MSB of the FIFO_SAMPLES register, allowing FIFO samples a range of 0 to 511. 2 FIFO_TEMP Store Temperature Data to FIFO. 1 = temperature data is stored in the FIFO 0x0 RW together with x-, y-, and z-axis acceleration data. [1:0] FIFO_MODE Enable FIFO and Mode Selection. 0x0 RW 00 FIFO is disabled. 01 Oldest saved mode. 10 Stream mode. 11 Triggered mode. Rev. E | Page 30 of 43