ICGOO在线商城 > 集成电路(IC) > 嵌入式 - DSP(数字式信号处理器) > ADSP-21368KBPZ-3A

- 型号: ADSP-21368KBPZ-3A

- 制造商: Analog

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

ADSP-21368KBPZ-3A产品简介:

ICGOO电子元器件商城为您提供ADSP-21368KBPZ-3A由Analog设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 ADSP-21368KBPZ-3A价格参考。AnalogADSP-21368KBPZ-3A封装/规格:嵌入式 - DSP(数字式信号处理器), 。您可以下载ADSP-21368KBPZ-3A参考资料、Datasheet数据手册功能说明书,资料中有ADSP-21368KBPZ-3A 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC)半导体 |

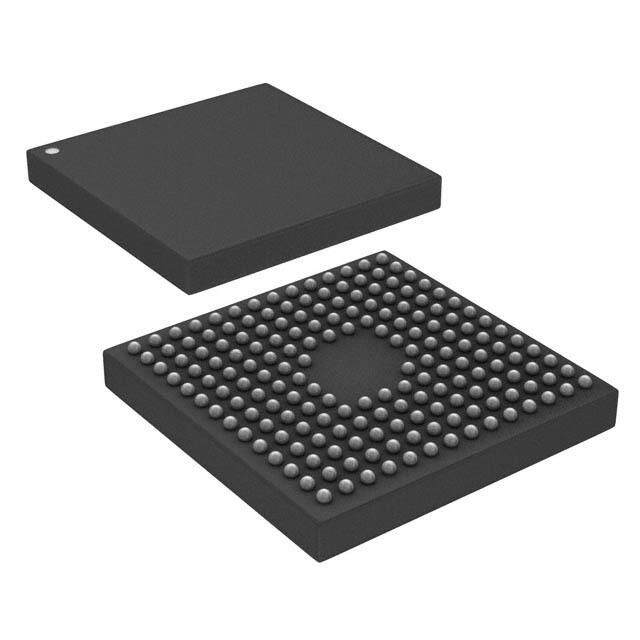

| 描述 | IC DSP 32BIT 400MHZ 256BGA数字信号处理器和控制器 - DSP, DSC High-Perf 32B Floating-Point |

| 产品分类 | |

| 品牌 | Analog Devices |

| MIPS | 800 MIPs |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 嵌入式处理器和控制器,数字信号处理器和控制器 - DSP, DSC,Analog Devices ADSP-21368KBPZ-3ASHARC® |

| 数据手册 | |

| 产品型号 | ADSP-21368KBPZ-3A |

| PCN设计/规格 | |

| 产品 | DSPs |

| 产品培训模块 | http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=12979 |

| 产品种类 | 数字信号处理器和控制器 - DSP, DSC |

| 供应商器件封装 | 256-BGA(27x27) |

| 其它名称 | ADSP21368KBPZ3A |

| 包装 | 托盘 |

| 可编程输入/输出端数量 | 16 |

| 商标 | Analog Devices |

| 商标名 | SHARC |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 定时器数量 | 3 Timer |

| 封装 | Tray |

| 封装/外壳 | 256-LBGA 裸露焊盘 |

| 封装/箱体 | BGA-256 |

| 工作温度 | 0°C ~ 70°C |

| 工作电源电压 | 1.25 V to 1.35 V |

| 工厂包装数量 | 40 |

| 接口 | DAI,DPI |

| 数据RAM大小 | 256 kB |

| 数据ROM大小 | 6 MB |

| 数据总线宽度 | 32 bit |

| 时钟速率 | 400MHz |

| 最大工作温度 | + 85 C |

| 最大时钟频率 | 400 MHz |

| 最小工作温度 | - 40 C |

| 标准包装 | 1 |

| 核心 | SHARC |

| 片载RAM | 256kB |

| 电压-I/O | 3.30V |

| 电压-内核 | 1.30V |

| 程序存储器大小 | 2 MB |

| 类型 | 浮点 |

| 系列 | ADSP-21368 |

| 输入/输出端数量 | 16 I/O |

| 非易失性存储器 | ROM(768 kB) |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

SHARC Processor ADSP-21369 SUMMARY DEDICATED AUDIO COMPONENTS High performance 32-bit/40-bit floating-point processor S/PDIF-compatible digital audio receiver/transmitter optimized for high performance audio processing 4 independent asynchronous sample rate converters (SRC) Single-instruction, multiple-data (SIMD) computational 16 PWM outputs configured as four groups of four outputs architecture ROM-based security features include On-chip memory—2M bits of on-chip SRAM and 6M bits of JTAG access to memory permitted with a 64-bit key on-chip mask programmable ROM Protected memory regions that can be assigned to limit Code compatible with all other members of the SHARC family access under program control to sensitive code 400 MHz core instruction rate with unique audiocentric PLL has a wide variety of software and hardware multi- peripherals such as the digital applications interface, plier/divider ratios S/PDIF transceiver, serial ports, 8-channel asynchronous Available in 256-ball BGA_ED and 208-lead LQFP_EP sample rate converter, precision clock generators, and packages more. For complete ordering information, see Ordering Guide. Internal Memory SIMD Core Block 0 Block 1 Block 2 Block 3 RAM/ROM RAM/ROM RAM RAM Instruction 5 stage Cache Sequencer S B0D B1D B2D B3D 64-BIT 64-BIT 64-BIT 64-BIT DAG1/2 Timer DMD 64-BIT DMD 64-BIT PEx PEy Core Bus Internal Memory I/F Cross Bar PMD PMD 64-BIT 64-BIT FLAGx/IRQx/ JTAG EPD BUS 32-BIT IOD0 32-BIT TMREXP PERIPHERAL BUS 32-BIT IOD1 32-BIT IOD0 BUS MTM PERIPHERAL BUS EP CORE PCG TIMER UART S/PDIF PCG ASRC IDP/ SPORT CORE PWM FLAGS C-D 2-0 TWI SPI/B 1-0 Tx/Rx A-D 3-0 PDAP 7-0 FLAGS 3-0 AMI SDRAM 7-0 DPI Routing/Pins DAI Routing/Pins External Port Pin MUX External DPI Peripherals DAI Peripherals Peripherals Port Figure 1. Functional Block Diagram SHARC and the SHARC logo are registered trademarks of Analog Devices, Inc. Rev. H Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 U.S.A. or otherwise under any patent or patent rights of Analog Devices. Trademarks and Tel: 781.329.4700 ©2019 Analog Devices, Inc. All rights reserved. registered trademarks are the property of their respective companies. Technical Support www.analog.com

ADSP-21369 TABLE OF CONTENTS General Description ................................................. 3 Maximum Power Dissipation ................................. 17 SHARC Family Core Architecture ............................ 4 Absolute Maximum Ratings ................................... 18 Family Peripheral Architecture ................................ 7 Timing Specifications ........................................... 18 I/O Processor Features ......................................... 10 Output Drive Currents ......................................... 50 System Design .................................................... 10 Test Conditions .................................................. 50 Development Tools ............................................. 11 Capacitive Loading .............................................. 50 Additional Information ........................................ 12 Thermal Characteristics ........................................ 52 Related Signal Chains .......................................... 12 256-Ball BGA_ED Pinout ......................................... 53 Pin Function Descriptions ....................................... 13 208-Lead LQFP_EP Pinout ....................................... 56 Specifications ........................................................ 16 Package Dimensions ............................................... 58 Operating Conditions .......................................... 16 Surface-Mount Design .......................................... 59 Electrical Characteristics ....................................... 17 Ordering Guide ..................................................... 60 ESD Caution ...................................................... 17 REVISION HISTORY 3/2019—Rev. G to Rev. H Deleted obsolete models ADSP-21367 and ADSP-21368 throughout data sheet. Reorganized layout of data sheet. Rev. H | Page 2 of 60 | March 2019

ADSP-21369 GENERAL DESCRIPTION The ADSP-21369 SHARC® processor is a member of the SIMD Table 2. Product Features (Continued) SHARC family of DSPs that feature Analog Devices’ Super Har- vard Architecture. These processors are source code-compatible Feature ADSP-21369 with the ADSP-2126x and ADSP-2116x DSPs as well as with DPI Yes first generation ADSP-2106x SHARC processors in SISD (sin- gle-instruction, single-data) mode. The processors are 32- S/PDIF Transceiver 1 bit/40-bit floating-point processors optimized for high perfor- AMI Interface Bus Width 32 bits/16 bits/8 bits mance automotive audio applications with its large on-chip SRAM, mask programmable ROM, multiple internal buses to SPI 2 eliminate I/O bottlenecks, and an innovative digital applications TWI Yes interface (DAI). SRC Performance 128 dB As shown in the functional block diagram onPage1, the processor uses two computational units to deliver a significant Shared Memory Support 256-Ball BGA only performance increase over the previous SHARC processors on a Package 256-Ball BGA, 208-Lead LQFP_EP range of DSP algorithms. Fabricated in a state-of-the-art, high speed, CMOS process, the processor achieves an instruction cycle time of up to 2.5 ns at 400 MHz. With its SIMD computa- The diagram onPage1 shows the two clock domains. The core tional hardware, the processor can perform 2.4 GFLOPS clock domain contains the following features. running at 400 MHz. • Two processing elements (PEx, PEy), each of which com- Table1 shows performance benchmarks for the ADSP-21369 prises an ALU, multiplier, shifter, and data register file processor. • Data address generators (DAG1, DAG2) • Program sequencer with instruction cache Table 1. Processor Benchmarks (at 400 MHz) • PM and DM buses capable of supporting two 64-bit data Speed transfers between memory and the core at every core pro- Benchmark Algorithm (at 400 MHz) cessor cycle 1024 Point Complex FFT (Radix 4, with Reversal) 23.2 s • One periodic interval timer with pinout FIR Filter (per Tap)1 1.25 ns • On-chip SRAM (2M bit) IIR Filter (per Biquad)1 5.0 ns • JTAG test access port for emulation and boundary scan. Matrix Multiply (Pipelined) The JTAG provides software debug through user break- [3×3] × [3×1] 11.25 ns points which allows flexible exception handling. [4×4] × [4×1] 20.0 ns The block diagram onPage1 also shows the peripheral clock Divide (y/x) 8.75 ns domain (also known as the I/O processor) and contains the fol- Inverse Square Root 13.5 ns lowing features: 1Assumes two files in multichannel SIMD mode. • IOD0 (peripheral DMA) andI OD1 (external port DMA) buses for 32-bit data transfers Table 2. Product Features • Peripheral and external port buses for core connection • External port with an AMI and SDRAM controller Feature ADSP-21369 • 4 units for PWM control Frequency 400 MHz • 1 MTM unit for internal-to-internal memory transfers RAM 2M bits • Digital applications interface that includes four precision ROM 6M bits clock generators (PCG), a input data port (IDP) for serial Pulse-Width Modulation Yes and parallel interconnect, an S/PDIF receiver/transmitter, four asynchronous sample rate converters, eight serial S/PDIF Yes ports, a flexible signal routing unit (DAI SRU). SDRAM Memory Bus Width 32 bits/16 bits • Digital peripheral interface that includes three timers, a 2- Serial Ports 8 wire interface, two UARTs, two serial peripheral interfaces (SPI), 2 precision clock generators (PCG) and a flexible sig- IDP Yes nal routing unit (DPI SRU). DAI Yes UART 2 Rev. H | Page 3 of 60 | March 2019

ADSP-21369 SHARC FAMILY CORE ARCHITECTURE shares architectural features with the ADSP-2126x and ADSP-2116x SIMD SHARC processors, as shown in Figure2 The processor is code compatible at the assembly level with the and detailed in the following sections. ADSP-2126x, ADSP-21160, and ADSP-21161, and with the first generation ADSP-2106x SHARC processors. The processor S JTAG FLAG TIMER INTERRUPT CACHE SIMD Core PM ADDRESS 24 DMD/PMD 64 5 STAGE PROGRAM SEQUENCER PM DATA 48 DAG1 DAG2 16x32 16x32 PM ADDRESS 32 SYSTEM I/F DM ADDRESS 32 USTAT PM DATA 64 4x32-BIT PX DM DATA 64 64-BIT RF DATA RF MULTIPLIER SHIFTER ALU Rx/Fx SWAP Sx/SFx ALU SHIFTER MULTIPLIER PEx PEy 16x40-BIT 16x40-BIT MRF MRB MSB MSF 80-BIT 80-BIT ASTATx ASTATy 80-BIT 80-BIT STYKx STYKy Figure 2. SHARC Core Block Diagram Rev. H | Page 4 of 60 | March 2019

ADSP-21369 SIMD Computational Engine The data bus exchange register (PX) permits data to be passed between the 64-bit PM data bus and the 64-bit DM data bus, or The processor contains two computational processing elements between the 40-bit register file and the PM data bus. These reg- that operate as a single-instruction, multiple-data (SIMD) isters contain hardware to handle the data width difference. engine. The processing elements are referred to as PEX and PEY and each contains an ALU, multiplier, shifter, and register file. Timer PEX is always active, and PEY may be enabled by setting the A core timer that can generate periodic software Interrupts. The PEYEN mode bit in the MODE1 register. When this mode is core timer can be configured to use FLAG3 as a timer expired enabled, the same instruction is executed in both processing ele- signal. ments, but each processing element operates on different data. This architecture is efficient at executing math intensive DSP Single-Cycle Fetch of Instruction and Four Operands algorithms. The processor features an enhanced Harvard architecture in Entering SIMD mode also has an effect on the way data is trans- which the data memory (DM) bus transfers data and the pro- ferred between memory and the processing elements. When in gram memory (PM) bus transfers both instructions and data SIMD mode, twice the data bandwidth is required to sustain (see Figure2). With separate program and data memory buses computational operation in the processing elements. Because of and on-chip instruction cache, the processors can simultane- this requirement, entering SIMD mode also doubles the band- ously fetch four operands (two over each data bus) and one width between memory and the processing elements. When instruction (from the cache), all in a single cycle. using the DAGs to transfer data in SIMD mode, two data values are transferred with each access of memory or the register file. Instruction Cache Independent, Parallel Computation Units The processors include an on-chip instruction cache that enables three-bus operation for fetching an instruction and four Within each processing element is a set of computational units. data values. The cache is selective—only the instructions whose The computational units consist of an arithmetic/logic unit fetches conflict with PM bus data accesses are cached. This (ALU), multiplier, and shifter. These units perform all opera- cache allows full-speed execution of core, looped operations tions in a single cycle. The three units within each processing such as digital filter multiply-accumulates, and FFT butterfly element are arranged in parallel, maximizing computational processing. throughput. Single multifunction instructions execute parallel ALU and multiplier operations. In SIMD mode, the parallel Data Address Generators with Zero-Overhead Hardware ALU and multiplier operations occur in both processing Circular Buffer Support elements. These computation units support IEEE 32-bit single- The processor has two data address generators (DAGs). The precision floating-point, 40-bit extended precision floating- DAGs are used for indirect addressing and implementing circu- point, and 32-bit fixed-point data formats. lar data buffers in hardware. Circular buffers allow efficient Data Register File programming of delay lines and other data structures required in digital signal processing, and are commonly used in digital A general-purpose data register file is contained in each pro- filters and Fourier transforms. The two DAGs contain sufficient cessing element. The register files transfer data between the registers to allow the creation of up to 32 circular buffers computation units and the data buses, and store intermediate (16primary register sets, 16 secondary). The DAGs automati- results. These 10-port, 32-register (16 primary, 16 secondary) cally handle address pointer wraparound, reduce overhead, register files, combined with the enhanced Harvard architecture increase performance, and simplify implementation. Circular of the ADSP-21369 processor, allow unconstrained data flow buffers can start and end at any memory location. between computation units and internal memory. The registers in PEX are referred to as R0–R15 and in PEY as S0–S15. Flexible Instruction Set Context Switch The 48-bit instruction word accommodates a variety of parallel operations for concise programming. For example, the Many of the processor’s registers have secondary registers that ADSP-21369 processor can conditionally execute a multiply, an can be activated during interrupt servicing for a fast context add, and a subtract in both processing elements while branching switch. The data registers in the register file, the DAG registers, and fetching up to four 32-bit values from memory—all in a sin- and the multiplier result registers all have secondary registers. gle instruction. The primary registers are active at reset, while the secondary registers are activated by control bits in a mode control register. Universal Registers These registers can be used for general-purpose tasks. The USTAT (4) registers allow easy bit manipulations (Set, Clear, Toggle, Test, XOR) for all system registers (control/status) of the core. Rev. H | Page 5 of 60 | March 2019

ADSP-21369 On-Chip Memory Using the DM bus and PM buses, with one bus dedicated to each memory block, assures single-cycle execution with two The processors contain two megabits of internal RAM and six data transfers. In this case, the instruction must be available in megabits of internal mask-programmable ROM. Each block can the cache. be configured for different combinations of code and data stor- age (see Table3). Each memory block supports single-cycle, On-Chip Memory Bandwidth independent accesses by the core processor and I/O processor. The internal memory architecture allows programs to have four The memory architecture, in combination with its separate on- accesses at the same time to any of the four blocks (assuming chip buses, allows two data transfers from the core and one there are no block conflicts). The total bandwidth is realized from the I/O processor, in a single cycle. using the DMD and PMD buses (2 × 64-bit, core CLK) and the The SRAM can be configured as a maximum of 64k words of IOD0/1 buses (2 × 32-bit, PCLK). 32-bit data, 128k words of 16-bit data, 42k words of 48-bit instructions (or 40-bit data), or combinations of different word ROM-Based Security sizes up to two megabits. All of the memory can be accessed as The processor has a ROM security feature that provides hard- 16-bit, 32-bit, 48-bit, or 64-bit words. A 16-bit floating-point ware support for securing user software code by preventing storage format is supported that effectively doubles the amount unauthorized reading from the internal code when enabled. of data that can be stored on-chip. Conversion between the When using this feature, the processor does not boot-load any 32-bit floating-point and 16-bit floating-point formats is per- external code, executing exclusively from internal ROM. Addi- formed in a single instruction. While each memory block can tionally, the processor is not freely accessible via the JTAG port. store combinations of code and data, accesses are most efficient Instead, a unique 64-bit key, which must be scanned in through when one block stores data using the DM bus for transfers, and the JTAG or test access port will be assigned to each customer. the other block stores instructions and data using the PM bus The device will ignore a wrong key. Emulation features and for transfers. external boot modes are only available after the correct key is scanned. Table 3. Internal Memory Space1 IOP Registers 0x0000 0000–0x0003 FFFF Extended Precision Normal or Long Word (64 Bits) Instruction Word (48 Bits) Normal Word (32 Bits) Short Word (16 Bits) Block 0 ROM (Reserved) Block 0 ROM (Reserved) Block 0 ROM (Reserved) Block 0 ROM (Reserved) 0x0004 0000–0x0004 BFFF 0x0008 0000–0x0008 FFFF 0x0008 0000–0x0009 7FFF 0x0010 0000–0x0012 FFFF Reserved Reserved Reserved Reserved 0x0004 F000–0x0004 FFFF 0x0009 4000–0x0009 FFFF 0x0009 E000–0x0009 FFFF 0x0013 C000–0x0013 FFFF Block 0 SRAM Block 0 SRAM Block 0 SRAM Block 0 SRAM 0x0004 C000–0x0004 EFFF 0x0009 0000–0x0009 3FFF 0x0009 8000–0x0009 DFFF 0x0013 0000–0x0013 BFFF Block 1 ROM (Reserved) Block 1 ROM (Reserved) Block 1 ROM (Reserved) Block 1 ROM (Reserved) 0x0005 0000–0x0005 BFFF 0x000A 0000–0x000A FFFF 0x000A 0000–0x000B 7FFF 0x0014 0000–0x0016 FFFF Reserved Reserved Reserved Reserved 0x0005 F000–0x0005 FFFF 0x000B 4000–0x000B FFFF 0x000B E000–0x000B FFFF 0x0017 C000–0x0017 FFFF Block 1 SRAM Block 1 SRAM Block 1 SRAM Block 1 SRAM 0x0005 C000–0x0005 EFFF 0x000B 0000–0x000B 3FFF 0x000B 8000–0x000B DFFF 0x0017 0000–0x0017 BFFF Block 2 SRAM Block 2 SRAM Block 2 SRAM Block 2 SRAM 0x0006 0000–0x0006 0FFF 0x000C 0000–0x000C 1554 0x000C 0000–0x000C 1FFF 0x0018 0000–0x0018 3FFF Reserved Reserved Reserved Reserved 0x0006 1000– 0x0006 FFFF 0x000C 1555–0x000C 3FFF 0x000C 2000–0x000D FFFF 0x0018 4000–0x001B FFFF Block 3 SRAM Block 3 SRAM Block 3 SRAM Block 3 SRAM 0x0007 0000–0x0007 0FFF 0x000E 0000–0x000E 1554 0x000E 0000–0x000E 1FFF 0x001C 0000–0x001C 3FFF Reserved Reserved Reserved Reserved 0x0007 1000–0x0007 FFFF 0x000E 1555–0x000F FFFF 0x000E 2000–0x000F FFFF 0x001C 4000–0x001F FFFF 1The processor includes a customer-definable ROM block. Please contact your Analog Devices sales representative for additional details. Rev. H | Page 6 of 60 | March 2019

ADSP-21369 FAMILY PERIPHERAL ARCHITECTURE Table 4. External Memory for SDRAM Addresses The processor contains a rich set of peripherals that support a Size in wide variety of applications including high quality audio, medi- Bank Words Address Range cal imaging, communications, military, test equipment, 3D graphics, speech recognition, motor control, imaging, and other Bank 0 62M 0x0020 0000–0x03FF FFFF applications. Bank 1 64M 0x0400 0000–0x07FF FFFF External Port Bank 2 64M 0x0800 0000–0x0BFF FFFF The external port interface supports access to the external mem- Bank 3 64M 0x0C00 0000–0x0FFF FFFF ory through core and DMA accesses. The external memory address space is divided into four banks. Any bank can be pro- devices and DIMMs (dual inline memory module), while the grammed as either asynchronous or synchronous memory. The second is an asynchronous memory controller intended to external ports of the processor are comprised of the following interface to a variety of memory devices. Four memory select modules. pins enable up to four separate devices to coexist, supporting • An Asynchronous Memory Interface which communicates any desired combination of synchronous and asynchronous with SRAM, FLASH, and other devices that meet the stan- device types. Non-SDRAM external memory address space is dard asynchronous SRAM access protocol. The AMI shown in Table5. supports 14M words of external memory in bank 0 and 16M words of external memory in bank 1, bank 2, and Table 5. External Memory for Non-SDRAM Addresses bank 3. • An SDRAM controller that supports a glueless interface Size in with any of the standard SDRAMs. The SDC supports 62M Bank Words Address Range words of external memory in bank 0, and 64M words of Bank 0 14M 0x0020 0000–0x00FF FFFF external memory in bank 1, bank 2, and bank 3. Bank 1 16M 0x0400 0000–0x04FF FFFF • Arbitration Logic to coordinate core and DMA transfers between internal and external memory over the external Bank 2 16M 0x0800 0000–0x08FF FFFF port. Bank 3 16M 0x0C00 0000–0x0CFF FFFF • A Shared Memory Interface that allows the connection of up to four processors to create shared external bus systems. Shared External Memory SDRAM Controller The ADSP-21369 processor supports connecting to common The SDRAM controller provides an interface of up to four sepa- shared external memory with other ADSP-21369 processors to rate banks of industry-standard SDRAM devices or DIMMs, at create shared external bus processor systems. This support speeds up to f . Fully compliant with the SDRAM standard, includes: SCLK each bank has its own memory select line (MS0–MS3), and can • Distributed, on-chip arbitration for the shared external bus be configured to contain between 16Mbytes and 128Mbytes of memory. SDRAM external memory address space is shown in • Fixed and rotating priority bus arbitration Table4. • Bus time-out logic A set of programmable timing parameters is available to config- • Bus lock ure the SDRAM banks to support slower memory devices. The Multiple processors can share the external bus with no addi- memory banks can be configured as either 32 bits wide for max- tional arbitration logic. Arbitration logic is included on-chip to imum performance and bandwidth or 16 bits wide for allow the connection of up to four processors. minimum device count and lower system cost. Bus arbitration is accomplished through the BR1–4 signals and The SDRAM controller address, data, clock, and control pins the priority scheme for bus arbitration is determined by the set- can drive loads up to distributed 30 pF loads. For larger memory ting of the RPBA pin. Table8 provides descriptions of the pins systems, the SDRAM controller external buffer timing should used in multiprocessor systems. be selected and external buffering should be provided so that the load on the SDRAM controller pins does not exceed 30 pF. External Port Throughput External Memory The throughput for the external port, based on 166 MHz clock and 32-bit data bus, is 221M bytes/s for the AMI and 664M The external port provides a high performance, glueless inter- bytes/s for SDRAM. face to a wide variety of industry-standard memory devices. The 32-bit wide bus can be used to interface to synchronous and/or asynchronous memory devices through the use of its separate internal memory controllers. The first is an SDRAM controller for connection of industry-standard synchronous DRAM Rev. H | Page 7 of 60 | March 2019

ADSP-21369 Asynchronous Memory Controller data or as seven channels plus a single 20-bit wide synchronous parallel data acquisition port. Each data channel has its own The asynchronous memory controller provides a configurable DMA channel that is independent from the processor’s serial interface for up to four separate banks of memory or I/O ports. devices. Each bank can be independently programmed with dif- ferent timing parameters, enabling connection to a wide variety For complete information on using the DAI, see the of memory devices including SRAM, ROM, flash, and EPROM, ADSP-2137x SHARC Processor Hardware Reference. as well as I/O devices that interface with standard memory Serial Ports control lines. Bank 0 occupies a 14M word window and Banks 1, 2, and 3 occupy a 16M word window in the processor’s address The processors feature eight synchronous serial ports (SPORTs) space but, if not fully populated, these windows are not made that provide an inexpensive interface to a wide variety of digital contiguous by the memory controller logic. The banks can also and mixed-signal peripheral devices such as Analog Devices’ be configured as 8-bit, 16-bit, or 32-bit wide buses for ease of AD183x family of audio codecs, ADCs, and DACs. The serial interfacing to a range of memories and I/O devices tailored ports are made up of two data lines, a clock, and frame sync. The either to high performance or to low cost and power. data lines can be programmed to either transmit or receive and each data line has a dedicated DMA channel. Pulse-Width Modulation Serial ports are enabled via 16 programmable and simultaneous The PWM module is a flexible, programmable, PWM waveform receive or transmit pins that support up to 32 transmit or 32 generator that can be programmed to generate the required receive channels of audio data when all eight SPORTs are switching patterns for various applications related to motor and enabled, or eight full duplex TDM streams of 128 channels engine control or audio power control. The PWM generator can per frame. generate either center-aligned or edge-aligned PWM wave- The serial ports operate at a maximum data rate of 50 Mbps. forms. In addition, it can generate complementary signals on Serial port data can be automatically transferred to and from two outputs in paired mode or independent signals in non- on-chip memory via dedicated DMA channels. Each of the paired mode (applicable to a single group of four PWM serial ports can work in conjunction with another serial port to waveforms). provide TDM support. One SPORT provides two transmit sig- The entire PWM module has four groups of four PWM outputs nals while the other SPORT provides the two receive signals. each. Therefore, this module generates 16 PWM outputs in The frame sync and clock are shared. total. Each PWM group produces two pairs of PWM signals on Serial ports operate in five modes: the four PWM outputs. • Standard DSP serial mode The PWM generator is capable of operating in two distinct modes while generating center-aligned PWM waveforms: single • Multichannel (TDM) mode with support for packed I2S update mode or double update mode. In single update mode, mode the duty cycle values are programmable only once per PWM • I2S mode period. This results in PWM patterns that are symmetrical • Packed I2S mode about the midpoint of the PWM period. In double update mode, a second updating of the PWM registers is implemented • Left-justified sample pair mode at the midpoint of the PWM period. In this mode, it is possible Left-justified sample pair mode is a mode where in each frame to produce asymmetrical PWM patterns that produce lower sync cycle two samples of data are transmitted/received—one harmonic distortion in 2-phase PWM inverters. sample on the high segment of the frame sync, the other on the Digital Applications Interface (DAI) low segment of the frame sync. Programs have control over var- ious attributes of this mode. The digital applications interface (DAI) provides the ability to Each of the serial ports supports the left-justified sample pair connect various peripherals to any of the DAI pins of the DSP and I2S protocols (I2S is an industry-standard interface com- (DAI_P20–1). Programs make these connections using the sig- monly used by audio codecs, ADCs, and DACs such as the nal routing unit (SRU1), shown in Figure1. Analog Devices AD183x family), with two data pins, allowing The SRU is a matrix routing unit (or group of multiplexers) that four left-justified sample pair or I2S channels (using two stereo enables the peripherals provided by the DAI to be intercon- devices) per serial port, with a maximum of up to 32 I2S chan- nected under software control. This allows easy use of the nels. The serial ports permit little-endian or big-endian associated peripherals for a much wider variety of applications transmission formats and word lengths selectable from 3 bits to by using a larger set of algorithms than is possible with noncon- 32 bits. For the left-justified sample pair and I2S modes, data- figurable signal paths. word lengths are selectable between 8 bits and 32 bits. Serial The DAI includes eight serial ports, an S/PDIF receiver/trans- ports offer selectable synchronization and transmit modes as mitter, four precision clock generators (PCG), eight channels of well as optional -law or A-law companding selection on a per synchronous sample rate converters, and an input data port channel basis. Serial port clocks and frame syncs can be inter- (IDP). The IDP provides an additional input path to the nally or externally generated. processor core, configurable as either eight channels of I2S serial Rev. H | Page 8 of 60 | March 2019

ADSP-21369 The serial ports also contain frame sync error detection logic Serial Peripheral (Compatible) Interface where the serial ports detect frame syncs that arrive early (for The processors contain two serial peripheral interface ports example, frame syncs that arrive while the transmission/recep- (SPIs). The SPI is an industry-standard synchronous serial link, tion of the previous word is occurring). All the serial ports also enabling the SPI-compatible port to communicate with other share one dedicated error interrupt. SPI-compatible devices. The SPI consists of two data pins, one S/PDIF-Compatible Digital Audio Receiver/Transmitter device select pin, and one clock pin. It is a full-duplex synchronous serial interface, supporting both master and slave The S/PDIF receiver/transmitter has no separate DMA chan- modes. The SPI port can operate in a multimaster environment nels. It receives audio data in serial format and converts it into a by interfacing with up to four other SPI-compatible devices, biphase encoded signal. The serial data input to the either acting as a master or slave device. The SPI-compatible receiver/transmitter can be formatted as left-justified, I2S, or peripheral implementation also features programmable baud right-justified with word widths of 16, 18, 20, or 24 bits. rate and clock phase and polarities. The SPI-compatible port The serial data, clock, and frame sync inputs to the S/PDIF uses open-drain drivers to support a multimaster configuration receiver/transmitter are routed through the signal routing unit and to avoid data contention. (SRU). They can come from a variety of sources such as the UART Port SPORTs, external pins, the precision clock generators (PCGs), or the sample rate converters (SRC) and are controlled by the The processors provide a full-duplex universal asynchronous SRU control registers. receiver/transmitter (UART) port, which is fully compatible with PC-standard UARTs. The UART port provides a simpli- Synchronous/Asynchronous Sample Rate Converter fied UART interface to other peripherals or hosts, supporting The sample rate converter (SRC) contains four SRC blocks and full-duplex, DMA-supported, asynchronous transfers of serial is the same core as that used in the AD1896 192 kHz stereo data. The UART also has multiprocessor communication capa- asynchronous sample rate converter and provides up to 128 dB bility using 9-bit address detection. This allows it to be used in SNR. The SRC block is used to perform synchronous or asyn- multidrop networks through the RS-485 data interface chronous sample rate conversion across independent stereo standard. The UART port also includes support for five data bits channels, without using internal processor resources. The four to eightdata bits, one stop bit or twostop bits, and none, even, SRC blocks can also be configured to operate together to con- or odd parity. The UART port supports two modes of vert multichannel audio data without phase mismatches. operation: Finally, the SRC can be used to clean up audio data from jittery • PIO (programmed I/O) – The processor sends or receives clock sources such as the S/PDIF receiver. data by writing or reading I/O-mapped UART registers. Input Data Port The data is double-buffered on both transmit and receive. • DMA (direct memory access) – The DMA controller trans- The IDP provides up to eight serial input channels—each with fers both transmit and receive data. This reduces the its own clock, frame sync, and data inputs. The eight channels number and frequency of interrupts required to transfer are automatically multiplexed into a single 32-bit by eight-deep data to and from memory. The UART has two dedicated FIFO. Data is always formatted as a 64-bit frame and divided DMA channels, one for transmit and one for receive. These into two 32-bit words. The serial protocol is designed to receive DMA channels have lower default priority than most DMA audio channels in I2S, left-justified sample pair, or right-justi- channels because of their relatively low service rates. fied mode. One frame sync cycle indicates one 64-bit left/right pair, but data is sent to the FIFO as 32-bit words (that is, one- The UART port’s baud rate, serial data format, error code gen- half of a frame at a time). The processor supports 24- and 32-bit eration and status, and interrupts are programmable: I2S, 24- and 32-bit left-justified, and 24-, 20-, 18- and 16-bit • Supporting bit rates ranging from (f /1,048,576) to right-justified formats. SCLK (f /16) bits per second. SCLK Precision Clock Generators • Supporting data formats from 7 bits to 12bits per frame. The precision clock generators (PCG) consist of four units, each • Both transmit and receive operations can be configured to of which generates a pair of signals (clock and frame sync) generate maskable interrupts to the processor. derived from a clock input signal. The units, A B, C, and D, are Where the 16-bit UART_Divisor comes from the DLH register identical in functionality and operate independently of each (most significant eight bits) and DLL register (least significant other. The two signals generated by each unit are normally used eightbits). as a serial bit clock/frame sync pair. In conjunction with the general-purpose timer functions, auto- Digital Peripheral Interface (DPI) baud detection is supported. The digital peripheral interface provides connections to two serial peripheral interface ports (SPI), two universal asynchro- nous receiver-transmitters (UARTs), a 2-wire interface (TWI), 12 flags, and three general-purpose timers. Rev. H | Page 9 of 60 | March 2019

ADSP-21369 Peripheral Timers Delay Line DMA Three general-purpose timers can generate periodic interrupts The processor provides delay line DMA functionality. This and be independently set to operate in one of three modes: allows processor reads and writes to external delay line buffers (in external memory, SRAM, or SDRAM) with limited core • Pulse waveform generation mode interaction. • Pulse width count/capture mode SYSTEM DESIGN • External event watchdog mode Each general-purpose timer has one bidirectional pin and four The following sections provide an introduction to system design registers that implement its mode of operation: a 6-bit configu- options and power supply issues. ration register, a 32-bit count register, a 32-bit period register, Program Booting and a 32-bit pulse width register. A single control and status register enables or disables all three general-purpose timers The internal memory of the processors can be booted up at sys- independently. tem power-up from an 8-bit EPROM via the external port, an SPI master or slave, or an internal boot. Booting is determined 2-Wire Interface Port (TWI) by the boot configuration (BOOT_CFG1–0) pins (see Table7 The TWI is a bidirectional 2-wire serial bus used to move 8-bit and the processor hardware reference). Selection of the boot data while maintaining compliance with the I2C bus protocol. source is controlled via the SPI as either a master or slave device, The TWI master incorporates the following features: or it can immediately begin executing from ROM. • Simultaneous master and slave operation on multiple Table 7. Boot Mode Selection device systems with support for multimaster data arbitration BOOT_CFG1–0 Booting Mode • Digital filtering and timed event processing 00 SPI Slave Boot • 7-bit and 10-bit addressing 01 SPI Master Boot 10 EPROM/FLASH Boot • 100 kbps and 400 kbps data rates 11 No boot (processor executes from • Low interrupt rate internal ROM after reset) I/O PROCESSOR FEATURES Power Supplies The I/O processor provides many channels of DMA, and con- trols the extensive set of peripherals described in the previous The processors have separate power supply connections for the sections. internal (V ), external (V ), and analog (A /A ) power DDINT DDEXT VDD VSS supplies. The internal and analog supplies must meet the 1.3 V DMA Controller requirement for the 400 MHz device and 1.2 V for the The processor’s on-chip DMA controller allows data transfers 333 MHz and 266 MHz devices. The external supply must meet without processor intervention. The DMA controller operates the 3.3 V requirement. All external supply pins must be con- independently and invisibly to the processor core, allowing nected to the same power supply. DMA operations to occur while the core is simultaneously exe- Note that the analog supply pin (A ) powers the processor’s VDD cuting its program instructions. DMA transfers can occur internal clock generator PLL. To produce a stable clock, it is rec- between the processor’s internal memory and its serial ports, the ommended that PCB designs use an external filter circuit for the SPI-compatible (serial peripheral interface) ports, the IDP A pin. Place the filter components as close as possible to the VDD (input data port), the parallel data acquisition port (PDAP), or A /A pins. For an example circuit, see Figure3. (A recom- VDD VSS the UART. mended ferrite chip is the muRata BLM18AG102SN1D). To Thirty four channels of DMA are available on the ADSP-2136x reduce noise coupling, the PCB should use a parallel pair of processors as shown in Table6. power and ground planes for VDDINT and GND. Use wide traces to connect the bypass capacitors to the analog power (A ) and VDD Table 6. DMA Channels ground (A ) pins. Note that the A and A pins specified in VSS VDD VSS Figure3 are inputs to the processor and not the analog ground Peripheral DMA Channels plane on the board—the A pin should connect directly to dig- VSS SPORTs 16 ital ground (GND) at the chip. PDAP 8 SPI 2 UART 4 External Port 2 Memory-to-Memory 2 Rev. H | Page 10 of 60 | March 2019

ADSP-21369 emulation capabilities and other evaluation and development ADSP-213xx features. Also available are various EZ-Extenders®, which are 100nF 10nF 1nF daughter cards delivering additional specialized functionality, VDDINT AVDD including audio and video processing. For more information visit www.analog.com and search on “ezkit” or “ezextender”. HI-ZFERRITE BEADCHIP AVSS EZ-KIT Lite Evaluation Kits For a cost-effective way to learn more about developing with LOCATEALLCOMPONENTS Analog Devices processors, Analog Devices offer a range of EZ- CLOSETOAVDDANDAVSSPINS KIT Lite evaluation kits. Each evaluation kit includes an EZ-KIT Lite evaluation board, directions for downloading an evaluation Figure 3. Analog Power (A ) Filter Circuit VDD version of the available IDE(s), a USB cable, and a power supply. The USB controller on the EZ-KIT Lite board connects to the Target Board JTAG Emulator Connector USB port of the user’s PC, enabling the chosen IDE evaluation Analog Devices DSP Tools product line of JTAG emulators uses suite to emulate the on-board processor in-circuit. This permits the IEEE 1149.1 JTAG test access port of the processor to moni- the customer to download, execute, and debug programs for the tor and control the target board processor during emulation. EZ-KIT Lite system. It also supports in-circuit programming of Analog Devices DSP Tools product line of JTAG emulators pro- the on-board Flash device to store user-specific boot code, vides emulation at full processor speed, allowing inspection and enabling standalone operation. With the full version of Cross- modification of memory, registers, and processor stacks. The Core Embedded Studio or VisualDSP++ installed (sold processor’s JTAG interface ensures that the emulator will not separately), engineers can develop software for supported EZ- affect target system loading or timing. KITs or any custom system utilizing supported Analog Devices processors. For complete information on Analog Devices’ SHARC DSP Tools product line of JTAG emulator operation, see the appro- Software Add-Ins for CrossCore Embedded Studio priate “Emulator Hardware User’s Guide.” Analog Devices offers software add-ins which seamlessly inte- DEVELOPMENT TOOLS grate with CrossCore Embedded Studio to extend its capabilities and reduce development time. Add-ins include board support Analog Devices supports its processors with a complete line of packages for evaluation hardware, various middleware pack- software and hardware development tools, including integrated ages, and algorithmic modules. Documentation, help, development environments (which include CrossCore® Embed- configuration dialogs, and coding examples present in these ded Studio and/or VisualDSP++®), evaluation products, add-ins are viewable through the CrossCore Embedded Studio emulators, and a wide variety of software add-ins. IDE once the add-in is installed. Integrated Development Environments (IDEs) Board Support Packages for Evaluation Hardware For C/C++ software writing and editing, code generation, and Software support for the EZ-KIT Lite evaluation boards and EZ- debug support, Analog Devices offers two IDEs. Extender daughter cards is provided by software add-ins called The newest IDE, CrossCore Embedded Studio, is based on the Board Support Packages (BSPs). The BSPs contain the required EclipseTM framework. Supporting most Analog Devices proces- drivers, pertinent release notes, and select example code for the sor families, it is the IDE of choice for future processors, given evaluation hardware. A download link for a specific BSP is including multicore devices. CrossCore Embedded Studio located on the web page for the associated EZ-KIT or EZ- seamlessly integrates available software add-ins to support real Extender product. The link is found in the Product Download time operating systems, file systems, TCP/IP stacks, USB stacks, area of the product web page. algorithmic software modules, and evaluation hardware board support packages. For more information visit www.analog.com/cces. The other Analog Devices IDE, VisualDSP++, supports proces- sor families introduced prior to the release of CrossCore Embedded Studio. This IDE includes the Analog Devices VDK real time operating system and an open source TCP/IP stack. For more information visit www.analog.com/visualdsp. Note that VisualDSP++ will not support future Analog Devices processors. EZ-KIT Lite Evaluation Board For processor evaluation, Analog Devices provides wide range of EZ-KIT Lite® evaluation boards. Including the processor and key peripherals, the evaluation board also supports on-chip Rev. H | Page 11 of 60 | March 2019

ADSP-21369 Middleware Packages RELATED SIGNAL CHAINS Analog Devices separately offers middleware add-ins such as A signal chain is a series of signal-conditioning electronic com- real time operating systems, file systems, USB stacks, and ponents that receive input (data acquired from sampling either TCP/IP stacks. For more information see the following web real-time phenomena or from stored data) in tandem, with the pages: output of one portion of the chain supplying input to the next. • www.analog.com/ucos2 Signal chains are often used in signal processing applications to gather and process data or to apply system controls based on • www.analog.com/ucos3 analysis of real-time phenomena. • www.analog.com/ucfs Analog Devices eases signal processing system development by • www.analog.com/ucusbd providing signal processing components that are designed to work together well. A tool for viewing relationships between • www.analog.com/ucusbh specific applications and related components is available on the • www.analog.com/lwip www.analog.com website. Algorithmic Modules The application signal chains page in the Circuits from the Lab® site (http:\\www.analog.com\circuits) provides: To speed development, Analog Devices offers add-ins that per- form popular audio and video processing algorithms. These are • Graphical circuit block diagram presentation of signal available for use with both CrossCore Embedded Studio and chains for a variety of circuit types and applications VisualDSP++. For more information visit www.analog.com and • Drill down links for components in each chain to selection search on “Blackfin software modules” or “SHARC software guides and application information modules”. • Reference designs applying best practice design techniques Designing an Emulator-Compatible DSP Board(Target) For embedded system test and debug, Analog Devices provides a family of emulators. On each JTAG DSP, Analog Devices sup- plies an IEEE 1149.1 JTAG Test Access Port (TAP). In-circuit emulation is facilitated by use of this JTAG interface. The emu- lator accesses the processor’s internal features via the processor’s TAP, allowing the developer to load code, set break- points, and view variables, memory, and registers. The processor must be halted to send data and commands, but once an operation is completed by the emulator, the DSP system is set to run at full speed with no impact on system timing. The emu- lators require the target board to include a header that supports connection of the JTAG port of the DSP to the emulator. For details on target board design issues including mechanical layout, single processor connections, signal buffering, signal ter- mination, and emulator pod logic, see “Analog Devices JTAG Emulation Technical Reference” (EE-68). This document is updated regularly to keep pace withimprovements to emulator support. ADDITIONAL INFORMATION This data sheet provides a general overview of the architecture and functionality of the ADSP-21369 processor. For detailed information on the ADSP-2136x family core archi- tecture and instruction set, refer to the ADSP-2137x SHARC Processor Hardware Reference and the SHARC Processor Pro- gramming Reference. Rev. H | Page 12 of 60 | March 2019

ADSP-21369 PIN FUNCTION DESCRIPTIONS The following symbols appear in the Type column of Table8: The ADSP-21369 SHARC processors use extensive pin multi- A = asynchronous, G = ground, I=input, O = output, plexing to achieve a lower pin count. For complete information O/T = output three-state, P = power supply, S = synchronous, on the multiplexing scheme, see the ADSP-2137x SHARC Pro- (A/D) = active drive, (O/D) = open-drain, (pd) = pull-down cessor Hardware Reference, “System Design” chapter. resistor, (pu) = pull-up resistor. Table 8. Pin Descriptions State During/ After Reset Name Type (ID = 00x) Description ADDR O/T (pu)1 Pulled high/ External Address. The processors output addresses for external memory and peripher- 23–0 driven low als on these pins. DATA I/O (pu)1 Pulled high/ External Data. Data pins can be multiplexed to support external memory interface data 31–0 pulled high (I/O), the PDAP (I), FLAGS (I/O), and PWM (O). After reset, all DATA pins are in EMIF mode and FLAG(0-3) pins are in FLAGS mode (default). When configured using the IDP_P- DAP_CTL register, IDP Channel 0 scans the external port data pins for parallel input data. ACK I (pu)1 Memory Acknowledge. External devices can deassert ACK (low) to add wait states to an external memory access. ACK is used by I/O devices, memory controllers, or other periph- erals to hold off completion of an external memory access. MS O/T (pu)1 Pulled high/ Memory Select Lines 0–1. These lines are asserted (low) as chip selects for the corre- 0–1 driven high sponding banks of external memory. The MS lines are decoded memory address lines 3-0 that change at the same time as the other address lines. When no external memory access is occurring, the MS lines are inactive; they are active, however, when a conditional 3-0 memory access instruction is executed, whether or not the condition is true. The MS pin can be used in EPORT/FLASH boot mode. See the processor hardware 1 reference for more information. RD O/T (pu)1 Pulled high/ External Port Read Enable. RD is asserted whenever the processors read a word from driven high external memory. WR O/T (pu)1 Pulled high/ External Port Write Enable. WR is asserted when the processors write a word to external driven high memory. FLAG[0]/IRQ0 I/O FLAG[0] INPUT FLAG0/Interrupt Request 0. FLAG[1]/IRQ1 I/O FLAG[1] INPUT FLAG1/Interrupt Request 1. FLAG[2]/IRQ2/ I/O with pro- FLAG[2] INPUT FLAG2/Interrupt Request 2/Memory Select 2. MS grammable pu 2 (for MS mode) FLAG[3]/ I/O with pro- FLAG[3] INPUT FLAG3/Timer Expired/Memory Select 3. TMREXP/MS grammable pu 3 (for MS mode) Rev. H | Page 13 of 60 | March 2019

ADSP-21369 Table 8. Pin Descriptions (Continued) State During/ After Reset Name Type (ID = 00x) Description SDRAS O/T (pu)1 Pulled high/ SDRAM Row Address Strobe. Connect to SDRAM’s RAS pin. In conjunction with other driven high SDRAM command pins, defines the operation for the SDRAM to perform. SDCAS O/T (pu)1 Pulled high/ SDRAM Column Address Select. Connect to SDRAM’s CAS pin. In conjunction with other driven high SDRAM command pins, defines the operation for the SDRAM to perform. SDWE O/T (pu)1 Pulled high/ SDRAM Write Enable. Connect to SDRAM’s WE or W buffer pin. driven high SDCKE O/T (pu)1 Pulled high/ SDRAM Clock Enable. Connect to SDRAM’s CKE pin. Enables and disables the CLK signal. driven high For details, see the data sheet supplied with the SDRAM device. SDA10 O/T (pu)1 Pulled high/ SDRAM A10 Pin. Enables applications to refresh an SDRAM in parallel with non- driven low SDRAM accesses. This pin replaces the DSP’s A10 pin only during SDRAM accesses. SDCLK0 O/T High-Z/driving SDRAM Clock Output 0. Clock driver for this pin differs from all other clock drivers. See Figure39. SDCLK1 O/T SDRAM Clock Output 1. Additional clock for SDRAM devices. For systems with multiple SDRAM devices, handles the increased clock load requirements, eliminating need of off- chip clock buffers. Either SDCLK1 or both SDCLKx pins can be three-stated. Clock driver for this pin differs from all other clock drivers. See Figure39. The SDCLK1 signal is only available on the FCBGA package. SDCLK1 is not available on the LQFP_EP package. DAI _P I/O with pro- Pulled high/ Digital Applications Interface. These pins provide the physical interface to the DAI SRU. 20–1 grammable pulled high The DAI SRU configuration registers define the combination of on-chip audiocentric pu2 peripheral inputs or outputs connected to the pin, and to the pin’s output enable. The configuration registers then determines the exact behavior of the pin. Any input or output signal present in the DAI SRU may be routed to any of these pins. The DAI SRU provides the connection from the serial ports (8), the SRC module, the S/PDIF module, input data ports (2), and the precision clock generators (4), to the DAI_P20–1 pins. Pull- ups can be disabled via the DAI_PIN_PULLUP register. DPI _P I/O with pro- Pulled high/ Digital Peripheral Interface. These pins provide the physical interface to the DPI SRU. 14–1 grammable pulled high The DPI SRU configuration registers define the combination of on-chip peripheral inputs pu2 or outputs connected to the pin and to the pin’s output enable. The configuration registers of these peripherals then determines the exact behavior of the pin. Any input or output signal present in the DPI SRU may be routed to any of these pins. The DPI SRU provides the connection from the timers (3), SPIs (2), UARTs (2), flags (12) TWI (1), and general-purpose I/O (9) to the DPI_P14–1 pins. The TWI output is an open-drain output— so the pins used for I2C data and clock should be connected to logic level 0. Pull-ups can be disabled via the DPI_PIN_PULLUP register. TDI I (pu) Test Data Input (JTAG). Provides serial data for the boundary scan logic. TDO O/T Test Data Output (JTAG). Serial scan output of the boundary scan path. TMS I (pu) Test Mode Select (JTAG). Used to control the test state machine. TCK I Test Clock (JTAG). Provides a clock for JTAG boundary scan. TCK must be asserted (pulsed low) after power-up, or held low for proper operation of the processor TRST I (pu) Test Reset (JTAG). Resets the test state machine. TRST must be asserted (pulsed low) after power-up or held low for proper operation of the processor. Rev. H | Page 14 of 60 | March 2019

ADSP-21369 Table 8. Pin Descriptions (Continued) State During/ After Reset Name Type (ID = 00x) Description EMU O (O/D, pu) Emulation Status. Must be connected to the processor Analog Devices DSP Tools product line of JTAG emulator target board connectors only. CLK_CFG I Core/CLKIN Ratio Control. These pins set the start-up clock frequency. See the processor 1–0 hardware reference for a description of the clock configuration modes. Note that the operating frequency can be changed by programming the PLL multiplier and divider in the PMCTL register at any time after the core comes out of reset. CLKIN I Local Clock In. Used with XTAL. CLKIN is the processor’s clock input. It configures the processors to use either its internal clock generator or an external clock source. Connect- ing the necessary components to CLKIN and XTAL enables the internal clock generator. Connecting the external clock to CLKIN while leaving XTAL unconnected configures the processor to use an external clock such as an external clock oscillator. CLKIN may not be halted, changed, or operated below the specified frequency. XTAL O Crystal Oscillator Terminal. Used in conjunction with CLKIN to drive an external crystal. RESET I Processor Reset. Resets the processor to a known state. Upon deassertion, there is a 4096 CLKIN cycle latency for the PLL to lock. After this time, the core begins program execution from the hardware reset vector address. The RESET input must be asserted (low) at power- up. RESETOUT O Driven low/ Reset Out. Drives out the core reset signal to an external device. driven high BOOT_CFG I Boot Configuration Select. These pins select the boot mode for the processor. The 1–0 BOOT_CFG pins must be valid before reset is asserted. See the processor hardware reference for a description of the boot modes. BR I/O (pu)1 Pulled high/ External Bus Request. Used to arbitrate for bus mastership. A processor only drives its 4–1 pulled high own BR line (corresponding to the value of its ID2-0 inputs) and monitors all others. In a x system with less than four processors, the unused BR pins should be tied high; the pro- x cessor’s own BR line must not be tied high or low because it is an output. x ID I (pd) Processor ID. Determines which bus request (BR ) is used by the processor. ID = 001 2–0 4–1 corresponds to BR ID = 010 corresponds to BR, and so on. Use ID = 000 or 001 in single- 1, 2 processor systems. These lines are a system configuration selection that should be hardwired or only changed at reset. ID = 101,110, and 111 are reserved. RPBA I (pu)1 Rotating Priority Bus Arbitration Select. When RPBA is high, rotating priority for external bus arbitration is selected. When RPBA is low, fixed priority is selected. This signal is a system configuration selection which must be set to the same value on every processor in the system. 1The pull-up is always enabled. 2Pull-up can be enabled/disabled, value of pull-up cannot be programmed. Rev. H | Page 15 of 60 | March 2019

ADSP-21369 SPECIFICATIONS OPERATING CONDITIONS 366 MHz 333 MHz 400 MHz 350 MHz 266 MHz Parameter1 Description Min Max Min Max Min Max Unit V Internal (Core) Supply Voltage 1.25 1.35 1.235 1.365 1.14 1.26 V DDINT A Analog (PLL) Supply Voltage 1.25 1.35 1.235 1.365 1.14 1.26 V VDD V External (I/O) Supply Voltage 3.13 3.47 3.13 3.47 3.13 3.47 V DDEXT V 2 High Level Input Voltage @ V = Max 2.0 V + 0.5 2.0 V + 0.5 2.0 V + 0.5 V IH DDEXT DDEXT DDEXT DDEXT V2 Low Level Input Voltage @ V = Min –0.5 +0.8 –0.5 +0.8 –0.5 +0.8 V IL DDEXT V 3 High Level Input Voltage @ V = Max 1.74 V + 0.5 1.74 V + 0.5 1.74 V + 0.5 V IH_CLKIN DDEXT DDEXT DDEXT DDEXT V 3 Low Level Input Voltage @ V = Min –0.5 +1.1 –0.5 +1.1 –0.5 +1.1 V IL_CLKIN DDEXT T Junction Temperature 208-Lead LQFP_EP @ J T 0C to 70C 0 95 0 110 0 110 C AMBIENT T Junction Temperature 208-Lead LQFP_EP @ J T –40C to +85C N/A N/A N/A N/A –40 +120 C AMBIENT T Junction Temperature 256-Ball BGA_ED @ J T 0C to 70C 0 95 N/A N/A 0 105 C AMBIENT T Junction Temperature 256-Ball BGA_ED @ J T –40C to +85C N/A N/A N/A N/A –40 +105 C AMBIENT 1Specifications subject to change without notice. 2Applies to input and bidirectional pins: DATAx, ACK, RPBA, BRx, IDx, FLAGx, DAI_Px, DPI_Px, BOOT_CFGx, CLK_CFGx, RESET, TCK, TMS, TDI, TRST. 3Applies to input pin CLKIN. Rev. H | Page 16 of 60 | March 2019

ADSP-21369 ELECTRICAL CHARACTERISTICS Parameter Description Test Conditions Min Typ Max Unit V 1 High Level Output Voltage @ V = Min, I = –1.0 mA2 2.4 V OH DDEXT OH V 1 Low Level Output Voltage @ V = Min, I = 1.0 mA2 0.4 V OL DDEXT OL I 3, 4 High Level Input Current @ V = Max, V = V Max 10 μA IH DDEXT IN DDEXT I3, 5, 6 Low Level Input Current @ V = Max, V = 0 V 10 μA IL DDEXT IN I 5 High Level Input Current Pull-Down @ V = Max, V = 0 V 250 μA IHPD DDEXT IN I 4 Low Level Input Current Pull-Up @ V = Max, V = 0 V 200 μA ILPU DDEXT IN I 7, 8 Three-State Leakage Current @ V = Max, V = V Max 10 μA OZH DDEXT IN DDEXT I 7, 9 Three-State Leakage Current @ V = Max, V = 0 V 10 μA OZL DDEXT IN I 8 Three-State Leakage Current Pull-Up @ V = Max, V = 0 V 200 μA OZLPU DDEXT IN I 10 Supply Current (Internal) t = 3.75 ns, V = 1.2 V, 25°C 700 mA DD-INTYP CCLK DDINT t = 3.00 ns, V = 1.2 V, 25°C 900 mA CCLK DDINT t = 2.85 ns, V = 1.3 V, 25°C 1050 mA CCLK DDINT t = 2.73 ns, V = 1.3 V, 25°C 1080 mA CCLK DDINT t = 2.50 ns, V = 1.3 V, 25°C 1100 mA CCLK DDINT AI 11 Supply Current (Analog) A = Max 11 mA DD VDD C 12 Input Capacitance f = 1 MHz, T = 25°C, V = 1.3 V 4.7 pF IN IN CASE IN 1Applies to output and bidirectional pins: ADDRx, DATAx, RD, WR, MSx, BRx, FLAGx, DAI_Px, DPI_Px, SDRAS, SDCAS, SDWE, SDCKE, SDA10, SDCLKx, EMU, TDO. 2See Output Drive Currents for typical drive current capabilities. 3Applies to input pins without internal pull-ups: BOOT_CFGx, CLK_CFGx, CLKIN, RESET, TCK. 4Applies to input pins with internal pull-ups: ACK, RPBA, TMS, TDI, TRST. 5Applies to input pins with internal pull-downs: IDx. 6Applies to input pins with internal pull-ups disabled: ACK, RPBA. 7Applies to three-statable pins without internal pull-ups: FLAGx, SDCLKx, TDO. 8Applies to three-statable pins with internal pull-ups: ADDRx, DATAx, RD, WR, MSx, BRx, DAI_Px, DPI_Px, SDRAS, SDCAS, SDWE, SDCKE, SDA10, EMU. 9Applies to three-statable pins with internal pull-ups disabled: ADDRx, DATAx, RD, WR, MSx, BRx, DAI_Px, DPI_Px, SDRAS, SDCAS, SDWE, SDCKE, SDA10 10See the Engineer-to-Engineer Note “Estimating Power Dissipation for ADSP-21368 SHARC Processors” (EE-299) for further information. 11Characterized, but not tested. 12Applies to all signal pins. ESD CAUTION MAXIMUM POWER DISSIPATION See the Engineer-to-Engineer Note “Estimating Power Dissipa- ESD (electrostatic discharge) sensitive device. tion for ADSP-21368 SHARC Processors” (EE-299) for detailed Charged devices and circuit boards can discharge thermal and power information regarding maximum power dis- without detection. Although this product features sipation. For information on package thermal specifications, see patented or proprietary protection circuitry, damage Thermal Characteristics. may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality. Rev. H | Page 17 of 60 | March 2019

ADSP-21369 ABSOLUTE MAXIMUM RATINGS Voltage Controlled Oscillator Stresses at or above those listed in Table9 may cause permanent In application designs, the PLL multiplier value should be damage to the product. This is a stress rating only; functional selected in such a way that the VCO frequency never exceeds operation of the product at these or any other conditions above fVCO specified in Table12. those indicated in the operational section of this specification is • The product of CLKIN and PLLM must never exceed 1/2 of not implied. Operation beyond the maximum operating condi- f (max) in Table12 if the input divider is not enabled VCO tions for extended periods may affect product reliability. (INDIV = 0). • The product of CLKIN and PLLM must never exceed f Table 9. Absolute Maximum Ratings VCO (max) in Table12 if the input divider is enabled Parameter Rating (INDIV = 1). Internal (Core) Supply Voltage (V ) –0.3 V to +1.5 V The VCO frequency is calculated as follows: DDINT Analog (PLL) Supply Voltage (A ) –0.3 V to +1.5 V f = 2 PLLM f VDD VCO INPUT External (I/O) Supply Voltage (V ) –0.3 V to +4.6 V f = (2 PLLM f ) (2 PLLD) DDEXT CCLK INPUT Input Voltage –0.5 V to +3.8 V where: Output Voltage Swing –0.5 V to VDDEXT + 0.5 V fVCO = VCO output Load Capacitance 200 pF PLLM = Multiplier value programmed in the PMCTL register. Storage Temperature Range –65C to +150C During reset, the PLLM value is derived from the ratio selected Junction Temperature Under Bias 125C using the CLK_CFG pins in hardware. PLLD = Divider value 1, 2, 4, or 8 based on the PLLD value pro- TIMING SPECIFICATIONS grammed on the PMCTL register. During reset this value is 1. Use the exact timing information given. Do not attempt to f = Input frequency to the PLL. INPUT derive parameters from the addition or subtraction of others. f = CLKIN when the input divider is disabled or While addition or subtraction would yield meaningful results INPUT for an individual device, the values given in this data sheet fINPUT = CLKIN 2 when the input divider is enabled reflect statistical variations and worst cases. Consequently, it is Note the definitions of the clock periods that are a function of not meaningful to add parameters to derive longer times. See CLKIN and the appropriate ratio control shown in and Figure40 under Test Conditions for voltage reference levels. Table10. All of the timing specifications for the ADSP-2136x Switching Characteristics specify how the processor changes its peripherals are defined in relation to t . See the peripheral spe- PCLK signals. Circuitry external to the processor must be designed for cific timing section for timing information for each peripheral. compatibility with these signal characteristics. Switching char- acteristics describe what the processor will do in a given Table 10. Clock Periods circumstance. Use switching characteristics to ensure that any Timing timing requirement of a device connected to the processor (such Requirements Description as memory) is satisfied. t CLKIN Clock Period Timing Requirements apply to signals that are controlled by cir- CK t Processor Core Clock Period cuitry external to the processor, such as the data input for a read CCLK operation. Timing requirements guarantee that the processor tPCLK Peripheral Clock Period = 2 × tCCLK operates correctly with other devices. Figure4 shows core to CLKIN relationships with external oscil- Core Clock Requirements lator or crystal. The shaded divider/multiplier blocks denote The processor’s internal clock (a multiple of CLKIN) provides where clock ratios can be set through hardware or software the clock signal for timing internal memory, processor core, and using the power management control register (PMCTL). For serial ports. During reset, program the ratio between the proces- more information, see the processor hardware reference. sor’s internal clock frequency and external (CLKIN) clock frequency with the CLK_CFG1–0 pins. The processor’s internal clock switches at higher frequencies than the system input clock (CLKIN). To generate the internal clock, the processor uses an internal phase-locked loop (PLL, see Figure4). This PLL-based clocking minimizes the skew between the system clock (CLKIN) signal and the processor’s internal clock. Rev. H | Page 18 of 60 | March 2019

ADSP-21369 PMCTL (SDCKR) PMCTL PLL (PLLBP) XTAL BCULFKIN DCIVLIKDIENR fINPUT FLILOTOEPR VCO fVCO DPIVMPILCDLTELR fCCLK BYPASSMUX CCLK DSIDVRIDAEMR YPASSUXM SDCLK (2xPLLD) B P(IMNDCITVL) MULPTLIPLLIER (PPMLLCBTPL) DBIVYID2E PCLK PCLK CLK_CFGx/PMCTL(2xPLLM) CCLK CLKOUT(TESTONLY) X U DELAYOF M BUF 4096CLKIN N CYCLES IP Figure 4. Core Clock and System Clock Relationship to CLKIN Rev. H | Page 19 of 60 | March 2019

ADSP-21369 Power-Up Sequencing The timing requirements for processor start-up are given in driven low before power up is complete. This leakage current Table11. Note that during power-up, a leakage current of results from the weak internal pull-up resistor on this pin being approximately 200μA may be observed on the RESET pin if it is enabled during power-up. Table 11. Power-Up Sequencing Timing Requirements (Processor Start-up) Parameter Min Max Unit Timing Requirements t RESET Low Before V /V On 0 ns RSTVDD DDINT DDEXT t V On Before V –50 +200 ms IVDDEVDD DDINT DDEXT t 1 CLKIN Valid After V /V Valid 0 200 ms CLKVDD DDINT DDEXT t CLKIN Valid Before RESET Deasserted 102 μs CLKRST t PLL Control Setup Before RESET Deasserted 20 μs PLLRST Switching Characteristic t Core Reset Deasserted After RESET Deasserted 4096t + 2 t 3, 4 CORERST CK CCLK 1Valid V /V assumes that the supplies are fully ramped to their 1.2 V rails and 3.3 V rails. Voltage ramp rates can vary from microseconds to hundreds of milliseconds DDINT DDEXT depending on the design of the power supply subsystem. 2Assumes a stable CLKIN signal, after meeting worst-case start-up timing of crystal oscillators. Refer to your crystal oscillator manufacturer’s data sheet for start-up time. Assume a 25 ms maximum oscillator start-up time if using the XTAL pin and internal oscillator circuit in conjunction with an external crystal. 3Applies after the power-up sequence is complete. Subsequent resets require RESET to be held low a minimum of four CLKIN cycles in order to properly initialize and propagate default states at all I/O pins. 4The 4096 cycle count depends on t specification in Table13. If setup time is not met, 1 additional CLKIN cycle may be added to the core reset time, resulting in 4097 cycles srst maximum. t RSTVDD RESET VDDINT t IVDDEVDD VDDEXT t CLKVDD CLKIN t CLKRST CLK_CFG1–0 t t PLLRST CORERST RESETOUT Figure 5. Power-Up Sequencing Rev. H | Page 20 of 60 | March 2019

ADSP-21369 Clock Input Table 12. Clock Input 400 MHz1 366 MHz2 350 MHz3 333 MHz4 266 MHz5 Parameter Min Max Min Max Min Max Min Max Min Max Unit Timing Requirements t CLKIN Period 156 100 16.396 100 17.146 100 186 100 22.56 100 ns CK t CLKIN Width Low 7.51 45 8.11 45 8.51 45 91 45 11.251 45 ns CKL t CLKIN Width High 7.51 45 8.11 45 8.51 45 91 45 11.251 45 ns CKH t CLKIN Rise/Fall (0.4 V to 2.0 V) 3 3 3 3 3 ns CKRF t 7 CCLK Period 2.56 10 2.736 10 2.856 10 3.06 10 3.756 10 ns CCLK f 8 VCO Frequency 100 800 100 800 100 800 100 800 100 600 MHz VCO t 9, 10 CLKIN Jitter Tolerance –250 +250 –250 +250 –250 +250 –250 +250 –250 +250 ps CKJ 1Applies to all 400 MHz models. See Ordering Guide. 2Applies to all 366 MHz models. See Ordering Guide. 3Applies to all 350 MHz models. See Ordering Guide. 4Applies to all 333 MHz models. See Ordering Guide. 5Applies to all 266 MHz models. See Ordering Guide. 6Applies only for CLK_CFG1–0 = 00 and default values for PLL control bits in PMCTL. 7Any changes to PLL control bits in the PMCTL register must meet core clock timing specification t . CCLK 8See Figure4 for VCO diagram. 9Actual input jitter should be combined with ac specifications for accurate timing analysis. 10Jitter specification is maximum peak-to-peak time interval error (TIE) jitter. t t CK CKJ CLKIN t t CKH CKL Figure 6. Clock Input Rev. H | Page 21 of 60 | March 2019

ADSP-21369 Clock Signals The processors can use an external clock or a crystal. See the CLKIN pin description in Table8. Programs can configure the processor to use its internal clock generator by connecting the necessary components to CLKIN and XTAL. Figure7 shows the component connections used for a crystal operating in funda- mental mode. Note that the clock rate is achieved using a 25 MHz crystal and a PLL multiplier ratio 16:1 (CCLK:CLKIN achieves a clock speed of 400 MHz). To achieve the full core clock rate, programs need to configure the multiplier bits in the PMCTL register. ADSP-21369 CLKIN R1 XTAL 1MV* R2 47V* C1 C2 22pF Y1 22pF 25.00MHz R2SHOULDBECHOSENTOLIMITCRYSTAL DRIVEPOWER.REFERTOCRYSTAL MANUFACTURER’SSPECIFICATIONS Figure 7. 400 MHz Operation (Fundamental Mode Crystal) Rev. H | Page 22 of 60 | March 2019

ADSP-21369 Reset Table 13. Reset Parameter Min Max Unit Timing Requirements t 1 RESET Pulse Width Low 4t ns WRST CK t RESET Setup Before CLKIN Low 8 ns SRST 1Applies after the power-up sequence is complete. At power-up, the processor’s internal phase-locked loop requires no more than100s while RESET is low, assuming stable V and CLKIN (not including start-up time of external clock oscillator). DD CLKIN t t WRST SRST RESET Figure 8. Reset Interrupts The following timing specification applies to the FLAG0, FLAG1, and FLAG2 pins when they are configured as IRQ0, IRQ1, and IRQ2 interrupts. Table 14. Interrupts Parameter Min Max Unit Timing Requirement t IRQx Pulse Width 2 × t +2 ns IPW PCLK INTERRUPT INPUTS t IPW Figure 9. Interrupts Rev. H | Page 23 of 60 | March 2019

ADSP-21369 Core Timer The following timing specification applies to FLAG3 when it is configured as the core timer (TMREXP). Table 15. Core Timer Parameter Min Max Unit Switching Characteristic t TMREXP Pulse Width 4 × t – 1 ns WCTIM PCLK t WCTIM FLAG3 (TMREXP) Figure 10. Core Timer Timer PWM_OUT Cycle Timing The following timing specification applies to Timer0, Timer1, and Timer2 in PWM_OUT (pulse-width modulation) mode. Timer signals are routed to the DPI_P14–1 pins through the DPI SRU. Therefore, the timing specifications provided below are valid at the DPI_P14–1 pins. Table 16. Timer PWM_OUT Timing Parameter Min Max Unit Switching Characteristic t Timer Pulse Width Output 2 × t – 1.2 2 × (231 – 1) × t ns PWMO PCLK PCLK t PWMO PWM OUTPUTS Figure 11. Timer PWM_OUT Timing Rev. H | Page 24 of 60 | March 2019

ADSP-21369 Timer WDTH_CAP Timing The following specification applies to Timer0, Timer1, and Timer2 in WDTH_CAP (pulse width count and capture) mode. Timer signals are routed to the DPI_P14–1 pins through the DPI SRU. Therefore, the specification provided in Table17 is valid at the DPI_P14–1 pins. Table 17. Timer Width Capture Timing Parameter Min Max Unit Switching Characteristic t Timer Pulse Width 2 × t 2 × (231 – 1) × t ns PWI PCLK PCLK t PWI TIMER CAPTURE INPUTS Figure 12. Timer Width Capture Timing Pin to Pin Direct Routing (DAI and DPI) For direct pin connections only (for example, DAI_PB01_I to DAI_PB02_O). Table 18. DAI/DPI Pin to Pin Routing Parameter Min Max Unit Timing Requirement t Delay DAI/DPI Pin Input Valid to DAI/DPI Output Valid 1.5 12 ns DPIO DAI_Pn DPI_Pn t DPIO DAI_Pm DPI_Pm Figure 13. DAI/DPI Pin to Pin Direct Routing Rev. H | Page 25 of 60 | March 2019

ADSP-21369 Precision Clock Generator (Direct Pin Routing) inputs and outputs are not directly routed to/from DAI pins (via pin buffers) there is no timing data available. All timing param- This timing is only valid when the SRU is configured such that eters and switching characteristics apply to external DAI pins the precision clock generator (PCG) takes its inputs directly (DAI_P01–20). from the DAI pins (via pin buffers) and sends its outputs directly to the DAI pins. For the other cases, where the PCG’s Table 19. Precision Clock Generator (Direct Pin Routing) Parameter Min Max Unit Timing Requirements t Input Clock Period t × 4 ns PCGIP PCLK t PCG Trigger Setup Before Falling 4.5 ns STRIG Edge of PCG Input Clock t PCG Trigger Hold After Falling 3 ns HTRIG Edge of PCG Input Clock Switching Characteristics t PCG Output Clock and Frame Sync Active Edge 2.5 10 ns DPCGIO Delay After PCG Input Clock t PCG Output Clock Delay After PCG Trigger 2.5 + (2.5 × t ) 10 + (2.5 × t ) ns DTRIGCLK PCGIP PCGIP t PCG Frame Sync Delay After PCG Trigger 2.5 + ((2.5 + D – PH) × t ) 10 + ((2.5 + D – PH) × t ) ns DTRIGFS PCGIP PCGIP t 1 Output Clock Period 2 × t – 1 ns PCGOW PCGIP D = FSxDIV, and PH = FSxPHASE. For more information, see the ADSP-2137x SHARC Processor Hardware Reference, “Precision Clock Gener- ators” chapter. 1In normal mode. t t STRIG HTRIG DAI_Pn DPI_Pn PCG_TRIGx_I DAI_Pm DPI_Pm PCG_EXTx_I (CLKIN) t t DPCGIO PCGIP DAI_Py DPI_Py PCG_CLKx_O tDTRIGCLK tDPCGIO tPCGOW DAI_Pz DPI_Pz PCG_FSx_O t DTRIGFS Figure 14. Precision Clock Generator (Direct Pin Routing) Rev. H | Page 26 of 60 | March 2019

ADSP-21369 Flags The timing specifications provided below apply to the FLAG3–0 and DPI_P14–1 pins, and the serial peripheral interface (SPI). See Table8 for more information on flag use. Table 20. Flags Parameter Min Max Unit Timing Requirement t FLAG3–0 IN Pulse Width 2 × t + 3 ns FIPW PCLK Switching Characteristic t FLAG3–0 OUT Pulse Width 2 × t – 1.5 ns FOPW PCLK FLAG INPUTS t FIPW FLAG OUTPUTS t FOPW Figure 15. Flags Rev. H | Page 27 of 60 | March 2019

ADSP-21369 SDRAM Interface Timing (166 MHz SDCLK) The 166 MHz access speed is for a single processor. When mul- tiple ADSP-21369 processors are connected in a shared memory system, the access speed is 100 MHz. Table 21. SDRAM Interface Timing1 All Other Speed 366 MHz 350 MHz Grades Parameter Min Max Min Max Min Max Unit Timing Requirements t DATA Setup Before SDCLK 500 500 500 ps SSDAT t DATA Hold After SDCLK 1.23 1.23 1.23 ns HSDAT Switching Characteristics t SDCLK Period 6.83 7.14 6.0 ns SDCLK t SDCLK Width High 3 3 2.6 ns SDCLKH t SDCLK Width Low 3 3 2.6 ns SDCLKL t Command, ADDR, Data Delay After SDCLK2 4.8 4.8 4.8 ns DCAD t Command, ADDR, Data Hold After SDCLK2 1.2 1.2 1.2 ns HCAD t Data Disable After SDCLK 5.3 5.3 5.3 ns DSDAT t Data Enable After SDCLK 1.3 1.3 1.3 ns ENSDAT 1The processor needs to be programmed in t = 2.5 t mode when operated at 350 MHz, 366 MHz, and 400 MHz. SDCLK CCLK 2Command pins include: SDCAS, SDRAS, SDWE, MSx, SDA10, SDCKE. t t SDCLKH SDCLK SDCLK tSSDAT tHSDAT tSDCLKL DATA (IN) t DCAD t t DSDAT ENSDAT t HCAD DATA (OUT) t t DCAD HCAD COMMAND/ADDR (OUT) Figure 16. SDRAM Interface Timing Rev. H | Page 28 of 60 | March 2019

ADSP-21369 SDRAM Interface Enable/Disable Timing (166 MHz SDCLK) Table 22. SDRAM Interface Enable/Disable Timing1 Parameter Min Max Unit Switching Characteristics t Command Disable After CLKIN Rise 2 × t + 3 ns DSDC PCLK t Command Enable After CLKIN Rise 4.0 ns ENSDC t SDCLK Disable After CLKIN Rise 8.5 ns DSDCC t SDCLK Enable After CLKIN Rise 3.8 ns ENSDCC t Address Disable After CLKIN Rise 9.2 ns DSDCA t Address Enable After CLKIN Rise 2 × t – 4 4 × t ns ENSDCA PCLK PCLK 1For f = 400 MHz (SDCLK ratio = 1:2.5). CCLK CLKIN t DSDC t DSDCC COMMAND tDSDCA SDCLK ADDR t ENSDC t ENSDCA t ENSDCC COMMAND SDCLK ADDR Figure 17. SDRAM Interface Enable/Disable Timing Rev. H | Page 29 of 60 | March 2019

ADSP-21369 Memory Read Use these specifications for asynchronous interfacing to memo- ries. These specifications apply when the processors are the bus master accessing external memory space in asynchronous access mode. Note that timing for ACK, DATA, RD, WR, and strobe timing parameters only apply to asynchronous access mode. Table 23. Memory Read Parameter Min Max Unit Timing Requirements t Address, Selects Delay to Data Valid1, 2 W + t – 5.12 ns DAD SDCLK t RD Low to Data Valid2 W – 3.2 ns DRLD t Data Setup to RD High 2.5 ns SDS t Data Hold from RD High3, 4 0 ns HDRH t ACK Delay from Address, Selects1, 5 t – 9.5 + W ns DAAK SDCLK t ACK Delay from RD Low5 W – 7.0 ns DSAK Switching Characteristics t Address Selects Hold After RD High RH + 0.20 ns DRHA t Address Selects to RD Low1 t – 3.3 ns DARL SDCLK t RD Pulse Width W – 1.4 ns RW t RD High to WR, RD Low HI + t – 0.8 ns RWR SDCLK W = (number of wait states specified in AMICTLx register) × t SDCLK RHC = (number of Read Hold Cycles specified in AMICTLx register) × t SDCLK Where PREDIS = 0 HI = RHC (if IC = 0): Read to Read from same bank HI = RHC+ t (if IC > 0): Read to Read from same bank SDCLK HI = RHC + IC: Read to Read from different bank HI = RHC + Max (IC, (4 × t )): Read to Write from same or different bank SDCLK Where PREDIS = 1 HI = RHC + Max (IC, (4 × t )): Read to Write from same or different bank SDCLK HI = RHC + (3 × t ): Read to Read from same bank SDCLK HI = RHC + Max (IC, (3 × t )): Read to Read from different bank SDCLK IC = (number of idle cycles specified in AMICTLx register) × t SDCLK H = (number of hold cycles specified in AMICTLx register) × t SDCLK 1The falling edge of MSx is referenced. 2The maximum limit of timing requirement values for t and t parameters are applicable for the case where AMI_ACK is always high and when the ACK feature is not used. DAD DRLD 3Note that timing for ACK, DATA, RD, WR, and strobe timing parameters only apply to asynchronous access mode. 4Data hold: User must meet t or t in asynchronous access mode. See Test Conditions for the calculation of hold times given capacitive and dc loads. HDA HDRH 5ACK delay/setup: User must meet t , or t , for deassertion of ACK (low). For asynchronous assertion of ACK (high), user must meet t or t . DAAK DSAK DAAK DSAK Rev. H | Page 30 of 60 | March 2019