ICGOO在线商城 > 射频/IF 和 RFID > RF 其它 IC 和模块 > ADRF6518ACPZ-R7

- 型号: ADRF6518ACPZ-R7

- 制造商: Analog

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

ADRF6518ACPZ-R7产品简介:

ICGOO电子元器件商城为您提供ADRF6518ACPZ-R7由Analog设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 ADRF6518ACPZ-R7价格参考。AnalogADRF6518ACPZ-R7封装/规格:RF 其它 IC 和模块, RF IC Programmable Filter, VGA General Purpose 0Hz ~ 1.1GHz 32-LFCSP-WQ (5x5)。您可以下载ADRF6518ACPZ-R7参考资料、Datasheet数据手册功能说明书,资料中有ADRF6518ACPZ-R7 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | |

| 描述 | IC AMP VGA 300MHZ DUAL 32LFCSP |

| 产品分类 | |

| 品牌 | Analog Devices Inc |

| 数据手册 | |

| 产品图片 | |

| 产品型号 | ADRF6518ACPZ-R7 |

| PCN组件/产地 | |

| RF类型 | 通用 |

| rohs | 无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | - |

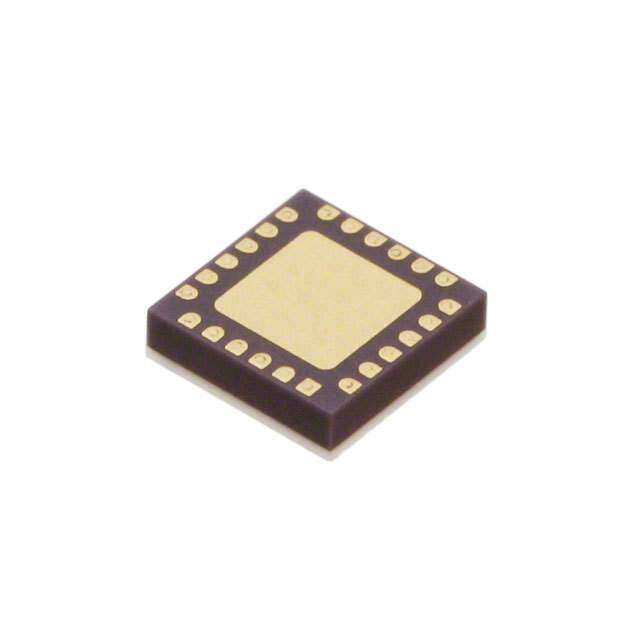

| 供应商器件封装 | 32-LFCSP-WQ(5x5) |

| 其它名称 | ADRF6518ACPZ-R7CT |

| 功能 | 可编程滤波器,VGA |

| 包装 | 剪切带 (CT) |

| 封装/外壳 | 32-WFQFN 裸露焊盘,CSP |

| 标准包装 | 1 |

| 辅助属性 | - |

| 频率 | 0Hz ~ 1.1GHz |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

1.1 GHz Variable Gain Amplifiers and Baseband Programmable Filters Data Sheet ADRF6518 FEATURES FUNCTIONAL BLOCK DIAGRAM Matched pair of programmable filters and triple VGAs ENBL INP1 INM1 VPS RAVG VGN1 OFS1 VPS Continuous gain control range: 72 dB Digital gain control: 30 dB ADRF6518 Filter bypass mode bandwidth ±1 dB gain flatness: 300 MHz VPSD OPP1 −3 dB small signal bandwidth: 650 MHz/1.1 GHz, VGA2 COMD OPM1 and VGA3 21 dB/12 dB, respectively LE COM 6-pole Butterworth filter: 1 MHz to 63 MHz CLK VGN3 in 1 MHz steps, 0.5 dB corner frequency SPI Peak detector DATA VOCM IMD3: >65 dBc for 1.5 V p-p composite output SDO/RST COM HD2, HD3: >65 dBc for 1.5 V p-p output VICM/AC OPM2 Differential input and output VPI OPP2 Flexible output and input common-mode ranges Optional dc output offset correction SPI programmable filter corners and gain steps Single 3.3 V supply operation with power-down feature COM INP2 INM2 VPS VPK VGN2 OFS2 VPS 11449-001 APPLICATIONS Figure 1 Point-to-point and point-to-multipoint radios Baseband IQ receivers Diversity receivers ADC drivers Instrumentation Medical GENERAL DESCRIPTION The ADRF6518 is a matched pair of fully differential low noise and A wideband peak detector is available to monitor the peak signal at low distortion programmable filters and variable gain amplifiers the filter inputs. The pair of VGAs that follow the filters each (VGAs). Each channel is capable of rejecting large out-of-band provides 24 dB of continuous gain control with fixed gain options interferers while reliably boosting the wanted signal, thus reducing of 12 dB, 15 dB, 18 dB, and 21 dB. The output buffers offer an the bandwidth and resolution requirements on the analog-to- additional option of 3 dB or 9 dB gain and provide a differential digital converters (ADCs). The excellent matching between output impedance of less than 10 Ω. They are capable of driving 1.5 channels and their high spurious-free dynamic range over all V p-p into 400 Ω loads at better than 65 dBc HD3. The output gain and bandwidth settings make the ADRF6518 ideal for common-mode voltage defaults to VPS/2 and can be adjusted quadrature-based (IQ) communication systems with dense down to 900 mV via the VOCM pin. Independent, built-in dc constellations, multiple carriers, and nearby interferers. The offset correction loops for each channel can be disabled via the SPI various amplifier gains, filter corners, and other features are all if fully dc-coupled operation is desired. The high-pass corner programmable via a serial port interface (SPI) port. frequency is determined by external capacitors on the OFS1 and OFS2 pins and the postfilter VGA gain. The first VGA that precedes the filters offers 24 dB of continuous gain control with fixed gain options of 9 dB, 12 dB, and 15 dB, and The ADRF6518 operates from a 3.15 V to 3.45 V supply and sets a differential input impedance of 400 Ω. The filters provide consumes a maximum supply current of 400 mA. When fully a six-pole Butterworth response with 0.5 dB corner frequencies disabled, it consumes <1 mA. The ADRF6518 is fabricated in an from 1 MHz to 63 MHz in 1 MHz steps. For operation beyond advanced silicon-germanium BiCMOS process and is available in a 63 MHz, the filter can be disabled and completely bypassed, 32-lead, exposed pad LFCSP. Performance is specified over the thereby extending the −3 dB bandwidth (BW) up to 1.1 GHz. −40°C to +85°C temperature range. Rev. A Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Tel: 781.329.4700 ©2013–2017 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. Technical Support www.analog.com

ADRF6518 Data Sheet TABLE OF CONTENTS Features .............................................................................................. 1 Key Parameters for Quadrature-Based Receivers .................. 25 Applications ....................................................................................... 1 Applications Information .............................................................. 26 Functional Block Diagram .............................................................. 1 Basic Connections ...................................................................... 26 General Description ......................................................................... 1 Supply Decoupling ..................................................................... 26 Revision History ............................................................................... 2 Input Signal Path ........................................................................ 26 Specifications ..................................................................................... 3 Output Signal Path ..................................................................... 26 Timing Diagrams .......................................................................... 5 DC Offset Compensation Loop Enabled ................................ 26 Absolute Maximum Ratings ............................................................ 6 Common-Mode Bypassing ....................................................... 27 ESD Caution .................................................................................. 6 Serial Port Connections ............................................................. 27 Pin Configuration and Function Descriptions ............................. 7 Enable/Disable Function ........................................................... 27 Typical Performance Characteristics ............................................. 8 Gain Pin Decoupling ................................................................. 27 Filter Mode .................................................................................... 8 Peak Detector Connections ...................................................... 27 Bypass Mode ............................................................................... 16 Error Vector Magnitude (EVM) Performance ........................... 27 Mixed Power and Filter Modes................................................. 18 EVM Test Setup .......................................................................... 27 Characterization ............................................................................. 19 EVM Measurement .................................................................... 27 Noise Figure Calculation ........................................................... 19 EVM System Measurement ....................................................... 29 Register Map and Codes ................................................................ 20 Effect of Filter BW on EVM ...................................................... 31 Theory of Operation ...................................................................... 21 Pull-Down Resistors for Disable Function ............................. 31 Input VGAs ................................................................................. 21 Instability at High Gain in Filter Bypass Mode ...................... 31 Peak Detector .............................................................................. 22 Instability at Low Filter Corners and Low Power Mode ....... 32 Programmable Filters ................................................................. 22 Peak Detector Bandwidth And Slew Rate ............................... 32 Variable Gain Amplifiers (VGAs) ............................................ 23 Linear Operation of the ADRF6518 ........................................ 32 Output Buffers/ADC Drivers ................................................... 23 Evaluation Board ............................................................................ 33 DC Offset Compensation Loop ................................................ 23 Evaluation Board Control Software ......................................... 33 Programming the ADRF6518 ................................................... 23 Schematics and Artwork ........................................................... 34 Noise Characteristics ................................................................. 24 Outline Dimensions ....................................................................... 39 Distortion Characteristics ......................................................... 24 Ordering Guide .......................................................................... 39 Maximizing the Dynamic Range .............................................. 25 REVISION HISTORY 12/2017—Rev. 0 to Rev. A Changes to Figure 56...................................................................... 16 Changed 1100 MHz to 1.1 GHz .................................. Throughout Changes to Figure 69 and Figure 69 Caption ............................. 22 Change to Product Title ................................................................... 1 Changes to Figure 72...................................................................... 26 Changes to Figure 1 .......................................................................... 1 Changes to Figure 73 and Figure 74 ............................................ 28 Changes to Table 1 ............................................................................ 3 Added Figure 86 and Figure 87; Renumbered Sequentially .......... 32 Changes to Figure 3 .......................................................................... 5 Added Instability at Low Filter Corners and Low Power Mode Changes to Figure 12 ........................................................................ 9 Section, and Peak Detector Bandwidth and Slew Rate Section ...... 32 Changes to Figure 20 ...................................................................... 10 Changes to Figure 88 ....................................................................... 32 Reorganized Typical Performance Characteristics Section; Changes to Figure 89...................................................................... 33 Renumbered Sequentially .............................................................. 10 Changes to Figure 49 Caption, Figure 51 Caption, and Figure 52 6/2013—Revision 0: Initial Version Caption ............................................................................................. 15 Rev. A | Page 2 of 39

Data Sheet ADRF6518 SPECIFICATIONS VPS, VPI, VPSD = 3.3 V, T = 25°C, Z = 400 Ω, power mode bit (B9) = 0 (low power mode), digital gain code bits (B8 to B2) = 0000001, and A LOAD dc offset disable bit (B1) = 0 (enabled), unless otherwise noted. Table 1. Parameter Test Conditions/Comments Min Typ Max Unit FREQUENCY RESPONSE, FILTER BYPASS MODE ±1 dB Gain Flatness Bandwidth 300 MHz −3 dB Small Signal Bandwidth VGA2 and VGA3 21 dB digital gain setting 650 MHz VGA2 and VGA3 12 dB digital gain setting 1100 MHz FREQUENCY RESPONSE Low-Pass Corner Frequency, f Six-pole Butterworth filter, 0.5 dB bandwidth 1 63 MHz C Step Size 1 MHz Corner Frequency Absolute Accuracy Over operating temperature range ±8 % f C Corner Frequency Matching Channel A and Channel B at same gain and ±0.5 % f C bandwidth settings Pass-Band Ripple 0.5 dB p-p Gain Matching Channel A and Channel B at same gain and ±0.1 dB bandwidth settings Group Delay Variation From midband to peak Corner Frequency = 1 MHz 135 ns Corner Frequency = 30 MHz 11 ns Group Delay Matching Channel A and Channel B at same gain Corner Frequency = 1 MHz 5 ns Corner Frequency = 30 MHz 0.2 ns Stop-Band Rejection Relative to Pass Band 2 × f 30 dB C 5 × f 75 dB C INPUT STAGE INP1, INM1, INP2, INM2, VICM/AC Maximum Input Swing At minimum gain, VGN1 = 0 V 5.0 V p-p Differential Input Impedance 400 Ω Input Common-Mode Range, DC-Coupled 1.5 V p-p input voltage, HD3 > 65 dBc (VPI = 3.3 V), 1.35 1.95 V Mode VICM/AC floating or logic high 1.5 V p-p input voltage, HD3 > 65 dBc (VPI = 5.0 V), 1.35 3.1 V VICM/AC floating or logic high Input Common-Mode, AC-Coupled Mode VPI = 3.3 V to 5.0 V, VICM/AC = 0 V VPS/2 V VICM/AC Input Impedance 7.75 kΩ PEAK DETECTOR VPK, RAVG, SDO/RST Output Scaling Relative to differential peak voltage at filter 1 V/V peak input Reset Threshold Logic high duration > 25 ns >2.0 V GAIN CONTROL VGN1, VGN2, VGN3 Gain Range Maximum digital gains −6 +66 dB Minimum digital gains −36 +36 dB Voltage Attenuation Range Each attenuator; V from 0 V to 1 V −24 0 dB GAIN Gain Slope 30 mV/dB Gain Error V from 300 mV to 800 mV 0.2 dB GAIN Rev. A | Page 3 of 39

ADRF6518 Data Sheet Parameter Test Conditions/Comments Min Typ Max Unit OUTPUT STAGE OPP1, OPM1, OPP2, OPM2, VOCM Maximum Output Swing At maximum gain, R = 400 Ω 3 V p-p LOAD HD2 > 65 dBc, HD3 > 65 dBc, R = 400 Ω 1.5 V p-p LOAD Differential Output Impedance <10 Ω Output DC Offset Inputs shorted, offset loop enabled <20 mV Output Common-Mode Range 1.5 V p-p output voltage 0.9 VPS − 1.2 V VOCM left floating VPS/2 V VOCM Input Impedance 23 kΩ NOISE/DISTORTION Corner Frequency = 63 MHz Output Noise Density Minimum gain at fc/2 −104.6 dBV/Hz Maximum gain at fc/2 −104.3 dBV/Hz Second Harmonic. HD2 16 MHz fundamental, 1.5 V p-p Output Level Gain = 6 dB 65 dBc Gain = 54 dB 65 dBc Third Harmonic, HD3 16 MHz fundamental, 1.5 V p-p Output Level Gain = 6 dB 82 dBc Gain = 54 dB 81 dBc IMD3 30 MHz and 31 MHz tones, 1.5 V p-p output level Gain = 0 dB 60 dBc Gain = 30 dB 80 dBc Gain = 60 dB 80 dBc DIGITAL LOGIC LE, CLK, DATA, SDO Input High Voltage, V >2 V HIGH Input Low Voltage, V <0.8 V LOW Input Current, I /I <1 µA HIGH LOW Input Capacitance, C 2 pF IN SPI TIMING LE, CLK, DATA, SDO f 1/t 20 MHz CLK CLK t DATA hold time 5 ns DH t DATA setup time 5 ns DS t LE hold time 5 ns LH t LE setup time 5 ns LS t CLK high pulse width 5 ns PW t CLK to SDO delay 5 ns D POWER AND ENABLE VPS, VPSD, COM, COMD, ENBL Supply Voltage Range 3.15 3.3 3.45 V Total Supply Current ENBL = 3.3 V Maximum BW setting, high power filter 400 mA Minimum BW setting, low power filter 360 mA Filter bypassed, high power mode 260 mA Filter bypassed, low power mode 230 mA Disable Current ENBL = 0 V, with pull-down resistors on output 1 mA Disable Threshold 1.6 V Enable Response Time Delay following ENBL low-to-high transition 20 µs Disable Response Time Delay following ENBL high-to-low transition 300 ns Rev. A | Page 4 of 39

Data Sheet ADRF6518 TIMING DIAGRAMS tCLK tPW CLK tLS tLH LE tDS tDH DATA WRITE BIT LSB LSB + 1 LSB + 2 LSB + 3 MSB – 3 MSB – 2 MSB – 1 MMSSBB - 2 N1.O TTTHHEEES FFIIRRSSTT BDIATT SAH BOIUT LDDE TBEER AM LINOEGSI CW 1H. ETTHHEE 1R6 -TBHITE WPAORRTD I SIS W TRHIETNIN RGE TGOIS OTERR REEDA IDNITNOG TFHREO DMA TTHAE P IINNT OERNN CAOLN 1S6E-BCIUTT RIVEEG IRSITSEINRG. FEODRG EAS W ORFIT TEH OE PCELROACTKIO.N, 11449-002 Figure 2. Write Mode Timing Diagram tD tCLK tPW CLK tLH tLS LE tDS tDH DATA READ BIT DC DC DC DC DC DC DDCC DC SDO LSB LSB + 1 LSB + 2 LSB + 3 MSB – 3 MSB – 2 MSB – 1 MSB NOTES 1. TCBHLITEO S CFHKIROESUDTL ODBU IBTT E DO AENT L ETOHRGEMI CICN O0E NSOS NWE HTCHEUETTH IDVEAERT R ATIHS LEIINN PGEA .ERtDDT G SISEE SCW OORNFITD TISNH GAE FTCTOLEO ROC RTK HREE ANDEIXNTG F FARLOLIMN GTH EED IGNET EORFN TAHLE 1 C6-LBOITC KR,E DGAISTTAE ORN. FTOHER SAD ROE ALIDN EO PBEERCAOTMIOENS ,V TAHLEID F IARNSDT IS 11449-003 Figure 3. Read Mode Timing Diagram Rev. A | Page 5 of 39

ADRF6518 Data Sheet ABSOLUTE MAXIMUM RATINGS Table 2. Stresses at or above those listed under Absolute Maximum Parameter Rating Ratings may cause permanent damage to the product. This is a Supply Voltages, VPS, VPSD 3.45 V stress rating only; functional operation of the product at these VPI 5.25 V or any other conditions above those indicated in the operational ENBL, LE, CLK, DATA, SDO VPSD + 0.5 V section of this specification is not implied. Operation beyond INP1, INM1, INP2, INM2, VICM VPS + 0.5 V the maximum operating conditions for extended periods may OPP1, OPM1, OPP2, OPM2, VOCM VPS + 0.5 V affect product reliability. OFS1, OFS2, VPK, RAVG VPS + 0.5 V ESD CAUTION VGN1, VGN2, VGN3 VPS + 0.5 V Internal Power Dissipation 1.25 W θ (Exposed Pad Soldered to Board) 37.4°C/W JA Maximum Junction Temperature 150°C Operating Temperature Range −40°C to +85°C Storage Temperature Range −65°C to +150°C Lead Temperature (Soldering 60 sec) 300°C Rev. A | Page 6 of 39

Data Sheet ADRF6518 PIN CONFIGURATION AND FUNCTION DESCRIPTIONS ENBLNP1INM1IVPSRAVGVGN1OFS1VPS 21098765 33322222 VPSD 1 24 OPP1 COMD 2 23 OPM1 LE 3 22 COM ADRF6518 CLK 4 21 VGN3 DATA 5 TOP VIEW 20 VOCM (Not to Scale) SDO/RST 6 19 COM VICM/AC 7 18 OPM2 VPI 8 17 OPP2 90123456 1111111 M22SK22S CONPIMNIVPVPGVNOFSVP N1.O CATO ELNSONWE CIMTP TEHDEA ENXCPEO GSREODU PNADD PDALED .TO 11449-004 Figure 4. Pin Configuration Table 3. Pin Function Descriptions Pin No. Mnemonic Description 1 VPSD Digital Positive Supply Voltage: 3.15 V to 3.45 V. 2 COMD Digital Common. Connect this pin to an external circuit common using the lowest possible impedance. 3 LE Latch Enable. SPI programming pin. TTL levels: V < 0.8 V, V > 2 V. LOW HIGH 4 CLK SPI Port Clock. TTL levels: V < 0.8 V, V > 2 V. LOW HIGH 5 DATA SPI Data Input. TTL levels: V < 0.8 V, V > 2 V. LOW HIGH 6 SDO/RST SPI Data Output (SDO). TTL levels: V < 0.8 V, V > 2 V. LOW HIGH Peak Detector Reset (RST). A >25 ns high pulse is required on this pin to reset the detector. 7 VICM/AC Input Common-Mode Reference (VICM). VPI/2 reference output for optimal common-mode level to drive the differential inputs. If this pin is used as a common-mode reference for the common- mode output of the previous stage, only connect high impedance nodes to this pin. AC Coupling/Internal Bias Activation (AC). Pull this pin low for ac coupling of the inputs. 8 VPI Input Stage Supply Voltage: 3.15 V to 5.25 V. Connect VPI to VPS if the input common-mode range is narrow (1.35 V to 1.95 V). Connect VPI to 5 V if a common-mode input up to 3.1 V is desired. 9, 19, 22 COM Analog Common. Connect COM to an external circuit common using the lowest possible impedance. 10, 11, 30, 31 INP2, INM2, Differential Inputs, 400 Ω Differential Input Impedance. INM1, INP1 12, 16, 25, 29 VPS Analog Positive Supply Voltage: 3.15 V to 3.45 V. 13 VPK Peak Detector Output. Scaling of 1 V/V peak differential at filter inputs is performed, and the bigger peak of two channels is reported. 14, 21, 27 VGN2, VGN3, VGA1, VGA2, and VGA3 Analog Gain Control. 0 V to 1 V, 30 mV/dB gain scaling. VGN1 15, 26 OFS2, OFS1 Offset Correction Loop Compensation Capacitors. Connect capacitors to a circuit common. 17, 18, 23, 24 OPP2, OPM2, Differential Outputs. These outputs have a <10 Ω output impedance. Common-mode range is 0.9 OPM1, OPP1 V to VPS − 1.2 V; default is VPS/2. 20 VOCM Output Common-Mode Setpoint. VOCM defaults to VPS/2 if left open. 28 RAVG Peak Detector Time-Constant Resistor. Connect this pin to VPS. Leave this pin open for the longest hold time. The RAVG range is ∞ to 1 kΩ. 32 ENBL Chip Enable. Pull this pin high to enable the chip. EP Exposed Ground Pad. Connect the exposed pad to a low impedance ground pad. Rev. A | Page 7 of 39

ADRF6518 Data Sheet TYPICAL PERFORMANCE CHARACTERISTICS FILTER MODE VPS, VPI, VPSD = 3.3 V, T = 25°C, Z = 400 Ω, power mode bit (B9) = 0 (low power mode), digital gain code bits (B8 to B2) = 1111110, A LOAD dc offset disable bit (B1) = 0 (enabled), filter corner = 63 MHz, ac coupling mode, fundamental at 31 MHz, unless otherwise noted. For HD2/HD3 vs. gain plots: 1.5 V p-p output target level, and reference Figure 67 for analog gain distribution. 0 4 –5 3 +25°C, VPS = 3.15V, 3.3V, 3.45V –10 2 –40°C, VPS = 3.15V, 3.3V, 3.45V –40°C, VPS = 3.15V, 3.3V, 3.45V B) –15 d 1 B) R ( d O N ( –20 RR 0 AI E G N –25 AI –1 G +25°C, VPS = 3.15V, 3.3V, 3.45V –30 –2 +85°C, VPS = 3.15V, 3.3V, 3.45V –35 –3 +85°C, VPS = 3.15V, 3.3V, 3.45V –40 –4 0 0.1 0.2 0.3 0.4VGN0.15 (V)0.6 0.7 0.8 0.9 1.0 11449-005 0 100 200 300 400VGN510 0(mV6)00 700 800 900 1000 11449-008 Figure 5. In-Band Gain vs. VGN1 over Supply and Temperature Figure 8. Gain Error vs. VGN1 over Supply and Temperature 0 4 –5 3 +25°C, VPS = 3.15V, 3.3V, 3.45V –10 2 –40°C, VPS = 3.15V, 3.3V, 3.45V –40°C, VPS = 3.15V, 3.3V, 3.45V B) –15 d 1 B) R ( d O AIN ( –20 ERR 0 G N –25 AI –1 G +25°C, VPS = 3.15V, 3.3V, 3.45V –30 –2 +85°C, VPS = 3.15V, 3.3V, 3.45V –35 –3 +85°C, VPS = 3.15V, 3.3V, 3.45V –40 –4 0 0.1 0.2 0.3 0.4VGN0.25 (V)0.6 0.7 0.8 0.9 1.0 11449-006 0 100 200 300 400VGN520 0(mV6)00 700 800 900 1000 11449-009 Figure 6. In-Band Gain vs. VGN2 over Supply and Temperature Figure 9. Gain Error vs. VGN2 over Supply and Temperature 0 4 –5 3 +25°C, VPS = 3.15V, 3.3V, 3.45V –10 2 –40°C, VPS = 3.15V, 3.3V, 3.45V –40°C, VPS = 3.15V, 3.3V, 3.45V B) –15 d 1 B) R ( d O N ( –20 RR 0 AI E G N –25 AI –1 G +25°C, VPS = 3.15V, 3.3V, 3.45V –30 –2 +85°C, VPS = 3.15V, 3.3V, 3.45V –35 –3 +85°C, VPS = 3.15V, 3.3V, 3.45V –40 –4 0 0.1 0.2 0.3 0.4VGN0.35 (V)0.6 0.7 0.8 0.9 1.0 11449-007 0 100 200 300 400VGN530 0(mV6)00 700 800 900 1000 11449-010 Figure 7. In-Band Gain vs. VGN3 over Supply and Temperature Figure 10. Gain Error vs. VGN3 over Supply and Temperature Rev. A | Page 8 of 39

Data Sheet ADRF6518 60 15 50 10 DIGITAL GAIN = 0000001 40 5 30 DIGITAL GAIN = 111110 0 20 dB) 10 dBV) –5 N ( B ( GAI 0 P1d –10 –10 O –15 –20 –20 –30 –40 –25 –505 15 25 FRE3Q5UENCY4 (5MHz) 55 65 75 11449-011 –30–10 0 10 GAI2N0 (dB) 30 40 50 11449-014 Figure 11. Gain vs. Frequency over VGN1/VGN2/VGN3 Figure 14. OP1dB vs. Gain at a Fundamental of 16 MHz 0 –30 +85°C, VPS = 3.15V, 3.3V, 3.45V +25°C, VPS = 3.15V, 3.3V, 3.45V –5 –40°C, VPS = 3.15V, 3.3V, 3.45V DIGITAL GAIN = 0000001 –10 –35 DIGITAL GAIN = 0000000 –15 DIGITAL GAIN = 0000010 dB) –20 DIGITAL GAIN = 0000100 dB) N ( DIGITAL GAIN = 0000110 N ( –40 AI –25 DIGITAL GAIN = 0001110 AI G G DIGITAL GAIN = 0010110 –30 DIGITAL GAIN = 0011110 DIGITAL GAIN = 0111110 –45 –35 DIGITAL GAIN = 1111110 –40 –455 10 15 20 2F5REQ3U0ENC3Y5 (MH4z0) 45 50 55 60 11449-012 –503 13 23 33 FR4E3QUE5N3CY (M63Hz) 73 83 93 103 11449-015 Figure 12. Digital Gain vs. Frequency; VGN1/VGN2/VGN3 = 0 V Figure 15. Frequency Response over Supply and Temperature; VGN1/VGN2/VGN3 = 0 V, Filter Corners = 15 MHz, 30 MHz, and 60 MHz 0.3 40 35 0.2 30 dB) 0.1 25 CH ( B) 20 T d MA 0 N ( 15 S AI MI G 10 N GAI –0.1 5 0 –0.2 –5 –0.30/0/0 0.2/0/0 0.4/0/0 0.6/0/0 0.8/0/0 1/0/0VGN1/0.2/01/VG1/0.4/0N2/1/0.6/0VGN1/0.8/03 (V1/1/0) 1/1/0.2 1/1/0.4 1/1/0.6 1/1/0.8 1/1/1 11449-013 –100 10 20 30 40 50FR6E0QU7E0NC8Y0 (M90Hz1)00110120130140150 11449-016 Figure 13. Gain Mismatch Between Channels vs. VGN1/VGN2/VGN3 Voltage Figure 16. Gain vs. Frequency over BW Setting (Linear); VGN1/VGN2/VGN3 = 0 V Rev. A | Page 9 of 39

ADRF6518 Data Sheet 31 10 8 s) 6 30 H (n C 4 T A B) TM 2 d S N ( 29 MI 0 GAI ELAY –2 D 28 OUP –4 BBAANNDDWWIIDDTTHH==715MMHHzz R G –6 –8 271 11 21FREQU3E1NCY (MH41z) 51 61 11449-017 –102 4 6 8 1F0REQ12UEN1C4Y (M1H6z) 18 20 22 24 11449-119 Figure 17. Gain vs. Frequency over BW Setting (Linear); Scaled to Show Figure 20. IQ Group Delay Mismatch vs. Frequency Peaking (BW = 7 MHz and BW = 15 MHz) 40 5 35 4 30 s) 3 n 25 CH ( 2 T B) 20 MA 1 d S GAIN ( 1105 ELAY MI –10 D 5 UP –2 BANDWIDTH= 30MHz O BANDWIDTH=60MHz R 0 G –3 –5 –4 –101 FREQU10ENCY (MHz) 100 11449-117 –55 15 25FREQUE3N5CY (MHz)45 55 65 11449-120 Figure 18. Gain vs. Frequency over BW Setting (Log); Figure 21. IQ Group Delay Mismatch vs. Frequency VGN1 = 1 V, VGN2 = 0.7 V, VGN3 = 0.75 V (BW = 30 MHz and BW = 60 MHz) FREQUENCY (MHz) 0 0.2 0.4 0.6 0.8 1.0 1.2 100 0.50 BANDWIDTH = 7MHz 90 0.40 80 0.30 ROUP DELAY (ns) 45670000 BANDWIDTH = 15MHz MISMATCH (dB) –0000....10120000 BBAANNDDWWIIDDTTHH==163MMHHzz G 30 –0.20 BANDWIDTH = 30MHz 20 –0.30 BANDWIDTH = 60MHz 10 –0.40 02 FREQUENCY (MHz2)0 11449-118 –0.500 10 20 FREQU30ENCY (M4H0z) 50 60 11449-121 Figure 19. Group Delay vs. Frequency; VGN1/VGN2/VGN3 = 0 V Figure 22. IQ Amplitude Mismatch vs. Frequency; VGN1/VGN2/VGN3 = 0 V Rev. A | Page 10 of 39

Data Sheet ADRF6518 50 –95 15dB –96 12dB 45 9dB –97 Hz) –98 40 BV/ –99 GURE (dB) 3350 DENSITY (d–––111000012 FI E –103 NOISE 25 T NOIS––110045 20 TPU–106 63MHz U–107 32MHz O 16MHz 15 –108 8MHz –109 4MHz 2MHz 0 –110 0 100 200 300 400VGN510 0(mV6)00 700 800 900 1000 11449-022 0 100 200 300 400VGN510 0(mV6)00 700 800 900 1000 11449-025 Figure 23. Noise Figure vs. VGN1 over VGA1 Digital Gain; Noise Density Figure 26. Output Noise Density vs. VGN1 over Bandwidth Setting; Measured at Half of Filter Corner Digital Gain = 0000001, Noise Density Measured at Half of Filter Corner 55 –100 63MHz 50 3126MMHHzz –105 45 842MMMHHHzzz BV/Hz)–110 GAIN = 60dB dB) 40 Y (d–115 RE ( 35 NSIT–120 GU DE–125 SE FI 30 OISE –130 GAIN = 40dB NOI 25 UT N–135 P 20 T U–140 O GAIN = 20dB 15 –145 10 –150 0 100 200 300 400VGN510 0(mV6)00 700 800 900 1000 11449-023 0 2.5 5.0 7.5 FR10E.Q0UE1N2.C5Y (1M5H.0z)17.5 20.0 22.5 25.0 11449-026 Figure 24. Noise Figure vs. VGN1 over Filter Corner; Figure 27. Output Noise Density vs. Frequency; Filter Corner = 7 MHz, Digital Gain = 0000001, Noise Density Measured at Half of Filter Corner Digital Gain = 0000001, Noise Density Measured at Half of Filter Corner –100 –100 15dB –101 12dB –105 V/Hz)–102 9dB V/Hz)–110 GAIN = 60dB B B d–103 d Y ( Y (–115 NSIT–104 NSIT–120 DE–105 DE E E –125 GAIN = 40dB S S OI–106 OI UT N–107 UT N–130 P P T T–135 U–108 U GAIN = 20dB O O –109 –140 –110 –145 0 100 200 300 400VGN510 0(mV6)00 700 800 900 1000 11449-024 0 20 40 60 FR8E0QUE1N0C0Y (1M2H0z) 140 160 180 200 11449-027 Figure 25. Output Noise Density vs. VGN1 over VGA1 Digital Gain; Figure 28. Output Noise Density vs. Frequency; Filter Corner = 60 MHz, Noise Density Measured at Half of Filter Corner Digital Gain = 0000001 Rev. A | Page 11 of 39

ADRF6518 Data Sheet 90 100 80 90 80 70 Bc) 60 Bc) 70 Hz (d 50 Hz (d 60 2M 8M 50 T 3 40 +25°C, VPS = 3.30V T 4 +25°C, VPS = 3.30V 2 A +25°C, VPS = 3.15V 3 A 40 +25°C, VPS = 3.15V D 30 +25°C, VPS = 3.45V D +25°C, VPS = 3.45V H +85°C, VPS = 3.30V H 30 +85°C, VPS = 3.30V 20 +85°C, VPS = 3.15V +85°C, VPS = 3.15V +85°C, VPS = 3.45V 20 +85°C, VPS = 3.45V –40°C, VPS = 3.30V –40°C, VPS = 3.30V 10 –40°C, VPS = 3.15V 10 –40°C, VPS = 3.15V –40°C, VPS = 3.45V –40°C, VPS = 3.45V 0 0 –12 –6 0 6 12 18GAIN24 (dB3)0 36 42 48 54 60 11449-029 –6 0 6 12 18 24GAIN30 (dB3)6 42 48 54 60 66 11449-130 Figure 29. HD2 vs. Gain over Supply and Temperature; 16 MHz Fundamental Figure 32. HD3 vs. Gain over Supply and Temperature; 16 MHz Fundamental Tone, Digital Gain = 0000000 Tone, Digital Gain = 0000001 100 90 90 80 80 70 Bc) 70 Bc) 60 Hz (d 60 Hz (d 50 8M 50 2M T 4 +25°C, VPS = 3.30V T 3 40 3 A 40 +25°C, VPS = 3.15V 2 A D +25°C, VPS = 3.45V D 30 H 30 +85°C, VPS = 3.30V H +85°C, VPS = 3.15V 20 20 +85°C, VPS = 3.45V VOCM = 0.90V –40°C, VPS = 3.30V VOCM = 1.25V 10 –40°C, VPS = 3.15V 10 VOCM = 1.65V –40°C, VPS = 3.45V VOCM = 1.95V 0 0 –12 –6 0 6 12 18GAIN24 (dB3)0 36 42 48 54 60 11449-129 –6 0 6 12 18 24GAIN30 (dB3)6 42 48 54 60 66 11449-031 Figure 30. HD3 vs. Gain over Supply and Temperature; 16 MHz Fundamental Figure 33. HD2 vs. Gain over VOCM; 16 MHz Fundamental Tone, Tone, Digital Gain = 0000000 Digital Gain = 0000001 90 100 80 90 80 70 Bc) 60 Bc) 70 Hz (d 50 Hz (d 60 2M 8M 50 T 3 40 +25°C, VPS = 3.30V T 4 2 A +25°C, VPS = 3.15V 3 A 40 D 30 +25°C, VPS = 3.45V D H +85°C, VPS = 3.30V H 30 20 ++8855°°CC,, VVPPSS == 33..1455VV 20 VOCM = 0.90V –40°C, VPS = 3.30V VOCM = 1.25V 10 –40°C, VPS = 3.15V 10 VOCM = 1.65V –40°C, VPS = 3.45V VOCM = 1.95V 0 0 –6 0 6 12 18 24GAIN30 (dB3)6 42 48 54 60 66 11449-030 –6 0 6 12 18 24GAIN30 (dB3)6 42 48 54 60 66 11449-131 Figure 31. HD2 vs. Gain over Supply and Temperature; 16 MHz Fundamental Figure 34. HD3 vs. Gain over VOCM; 16 MHz Fundamental Tone, Tone, Digital Gain = 0000001 Digital Gain = 0000001 Rev. A | Page 12 of 39

Data Sheet ADRF6518 90 50 DIGITAL GAIN = 0000001 80 45 40 70 Bc) 60 35 Hz (d 50 BV) 30 AT 32M 40 OIP3 (d 2250 2 D 30 H 15 20 VGA1 = 9dB, VGN1 = 0V 10 VGA1 = 9dB, VGN1 = 1V +25°C 10 VGA1 = 15dB, VGN1 = 0V 5 +85°C VGA1 = 15dB, VGN1 = 1V –40°C 0 0 0.02 0.04 0V.0G6A1 0O.U09TPU0T. 1S4IGN0A.2L3 LEV0E.3L6 (V 0p.-5p7) 0.90 1.1411449-032 –6 0 6 12 18 24GAIN30 (dB3)6 42 48 54 60 66 11449-135 Figure 35. HD2 vs. VGA1 Output Signal Level (Inferred); Figure 38. In-Band OIP3 vs. Gain over Temperature; 16 MHz Fundamental Tone, VGN2/VGN3 = 0 V 30 MHz and 31 MHz Tones, Digital Gain = 0000001 100 120 90 100 80 Bc) 70 80 Hz (d 60 Bc) 3 AT 48M 5400 IMD3 (d 60 D 40 H 30 GAIN = 40 20 VGA1 = 9dB, VGN1 = 0V 20 GAIN = 30 VGA1 = 9dB, VGN1 = 1V GAIN = 20 10 VGA1 = 15dB, VGN1 = 0V GAIN = 10 VGA1 = 15dB, VGN1 = 1V GAIN = 0 0 0 0.02 0.04 0V.0G6A1 O0.U09TPU0T. 1S4IGN0A.2L3 LEV0E.3L6 (V 0p.-5p7) 0.90 1.14 11449-132 0.5 0.C6OMPO0.S9ITE O1U.3TPUT 1V.O8LTAG2.E5 (V p-3p.)6 4.5 11449-036 Figure 36. HD3 vs. VGA1 Output Signal Level (Inferred); Figure 39. In-Band IMD3 vs. Composite Output Voltage over Gain; 16 MHz Fundamental Tone, VGN2/VGN3 = 0 V 30 MHz and 31 MHz Tones , Digital Gain = 1111110 50 110 DIGITAL GAIN = 0000001 100 40 90 30 80 70 BV) 20 Bc) 60 d d OIP3 ( 10 DIGITAL GAIN = 111110 IMD3 ( 5400 GGAAIINN == 6660 GAIN = 50 0 30 GAIN = 40 GAIN = 30 20 GAIN = 30 –10 GAIN = 20 GAIN = 10 10 GAIN = 0 GAIN = –5 –20–20 –10 0 10 GAI2N0 (dB) 30 40 50 60 11449-035 00 0.5 1C.0OMP1O.5SITE2 .O0UTP2U.5T VO3L.0TAG3E.5 (V p4-p.0) 4.5 5.0 11449-037 Figure 37. In-Band OIP3 vs. Gain over Digital Gain; 1.5 V p-p Composite Figure 40. In-Band IMD3 vs. Composite Output Voltage over Gain; Output Target, 30 MHz and 31 MHz Tones 30 MHz and 31 MHz Tones , Digital Gain = 0000001 Rev. A | Page 13 of 39

ADRF6518 Data Sheet 60 0.45 50 VGA1 = 15dB 40 VGA1 = 12dB 30 VGA1 = 9dB 20 10 0.40 0 V) –10 B –20 Hz (d ––3400 mA) 0.35 D2 AT 30M –––––9758600000 2:1 SLOPE I (SUPPLY0.30 IM––111000 OUT-OF-BAND IP2 –120 0.25 DIGITAL GAIN = 1111110, LOW POWER –130 DIGITAL GAIN = 1111110, HIGH POWER –140 DIGITAL GAIN = 0000001, LOW POWER –150 –160 DIGITAL GAIN = 0000001, HIGH POWER –170 0.20 –65 –55 –I4N5PU–3T5 LE–V25EL– A15T 1–155MH5z AN1D5 14255MHz3 5(dBV45) 55 65 11449-141 0 5 10 15 F2I0LTE2R5 BA30NDW35IDTH40 (MH45z) 50 55 60 65 11449-140 Figure 41. Out-of-Band IIP2, IMD2 vs. PIN over Digital Gain; Figure 44. Supply Current vs. Filter Bandwidth over Digital Gain and Power 115 MHz and 145 MHz Tones Modes 15 0.45 VGA1 = 15dB 0 VGA1 = 12dB VGA1 = 9dB –15 0.40 –30 BV) –45 Hz (d –60 mA) 0.35 3 AT 30M ––9705 3:1 SLOPE I (SUPPLY0.30 D–105 M I OUT-OF-BAND IIP3 –120 0.25 –135 +25°C, DIGITAL GAIN = 1111110, LOW POWER –150 +85°C, DIGITAL GAIN = 1111110, LOW POWER –40°C, DIGITAL GAIN = 1111110, LOW POWER –165 0.20 –55–50–4I5NP–U4T0 L–E35VE–L3 0AT– 21515–M2H0z– A15ND– 11045M–5Hz (0dBV5) 10 15 11449-142 0 5 10 15 F2I0LTE2R5 BA30NDW35IDTH40 (MH45z) 50 55 60 65 11449-041 Figure 42. Out-of-Band IIP3, IMD3 vs. PIN over Digital Gain; Figure 45. Supply Current vs. Filter Bandwidth over Temperature, Digital 115 MHz and 145 MHz Tones Gain, and Power Modes 0.45 80 75 GAIN = 20dB 0.40 70 GAIN = 60dB (mA)Y0.35 R (dB) 6650 PPL MR ISU0.30 C 55 50 DIGITAL GAIN = 1111110, LOW POWER 0.25 DIGITAL GAIN = 1111110, HIGH POWER DIGITAL GAIN = 0000001, LOW POWER 45 DIGITAL GAIN = 0000001, HIGH POWER 0.20 40 0 5 10 15 F2I0LTE2R5 BA30NDW35IDTH40 (MH45z) 50 55 60 65 11449-040 0 10 20FREQUE3N0CY (MHz)40 50 60 11449-046 Figure 43. Supply Current vs. Filter Bandwidth over Digital Gain and Power Figure 46. Common-Mode Rejection Ratio vs. Frequency Modes Rev. A | Page 14 of 39

Data Sheet ADRF6518 VPK (200mV/DIV) VPK (200mV/DIV) SDO/RST (1V/DIV) BASEBAND OUTPUT (500mV/DIV) 20ns/DIV 11449-047 10ns/DIV 11449-055 Figure 47. Peak Detector Time Domain Response Figure 50. Peak Detector Hold Reset Time Domain Response 10 0.6 OPEN 1MΩ 100kΩ OUTPUT (V peak) 1 OUTPUT (V peak) 00..54 OR OR 0.3 PEAK DETECT 0.1 +25°C PEAK DETECT 00..21 +85°C –40°C 0.01–24 –19 –14 –9 VIN –(d4BV) 1 6 11 16 11449-044 00 2 4 6 8TIME10 (ms)12 14 16 18 20 11449-050 Figure 48. Peak Detector Output vs. VIN over Temperature; Figure 51. Peak Detector Hold Time Over RAVG VGN1 = 0.5 V, VGN2 = VGN3 = 0 V 20dB GAIN STEP 20dB GAIN STEP VGN1 = 200mV to 860mV VGN2/VGN3 = 200mV to 530mV (200mV/DIV) (100mV/DIV) 25mV p-p TO 250mV p-p 75mV p-p TO 750mV p-p 5(5000mnVs//DDIVIV) 11449-048 5(5000mnVs//DDIVIV) 11449-148 Figure 49. VGA1 Gain Step Response; VGN2/VGN3 = 0.5 V, −24 dBV RMS Figure 52. VGA2/VGA3 Gain Step Response; VGN1 = 0.5 V, −4 dBV RMS Input Signal Level, C27 = 100 pF Input Signal Level, C17 and C32 = 100 pF Rev. A | Page 15 of 39

ADRF6518 Data Sheet BYPASS MODE VPS = 3.3 V, T = 25°C, Z = 400 Ω, power mode bit (B9) = 1 (high power mode), digital gain code bits (B8 to B2) = 1111110, dc offset A LOAD disable bit (B1) = 0 (enabled), unless otherwise noted. 50 45 +85°C VPS = 3.15V, 3.3V, 3.45V 15dB +25°C 12dB –40°C 9dB 40 40 30 B) 35 DIGITAL GAIN = 0000001 d B) RE ( N (d 20 GU 30 GAI E FI S 10 NOI 25 DIGITAL GAIN = 1111110 0 20 –101M 10MFREQUENCY (Hz1)00M 1G 11449-202 150 100 200 300 400VGN510 0(mV6)00 700 800 900 1000 11449-158 Figure 53. Frequency Response over Supply and Temperature Figure 56. Noise Figure vs. VGN1 over Digital Gain 30 –110 15dB –111 12dB 9dB 25 Hz) –112 V/ B ns) 20 Y (d –113 OUP DELAY ( 15 OISE DENSIT –––111111456 R N G 10 UT –117 P T U –118 5 O –119 01M 10MFREQUENCY (Hz1)00M 1G 11449-154 –1200 100 200 300 400VGN510 0(mV6)00 700 800 900 1000 11449-159 Figure 54. Group Delay vs. Frequency Figure 57. Output Noise Density vs. VGN1 over Digital Gain –100 70 NSITY (dBV/Hz) –––111321000 VGN11,V V ,G1VN 2,1, VVGN3: Hz (dBc)456000 E VGN1, VGN2, VGN3: M E D –140 1V ,1V ,0V 160 TPUT NOIS ––116500 0V ,V0GV N,01V, V AGNND2 , 1VVG ,N03V: ,0V HD2AT 2300 ++–482055°°°CCC U O –170 10 –18050 100 150 FRE2Q00UENCY2 5(M0Hz) 300 350 400 11449-156 00 6 12 18 24GAI3N0 (dB)36 42 48 54 60 11449-051 Figure 55. Output Noise Density vs. Frequency over Analog Gains; Figure 58. HD2 vs. Gain over Temperature; Fundamental at 80 MHz, Digital Digital Gain = 0000001 Gain = 0000001 Rev. A | Page 16 of 39

Data Sheet ADRF6518 90 80 VGN1, VGN2, VGN3 = 1V DIGITAL GAIN = 0000001 70 80 60 70 50 T 240MHz (dBc) 456000 GAIN (dB) 12340000 VGN1, VGN2, VGN3 = 1V DIGITAL GAIN = 1111110 A +85°C 0 VGN1, VGN2, VGN3 = 0V DIGITAL GAIN = 0000001 HD3 30 +–4205°°CC –10 20 –20 VGN1, VGN2, VGN3 = 0V DIGITAL GAIN = 1111110 –30 10 –40 0 –50 0 6 12 18 24GAI3N0 (dB)36 42 48 54 60 11449-052 1M 10MFREQUENCY (Hz1)00M 1G 11449-203 Figure 59. HD3 vs. Gain over Temperature; Fundamental at 80 MHz, Digital Figure 62. Gain vs. Frequency Gain = 0000001 120 10 100 k) a e p V 80 T ( 1 U P Bc) UT d O D3 ( 60 OR M T I EC 40 T 0.1 E D GAIN = 40 AK 20 GAIN = 30 PE GAIN = 20 +25°C GAIN = 10 +85°C GAIN = 0 –40°C 0 0.01 0.5 0.C6OMPO0.S9ITE O1U.3TPUT 1V.O8LTAG2E.5 (V p-p3.)6 4.5 11449-061 –24 –19 –14 –9 VIN –(4dBV) 1 6 11 16 11449-065 Figure 60. IMD3 vs. Composite Output Voltage over VOCM; Figure 63. Peak Detector Output vs. VIN over Temperature; VGN1 = 0.5 V, VGN1/VGN2/VGN3 = 1 V, 125 MHz and 126 MHz Tones VGN2/VGN3 = 0 V; 125 MHz Tone 50 40 V) B S (d 30 S A P Y 3 B 20 P OI 10 +25°C +85°C –40°C 0 12 18 24 30 G36AIN (d4B2) 48 54 60 66 11449-056 Figure 61. In-Band OIP3 Bypass vs. Gain over Temperature; Digital Gain = 0000001, 125 MHz and 126 MHz Tones Rev. A | Page 17 of 39

ADRF6518 Data Sheet MIXED POWER AND FILTER MODES VPS = 3.3 V, T = 25°C, Z = 400 Ω, digital gain code bits (B8 to B2) = 1111110, dc offset disable bit (B1) = 0 (enabled), unless A LOAD otherwise noted. 80 100 BANDWIDTH=63MHz 70 90 GAIN = 60dB 80 60 GAIN = 40dB 70 GAIN=20dB 50 B) dB) GAIN = 20dB N (d 60 CMRR ( 4300 SOLATIO 4500 I GAIN=60dB 30 20 20 10 10 00 100 200 300 FR40E0QUE5N00CY (6M0H0z)700 800 900 1000 11449-057 0100 200 300 400FREQ50U0ENC6Y0 0(MHz7)00 800 900 1000 11449-172 Figure 64. Common-Mode Rejection Ratio (CMRR) vs. Frequency Figure 66. Channel Isolation (OPM1_SE to OPM2_SE) vs. Frequency, Bypass Mode 100 BANDWIDTH=63MHz GAIN=20dB 90 80 B) GAIN=60dB d N ( 70 O TI A L 60 O S I 50 40 30 0 10 20 FRE3Q0UENCY4 (0MHz) 50 60 11449-171 Figure 65. Channel Isolation (OPM1_SE to OPM2_SE) vs. Frequency, Filter Mode Rev. A | Page 18 of 39

Data Sheet ADRF6518 CHARACTERIZATION 1.2 NOISE FIGURE CALCULATION VGN1 SOLID LINES, DIGITAL GAIN CODE = 0000001 VGN2 DASHED LINES, DIGITAL GAIN CODE = 0000000 All of the noise figure plots (see Figure 23, Figure 24, and 1.0 VGN3 Figure 56) were completed by input referring the output noise VGN1 VGN2 density and then dividing it by the theoretical noise density of a 3 (V) 0.8 VGN3 50 Ω resister. The input SMA on the evaluation board was N VG terminated with a 50 Ω resistor to ground, which provided the N2/ 0.6 ADRF6518 input with a 400 Ω differential impedance via the 8:1 G V 1/ balun. In signal chain calculations, it is often convenient to N VG 0.4 reference the noise figure to 50 Ω, even though the ADRF6518 input is terminated in 400 Ω. 0.2 The noise factor is calculated as follows: 0 N –12 –6 0 6 12 18 G2A4IN (3d0B)36 42 48 54 60 66 11449-066 NoiseFactor OUNTGAIN Figure 67. Gain Distribution for HD2/HD3 vs. Gain 50 where the noise densities are in nV/√Hz and GAIN is in linear Figure 67 shows the ADRF6518 analog gain distribution for the terms. The noise figure is then HD2 vs. gain and HD3 vs. gain plots while the gain and input voltage levels were swept and while keeping the output voltage Noise Figure = 10 log (Noise Factor) 10 level at 1.5 V p-p. Rev. A | Page 19 of 39

ADRF6518 Data Sheet REGISTER MAP AND CODES The filter frequency, amplifier gains, filter bypass mode, and Table 4. Filter Mode and Power Mode Options offset correction loops can be programmed using the SPI B9 Filter Bypass Filter interface. Table 5 provides the bit map for the internal 15-bit 0 VGA low power; filter off VGA low power; filter low register of the ADRF6518. power 1 VGA high power; filter VGA low power; filter high off power Table 5. Register Map MSB LSB B15 B14 B13 B12 B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 Filter frequency code and filter bypass mode Power mode Digital gain code DC offset disable Code = 1 dB corner in MHz 0: low power VGA1 gain VGA2 gain VGA3 gain Postamp 0: enable For example, 31 MHz = 011111 (MSB first) 1: high power 00: 15 dB 00: 21 dB 00: 21 dB 0: 3 dB 1: disable Use 000000 for filter bypass mode Use 1 for filter BW > 31 MHz, in 01: 12 dB 01: 18 dB 01: 18 dB 1: 9 dB filter mode 10: 9 dB 10: 15 dB 10: 15 dB Use 1 for channel BW > 60 MHz, 11: 9 dB 11: 12 dB 11: 12 dB in filter bypass mode Rev. A | Page 20 of 39

Data Sheet ADRF6518 THEORY OF OPERATION 1MHz TO 63MHz 3dB/9dB 24dB PROGRAMMABLE 24dB 24dB ADC VGA FILTERS VGA VGA DRIVER BASEBAND BASEBAND INPUTS OUTPUTS ANALOG GAIN CONTROL 30mV/dB B INPUT 5d COMMCOONN-MTORODEL 2dB/1 15dB/21dB 15dB/21dB dB B/1 dB/dB/ dB/dB/ B/9 d 28 28 d 9 11 11 3 SPI INTERFACE GPARINOS GAPRNI ADBM UFMSILITNEGR COMCOOMUNOTTNPR-UMOTOLDE 11449-067 Figure 68. Signal Path Block Diagram for a Single Channel of the ADRF6518 The ADRF6518 consists of a matched pair of input VGAs to set the output common-mode voltage of the driving circuit. followed by programmable filters, and then by a cascade of two However, this is optional and input common-mode can be variable gain amplifiers and output ADC drivers. The filters can independently set within the supported range. For a 3.3 V be bypassed and powered down through the SPI interface for supply on VPI, the input common mode can range from 1.35 V operation beyond the maximum filter bandwidth. The block to 1.95 V, while maintaining a 5 V p-p input level at >60 dBc diagram of a single channel is shown in Figure 68. HD2 and HD3. For a 5 V supply on VPI, the input common-mode range extends to 1.35 V to 3.1 V. Extra current is drawn from the The programmability of the filter bandwidth and of the prefilter- VPI supply to support an input common mode greater than the ing and postfiltering fixed gains through the SPI interface offers midvalue of the main 3.3 V supply, that is, VPS/2. great flexibility when coping with signals of varying levels in the presence of noise and large, undesired signals near the desired The VICM/AC voltage is not buffered and must be sensed at a band. The entire differential signal chain is dc-coupled with high impedance point to prevent it from being loaded down. flexible interfaces at the input and output. The bandwidth and When the baseband input signal is ac-coupled, pull the VICM/AC gain setting controls for the two channels are shared, ensuring pin low to activate the internal bias for the input stage. close matching of their magnitude and phase responses. The The input VGAs have analog gain control of 24 dB, followed ADRF6518 can be fully disabled through the ENBL pin. by a digital gain settings of 9 dB, 12 dB, or 15 dB, selectable Filtering and amplification are fundamental operations in any through the SPI (see the Register Map and Codes section). The signal processing system. Filtering is necessary to select the VGAs are based on the Analog Devices, Inc., patented X-AMP® intended signal while rejecting out-of-band noise and interfer- architecture, consisting of tapped 24 dB attenuators, followed by ers. Amplification increases the level of the desired signal to programmable gain amplifiers. The X-AMP architecture gener- overcome noise added by the system. When used together, ates a continuous linear-in-dB monotonic gain response with filtering and amplification can extract a low level signal of low ripple. The analog gain of the VGA sections are controlled interest in the presence of noise and out-of-band interferers. through the high impedance VGN1 pin with an accurate slope Such analog signal processing alleviates the requirements on the of 30 mV/dB. Adjust the VGA analog gain through an AGC analog, mixed signal, and digital components that follow. mechanism, such that 1.5 V p-p at the output of the first VGA is not exceeded. If, however, the input signal is small enough, the INPUT VGAs first VGA can be set at full gain for best noise figure (NF) perfor- The input VGAs provide a convenient interface to the sensitive mance and gain control achieved in the second or third VGA. filter sections that follow. They are designed to have a low noise Driving ADRF6518 Single-Ended figure and high linearity. The combination of analog gain control and digital gain settings allow a wide range of input signal levels The input structure of the ADRF6518 is designed for differen- to be conditioned to drive the filters at up to 1.5 V p-p amplitude. tial drive. However, with some performance degradation, it can The VGAs set a differential input impedance of 400 Ω. be driven single-ended, especially at low bandwidth signals. See the Applications Information section for guidance on single- The baseband input signal can be ac-coupled or dc-coupled via ended drive. Pin 7 selection. When the signal is dc-coupled, the wide input common-mode voltage is supported by having an optional 5 V supply on Pin 8, VPI. The default common-mode voltage is VPI/2, which is available on the dual function Pin 7, VICM/AC, Rev. A | Page 21 of 39

ADRF6518 Data Sheet PEAK DETECTOR 0 To measure the signal level at the critical interface of the VGA1 –20 output and the programmable filter input, a peak detector has B) –40 been implemented. The peak detector simultaneously measures E ((d –60 12MMHHzz both channels at the VGA1 output and reports the bigger of the UD 4MHz two at the VPK pin. The on-chip holding capacitor and negligi- NIT –80 816MMHHzz G 32MHz ble leakage at the internal node ensure a large droop time of the MA –100 63MHz E order of a millisecond, which is a function of the peak voltage as V TI –120 well. Bigger peak voltage results in longer droop time. The droop LA E time can be adjusted down by placing a resistor between the R –140 RAVG and VPS pins. Typical values of RAVG can range from –160 1 MΩ to 1 kΩ. As the RAVG resistor value is reduced, the peak –180 vhoalst athgee, aVttPacKk, bapanpedawrisd atsh aonf e1n0v0e MlopHez o. utput. The peak detector 100k 1M FREQU1E0NMCY (Hz) 100M 1G 11449-068 Figure 69. Sixth-Order Butterworth Magnitude Response for 0.5 dB The peak detector can be used in an AGC loop to set the appropri- Bandwidths ate signal level at the filter input. For such an implementation, 500 filter VPK appropriately, considering that it is a peak hold output. A high pulse of 25 ns or longer duration applied to the 400 SDO/RST dual function pin resets the VPK voltage to 0 V by BW = 2MHz BW = 28MHz discharging the internal holding capacitor. s) 300 n PROGRAMMABLE FILTERS AY ( L E 200 The integrated programmable filter is the key signal processing P D 14× U function in the ADRF6518. The filters follow a six-pole Butter- O GR 100 worth prototype response that provides a compromise between band rejection, ripple, and group delay. The 0.5 dB bandwidth is 0 programmed from 1 MHz to 63 MHz in 1 MHz steps via the serial programming interface (SPI) as described in the Programming –100 tThhee A fiDltRerFs6 a5r1e8 d seescigtinoend. so that the Butterworth prototype filter 100k 1MFREQUENCY (Hz)10M 100M 11449-069 Figure 70. Sixth-Order Butterworth Group Delay Response for shape and group delay responses vs. frequency are retained for 0.5 dB Bandwidths Programmed to 2 MHz and 28 MHz any bandwidth setting. Figure 69 and Figure 70 illustrate the The corner frequency of the filters is defined by RC products, ideal six-pole Butterworth response. The group delay, τ, is g which can vary by ±30% in a typical process. Therefore, all the defined as parts are factory calibrated for corner frequency, resulting in τg = −∂φ/∂ω a residual ±8% corner frequency variation over the −40°C to where: +85°C temperature range. Although absolute accuracy requires φ is the phase in radians. calibration, the matching of RC products between the pair of ω = 2πf is the frequency in radians per second. channels is better than 1% by observing careful design and layout practices. Calibration and excellent matching ensure Note that for a frequency scaled filter prototype, the absolute that the magnitude and group delay responses of both channels magnitude of the group delay scales inversely with the band- track together, a critical requirement for digital IQ-based width; however, the shape is retained. For example, the peak communication systems. group delay for a 28 MHz bandwidth setting is 14× less than Bypassing the Filters for a 2 MHz setting. For higher bandwidth applications, filters of the ADRF6518 can be bypassed via the SPI. In the filter bypass mode, filters are disabled and power consumption is significantly reduced. The bandwidth of cascaded VGAs, which is significantly larger than 63 MHz maximum of the filters, is fully realized in the filter bypass mode. Rev. A | Page 22 of 39

Data Sheet ADRF6518 VARIABLE GAIN AMPLIFIERS (VGAs) The cascaded VGA2 and VGA3 are also based on the X-AMP OFDS COFS OFSx architecture, and each has 24 dB gain range with separate high impedance gain control inputs, VGN2 and VGN3. The VGA structures of the second and third VGAs are identical to that of the first VGA. However, these have slightly higher noise figure FILFTREORMS BOAUSTEPBUATSND and less drive level capability. Their output is rated at 1 V p-p 50dB OUTPUT ADC froarn g>e6,0 t hdeB sce HcoDn2d aonr dth HirDd 3V. GDAep oern bdointhg ocann t hbee iunspeudt fsoirg nAaGl C GAINVGA DRIVER 11449-070 purposes. The critical level to consider while making this choice Figure 71. Offset Compensation Loop Operates Around the VGA is the signal level at the output of the VGAs, which must not and Output Buffer exceeded 1 V p-p to maintain low distortion. The offset control loop creates a high-pass corner, f , that HP The fixed gain following both of the variable gain sections can is superimposed on the normal Butterworth filter response also be programmed to 12 dB, 15 dB, 18 dB, or 21 dB to maxim- when filters are enabled. Typically, fHP is many orders of ize the dynamic range. magnitude lower than the lower programmed filter bandwidth so that there is no interaction between them. Setting f is OUTPUT BUFFERS/ADC DRIVERS HP accomplished with capacitors, C , from the OFS1 and OFS2 OFS The low impedance (<10 Ω) output buffers of the ADRF6518 pins to ground. Because the correction loop works around the are designed to drive either ADC inputs or subsequent amplifier VGA sections, f is also dependent on the total gain of the HP stages. They are capable of delivering up to 4 V p-p composite cascaded VGAs. In general, the expression for f is given by HP two-tone signals into 400 Ω differential loads with >60 dBc f (Hz) = 6.7 × Post Filter Linear Gain/C (μF) IMD3. The output common-mode voltage defaults to VPS/2, HP OFS but it can be adjusted from 900 mV to VPS − 1.2 V without loss where Post Filter Linear Gain is expressed in linear terms, not of drive capability by presenting the VOCM pin with the in decibels (dB), and is the gain following the filters, which desired common-mode voltage. The high input impedance of excludes the VGA1 gain. VOCM allows the ADC reference output to be connected Note that f increases in proportion to the gain. For this HP directly. Even though the output common-mode voltage is reason, choose C at the highest operating gain to guarantee OFS adjustable, and the offset compensation loop can null the that f is always below the maximum limit required by the HP accumulated dc offsets (see the DC Offset Compensation Loop system. section), it may still be desirable to ac-couple the outputs by PROGRAMMING THE ADRF6518 selecting the coupling capacitors according to the load imped- ance and desired bandwidth. The 0.5 dB corner frequencies for both filters, the digital gains of all the VGAs, and the output buffers are programmed simultane- DC OFFSET COMPENSATION LOOP ously through the SPI port. In addition to these, enabling the dc In many signal processing applications, no information is offset compensation loop and power mode selection are also carried in the dc level. In fact, dc voltages and other low controlled through SPI port. A 16-bit register stores 15 data bits, frequency disturbances can often dominate the intended signal including the 6-bit code for corner frequencies of 1 MHz through and consume precious dynamic range in the analog path and 63 MHz and filter bypass, as well as the codes for VGA gains, bits in the data converters. These dc voltages can be present and the postamplifier gain (see Table 5). The SPI protocol not with the desired input signal or can be generated inside the only allows these selections to be written to the DATA pin, but signal path by inherent dc offsets or other unintended signal- also allows the stored code to be read back via the SDO/RST pin. dependent processes such as self-mixing or rectification. The latch enable (LE) pin must first go to a Logic 0 for a read or Because the ADRF6518 is fully dc-coupled, it may be necessary write cycle to begin. On the next rising edge of the clock (CLK), to remove these offsets to realize the maximum signal-to-noise a Logic 1 on the DATA pin initiates a write cycle, whereas a ratio (SNR). The external offsets can be eliminated with ac- Logic 0 on the DATA pin initiates a read cycle. In a write cycle, coupling capacitors at the input pins; however, that requires the next 15 CLK rising edges latch the desired 15-bit code, LSB large value capacitors because the impedances can be fairly low, first. This results in 16-bit code, including the first Logic 1 to and high-pass corners may need to be <10 Hz in some cases. To initiate a write cycle. When LE goes high, the write cycle is address the issue of dc offsets, the ADRF6518 provides an offset completed and different codes are presented various blocks that correction loop that nulls the output differential dc level, as need programming. In a read cycle, the next 15 CLK falling shown in Figure 71. If the correction loop is not required, it can edges present the stored 15-bit code, LSB first. When LE goes be disabled through the SPI port. high, the read cycle is completed. Detailed timing diagrams are shown in Figure 2 and Figure 3. Rev. A | Page 23 of 39

ADRF6518 Data Sheet NOISE CHARACTERISTICS In the filter mode, these out-of-band signals are filtered before reaching VGA2 and VGA3. It is important to understand the The output noise behavior of the ADRF6518 depends on the gain signals presented to the ADRF6518 and to match these signals and bandwidth settings. VGA1 noise dominates in the filter with the input and output characteristics of the part. It is useful bypass mode and at high filter corner settings. While at low to partition the ADRF6518 into the front end, composed of corner settings, filter noise tends to dominate. VGA1 and the filter, and the back end, composed of VGA2 and The filter contributes a noise spectral density profile that is flat VGA3 and the output buffers. at low frequencies, peaks near the corner frequency, and then VGA1 can handle a 5 V p-p signal at a maximum analog attenua- rolls off as the filter poles roll off the gain and noise. The tion setting, without experiencing appreciable distortion at the magnitude of the noise spectral density contributed by the filter, input. In most applications, VGA1 gain should be adjusted such expressed in nV/√Hz, varies inversely with the square root of that the maximum signal presented at the filter inputs (or the bandwidth setting, resulting in filter noise in nV that is VGA2 input in filter bypass mode) is <1.5 V p-p. At this level, nearly constant with the bandwidth setting. However, with the front end does not limit the distortion performance. The VGA1 NF being lower than the filter, VGA1 tends to dominate peak detector output, VPK, can be used as an indicator of the the overall NF. At higher frequencies, after the filter noise rolls signal level present at this critical interface. Choose the second off, the noise floor is set by the VGAs. and third VGA gains such that their output levels do not exceed Each of the X-AMP VGA sections used in the ADRF6518 1 V p-p. If the output signal level is expected to exceed 1.5 V p-p, contributes a fixed noise spectral density to its respective output, it is recommended to set the postamplifier gain to 9 dB. independent of the analog gain setting. With the digital gain For these signal level considerations, it is recommended that the change, however, VGA output noise changes, because the gain out-of-band signal, if larger than the desired in-band signal, be setting resistors values change. As an example, the VGA1 NF addressed. In filter mode, such an out-of-band signal only corresponding to a 15 dB gain setting is 17.3 dB, whereas for a affects the VGA1 operation, because it is filtered out by the 9 dB gain, the NF is 19 dB. When cascaded, the total noise filter and does not affect the following stages. In this case, a contributed by the VGAs at the output of the ADRF6518 high VGA2 and VGA3 gain may be needed to raise the small increases gradually with higher gain. This is apparent in the desired signal to a higher level at the output. In the filter bypass noise floor variation at high frequencies at different VGA gain mode, such out-of-band signals may need to be filtered prior to settings. The exact relationship depends on the programmed the ADRF6518. fixed gain of the amplifiers. At lower frequencies within the filter bandwidth setting, the VGAs translate the filter noise directly to The overall distortion introduced by the part depends on the the output by a factor equal to the gain following the filter. input drive level, including the out-of-band signals, and the desired output signal level. To achieve best distortion At low values of VGA gain, the noise at the output is the flat performance and the desired overall gain, keep in mind the spectral density contributed by the last VGA. As the gain maximum signal levels indicated previously when selecting increases, more of the filter and first VGA noise appears at different VGA gains. the output. Because the intrinsic filter noise density increases at lower bandwidth settings, it is more pronounced than it is To distinguish and quantify the distortion performance of the at higher bandwidth settings. In either case, the noise density input section, two different IP3 specifications are presented. asymptotically approaches the limit set by the VGAs at the The first is called in-band IP3 and refers to a two-tone test highest frequencies. For other values of VGA gain and bandwidth where the signals are inside the filter bandwidth. This is exactly setting, the detailed shape of the noise spectral density changes the same figure of merit familiar to communications engineers according to the relative contributions of the filters and VGAs. in which the third-order intermodulation level, IMD3, is measured. Because the noise spectral density outside the filter bandwidth is limited by the VGA output noise, it may be necessary to use To quantify the effect of out-of-band signals, a new out-of-band an external, fixed frequency, passive filter prior to analog-to- (OOB) IIP3 figure of merit is introduced. This test also involves digital conversion to prevent noise aliasing from degrading the a two-tone stimulus; however, the two tones are placed out-of- signal-to-noise ratio. A higher sampling rate, relative to the maxi- band so that the lower IMD3 product lands in the middle of the mum required ADRF6518 corner frequency setting, reduces the filter pass band. At the output, only the IMD3 product is visible order and complexity of this external filter. because the original two tones are filtered out. To calculate the OOB IIP3 at the input, the IMD3 level is referred to the input DISTORTION CHARACTERISTICS by the overall gain. The OOB IIP3 allows the user to predict the To maintain low distortion through the cascaded VGAs and impact of out-of-band blockers or interferers at an arbitrary filter of the ADRF6518, consider the distortion limits of each signal level on the in-band performance. The ratio of the desired stage. The first VGA has higher signal handling capability and input signal level to the input-referred IMD3 at a given blocker bandwidth than VGA2 and VGA3, because it must cope with level represents a signal-to-distortion limit imposed by the out- out-of-band signals that can be larger than the in-band signals. of-band signals. Rev. A | Page 24 of 39

Data Sheet ADRF6518 MAXIMIZING THE DYNAMIC RANGE VGA2 and VGA3. In such a case, both the distortion limits associated with the blocker at the input and the SNR limits When used in the filter mode, the role of the ADRF6518 is to created by the weaker signal and higher gains are present increase the level of a variable in-band signal while minimizing simultaneously. Furthermore, not only does the blocker out-of-band signals. Ideally, this is achieved without degrading scenario degrade the dynamic range, it also reduces the range of the SNR of the incoming signal or introducing distortion to the input signals that can be handled because a larger part of the incoming signal. gain range is simply used to extract the weak desired signal from The first goal is to maximize the output signal swing, which can the stronger blocker. be defined by the ADC input range or the input signal capacity KEY PARAMETERS FOR QUADRATURE-BASED of the next analog stage. For the complex waveforms often encoun- RECEIVERS tered in communication systems, the peak-to-average ratio, or crest factor, must be considered when choosing the peak-to-peak The majority of digital communication receivers make use of output. From the chosen output signal and the maximum gain quadrature signaling, in which bits of information are encoded of the ADRF6518, the minimum input level can be defined. onto pairs of baseband signals that then modulate in-phase (I) and quadrature (Q) sinusoidal carriers. Both the baseband and As the input signal level increases, the VGA3 gain is reduced modulated signals appear quite complex in the time domain with from its maximum gain point to maintain the desired fixed dramatic peaks and valleys. In a typical receiver, the goal is to output level. VGA2 and VGA1 can then be adjusted as the input recover the pair of quadrature baseband signals in the presence signal level keeps increasing. This maintains the best NF for the of noise and interfering signals after quadrature demodulation. cascaded chain. The output noise, initially dominated by the In the process of filtering out-of-band noise and unwanted inter- filter and VGA1 combination, follows the gain reduction, ferers and restoring the levels of the wanted I and Q baseband yielding a progressively better SNR. At some point, the VGA3 signals, it is critical to retain their gain and phase integrity over and VGA2 gains drop sufficiently so that their noise becomes the bandwidth. dominant, resulting in a slower reduction in SNR from that point. From the perspective of SNR alone, the maximum input In filter mode, the ADRF6518 delivers flat in-band gain and level is reached when the VGA1 reaches its minimum gain. group delay, consistent with a six-pole Butterworth prototype filter, as described in the Programmable Filters section. Distortion must also be considered when maximizing the dynamic Furthermore, careful design ensures excellent matching of these range. At low and moderate signal levels, the output distortion parameters between the I and Q channels. Although absolute is constant and assumed to be adequate for the selected output gain flatness and group delay can be corrected with digital level. At some point, the input signal becomes large enough that equalization, mismatch introduces quadrature errors and distortion at the input limits the system. This can be kept in check intersymbol interference that degrade bit error rates in digital by monitoring peak detector voltage, VPK. communication systems. The most challenging scenario in terms of dynamic range is the For wideband signals, filters can be bypassed and the presence of a large out-of-band blocker accompanying a weaker ADRF6518 then becomes a dual cascaded chain of three VGAs, in-band wanted signal. In this case, the maximum input level is offering large gain range options, while maintaining gain and dictated by the blocker and its inclination to cause distortion. group delay match between the two channels. After filtering, the weak wanted signal must be amplified to the desired output level, possibly requiring the maximum gain on Rev. A | Page 25 of 39

ADRF6518 Data Sheet APPLICATIONS INFORMATION BASIC CONNECTIONS 1.35 V to 1.95 V while VPI = 3.3 V. The user has the option of tying VPI to a voltage up to 5 V. This provides a common-mode range of Figure 72 shows the basic connections for a typical ADRF6518 1.35 V to 3.1 V. In general, the minimum input common-mode application. voltage is always 1.35 V, but the maximum common-mode voltage SUPPLY DECOUPLING is V = 0.64 × VPI − 0.135 V. The VICM pin can be used as a CM_MAX Apply a nominal supply voltage of 3.3 V to the supply pins, reference common-mode voltage for driving a high impedance VPS, VPI, and VPSD. The supply voltage must not exceed sensing node of the preceding cascaded part (VICM has a 3.45 V or drop below 3.15 V for VPS and VPSD. The supply 7.75 kΩ impedance). voltage on VPI must not exceed 5.25 V. Decouple each supply OUTPUT SIGNAL PATH pin to ground with at least one low inductance, surface-mount The low impedance (10 Ω) output buffers are designed to drive ceramic capacitor of 0.1 μF placed as close as possible to the a high impedance load, such as an ADC input or another amplifier ADRF6518 device. stage. The output pins—OPP1, OPM1, OPP2, and OPM2—sit The ADRF6518 has three separate supplies: two analog supplies at a nominal output common-mode voltage of VPS/2, but can and a digital supply. Take care to separate the analog and digital be driven to a voltage of 0.9 V to VPS − 1.2 V by applying the supplies with a large surface-mount inductor of 33 μH. Then desired common-mode voltage to the high impedance VOCM decouple each supply separately to its respective ground through pin. a 10 μF capacitor. DC OFFSET COMPENSATION LOOP ENABLED INPUT SIGNAL PATH When the dc offset compensation loop is enabled via B1 of the Each signal path has an input VGA, accessed through the INP1, SPI register, the ADRF6518 can null the output differential dc INM1, INP2, and INM2 pins, that sets a differential input level. The loop is enabled by setting B1 = 0. The offset impedance of 400 Ω. compensation loop creates a high-pass corner frequency, which The inputs can be dc-coupled or ac-coupled. To ac couple the is proportional to the value of the capacitors that are connected inputs, the user must pull the VICM/AC pin to ground. This from the OFS1 and OFS2 pins to ground. For more information provides an input common-mode voltage of VPI/2. To dc about setting the high-pass corner frequency, see the DC Offset couple the inputs, let the VICM pin float. If using direct dc Compensation Loop section. coupling, the common-mode voltage, V , can range from CM INPUT1(–) 0.1µF VPS 0.1µF INPUT1(+) VPS VPS 0.1µF OUTPUT1(+) E C ENBL INM1 RAVG OFS1 FA VPSD VPSD INP1 VPS VGN1 VPOSPP1 ER 0.1µF COMD OPM1 T N LE COM OUTPUT1(–) ONTROL I CDSDLAKOTA/RSTADRF6518 VVCOGOCNMM3 0.1µF 0.1µF RIAL C 0.1µF VVPICIMC/OAMCINP2INM2VPSVPKVGNO2FS2VPOOSPPMP22 OUTPUT2(–) E S 0.1µF VPS INPUT2(+) 0.1µF VPI OUTPUT2(+) 0.1µF VPS INPUT2(–) 0.1µF 11449-071 Figure 72. Basic Connections Rev. A | Page 26 of 39

Data Sheet ADRF6518 COMMON-MODE BYPASSING noise contributions, EVM has a tendency to reach an opti- mal level determined dominantly by either the quadrature Decouple the ADRF6518 common-mode pins, VICM/AC and accuracy and IQ gain match of the signal chain or the VOCM, to ground. Use at least one low inductance, surface- precision of the test equipment. mount ceramic capacitor with a value of 0.1 μF to decouple the • As signal levels decrease, such that noise is a major con- common-mode pins. tributor, EVM performance vs. the signal level exhibits SERIAL PORT CONNECTIONS a decibel-for-decibel degradation with decreasing signal The ADRF6518 has a SPI port to control the gain and filter band- level. At these lower signal levels, where noise is the width settings. Data can be written to the internal 15-bit register dominant limitation, decibel EVM is directly proportional and read from the register. It is recommended that low-pass RC to the SNR. filtering be placed on the SPI lines to filter out any high frequency EVM TEST SETUP glitches. See Figure 90, the evaluation board schematic, for an example of a low-pass RC filter. The basic setup to test the EVM for the ADRF6518 consisted of an Agilent MXG N5182B vector signal generator used as a ENABLE/DISABLE FUNCTION signal source and an Agilent DSO7104B oscilloscope used to To enable the ADRF6518, pull the ENBL pin high. Driving the sample the signal while connected to a computer running Agilent ENBL pin low disables the device, reducing current consump- 89600 vector signal analysis (VSA) software to calculate the EVM tion to approximately 1 mA at room temperature. For the of the signal. The I and Q outputs of the ADRF6518 were disable function to work properly, connect 10 kΩ pull-down loaded with 400 Ω differential impedances and connected resistors from the signal output pins (OPP1, OPM1, OPP2, differentially to two AD8130 amplifiers to convert the signals OPM2) to ground to allow a dc path to ground for proper into single-ended signals. The single-ended signals were discharge (see Figure 67). If the disable function is not used, connected to the input channels of the vector signal analyzer. pull-down resistors are not necessary. EVM MEASUREMENT GAIN PIN DECOUPLING EVM was measured for the ADRF6518 only (the AD8130 The ADRF6518 has three analog gain control pins: VGN1, amplifiers were used, but their EVM contribution is minimal VGN2, and VGN3. Use at least one low inductance, surface- and do not dominate the measurement). The N5182B IQ baseband mount ceramic capacitor with a value of 0.1 μF to decouple differential outputs drove the ADRF6518 inputs through 1 µF each gain control pin to ground. coupling capacitors. Large coupling capacitors are necessary to PEAK DETECTOR CONNECTIONS keep the high-pass corner created by the capacitors as low as possible and to prevent the low-pass corner from corrupting the The ADRF6518 has a peak detector output on the VPK pin, signal. The VICM/AC pin was grounded to enable ac coupling. with a scaling of 1 V/V peak differential at filter inputs. The The VPI pin was connected to 3.3 V by shorting it to VPS. The bigger peak of the two channels is reported. The peak detector alpha of the pulse response filter was set to 0.35. The baseband time-constant can be changed with a resistor from the RAVG input power to the ADRF6518 was swept, and the analog gains pin to VPS. Leave the RAVG pin open for the longest time- were adjusted to maintain a target 1.5 V p-p differential signal constant (hold time). The RAVG resistor range is ∞ to 1 kΩ. level on both the I and Q outputs. The VGA1 analog gain was To reset the peak detector, pull the SDO/RST pin high for 25 ns adjusted to limit its output to 1.5 V p-p (0.75 V peak on the or longer. Logic levels are V < 0.8 V, V > 2 V. LOW HIGH peak detector output). The filter corner was set to 63 MHz, and ERROR VECTOR MAGNITUDE (EVM) PERFORMANCE the digital gains for VGA1, VGA2, VGA3, and the postamplifier were set to 15 dB, 21 dB, 21 dB, and 3 dB, respectively. Several Error vector magnitude (EVM) is a measure used to quantify signal bandwidths, signal types, gains, and output levels were the performance of a digital radio transmitter or receiver by tested, in filter mode and in filter bypass mode. measuring the fidelity of the digital signal transmitted or received. Various imperfections in the link, such as magnitude It is important to keep the high-pass corner of the output offset and phase imbalance, noise, and distortion, cause the compensation loop low compared to the signal bandwidth. The constellation points to deviate from their ideal locations. lower the signal bandwidth is, the lower the user must set the high-pass corner to ensure that the minimal amount of the In general, a receiver exhibits three distinct EVM limitations signal is not corrupted. See the Applications Information vs. received input signal power. As signal power increases, the section of the ADRF6510 and the ADRF6516 data sheets for distortion components increase. additional information on the effects of setting the high-pass • At large enough signal levels, where the distortion compo- corner too high in frequency. nents due to the harmonic nonlinearities in the device are It is also important to set the filter corner appropriately for the falling in-band, EVM degrades as signal levels increase. given signal bandwidth. The user must be careful not to set the • At medium signal levels, where the signal chain behaves filter corner too low in an attempt to achieve more rejection of in a linear manner and the signal is well above any notable Rev. A | Page 27 of 39

ADRF6518 Data Sheet the out-of-band blockers, because this can corrupt the data in 0 5MSPS the signal and degrade the EVM. For examples of this, see the –5 10MSPS 50MSPS applications information section in the ADRF6510 and the –10 ADRF6516 data sheets. Figure 83 also shows this trade-off –15 between filter corner and signal bandwidth. –20 In Figure 73 through Figure 77, the x-axis is appropriately dB) labeled in units of a voltage ratio, which is defined as VM ( –25 E –30 20 × log10(x/1 V p-p) –35 where x is any number in units of V p-p. –40 This is done because the 100 Ω differential baseband source –45 (Agilent MXG N5182B) drives the 400 Ω differential input –50 idmBpme,d iasn ocnel yo fa tphpel iAcaDbRleF i6n5 a1 85.0 T Ωh es yssttaenmda. r d unit of power ratio, –40 –30 –20 VIN (d–B10V p-p) 0 10 20 11449-080 Figure 74. EVM vs. Input Voltage over Symbol Rates; Filter Bypass Mode, Figure 73 and Figure 74 show EVM vs. input voltage over QPSK, Gain Code = 0000000, 1.5 V p-p Differential Output Level Maintained different symbol rates in filter mode (filter corner = 63 MHz) Figure 75 and Figure 76 show EVM vs. input voltage over and in filter bypass mode, respectively. EVM is generally better different modulation types at 50 MSPS in filter mode and in for higher symbol rates while in filter bypass mode. This is filter bypass mode, respectively. EVM improves for the high- mainly due to the absence of noise and distortion components order modulation types when the filter is in bypass mode. that the filter introduces. For the same 80 MSPS signal, EVM improves 11 dB when switching from a 63 MHz filter corner to 0 QPSK filter bypass mode. For the lower symbol rates, the difference in –5 16QAM EVM between a 63 MHz filter corner and filter bypass mode is 256QAM –10 negligible. –15 0 5MSPS –20 –5 10MSPS dB) 50MSPS M ( –25 –10 V E –30 –15 –35 –20 B) –40 d M ( –25 –45 V E –30 –50 –35 –40 –30 –20 VIN (d–B10V p-p) 0 10 20 11449-081 –40 Figure 75. EVM vs. Input Voltage over Modulation Type; Filter Corner = –45 63 MHz, QPSK, 50 MSPS, Gain Code = 0000000, 1.5 V p-p Differential Output Level Maintained –50 –40 –30 –20 VIN (d–B10V p-p) 0 10 20 11449-079 –50 Q16PQSAKM Figure 73. EVM vs. Input Voltage over Symbol Rates; Filter Corner = 63 MHz, 256QAM QPSK, Gain Code = 0000000, 1.5 V p-p Differential Output Level Maintained –10 –15 –20 B) d M ( –25 V E –30 –35 –40 –45 –50 –40 –30 –20 VIN (d–B10V p-p) 0 10 20 11449-082 Figure 76. EVM vs. Input Voltage over Modulation Type; Filter Bypass Mode, QPSK, 50 MSPS, Gain Code = 0000000, 1.5 V p-p Differential Output Level Maintained Rev. A | Page 28 of 39

Data Sheet ADRF6518 Figure 77 shows EVM vs. input voltage over various digital gain 0 10MSPS settings. There is about a 1 dB spread of EVM over the gain –5 50MSPS settings. –10 0 9dB, 12dB, 12dB, 3dB –15 –5 12dB, 12dB, 12dB, 3dB 15dB, 12dB, 12dB, 3dB B) –20 –10 1155ddBB,, 1158ddBB,, 1158ddBB,, 33ddBB M (d –25 –15 1155ddBB,, 2211ddBB,, 2211ddBB,, 39ddBB EV –30 –20 B) –35 d M ( –25 –40 V E –30 –45 –35 –50 –40 –80 –70 –60 –50 –40PIN– (3d0Bm)–20 –10 0 10 20 11449-084 –45 Figure 78. EVM vs. Input Power Over Symbol Rate; QPSK, Filter Corner = –50 63 MHz, Gain Code = 0000000, 1.5 V p-p Differential Output Level –40 –30 –20 VIN (d–B10V p-p) 0 10 20 11449-083 Figure 79 shows four differeMnati nstyaminbedo l rates, with the filter in Figure 77. EVM vs. Input Voltage over Digital Gain Settings, Filter Corner = 63 MHz, QPSK, 50 MSPS, 1.5 V p-p Differential Output Level Maintained bypass mode. EVM generally improves while in filter bypass mode, especially at the higher symbol rates, due to the absence EVM SYSTEM MEASUREMENT of noise, IQ gain mismatch, IQ phase mismatch, raw group An overall EVM measurement was completed with the ADL5380 delay, and group delay mismatch, which are some dominant IQ demodulator driving the ADRF6518. The interface between sources of error that the filter adds when enabled. the two parts was dc-coupled. To achieve this, the VICM/AC 0 pin was floated to enable dc coupling mode and the VPI pin on 10MSPS –5 50MSPS the ADRF6518 was connected to 5 V to accommodate the 3.1 V –10 output common-mode voltage of the ADL5380. The RF carrier frequency applied to the RF input of the ADL5380 and the LO –15 frequency were set to 900 MHz, creating a zero intermediate –20 B) frequency (I/F). The alpha of the pulse response filter was set to d M ( –25 0.35. The RF input power to the ADL5380 was swept, and the V E –30 analog gains on the ADRF6518 were adjusted to maintain a –35 target 1.5 V p-p differential signal level on both the I and Q outputs. The VGA1 analog gain was adjusted to limit its output –40 to 1.5 V p-p (0.75 V peak on the peak detector output). The –45 filter corner was set to 63 MHz, and digital gains for VGA1, –50 V21G dAB2, ,a VnGd A3 3d,B a,n rde stpheec ptiovsetlaym. Spelvifeirearl wsiegrnea sle bt atnod 1w5i ddBth, s2, 1s idgBna, l –80 –70 –60 –50 –40PIN– (3d0Bm)–20 –10 0 10 20 11449-085 Figure 79. EVM vs. Input Power over Symbol Rate; Filter Bypass Mode, types, gains, and output levels were tested, in filter mode and in Gain Code = 0000000, 1.5 V p-p Differential Output Level Maintained filter bypass mode. Figure 80 shows the EVM for a 50 MSPS signal over several Figure 78 shows three different symbol rates: 10 MSPS, 50 MSPS, different digital modulation types while the filter is in bypass and 80 MSPS, with the filter enabled. There is a degradation of mode. Up to 256 QAM, there is an improvement to EVM, but EVM with increasing symbol rate, but at 10 MSPS, the system this is due to how EVM is calculated, rather than absolute achieves better than −40 dB of EVM for about 50 dB of the symbol error being reduced. (EVM is calculated as the ratio of input power range. The degradation of EVM at the high input the rms power of the symbol error vector to the rms average power for Figure 78 to Figure 83 is caused by the ADL5380 power of the constellation. A similar and perhaps better metric compressing. By placing an RF attenuator in front of the is modulation error ratio, or MER, which is defined as the ratio ADL5380, the user can extend the dynamic range of the system. of the rms power of the ideal symbol to the rms power of the symbol error vector.) The 1024 QAM signal starts to degrade due to the noise and distortion components impacting the closely packed symbols in the constellation. Rev. A | Page 29 of 39