ICGOO在线商城 > 集成电路(IC) > PMIC - 电压基准 > ADR421BR-REEL7

- 型号: ADR421BR-REEL7

- 制造商: Analog

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

ADR421BR-REEL7产品简介:

ICGOO电子元器件商城为您提供ADR421BR-REEL7由Analog设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 ADR421BR-REEL7价格参考。AnalogADR421BR-REEL7封装/规格:PMIC - 电压基准, Series Voltage Reference IC ±0.04% 10mA 8-SOIC。您可以下载ADR421BR-REEL7参考资料、Datasheet数据手册功能说明书,资料中有ADR421BR-REEL7 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC) |

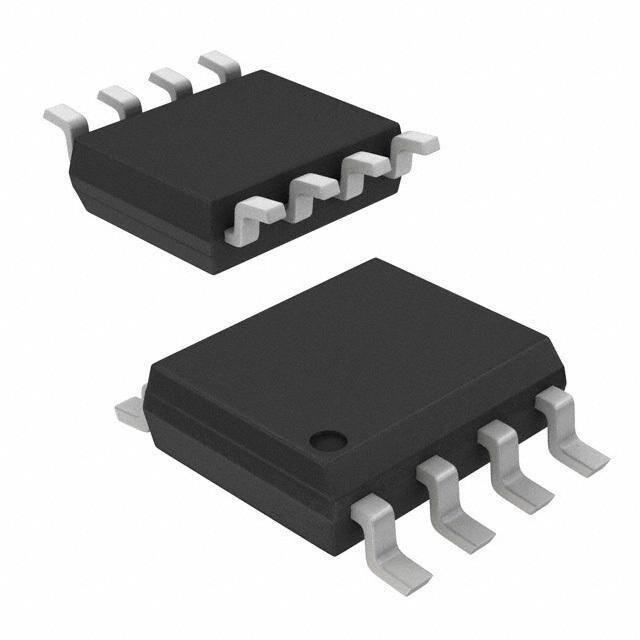

| 描述 | IC VREF SERIES PREC 2.5V 8-SOIC |

| 产品分类 | |

| 品牌 | Analog Devices Inc |

| 数据手册 | |

| 产品图片 |

|

| 产品型号 | ADR421BR-REEL7 |

| rohs | 无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | XFET® |

| 供应商器件封装 | 8-SOIC N |

| 其它名称 | ADR421BR-REEL7CT |

| 包装 | 带卷 (TR) |

| 参考类型 | 串联,精度 |

| 安装类型 | 表面贴装 |

| 容差 | ±0.04% |

| 封装/外壳 | 8-SOIC(0.154",3.90mm 宽) |

| 工作温度 | -40°C ~ 125°C |

| 标准包装 | 1 |

| 温度系数 | 3ppm/°C |

| 电压-输入 | 4.5 V ~ 18 V |

| 电压-输出 | 2.5V |

| 电流-输出 | 10mA |

| 电流-阴极 | - |

| 电流-静态 | 500µA |

| 设计资源 | 点击此处下载产品Datasheet点击此处下载产品Datasheet点击此处下载产品Datasheet点击此处下载产品Datasheet点击此处下载产品Datasheet点击此处下载产品Datasheet点击此处下载产品Datasheet点击此处下载产品Datasheet点击此处下载产品Datasheet点击此处下载产品Datasheet点击此处下载产品Datasheet |

| 通道数 | 1 |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

Ultraprecision, Low Noise, 2.048 V/2.500 V/ 3.00 V/5.00 V XFET® Voltage References Data Sheet ADR420/ADR421/ADR423/ADR425 FEATURES PIN CONFIGURATION Low noise (0.1 Hz to 10 Hz) TP 1 ADR420/ 8 TP ADR420: 1.75 μV p-p ADR421/ VIN 2 ADR423/ 7 NIC ADR421: 1.75 μV p-p NIC 3 ADR425 6 VOUT ADR423: 2.0 μV p-p TOP VIEW GND 4 (Not to Scale) 5 TRIM ADR425: 3.4 μV p-p LLoowng t-etmerpme sratatubrilei tcyo: e5f0fi pcipemnt/:1 30 p0p0 mho/°uCr s TNPIC = =T NEOST I NPTINE R(DNOA LN OCOT NCNOENCNTEIOCTN) 02432-001 Figure 1. 8-Lead SOIC, 8-Lead MSOP Load regulation: 70 ppm/mA Line regulation: 35 ppm/V GENERAL DESCRIPTION Low hysteresis: 40 ppm typical The ADR42x are a series of ultraprecision, second generation Wide operating range eXtra implanted junction FET (XFET) voltage references ADR420: 4 V to 18 V featuring low noise, high accuracy, and excellent long-term ADR421: 4.5 V to 18 V stability in SOIC and MSOP footprints. ADR423: 5 V to 18 V Patented temperature drift curvature correction technique and ADR425: 7 V to 18 V XFET technology minimize nonlinearity of the voltage change Quiescent current: 0.5 mA maximum with temperature. The XFET architecture offers superior High output current: 10 mA accuracy and thermal hysteresis to the band gap references. It Wide temperature range: −40°C to +125°C also operates at lower power and lower supply headroom than APPLICATIONS the buried Zener references. Precision data acquisition systems The superb noise and the stable and accurate characteristics High resolution converters of the ADR42x make them ideal for precision conversion Battery-powered instrumentation applications such as optical networks and medical equipment. Portable medical instruments The ADR42x trim terminal can also be used to adjust the out- Industrial process control systems put voltage over a ±0.5% range without compromising any Precision instruments other performance. The ADR42x series voltage references Optical network control circuits offer two electrical grades and are specified over the extended industrial temperature range of −40°C to +125°C. Devices have 8-lead SOIC or 30% smaller, 8-lead MSOP packages. ADR42x PRODUCTS Table 1. Initial Accuracy Model Output Voltage, V (V) mV % Temperature Coefficient (ppm/°C) OUT ADR420 2.048 1, 3 0.05, 0.15 3, 10 ADR421 2.50 1, 3 0.04, 0.12 3, 10 ADR423 3.00 1.5, 4 0.04, 0.13 3, 10 ADR425 5.00 2, 6 0.04, 0.12 3, 10 Rev. J Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Tel: 781.329.4700 ©2001–2013 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. Technical Support www.analog.com

ADR420/ADR421/ADR423/ADR425 Data Sheet TABLE OF CONTENTS Features .............................................................................................. 1 Device Power Dissipation Considerations .............................. 17 Applications ....................................................................................... 1 Basic Voltage Reference Connections ..................................... 17 Pin Configuration ............................................................................. 1 Noise Performance ..................................................................... 17 General Description ......................................................................... 1 Turn-On Time ............................................................................ 17 ADR42x Products ............................................................................. 1 Applications ..................................................................................... 18 Revision History ............................................................................... 3 Output Adjustment .................................................................... 18 Specifications ..................................................................................... 4 Reference for Converters in Optical Network Control ADR420 Electrical Specifications ............................................... 4 Circuits......................................................................................... 18 ADR421 Electrical Specifications ............................................... 5 High Voltage Floating Current Source .................................... 18 Kelvin Connections .................................................................... 19 ADR423 Electrical Specifications ............................................... 6 ADR425 Electrical Specifications ............................................... 7 Dual-Polarity References ........................................................... 19 Programmable Current Source ................................................ 20 Absolute Maximum Ratings ............................................................ 8 Thermal Resistance ...................................................................... 8 Programmable DAC Reference Voltage .................................. 20 ESD Caution .................................................................................. 8 Precision Voltage Reference for Data Converters .................. 21 Pin Configurations and Function Descriptions ........................... 9 Precision Boosted Output Regulator ....................................... 21 Typical Performance Characteristics ........................................... 10 Outline Dimensions ....................................................................... 22 Ordering Guide .......................................................................... 23 Terminology .................................................................................... 16 Theory of Operation ...................................................................... 17 Rev. J | Page 2 of 24

Data Sheet ADR420/ADR421/ADR423/ADR425 REVISION HISTORY 12/13—Rev. I to Rev. J 7/04—Rev. D to Rev. E Added θ Values to Table 7 .............................................................. 8 Changes to Ordering Guide ............................................................. 5 JC Changes to Ordering Guide ........................................................... 23 3/04—Rev. C to Rev. D 5/11—Rev. H to Rev. I Changes to Table I ............................................................................. 1 Added Endnote 1 in Table 2 ............................................................. 4 Changes to Ordering Guide ............................................................. 4 Added Endnote 1 in Table 3 ............................................................. 5 Updated Outline Dimensions........................................................ 16 Added Endnote 1 in Table 4 ............................................................. 6 1/03—Rev. B to Rev. C Added Endnote 1 in Table 5 ............................................................. 7 Changed Mini_SOIC to MSOP ........................................ Universal Deleted A Negative Precision Reference Without Precision Changes to Ordering Guide ............................................................. 4 Resistors Section .............................................................................. 17 Corrections to Y-axis labels in TPCs 21 and 24 ............................ 9 Deleted Figure 42; Renumbered Sequentially ............................. 17 Enhancement to Figure 13 ............................................................. 15 Updated Outline Dimensions ........................................................ 21 Updated Outline Dimensions........................................................ 16 Changes to Ordering Guide ........................................................... 22 3/02—Rev. A to Rev. B 6/07—Rev. G to Rev. H Edits to Ordering Guide ................................................................... 4 Changes to Table 2 ............................................................................ 3 Deletion of Precision Voltage Regulator section......................... 15 Changes to Table 3 ............................................................................ 4 Addition of Precision Boosted Output Regulator section ........ 15 Changes to Table 4 ............................................................................ 5 Addition of Figure 13 ...................................................................... 15 Changes to Table 5 ............................................................................ 6 Updated Outline Dimensions ........................................................ 21 10/01—Rev. 0 to Rev. A Changes to Ordering Guide ........................................................... 22 Addition of ADR423 and ADR425 to 6/05—Rev. F to Rev. G ADR420/ADR421 .............................................................. Universal Changes to Table 1 ............................................................................ 1 5/01—Revision 0: Initial Version Changes to Ordering Guide ........................................................... 22 2/05—Rev. E to Rev. F Updated Format.................................................................. Universal Updated Outline Dimensions ........................................................ 21 Changes to Ordering Guide ........................................................... 22 Rev. J | Page 3 of 24

ADR420/ADR421/ADR423/ADR425 Data Sheet SPECIFICATIONS ADR420 ELECTRICAL SPECIFICATIONS V = 5.0 V to 15.0 V, T = 25°C, unless otherwise noted. IN A Table 2. Parameter Symbol Conditions Min Typ Max Unit OUTPUT VOLTAGE VOUT A Grade 2.045 2.048 2.051 V B Grade 2.047 2.048 2.049 V INITIAL ACCURACY1 VOUTERR A Grade −3 +3 mV −0.15 +0.15 % B Grade −1 +1 mV −0.05 +0.05 % TEMPERATURE COEFFICIENT TCVOUT −40°C < TA < +125°C A Grade 2 10 ppm°C B Grade 1 3 ppm/°C SUPPLY VOLTAGE HEADROOM VIN − VOUT 2 V LINE REGULATION ∆VOUT/∆VIN VIN = 5 V to 18 V, 10 35 ppm/V −40°C < T < +125°C A LOAD REGULATION ∆VOUT/∆IL IL = 0 mA to 10 mA, 70 ppm/mA −40°C < T < +125°C A QUIESCENT CURRENT IIN No load 390 500 µA −40°C < T < +125°C 600 µA A VOLTAGE NOISE e p-p 0.1 Hz to 10 Hz 1.75 µV p-p N VOLTAGE NOISE DENSITY eN 1 kHz 60 nV/√Hz TURN-ON SETTLING TIME tR 10 µs LONG-TERM STABILITY ∆VOUT 1000 hours 50 ppm OUTPUT VOLTAGE HYSTERESIS VOUT_HYS 40 ppm RIPPLE REJECTION RATIO RRR f = 1 kHz −75 dB IN SHORT CIRCUIT TO GND ISC 27 mA 1 Initial accuracy does not include shift due to solder heat effect. Rev. J | Page 4 of 24

Data Sheet ADR420/ADR421/ADR423/ADR425 ADR421 ELECTRICAL SPECIFICATIONS V = 5.0 V to 15.0 V, T = 25°C, unless otherwise noted. IN A Table 3. Parameter Symbol Conditions Min Typ Max Unit OUTPUT VOLTAGE VOUT A Grade 2.497 2.500 2.503 V B Grade 2.499 2.500 2.501 V INITIAL ACCURACY1 VOUTERR A Grade −3 +3 mV −0.12 +0.12 % B Grade −1 +1 mV −0.04 +0.04 % TEMPERATURE COEFFICIENT TCVOUT −40°C < TA < +125°C A Grade 2 10 ppm/°C B Grade 1 3 ppm/°C SUPPLY VOLTAGE HEADROOM VIN − VOUT 2 V LINE REGULATION ∆VOUT/∆VIN VIN = 5 V to 18 V, 10 35 ppm/V −40°C < T < +125°C A LOAD REGULATION ∆VOUT/∆IL IL = 0 mA to 10 mA, 70 ppm/mA −40°C < T < +125°C A QUIESCENT CURRENT IIN No load 390 500 µA −40°C < T < +125°C 600 µA A VOLTAGE NOISE e p-p 0.1 Hz to 10 Hz 1.75 µV p-p N VOLTAGE NOISE DENSITY eN 1 kHz 80 nV/√Hz TURN-ON SETTLING TIME tR 10 µs LONG-TERM STABILITY ∆VOUT 1000 hours 50 ppm OUTPUT VOLTAGE HYSTERESIS VOUT_HYS 40 ppm RIPPLE REJECTION RATIO RRR f = 1 kHz −75 dB IN SHORT CIRCUIT TO GND ISC 27 mA 1 Initial accuracy does not include shift due to solder heat effect. Rev. J | Page 5 of 24

ADR420/ADR421/ADR423/ADR425 Data Sheet ADR423 ELECTRICAL SPECIFICATIONS V = 5.0 V to 15.0 V, T = 25°C, unless otherwise noted. IN A Table 4. Parameter Symbol Conditions Min Typ Max Unit OUTPUT VOLTAGE VOUT A Grade 2.996 3.000 3.004 V B Grade 2.9985 3.000 3.0015 V INITIAL ACCURACY1 VOUTERR A Grade −4 +4 mV −0.13 +0.13 % B Grade −1.5 +1.5 mV −0.04 +0.04 % TEMPERATURE COEFFICIENT TCVOUT −40°C < TA < +125°C A Grade 2 10 ppm/°C B Grade 1 3 ppm/°C SUPPLY VOLTAGE HEADROOM VIN − VOUT 2 V LINE REGULATION ∆VOUT/∆VIN VIN = 5 V to 18 V, 10 35 ppm/V −40°C < T < +125°C A LOAD REGULATION ∆VOUT/∆IL IL = 0 mA to 10 mA, 70 ppm/mA −40°C < T < +125°C A QUIESCENT CURRENT IIN No load 390 500 µA −40°C < T < +125°C 600 µA A VOLTAGE NOISE e p-p 0.1 Hz to 10 Hz 2 µV p-p N VOLTAGE NOISE DENSITY eN 1 kHz 90 nV/√Hz TURN-ON SETTLING TIME tR 10 µs LONG-TERM STABILITY ∆VOUT 1000 hours 50 ppm OUTPUT VOLTAGE HYSTERESIS VOUT_HYS 40 ppm RIPPLE REJECTION RATIO RRR f = 1 kHz −75 dB IN SHORT CIRCUIT TO GND ISC 27 mA 1 Initial accuracy does not include shift due to solder heat effect. Rev. J | Page 6 of 24

Data Sheet ADR420/ADR421/ADR423/ADR425 ADR425 ELECTRICAL SPECIFICATIONS V = 7.0 V to 15.0 V, T = 25°C, unless otherwise noted. IN A Table 5. Parameter Symbol Conditions Min Typ Max Unit OUTPUT VOLTAGE VOUT A Grade 4.994 5.000 5.006 V B Grade 4.998 5.000 5.002 V INITIAL ACCURACY1 VOUTERR A Grade −6 +6 mV −0.12 +0.12 % B Grade −2 +2 mV −0.04 +0.04 % TEMPERATURE COEFFICIENT TCVOUT A Grade −40°C < T < +125°C 2 10 ppm/°C A B Grade 1 3 ppm/°C SUPPLY VOLTAGE HEADROOM VIN − VO 2 V LINE REGULATION ∆VO/∆VIN VIN = 7 V to 18 V, 10 35 ppm/V −40°C < T < +125°C A LOAD REGULATION ∆VO/∆IL IL = 0 mA to 10 mA, 70 ppm/mA −40°C < T < +125°C A QUIESCENT CURRENT IIN No load 390 500 µA −40°C < T < +125°C 600 µA A VOLTAGE NOISE e p-p 0.1 Hz to 10 Hz 3.4 µV p-p N VOLTAGE NOISE DENSITY eN 1 kHz 110 nV/√Hz TURN-ON SETTLING TIME tR 10 µs LONG-TERM STABILITY ∆VO 1000 hours 50 ppm OUTPUT VOLTAGE HYSTERESIS VO_HYS 40 ppm RIPPLE REJECTION RATIO RRR f = 1 kHz −75 dB IN SHORT CIRCUIT TO GND ISC 27 mA 1 Initial accuracy does not include shift due to solder heat effect. Rev. J | Page 7 of 24

ADR420/ADR421/ADR423/ADR425 Data Sheet ABSOLUTE MAXIMUM RATINGS These ratings apply at 25°C, unless otherwise noted. THERMAL RESISTANCE θ is specified for the worst-case conditions, that is, θ is Table 6. JA JA specified for devices soldered in the circuit board for surface- Parameter Rating mount packages. Supply Voltage 18 V Output Short-Circuit Duration to GND Indefinite Table 7. Storage Temperature Range −65°C to +150°C Package Type θ θ Unit JA JC Operating Temperature Range −40°C to +125°C 8-Lead MSOP (RM) 190 44 °C/W Junction Temperature Range −65°C to +150°C 8-Lead SOIC (R) 130 43 °C/W Lead Temperature (Soldering, 60 sec) 300°C ESD CAUTION Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Rev. J | Page 8 of 24

Data Sheet ADR420/ADR421/ADR423/ADR425 PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS TP 1 ADR420/ 8 TP ADR421/ VIN 2 ADR423/ 7 NIC NIC 3 ADR425 6 VOUT TOP VIEW GND 4 (Not to Scale) 5 TRIM TNPIC = =T NESOT I NPTINE R(DNOA LN OCOT NCNOENCNTEIOCTN)02432-002 Figure 2. 8-Lead SOIC, 8-Lead MSOP Pin Configuration Table 8. Pin Function Descriptions Pin No. Mnemonic Description 1, 8 TP Test Pin. There are actual connections in TP pins, but they are reserved for factory testing purposes. Users should not connect anything to TP pins; otherwise, the device may not function properly. 2 VIN Input Voltage. 3, 7 NIC No Internal Connect. NICs have no internal connections. 4 GND Ground Pin = 0 V. 5 TRIM Trim Terminal. It can be used to adjust the output voltage over a ±0.5% range without affecting the temperature coefficient. 6 VOUT Output Voltage. Rev. J | Page 9 of 24

ADR420/ADR421/ADR423/ADR425 Data Sheet TYPICAL PERFORMANCE CHARACTERISTICS 2.0495 5.0025 2.0493 5.0023 2.0491 5.0021 2.0489 5.0019 2.0487 5.0017 V) V) (UT2.0485 (UT5.0015 O O V V 2.0483 5.0013 2.0481 5.0011 2.0479 5.0009 22..00447775 02432-004 55..00000075 02432-007 –40 –10 20 50 80 110 125 –40 –10 20 50 80 110 125 TEMPERATURE (°C) TEMPERATURE (°C) Figure 3. ADR420 Typical Output Voltage vs. Temperature Figure 6. ADR425 Typical Output Voltage vs. Temperature 2.5015 0.55 2.5013 0.50 2.5011 +125°C 2.5009 mA)0.45 2.5007 NT ( (V)UT2.5005 URRE0.40 +25°C VO2.5003 Y C PPL0.35 –40°C 2.5001 U S 2.4999 0.30 22..44999975 02432-005 0.25 02432-008 –40 –10 20 50 80 110 125 4 6 8 10 12 14 15 TEMPERATURE (°C) INPUT VOLTAGE (V) Figure 4. ADR421 Typical Output Voltage vs. Temperature Figure 7. ADR420 Supply Current vs. Input Voltage 3.0010 0.55 3.0008 0.50 3.0006 3.0004 mA)0.45 3.0002 NT ( +125°C (V)UT3.0000 URRE0.40 VO2.9998 Y C PPL0.35 +25°C 2.9996 U S 2.9994 –40°C 0.30 22..99999920 02432-006 0.25 02432-009 –40 –10 20 50 80 110 125 4 6 8 10 12 14 15 TEMPERATURE (°C) INPUT VOLTAGE (V) Figure 5. ADR423 Typical Output Voltage vs. Temperature Figure 8. ADR421 Supply Current vs. Input Voltage Rev. J | Page 10 of 24

Data Sheet ADR420/ADR421/ADR423/ADR425 0.55 70 IL = 0mATO 5mA 60 0.50 +125°C mA) UPPLY CURRENT (mA)000...443505 +25°C D REGULATION (ppm/ 54320000 VIN = V5IVN = 6.5V S –40°C A O L 0.30 10 0.25 02432-010 0 02432-013 4 6 8 10 12 14 15 –40 –10 20 50 80 110 125 INPUT VOLTAGE (V) TEMPERATURE (°C) Figure 9. ADR423 Supply Current vs. Input Voltage Figure 12. ADR421 Load Regulation vs. Temperature 0.55 70 IL = 0mATO 10mA 60 0.50 A) m UPPLY CURRENT (mA)000...443505 ++12255°°CC D REGULATION (ppm/ 54320000 VIN = V7IVN = 15V S –40°C OA L 0.30 10 0.25 02432-011 0 02432-014 6 8 10 12 14 15 –40 –10 20 50 80 110 125 INPUT VOLTAGE (V) TEMPERATURE (°C) Figure 10. ADR425 Supply Current vs. Input Voltage Figure 13. ADR423 Load Regulation vs. Temperature 70 35 IL = 0mATO 5mA VILI N= =0 m15AVTO 10mA 60 30 A) A) m m m/ 50 m/ 25 p p p p N ( 40 N ( 20 O O LATI VIN = 6V VIN = 4.5V LATI U 30 U 15 G G E E R R D 20 D 10 A A O O L L 10 5 0 02432-012 0 02432-015 –40 –10 20 50 80 110 125 –40 –10 20 50 80 110 125 TEMPERATURE (°C) TEMPERATURE (°C) Figure 11. ADR420 Load Regulation vs. Temperature Figure 14. ADR425 Load Regulation vs. Temperature Rev. J | Page 11 of 24

ADR420/ADR421/ADR423/ADR425 Data Sheet 6 14 VIN = 4.5VTO 15V VIN = 7.5VTO 15V 12 5 V) V) m/ m/ 10 p 4 p p p ON ( ON ( 8 ATI 3 ATI L L U U 6 G G E E NE R 2 NE R 4 LI LI 1 2 0 02432-016 0 02432-019 –40 –10 20 50 80 110 125 –40 –10 20 50 80 110 125 TEMPERATURE (°C) TEMPERATURE (°C) Figure 15. ADR420 Line Regulation vs. Temperature Figure 18. ADR425 Line Regulation vs. Temperature 6 2.5 VIN = 5VTO 15V 5 2.0 m/V) E (V) –40°C p 4 G p A +25°C N ( LT1.5 O O LATI 3 AL V +85°C U TI G N1.0 E E LINE R 2 DIFFER 0.5 1 0 02432-017 0 02432-020 –40 –10 20 50 80 110 125 0 1 2 3 4 5 TEMPERATURE (°C) LOAD CURRENT (mA) Figure 16. ADR421 Line Regulation vs. Temperature Figure 19. ADR420 Minimum Input/Output Voltage Differential vs. Load Current 9 2.5 VIN = 5VTO 15V 8 2.0 m/V) 7 E (V) –40°C p 6 G p A +25°C N ( LT1.5 O 5 O ULATI 4 TIAL V +125°C G N1.0 E E LINE R 32 DIFFER 0.5 10 02432-018 0 02432-021 –40 –10 20 50 80 110 0 1 2 3 4 5 TEMPERATURE (°C) LOAD CURRENT (mA) Figure 17. ADR423 Line Regulation vs. Temperature Figure 20. ADR421 Minimum Input/Output Voltage Differential vs. Load Current Rev. J | Page 12 of 24

Data Sheet ADR420/ADR421/ADR423/ADR425 2.5 2.0 V) E ( –40°C G VOLTA1.5 +25°C DIV L +125°C V/ A µ TI 1 N1.0 E R E F F DI 0.5 0 02432-022 02432-025 0 1 2 3 4 5 TIME (1s/DIV) LOAD CURRENT (mA) Figure 21. ADR423 Minimum Input/Output Voltage Figure 24. ADR421 Typical Noise Voltage 0.1 Hz to 10 Hz Differential vs. Load Current 2.5 2.0 V) E ( –40°C G A +25°C LT1.5 V TIAL VO +125°C 50µV/DI N1.0 E R E F F DI 0.5 0 02432-023 02432-026 0 1 2 3 4 5 TIME (1s/DIV) LOAD CURRENT (mA) Figure 22. ADR425 Minimum Input/Output Voltage Figure 25. Typical Noise Voltage 10 Hz to 10 kHz Differential vs. Load Current 30 1k TEMPERATURE SAMPLE SIZE – 160 +25°C –40°C +125°C +25°C 25 Hz) V/ n TS 20 Y ( PAR NSIT ADR425ADR423 F E O 15 D100 R E E S B OI NUM 10 GE N ADR420 ADR421 A T L 5 VO 0 02432-024 10 02432-027 –100–90–80–70–60–50–40–30–20–100102030405060708090100110120130MORE 10 100FREQUENCY (Hz)1k 10k DEVIATION (ppm) Figure 23. ADR421 Typical Hysteresis Figure 26. Voltage Noise Density vs. Frequency Rev. J | Page 13 of 24

ADR420/ADR421/ADR423/ADR425 Data Sheet CBYPASS = 0µF LINE INTERRUPTION CL = 100nF 1mA LOAD VOUT 1V/DIV VIN 500mV/DIV LOAD OFF VOUT 500mV/DIV LOAD ON 2V/DIV 02432-028 02432-031 TIME (100µs/DIV) TIME (100µs/DIV) Figure 27. ADR421 Line Transient Response, no CBYPASS Figure 30. ADR421 Load Transient Response, CL = 100 nF CBYPASS = 0.1µF CNOIN L=O 0A.0D1µF LINE INTERRUPTION VOUT VIN 500mV/DIV 2V/DIV VIN VOUT 500mV/DIV 2V/DIV 02432-029 02432-032 TIME (100µs/DIV) TIME (4µs/DIV) Figure 28. ADR421 Line Transient Response, CBYPASS = 0.1 μF Figure 31. ADR421 Turn-Off Response CL = 0µF 1mA LOAD CNOIN L=O 0A.0D1µF VOUT 1V/DIV 2V/DIV VOUT LOAD OFF 2V/DIV 2V/DIV LOAD ON VIN 02432-030 02432-033 TIME (100µs/DIV) TIME (4µs/DIV) Figure 29. ADR421 Load Transient Response, no CL Figure 32. ADR421 Turn-On Response Rev. J | Page 14 of 24

Data Sheet ADR420/ADR421/ADR423/ADR425 CL = 0.01µF 50 NO INPUT CAP 45 VOUT 40 2V/DIV E (Ω) 35 C N 30 A VIN PED 25 ADR425 M T I 20 ADR423 U UTP 15 ADR421 O 2V/DIV 10 02432-034 50 ADR420 02432-037 TIME (4µs/DIV) 10 100 1k 10k 100k FREQUENCY (Hz) Figure 33. ADR421 Turn-Off Response Figure 36. Output Impedance vs. Frequency CL = 0.01µF 0 NO INPUT CAP –10 2V/DIV –20 VOUT dB)–30 N ( O–40 TI C E–50 J 2V/DIV E RE–60 L P P–70 RI VIN –80 02432-035 –1–0900 02432-038 TIME (4µs/DIV) 10 100 1k 10k 100k 1M FREQUENCY (Hz) Figure 34. ADR421 Turn-On Response Figure 37. Ripple Rejection vs. Frequency CBYPASS = 0.1µF RL = 500Ω CL = 0 VOUT 5V/DIV VIN 2V/DIV 02432-036 TIME (100µs/DIV) Figure 35. ADR421 Turn-On/Turn-Off Response Rev. J | Page 15 of 24

ADR420/ADR421/ADR423/ADR425 Data Sheet TERMINOLOGY Temperature Coefficient Thermal Hysteresis The change of output voltage over the operating temperature The change of output voltage after the device is cycled through range is normalized by the output voltage at 25°C, and temperatures from +25°C to −40°C to +125°C and back to expressed in ppm/°C as +25°C. This is a typical value from a sample of parts put V T V T through such a cycle. TCV ppm/C OUT 2 OUT 1 106 OUT VOUT25CT2 T1 VOUT_HYS VOUT25CVOUT_TC where: V ppm VOUT25CVOUT_TC 106 VOUT (25°C) = VOUT at 25°C. OUT_HYS VOUT25C V (T) = V at Temperature 1. OUT 1 OUT where: V (T) = V at Temperature 2. OUT 2 OUT V (25°C) = V at 25°C. OUT OUT Line Regulation V = V at 25°C after temperature cycle at +25°C to OUT_TC OUT The change in output voltage due to a specified change in input −40°C to +125°C and back to +25°C. voltage. It includes the effects of self-heating. Line regulation is Input Capacitor expressed in either percent per volt, parts per million per volt, Input capacitors are not required on the ADR42x. There is or microvolts per volt change in input voltage. no limit for the value of the capacitor used on the input, but a Load Regulation 1 μF to 10 μF capacitor on the input improves transient response The change in output voltage due to a specified change in load in applications where the supply suddenly changes. An addi- current. It includes the effects of self-heating. Load regulation is tional 0.1 μF capacitor in parallel also helps to reduce noise expressed in either microvolts per milliampere, parts per from the supply. million per milliampere, or ohms of dc output resistance. Output Capacitor Long-Term Stability The ADR42x do not need output capacitors for stability under Typical shift of output voltage at 25°C on a sample of parts any load condition. An output capacitor, typically 0.1 μF, filters subjected to operation life test of 1000 hours at 125°C. out any low level noise voltage and does not affect the operation V V t V t of the part. On the other hand, the load transient response can OUT OUT 0 OUT 1 be improved with an additional 1 μF to 10 μF output capacitor V t V t V ppm OUT 0 OUT 1 106 in parallel. A capacitor here acts as a source of stored energy for OUT V t sudden increase in load current. The only parameter that OUT 0 degrades by adding an output capacitor is the turn-on time, where: which depends on the size of the selected capacitor. V (t) = V at 25°C at Time 0. OUT 0 OUT V (t) = V at 25°C after 1000 hours operation at 125°C. OUT 1 OUT Rev. J | Page 16 of 24

Data Sheet ADR420/ADR421/ADR423/ADR425 THEORY OF OPERATION The ADR42x series of references uses a reference generation DEVICE POWER DISSIPATION CONSIDERATIONS technique known as XFET (eXtra implanted junction FET). The ADR42x family of references is guaranteed to deliver load This technique yields a reference with low supply current, good currents to 10 mA with an input voltage that ranges from 4.5 V thermal hysteresis, and exceptionally low noise. The core of the to 18 V. When these devices are used in applications at higher XFET reference consists of two junction field-effect transistors currents, the following equation should be used to account for (JFET), one having an extra channel implant to raise its pinch- the temperature effects due to power dissipation increases: off voltage. By running the two JFETs at the same drain current, T = P × θ + T (2) the difference in pinch-off voltage can be amplified and used to J D JA A form a highly stable voltage reference. where: T and T are the junction temperature and the ambient The intrinsic reference voltage is about 0.5 V with a negative J A temperature, respectively. temperature coefficient of about −120 ppm/°C. This slope is P is the device power dissipation. essentially constant to the dielectric constant of silicon and can D θ is the device package thermal resistance. be closely compensated by adding a correction term generated JA in the same fashion as the proportional-to-temperature (PTAT) BASIC VOLTAGE REFERENCE CONNECTIONS term used to compensate band gap references. The primary Voltage references, in general, require a bypass capacitor advantage over a band gap reference is that the intrinsic tem- connected from V to GND. The circuit in Figure 39 OUT perature coefficient is approximately 30 times lower (therefore illustrates the basic configuration for the ADR42x family of requiring less correction). This results in much lower noise references. Other than a 0.1 µF capacitor at the output to help because most of the noise of a band gap reference comes from improve noise suppression, a large output capacitor at the the temperature compensation circuitry. output is not required for circuit stability. Figure 38 shows the basic topology of the ADR42x series. The TP 1 ADR420/ 8 TP temperature correction term is provided by a current source ADR421/ with a value designed to be proportional to absolute tempera- VIN + 2 ADR423/ 7 NIC ture. The general equation is 10µF 0.1µF NIC 3 ADR425 6 OUTPUT TOP VIEW 0.1µF 4 (Not to Scale) 5 TRIM V = G × (∆V − R1 × I ) (1) where:O UT P PTAT TNPIC = =T NESOT I NPTINE R(DNOA LN OCOT NCNOENCNTEIOCTN) 02432-040 G is the gain of the reciprocal of the divider ratio. Figure 39. Basic Voltage Reference Configuration ∆V is the difference in pinch-off voltage between the two JFETs. P NOISE PERFORMANCE I is the positive temperature coefficient correction current. PTAT The noise generated by ADR42x references is typically less Each ADR42x device is created by on-chip adjustment of R2 than 2 µV p-p over the 0.1 Hz to 10 Hz band for the ADR420, and R3 to achieve the specified reference output. ADR421, and ADR423. Figure 24 shows the 0.1 Hz to 10 Hz I1 I1 VIN noise of the ADR421, which is only 1.75 µV p-p. The noise ADR420/ADR421/ IPTAT ADR423/ADR425 measurement is made with a band-pass filter made of a 2-pole high-pass filter with a corner frequency at 0.1 Hz and a 2-pole VOUT low-pass filter with a corner frequency at 10 Hz. R2 TURN-ON TIME * At power-up (cold start), the time required for the output ΔVP R1 R3 voltage to reach its final value within a specified error band is defined as the turn-on settling time. Two components typi- *EVXOTUTR A= GCH(ΔAVNPN –E RL1 I M× PIPLTAANT)T GND 02432-039 cseatltlyle a asnsodc tihatee tdim weit fho rth tihse a trhe etrhme atilm grea fdoire nthtse oanct tihvee ccihricpu ittos to Figure 38. Simplified Schematic stabilize. Figure 31 to Figure 35 show the turn-on settling time for the ADR421. Rev. J | Page 17 of 24

ADR420/ADR421/ADR423/ADR425 Data Sheet APPLICATIONS OUTPUT ADJUSTMENT SOURCE FIBER GIMBAL + SENSOR The ADR42x trim terminal can be used to adjust the output DESTINATION LASER BEAM FIBER voltage over a ±0.5% range. This feature allows the system designer to trim system errors out by setting the reference to ACTIVATOR ACTIVATOR MEMS MIRROR RIGHT a voltage other than the nominal. This is also helpful if the LEFT part is used in a system at temperature to trim out any error. Adjustment of the output has a negligible effect on the AMPL PREAMP AMPL temperature performance of the device. To avoid degrading temperature coefficients, both the trimming potentiometer ADR421 and the two resistors need to be low temperature coefficient CONTROL ELECTRONICS ADR421 types, preferably <100 ppm/°C. DAC ADC DAC ADR421 INPUT V2IN VOUT 6 OVOUUTTP =U T±0.5% Figure 41. All ODpStPical Router Network 02432-042 ADR420/ ADR421/ HIGH VOLTAGE FLOATING CURRENT SOURCE ADR423/ ADR425 R1 The circuit in Figure 42 can be used to generate a floating GND TRIM 5 470kΩ R10PkΩ current source with minimal self-heating. This particular 4 R2 10kΩ (ADR420) configuration can operate on high supply voltages determined 15kΩ (ADR421) 02432-041 by the breakdown voltage of the N-channel JFET. Figure 40. Output Trim Adjustment +VS REFERENCE FOR CONVERTERS IN OPTICAL SST111 VISHAY NETWORK CONTROL CIRCUITS 2 In the high capacity, all optical router network of Figure 41, VIN arrays of micromirrors direct and route optical signals from ADR420/ ADR421/ fiber to fiber, without first converting them to electrical form, ADR423/ which reduces the communication speed. The tiny micro- ADR425 mechanical mirrors are positioned so that each is illuminated VOUT 6 OP09 2N3904 by a single wavelength that carries unique information and GND can be passed to any desired input and output fiber. The mirrors 4 are tilted by the dual-axis actuators controlled by precision RL 2.10kΩ caonnalvoegr-tteors-d (iDgAitaCl sc)o wnvitehritne rtsh (eA sDysCtesm) a. nDdu de itgoi ttahl-et om-aicnraolsocgo pic –VS 02432-044 movement of the mirrors, not only is the precision of the Figure 42. High Voltage Floating Current Source converters important, but the noise associated with these controlling converters is extremely critical, because total noise within the system can be multiplied by the numbers of converters used. Consequently, the exceptional low noise of the ADR42x is necessary to maintain the stability of the control loop for this application. Rev. J | Page 18 of 24

Data Sheet ADR420/ADR421/ADR423/ADR425 KELVIN CONNECTIONS DUAL-POLARITY REFERENCES In many portable instrumentation applications where PC board Dual-polarity references can easily be made with an op amp and cost and area are important considerations, circuit intercon- a pair of resistors. In order not to defeat the accuracy obtained nects are often narrow. These narrow lines can cause large by the ADR42x, it is imperative to match the resistance toler- voltage drops if the voltage reference is required to provide load ance and the temperature coefficient of all components. currents to various functions. In fact, a circuit’s interconnects VIN can exhibit a typical line resistance of 0.45 mΩ/square (1 oz. Cu, 1µF 0.1µF 2 for example). Force and sense connections, also referred to as VIN VOUT 6 +5V R1 R2 Kelvin connections, offer a convenient method of eliminating U1 10kΩ 10kΩ the effects of voltage drops in circuit wires. Load currents flow- ADR425 +10V ing through wiring resistance produce an error (V = R × I) ERROR L GND TRIM 5 V+ at the load. However, the Kelvin connection in Figure 43 U2 4 OP1177 –5V overcomes the problem by including the wiring resistance wseinthseins tthhee lfooardci nvogl ltoagoep, oofp t ahme opp l oaompp c. oBnetcraoul sfoe rtchees othpe a omuptp ut to 5kRΩ3 –1V0–V 02432-046 compensate for the wiring error and to produce the correct Figure 44. +5 V and −5 V Reference Using ADR425 voltage at the load. VIN +2.5V 2 +10V ADR420/ RLW VOUT 2 ADR421/ VIN SENSE VIN VOUT 6 ADR423/ ADRV4O2U5T 6 A1 RLW VFOOURTCE ADUR1425 5.6kRΩ1 GND GND TRIM 5 4 A1 = OP191 RL 02432-045 4 5.6kRΩ2 UV2+ Figure 43. Advantage of Kelvin Connection OP1177 V– –2.5V –10V 02432-047 Figure 45. +2.5 V and −2.5 V Reference Using ADR425 Rev. J | Page 19 of 24

ADR420/ADR421/ADR423/ADR425 Data Sheet PROGRAMMABLE CURRENT SOURCE PROGRAMMABLE DAC REFERENCE VOLTAGE Together with a digital potentiometer and a Howland current With a multichannel DAC, such as the quad, 12-bit voltage pump, the ADR425 forms the reference source for a program- output AD7398, one of its internal DACs, and an ADR42x mable current as voltage reference can be used as a common programmable V x for the rest of the DACs. The circuit configuration is R2 + R2 REF A B shown in Figure 47. The relationship of V x to V depends REF REF R1 I = ×V (3) on the digital code and the ratio of R1 and R, and is given by L W R2 B R2 V ×1+ and REF R1 V x = (5) D REF D R2 VW = ×V (4) 1+ × 2N REF 2N R1 where: where: D is the decimal equivalent of the input code. D is the decimal equivalent of input code. N is the number of bits. N is the number of bits. 1C0p1F VREF is the applied external reference. V x is the reference voltage for DACs A to D. REF VDD R1' R2' 50kΩ 1kΩ Table 9. V x vs. R1 and R2 REF V2IN TRIM 5 VDD R1, R2 Digital Code VREF U1 AD5232 V+ R1 = R2 0000 0000 0000 2 VREF GANDDRV4O2U5T 6 DIGITAUA2L POT VDD 1C0p2F OVP–A22177R2B RR11 == RR22 11010101 01010101 01010101 1V.R3EF V REF 4 U2B W OVPA+21177 VSS 10Ω RR11 == 33RR22 10000000 00000000 00000000 41 .V6 RVEFR EF R1 R2A V– 50kΩ 1kΩ R1 = 3R2 1111 1111 1111 VREF VSS VL LOAD IL 02432-048 Figure 46. Programmable Current Source R2 R1' and R2' must be equal to R1 and R2A + R2B, respectively. VREFA VOUTA ±0R.11% ±0.1% Theoretically, R2B can be made as small as needed to achieve DACA VREF the current needed within A2 output current driving capability. VIN ADR425 In the example shown in Figure 46, OP2177 is able to deliver a maximum of 10 mA. Because the current pump uses both VREFB VOUTB VOB = VREFx (DB) positive and negative feedback, capacitors C1 and C2 are needed DACB to ensure that negative feedback prevails and, therefore, avoiding oscillation. This circuit also allows bidirectional current flow if VREFC VOUTC the inputs VA and VB of the digital potentiometer are supplied DACC VOC = VREFx (DC) with the dual-polarity references as previously shown. VREFD VOUTD VOD = VREFx (DD) DACD AD7398 02432-049 Figure 47. Programmable DAC Reference Rev. J | Page 20 of 24

Data Sheet ADR420/ADR421/ADR423/ADR425 PRECISION VOLTAGE REFERENCE FOR DATA PRECISION BOOSTED OUTPUT REGULATOR CONVERTERS A precision voltage output with boosted current capability The ADR42x family has a number of features that make it ideal can be realized with the circuit shown in Figure 49. In this for use with ADCs and DACs. The exceptionally low noise, circuit, U2 forces VOUT to be equal to VREF by regulating the turn tight temperature coefficient, and high accuracy characteristics on of N1. Therefore, the load current is furnished by VIN. In make the ADR42x ideal for low noise applications such as this configuration, a 50 mA load is achievable at VIN of 5 V. cellular base station applications. Moderate heat is generated on the MOSFET, and higher current can be achieved by replacing the larger device. In addition, for AD7701 is an example of an ADC that is well suited for the a heavy capacitive load with step input, a buffer may be added ADR42x. The ADR421 is used as the precision reference for at the output to enhance the transient response. the converter in Figure 48. The AD7701 is a 16-bit ADC with on-chip digital filtering intended for measuring wide dynamic N1 range and low frequency signals, such as those representing VIN VOUT RL chemical, physical, or biological processes. It contains a charge- 2 U1 5V 25Ω balancing (Σ-∆) ADC, calibration microcontroller with on-chip VIN 2N7002 static RAM, clock oscillator, and serial communications port. VOUT 6 + V+ ADR421 U2 +5V 5 AD8601 ANALOG TRIM SUPPLY 0.1µF 10µF AVDD AD7701DVDD GND4 – V– 02432-051 Figure 49. Precision Boosted Output Regulator SLEEP 0.1µF VIN MODE VOUT VREF 0.1µF ADR420/ DRDY DATA READY ADR421/ CS READ (TRANSMIT) ADR423/ ADR425 SCLK SERIAL CLOCK SDATA SERIAL CLOCK GND CLKIN RANGES BP/UP SELECT CLKOUT CALIBRATE CAL SC1 ANIANLPOUGT AIN SC2 GARNOALUONGD AGND DGND 0.1µF 0.1µF AVSS DVSS –5V ANALOG SUPPLY 0.1µF 10µF 02432-050 Figure 48. Voltage Reference for 16-Bit ADC AD7701 Rev. J | Page 21 of 24

ADR420/ADR421/ADR423/ADR425 Data Sheet OUTLINE DIMENSIONS 5.00(0.1968) 4.80(0.1890) 8 5 4.00(0.1574) 6.20(0.2441) 3.80(0.1497) 1 4 5.80(0.2284) 1.27(0.0500) 0.50(0.0196) BSC 1.75(0.0688) 0.25(0.0099) 45° 0.25(0.0098) 1.35(0.0532) 8° 0.10(0.0040) 0° COPLANARITY 0.51(0.0201) 0.10 SEATING 0.31(0.0122) 0.25(0.0098) 10..2470((00..00510507)) PLANE 0.17(0.0067) COMPLIANTTOJEDECSTANDARDSMS-012-AA C(RINOEFNPEATRRREOENNLCLTEIHNEOGSNDELISYM)AEANNRDSEIAORRNOESUNANORDEETDAIN-POMPFRIFLOLMPIMIRLELIATIMTEEERTFSEO;RIRNECUQHSUEDIVIINMAELDENENSSTIIOGSNNFS.OR 012407-A Figure 50. 8-Lead Standard Small Outline Package [SOIC_N] Narrow Body (R-8) Dimensions shown in millimeters and (inches) 3.20 3.00 2.80 8 5 5.15 3.20 4.90 3.00 4.65 2.80 1 4 PIN 1 IDENTIFIER 0.65 BSC 0.95 15° MAX 0.85 1.10 MAX 0.75 0.80 0.15 0.40 6° 0.23 0.55 CO0P.0L50A.1N0ARICTOYMPLIANT0. 2T5O JEDEC STA0°NDARDS 0M.0O9-187-AA 0.40 10-07-2009-B Figure 51. 8-Lead Mini Small Outline Package [MSOP] (RM-8) Dimensions shown in millimeters Rev. J | Page 22 of 24

Data Sheet ADR420/ADR421/ADR423/ADR425 ORDERING GUIDE Output Initial Temperature Voltage, Accuracy Coefficient Temperature Package Package Model1 V (V) mV % (ppm/°C) Range Description Option Branding OUT ADR420ARZ 2.048 3 0.15 10 −40°C to +125°C 8-Lead SOIC_N R-8 ADR420ARZ-REEL7 2.048 3 0.15 10 −40°C to +125°C 8-Lead SOIC_N R-8 ADR420ARMZ 2.048 3 0.15 10 −40°C to +125°C 8-Lead MSOP RM-8 L0C ADR420ARMZ-REEL7 2.048 3 0.15 10 −40°C to +125°C 8-Lead MSOP RM-8 L0C ADR420BRZ 2.048 1 0.05 3 −40°C to +125°C 8-Lead SOIC_N R-8 ADR420BRZ-REEL7 2.048 1 0.05 3 −40°C to +125°C 8-Lead SOIC_N R-8 ADR421ARZ 2.50 3 0.12 10 −40°C to +125°C 8-Lead SOIC_N R-8 ADR421ARZ-REEL7 2.50 3 0.12 10 −40°C to +125°C 8-Lead SOIC_N R-8 ADR421ARMZ 2.50 3 0.12 10 −40°C to +125°C 8-Lead MSOP RM-8 R06 ADR421ARMZ-REEL7 2.50 3 0.12 10 −40°C to +125°C 8-Lead MSOP RM-8 R06 ADR421BR 2.50 1 0.04 3 −40°C to +125°C 8-Lead SOIC_N R-8 ADR421BR-REEL7 2.50 1 0.04 3 −40°C to +125°C 8-Lead SOIC_N R-8 ADR421BRZ 2.50 1 0.04 3 −40°C to +125°C 8-Lead SOIC_N R-8 ADR421BRZ-REEL7 2.50 1 0.04 3 −40°C to +125°C 8-Lead SOIC_N R-8 ADR423ARZ 3.00 4 0.13 10 −40°C to +125°C 8-Lead SOIC_N R-8 ADR423ARZ-REEL7 3.00 4 0.13 10 −40°C to +125°C 8-Lead SOIC_N R-8 ADR423ARMZ 3.00 4 0.13 10 −40°C to +125°C 8-Lead MSOP RM-8 R0U ADR423ARMZ-REEL7 3.00 4 0.13 10 −40°C to +125°C 8-Lead MSOP RM-8 R0U ADR423BRZ 3.00 1.5 0.04 3 −40°C to +125°C 8-Lead SOIC_N R-8 ADR423BRZ-REEL7 3.00 1.5 0.04 3 −40°C to +125°C 8-Lead SOIC_N R-8 ADR425ARZ 5.00 6 0.12 10 −40°C to +125°C 8-Lead SOIC_N R-8 ADR425ARZ-REEL7 5.00 6 0.12 10 −40°C to +125°C 8-Lead SOIC_N R-8 ADR425ARMZ 5.00 6 0.12 10 −40°C to +125°C 8-Lead MSOP RM-8 R7A# ADR425ARMZ-REEL7 5.00 6 0.12 10 −40°C to +125°C 8-Lead MSOP RM-8 R7A# ADR425BRZ 5.00 2 0.04 3 −40°C to +125°C 8-Lead SOIC_N R-8 ADR425BRZ-REEL7 5.00 2 0.04 3 −40°C to +125°C 8-Lead SOIC_N R-8 1 Z = RoHS Compliant Part. # denotes RoHS-compliant product may be top or bottom marked. Rev. J | Page 23 of 24

ADR420/ADR421/ADR423/ADR425 Data Sheet NOTES ©©22000011––22001133 AAnnaalloogg DDeevviicceess,, IInncc.. AAllll rriigghhttss rreesseerrvveedd.. TTrraaddeemmaarrkkss aanndd rreeggiisstteerreedd ttrraaddeemmaarrkkss aarree tthhee pprrooppeerrttyy ooff tthheeiirr rreessppeeccttiivvee oowwnneerrss.. DD0022443322--00--1122//1133((JJ)) Rev. J | Page 24 of 24

Datasheet下载

Datasheet下载