ICGOO在线商城 > 集成电路(IC) > PMIC - 稳压器 - 线性 > ADP7104ARDZ-1.8-R7

- 型号: ADP7104ARDZ-1.8-R7

- 制造商: Analog

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

ADP7104ARDZ-1.8-R7产品简介:

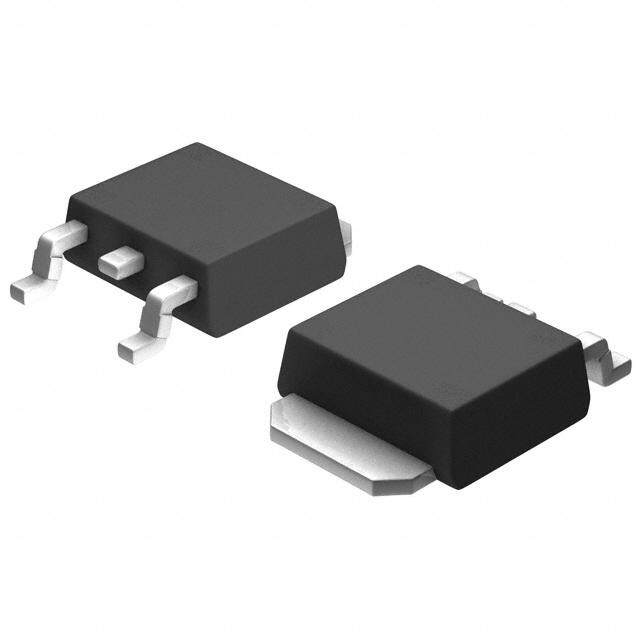

ICGOO电子元器件商城为您提供ADP7104ARDZ-1.8-R7由Analog设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 ADP7104ARDZ-1.8-R7价格参考¥25.84-¥41.27。AnalogADP7104ARDZ-1.8-R7封装/规格:PMIC - 稳压器 - 线性, Linear Voltage Regulator IC Positive Fixed 1 Output 1.8V 500mA 8-SOIC-EP。您可以下载ADP7104ARDZ-1.8-R7参考资料、Datasheet数据手册功能说明书,资料中有ADP7104ARDZ-1.8-R7 详细功能的应用电路图电压和使用方法及教程。

ADP7104ARDZ-1.8-R7 是由 Analog Devices Inc. 生产的一款线性稳压器(PMIC),属于低噪声、低压差 (LDO) 稳压器系列。该型号的典型应用场景包括: 1. 消费电子设备 - 智能手机和平板电脑:这些设备需要稳定的电源供应来确保处理器、传感器和其他组件的正常工作。ADP7104ARDZ-1.8-R7 提供了低噪声和高精度的电压输出,适用于为这些设备中的敏感电路供电。 - 便携式音频设备:如蓝牙耳机、智能音箱等,对电源噪声非常敏感,尤其是在音频信号处理部分。ADP7104ARDZ-1.8-R7 的低噪声特性可以有效减少音频失真,提升音质。 2. 通信设备 - 基站和无线模块:在通信系统中,射频 (RF) 电路对电源噪声非常敏感。ADP7104ARDZ-1.8-R7 的低噪声性能有助于提高 RF 信号的质量,减少干扰,确保通信的稳定性和可靠性。 - 物联网 (IoT) 设备:许多 IoT 设备依赖电池供电,且要求长时间运行。ADP7104ARDZ-1.8-R7 的低压差特性可以延长电池寿命,同时保持稳定的电压输出,适用于各种传感器、微控制器和无线模块。 3. 工业自动化 - 传感器和数据采集系统:工业环境中使用的传感器和数据采集系统通常需要高精度的电源供应。ADP7104ARDZ-1.8-R7 可以为这些设备提供稳定的电源,确保测量结果的准确性。 - PLC 和嵌入式控制系统:可编程逻辑控制器 (PLC) 和其他嵌入式控制系统需要可靠的电源管理,以确保系统的稳定运行。ADP7104ARDZ-1.8-R7 的高可靠性和稳定性使其成为这些应用的理想选择。 4. 医疗设备 - 便携式医疗设备:如血糖仪、心率监测器等,这些设备通常依赖电池供电,并且对电源噪声非常敏感。ADP7104ARDZ-1.8-R7 的低噪声和高精度特性可以确保这些设备的测量结果准确无误。 - 植入式医疗设备:如心脏起搏器等,要求极高的电源稳定性。ADP7104ARDZ-1.8-R7 的低功耗和高可靠性使其适合用于这些关键应用。 总结 ADP7104ARDZ-1.8-R7 以其低噪声、低压差和高精度的特点,广泛应用于消费电子、通信设备、工业自动化和医疗设备等领域,特别是在对电源质量和稳定性有严格要求的应用场景中表现出色。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC)半导体 |

| 描述 | IC REG LDO 1.8V 0.5A 8SOIC低压差稳压器 20V 500mA CMOS LDO Low Noise |

| 产品分类 | |

| 品牌 | Analog Devices Inc |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 电源管理 IC,低压差稳压器,Analog Devices ADP7104ARDZ-1.8-R7- |

| 数据手册 | |

| 产品型号 | ADP7104ARDZ-1.8-R7 |

| PSRR/纹波抑制—典型值 | 50 dB |

| 产品种类 | 低压差稳压器 |

| 供应商器件封装 | 8-SOIC-EP |

| 其它名称 | ADP7104ARDZ-1.8-R7-ND |

| 包装 | 带卷 (TR) |

| 商标 | Analog Devices |

| 回动电压—最大值 | 550 mV |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装 | Reel |

| 封装/外壳 | 8-SOIC(0.154",3.90mm 宽)裸焊盘 |

| 封装/箱体 | SOIC-8 |

| 工作温度 | -40°C ~ 85°C |

| 工厂包装数量 | 1000 |

| 最大工作温度 | + 125 C |

| 最大输入电压 | 20 V |

| 最小工作温度 | - 40 C |

| 最小输入电压 | 3.3 V |

| 标准包装 | 1,000 |

| 电压-跌落(典型值) | - |

| 电压-输入 | 3.3 V ~ 20 V |

| 电压-输出 | 1.8V |

| 电流-输出 | 500mA |

| 电流-限制(最小值) | 625mA |

| 稳压器拓扑 | 正,固定式 |

| 稳压器数 | 1 |

| 系列 | ADP7104 |

| 线路调整率 | +/- 0.015 % / V |

| 视频文件 | http://www.digikey.cn/classic/video.aspx?PlayerID=1364138032001&width=640&height=505&videoID=2245193149001 |

| 负载调节 | 0.2 % / A |

| 输出电压 | 1.8 V |

| 输出电流 | 500 mA |

| 输出端数量 | 1 Output |

| 输出类型 | Fixed |

| 配用 | /product-detail/zh/AD-FMCADC2-EBZ/AD-FMCADC2-EBZ-ND/4915055/product-detail/zh/EVAL-CN0276-SDPZ/EVAL-CN0276-SDPZ-ND/4571727 |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

20 V、500 mA低噪声 CMOS LDO ADP7104 产品特性 典型应用电路 输入电压范围:3.3 V至20 V 最大输出电流:500 mA 低噪声:15 μV rms(固定输出型) PSRR性能:60 dB (10 kHz,VOUT = 3.3 V) 反向电流保护 低压差:350 mV(500 mA) 初始精度: ±0.8% 在整个线路、负载与温度范围内的精度: −2%/+1% 低静态电流(VIN = 5 V):IGND = 900 µA(500 mA负载) 图1. 提供5 V固定输出电压的ADP7104 低关断电流:<40 µA(VIN = 12 V时) 利用1 μF小型陶瓷输出电容实现稳定工作 7种固定输出电压选项:1.5 V、1.8 V、2.5 V、3 V、3.3 V、 5 V和9 V 可调输出电压范围:1.22 V至VIN – VDO 返送电流限制和热过载保护 用户可编程的精密UVLO/使能功能 电源良好指示 图2. 提供5 V可调输出电压的ADP7104 8引脚LFCSP和8引脚SOIC封装 应用 适应噪声敏感应用:ADC、DAC电路、精密放大器、高频振 荡器、时钟和PLL 通信和基础设施 医疗和保健 工业与仪器仪表 概述 ADP7104是一款CMOS、低压差线性调节器,采用3.3 V至 响。这些器件具有一个“电源良好”数字输出引脚,允许电 20 V电源供电,最大输出电流为500 mA。这款高输入电压 源系统监控器检查输出电压是否正常。用户可编程精密欠 LDO适用于调节19 V至1.22 V供电的高性能模拟和混合信 压闭锁功能方便控制多个电源的时序。 号电路。该器件采用先进的专有架构,提供高电源抑制、 ADP7104提供8引脚3 mm × 3 mm LFCSP和8引脚SOIC两种 低噪声特性,仅需一个1 μF小型陶瓷输出电容,便可实现 封装。LFCSP不仅提供一种超紧凑的解决方案,而且散热 出色的线路与负载瞬态响应性能。 性能出色,在小尺寸薄型电路板空间中满足高达500 mA输 ADP7104提供7个固定输出电压选项和可调输出型号,可 出电流的应用需求。 通过外置反馈分压器,将输出电压调节至1.22 V至V − V 。 IN DO ADP7104输出噪声电压为15 μV rms,并不受输出电压影 Rev. G Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Tel: 781.329.4700 ©2011–2014 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. Technical Support www.analog.com ADI中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI不对翻译中存在的差异或由此产生的错误负责。如需确认任何词语的准确性,请参考ADI提供 的最新英文版数据手册。

ADP7104 目录 产品特性...........................................................................................1 典型性能参数..................................................................................7 应用....................................................................................................1 工作原理........................................................................................16 典型应用电路..................................................................................1 应用信息........................................................................................17 概述....................................................................................................1 电容选择...................................................................................17 修订历史...........................................................................................2 可编程欠压闭锁(UVLO).......................................................18 技术规格...........................................................................................3 电源良好特性..........................................................................19 推荐规格:输入和输出电容...................................................4 ADP7104可调型号的降噪特性............................................19 绝对最大额定值..............................................................................5 限流和热过载保护.................................................................20 热数据..........................................................................................5 散热考虑...................................................................................20 热阻..............................................................................................5 印刷电路板布局考量..................................................................23 ESD警告.......................................................................................5 外形尺寸........................................................................................24 引脚配置和功能描述.....................................................................6 订购指南...................................................................................25 修订历史 2014年5月 — 修订版F至修订版G 更改表1中的UVLO阈值上升参数..............................................4 更改“电源良好特性”部分..........................................................19 2013年11月 — 修订版E至修订版F 更改图53到图58...........................................................................15 2013年10月 — 修订版D至修订版E 更改图1和图2..................................................................................1 更改图65........................................................................................18 更改图69........................................................................................19 2013年8月 — 修订版C至修订版D 更改表3.............................................................................................5 2013年2月 — 修订版B至修订版C 更改“ADP7104可调型号的降噪特性”部分............................19 更新“外形尺寸”............................................................................25 2012年3月 — 修订版A至修订版B 更改图66........................................................................................18 2011年11月—修订版0至修订版A 将低压差从200 mV更改为350 mV.............................................1 更改压差参数..................................................................................3 2011年10月—修订版0:初始版 Rev. G | Page 2 of 28

ADP7104 技术规格 除非另有说明,V = (V + 1 V)或3.3 V(取较大者),EN = V ,I = 10 mA,C = C = 1 μF,T = 25°C。 IN OUT IN OUT IN OUT A 表1 . 参数 符号 条件 最小 值 典型 值 最大 值 单位 输入电压范围 VIN 3.3 20 V 工作电源电流 I I = 100 µA, V = 10 V 400 µA GND OUT IN I = 100 µA, V = 10 V, T = −40°C至+125°C 900 µA OUT IN J I = 10 mA, V = 10 V 450 µA OUT IN I = 10 mA, V = 10 V, T −40°C至+125°C 1050 µA OUT IN J I = 300 mA, V = 10 V 750 µA OUT IN I = 300 mA, V = 10 V, T −40°C至+125°C 1400 µA OUT IN J I = 500 mA, V = 10 V 900 µA OUT IN I = 500 mA, V = 10 V, T −40°C至+125°C 1600 µA OUT IN J 关断电流 IGND-SD EN = GND, VIN = 12 V 40 50 µA EN = GND, V = 12 V, T = −40°C至+125°C 75 µA IN J 输入反向电流 IREV-INPUT EN = GND, VIN = 0 V, VOUT = 20 V 0.3 µA EN = GND, V = 0 V, V = 20 V, T = −40°C t至 5 µA IN OUT J +125°C 输出电压精度 固定输出电压精度 VOUT IOUT = 10 mA –0.8 +0.8 % 1 mA < I < 500 mA, V = (V + 1 V) 至20 V, –2 +1 % OUT IN OUT T = −40°C至+125°C J 可调输出电压精度 VADJ IOUT = 10 mA 1.21 1.22 1.23 V 1 mA < I < 500 mA, V = (V + 1 V) to 20 V, 1.196 1.232 V OUT IN OUT T = −40°C至+125°C J 电压调整率 ∆VOUT/∆VIN VIN = (VOUT + 1 V)至20 V, TJ = −40°C至+125°C −0.015 +0.015 %/V 负载调整率1 ∆V /∆I I = 1 mA至500 mA 0.2 %/A OUT OUT OUT I = 1 mA至500 mA, T = −40°C至+125°C 0.75 %/A OUT J ADJ输入偏置电流 ADJ 1 mA < IOU T < 500 mA, VIN = (VOU T + 1 V)至 10 nA I-BIAS 20 V,ADJ连接到VOUT SENSE输入偏置电流 SENSEI-BIAS 1 mA < IOU T < 500 mA, VIN = (V OU T + 1 V)至 1 20 V,SENSE连接到VOUT,VO UT = 1. 5 V 压差2 V I = 10 mA 20 mV DROPOUT OUT I = 10 mA, T = −40°C至+125°C 40 mV OUT J I = 150 mA 100 mV OUT I = 150 mA, T = −40°C至+125°C 175 mV OUT J I = 300 mA 200 mV OUT I = 300 mA, T = −40°C至+125°C 325 mV OUT J I = 500 mA 350 mV OUT I = 500 mA, T = −40°C至+125°C 550 mV OUT J 启动时间3 t V = 5 V 1000 µs START-UP OUT 限流阈值4 I 625 775 1000 mA LIMIT PG输出逻辑电平 PG输出逻辑高电平 PG I < 1 µA 1.0 V HIGH OH PG输出逻辑低电平 PG I < 2 mA 0.4 V LOW OL PG输出阈值 输出电压下降 PG −9.2 % FALL 输出电压上升 PGRISE −6.5 % 热关断 热关断阈值 TSSD TJ上 升 150 °C 热关断迟滞 TSSD-HYS 15 °C Rev. G | Page 3 of 28

ADP7104 参数 符号 条件 最小 值 典型 值 最大 值 单位 可编程EN/UVLO UVLO阈值上升 UVLO 3.3 V ≤ V ≤ 20 V, T = −40°C to +125°C 1.18 1.22 1.28 V RISE IN J UVLO阈值下降 UVLO 3.3 V ≤ VIN ≤ 20 V,TJ = −40°C至+125°C, 1.13 V FALL 10 kΩ电阻与使能引脚串联 UVLO迟滞电流 UVLO V > 1.25 V, T = −40°C至+125°C 7.5 9.8 12 µA HYS EN J 使能下拉电流 I EN = V 500 nA EN-IN IN 启动阈值 V T = −40°C至+125°C 3.2 V START J 关断阈值 V T = −40°C至+125°C 2.45 V SHUTDOWN J 迟滞 250 mV 输出噪声 OUT 10 Hz to 100 kHz, V = 5.5 V, V = 1.8 V 15 µV rms NOISE IN OUT 10 Hz to 100 kHz, V = 6.3 V, V = 3.3 V 15 µV rms IN OUT 10 Hz to 100 kHz, V = 8 V, V = 5 V 15 µV rms IN OUT 10 Hz to 100 kHz, V = 12 V, V = 9 V 15 µV rms IN OUT 10 Hz to 100 kHz, V = 5.5 V, V = 1.5 V, 18 µV rms IN OUT 可调模式 10 Hz to 100 kHz, V = 12 V, V = 5 V, 30 µV rms IN OUT 可调模式 10 Hz to 100 kHz, V = 20 V, V = 15 V, 65 µV rms IN OUT 可调模式 电源抑制比 PSRR 100 kHz, V = 4.3 V, V = 3.3 V 50 dB IN OUT 100 kHz, V = 6 V, V = 5 V 50 dB IN OUT 10 kHz, V = 4.3 V, V = 3.3 V 60 dB IN OUT 10 kHz, V = 6 V, V = 5 V 60 dB IN OUT 100 kHz, V = 3.3 V, V = 1.8 V, 可调模式 50 dB IN OUT 100 kHz, V = 6 V, V = 5 V, 可调模式 60 dB IN OUT 100 kHz, V = 16 V, V = 15 V, 可调模式 60 dB IN OUT 10 kHz, V = 3.3 V, V = 1.8 V, 可调模式 60 dB IN OUT 10 kHz, V = 6 V, V = 5 V, 可调模式 80 dB IN OUT 10 kHz, V = 16 V, V = 15 V, 可调模式 80 dB IN OUT 1 基于使用1 mA 和300 mA负载的端点计算。1 mA以下负载的典型负载调整性能见图6。 2 压差定义为将输入电压设置为标称输出电压时的输入至输出电压差。仅适用于高于3.0 V的输出电压。 3 启动时间定义为EN的上升沿到VOUT达到其标称值90%的时间。 4 限流阈值定义为输出电压降至额定典型值90%时的电流。例如,5.0 V输出电压的电流限值定义为引起输出电压降至5.0 V的90%或4.5 V的电流。 推荐规格:输入和输出电容 表2 . 参数 符号 条件 最小 值 典型 值 最大 值 单位 最小输入和 输出 电容1 CMIN TA = −40°C至+125°C 0.7 µF 电容ESR R T = −40°C至+125°C 0.001 0.2 Ω ESR A 1 在所有工作条件下,输入和输出电容至少应大于0.7 μF。选择器件时必须考虑应用的所有工作条件,确保达到最小电容要求。配合任何LDO使用时,建议使用X7R 型和X5R型电容,不建议使用Y5V和Z5U电容。 Rev. G | Page 4 of 28

ADP7104 绝对最大额定值 θ 的值可能随PCB材料、布局和环境条件不同而异。θ 的 表3. JA JA 额定值基于4" × 3"的4层电路板。有关板结构的详细信息, 参数 额定值 VIN至GND −0.3 V至+22 V 请参考JESD51-7和JESD51-9。更多信息请登录www.ana- VOUT至GND −0.3 V至+20 V log.com,查阅应用笔记AN-617:“MicroCSP™晶圆级芯片 EN/UVLO 至GND −0.3 V至VIN 规模封装”。 PG to GND −0.3 V至VIN Ψ 是结至板热特性参数,单位为°C/W。封装的Ψ 基于使 SENSE/ADJ至GND −0.3 V至VOUT JB JB 用4层板的建模和计算方法。JESD51-12报告和使用电子封 存储温度范围 −65°C至+150°C 工作结温范围 −40°C至+125°C 装热信息指南中声明,热特性参数与热阻不是一回事。Ψ JB 焊接条件 JEDEC J-STD-020 衡量沿多条热路径流动的器件功率,而θ 只涉及一条路 JB 径。因此,Ψ 热路径包括来自封装顶部的对流和封装的 注意,超出上述绝对最大额定值可能会导致器件永久性损 JB 辐射,这些因素使得Ψ 在现实应用中更有用。最高结温 坏。这只是额定最值,不表示在这些条件下或者在任何其 JB (T)由板温度(T )和功耗(P )通过下式计算: 它超出本技术规范操作章节中所示规格的条件下,器件能 J B D 够正常工作。长期在绝对最大额定值条件下工作会影响器 T = T + (P × Ψ ) J B D JB 件的可靠性。 有关ΨJB的更详细信息,请参考JESD51-8和JESD51-12。 热数据 热阻 绝对最大额定值仅适合单独应用,但不适合组合使用。如 θ 和Ψ 针对最差条件,即器件焊接在电路板上以实现表 JA JB 果温度超过结温限值,ADP7104可能会受损。监控环境温 贴封装。θ 是带顶部安装散热器的表贴封装的参数,这 JC 度并不能保证T不会超出额定温度限值。在功耗高、热阻 里提供的θ 仅供参考。 J JC 差的应用中,可能必须降低最大环境温度。 表4. 热阻 在功耗适中、PCB热阻较低的应用中,只要结温处于额定 封装类型 θJA θJC ΨJB Unit 限值以内,最大环境温度可以超过最大限值。器件的结温 8引脚LFCSP 40.1 27.1 17.2 °C/W (T)取决于环境温度(T )、器件的功耗(PD)和封装的结至 8引脚SOIC 48.5 58.4 31.3 °C/W J A 环境热阻(θ )。 JA ESD警告 最高结温(T)由环境温度(T )和功耗(P )通过下式计算: J A D ESD(静电放电)敏感器件。 T = T + (P × θ ) J A D JA 带电器件和电路板可能会在没有察觉的情况下放电。尽 封装的结至环境热阻(θ )基于使用4层板的建模和计算方 管本产品具有专利或专有保护电路,但在遇到高能量 JA ESD时,器件可能会损坏。因此,应当采取适当的ESD 法,主要取决于应用和板布局。在最大功耗较高的应用 防范措施,以避免器件性能下降或功能丧失。 中,需要特别注意热板设计。 Rev. G | Page 5 of 28

引脚配置和功能描 述 VOUT1 8VIN VOUT 1 8 VIN SENSE/ADJ2 ADP7104 7PG SENSE/ADJ 2 ADP7104 7 PG TOP VIEW TOP VIEW GND3 (Not to Scale) 6GND GND 3 (Not to Scale) 6 GND NC4 5EN/UVLO NC 4 5 EN/UVLO NOTES NOTES 1. NC = NO CONNECT. DO NOT CONNECTTO 1. NC = NO CONNECT. DO NOT CONNECTTO THIS PIN. THIS PIN. 2.IT IS HIGHLY RECOMMENDED THAT THE 2.IT IS HIGHLY RECOMMENDED THAT THE EPPXALAPCONKESA EGODEN P BTAEHD EC OOBNNO NATEHRCEDT .BEODT TTOO MTH OEF G TRHOEUND 09507-003 EPPXALAPCONKESA EGODEN P BTAEHD EC OOBNNO NATEHRCEDT .BEODT TTOO MTH OEF G TRHOEUND 09507-004 图3. L FCSP封装 图4. 窄体SOIC封装 表5. 引脚功能描述 引脚编号 引脚名称 说明 1 VOUT 调节输出电压。VOUT至GND接1 μF或更大的旁路电容。 2 SENSE/ADJ 检测(SENSE)。测量负载上的实际输出电压,并将其馈入误差放大器。应使SENSE引脚尽可 能靠近负载,使得调节器输出与负载之间的IR压降的影响最小。此功能仅适用于固定电压 选项。 调整输入(ADJ)。外部电阻分压器设置输出电压。此功能仅适用于可调电压选项。 3 GND 地。 4 NC 请勿连接该引脚。 5 EN/UVLO 使能输入(EN)。将EN接到高电平,调节器启动;将EN接到低电平,调节器关闭。若要实现 自动启动,请将EN接VIN。 可编程欠压闭锁(UVLO)。使用可编程UVLO功能时,上下限由编程电阻决定。 6 GND 地。 7 PG 电源良好。此开漏输出需要一个外部上拉电阻连接至VIN或VOUT。如果器件处于关断模 式、限流模式、热关断模式,或者如果它降至标称输出电压的90%以下,PG引脚将立即变 为低电平。如果不用电源良好功能,可将此引脚悬空或连接到地。 8 VIN 调节器输入电源。VIN至GND接1 μF或更大的旁路电容。 EPAD 裸露焊盘 。封装底部的裸露焊盘。EPAD可增强散热性能,它与封装内部的GND形成电气 连接。强烈建议将EPAD连接到板上的接地层。 Rev. G | Page 6 of 28

典型性能参数 除非 另有 说明,V = 7.5 V,V = 5 V,I = 10 mA,C = COUT = 1 μF,T = 25°C。 IN OUT OUT IN A 3.35 1200 LOAD = 100µA LOAD = 100µA LOAD = 1mA LOAD = 1mA LOAD = 10mA LOAD = 10mA LOAD = 100mA 1000 LOAD = 100mA 3.33 LOAD = 300mA LOAD = 300mA LOAD = 500mA A) LOAD = 500mA µ T ( 800 V)3.31 REN (OUT CUR 600 V D 3.29 N U O 400 R G 3.27 200 3.25 0 –40°C –5°C T2J5 (°°CC) 85°C 125°C 09507-005 –40°C –5°C T2J5 (°°CC) 85°C 125°C 09507-008 图5. 输出电压与结温的关系 图8. 接地电流与结温的关系 3.35 800 700 3.33 A) 600 µ V)3.31 RENT ( 500 (OUT CUR 400 V D 3.29 UN 300 O R G 200 3.27 100 3.25 0 0.1 1 ILOAD10 (mA) 100 1000 09507-006 0.1 1 ILOAD10 (mA) 100 1000 09507-009 图6. 输出电压与负载电流的关系 图9. 接地电流与负载电流的关系 3.35 1200 LOAD = 100µA LOAD = 100µA LOAD = 1mA LOAD = 1mA LOAD = 10mA LOAD = 10mA LOAD = 100mA 1000 LOAD = 100mA 3.33 LOAD = 300mA LOAD = 300mA LOAD = 500mA LOAD = 500mA A) µ T ( 800 V)3.31 REN (VOUT D CUR 600 3.29 N U O 400 R G 3.27 200 3.25 0 4 6 8 10 VIN1 2(V) 14 16 18 20 09507-007 4 6 8 10 VIN1 2(V) 14 16 18 20 09507-010 图7. 输出电压与输入电压的关系 图10. 接地电流与输入电压的关系 Rev. G | Page 7 of 28

ADP7104 160 1400 3.3V 4.0V 140 68..00VV 1200 12.0V ENT (µA) 110200 20.0V NT (µA)1000 RR RE 800 CU 80 UR N C W D 600 DO 60 UN T O SHU 40 GR 400 LOAD = 5mA LOAD = 10mA 20 200 LLOOAADD == 120000mmAA LOAD = 300mA LOAD = 500mA 0–50 –25 0 TE2M5PERAT5U0RE (°C7)5 100 125 09507-011 03.1 3.2 3.3 VI3N. 4(V) 3.5 3.6 3.7 09507-014 图11. 不同输入电压下关断电流与温度的关系 图14. 低压差下接地电流与输入电压的关系 350 5.05 VOUT = 3.3V LOAD = 100µA TA = 25°C 5.04 LOAD = 1mA 300 LOAD = 10mA LOAD = 100mA 5.03 LOAD = 300mA LOAD = 500mA 250 5.02 V) m 5.01 OUT ( 200 (V)UT5.00 OP 150 VO R 4.99 D 100 4.98 4.97 50 4.96 01 10 ILOAD (mA) 100 1000 09507-012 4.95 –40°C –5°C T2J5 (°°CC) 85°C 125°C 09507-015 图12. 压差与负载电流的关系 图15. 输出电压与结温的关系(V = 5 V) OUT 3.4 5.05 5.04 3.3 5.03 3.2 5.02 5.01 V) 3.1 V) (UT (UT5.00 O O V 3.0 V 4.99 2.9 4.98 LOAD = 5mA LOAD = 10mA 4.97 LOAD = 100mA 2.8 LOAD = 200mA LOAD = 300mA 4.96 LOAD = 500mA 2.7 4.95 3.1 3.2 3.3 VI3N. 4(V) 3.5 3.6 3.7 09507-013 0.1 1 ILOAD10 (mA) 100 1000 09507-016 图13. 低压差下输出电压与输入电压的关系 图16. 输出电压与负载电流的关系(V = 5 V) OUT Rev. G | Page 8 of 28

ADP7104 5.05 300 LOAD = 100µA VOUT = 5V 5.04 LLOOAADD == 11m0mAA TA = 25°C LOAD = 100mA 250 5.03 LOAD = 300mA LOAD = 500mA 5.02 200 V) 5.01 m (V)UT5.00 OUT ( 150 VO4.99 ROP D 100 4.98 4.97 50 4.96 4.95 0 6 8 10 12VIN (V)14 16 18 20 09507-017 1 10 ILOAD (mA) 100 1000 09507-018 图17. 输出电压与输入电压的关系(V = 5 V) 图20. 压差与负载电流的关系(V = 5 V) OUT OUT 1000 5.05 LOAD = 100µA 900 LOAD = 1mA 5.00 LOAD = 10mA LOAD = 100mA 800 LOAD = 300mA 4.95 µA) 700 4.90 T ( REN 600 V)4.85 D CUR 500 (VOUT4.80 N 400 4.75 U O R 300 4.70 G LOAD = 5mA 200 4.65 LOAD = 10mA LOAD = 100mA LOAD = 200mA 100 4.60 LOAD = 300mA LOAD = 500mA 0 4.55 –40°C –5°C T2J5 (°°CC) 85°C 125°C 09507-118 4.8 4.9 5.0 VI5N. 1(V) 5.2 5.3 5.4 09507-019 图18. 接地电流与结温的关系(V = 5 V) 图21. 低压差下输出电压与输入电压的关系 OUT 700 2500 600 2000 NT (µA) 500 NT (µA)1500 RE 400 RE UR UR1000 C C D 300 D N N U U O O 500 GR 200 GR LOAD = 5mA LOAD = 10mA 0 LOAD = 100mA 100 LOAD = 200mA LOAD = 300mA LOAD = 500mA 0 –500 0.1 1 ILOAD10 (mA) 100 1000 09507-119 4.80 4.90 5.00 V5IN.1 (0V) 5.20 5.30 5.40 09507-020 图19. 接地电流与负载电流的关系(V = 5 V) 图22. 低压差下接地电流与输入电压的关系(V = 5 V) OUT OUT Rev. G | Page 9 of 28

ADP7104 1.85 900 LOAD = 100µA LOAD = 100µA LOAD = 1mA LOAD = 1mA LOAD = 10mA 800 LOAD = 10mA LOAD = 100mA LOAD = 100mA 1.83 LLOOAADD == 350000mmAA 700 LOAD = 300mA A) µ T ( 600 1.81 N V) RE 500 V (OUT1.79 ND CUR 400 U O 300 R G 1.77 200 100 1.75 0 –40°C –5°C T2J5 (°°CC) 85°C 125°C 09507-021 –40°C –5°C T2J5 (°°CC) 85°C 125°C 09507-126 图23. 输出电压与结温的关系(V = 1.8 V) 图26. 接地电流与结温的关系(V = 1.8 V) OUT OUT 1.85 700 600 1.83 A) 500 µ T ( 1.81 N (V)UT URRE 400 O C V1.79 ND 300 U O GR 200 1.77 100 1.750.1 1 ILOA1D0 (mA) 100 1000 09507-022 00.1 1 ILOAD1 0(mA) 100 1000 09507-127 图24. 输出电压与负载电流的关系(V = 1.8 V) 图27. 接地电流与负载电流的关系(V = 1.8 V) OUT OUT 1.85 1200 LOAD = 100µA LOAD = 100µA LOAD = 1mA LOAD = 1mA LOAD = 10mA LOAD = 10mA LOAD = 100mA 1000 LOAD = 100mA 1.83 LOAD = 300mA LOAD = 300mA LOAD = 500mA LOAD = 500mA A) µ T ( 800 1.81 N (V)UT URRE 600 O C V1.79 ND U O 400 R G 1.77 200 1.75 0 2 4 6 8 10VIN (V1)2 14 16 18 20 09507-023 2 4 6 8 10VIN (V1)2 14 16 18 20 09507-024 图25. 输出电压与输入电压的关系(V = 1.8 V) 图28. 接地电流与输入电压的关系(V = 1.8 V) OUT OUT Rev. G | Page 10 of 28

ADP7104 5.08 2.0 LOAD = 100µA 3.3V 5.07 LOAD = 1mA 4V LOAD = 10mA 5V LOAD = 100mA 6V 5.06 LOAD = 300mA A) 8V 5.05 LOAD = 500mA ENT (µ 1.5 111025VVV R 18V (V)OUT55..0034 WN CUR 1.0 20V V O 5.02 D T U 5.01 H S 5.00 OUT 0.5 I 4.99 4.98 –40°C –5°C T2J5 (°°CC) 85°C 125°C 09507-025 0–40 –20 0 20TEMP4E0RATU6R0E (°C8)0 100 120 140 09507-054 图29. 输出电压与结温的关系(V = 5 V,可调) 图32. 反相输入电流与温度的关系(V = 0 V, OUT IN V 为差分电压) OUT 5.08 0 LOAD = 500mA LOAD = 300mA 5.07 –10 LOAD = 100mA LOAD = 10mA 5.06 –20 LOAD = 1mA 5.05 –30 (V)UT55..0034 R (dB) ––5400 O R V S 5.02 P –60 5.01 –70 5.00 –80 4.99 –90 4.98 –100 0.1 1 ILOAD10 (mA) 100 1000 09507-026 10 100 1kFREQU1E0NkCY (Hz)100k 1M 10M 09507-028 图30. 输出电压与负载电流的关系(V = 5 V,可调) 图33. 电源抑制比与频率的关系(V = 1.8 V,V = 3.3 V) OUT OUT IN 5.08 0 LOAD = 500mA LOAD = 300mA 5.07 –10 LOAD = 100mA LOAD = 10mA LOAD = 1mA 5.06 –20 5.05 –30 V)5.04 dB) –40 V (OUT55..0023 PSRR ( ––6500 5.01 –70 LOAD = 100µA 5.00 LOAD = 1mA –80 LOAD = 10mA 4.99 LOAD = 100mA –90 LOAD = 300mA LOAD = 500mA 4.986 8 10 12VIN (V)14 16 18 20 09507-027 –10010 100 1kFREQU1E0NkCY (Hz)100k 1M 10M 09507-029 图31. 输出电压与输入电压的关系(V = 5 V,可调) 图34. 电源抑制比与频率的关系(V = 3.3 V,V = 4.8 V) OUT OUT IN Rev. G | Page 11 of 28

ADP7104 0 0 LOAD = 500mA LOAD = 500mA LOAD = 300mA LOAD = 300mA –10 LOAD = 100mA –10 LOAD = 100mA LOAD = 10mA LOAD = 10mA –20 LOAD = 1mA –20 LOAD = 1mA –30 –30 B) –40 B) –40 d d R ( –50 R ( –50 R R S S P –60 P –60 –70 –70 –80 –80 –90 –90 –10010 100 1kFREQU1E0NkCY (Hz)100k 1M 10M 09507-030 –10010 100 1kFREQU1E0NkCY (Hz)100k 1M 10M 09507-033 图35. 电源抑制比与频率的关系(V = 3.3 V,V = 4.3 V) 图38. 电源抑制比与频率的关系(V = 5 V,V = 6 V) OUT IN OUT IN 0 0 LOAD = 500mA LOAD = 500mA LOAD = 300mA LOAD = 300mA –10 LOAD = 100mA –10 LOAD = 100mA LOAD = 10mA LOAD = 10mA –20 LOAD = 1mA –20 LOAD = 1mA –30 –30 B) –40 B) –40 d d R ( –50 R ( –50 R R S S P –60 P –60 –70 –70 –80 –80 –90 –90 –100 –100 10 100 1kFREQU1E0NkCY (Hz)100k 1M 10M 09507-031 10 100 1kFREQU1E0NkCY (Hz)100k 1M 10M 09507-034 图36. 电源抑制比与频率的关系(V = 3.3 V,V = 3.8 V) 图39. 电源抑制比与频率的关系(V = 5 V,V = 5.5 V) OUT IN OUT IN 0 0 LOAD = 500mA LOAD = 500mA LOAD = 300mA LOAD = 300mA –10 LOAD = 100mA –10 LOAD = 100mA LOAD = 10mA LOAD = 10mA –20 LOAD = 1mA –20 LOAD = 1mA –30 –30 B) –40 B) –40 d d R ( –50 R ( –50 R R S S P –60 P –60 –70 –70 –80 –80 –90 –90 –100 –100 10 100 1kFREQU1E0NkCY (Hz)100k 1M 10M 09507-032 10 100 1kFREQU1E0NkCY (Hz)100k 1M 10M 09507-035 图37. 电源抑制比与频率的关系(V = 5 V,V = 6.5 V) 图40. 电源抑制比与频率的关系(V = 5 V,V = 5.3 V) OUT IN OUT IN Rev. G | Page 12 of 28

ADP7104 0 0 LOAD = 500mA LOAD = 300mA –10 –10 LOAD = 100mA LOAD = 10mA –20 –20 LOAD = 1mA –30 –30 B) –40 B) –40 R (d –50 R (d –50 R R S S P –60 P –60 –70 –70 –80 –80 LOAD = 500mA LOAD = 300mA –90 LOAD = 100mA –90 LOAD = 10mA LOAD = 1mA –10010 100 1kFREQU1E0NkCY (Hz)100k 1M 10M 09507-036 –1000 0.25 H0E.5A0DROOM0. 7V5OLTAGE1. 0(V0) 1.25 1.50 09507-039 图41. 电源抑制比与频率的关系(V = 5 V,V = 5.2 V) 图44. 电源抑制比与裕量电压的关系(100 Hz,V = 5 V) OUT IN OUT 0 0 LOAD = 500mA LOAD = 500mA LOAD = 300mA LOAD = 300mA –10 LOAD = 100mA –10 LOAD = 100mA LOAD = 10mA LOAD = 10mA LOAD = 1mA LOAD = 1mA –20 –20 –30 –30 B) –40 B) –40 d d R ( –50 R ( –50 R R S S P –60 P –60 –70 –70 –80 –80 –90 –90 –10010 100 1kFREQU1E0NkCY (Hz)100k 1M 10M 09507-037 –1000 0.25 H0E.5A0DROOM0. 7V5OLTAGE1. 0(V0) 1.25 1.50 09507-040 图42. 电源抑制比与频率的关系(V = 5 V,V = 6 V,可调) 图45. 电源抑制比与裕量电压的关系(1 kHz,V = 5 V) , OUT IN OUT 0 0 LOAD = 500mA LOAD = 500mA LOAD = 300mA LOAD = 300mA –10 LOAD = 100mA –10 LOAD = 100mA LOAD = 10mA LOAD = 10mA –20 LOAD = 1mA –20 LOAD = 1mA –30 –30 B) –40 B) –40 R (d –50 R (d –50 R R S S P –60 P –60 –70 –70 –80 –80 –90 –90 –10010 100 1kFREQU1E0NkCY (Hz)100k 1M 10M 09507-038 –1000 0.25 H0E.5A0DROOM0. 7V5OLTAGE1. 0(V0) 1.25 1.50 09507-041 图43. 电源抑制比与频率的关系(V = 5 V,V = 6 V, 图46. 电源抑制比与裕量电压的关系(10 kHz,V = 5 V) 可调并带降噪电O路UT) IN OUT Rev. G | Page 13 of 28

ADP7104 0 LOAD = 500mA LOAD = 300mA –10 LOAD = 100mA LOAD = 10mA LOAD = 1mA –20 –30 B) –40 d R ( –50 R S P –60 –70 –80 –90 –100 0 0.25 H0E.5A0DROOM0. 7V5OLTAGE1. 0(V0) 1.25 1.50 09507-042 图47. 电源抑制比与裕量电压的关系(100 kHz,V = 5 V) 图50. 负载瞬态响应(CIN、COUT = 1 μF,ILOAD = 1 mA至 OUT 500 mA,V = 1.8 V,V = 5 V) OUT IN 30 25 20 s) m V r E (µ 15 S OI N 10 3.3V 5 1.8V 5V 5VADJ 5VADJ NR 0 0.00001 0.0001 LO0.A00D1 CURREN0T.0 (1A) 0.1 1 09507-043 图48. 输出噪声与负载电流和输出电压的关系(C = 1 μF) 图51. 负载瞬态响应(CIN、COUT = 1 μF,ILOAD = 1 mA至 OUT 500 mA,V = 3.3 V,V = 5 V) OUT IN 10 3.3V 5V 5VADJ 5VADJ NR Hz) 1 √ V/ µ E ( S OI N 0.1 0.0110 100 FREQUE1NkCY (Hz) 10k 100k 09507-044 图49. 输出噪声频谱密度(I = 10 mA,C = 1 μF) 图52. 负载瞬态响应(CIN、COUT = 1 μF,ILOAD = 1 mA至 LOAD OUT 500 mA,V = 5 V,V = 7 V) OUT IN Rev. G | Page 14 of 28

ADP7104 INPUT VOLTAGE INPUT VOLTAGE 2 OUTPUT VOLTAGE 2 OUTPUT VOLTAGE 1 1 CH1 1V BW CH2 10mV BW TM 94.µ8s% A CH4 1.56V 09507-048 CH1 1VBW CH2 10mV BW TM 94.µ8s% A CH4 1.56V 09507-051 图53.线路瞬态响应(C 、C = 1 μF,I = 500 mA,V = 1.8 V) 图56.线路瞬态响应(C 、C = 1 μF,I = 1 mA,V = 1.8 V) IN OUT LOAD OUT IN OUT LOAD OUT INPUT VOLTAGE INPUT VOLTAGE 2 OUTPUT VOLTAGE 2 OUTPUT VOLTAGE 1 1 CH1 1V BW CH2 10mV BW TM 94.µ8s% A CH4 1.56V 09507-049 CH1 1VBW CH2 10mV BW TM 94.µ8s% A CH4 1.56V 09507-052 图54.线路瞬态响应(C 、C = 1 μF,I = 500 mA,V = 3.3 V) 图57.线路瞬态响应(C 、C = 1 μF,I = 1 mA,V = 3.3 V) IN OUT LOAD OUT IN OUT LOAD OUT INPUT VOLTAGE INPUT VOLTAGE 2 OUTPUT VOLTAGE 2 OUTPUT VOLTAGE 1 CH1 1V BW CH2 10mV BW TM 49µ.8s% A CH4 1.56V 09507-050 1 CH1 1VBW CH2 10mV BW TM 49µ.8s% A CH4 1.56V 09507-053 图55.线路瞬态响应(C 、C = 1 μF,I = 500 mA,V = 5 V) 图58.线路瞬态响应(C 、C = 1 μF,I = 1 mA,V = 5 V) IN OUT LOAD OUT IN OUT LOAD OUT Rev. G | Page 15 of 28

ADP7104 工作原理 ADP7104是一款低静态电流、低压差线性稳压器,采用3.3 如果反馈电压高于基准电压,PMOS器件的栅极将被拉 V至20 V电源供电,最大输出电流为500 mA。满负载时静 高,以便通过较少电流,降低输出电压。 态电流典型值低至1 mA,因此ADP7104非常适合电池供 ADP7104提供7个固定输出电压选项(范围从1.5 V到9 V)以 电的便携式设备使用。室温时,关断模式下的功耗典型值 及可调输出型号,可通过外置分压器,将输出电压调节至 为40 μA。ADP7104经过优化,利用1 μF陶瓷电容可实现出 1.22 V至19 V。输出电压可根据下式设置: 色的瞬态性能。 V = 1.22 V(1 + R1/R2) OUT VIN VOUT VREG GND SHORT-CIRCUIT, PGOOD PG THERMAL PROTECT R1 SENSE 10µA SHUTDOWN R2 EN/ UVLO REF1E.R22EVNCE 09507-055 图62. 典型可调输出电压应用原理图 图59. 固定输出电压型号内部框图 R2的阻值应低于200 kΩ,以便将ADJ引脚输入电流引起的 输出电压误差降至最低。例如,当R1和R2都是200 kΩ时, VIN VOUT 输出电压为2.44 V。假设25°C时ADJ引脚输入电流为10 nA VREG GND SHORT-CIRCUIT, PGOOD PG (典型值),则ADJ引脚输入电流引起的输出电压误差为2 THERMAL PROTECT mV或0.08%。 10µA SHUTDOWN R2 EN/ ADJ 在正常工作条件下,ADP7104利用EN/UVLO引脚使能和禁 UVLO 用VOUT引脚。EN/UVLO为高电平时,VOUT开启;EN为 REF1E.R22EVNCE 09507-056 低LO电接平至时VI,NV。O UT关闭。若要实现自动启动,可将EN/UV- 图60. 可选输出电压型号内部框图 ADP7104内置反向电流保护电路,当输出电压高于输入电 ADP7104内置一个基准电压源、一个误差放大器、一个 压时,它可防止电流通过调整元件回流。比较器检测输入 反馈分压器和一个PMOS调整管。输出电流经由PMOS调 电压与输出电压之间的差值。当该差值超过55 mV时, 整管提供,其受误差放大器控制。误差放大器比较基准 PFET的本体切换到V 并关闭或开路。换言之,栅极连接 电压与输出端的反馈电压,并放大该差值。如果反馈电 OUT 到VOUT。 压低于基准电压,PMOS器件的栅极将被拉低,以便通 过更多电流,提高输出电压。 Rev. G | Page 16 of 28

ADP7104 应用信息 电容选择 图63所示为0402、1 μF、10 V、X5R电容的电容与电压偏置 特性关系图。电容的电压稳定性受电容尺寸和电压额定值 输出电容 影响极大。一般来说,封装较大或电压额定值较高的电容 ADP7104设计采用节省空间的小型陶瓷电容,不过只要注 意等效串联电阻(ESR)值要求,也可以采用大多数常用电 具有更好的稳定性。X5R电介质的温度变化率在-40℃至 容。输出电容的ESR会影响LDO控制回路的稳定性。为了 +85°C温度范围内为±15%,与封装或电压额定值没有函数 确保ADP7104稳定工作,推荐使用至少1 μF、ESR为1 Ω或 关系。 1.2 更小的电容。输出电容还会影响负载电流变化的瞬态响 应。采用较大的输出电容值可以改善ADP7104对大负载电 1.0 流变化的瞬态响应。图62显示输出电容值为1 μF时的瞬态 响应。 µF) 0.8 E ( C N A 0.6 T CI A P CA 0.4 0.2 00 2 4VOLTAGE (V6) 8 10 09507-058 图63. 电容与电压关系特性 考虑电容随温度、元件容差和电压的变化,可以利用公式1 确定最差情况下的电容。 C = C × (1 − TEMPCO) × (1 − TOL) (1) EFF BIAS 图62. 输出瞬态响应(V = 1.8 V,C = 1 µF) 其中: OUT OUT 输入旁路电容 C 为工作电压下的有效电容。 BIAS 在VIN与GND之间连接一个1 µF电容可降低电路对印刷 TEMPCO为最差的电容温度系数。 电路板(PCB)布局的敏感性,尤其是输入走线较长或源 阻抗较高的情况下。如果要求输出电容大于1 μF,应选 TOL为最差的元件容差。 用更高的输入电容。 本例中,假定X5R电介质在−40°C至+85°C范围内的最差条件 温度系数(TEMPCO)为15%。如图63所示,在1.8 V电压下, 输入和输出电容特性 假定电容容差(TOL)为10%,C =0.94 μF。 只要符合最小电容和最大ESR要求,ADP7104可以采用任 BIAS 何质量优良的电容。陶瓷电容可采用各种各样的电介质制 将这些值代入公式1中可得到: 造,温度和所施加的电压不同,其特性也不相同。电容必 C = 0.94 μF × (1 − 0.15) × (1 − 0.1) = 0.719 μF EFF 须具有足以在必要的温度范围和直流偏置条件下确保最小 因此,在选定输出电压条件下,本例中所选电容满足LDO 电容的电介质。推荐使用额定电压为6.3 V至25 V的X5R或 在温度和容差方面的最小电容要求。 X7R电介质。Y5V和Z5U电介质的温度和直流偏置特性不 佳,建议不要使用。 为了保证ADP7104的性能,必须针对每一种应用来评估直流 偏置、温度和容差对电容性能的影响。 Rev. G | Page 17 of 28

ADP7104 可编程欠压闭锁(UVLO) 迟滞也可以通过在EN/UVLO引脚上串联一个电阻来实现。 在图65所示的例子中,使能阈值为2.44 V,迟滞为1 V。 在正常工作条件下,ADP7104利用EN/UVLO引脚使能和禁 用VOUT引脚。如图64所示,当EN上的上升电压越过上阈 值时,VOUT开启。当EN/UVLO上的下降电压越过下阈值 时,VOUT关闭。EN/UVLO阈值的迟滞由EN/UVLO引脚 串联的戴维宁等效电阻决定。 2.0 1.8 图65 EN引脚的典型分压器 1.6 1.4 图64显示了EN/UVLO引脚的典型迟滞,这可以防止EN引 1.2 脚上的噪声在经过阈值点时引起开关振荡。 1.0 VVOOUUTT,, EENN FRAISLEL ADP7104利用内置软启动功能,在输出使能时限制浪涌电 0.8 流。当输入电压为3.3 V时,从通过EN有效阈值到输出达 0.6 到其最终值90%的启动时间约为580 μs。如图66所示,启 0.4 动时间取决于输出电压设置。 0.2 01.00 1.25 1.50 1.75 2.00 2.25 2.50 2.75 3.00 09507-060 6 图64. 对EN引脚工作方式的典型VOUT响应 5V 5 上下阈值是用户可编程的,可以利用两个电阻来设置。当 EN/UVLO引脚电压低于1.22 V时,LDO禁用。当EN/UVLO 4 引脚电压跃迁至1.22 V以上时,LDO使能,该引脚提供10 (V)UT 3 3.3V µA迟滞电流以提升电压,从而提供阈值迟滞。通常由两个 VO 外部电阻设置LDO的最小工作电压。R1和R2电阻的值可通 2 ENABLE 过下式确定: 1 R1 = V /10 μA HYS R2 = 1.22 V × R1/(V − 1.22 V) 0 其中: IN 0 500 TIM10E0 (0µs) 1500 2000 09507-061 V 为所需的开启电压。 图66. 典型启动性能 IN V 为所需的EN/UVLO迟滞电平。 HYS Rev. G | Page 18 of 28

ADP7104 电源良好特性 ADP7104可调型号的降噪特性 ADP7104提供一个电源良好引脚(PG)来指示输出的状态。 固定输出ADP7104的超低输出噪声特性是通过如下方法实 此开漏输出需要一个外部上拉电阻连接至VIN或VOUT。 现的:LDO误差放大器保持单位增益,并设置基准电 压 如果器件处于关断模式、限流模式或热关断,或者如果它 等于输出电压。这种架构不适用于可调输出电压LDO。 降至标称输出电压的90%以下,电源良好引脚(PG)将立即 可调输出ADP7104采用更为传统的架构,基准电压为固定 变为低电平。软启动期间,电源良好信号的上升阈值为标 值,误差放大器增益为输出电压的函数。传统LDO架构 称输出电压的93.5%。当ADP7104有足够的输入电压来开 的缺点是输出电压噪声与输出电压成比例。 启内部PG晶体管时,此开漏输出保持低电平。PG晶体管 可以对可调LDO电路稍加修改,以将输出电压噪声降低 通过一个接VOUT或VIN的上拉电阻端接。 到与固定输出ADP7104接近的水平。图69所示的电路在输 当此电压上升时,电源良好精度为调节器标称输出电压的 出电压设置电阻分压器上增加了2个元件:C 和R ,它 NR NR 93.5%;当此电压下降时,跳变点为标称输出电压的90%。 们与R 并联,用以降低误差放大器的交流增益。选择的 FB1 如果V 降至90%以下,则表明调节器输入电压关断或受 RNR等于R ,从而把误差放大器的交流增益限制在大约6 OUT FB2 到干扰,从而触发电源不良信号。 dB。实际增益为R 和R 的并联组合除以R ,这可以确 NR FB1 FB2 保误差放大器始终以大于1的增益工作。 当V 降至90%以下时,正常关断将导致电源良好信号变 OUT 为低电平。 选择的CNR应使得在频率为50 Hz至100 Hz时,C 的电抗 NR 等于R − R 。由此设置的频率将使得误差放大器的交流 图67和图68显示整个温度范围内的典型电源良好上升和下 FB1 NR 增益比直流增益低3 dB。 降阈值。 6 PG –40°C PG –5°C PG +25°C 5 PG +85°C PG +125°C 4 V) G ( 3 P 2 图69. 更改可调输出LDO以降低噪声 1 可调LDO的噪声可通过下式计算,计算时假定固定输出 LDO的噪声约为15 μV。 0 4.2 4.3 4.4 4.5 VOU4.T6 (V) 4.7 4.8 4.9 5.0 09507-062 1 图67. 典型电源良好阈值 与温度的关系(V 上升) 15μV× 1+ /13kΩ OUT 1/13kΩ+1/40.2kΩ 6 PG –40°C PG –5°C 基于图69所示的元件值,ADP7104具有下列特性: PG +25°C 5 PG +85°C PG +125°C • 直流增益:4.09 (12.2 dB) 4 • 3 dB滚降频率:59 Hz V) • 高频交流增益:1.76 (4.89dB) PG ( 3 • 降噪系数:1.33 (2.59 dB) • 无降噪功能的可调LDO的RMS噪声:27.8 µV rms 2 • 有降噪功能的可调LDO的RMS噪声(假设固定电压选 1 项为15 µV rms):19.95 µV rms 0 4.2 4.3 4.4 4.5 VOU4.T6 (V) 4.7 4.8 4.9 5.0 09507-063 图68. 典型电源良好阈值与温度的关系(V 下降) OUT Rev. G | Page 19 of 28

ADP7104 限流和热过载保护 为保证器件可靠工作,ADP7104的结温不得超过125°C。 ADP7104内置限流和热过载保护电路,可防止功耗过大导 为确保结温低于此最高结温,用户需要注意会导致结温 致受损。当输出负载达到600 mA(典型值)时,限流电路就 变化的参数。这些参数包括环境温度、功率器件的功 会起作用。当输出负载超过600 mA时,输出电压会被降 耗、结与周围空气之间的热阻(θ )。θ 值取决于所用的 JA JA 低,以保持恒定的电流限制。 封装填充物和将封装GND引脚焊接到PCB所用的覆铜数 量。 热过载保护电路将结温限制在150°C(典型值)以下。在极端 条件下(即高环境温度和/或高功耗),当结温开始升至150°C 表6给出了各种PCB覆铜尺寸时8引脚SOIC和8引脚LFCSP 以上时,输出就会关闭,从而将输出电流降至0。当结温降 封装的典型θ 值。表7给出了8引脚SOIC和8引脚LFCSP封 JA 至135°C以下时,输出又会开启,输出电流恢复为工作值。 装的典型Ψ 值。 JB 考虑VOUT至地发生负载短路的情况。首先,ADP7104的限 表6. 典型θ 值 JA 流功能起作用,因此,仅有600 mA电流传导至短路电路。 θJA (°C/W) 覆铜面积(mm2) LFCSP SOIC 如果结的自发热量足够大,使其温度升至150°C以上,热关 251 165.1 167.8 断功能就会激活,输出关闭,输出电流降至0。当结温冷却 100 125.8 111 下来,降至135°C以下时,输出开启,将600 mA电流传导至 500 68.1 65.9 短路路径中,再次导致结温升至150°C以上。结温在135°C 1000 56.4 56.1 6400 42.1 45.8 至150°C范围内的热振荡导致电流在600 mA和0 mA之间振 1 器件焊接在最小尺寸引脚走线上。 荡;只要输出端存在短路,振荡就会持续下去。 表7. 典型Ψ 值 限流和热过载保护旨在保护器件免受偶然过载条件影响。 JB 型号 Ψ (°C/W) JB 为保证器件稳定工作,必须从外部限制器件的功耗,使结 LFCSP 15.1 温不会超过125°C。 SOIC 31.3 散热考虑 ADP7104的结温可通过下式计算: 在输入至输出电压差很小的应用中,ADP7104不会产生很 TJ = TA + (PD × θJA) (2) 其中: 多热量。然而,在环境温度很高和/或输入电压很大的应用 TA是环境温度。 中,封装发出的热量可能非常大,导致芯片结温超过最高 PD为芯片的功耗,通过下式计算: 结温125°C。 PD = [(V − V ) × I ] + (V × I ) (3) 当结温超过150°C时,转换器进入热关断模式。只有当结温 IN OUT LOAD IN GND 其中: 降至135°C及以下时,它才会恢复,以免永久性受损。因 I 为负载电流。 此,为了保证器件在所有条件下具有可靠性能,必须对具 LOAD I 为接地电流。 体应用进行热分析。芯片的结温为环境温度与功耗所引起 GND V 和V 分别为输入和输出电压。 的封装温升之和,如公式2所示。 IN OUT 接地电流引起的功耗相当小,可忽略不计。因此,结温的 计算公式可简化为: T = T + {[(V − V ) × I ] × θ } (4) J A IN OUT LOAD JA 如公式4所示,针对给定的环境温度、输入与输出电压差和 连续负载电流,需满足PCB的最小覆铜尺寸要求,以确保 结温不升至125°C以上。图70至图77显示不同环境温度、功 耗和PCB覆铜面积下的结温计算结果。 Rev. G | Page 20 of 28

ADP7104 145 145 135 135 125 125 C) C) E (° 115 E (° 115 UR 105 UR 105 RAT 95 RAT 95 E E MP 85 MP 85 E E N T 75 N T 75 TIO 65 TIO 65 C C N 55 N 55 U U J 45 6400mm2 J 45 6400mm2 500mm2 500mm2 35 25mm2 35 25mm2 TJMAX TJMAX 250 0.2 0.4 0.T6OT0A.8L P1O.0WE1R. 2DIS1S.4IPA1T.I6ON1 (.W8)2.0 2.2 2.4 09507-065 250 0.2 0.4 0.T6OT0A.8L P1O.0WE1R. 2DIS1S.4IPA1T.I6ON1 (.W8)2.0 2.2 2.4 09507-068 图70. LFCSP,T = 25°C 图73. SOIC,T = 25°C A A 140 140 130 130 C) 120 C) 120 E (° E (° UR 110 UR 110 T T A A ER 100 ER 100 P P M M E 90 E 90 T T N N TIO 80 TIO 80 C C N N U 70 U 70 J 6400mm2 J 6400mm2 60 52050mmmm22 60 52050mmmm22 TJMAX TJMAX 500 0.2 0.4TOTA0L.6 POW0E.8R DIS1S.0IPATI1O.2N (W)1.4 1.6 1.8 09507-066 500 0.2 0.4TOTA0L.6 POW0E.8R DIS1S.0IPATI1O.2N (W)1.4 1.6 1.8 09507-069 图71. LFCSP,T = 50°C 图74 .SOIC,T = 50°C A A 145 145 135 135 C) C) E (° 125 E (° 125 R R U U AT 115 AT 115 R R E E MP 105 MP 105 E E T T ON 95 ON 95 TI TI C C N 85 N 85 U U J 6400mm2 J 6400mm2 75 500mm2 75 500mm2 25mm2 25mm2 TJMAX TJMAX 650 0.1 0.2TO0T.A3L P0O.W4ER0 D.5ISSIP0.A6TION0. 7(W)0.8 0.9 1.0 09507-067 650 0.1 0.2TO0T.A3L P0O.4WER0 D.5ISSI0P.A6TION0. 7(W)0.8 0.9 1.0 09507-070 图72. LFCSP,T= 85°C 图75. SOIC,T= 85°C A A Rev. G | Page 21 of 28

ADP7104 140 在已知板温的情况下,可以利用热特性参数(Ψ )来估算结 JB 温上升情况(见图76和图77)。最高结温(T )可由板温度(T ) 120 J B 和功耗(PD)通过下式计算: T)J E ( 100 R T = T + (P × Ψ ) (5) U J B D JB T A R 80 8引脚LFCSP封装的Ψ 典型值为15.1°C/W,8引脚SOIC封装 E JB MP 为31.3°C/W。 TE 60 N O TI C 40 N 140 JU TB = 25°C 20 TTBB == 5605°°CC 120 TB = 85°C TJMAX URE (T)J 100 00 0.5 TO1.T0AL POW1.5ER DISS2.I0PATION2 (.W5) 3.0 3.5 09507-072 T A 图77. SOIC封装 R 80 E MP E T 60 N O TI C 40 N JU TB = 25°C 20 TTBB == 5605°°CC TB = 85°C TJMAX 00 0.5 1.0 1.5TO2.T0AL2 .P5OW3.0ER3 D.5IS4S.I0PA4T.I5ON5 .(0W)5.5 6.0 6.5 7.0 09506-071 图76. LFCSP封装 Rev. G | Page 22 of 28

印刷电路板布局考量 通过增加ADP7104引脚处的覆铜用量,可改善封装的散热 性能。但是,如表6所示,这种增加存在效益递减现象,当 覆铜量达到某一数量点后,再继续增加覆铜的用量并不会 带来明显的散热效益。 输入电容应尽可能靠近VIN和GND引脚放置。输出电容应 尽可能靠近VOUT和GND引脚放置。在板面积受限的情况 下,采用0805或0603尺寸的电容和电阻可实现最小尺寸解 决方案。 09507-074 图79. SOIC PCB布局示例 09507-073 图78. LFCSP PCB布局示 例 Rev. G | Page 23 of 28

ADP7104 外形尺寸 3.10 2.48 3.00 SQ 2.38 2.90 2.23 5 8 EXPOSED 1.74 PAD 1.64 0.50 1.49 0.40 IANRDEEXA 0.30 4 1 0.20 MIN TOP VIEW BOTTOM VIEW PIN 1 INDICATOR 0.80 0.80 MAX (R 0.2) 0.55 NOM 0.75 FOR PROPER CONNECTION OF 0.70 0.05 MAX THE EXPOSED PAD, REFER TO 0.02 NOM THE PIN CONFIGURATION AND COPLANARITY FUNCTION DESCRIPTIONS 0.08 SECTION OF THIS DATA SHEET. SEPALTAINNGE 0.30 0.50 BSC 0.20 REF 0.25 0.18 COMPLIANTTOJEDEC STANDARDS MO-229-WEED-4 02-05-2013-B 图80. 8引脚引脚架构芯片级封装[LFCSP_WD] 3 mm x 3 mm,超薄体,双排引脚 (CP-8-5) 图示尺寸单位:mm 5.00 3.098 4.90 4.80 0.356 8 5 6.20 4.00 6.00 3.90 5.80 2.41 3.80 0.457 1 4 FOR PROPER CONNECTION OF 1.27 BSC BOTTOM VIEW THE EXPOSED PAD, REFER TO 3.81 REF THE PIN CONFIGURATION AND FUNCTION DESCRIPTIONS TOP VIEW SECTION OF THIS DATA SHEET. 1.75 1.65 0.50 45° 1.35 1.25 0.25 0.25 0.17 0.10 MAX SEATING PLANE 0.51 0.05 NOM 8° 1.04 REF 0.31 COPL0A.1N0ARITY 0° 10..2470 COMPLIANTTO JEDEC STANDARDS MS-012-AA 06-03-2011-B 图81. 8引脚标准小型封装,带裸露焊盘[SOIC_N_EP] 窄体 (RD-8-2) 尺寸单位:mm Rev. G | Page 24 of 28

ADP7104 订购指南 型号1 温度范围 输出电压(V)2, 3 封装描述 封装选项 标识 ADP7104ACPZ-R7 −40°C至+125°C 可调 8 引脚 LFCSP_WD CP-8-5 LH1 ADP7104ACPZ-1.5-R7 −40°C至+125°C 1.5 8 引脚 LFCSP_WD CP-8-5 LK6 ADP7104ACPZ-1.8-R7 −40°C至+125°C 1.8 8 引脚 LFCSP_WD CP-8-5 LK7 ADP7104ACPZ-2.5-R7 −40°C至+125°C 2.5 8 引脚 LFCSP_WD CP-8-5 LKJ ADP7104ACPZ-3.0-R7 −40°C至+125°C 3.0 8 引脚 LFCSP_WD CP-8-5 LKK ADP7104ACPZ-3.3-R7 −40°C至+125°C 3.3 8 引脚 LFCSP_WD CP-8-5 LKL ADP7104ACPZ-5.0-R7 −40°C至+125°C 5 8 引脚 LFCSP_WD CP-8-5 LKM ADP7104ACPZ-9.0-R7 −40°C至+125°C 9 8 引脚 LFCSP_WD CP-8-5 LLD ADP7104ARDZ-R7 −40°C至+125°C 可调 8 引脚 SOIC_N_EP RD-8-2 ADP7104ARDZ-1.5-R7 −40°C至+125°C 1.5 8 引脚 SOIC_N_EP RD-8-2 ADP7104ARDZ-1.8-R7 −40°C至+125°C 1.8 8 引脚 SOIC_N_EP RD-8-2 ADP7104ARDZ-2.5-R7 −40°C至+125°C 2.5 8 引脚 SOIC_N_EP RD-8-2 ADP7104ARDZ-3.0-R7 −40°C至+125°C 3.0 8 引脚 SOIC_N_EP RD-8-2 ADP7104ARDZ-3.3-R7 −40°C至+125°C 3.3 8 引脚 SOIC_N_EP RD-8-2 ADP7104ARDZ-5.0-R7 −40°C至+125°C 5 8 引脚 SOIC_N_EP RD-8-2 ADP7104ARDZ-9.0-R7 −40°C至+125°C 9 8 引脚 SOIC_N_EP RD-8-2 ADP7104CP-EVALZ 3.3 LFCSP评估板 ADP7104RD-EVALZ 3.3 SOIC评估板 ADP7104CPZ-REDYKIT LFCSP REDYKIT ADP7104RDZ-REDYKIT SOIC REDYKIT 1 Z = 符合RoHS标准的器件 。 2 如需其它电压选项,请联系当地的ADI公司办事处或代理商。 3 ADP7104CP-EVALZ和ADP7104RD-EVALZ评估板预配置有3.3 V ADP7104。 Rev. G | Page 25 of 28

ADP7104 注释 Rev. G | Page 26 of 28

ADP7104 注释 Rev. G | Page 27 of 28

ADP7104 注释 ©2011–2014 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D09507sc-0-5/14(G) Rev. G | Page 28 of 28

Datasheet下载

Datasheet下载