ICGOO在线商城 > 射频/IF 和 RFID > RF 混频器 > ADL5802ACPZ-R7

- 型号: ADL5802ACPZ-R7

- 制造商: Analog

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

ADL5802ACPZ-R7产品简介:

ICGOO电子元器件商城为您提供ADL5802ACPZ-R7由Analog设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 ADL5802ACPZ-R7价格参考¥70.53-¥77.72。AnalogADL5802ACPZ-R7封装/规格:RF 混频器, RF Mixer IC Cellular 100MHz ~ 6GHz 24-LFCSP-WQ (4x4)。您可以下载ADL5802ACPZ-R7参考资料、Datasheet数据手册功能说明书,资料中有ADL5802ACPZ-R7 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | |

| 描述 | IC MIXER 100MHZ-6GHZ 24LFCSP射频混合器 Dual WB Active Mixer in XFCB3 "DRx" |

| 产品分类 | |

| 品牌 | Analog Devices Inc |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | RF集成电路,射频混合器,Analog Devices ADL5802ACPZ-R7- |

| 数据手册 | |

| 产品型号 | ADL5802ACPZ-R7 |

| PCN组件/产地 | |

| RF类型 | 手机 |

| 产品种类 | 射频混合器 |

| 供应商器件封装 | 24-LFCSP-VQ(4x4) |

| 其它名称 | ADL5802ACPZ-R7CT |

| 功率增益类型 | 1.6 dB |

| 包装 | 剪切带 (CT) |

| 商标 | Analog Devices |

| 噪声系数 | 11dB |

| 增益 | 7.6dB |

| 安装风格 | SMD/SMT |

| 封装 | Reel |

| 封装/外壳 | 24-VFQFN 裸露焊盘,CSP |

| 封装/箱体 | lFCSP-24 |

| 工作电源电压 | 5 V |

| 工厂包装数量 | 1500 |

| 最大功率耗散 | 1.6 W |

| 最大工作温度 | + 85 C |

| 最小工作温度 | - 40 C |

| 标准包装 | 1 |

| 混频器数 | 2 |

| 电压-电源 | 4.75 V ~ 5.25 V |

| 电流-电源 | 220mA |

| 电源电流 | 220 mA |

| 类型 | Mixer |

| 系列 | ADL5802 |

| 视频文件 | http://www.digikey.cn/classic/video.aspx?PlayerID=1364138032001&width=640&height=505&videoID=2245193150001 |

| 转换损失——最大 | 18 dB |

| 辅助属性 | - |

| 频率 | 100MHz ~ 6GHz |

| 频率范围 | 100 MHz to 6000 MHz |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

Dual Channel, High IP3, 100 MHz to 6 GHz Active Mixer Data Sheet ADL5802 FEATURES FUNCTIONAL BLOCK DIAGRAM Power conversion gain of 1.6 dB VPOSRF1+RF1–GNDRF2+RF2– Wideband RF, LO, and IF ports 24 23 22 21 20 19 SSB noise figure of 11 dB Input IP3 of 28 dBm GND 1 18 GND Input P1dB of 12 dBm GND 2 17 GND Typical LO drive of 0 dBm Low LO leakage OP1+ 3 16 OP2+ Single supply operation: 5 V @ 240 mA OP1– 4 15 OP2– Exposed paddle, 4 mm × 4 mm, 24-lead LFCSP package GND 5 14 GND APPLICATIONS ADL5802 IP3 VPOS 6 BIAS 13 VPOS Cellular base station receivers MRaadinio a lnindk d divoewrnsictoyn rveecertievresr designs EN7BLGN8D LO9IPLO10ING1N1DVS12ET 07882-001 Figure 1. GENERAL DESCRIPTION The ADL5802 uses high linearity, double-balanced, active mixer The IF outputs are designed for a 200 Ω source impedance and cores with integrated LO buffer amplifiers to provide high provide a typical voltage conversion gain of 7.6 dB when loaded dynamic range frequency conversion from 100 MHz to 6 GHz. into a 200 Ω load. The mixers benefit from a proprietary linearization architecture The ADL5802 is fabricated using a SiGe high performance IC that provides enhanced input IP3 performance when subject to process. The device is available in a compact 4 mm × 4 mm, high input levels. A bias adjust feature allows the input linearity, 24-lead LFCSP package and operates over a −40°C to +85°C SSB noise figure, and dc current to be optimized using a single temperature range. An evaluation board is also available. control pin. The high input linearity allows the device to be used in demanding cellular applications where in-band blocking signals may otherwise result in degradation in dynamic perform- ance. The balanced active mixer arrangement provides superb LO to RF and LO to IF leakage, typically better than −30 dBm. Rev. B Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. rliicgehntsse o ifs t hgirradn pteadrt bieys itmhaptl imcaatyio rne sourl to ftrhoemrw itiss ue suen. Sdpeer caifnicya ptiaotnesn st uobr jpecatt eton tc hriagnhgtse owf iAthnoaulot gn oDteicvei.c Neso. Tel: 781.329.4700 ©2009–2015 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of thei r respective owners. Technical Support www.analog.com

ADL5802 Data Sheet TABLE OF CONTENTS Features .............................................................................................. 1 Spur Performance ....................................................................... 21 Applications ....................................................................................... 1 Circuit Description......................................................................... 24 Functional Block Diagram .............................................................. 1 LO Amplifier and Splitter.......................................................... 24 General Description ......................................................................... 1 RF Voltage to Current (V-to-I) Converter .............................. 24 Revision History ............................................................................... 2 Mixer Cores ................................................................................. 24 Specifications ..................................................................................... 3 Mixer Load .................................................................................. 24 Absolute Maximum Ratings ............................................................ 5 Bias Circuit .................................................................................. 24 ESD Caution .................................................................................. 5 Applications Information .............................................................. 25 Pin Configuration and Function Descriptions ............................. 6 Basic Connections ...................................................................... 25 Typical Performance Characteristics ............................................. 7 RF and LO Ports ......................................................................... 25 Downconverter Mode Using a Broadband Balun .................... 7 IF Port .......................................................................................... 26 Downconverter Mode Using a Johanson 2.5 GHz Balun ..... 12 Evaluation Board ............................................................................ 27 Downconverter Mode Using a Johanson 3.5 GHz Balun ..... 15 Outline Dimensions ....................................................................... 29 Downconverter Mode Using a Johanson 5.5 GHz Balun ..... 18 Ordering Guide .......................................................................... 29 REVISION HISTORY 2/15—Rev. A to Rev. B Balun Section and Figure 44 ......................................................... 15 Changes to Figure 48 and Figure 49 ............................................ 16 Updated Outline Dimensions ....................................................... 29 Changes to Figure 53 ...................................................................... 17 Changes to Ordering Guide .......................................................... 29 Changed Downconverter Mode Using a Johanson 5.7 GHz 6/12—Rev. 0 to Rev. A Balun Section to Downconverter Mode Using a Johanson 5.5 Changes to Downconverter Mode Using a Broadband Balun GHz Balun Section ......................................................................... 18 Section and Figure 6 ......................................................................... 7 Changes to Downconverter Mode Using a Johanson 5.5 GHz Changes to Figure 11 ........................................................................ 8 Balun Section .................................................................................. 18 Changes to Figure 17, Figure 18, Figure 19, and Figure 20 ......... 9 Changes to Figure 61 and Figure 62 ............................................ 19 Changes to Figure 27 ...................................................................... 11 Changes to Figure 20 ...................................................................... 20 Changed Downconverter Mode Using a Johanson 2.7 GHz Changes to 900 MHz Performance Section and 2090 MHz Balun Section to Downconverter Mode Using a Johanson 2.5 GHz Performance Section ...................................................................... 21 Balun Section .................................................................................. 12 Changes to 2600 MHz Performance Section and 3500MHz Changes to Downconverter Mode Using a Johanson 2.5 GHz Performance Section ...................................................................... 22 Balun Section and Figure 31 ......................................................... 12 Changes to 5800 MHz Performance Section .............................. 23 Changes o Figure 35 and Figure 36 .............................................. 13 Updated Outline Dimensions ....................................................... 29 Changes to Figure 40 ...................................................................... 14 11/09—Revision 0: Initial Version Changes to Downconverter Mode Using a Johanson 3.5 GHz Rev. B | Page 2 of 32

Data Sheet ADL5802 SPECIFICATIONS V = 5 V, VSET = 4 V, T = 25°C, f = (f − 153) MHz, LO power = 0 dBm, Z1 = 50 Ω, unless otherwise noted. S A LO RF 0 Table 1. Parameter Test Conditions/Comments Min Typ Max Unit RF INPUT INTERFACE Return Loss Tunable to >20 dB over a limited bandwidth 18 dB Input Impedance 50 Ω RF Frequency Range 100 6000 MHz OUTPUT INTERFACE Output Impedance Differential impedance, f = 200 MHz 240 Ω IF Frequency Range Can be matched externally to 3000 MHz LF 600 MHz DC Bias Voltage2 Externally generated 4.75 V 5.25 V S LO INTERFACE LO Power −10 0 +10 dBm Return Loss 18 dB Input Impedance 50 Ω LO Frequency Range 100 6000 MHz POWER INTERFACE Supply Voltage 4.75 5 5.25 V Quiescent Current Resistor programmable 220 300 mA Disable Current ENBL pin low 170 mA Enable Time Time from ENBL pin low to power-up 182 ns Disable Time Time from ENBL pin high to power-down 28 ns DYNAMIC PERFORMANCE at f = 900 MHz/1900 MHz RF Power Conversion Gain3 f = 900 MHz 1.5 dB RF f = 1900 MHz 1.6 dB RF Voltage Conversion Gain4 f = 900 MHz 7.5 dB RF f = 1900 MHz 7.6 dB RF SSB Noise Figure f = 900 MHz 10 dB CENT f = 1900 MHz 11 dB CENT SSB Noise Figure Under Blocking5 f = 900 MHz 18 dB CENT f = 1900 MHz 22 dB CENT Input Third Order Intercept6 f = 890 MHz 26 dBm CENT f = 1890 MHz 28 dBm CENT Input Second Order Intercept7 f = 890 MHz 60 dBm CENT f = 1890 MHz 45 dBm CENT Input 1 dB Compression Point f = 900 MHz 12 dBm RF f = 1900 MHz 12 dBm RF LO to IF Output Leakage Unfiltered IF output −35 dBm LO to RF Input Leakage −30 dBm RF to IF Output Isolation 25 dBc RFI1 to RFI2 Channel Isolation 45 dBc IF/2 Spurious8 0 dBm input power, f = 900 MHz −68 dBc RF IF/3 Spurious8 0 dBm input power, f = 900 MHz −67 dBc RF IF/2 Spurious8 0 dBm input power, f = 1900 MHz −53 dBc RF IF/3 Spurious8 0 dBm input power, f = 1900 MHz −59 dBc RF DYNAMIC PERFORMANCE at f = 2500 MHz9 RF Power Conversion Gain10 −0.5 dB Voltage Conversion Gain4 5.67 dB SSB Noise Figure 11.5 dB SSB Noise Figure Under Blocking11 f = 2145 MHz 18 dB CENT Input Third Order Intercept6 f = 2500 MHz 30 dBm CENT Rev. B | Page 3 of 32

ADL5802 Data Sheet Parameter Test Conditions/Comments Min Typ Max Unit Input Second Order Intercept7 f = 2500 MHz 47 dBm CENT Input 1 dB Compression Point 13 dBm LO to IF Output Leakage Unfiltered IF output 36 dBm LO to RF Input Leakage 31 dBm RF to IF Output Isolation 26 dBc RFI1 to RFI2 Channel Isolation 42 dBc IF/2 Spurious8 0 dBm input power −52 dBc IF/3 Spurious8 0 dBm input power −56 dBc DYNAMIC PERFORMANCE at f = 3500 MHz12 RF Power Conversion Gain13 −0.5 dB Voltage Conversion Gain4 5.5 dB SSB Noise Figure 12.5 dB SSB Noise Figure Under Blocking14 f = 3500 MHz 18 dB CENT Input Third Order Intercept5 f = 3500 MHz 25 dBm CENT Input Second Order Intercept7 f = 3500 MHz 39 dBm CENT Input 1 dB Compression Point 13 dBm LO to IF Output Leakage Unfiltered IF output 33 dBm LO to RF Input Leakage 28 dBm RF to IF Output Isolation 31 dBc RFI1 to RFI2 Channel Isolation 39 dBc IF/2 Spurious8 0 dBm input power −46 dBc IF/3 Spurious8 0 dBm input power −63 dBc DYNAMIC PERFORMANCE at f = 5500 MHz15 RF Power Conversion Gain16 −3 dB Voltage Conversion Gain4 5.67 dB SSB Noise Figure 14 dB SSB Noise Figure Under Blocking17 f = 5800 MHz 17 dB CENT Input Third Order Intercept5 f = 5500 MHz 23 dBm CENT Input Second Order Intercept7 f = 5500 MHz 35 dBm CENT Input 1 dB Compression Point 13 dBm LO to IF Output Leakage Unfiltered IF output 42 dBm LO to RF Input Leakage 27 dBm RF to IF Output Isolation 50 dBc RFI1 to RFI2 Channel Isolation 33 dBc IF/2 Spurious8 0 dBm input power −49 dBc IF/3 Spurious8 0 dBm input power −64 dBc 1 Z0 is the characteristic impedance assumed for all measurements and the PCB. 2 Supply voltage must be applied from an external circuit through choke inductors. 3 Excluding 4:1 IF port transformer (TC4-1W+), RF and LO port transformers (TC1-1-13M+), and PCB loss. 4 ZSOURCE = 50 Ω, differential; ZLOAD = 200 Ω, differential 5 dBm; ZSOURCE is the impedance of the source instrument; ZLOAD is the load impedance at the output. 5 fRF1 = fCENT, fBLOCKER = (fCENT − 5) MHz, fLO = (fCENT − 153) MHz, blocker level = 0 dBm. 6 fRF1 = (fCENT − 1) MHz, fRF2 = fCENT, fLO = (fCENT − 153) MHz, each RF tone at −10 dBm. 7 fRF1 = fCENT, fRF2 = (fCENT + 100) MHz, fLO = (fCENT − 153) MHz, each RF tone at −10 dBm. 8 For details, see the Spur Performance section. 9 VS = 5 V, VSET = 4.5 V, TA = 25°C, fLO = (fRF − 211) MHz, LO power = 0 dBm, Z0 = 50 Ω. 10 Excluding 4:1 IF port transformer (TC4-1W+), RF and LO port transformers (2500BL14M050), and PCB loss. 11 fRF1 = fCENT, fBLOCKER = (fCENT − 5) MHz, fLO = (fCENT − 235) MHz, blocker level = 0 dBm. 12 VS = 5 V, VSET = 5 V, TA = 25°C, fLO = (fRF − 153) MHz, LO power = 0 dBm, Z0 = 50 Ω. 13 Including 4:1 IF port transformer (TC4-1W+), RF and LO port transformers (3600BL14M050), and PCB loss. 14 fRF1 = fCENT, fBLOCKER = (fCENT − 5) MHz, fLO = (fCENT − 153) MHz, blocker level = −20 dBm. 15 VS = 5 V, VSET = 4.8 V, TA = 25°C, fLO = (fRF − 380) MHz, LO power = 0 dBm, Z0 = 50 Ω. 16 Including 4:1 IF port transformer (TC4-1W+), RF and LO port transformers (5400BL15B050), and PCB loss. 17 fRF1 = fCENT, fBLOCKER = (fCENT − 5) MHz, fLO = (fCENT − 300) MHz, blocker level = −20 dBm. Rev. B | Page 4 of 32

Data Sheet ADL5802 ABSOLUTE MAXIMUM RATINGS Table 2. Stresses at or above those listed under Absolute Maximum Parameter Rating Ratings may cause permanent damage to the product. This is a Supply Voltage, VPOS 5.5 V stress rating only; functional operation of the product at these VSET, ENBL 5.5 V or any other conditions above those indicated in the operational OP1+, OP1−, OP2+, OP2− 5.5 V section of this specification is not implied. Operation beyond RF Input Power 20 dBm the maximum operating conditions for extended periods may Internal Power Dissipation 1.6 W affect product reliability. θJA (Exposed Paddle Soldered Down)1 26.5°C/W ESD CAUTION θ (at Exposed Paddle) 8.7°C/W JC Maximum Junction Temperature 150°C Operating Temperature Range −40°C to +85°C Storage Temperature Range −65°C to +150°C 1 As measured on the evaluation board. For details, see the Evaluation Board section. Rev. B | Page 5 of 32

ADL5802 Data Sheet PIN CONFIGURATION AND FUNCTION DESCRIPTIONS SOP+1F–1FDN+2F–2F VRRGRR 432109 222221 PIN 1 GND 1 INDICATOR 18GND GND 2 17GND OP1+ 3 ADL5802 16OP2+ OP1– 4 TOP VIEW 15OP2– GND 5 (Not to Scale) 14GND VPOS 6 13VPOS 789011121 LBNEDNGPIOLNIOLDNGTESV 07882-002 NOTES 1. THERE ISAN EXPOSEDPADDLE THAT MUST BE SOLDEREDTO GROUND. Figure 2. Pin Configuration Table 3. Pin Function Descriptions Pin No. Mnemonic Function 1, 2, 5, 8, 11, GND Device Common (DC Ground). 14, 17, 18, 21 3, 4 OP1+, OP1− Channel 1 Mixer Differential Output Terminals. Bias must be applied through pull-up choke inductors or the center tap of the IF transformer. 6, 13, 24 VPOS Positive Supply Voltage. 5.0 V nominal. 7 ENBL Device Enable. Pull low or leave disconnected to enable the device; pull high to disable the device. 9, 10 LOIP, LOIN Differential LO Input Terminals. Internally matched to 50 Ω; must be ac-coupled. 12 VSET High Input IP3 Bias Control. For high input IP3 performance, apply ~4 V to 5 V. Improved noise figure (NF) performance and lower supply current can be set by applying ~2 V to 3 V to the VSET pin. A resistor can be connected to the supply to raise the voltage, whereas a resistor to GND lowers the voltage. 15, 16 OP2−, OP2+ Channel 2 Mixer Differential Output Terminals. Bias must be applied through pull-up choke inductors or the center tap of the IF transformer. 19, 20 RF2−, RF2+ Differential RF Input Terminals for Channel 2. Internally matched to 50 Ω; must be ac-coupled. 22, 23 RF1−, RF1+ Differential RF Input Terminals for Channel 1. Internally matched to 50 Ω; must be ac-coupled. EPAD Exposed Paddle. Must be soldered to ground. Rev. B | Page 6 of 32

Data Sheet ADL5802 TYPICAL PERFORMANCE CHARACTERISTICS DOWNCONVERTER MODE USING A BROADBAND BALUN V = 5 V, T = 25°C, VSET = 4 V, IF = 153 MHz, as measured using a typical circuit schematic with low-side local oscillator (LO), unless S A otherwise noted. Insertion loss of input and output baluns (TC1-1-13M+, TC4-1W+) is extracted from the gain measurement. 6 4.0 35 GAIN = 900MHz 5 GAIN = 1900MHz INPUT IP3 = 900MHz 3.5 INPUT IP3 = 1900MHz 30 4 3 TA = –40°C TA = +25°C 3.0 25 m) B) 2 B) dB N (d 1 N(d2.5 20 P3 ( AI AI T I G 0 G PU TA = +85°C 2.0 15 IN –1 –2 1.5 10 ––340 500 1000RF F1R5E0Q0UEN2C0Y0 0(MHz)2500 3000 350007882-003 1.0–15 –10 –5LOPOW0ER(dBm)5 10 155 07882-006 Figure 3. Power Conversion Gain vs. RF Frequency Figure 6. Power Conversion Gain and Input IP3 vs. LO Power 4.0 100 MEAN = 1.5 3.5 SD = 0.039 80 3.0 2.5 %) B) Y ( 60 d C N (2.0 900MHz EN GAI QU E 40 1.5 R 1900MHz F 1.0 20 0.50 07882-004 0 07882-007 0 50 100 150 200 250 0 8 6 4 2 0 8 6 4 2 0 8 6 0 0 1 2 3 4 4 5 6 7 8 8 9 IF FREQUENCY (MHz) 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. GAIN (dB) Figure 4. Power Conversion Gain vs. IF Frequency Figure 7. Power Conversion Gain Distribution 3.0 0.30 2.5 2.5 0.25 2.0 TA =–40°C A) 2.0 0.20 T ( TA =+25°C GAIN (dB) 1.5 0.15 LY CURREN GAIN (dB)11..50 TA =+85°C P 1.0 0.10 UP S 0.5 GAIN = 900MHz 0.05 0.5 GAIN = 1900MHz 0 IIPPOOSS == 910900M0MHHzz 0 07882-005 0 07882-008 0 1 2 3 4 5 6 4.7 4.8 4.9 5.0 5.1 5.2 5.3 VSET (V) SUPPLY (V) Figure 5. Power Conversion Gain and IPOS vs. VSET Figure 8. Power Conversion Gain vs. Supply Voltage Rev. B | Page 7 of 32

ADL5802 Data Sheet V = 5 V, T = 25°C, VSET = 4 V, IF = 153 MHz, as measured using a typical circuit schematic with low-side local oscillator (LO), unless S A otherwise noted. Insertion loss of input and output baluns (TC1-1-13M+, TC4-1W+) is extracted from the gain measurement. 40 80 TA = +25°C TA = –40°C 35 70 TA = +85°C 30 60 TA = +85°C Bm)25 Bm)50 TA = +25°C P3 (d20 TA = –40°C P2 (d40 UTI UTI NP15 NP30 I I 10 20 50 07882-009 100 07882-012 0 500 1000 1500 2000 2500 3000 3500 0 500 1000 1500 2000 2500 3000 3500 RF FREQUENCY (MHz) RF FREQUENCY (MHz) Figure 9. Input IP3 vs. RF Frequency Figure 12. Input IP2 vs. RF Frequency 40 80 70 35 900MHz 60 INPUTIP3 (dBm) 223050 1990000MMHHzz INPUT IP2 (dBm)345000 1900MHz 20 15 10 07882-010 100 07882-013 0 50 100 150 200 250 0 50 100 150 200 250 IF FREQUENCY (MHz) IF FREQUENCY (MHz) Figure 10. Input IP3 vs. IF Frequency Figure 13. Input IP2 vs. IF Frequency 35 80 B) d E (30 70 R E FIGU25 60 900MHz OIS Bm) 50 m) AND SSB N1250 INPUTIP2 (d 3400 1900MHz 3 (dB10 20 IP INPUTIP3 = 900MHz INPUT 05 INNNFFP ==U T9109IP00M03M H=H z1z900MHz 07882-011 100 07882-014 0 1 2 3 4 5 6 0 1 2 3 4 5 6 VSET (V) VSET (V) Figure 11. Input IP3, Noise Figure vs. VSET Figure 14. Input IP2 vs. VSET Rev. B | Page 8 of 32

Data Sheet ADL5802 V = 5 V, T = 25°C, VSET = 4 V, IF = 153 MHz, as measured using a typical circuit schematic with low-side local oscillator (LO), unless S A otherwise noted. Insertion loss of input and output baluns (TC1-1-13M+, TC4-1W+) is extracted from the gain measurement. 20 25 18 16 20 P1dB(dBm) 1124 TA = –40°C TA = +85°C URE (dB)15 NF vs. IF, RF = 1900MHz UT 10 FIG INP 8 TA = +25°C OISE 10 6 N NF vs. IF, RF = 900MHz 4 5 02 07882-015 0 07882-018 0 500 1000 1500 2000 2500 3000 3500 0 100 200 300 400 500 600 700 RF FREQUENCY (MHz) IFFREQUENCY(MHz) Figure 15. Input P1dB vs. RF Frequency Figure 18. SSB Noise Figure vs. IF Frequency (VSET = 2.0 V) 20 30 18 25 16 dBm) 1142 900MHz E (dB) 20 NF, RF 1846MHz, P1dB ( 10 1900MHz FIGUR 15 IF 153MHz, BLOCKER 1841MHz UT 8 SE INP 6 NOI 10 NF, RF 951MHZ, IF 153MHz, BLOCKER 946MHz 4 5 02 07882-016 0 07882-019 0 50 100 150 200 250 –30 –25 –20 –15 –10 –5 0 5 10 IF FREQUENCY (MHz) BLOCKER LEVEL (dBm) Figure 16. Input P1dB vs. IF Frequency Figure 19. SSB Noise Figure vs. Blocker Level (VSET = 2.0 V) 18 20 16 18 B) 14 TA = +85°C 16 NOISE FIGURE (d 11802 TA = +25°C TA = –40°C SE FIGURE (dB) 1110248 1990000MMHHzz OI 6 N 6 4 4 02 07882-017 20 07882-020 0 500 1000 1500 2000 2500 3000 3500 –15 –10 –5 0 5 10 15 RF FREQUENCY (MHz) LO LEVEL (dBm) Figure 17. SSB Noise Figure vs. RF Frequency (VSET = 2.0 V) Figure 20. SSB Noise Figure vs. LO Drive (VSET = 2.0 V) Rev. B | Page 9 of 32

ADL5802 Data Sheet V = 5 V, T = 25°C, VSET = 4 V, IF = 153 MHz, as measured using a typical circuit schematic with low-side local oscillator (LO), unless S A otherwise noted. Insertion loss of input and output baluns (TC1-1-13M+, TC4-1W+) is extracted from the gain measurement. –0 –10 RFRETURNLOSS5500MHz BALUN: 5400BL15B0503pFINPUTCAPACITANCE –15 –5 –20 –10 m) B) dB –25 TA = –40°C S (d–15 GE ( –30 TA = +25°C S A O K L–20 A –35 RETURN –25 3600RBFLR1E4TMU0R50N1L.5OpSFSIN3P50U0TMCHAzP BAACLIUTANN:CE TO IF LE –40 TA = +85°C RFRETURNLOSS2500MHz BALUN: O –45 –30 2500BL14M0503pFINPUTCAPACITANCE L –50 ––4305 RTCF1R-1E-T1U3MRN+1L0O0SpSFI9N0P0UMTHzC AANPDAC1I9T0A0NMCHEzBALUN: 07882-021 ––6505 07882-024 0 1000 2000 3000 4000 5000 6000 7000 0 500 1000 1500 2000 2500 3000 3500 FREQUENCY (MHz) LO FREQUENCY (MHz) Figure 21. RF Return Loss Measured Differentially at the RF Port Figure 24. LO to IF Leakage vs. LO Frequency 0 –10 LO RETURN LOSS 2500MHz BALUN: IN2P5U00TB CLA1P4MAC05IT0A 3NpCFE LO RETU5R4N0 0LBOLS1S5 B5055000 M3pHFz BALUN: –15 –5 INPUT CAPACITANCE –20 m) TA = +85°C N LOSS (dB)––1150 LEAKAGE (dB –––323550 TA = +25°C RETUR–20 LTINOCP1 UR-1TE- T1CU3AMRPN+A 1CL0OIT0SpASFN CBEALUN: O TO RF ––4450 TA = –40°C L –50 –25 –30 LO RETIU3N6RP0NU0 TBL LOC1AS4SPM A30C550I0T0 A1M.N5HCpzFE BALUN: 07882-022 ––6505 07882-025 0 1000 2000 3000 4000 5000 6000 7000 0 500 1000 1500 2000 2500 3000 3500 FREQUENCY (MHz) LO FREQUENCY (MHz) Figure 22. LO Return Loss Measured Differentially at the LO Port Figure 25. LO to RF Leakage vs. LO Frequency 500 8 0 Bc) –10 400 6 d N ( O STANCE (Ω) 300 RESISTANCE 4 CITANCE (pF) PUT ISOLATI ––3200 TTAA = = + +8255°C°C RESI 200 2 CAPA F OUT –40 100 CAPACITANCE 0 F TO I TA = –40°C R –50 0 –2 07882-023 –60 07882-026 10 100 1000 3000 0 500 1000 1500 2000 2500 3000 3500 IF FREQUENCY (MHz) RF FREQUENCY (MHz) Figure 23. IF Differential Output Impedance (R Parallel C Equivalent) Figure 26. RF to IF Output Isolation vs. RF Frequency Rev. B | Page 10 of 32

Data Sheet ADL5802 V = 5 V, T = 25°C, VSET = 4 V, IF = 153 MHz, as measured using a typical circuit schematic with low-side local oscillator (LO), unless S A otherwise noted. Insertion loss of input and output baluns (TC1-1-13M+, TC4-1W+) is extracted from the gain measurement. 70 B)65 d N (60 O ATI55 TA = –40°C OL TA = +25°C EL IS50 HANN45 TA = +85°C C40 O- L-T35 E NN30 A CH2205 07882-027 0 500 1000 1500 2000 2500 3000 3500 RF FREQUENCY (MHz) Figure 27. Channel-to-Channel Isolation Rev. B | Page 11 of 32

ADL5802 Data Sheet DOWNCONVERTER MODE USING A JOHANSON 2.5 GHZ BALUN V = 5 V, T = 25°C, VSET = 4.5 V, IF = 211 MHz, as measured using a typical circuit schematic with low-side LO, unless otherwise noted. S A Insertion loss of input and output baluns (2500BL14M050, TC4-1W+) is included in the gain measurement. 5 35 B) 4 RE (d30 3 GU 2 E FI25 S N (dB) 01 TA = –40°C TA = +25°C SSB NOI20 INPUTIP3 GAI–1 AND 15 m) –2 TA = +85°C 3 (dB10 NOISE FIGURE –3 P I T 5 ––54 07882-028 INPU 0 07882-031 1900 2100 2300 2500 2700 2900 3100 0 1 2 3 4 5 6 RF FREQUENCY (MHz) VSET (V) Figure 28. Power Conversion Gain vs. RF Frequency Figure 31. Input IP3, Noise Figure vs. VSET 5 0.30 60 4 0.27 55 3 IPOS 0.24 TA = +85°C 2 0.21 A) T ( m)50 TA = –40°C GAIN (dB)–101 GAIN 000...111852 PLY CURREN NPUTIP2 (dB45 TA = +25°C –2 0.09 SUP I40 –3 0.06 35 ––54 00.03 07882-029 30 07882-032 0 1 2 3 4 5 6 1900 2100 2300 2500 2700 2900 3100 VSET (V) RF FREQUENCY (MHz) Figure 29. Power Conversion Gain and IPOS vs. VSET Figure 32. Input IP2 vs. RF Frequency 35 50 TA = +85°C TA = +25°C 48 30 46 25 44 m) TA = –40°C m) B B42 d 20 d 3 ( 2 ( P P40 UTI 15 UT I P P38 N N I I 10 36 34 5 0 07882-030 3302 07882-033 1900 2100 2300 2500 2700 2900 3100 0 1 2 3 4 5 6 RF FREQUENCY (MHz) VSET (V) Figure 30. Input IP3 vs. RF Frequency Figure 33. Input IP2 vs. VSET Rev. B | Page 12 of 32

Data Sheet ADL5802 V = 5 V, T = 25°C, VSET = 4.5 V, IF = 211 MHz, as measured using a typical circuit schematic with low-side LO, unless otherwise noted. S A Insertion loss of input and output baluns (2500BL14M050, TC4-1W+) is included in the gain measurement 15 0 TA = +25°C TA = +85°C –5 14 –10 m) 13 B –15 Bm) TA = –40°C E (d d G –20 P1dB (12 EAKA –25 INPUT 1101 O TO IF L ––3350 TA = –40°C L –40 TA = +25°C 89 07882-034 ––5405 TA = +85°C 07882-037 1900 2100 2300 2500 2700 2900 3100 1900 2100 2300 2500 2700 2900 3100 RF FREQUENCY (MHz) LO FREQUENCY (MHz) Figure 34. Input P1dB vs. RF Frequency Figure 37. LO to IF Leakage vs. LO Frequency 20 –30 TA = +85°C 18 –31 TA = +25°C 16 –32 NOISE FIGURE (dB)11102468 TA = +85°TCA = –4T0°AC = +25°C LO TO RF LEAKAGE (dBm) –––––3333376543 TA = –40°C 4 –38 02 07882-035 ––4309 07882-038 1800 2000 2200 2400 2600 2800 3000 1900 2100 2300 2500 2700 2900 3100 RF FREQUENCY (MHz) LO FREQUENCY (MHz) Figure 35. SSB Noise Figure vs. RF Frequency (VSET = 2.0 V) Figure 38. LO to RF Leakage vs. LO Frequency 30 –21 c) 25 dB–23 ON ( TA = –40°C TA = +25°C E (dB)20 OLATI–25 NOISE FIGUR1105 IF 230MNHFz,, RBFL O21C4K5EMRH 2z,140MHz O IF OUTPUT IS–––322197 TA = +85°C T F 05 07882-036 R––3353 07882-039 –60 –50 –40 –30 –20 –10 0 10 1900 2100 2300 2500 2700 2900 3100 BLOCKER LEVEL (dBm) RF FREQUENCY (MHz) Figure 36. SSB Noise Figure vs. Blocker Level (VSET = 2.0 V) Figure 39. RF to IF Output Isolation vs. RF Frequency Rev. B | Page 13 of 32

ADL5802 Data Sheet V = 5 V, T = 25°C, VSET = 4.5 V, IF = 211 MHz, as measured using a typical circuit schematic with low-side LO, unless otherwise noted. S A Insertion loss of input and output baluns (2500BL14M050, TC4-1W+) is included in the gain measurement 50 B)48 d ON (46 TI TA = –40°C A44 L O EL IS42 NN40 A TA = +25°C CH38 TA = +85°C L-TO-36 E NN34 A CH3302 07882-040 1900 2100 2300 2500 2700 2900 3100 RF FREQUENCY (MHz) Figure 40. Channel-to-Channel Isolation Rev. B | Page 14 of 32

Data Sheet ADL5802 DOWNCONVERTER MODE USING A JOHANSON 3.5 GHZ BALUN V = 5 V, T = 25°C, VSET = 5 V, IF = 153 MHz, as measured using a typical circuit schematic with low-side LO, unless otherwise noted. S A Insertion loss of input and output baluns (3600BL14M050, TC4-1W+) is included in the gain measurement. 5 25 30 4 3 20 25 INPUT IP3 B) 2 d GAIN (dB) –101 TA = –40°C TA = +25°C PUT IP3 (dBm)1105 NOISE FIGURE 1250 OISE FIGURE ( N N I B –2 S TA = +85°C S –3 5 10 ––542900 3100 33R0F0 FREQ3U5E0N0CY (MH37z0)0 3900 41007882-0410 00 1 2 VSE3T (V) 4 5 65 07882-044 Figure 41. Power Conversion Gain vs. RF Frequency Figure 44. Input IP3, Noise Figure vs. VSET 5 0.30 50 4 0.27 48 3 0.24 46 2 IPOS 0.21 T (A) m)44 TA = –40°C GAIN (dB)–101 GAIN 000...111852 LY CURREN PUT IP2 (dB434082 TA = +85°C TA = +25°C P N –2 0.09 SUP I36 –3 0.06 34 ––54 00.03 07882-042 3302 07882-045 0 1 2 3 4 5 6 2900 3100 3300 3500 3700 3900 4100 VSET (V) RF FREQUENCY (MHz) Figure 42. Power Conversion Gain and IPOS vs. VSET Figure 45. Input IP2 vs. RF Frequency 30 50 TA = +85°C TA = +25°C 48 25 46 TA = –40°C 44 m) 20 m) B B42 d d 3 ( 2 ( P 15 P40 T I T I U U P P38 N N I 10 I 36 34 5 0 07882-043 3302 07882-046 2900 3100 3300 3500 3700 3900 4100 0 1 2 3 4 5 6 RF FREQUENCY (MHz) VSET (V) Figure 43. Input IP3 vs. RF Frequency Figure 46. Input IP2 vs. VSET Rev. B | Page 15 of 32

ADL5802 Data Sheet V = 5 V, T = 25°C, VSET = 5 V, IF = 153 MHz, as measured using a typical circuit schematic with low-side LO, unless otherwise noted. S A Insertion loss of input and output baluns (3600BL14M050, TC4-1W+) is included in the gain measurement. 15 –20 TA = +25°C TA = +85°C 14 –25 m) 13 B dBm) GE (d –30 TA = +25°C B (12 KA INPUT P1d1101 TA = –40°C O TO IF LEA ––4305 TA = –40°CTA = +85°C L –45 89 07882-047 –50 07882-050 2900 3100 3300 3500 3700 3900 4100 2900 3100 3300 3500 3700 3900 4100 RF FREQUENCY (MHz) LO FREQUENCY (MHz) Figure 47. Input P1dB vs. RF Frequency Figure 50. LO to IF Leakage vs. LO Frequency 20 –20 18 –22 16 TA =+85°C –24 B)14 dBm)–26 TA = –40°C E (d12 GE (–28 R A U K OISE FIG108 TA =–40°C TA =+25°C O RF LEA––3320 TA = +25°C TA = +85°C N 6 O T–34 L 4 –36 02 07882-048 ––4308 07882-051 2700 2900 3100 3300 3500 3700 3900 4100 4300 2900 3100 3300 3500 3700 3900 4100 RF FREQUENCY (MHz) LOFREQUENCY(MHz) Figure 48. SSB Noise Figure vs. RF Frequency (VSET = 2.0 V) Figure 51. LO to RF Leakage vs. LO Frequency 45 –10 40 –15 c) B 35 d N ( –20 E (dB)30 LATIO –25 UR25 SO NOISE FIG112050 IF 300MNHFz,, RBFL O38C0K5EMRH 3z,800MHz TO IF OUTPUT I –––433050 TTTAAA === –++482055°°°CCC F R 05 07882-049 ––5405 07882-052 –60 –50 –40 –30 –20 –10 0 10 2900 3100 3300 3500 3700 3900 4100 BLOCKER LEVEL (dBm) RF FREQUENCY (MHz) Figure 49. SSB Noise Figure vs. Blocker Level (VSET = 2.0 V) Figure 52. RF to IF Output Isolation vs. RF Frequency Rev. B | Page 16 of 32

Data Sheet ADL5802 V = 5 V, T = 25°C, VSET = 5 V, IF = 153 MHz, as measured using a typical circuit schematic with low-side LO, unless otherwise noted. S A Insertion loss of input and output baluns (3600BL14M050, TC4-1W+) is included in the gain measurement. 50 B)48 d N (46 O TI A44 OL EL IS42 TA = +25°C NN40 CHA38 O- L-T36 TA = –40°C TA = +85°C E NN34 A CH3302 07882-053 2900 3100 3300 3500 3700 3900 4100 RF FREQUENCY (MHz) Figure 53. Channel-to-Channel Isolation Rev. B | Page 17 of 32

ADL5802 Data Sheet DOWNCONVERTER MODE USING A JOHANSON 5.5 GHZ BALUN V = 5 V, T = 25°C, VSET = 4.8 V, IF = 380 MHz, as measured using a typical circuit schematic with low-side LO, unless otherwise noted. S A Insertion loss of input and output baluns (5400BL15B050, TC4-1W+) is included in the gain measurement. 25 30 2 20 24 0 TA =–40°C TA =+85°C m) IP3 dB) N (dB)–2 P3 (dB15 18 GURE ( GAI UT I NOISE FIGURE E FI –4 TA =+25°C INP10 12 NOIS –6 5 6 –8 07882-054 0 0 07882-057 4900 5100 5300 5500 5700 5900 6100 0 1 2 3 4 5 6 RF FREQUENCY (MHz) VSET (V) Figure 54. Power Conversion Gain vs. RF Frequency Figure 57. Input IP3, Noise Figure vs. VSET 5 0.30 60 4 0.27 55 3 0.24 50 GAIN (dB)–1021 IPOS 0000....21111852 LY CURRENT (A) PUT IP2 (dBm)33440505 TTTAAA ===++–284550°°°CCC P N –2 0.09 SUP I25 GAIN –3 0.06 20 ––54 00.03 07882-055 1105 07882-058 0 1 2 3 4 5 6 4900 5100 5300 5500 5700 5900 VSET (V) RF FREQUENCY (MHz) Figure 55. Power Conversion Gain and IPOS vs. VSET Figure 58. Input IP2 vs. RF Frequency 30 50 TA =–40°C 25 45 m)20 TA =+25°C m) 40 B TA =+85°C B d d IP3 (INPUT1105 INPUT IP2 ( 3305 5 25 0 07882-056 20 07882-059 4900 5100 5300 5500 5700 5900 6100 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 RFFREQUENCY(MHz) VSET (V) Figure 56. Input IP3 vs. RF Frequency Figure 59. Input IP2 vs. VSET Rev. B | Page 18 of 32

Data Sheet ADL5802 V = 5 V, T = 25°C, VSET = 5 V, IF = 153 MHz, as measured using a typical circuit schematic with low-side LO, unless otherwise noted. S A Insertion loss of input and output baluns (3600BL14M050, TC4-1W+) is included in the gain measurement. 16 –10 –15 15 14 TA =+85°C m)–20 B PUTP1dB (dBm)111123 TA =–40°C TA =+25°C O IF LEAKAGE (d––––43320505 TA =–40°CTA =+25°C N T I O –45 L 10 –50 TA =+85°C 89 07882-060 ––6505 07882-063 4900 5100 5300 5500 5700 5900 6100 4900 5100 5300 5500 5700 5900 6100 RF FREQUENCY (MHz) LO FREQUENCY (MHz) Figure 60. Input P1dB vs. RF Frequency Figure 63. LO to IF Leakage vs. LO Frequency 25 –15 –17 20 –19 m) B dB) E (d –21 GURE (15 EAKAG ––2253 TA =–40°CTA =+25°C SE FI10 RF L –27 NOI TTTAAA ===–++428055°°°CCC LO TO –29 TA =+85°C 5 –31 0 07882-061 ––3353 07882-064 4900 5100 5300 5500 5700 5900 6100 4900 5100 5300 5500 5700 5900 6100 RF FREQUENCY (MHz) LOFREQUENCY(MHz) Figure 61. SSB Noise Figure vs. RF Frequency (VSET = 2.0 V) Figure 64. LO to RF Leakage vs. LO Frequency 45 –30 40 c)–35 B 35 N (d–40 B)30 TIO TA =–40°C TA =+25°C E FIGURE (d2205 IF 380MNHFz,, RBFL O58C0K5EMRH 5z,800MHz TPUT ISOLA––5405 NOIS15 F OU–55 TA =+85°C O I–60 10 F T R 05 07882-062 ––7605 07882-065 –60 –50 –40 –30 –20 –10 0 4900 5100 5300 5500 5700 5900 6100 BLOCKER LEVEL (dBm) RF FREQUENCY (MHz) Figure 62. SSB Noise Figure vs. Blocker Level (VSET = 2.0 V) Figure 65. RF to IF Output Isolation vs. RF Frequency Rev. B | Page 19 of 32

ADL5802 Data Sheet V = 5 V, T = 25°C, VSET = 5 V, IF = 153 MHz, as measured using a typical circuit schematic with low-side LO, unless otherwise noted. S A Insertion loss of input and output baluns (3600BL14M050, TC4-1W+) is included in the gain measurement. 45 B) 43 d N ( 41 O TI LA 39 O L IS 37 E NN 35 A H C 33 O- L-T 31 NE TA =–40°C N 29 TA =+25°C CHA 2257 TA =+85°C 07882-066 4900 5100 5300 5500 5700 5900 6100 RF FREQUENCY (MHz) Figure 66. Channel-to-Channel Isolation Rev. B | Page 20 of 32

Data Sheet ADL5802 SPUR PERFORMANCE All spur tables are (N × f ) − (M × f ) and were measured using the standard evaluation board (see the Evaluation Board section). Mixer RF LO spurious products are measured in decibels relative to the carrier (dBc) from the IF output power level. Data was measured for frequencies less than 6 GHz only. The typical noise floor of the measurement system is −100 dBm. 900 MHz Performance V = 5 V, VSET = 4 V, T = 25°C, RF power = 0 dBm, LO power = 0 dBm, f = 900 MHz, f = 703 MHz, Z = 50 Ω. S A RF LO 0 M 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 0 −35.9 −25.5 −47.3 −27.4 −51.5 −37.5 −62.1 −47.5 1 −34.3 0.0 −46.3 −19.8 −64.3 −30.0 −75.6 −45.0 −67.8 −55.3 2 −49.1 −69.2 −68.2 −61.6 −68.7 −80.7 −67.5 −88.1 −79.1 −82.6 −91.5 ≤−100 3 −86.7 −79.6 ≤−100 −67.3 −98.0 −71.0 ≤−100 −86.3 ≤−100 ≤−100 ≤−100 −98.4 ≤−100 4 −91.8 ≤−100 −96.4 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 5 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 6 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 N 7 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 8 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 9 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 10 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 11 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 12 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 13 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 14 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 15 ≤−100 ≤−100 ≤−100 ≤−100 2090 MHz Performance V = 5 V, VSET = 4 V, T = 25°C, RF power = 0 dBm, LO power = 0 dBm, f = 2090 MHz, f = 1842 MHz, Z = 50 Ω. S A RF LO 0 M 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 0 −43.0 −23.7 −52.9 1 −26.8 0.0 −59.6 −42.2 −80.5 2 −59.8 −71.9 −53.8 −67.5 −68.2 −84.1 3 −67.6 −97.6 −59.3 −92.2 −79.3 ≤−100 4 ≤−100 ≤−100 −93.7 −97.8 ≤−100 ≤−100 5 ≤−100 ≤−100 −96.1 ≤−100 ≤−100 ≤−100 6 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 N 7 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 8 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 9 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 10 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 11 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 12 ≤−100 ≤−100 ≤−100 ≤−100 13 ≤−100 ≤−100 ≤−100 14 ≤−100 ≤−100 15 ≤−100 Rev. B | Page 21 of 32

ADL5802 Data Sheet 2600 MHz Performance V = 5 V, VSET = 4.5 V, T = 25°C, RF power = 0 dBm, LO power = 0 dBm, f = 2600 MHz, f = 2350 MHz, Z = 50 Ω. S A RF LO 0 M 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 0 −37.9 −31.5 1 −27.5 0.0 −62.6 −36.3 2 −75.5 −59.7 −52.2 −65.8 −68.8 3 −75.0 −88.7 −56.3 −86.8 −90.5 4 ≤−100 ≤−100 −82.5 −92.1 ≤−100 5 ≤−100 ≤−100 −94.4 ≤−100 ≤−100 ≤−100 6 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 N 7 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 8 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 9 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 10 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 11 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 12 ≤−100 ≤−100 ≤−100 ≤−100 13 ≤−100 ≤−100 ≤−100 14 ≤−100 ≤−100 15 3500 MHz Performance V = 5 V, VSET= 5 V, T = 25°C, RF power = 0 dBm, LO power = 0 dBm, f = 3500 MHz, f = 3800 MHz, Z = 50 Ω. S A RF LO 0 M 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 0 −43.0 −23.7 −52.9 1 −26.8 0.0 −59.6 −42.2 −80.5 2 −59.8 −71.9 −53.8 −67.5 −68.2 −84.1 3 −67.6 −97.6 −59.3 −92.2 −79.3 ≤−100 4 ≤−100 ≤−100 −93.7 −97.8 ≤−100 ≤−100 5 ≤−100 ≤−100 −96.1 ≤−100 ≤−100 ≤−100 6 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 N 7 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 8 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 9 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 10 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 11 ≤−100 ≤−100 ≤−100 ≤−100 ≤−100 12 ≤−100 ≤−100 ≤−100 ≤−100 13 ≤−100 ≤−100 ≤−100 14 ≤−100 ≤−100 15 ≤−100 Rev. B | Page 22 of 32

Data Sheet ADL5802 5800 MHz Performance V = 5 V, VSET= 4.8 V, T = 25°C, RF power = −10 dBm, LO power = 0 dBm, f = 5800 MHz, f = 5600 MHz, Z = 50 Ω. S A RF LO 0 M 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 0 −28.3 1 −63.6 0.0 −80.5 2 −48.6 −92.6 3 −64.2 −98.7 4 −90.5 −98.3 5 ≤−100 −99.4 6 −81.6 −98.0 N 7 −87.2 −95.9 8 −84.0 −99.5 9 ≤−100 ≤−100 10 ≤−100 ≤−100 11 ≤−100 ≤−100 12 ≤−100 −99.6 13 ≤−100 −99.8 14 ≤−100 15 Rev. B | Page 23 of 32

ADL5802 Data Sheet CIRCUIT DESCRIPTION The ADL5802 provides two double-balanced active mixers. RF VOLTAGE TO CURRENT (V-TO-I) CONVERTER These mixers are designed for a 50 Ω input impedance and a The differential RF input signal is applied to a voltage-to-current 200 Ω output impedance. Both are driven from a common local converter that converts the differential input voltage to output oscillator (LO) amplifier. The RF inputs and LO outputs are currents. The V-to-I converter provides a 50 Ω input differential, providing maximum usable bandwidth at the input impedance. The V-to-I section bias current can be adjusted up and output ports. The LO also operates with a 50 Ω input or down using the VSET pin. Adjusting the current up improves impedance and can, optionally, be operated differentially or IP3 and P1dB input but degrades SSB NF. Adjusting the current single-ended. The input, output, and LO ports can be operated down improves SSB NF but degrades IP3 and P1dB input. The over an exceptionally wide frequency range. The ADL5802 can conversion gain remains nearly constant over a wide range of be configured as a downconvert mixer or as an upconvert mixer. VSET pin settings, allowing the part to be adjusted dynamically The ADL5802 can be divided into the following sections: the without affecting the conversion gain. The current adjustment local oscillator (LO) amplifier and splitter, the RF voltage-to- can be made by connecting a resistor from the VSET pin to the current (V-to-I) converter, the mixer cores, the output loads, positive supply to increase the bias current or from the VSET and the bias circuit. A simplified block diagram of the device is pin to ground to decrease the bias current. The VSET pin shown in Figure 67. The LO block generates a pair of differential impedance is approximately 675 Ω in series with two diodes LO signals to drive two mixer cores. The RF input is converted and an internal current source. into current by the V-to-I converters that then feed into the two MIXER CORES mixer cores. The internal differential load of the mixers is The ADL5802 has two double-balanced mixers that use high designed for a wideband 200 Ω output impedance from the performance SiGe NPN transistors. These mixers are based on mixer. Reference currents to each section are generated by the the Gilbert cell design of four cross-connected transistors. bias circuit, which can be enabled or disabled using the ENBL pin. A detailed description of each section of the ADL5802 MIXER LOAD follows. Each mixer load is designed to use a pair of 100 Ω resistors con- VPOSRF1+RF1–GNDRF2+RF2– nected to the positive supply. This provides a 200 Ω differential 24 23 22 21 20 19 output resistance. The mixer output should be pulled to the positive supply externally using a pair of RF chokes or using an GND 1 18 GND output transformer with the center tap connected to the positive GND 2 17 GND supply. It is possible to exclude these components when the mixer core current is low, but both P1dB and IP3 are then reduced. OP1+ 3 16 OP2+ The mixer load output can operate from direct current (dc) up to OP1– 4 15 OP2– approximately 500 MHz into a 200 Ω load. For upconversion GND 5 14 GND applications, the mixer load can be matched using off-chip IP3 VPOS 6 ADL5802 BIAS 13 VPOS matching components. Transmit operation up to 2 GHz is possible. See the Applications Information section for matching EN7BLGN8D LO9IPLO10ING1N1DVS12ET 07882-128 cBirIAcuSit CdeIRtaCilsU. IT Figure 67. ADL5802 Block Diagram A band gap reference circuit generates the reference currents LO AMPLIFIER AND SPLITTER used by the mixers. The bias circuit can be enabled and disabled The LO input is amplified using a broadband LNA and is then using the ENBL pin. If the ENBL pin is grounded or left open, split and followed by separate LO limiting amplifiers. The LNA the part is enabled. Pulling the ENBL pin high shuts off the bias input impedance is nominally 50 Ω. The LO is designed to circuit and disables the part. However, the ENBL pin does not accommodate a wide range of LO input power levels. The LO alter the current in the LO section and, therefore, does not input is conditioned by the series of amplifiers to provide a well provide a true power-down feature. Certain configurations may controlled and limited LO swing to the mixer core, resulting in require the VSET pin to be connected to the positive supply excellent IP3. The LO circuit exhibits low additive noise, through a resistor. This will result in an increased mixer core resulting in an excellent mixer noise figure and output noise current. Unless this resistor to positive supply is removed, bias under RF blocking. For optimal performance, the LO inputs current will continue to be supplied to the mixer core. should be driven differentially but at lower frequencies; single- ended drive is acceptable. Rev. B | Page 24 of 32

Data Sheet ADL5802 APPLICATIONS INFORMATION BASIC CONNECTIONS RF AND LO PORTS The ADL5802 features dual channel mixers with a common The RF and LO input ports are designed for differential input local oscillator (LO). The mixer is designed to translate between impedance of approximately 50 Ω. Figure 69 and Figure 70 radio frequencies (RF) and intermediate frequencies (IF). For illustrate the RF and LO interfaces, respectively. It is recommended both upconversion and downconversion applications, RF1+ that each of the RF and LO differential ports be driven through a (Pin 23), RF1− (Pin 22), RF2+ (Pin 20), and RF2− (Pin 19) balun for optimum performance. It is also necessary to ac- must be configured as the input interfaces. OP1+ (Pin 3), OP1− couple both RF and LO ports with the proper size capacitors. (Pin 4), OP2+ (Pin 16), and OP2− (Pin 15) must be configured Table 4 lists the recommended components for various RF as the output interfaces. Figure 68 illustrates the basic connections frequency bands. The characterization data is available in the for ADL5802 operation. Typical Performance Characteristics section. RF1 RF2 T5 T3 C13 C14 C5 C12 VPOS C11 C8 24 23 22 21 20 19 VPOS RF1+ RF1– GND RF2+ RF2– 1 GND GND 18 VPOS 2 GND GND 17 VPOS IF1P C16 3 OP1+ OP2+ 16 C15 T4 ADL5802 T2 4 OP1– OP2– 15 IF2P 5 GND GND 14 VPOS 6 VPOS VPOS 13 VPOS C9 C6 ENBL GND LOIP LOIN GND VSET C7 C10 7 8 9 10 11 12 VSET C2 C3 T1 LO 07882-101 Figure 68. Basic Connections Schematic Rev. B | Page 25 of 32

ADL5802 Data Sheet frequency. A variety of suitable choke inductors is commercially RF1 RF2 available from manufacturers such as Coilcraft and Murata. An T5 T3 impedance transforming network may be required to transform C13 C14 C5 C12 the final load impedance to 200 Ω at the IF outputs. 23 22 21 20 19 RF1+ RF1– GND RF2+ RF2– ADL5802 07882-102 VPOS 1 GND Figure 69. ADL5802 RF Interface 2 GND IF1P C16 3 OP1+ ADL5802 T4 ADL5802 4 OP1– ENBL GND LOIP LOIN GND 7 8 9 10 11 5 GND C2 C3 T1 GND 18 LO 07882-103 GND 17 VPOS Figure 70. ADL5802 LO Interface OP2+ 16 C15 ADL5802 T2 Table 4. Suggested Components for the RF and LO Interfaces OP2– 15 IF2P RF and LO C2, C3, C5, Frequency T1, T3, T5 C12, C13, C14 GND 14 910900 0M MHHz z MMiinnii--CCiirrccuuiittss ®T TCC11-1-1-1-133MM++ 110000 ppFF 07882-104 Figure 71. Biasing the IF Port Open-Collector Outputs 2500 MHz Johanson Technology 3 pF Using a Center-Tapped Impedance Transformer 2500BL14M050 3500 MHz Johanson Technology 1.5 pF 3600BL14M050 VPOS 5500 MHz Johanson Technology 3 pF C17 1 GND 5400BL15B050 2 GND L3 IF PORT IF1 OUT+ IMPEDANCE 3 OP1+ The IF port features an open-collector differential output ZL TRANSFORMING ZLOAD= 200Ω ADL5802 interface. It is necessary to bias the open collector outputs using NETWORK 4 OP1– IF1 OUT– one of the schemes presented in Figure 71 and Figure 72. L4 5 GND Figure 71 shows the use of center-tapped impedance transformers. C18 The turns ratio of the transformer should be selected to provide VPOS the desired impedance transformation. In the case of a 50 Ω load impedance, a 4:1 impedance ratio transformer should be VPOS used to transform the 50 Ω load into a 200 Ω differential load at GND 18 C4 the IF output pins. GND 17 L2 Figure 72 shows a differential IF interface where pull-up choke IF2 OUT+ inductors are used to bias the open-collector outputs. The OP2+ 16 IMPEDANCE shunting impedance of the choke inductors used to couple dc ADL5802 ZLOAD= 200Ω TRANNESTFWOORRMKING ZL OP2– 15 current into the mixer core should be large enough at the IF IF2 OUT– L1 frequency of operation so as not to load down the output GND 14 C1 ccuurrrreenntt bheafnodrlei nitg r ceaapchabeisl itthye o ifn tthene dseelde cloteadd .c Ahodkdei tiinodnualcltyo, rtsh e dc VPOS 07882-105 must be at least 45 mA. The self-resonant frequency of the Figure 72. Biasing the IF Port Open-Collector Outputs selected choke inductors must be higher than the intended IF Using Pull-Up Choke Inductors Rev. B | Page 26 of 32

Data Sheet ADL5802 EVALUATION BOARD An evaluation board is available for the ADL5802. The standard evaluation board is fabricated using Rogers® RO3003 material. Each of the RF, LO, and IF ports is configured for single-ended signaling via a balun transformer. The schematic for the evaluation board is shown in Figure 73. Table 5 describes the various configuration options for the evaluation board. Layout for the board is shown in Figure 74 and Figure 75. RF1 RF2 T5 T3 VPOS GND C11 C8 C13 C14 C5 C12 VPOS R19 VPOS1 24 23 22 21 20 19 VPOS RF1+ RF1– GNDRF2+ RF2– VPOS VPOS C17 1 GND GND 18 C4 2 GND GND 17 L2 L3 R2 IF1P R16 R14 IF2N C16 3 OP1+ OP2+ 16 C15 T4 R7 ADL5802 R6 T2 IF1N R15 4 OP1– OP2– 15 R13 IF2P R3 L4 L1 R21 5 GND GND 14 C1 R20 C18 R10 R12 VPOS 6 VPOS VPOS 13 VPOS C9 C6 ENBLGND LOIP LOIN GNDVSET C7 C10 7 8 9 10 11 12 R9 R4 R5 VPOS VSET R11 C2 C3 R23 R22 ENBL1 R1LON TL1O LOVPPOS 07882-001 07882-100 Figure 73. Evaluation Board Schematic Table 5. Evaluation Board Configuration Components Function Default Conditions C1, C4, C6, C7, C8, C9, Power supply decoupling. Nominal supply decoupling C6, C7, C8 = 10 pF (size 0402) C10, C11, C17, C18, consists of a 0.01 µF capacitor to ground in parallel with 10 C9, C10, C11 = 0.01 µF (size 0402) R10, R12, R19, R20, pF capacitors to ground, positioned as close to the device C1, C4, C17, C18 = open (size 0402) R21 as possible. Series resistors are provided for enhanced R10, R12, R19, R20, R21 = 0 Ω (size 0402) supply decoupling using optional ferrite chip inductors. C5, C12, C13, C14, T3, RF Channel 1 and RF Channel 2 input interfaces. Input C5, C12, C13, C14 = 100 pF (size 0402) T5, RF1, RF2 channels are ac-coupled through C5, C12, C13, and C14. T3 T3, T5 = TC1-1-13M+ (Mini-Circuits) and T4 are 1:1 baluns used to interface to the 50 Ω differential inputs. C15, C16, L1, L2, L3, IF Channel 1 and IF Channel 2 output interfaces. The 200 Ω C15, C16 = 100 pF (size 0402) L4, R2, R3, R6, R7, open-collector IF output interfaces are biased through the L1, L2, L3, L4 = open (size 0805) R13, R14, R15, R16, center taps of T2 and T4 4:1 impedance transformers. C15 R2, R3, R13, R14, R15, R16, R20, R21 = 0 Ω (size 0402) R20, R21, T2, T4, IF1, and C16 provide local bypassing with R20 and R21 available R6, R7 = open (size 0402) IF2 for additional supply bypassing. R6, R7, R13, R14, R15, and T2, T4 = TC4-1W+ (Mini-Circuits) R16 are provided for IF filtering and matching options. C2, C3, R4, R5, T1, LO LO interface. C2 and C3 provide ac coupling for the local C2, C3 = 1 nF (size 0402) oscillator input. T1 is a 1:1 balun to allow single-ended R4, R5 = open (size 0402) interfacing to the differential 50 Ω local oscillator input. T1 = TC1-1-13M+ (Mini-Circuits) R1, R9, R11, ENBL1 Enable interface. The ADL5802 can be disabled using the 3- R9 = 10 kΩ (size 0402); R1, R11 = open (size 0402) pin ENBL1 header. The ENBL pin is pulled up to VPOS Or R1 = 10 kΩ (size 0402);R9, R11 = open (size 0402) through R9. R1 is provided as an optional termination for Or R11 = 10 kΩ (size 0402); R1, R9 = open (size 0402) the high impedance enable interface. If desired, the ENBL ENBL1 = 3-pin header and shunt pin can be driven by an external source through the ENBL SMA connector. Rev. B | Page 27 of 32

ADL5802 Data Sheet Components Function Default Conditions R22, R23, VSET VSET bias control. R22 and R23 form an optional resistor R22, R23 = open (size 0402) divider network between VPOS and GND, allowing for a fixed bias setting. See the Typical Performance Characteristics section to choose the recommended VSET control voltage for the desired frequency band. EPAD (EP) Exposed paddle. Must be soldered to ground. 07882-106 07882-107 Figure 74. Evaluation Board Top Layer Figure 75. Evaluation Board Bottom Layer Rev. B | Page 28 of 32

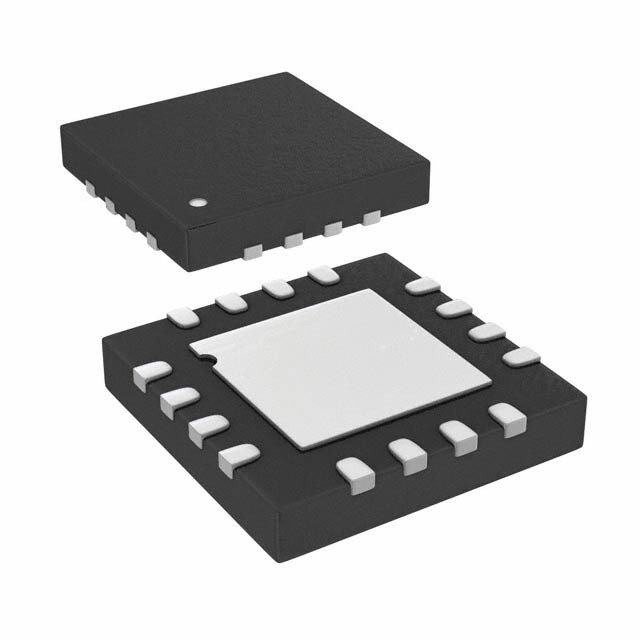

Data Sheet ADL5802 OUTLINE DIMENSIONS 4.10 0.30 4.00 SQ 0.25 PIN 1 3.90 0.18 INDICATOR PIN 1 0.50 19 24 INDICATOR BSC 18 1 EXPOSED 2.65 PAD 2.50 SQ 2.45 13 6 0.50 12 7 0.25 MIN TOP VIEW BOTTOM VIEW 0.40 0.30 0.80 FOR PROPER CONNECTION OF 0.75 0.05 MAX THE EXPOSED PAD, REFER TO 0.70 0.02 NOM THE PIN CONFIGURATION AND FUNCTION DESCRIPTIONS COPLANARITY SECTION OF THIS DATA SHEET. 0.08 SEATING PLANE COMPLIANTTOJED0E.2C0 SRTEAFNDARDS MO-220-WGGD. 03-11-2013-A Figure 76. 24-Lead Lead Frame Chip Scale Package [LFCSP_WQ] 4 mm × 4 mm Body, Very Very Thin Quad (CP-24-7) Dimensions shown in millimeters ORDERING GUIDE Temperature Package Ordering Model1 Range Package Description Option Quantity ADL5802ACPZ-R7 −40°C to +85°C 24-Lead Lead Frame Chip Scale Package [LFCSP_WQ] CP-24-7 1,500 per Reel ADL5802-EVALZ Evaluation Board 1 1 Z = RoHS Compliant Part. Rev. B | Page 29 of 32

ADL5802 Data Sheet NOTES Rev. B | Page 30 of 32

Data Sheet ADL5802 NOTES Rev. B | Page 31 of 32

ADL5802 Data Sheet NOTES ©2009–2015 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D07882-0-2/15(B) Rev. B | Page 32 of 32

Datasheet下载

Datasheet下载