ICGOO在线商城 > 集成电路(IC) > 数据采集 - 模数转换器 > AD9271BSVZ-50

- 型号: AD9271BSVZ-50

- 制造商: Analog

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

AD9271BSVZ-50产品简介:

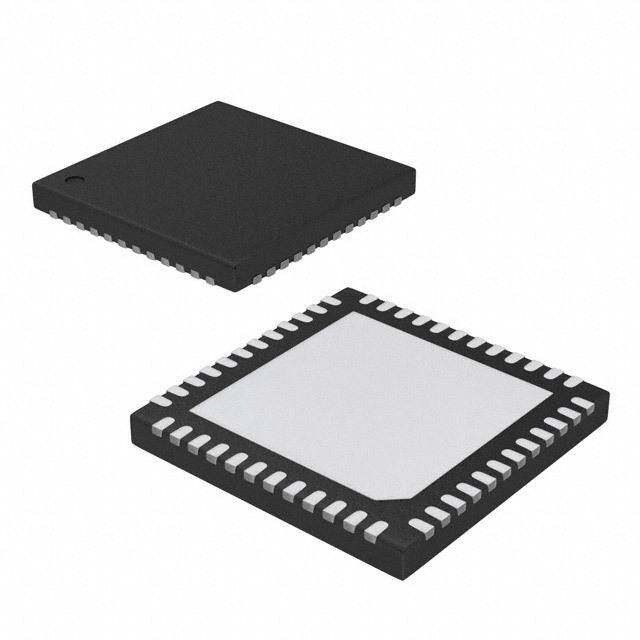

ICGOO电子元器件商城为您提供AD9271BSVZ-50由Analog设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 AD9271BSVZ-50价格参考¥721.30-¥721.30。AnalogAD9271BSVZ-50封装/规格:数据采集 - 模数转换器, 12 Bit Analog to Digital Converter 8,16 Input 8 管线 100-TQFP-EP(14x14)。您可以下载AD9271BSVZ-50参考资料、Datasheet数据手册功能说明书,资料中有AD9271BSVZ-50 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC)半导体 |

| 描述 | IC ADC 12BIT 50MSPS VGA 100-TQFP模数转换器 - ADC 12-Bit 50 MSPS Octal |

| 产品分类 | |

| 品牌 | Analog Devices |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 数据转换器IC,模数转换器 - ADC,Analog Devices AD9271BSVZ-50- |

| 数据手册 | |

| 产品型号 | AD9271BSVZ-50 |

| 产品目录页面 | |

| 产品种类 | 模数转换器 - ADC |

| 位数 | 12 |

| 供应商器件封装 | 100-TQFP-EP(14x14) |

| 信噪比 | 65.8 dB |

| 其它名称 | AD9271BSVZ50 |

| 分辨率 | 12 bit |

| 包装 | 托盘 |

| 商标 | Analog Devices |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装 | Tray |

| 封装/外壳 | 100-TQFP 裸露焊盘 |

| 封装/箱体 | TQFP-100 |

| 工作温度 | -40°C ~ 85°C |

| 工作电源电压 | 1.8 V, 3.3 V |

| 工厂包装数量 | 90 |

| 接口类型 | Serial, LVDS |

| 数据接口 | SPI |

| 最大功率耗散 | 1.19 W |

| 最大工作温度 | + 85 C |

| 最小工作温度 | - 40 C |

| 标准包装 | 1 |

| 特性 | 同步采样 |

| 电压参考 | Internal, External |

| 电压源 | 单电源 |

| 系列 | AD9271 |

| 结构 | Pipeline |

| 转换器数 | 8 |

| 转换器数量 | 8 |

| 转换速率 | 50 MS/s |

| 输入数和类型 | 8 个单端,单极8 个差分,单极 |

| 输入类型 | Single-Ended |

| 通道数量 | 8 Channel |

| 采样率(每秒) | 50M |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

Octal LNA/VGA/AAF/ADC and Crosspoint Switch AD9271 FEATURES FUNCTIONAL BLOCK DIAGRAM 8Lo cwha nnoniseels p orfe LaNmAp,l VifGieAr ,( LANAAF,) and ADC VDD DWNTBY RVDD A PS D Input-referred noise = 1.1 nV/√Hz @ 5 MHz typical, gain = 18 dB LOSW-A AD9271 LO-A SPI-programmable gain = 14 dB/15.6 dB/18 dB Single-ended input; VIN maximum = 400 mV p-p/ LLGI--AA LNA VGA AAF 1A2-DBCIT SLEVRDIASL DDOOUUTTAA+– 333 mV p-p/250 mV p-p LOSW-B Dual-mode active input impedance matching LO-B Bandwidth (BW) > 70 MHz LLGI--BB LNA VGA 1A2-DBCIT SLEVRDIASL DDOOUUTTBB+– Full-scale (FS) output = 2 V p-p differential LOSW-C AAF Variable gain amplifier (VGA) LO-C GLianiena rra-inng-de B= g−a6i nd Bco tnot +ro2l4 dB LLGI--CC LNA VGA AAF 1A2-DBCIT SLEVRDIASL DDOOUUTTCC+– LOSW-D Antialiasing filter (AAF) LO-D P3rrdo-ogrrdamerm Baubttleer fwroomrt h8 cMuHtozf tf o 18 MHz LLGI--DD LNA VGA 1A2-DBCIT SLEVRDIASL DDOOUUTTDD+– AAF Analog-to-digital converter (ADC) LOSW-E LO-E 12 bits at 10 MSPS to 50 MSPS SNR = 70 dB LLGI--EE LNA VGA 1A2-DBCIT SLEVRDIASL DDOOUUTTEE+– AAF SFDR = 80 dB LOSW-F Serial LVDS (ANSI-644, IEEE 1596.3 reduced range link) LO-F Data and frame clock outputs LLGI--FF LNA VGA 1A2-DBCIT SLEVRDIASL DDOOUUTTFF+– Includes crosspoint switch to support LOSW-G AAF continuous wave (CW) Doppler LO-G Low power, 150 mW per channel at 12 bits/40 MSPS (TGC) LLGI--GG LNA VGA 1A2-DBCIT SLEVRDIASL DDOOUUTTGG+– 90 mW per channel in CW Doppler AAF LOSW-H Single 1.8 V supply (3.3 V supply for CW Doppler output bias) LO-H FOlveexriblolea dp orewceorv-edroyw inn <m1o0d ness LLGI--HH LNA VGA 1A2-DBCIT SLEVRDIASL DDOOUUTTHH+– AAF F1AMa0Pes0dtP- ilrLceeaaIcCldo i vAmTeQTarIFgyOP ifn rN ogSm/u lltorwas poouwnde r standby mode, <2 μs SAWRRITACYH REFERENCE SERIALPORTINTERFACE DATARATEMULTIPLIER FFDDCCCCOOOO+–+– Automotive radar GThEeN AEDR9A27L1 D isE dSeCsigRnIePdT fIoOr Nlo w cost, low power, small size, CWVDD CWD[5:0]+/– GAIN+ GAIN– SENSEVREFREFBREFTRBIAS CSBSCLK SDIO CLK+CLK– 06304-001 and ease of use. It contains eight channels of a variable gain amp- Figure 1. lifier (VGA) with low noise preamplifier (LNA); an antialiasing The LNA has a single-ended-to-differential gain that is selectable filter (AAF); and a 12-bit, 10 MSPS to 50 MSPS analog-to-digital through the SPI. The LNA input noise is typically 1.2 nV/√Hz, converter (ADC). and the combined input-referred noise of the entire channel Each channel features a variable gain range of 30 dB, a fully is 1.4 nV/√Hz at maximum gain. Assuming a 15 MHz noise differential signal path, an active input preamplifier termination, a bandwidth (NBW) and a 15.6 dB LNA gain, the input SNR is maximum gain of up to 40 dB, and an ADC with a conversion roughly 86 dB. In CW Doppler mode, the LNA output drives a rate of up to 50 MSPS. The channel is optimized for dynamic transconductance amp that is switched through an 8 × 6 performance and low power in applications where a small differential crosspoint switch. The switch is programmable package size is critical. through the SPI. Rev. B Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Tel: 781.329.4700 www.analog.com Trademarks and registered trademarks are the property of their respective owners. Fax: 781.461.3113 ©2007–2009 Analog Devices, Inc. All rights reserved.

AD9271 TABLE OF CONTENTS Features .............................................................................................. 1 TGC Operation ........................................................................... 25 Applications ....................................................................................... 1 ADC ............................................................................................. 27 General Description ......................................................................... 1 Clock Input Considerations ...................................................... 28 Functional Block Diagram .............................................................. 1 Serial Port Interface (SPI) .............................................................. 35 Revision History ............................................................................... 2 Hardware Interface ..................................................................... 35 Product Highlights ........................................................................... 3 Memory Map .................................................................................. 37 Specifications ..................................................................................... 4 Reading the Memory Map Table .............................................. 37 AC Specifications .......................................................................... 4 Reserved Locations .................................................................... 37 Digital Specifications ................................................................... 7 Default Values ............................................................................. 37 Switching Specifications .............................................................. 8 Logic Levels ................................................................................. 37 ADC Timing Diagrams ............................................................... 9 Applications Information .............................................................. 41 Absolute Maximum Ratings .......................................................... 10 Design Guidelines ...................................................................... 41 Thermal Impedance ................................................................... 10 Evaluation Board ............................................................................ 42 ESD Caution ................................................................................ 10 Power Supplies ............................................................................ 42 Pin Configuration and Function Descriptions ........................... 11 Input Signals................................................................................ 42 Equivalent Circuits ......................................................................... 14 Output Signals ............................................................................ 42 Typical Performance Characteristics ........................................... 16 Default Operation and Jumper Selection Settings ................. 43 Theory of Operation ...................................................................... 20 Quick Start Procedure ............................................................... 44 Ultrasound ................................................................................... 20 Schematics and Artwork ........................................................... 45 Channel Overview ...................................................................... 21 Outline Dimensions ....................................................................... 58 Input Overdrive .......................................................................... 23 Ordering Guide .......................................................................... 58 CW Doppler Operation ............................................................. 24 REVISION HISTORY 5/09—Rev. A to Rev. B Changes to LNA Noise Section .................................................... 22 Changes to Figure 43 ...................................................................... 22 Changes to Figure 27 ...................................................................... 17 Change to Input Overload Protection Section ........................... 23 Changes to Figure 40 and Figure 41 ............................................. 21 Changes to TGC Operation Section ............................................ 25 Changes to Ordering Guide .......................................................... 58 Changes to Gain Control Section ................................................. 26 12/07—Rev. 0 to Rev. A Changes to Figure 52 ...................................................................... 26 Change to AC Specifications Text .................................................. 4 Change to Table 11 ......................................................................... 33 Added Input Noise Current ............................................................ 4 Changes to Serial Interface Port (SPI) Section ........................... 35 Added Noise Figure .......................................................................... 4 Changes to Hardware Interface Section ...................................... 35 Changes to Signal-to-Noise Ratio Units ........................................ 4 Changes to Reading the Memory Map Table Section ............... 37 Changes to Harmonic Distortion Units ........................................ 5 Added Applications Information and Added Endnote 3 .............................................................................. 6 Design Guidelines Sections ...................................................... 41 Changes to Table 6 .......................................................................... 11 Change to Input Signals Section ................................................... 42 Inserted Figure 19 and Figure 21 .................................................. 16 Changes to Figure 73 ...................................................................... 42 Changes to Figure 20 ...................................................................... 16 Changes to Table 16 ....................................................................... 55 Changes to Theory of Operation Section .................................... 20 6/07—Revision 0: Initial Version Changes to Figure 40 and Figure 41 ............................................. 21 Change to Active Impedance Matching Section ........................ 22 Rev. B | Page 2 of 60

AD9271 The AD9271 requires a LVPECL-/CMOS-/LVDS-compatible Fabricated in an advanced CMOS process, the AD9271 is sample rate clock for full performance operation. No external available in a 16 mm × 16 mm, RoHS compliant, 100-lead reference or driver components are required for many TQFP. It is specified over the industrial temperature range of applications. −40°C to +85°C. The ADC automatically multiplies the sample rate clock for PRODUCT HIGHLIGHTS the appropriate LVDS serial data rate. A data clock (DCO±) for 1. Small Footprint. Eight channels are contained in a small, capturing data on the output and a frame clock (FCO±) trigger space-saving package. Full TGC path, ADC, and crosspoint for signaling a new output byte are provided. switch contained within a 100-lead, 16 mm × 16 mm TQFP. Powering down individual channels is supported to increase 2. Low Power of 150 mW per Channel at 40 MSPS. battery life for portable applications. There is also a standby 3. Integrated Crosspoint Switch. This switch allows numerous mode option that allows quick power-up for power cycling. In CW multichannel configuration options to enable the CW Doppler operation, the VGA, AAF, and ADC are powered down. Doppler mode. The power of the TGC path scales with selectable speed grades. 4. Ease of Use. A data clock output (DCO±) operates up to 300 MHz and supports double data rate (DDR) operation. The ADC contains several features designed to maximize flexibility 5. User Flexibility. Serial port interface (SPI) control offers a wide and minimize system cost, such as a programmable clock, data range of flexible features to meet specific system requirements. alignment, and programmable digital test pattern generation. The 6. Integrated Third-Order Antialiasing Filter. This filter is placed digital test patterns include built-in fixed patterns, built-in between the TGC path and the ADC and is programmable pseudorandom patterns, and custom user-defined test patterns from 8 MHz to 18 MHz. entered via the serial port interface. Rev. B | Page 3 of 60

AD9271 SPECIFICATIONS AC SPECIFICATIONS AVDD = 1.8 V, DRVDD = 1.8 V, CWVDD = 3.3 V, 1.0 V internal ADC reference, f = 5 MHz, R = 50 Ω, LNA gain = 15.6 dB (6), AAF IN S LPF cutoff = 1/3 × f, HPF cutoff = 700 kHz, full temperature, unless otherwise noted. S Table 1. AD9271-25 AD9271-40 AD9271-50 Parameter1 Conditions Min Typ Max Min Typ Max Min Typ Max Unit LNA CHARACTERISTICS Gain = 5/6/8 Single-ended input 14/15.6/18 14/15.6/18 14/15.6/18 dB to differential output Single-ended input 8/9.6/12 8/9.6/12 8/9.6/12 dB to single-ended output Input Voltage Range, LNA output limited 400/333/250 400/333/250 400/333/250 mV p-p Gain = 5/6/8 to 2 V p-p differential SE2 output Input Common 1.4 1.4 1.4 V Mode Input Resistance RFB = 200 Ω 50 50 50 Ω RFB = 400 Ω 100 100 100 Ω RFB = ∞ 15 15 15 kΩ Input Capacitance LI-x 15 15 15 pF −3 dB Bandwidth 40 60 70 MHz Input Noise Current, 1.1 1.1 1.1 pA/√Hz Gain = 5/6/8 Input Noise Voltage, RS = 0 Ω, RFB = ∞ 1.4/1.4/1.3 1.3/1.2/1.1 1.3/1.2/1.1 nV/√Hz Gain = 5/6/8 1 dB Input VGAIN = 0 V 770/650/495 770/650/495 770/650/495 mV p-p Compression Point, Gain = 5/6/8 Noise Figure Active Termination RS = 50 Ω, RFB = 200 Ω 6.7 6.7 6.7 dB Match Unterminated RFB = ∞ 4.9 4.4 4.2 dB FULL-CHANNEL (TGC) CHARACTERISTICS AAF High-Pass Cutoff −3 dB DC/350/700 DC/350/700 DC/350/700 kHz AAF Low-Pass Cutoff −3 dB, programmable 1/3 × fSAMPLE 1/3 × fSAMPLE 1/3 × fSAMPLE MHz (8 to 18) (8 to 18) (8 to 18) Bandwidth Tolerance ±15 ±15 ±15 % Group Delay Variation f = 1 to 18 MHz, ±2 ±2 ±2 ns gain = 0 V to 1 V Input-Referred Noise LNA gain = 5/6/8, 1.7/1.6/1.5 1.6/1.4/1.3 1.6/1.4/1.2 nV/√Hz Voltage RFB = ∞ Correlated Noise Ratio No signal, correlated/ −30 −30 −30 dB uncorrelated Output Offset AAF high pass = −50 +50 −35 +35 −35 +35 LSB 700 kHz Signal-to-Noise Ratio (SNR) fIN = 5 MHz VGAIN = 0 V 65.8 64.4 63.7 dBFS at −7 dBFS fIN = 5 MHz VGAIN = 1 V 62 59.7 59 dBFS at −1 dBFS Rev. B | Page 4 of 60

AD9271 AD9271-25 AD9271-40 AD9271-50 Parameter1 Conditions Min Typ Max Min Typ Max Min Typ Max Unit Harmonic Distortion Second Harmonic VGAIN = 0 V −73 −71 −71 dBFS fIN = 5 MHz at −7 dBFS Second Harmonic VGAIN = 1 V −80 −72 −68 dBFS fIN = 5 MHz at −1 dBFS Third Harmonic VGAIN = 0 V −81 −77 −74 dBFS fIN = 5 MHz at −7 dBFS Third Harmonic VGAIN = 1 V −65 −63 −66 dBFS fIN = 5 MHz at −1 dBFS Two-Tone IMD3 VGAIN = 1 V −54.6 −63.4 −68.5 dBc (2 × F1 − F2) Distortion fIN1 = 5.0 MHz at −7 dBFS, fIN2 = 6.0 MHz at −7 dBFS Channel-to-Channel −70 −70 −70 dB Crosstalk Channel-to-Channel −70 −70 −70 dB Crosstalk (Over- range Condition)3 Overload Recovery Full TGC path, 5 5 5 Degrees fIN = 1 MHz to 10 MHz, gain = 0 V to 1 V GAIN ACCURACY 25°C Gain Law Confor- 0 < VGAIN < 0.1 V +0.8 +0.8 +0.8 dB mance Error 0.1 V < VGAIN < 0.9 V −1.2 +1.2 −1.2 +1.2 −1.2 +1.2 dB 0.9 V < VGAIN < 1 V −1.2 −1.2 −1.2 dB Linear Gain Error VGAIN = 0.5 V, −1.3 +1.3 −1.3 +1.3 −1.3 +1.3 dB normalized for ideal AAF loss Channel-to-Channel 0.1 V < VGAIN < 0.9 V 0.2 0.2 0.2 dB Matching GAIN CONTROL INTERFACE Normal Operating 0 1 0 1 0 1 V Range Gain Range 0 V to 1 V, normalized 10 to 40 10 to 40 10 to 40 dB for ideal AAF loss Scale Factor 31.6 31.6 31.6 dB/V Response Time 30 dB change 350 350 350 ns CW DOPPLER MODE Transconductance LNA gain = 5/6/8 10/12/16 10/12/16 10/12/16 mA/V Common Mode CW Doppler 1.5 3.6 1.5 3.6 1.5 3.6 V output pins Input-Referred Noise LNA gain = 5/6/8, 1.8 /1.7/1.5 1.7 /1.5/1.4 1.7 /1.5/1.3 nV/√Hz Voltage RS = 0 Ω, RFB = ∞ Output DC Bias Per channel 2.4 2.4 2.4 mA Maximum Output Per channel ±2 ±2 ±2 mA p-p Swing Rev. B | Page 5 of 60

AD9271 AD9271-25 AD9271-40 AD9271-50 Parameter1 Conditions Min Typ Max Min Typ Max Min Typ Max Unit POWER SUPPLY AVDD 1.7 1.8 1.9 1.7 1.8 1.9 1.7 1.8 1.9 V DRVDD 1.7 1.8 1.9 1.7 1.8 1.9 1.7 1.8 1.9 V CWVDD 3.0 3.3 3.6 3.0 3.3 3.6 3.0 3.3 3.6 IAVDD Full-channel mode 505 613 742 mA CW Doppler mode 136 160 170 mA with four channels enabled IDRVDD 46.7 48.7 50 mA Total Power Full-channel mode, 993 1063 1190 1280 1425 1494 mW Dissipation no signal (Including Output Drivers) CW Doppler mode 192 216 224 mW with four channels enabled Power-Down 4.5 4.5 4.5 mW Dissipation Standby Power 101.7 112.5 120.6 mW Dissipation Power Supply 1 1 1 mV/V Rejection Ratio (PSRR) ADC RESOLUTION 12 12 12 Bits ADC REFERENCE Output Voltage Error ±20 ±20 ±20 mV (VREF = 1 V) Load Regulation @ 3 3 3 mV 1.0 mA (VREF = 1 V) Input Resistance 6 6 6 kΩ 1 See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions and how these tests were completed. 2 SE = single ended. 3 The overrange condition is specified as being 6 dB more than the full-scale input range. Rev. B | Page 6 of 60

AD9271 DIGITAL SPECIFICATIONS AVDD = 1.8 V, DRVDD = 1.8 V, CWVDD = 3.3 V, 400 mV p-p differential input, 1.0 V internal ADC reference, AIN = −0.5 dBFS, unless otherwise noted. Table 2. Parameter1 Temperature Min Typ Max Unit CLOCK INPUTS (CLK+, CLK−) Logic Compliance CMOS/LVDS/LVPECL Differential Input Voltage2 Full 250 mV p-p Input Common-Mode Voltage Full 1.2 V Input Resistance (Differential) 25°C 20 kΩ Input Capacitance 25°C 1.5 pF LOGIC INPUTS (PDWN, STBY, SCLK) Logic 1 Voltage Full 1.2 3.6 V Logic 0 Voltage Full 0.3 V Input Resistance 25°C 30 kΩ Input Capacitance 25°C 0.5 pF LOGIC INPUT (CSB) Logic 1 Voltage Full 1.2 3.6 V Logic 0 Voltage Full 0.3 V Input Resistance 25°C 70 kΩ Input Capacitance 25°C 0.5 pF LOGIC INPUT (SDIO) Logic 1 Voltage Full 1.2 DRVDD + 0.3 V Logic 0 Voltage Full 0 0.3 V Input Resistance 25°C 30 kΩ Input Capacitance 25°C 2 pF LOGIC OUTPUT (SDIO)3 Logic 1 Voltage (I = 800 μA) Full 1.79 V OH Logic 0 Voltage (I = 50 μA) Full 0.05 V OL DIGITAL OUTPUTS (D+, D−), (ANSI-644)1 Logic Compliance LVDS Differential Output Voltage (V ) Full 247 454 mV OD Output Offset Voltage (V ) Full 1.125 1.375 V OS Output Coding (Default) Offset binary DIGITAL OUTPUTS (D+, D−), (LOW POWER, REDUCED SIGNAL OPTION)1 Logic Compliance LVDS Differential Output Voltage (V ) Full 150 250 mV OD Output Offset Voltage (V ) Full 1.10 1.30 V OS Output Coding (Default) Offset binary 1 See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions and how these tests were completed. 2 Specified for LVDS and LVPECL only. 3 Specified for 13 SDIO pins sharing the same connection. Rev. B | Page 7 of 60

AD9271 SWITCHING SPECIFICATIONS AVDD = 1.8 V, DRVDD = 1.8 V, CWVDD = 3.3 V, 400 mV p-p differential input, 1.0 V internal ADC reference, AIN = −0.5 dBFS, unless otherwise noted. Table 3. Parameter1 Temp Min Typ Max Unit CLOCK2 Maximum Clock Rate Full 50 MSPS Minimum Clock Rate Full 10 MSPS Clock Pulse Width High (t ) Full 10.0 ns EH Clock Pulse Width Low (t ) Full 10.0 ns EL OUTPUT PARAMETERS2, 3 Propagation Delay (t ) Full 1.5 2.3 3.1 ns PD Rise Time (t) (20% to 80%) Full 300 ps R Fall Time (t) (20% to 80%) Full 300 ps F FCO Propagation Delay (t ) Full 1.5 2.3 3.1 ns FCO DCO Propagation Delay (t )4 Full t + ns CPD FCO (t /24) SAMPLE DCO to Data Delay (t )4 Full (t /24) − 300 (t /24) (t /24) + 300 ps DATA SAMPLE SAMPLE SAMPLE DCO to FCO Delay (t )4 Full (t /24) − 300 (t /24) (t /24) + 300 ps FRAME SAMPLE SAMPLE SAMPLE Data-to-Data Skew (t − t ) Full ±50 ±200 ps DATA-MAX DATA-MIN Wake-Up Time (Standby), V = 0.5 V 25°C 1 μs GAIN Wake-Up Time (Power-Down) 25°C 1 ms Pipeline Latency Full 8 Clock cycles APERTURE Aperture Uncertainty (Jitter) 25°C <1 ps rms 1 See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions and how these tests were completed. 2 Can be adjusted via the SPI interface. 3 Measurements were made using a part soldered to FR-4 material. 4 tSAMPLE/24 is based on the number of bits divided by 2, because the delays are based on half duty cycles. Rev. B | Page 8 of 60

AD9271 ADC TIMING DIAGRAMS N – 1 AIN t A N t t EH EL CLK– CLK+ t CPD DCO– DCO+ tFCO tFRAME FCO– FCO+ t PD t DATA DOUTx– MSB D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 MSB D10 DOUTx+ N – 9 N – 9 N – 9 N – 9 N – 9 N – 9 N – 9 N – 9 N – 9 N – 9 N – 9 N – 9 N – 8 N – 8 06304-002 Figure 2. 12-Bit Data Serial Stream (Default) N – 1 AIN t A N t t EH EL CLK– CLK+ t CPD DCO– DCO+ tFCO tFRAME FCO– FCO+ tPD tDATA DOUTx– LSB D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 LSB D0 N – 9 N – 9 N – 9 N – 9 N – 9 N – 9 N – 9 N – 9 N – 9 N – 9 N – 9 N – 9 N – 8 N – 8 DOUTx+ 06304-004 Figure 3. 12-Bit Data Serial Stream, LSB First Rev. B | Page 9 of 60

AD9271 ABSOLUTE MAXIMUM RATINGS Table 4. With Stresses above those listed under Absolute Maximum Ratings Parameter Respect To Rating may cause permanent damage to the device. This is a stress ELECTRICAL rating only; functional operation of the device at these or any AVDD GND −0.3 V to +2.0 V other conditions above those indicated in the operational DRVDD GND −0.3 V to +2.0 V section of this specification is not implied. Exposure to absolute CWVDD GND −0.3 V to +3.9 V maximum rating conditions for extended periods may affect GND GND −0.3 V to +0.3 V device reliability. AVDD DRVDD −2.0 V to +2.0 V THERMAL IMPEDANCE Digital Outputs GND −0.3 V to +2.0 V (DOUTx+, DOUTx−, Table 5. DCO+, DCO−, Air Flow Velocity (m/s) θ 1 θ θ Unit JA JB JC FCO+, FCO−) 0.0 20.3 °C/W CLK+, CLK− GND −0.3 V to +3.9 V 1.0 14.4 7.6 4.7 °C/W LI-x LG-x −0.3 V to +2.0 V 2.5 12.9 °C/W LO-x LG-x −0.3 V to +2.0 V LOSW-x LG-x −0.3 V to +2.0 V 1 θJA for a 4-layer PCB with solid ground plane (simulated). Exposed pad CWDx−, CWDx+ GND −0.3 V to +3.9 V soldered to PCB. SDIO, GAIN+, GAIN− GND −0.3 V to +2.0 V ESD CAUTION PDWN, STBY, SCLK, CSB GND −0.3 V to +3.9 V REFT, REFB, RBIAS GND −0.3 V to +2.0 V VREF, SENSE GND −0.3 V to +2.0 V ENVIRONMENTAL Operating Temperature −40°C to +85°C Range (Ambient) Storage Temperature −65°C to +150°C Range (Ambient) Maximum Junction 150°C Temperature Lead Temperature 300°C (Soldering, 10 sec) Rev. B | Page 10 of 60

AD9271 PIN CONFIGURATION AND FUNCTION DESCRIPTIONS OSW-E O-E WD5+ WD5– WD4+ WD4– WD3+ WD3– VDD EFT EFB REF ENSE BIAS AIN+ AIN– WVDD WD2+ WD2– D1+W WD1– WD0+ WD0– O-D OSW-D L L C C C C C C A R R V S R G G C C C C C C C L L 100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81 80 79 78 77 76 LI-E 1 PIN 1 75 LI-D INDICATOR LG-E 2 74 LG-D AVDD 3 73 AVDD AVDD 4 72 AVDD LO-F 5 EXPOSED PADDLE, PIN 0 71 LO-C (BOTTOM OF PACKAGE) LOSW-F 6 70 LOSW-C LI-F 7 69 LI-C AD9271 LG-F 8 TOP VIEW 68 LG-C AVDD 9 (Not to Scale) 67 AVDD AVDD 10 66 AVDD LO-G 11 65 LO-B LOSW-G 12 64 LOSW-B LI-G 13 63 LI-B LG-G 14 62 LG-B AVDD 15 61 AVDD AVDD 16 60 AVDD LO-H 17 59 LO-A LOSW-H 18 58 LOSW-A LI-H 19 57 LI-A LG-H 20 56 LG-A AVDD 21 55 AVDD AVDD 22 54 AVDD CLK– 23 53 CSB CLK+ 24 52 SDIO AVDD 25 51 SCLK 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 DRVDD DOUTH– DOUTH+ DOUTG– DOUTG+ DOUTF– DOUTF+ DOUTE– DOUTE+ DCO– DCO+ FCO– FCO+ DOUTD– DOUTD+ DOUTC– DOUTC+ DOUTB– DOUTB+ DOUTA– DOUTA+ DRVDD STBY PDWN AVDD 06304-005 Figure 4. 100-Lead TQFP Pin Configuration Table 6. Pin Function Descriptions Pin No. Name Description 0 GND Ground (exposed paddle should be tied to a quiet analog ground) 3, 4, 9, 10, 15, AVDD 1.8 V Analog Supply 16, 21, 22, 25, 50, 54, 55, 60, 61, 66, 67, 72, 73, 92 26, 47 DRVDD 1.8 V Digital Output Driver Supply 84 CWVDD 3.3 V Analog Supply 1 LI-E LNA Analog Input for Channel E 2 LG-E LNA Ground for Channel E 5 LO-F LNA Analog Output for Channel F 6 LOSW-F LNA Analog Output Complement for Channel F 7 LI-F LNA Analog Input for Channel F 8 LG-F LNA Ground for Channel F 11 LO-G LNA Analog Output for Channel G 12 LOSW-G LNA Analog Output Complement for Channel G 13 LI-G LNA Analog Input for Channel G 14 LG-G LNA Ground for Channel G 17 LO-H LNA Analog Output for Channel H Rev. B | Page 11 of 60

AD9271 Pin No. Name Description 18 LOSW-H LNA Analog Output Complement for Channel H 19 LI-H LNA Analog Input for Channel H 20 LG-H LNA Ground for Channel H 23 CLK− Clock Input Complement 24 CLK+ Clock Input True 27 DOUTH− ADC H Digital Output Complement 28 DOUTH+ ADC H Digital Output True 29 DOUTG− ADC G Digital Output Complement 30 DOUTG+ ADC G Digital Output True 31 DOUTF− ADC F Digital Output Complement 32 DOUTF+ ADC F Digital Output True 33 DOUTE− ADC E Digital Output Complement 34 DOUTE+ ADC E Digital Output True 35 DCO− Data Clock Digital Output Complement 36 DCO+ Data Clock Digital Output True 37 FCO− Frame Clock Digital Output Complement 38 FCO+ Frame Clock Digital Output True 39 DOUTD− ADC D Digital Output Complement 40 DOUTD+ ADC D Digital Output True 41 DOUTC− ADC C Digital Output Complement 42 DOUTC+ ADC C Digital Output True 43 DOUTB− ADC B Digital Output Complement 44 DOUTB+ ADC B Digital Output True 45 DOUTA− ADC A Digital Output Complement 46 DOUTA+ ADC A Digital Output True 48 STBY Standby Power-Down 49 PDWN Full Power-Down 51 SCLK Serial Clock 52 SDIO Serial Data Input/Output 53 CSB Chip Select Bar 56 LG-A LNA Ground for Channel A 57 LI-A LNA Analog Input for Channel A 58 LOSW-A LNA Analog Output Complement for Channel A 59 LO-A LNA Analog Output for Channel A 62 LG-B LNA Ground for Channel B 63 LI-B LNA Analog Input for Channel B 64 LOSW-B LNA Analog Output Complement for Channel B 65 LO-B LNA Analog Output for Channel B 68 LG-C LNA Ground for Channel C 69 LI-C LNA Analog Input for Channel C 70 LOSW-C LNA Analog Output Complement for Channel C 71 LO-C LNA Analog Output for Channel C 74 LG-D LNA Ground for Channel D 75 LI-D LNA Analog Input for Channel D 76 LOSW-D LNA Analog Output Complement for Channel D 77 LO-D LNA Analog Output for Channel D 78 CWD0− CW Doppler Output Complement for Channel 0 79 CWD0+ CW Doppler Output True for Channel 0 80 CWD1− CW Doppler Output Complement for Channel 1 81 CWD1+ CW Doppler Output True for Channel 1 82 CWD2− CW Doppler Output Complement for Channel 2 83 CWD2+ CW Doppler Output True for Channel 2 85 GAIN− Gain Control Voltage Input Complement Rev. B | Page 12 of 60

AD9271 Pin No. Name Description 86 GAIN+ Gain Control Voltage Input True 87 RBIAS External Resistor to Set the Internal ADC Core Bias Current 88 SENSE Reference Mode Selection 89 VREF Voltage Reference Input/Output 90 REFB Differential Reference (Negative) 91 REFT Differential Reference (Positive) 93 CWD3− CW Doppler Output Complement for Channel 3 94 CWD3+ CW Doppler Output True for Channel 3 95 CWD4− CW Doppler Output Complement for Channel 4 96 CWD4+ CW Doppler Output True for Channel 4 97 CWD5− CW Doppler Output Complement for Channel 5 98 CWD5+ CW Doppler Output True for Channel 5 99 LO-E LNA Analog Output for Channel E 100 LOSW-E LNA Analog Output Complement for Channel E Rev. B | Page 13 of 60

AD9271 EQUIVALENT CIRCUITS AVDD AVDD VCM 15kΩ 350Ω LI-x, SDIO LG-x 30kΩ 06304-073 06304-008 Figure 5. Equivalent LNA Input Circuit Figure 8. Equivalent SDIO Input Circuit DRVDD AVDD V V DOUTx– DOUTx+ LO-x, 10Ω V V LOSW-x 06304-075 DRGND 06304-009 Figure 6. Equivalent LNA Output Circuit Figure 9. Equivalent Digital Output Circuit 10Ω CLK+ 10kΩ 1.25V 10kΩ 1kΩ 10Ω SCLK OR PDWN CLK– OR STBY 30kΩ 06304-007 06304-010 Figure 7. Equivalent Clock Input Circuit Figure 10. Equivalent SCLK Input Circuit Rev. B | Page 14 of 60

AD9271 AVDD 100Ω RBIAS AVDD VREF 06304-011 6kΩ 06304-014 Figure 11. Equivalent RBIAS Circuit Figure 14. Equivalent VREF Circuit AVDD 70kΩ 1kΩ CSB 50Ω GAIN+ 06304-012 06304-074 Figure 12. Equivalent CSB Input Circuit Figure 15. Equivalent GAIN+ Input Circuit 1kΩ SENSE 40kΩ GAIN– +0.5V 06304-013 06304-112 Figure 13. Equivalent SENSE Circuit Figure 16. Equivalent GAIN− Input Circuit CWDx+, 10Ω CWDx– 06304-076 Figure 17. Equivalent CWDx± Output Circuit Rev. B | Page 15 of 60

AD9271 TYPICAL PERFORMANCE CHARACTERISTICS f = 50 MSPS, f = 5 MHz, LPF = 1/3 × f , HPF = 700 kHz, LNA gain = 6×. SAMPLE IN SAMPLE 2.0 25 SAMPLE SIZE = 720 CHANNELS 1.5 20 1.0 B) %) RROR (d 0.5 +85°C UNITS ( 15 E 0 F OLUTE –0.5 –+4205°°CC CENT O 10 S R B E A –1.0 P 5 ––21..05 06304-019 0 06304-121 0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0 –1.0 –0.8 –0.6 –0.4 –0.2 0 0.2 0.4 0.6 0.8 1.0 VGAIN (V) GAIN ERROR (dB) Figure 18. Gain Error vs. VGAIN at Three Temperatures Figure 21. Gain Error Histogram with VGAIN = 0.9 V 20 30 SAMPLE SIZE = 720 CHANNELS 18 25 16 %) 14 %) S ( S ( 20 NIT 12 NIT U U OF 10 OF 15 T T EN 8 EN C C R R 10 E 6 E P P 4 5 02 4-1200630 0 06304-118 –1.0 –0.8 –0.6 –0.4 –0.2 0 0.2 0.4 0.6 0.8 1.0 –1.25 –1.00 –0.75 –0.50 –0.25 0 0.25 0.50 0.75 1.00 1.25 GAIN ERROR (dB) CHANNEL-TO-CHANNEL GAIN MATCHING (dB) Figure 19. Gain Error Histogram with VGAIN = 0.1 V Figure 22. Gain Match Histogram for VGAIN = 0.2 V 16 30 SAMPLE SIZE = 720 CHANNELS 14 25 PERCENT OF UNITS (%) 1120864 PERCENT OF UNITS (%) 211050 5 20 06304-116 0 06304-117 –1.0 –0.9 –0.8 –0.7 –0.6 –0.5 –0.4 –0.3G–0.2AIN–0.1 E0RR0.1OR0.2 (d0.3B)0.4 0.5 0.6 0.7 0.8 0.9 1.0 –1.25 –1C.0H0A–N0N.7E5L–-T0.O50-C–H0A.2N5NE0L GA0I.N25 MA0.T5C0HI0N.7G5 (d1B.0)0 1.25 Figure 20. Gain Error Histogram with VGAIN = 0.5 V Figure 23. Gain Match Histogram for VGAIN = 0.8 V Rev. B | Page 16 of 60

AD9271 2000000 –131 11680000000000 S/ Hz) ––113332 LNA GAIN = 8× F B 1400000 d MBER OF HITS11028000000000000000 ERRED NOISE ( –––111333654 LNA GAIN = 6× U F N E –137 600000 R T- 400000 PU –138 LNA GAIN = 5× T U 2000000 06304-022 O ––114309 06304-021 –5 –4 –3 –2 –1 0 1 2 3 4 5 0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0 CODES VGAIN (V) Figure 24. Output-Referred Noise Histogram with VGAIN = 0.0 V Figure 27. Short-Circuit, Output-Referred Noise vs. VGAIN 1200000 64.0 63.5 SNR (dBFS) 1000000 63.0 TS 800000 62.5 SINAD (dBFS) HI D OF NA 62.0 R 600000 SI BE NR/ 61.5 M S U N 400000 61.0 60.5 200000 0 06304-023 5690..50 06304-020 –5 –4 –3 –2 –1 0 1 2 3 4 5 0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0 CODES VGAIN (V) Figure 25. Output-Referred Noise Histogram with VGAIN = 1.0 V Figure 28. SNR/SINAD vs. VGAIN, AIN = −6.5 dBFS 4.5 1.70 4.0 V/ Hz) 3.5 V/ Hz) 1.65 n n E ( 3.0 E ( 1.60 S S OI OI N 2.5 N D D 1.55 E E R 2.0 R R LNA GAIN = 5× R E E F F E 1.5 LNA GAIN = 6× E 1.50 R R T- LNA GAIN = 8× T- PU 1.0 PU IN IN 1.45 0.50 06304-025 1.40 06304-024 0 5 10 15 20 25 –40 –20 0 20 40 60 80 FREQUENCY (MHz) TEMPERATURE (°C) Figure 26. Short-Circuit, Input-Referred Noise vs. Frequency Figure 29. Short-Circuit, Input-Referred Noise vs. Temperature Rev. B | Page 17 of 60

AD9271 0 –50 –5 –55 AL (dBFS) ––1150 –3dB LINE (1/3) × 40MSP(1S/3) × 50MSPS NIC (dBFS) ––6650 VGAIN = 1V NT –20 MO VGAIN = 0.5V ME AR –70 FUNDA –25 HIRD H –75 –30 (1/3) × 25MSPS T VGAIN = 0.2V ––3450 06304-030 ––8850 06304-029 0 2.5 5.0 7.5 10.0 12.5 15.0 17.5 20.0 22.5 25.0 2 4 6 8 10 12 14 16 FREQUENCY (MHz) fIN (MHz) Figure 30. Antialiasing Filter (AAF) Pass-Band Response, No HPF Applied Figure 33. Third-Order Harmonic Distortion vs. Frequency, AIN = −0.5 dBFS 300 –40 VGAIN = 0.5V 250 –50 VGAIN = 1.0V S) LAY (ns) 200 ONIC (dBF ––6700 VGAIN = 0VVGAIN = 1V UP DE 150 HARM –80 GRO 100 OND C –90 VGAIN = 0V SE 50 0 06304-033 ––111000 VGAIN = 0.5V 06304-114 0.1 1 10 100 –40 –35 –30 –25 –20 –15 –10 –5 0 ANALOG INPUT FREQUENCY (MHz) ADC OUTPUT LEVEL (dBFS) Figure 31. Antialiasing Filter (AAF) Group Delay Response Figure 34. Second-Order Harmonic Distortion vs. ADC Output Level –50 –40 –55 –50 ONIC (dBFS) ––6650 VVGGAAININ = = 0 1.2VV NIC (dBFS) ––6700 VGAIN = 1V RM MO VGAIN = 0V HA –70 AR –80 ND D H O R C –75 HI –90 SE VGAIN = 0.5V T –80 –100 –85 06304-028 –110 VGAIN = 0.5V 06304-115 2 4 6 8 10 12 14 16 –40 –35 –30 –25 –20 –15 –10 –5 0 fIN (MHz) ADC OUTPUT LEVEL (dBFS) Figure 32. Second-Order Harmonic Distortion vs. Frequency, AIN = −0.5 dBFS Figure 35. Third-Order Harmonic Distortion vs. ADC Output Level Rev. B | Page 18 of 60

AD9271 0 0 –10 AIN1 =AIN2 = –7dBFS AIN1= AIN2=–7dBFS f1= 5MHz –20 –20 IMD2=–f720=.5 69MdBHcz IMD3=–64.45dBc –30 VGAIN=1V S) –40 –40 F BFS) –50 E (dB MD3 (d –60 8MHzAND 10.3MHz LITUD –60 I –70 AMP –80 –80 –90 –100 ––110100 5MHzAND 6MHz 2.3MHzAND 3.5MHz 06304-106 –120 06304-108 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0 0 5 10 15 20 25 VGAIN(V) FREQUENCY (MHz) Figure 36. IMD3 vs. VGAIN Figure 38. Typical IMD3 and IMD2 Performance 0 –10 f1 = 5MHz f2 = 6MHz –20 –30 –40 S) BF –50 d 3 ( –60 D M I –70 –80 VGAIN =1V VGAIN =0.5V –90 VGAIN =0V ––110100–60 –55 –50 –45 –40 –35 –30 –25 –20 –15 –10 –506304-107 INPUT AMPLITUDE (dBFS) Figure 37. IMD3 vs. Amplitude Rev. B | Page 19 of 60

AD9271 THEORY OF OPERATION ULTRASOUND following the TGC amplifier, and then beam forming is accomplished digitally. The primary application for the AD9271 is medical ultrasound. The ADC resolution of 12 bits with up to 50 MSPS sampling Figure 39 shows a simplified block diagram of an ultrasound satisfies the requirements of both general-purpose and high- system. A critical function of an ultrasound system is the time end systems. gain control (TGC) compensation for physiological signal attenuation. Because the attenuation of ultrasound signals is Power consumption and low cost are of primary importance in exponential with respect to distance (time), a linear-in-dB VGA low-end and portable ultrasound machines, and the AD9271 is is the optimal solution. designed for these criteria. Key requirements in an ultrasound signal chain are very low For additional information regarding ultrasound systems, refer noise, active input termination, fast overload recovery, low to “How Ultrasound System Considerations Influence Front-End power, and differential drive to an ADC. Because ultrasound Component Choice,” Analog Dialogue, Volume 36, Number 3, machines use beam-forming techniques requiring large binary- May–July 2002, and “The AD9271—A Revolutionary Solution weighted numbers (for example, 32 to 512) of channels, the for Portable Ultrasound,” Analog Dialogue, Volume 41, Number 7, lowest power at the lowest possible noise is of key importance. July 2007. Most modern machines use digital beam forming. In this technique, the signal is converted to digital format immediately Tx HVAMPs TxBEAM FORMER BEAM FORMER CENTRAL CONTROL MULTICHANNELS HV Rx BEAM FORMER DMEMUXU/X SWITT/CRHES LNA VGA AAF ADC (BAND F MODES) CW AD9271 TRANSDUCER ARRAY 128, 256, ETC., ELEMENTS CW (ANALOG) BIDIRECTIONAL BEAM FORMER SPECTRAL IMAGEAND COLOR CABLE DOPPLER MOTION DOPPLER (PW) PROCESSING PROCESSING PROCESSING MODE (B MODE) (F MODE) AUDIO DISPLAY OUTPUT 06304-077 Figure 39. Simplified Ultrasound System Block Diagram Rev. B | Page 20 of 60

AD9271 RFB1 LO-x gm SWTIOTCH CDWx+ ARRAY CDWx– CFB RFB2 LOSW-x T/R SWITCH CS LI-x CER CSH LNA A–3T0TdEBN TUOA T0OdBR +24dB AAF PI1PA2E-DBLCIITNE SLEVRDIASL DDOOUUTTxx+– DU CLG LG-x S N A R T GAIN INTERPOLATOR AD9271 + – N N GAI GAI 06304-071 Figure 40. Simplified Block Diagram of a Single Channel CHANNEL OVERVIEW The LNA supports differential output voltages as high as 2 V p-p with positive and negative excursions of ±0.5 V from a common- Each channel contains both a TGC signal path and a CW Doppler mode voltage of 0.9 V. The LNA differential gain sets the maximum signal path. Common to both signal paths, the LNA provides user- input signal before saturation. One of three gains is set through adjustable input impedance termination. The CW Doppler path the SPI. The corresponding input full scale for the gain settings includes a transconductance amplifier and a crosspoint switch. The of 5, 6, or 8 is 400 mV p-p, 333 mV p-p, and 250 mV p-p, TGC path includes a differential X-AMP® VGA, an antialiasing respectively. Overload protection ensures quick recovery time filter, and an ADC. Figure 40 shows a simplified block diagram from large input voltages. Because the inputs are capacitively with external components. coupled to a bias voltage near midsupply, very large inputs can The signal path is fully differential throughout to maximize be handled without interacting with the ESD protection. signal swing and reduce even-order distortion; however, the Low value feedback resistors and the current-driving capability LNA is designed to be driven from a single-ended signal source. of the output stage allow the LNA to achieve a low input-referred Low Noise Amplifier (LNA) noise voltage of 1.2 nV/√Hz. This is achieved with a current Good noise performance relies on a proprietary ultralow noise consumption of only 16 mA per channel (30 mW). On-chip LNA at the beginning of the signal chain, which minimizes the resistor matching results in precise single-ended gains, which noise contribution in the following VGA. Active impedance are critical for accurate impedance control. The use of a fully control optimizes noise performance for applications that benefit differential topology and negative feedback minimizes distortion. from input impedance matching. Low HD2 is particularly important in second-harmonic ultrasound imaging applications. Differential signaling enables smaller swings A simplified schematic of the LNA is shown in Figure 41. LI-x is at each output, further reducing third-order distortion. capacitively coupled to the source. An on-chip bias generator establishes dc input bias voltages of around 1.4 V and centers Active Impedance Matching the output common-mode levels at 0.9 V (VDD/2). A capacitor, The LNA consists of a single-ended voltage gain amplifier with C , of the same value as the input coupling capacitor, C, is LG S differential outputs and the negative output externally available. connected from the LG-x pin to ground. For example, with a fixed gain of 6× (15.6 dB), an active input CFB RFB1 termination is synthesized by connecting a feedback resistor RFB2 between the negative output pin, LO-x, and the positive input AVDD2 VO– VO+ LOSW-x pin, LI-x. This technique is well known and results in the input VCM VCM resistance shown in Equation 1: LO-x T/R SWITCHCS LI-x LG-x R = RFB (1) R IN (1+A ) UCE CSH CLG 2 D S where A/2 is the single-ended gain or the gain from the LI-x TRAN 06304-101 inputs to the LO-x outputs. Figure 41. Simplified LNA Schematic Rev. B | Page 21 of 60

AD9271 Because the amplifier has a gain of 6× from its input to its Table 7. Active Termination External Component Values differential output, it is important to note that the gain A/2 is Minimum the gain from Pin LI-x to Pin LO-x, and it is 6 dB less than the LNA Gain RIN (Ω) RFB (Ω) CSH (pF) BW (MHz) gain of the amplifier, or 9.6 dB (3×). The input resistance is 5× 50 175 90 49 reduced by an internal bias resistor of 15 kΩ in parallel with the 6× 50 200 70 59 source resistance connected to Pin LI-x, with Pin LG-x ac 8× 50 250 50 73 grounded. Equation 2 can be used to calculate the needed R 5× 100 350 30 49 FB for a desired R , even for higher values of R . 6× 100 400 20 59 IN IN 8× 100 500 10 73 R RIN =(1+FB3)||15kΩ (2) 5× 200 700 N/A 49 6× 200 800 N/A 49 For example, to set R to 200 Ω, the value of R is 845 Ω. If the IN FB 8× 200 1000 N/A 49 simplified equation (Equation 2) is used to calculate R , the IN value is 190 Ω, resulting in a gain error less than 0.5 dB. Some LNA Noise factors, such as the presence of a dynamic source resistance, might influence the absolute gain accuracy more significantly. The short-circuit noise voltage (input-referred noise) is an At higher frequencies, the input capacitance of the LNA needs important limit on system performance. The short-circuit noise to be considered. The user must determine the level of voltage for the LNA is 1.2 nV/√Hz or 1.4 nV/√Hz (at 15.6 dB matching accuracy and adjust R accordingly. LNA gain), including the VGA noise. These measurements, FB which were taken without a feedback resistor, provide the basis The bandwidth (BW) of the LNA is about 70 MHz. Ultimately for calculating the input noise and noise figure (NF) performance the BW of the LNA limits the accuracy of the synthesized R . IN of the configurations shown in Figure 43. Figure 44 and Figure 45 For R = R up to about 200 Ω, the best match is between IN S are simulations of noise figure vs. R results using these config- S 100 kHz and 10 MHz, where the lower frequency limit is urations and an input-referred noise voltage of 4 nV/√Hz for determined by the size of the ac-coupling capacitors, and the the VGA. Unterminated (R = ∞) operation exhibits the lowest FB upper limit is determined by the LNA BW. Furthermore, the equivalent input noise and noise figure. Figure 45 shows the input capacitance and R limit the BW at higher frequencies. S noise figure vs. source resistance rising at low R—where the S Figure 42 shows R vs. frequency for various values of R . IN FB LNA voltage noise is large compared with the source noise—and 1k at high R due to the noise contribution from R . The lowest S FB RS = 500Ω, RFB = 2kΩ NF is achieved when RS matches RIN. UNTERMINATED E (Ω) RS = 200Ω, RFB = 800Ω RS RIN C N + DA RS = 100Ω, RFB = 400Ω, CSH = 20pF VIN VOUT E 100 – P M UT I RS = 50Ω, RFB = 200Ω, CSH = 70pF RESISTIVE TERMINATION P IN RIN RS 10 06304-105 VIN+– RS VOUT 100k 1M 10M 50M FREQUENCY (Hz) ACTIVE IMPEDANCE MATCH Figure 42. RIN vs. Frequency for Various Values of RFB RIN RFB (Effects of RSH and CSH Are Also Shown) RS + Note that at the lowest value, 50 Ω, in Figure 42, RIN peaks at VIN VOUT frequencies greater than 10 MHz. This is due to the BW roll-off – oHfo twheev LeNr, Aas, caasn m been steieonn efodr plarregveiro RusINly v. alues, parasitic capacitance RIN=1 R+ FAB/2 06304-104 starts rolling off the signal BW before the LNA can produce Figure 43. Input Configurations peaking. C further degrades the match; therefore, C should SH SH not be used for values of R that are greater than 100 Ω. Table 7 IN lists the recommended values for R and C in terms of R . FB SH IN C is needed in series with R because the dc levels at Pin LO-x FB FB and Pin LI-x are unequal. Rev. B | Page 22 of 60

AD9271 16 INPUT OVERDRIVE 14 Excellent overload behavior is of primary importance in ultra- UNTERMINATED sound. Both the LNA and VGA have built-in overdrive 12 protection and quickly recover after an overload event. B) RESISTIVE TERMINATION E (d 10 ACTIVE TERMINATION Input Overload Protection R U G 8 As with any amplifier, voltage clamping prior to the inputs is FI OISE 6 highly recommended if the application is subject to high N transient voltages. 4 A block diagram of a simplified ultrasound transducer interface 02 06304-103 idsu sahl ofwunnc itnio Fnisg oufr et r4a6n.s Am ictotimngm aonnd trreacnesidvuincge ru eltlreamsoenutn sde ervneesr gthy.e 10 100 1000 During the transmitting phase, high voltage pulses are applied RS(Ω) to the ceramic elements. A typical transmit/receive (T/R) switch Figure 44. Noise Figure vs. RS for Resistive Termination, Active Termination can consist of four high voltage diodes in a bridge configuration. Matched, and Unterminated Inputs, VGain = 1 V, 15.6 dB LNA Gain Although the diodes ideally block transmit pulses from the 16 sensitive receiver input, diode characteristics are not ideal, and 14 resulting leakage transients imposed on the LI-x inputs can be problematic. 12 RIN = 50Ω B) Because ultrasound is a pulse system and time-of-flight is used E (d 10 RIN = 75Ω to determine depth, quick recovery from input overloads is R U FIG 8 RIN = 100Ω essential. Overload can occur in the preamp and the VGA. E Immediately following a transmit pulse, the typical VGA gains OIS 6 are low, and the LNA is subject to overload from T/R switch N 4 leakage. With increasing gain, the VGA can become overloaded due to strong echoes that occur near field echoes and 02 RINU =N T20E0RΩMINATED 06304-102 acoustically dense materials, such as bone. 10 100 1000 Figure 46 illustrates an external overload protection scheme. A RS(Ω) pair of back-to-back Schottky diodes is installed prior to installing Figure 45. Noise Figure vs. RS for Various Fixed Values of RIN, the ac-coupling capacitors. Although the BAS40 diodes are shown, Active Termination Matched Inputs, VGain = 1 V, 15.6 dB LNA Gain any diode is prone to exhibiting some amount of shot noise. Many The primary purpose of input impedance matching is to improve types of diodes are available for achieving the desired noise per- the transient response of the system. With resistive termination, the formance. The configuration shown in Figure 46 tends to add input noise increases due to the thermal noise of the matching 2 nV/√Hz of input-referred noise. Decreasing the 5 kΩ resistor resistor and the increased contribution of the LNA’s input and increasing the 2 kΩ resistor may improve noise contribution, voltage noise generator. With active impedance matching, depending on the application. With the diodes shown in Figure 46, however, the contributions of both are smaller (by a factor of clamping levels of ±0.5 V or less significantly enhance the 1/(1 + LNA Gain)) than they would be for resistive termination. overload performance of the system. Figure 44 shows the relative noise figure performance. In this +5V graph, the input impedance was swept with R to preserve the S Tx 5kΩ match at each point. The noise figures for a source impedance of DRIVER HV AD9271 50 Ω are 7.1 dB, 4.1 dB, and 2.5 dB for the resistive termination, BAS40-04 10nF active termination, and unterminated configurations, respectively. LNA The noise figures for 200 Ω are 4.6 dB, 2.0 dB, and 1.0 dB, 2kΩ 5kΩ 10nF rFeigspuercet 4iv5e slyh.o ws the noise figure as it relates to RS for various values TRANSDUCER –5V 06304-100 of R , which is helpful for design purposes. Figure 46. Input Overload Protection IN Rev. B | Page 23 of 60

AD9271 CW DOPPLER OPERATION gain, and it defines a focal point within the body from which the location of the returning echo is derived. Modern ultrasound machines used for medical applications employ a 2N binary array of receivers for beam forming, with The AD9271 includes the front-end components needed to typical array sizes of 16 or 32 receiver channels phase-shifted implement analog beam forming for CW Doppler operation. and summed together to extract coherent information. When These components allow CW channels with similar phases to be used in multiples, the desired signals from each channel can be coherently combined before phase alignment and down mixing, summed to yield a larger signal (increased by a factor N, where thus reducing the number of delay lines or adjustable phase shifters/ N is the number of channels), and the noise is increased by the down mixers (AD8333 or AD8339) required. Next, if delay lines square root of the number of channels. This technique enhances are used, the phase alignment is performed and then the channels the signal-to-noise performance of the machine. The critical are coherently summed and down converted by a dynamic range elements in a beam-former design are the means to align the I/Q demodulator. Alternatively, if phase shifters/down mixers, incoming signals in the time domain and the means to sum the such as the AD8333 and AD8339, are used, phase alignment individual signals into a composite whole. and downconversion are done before coherently summing all channels into I/Q signals. In either case, the resultant I and Q Beam forming, as applied to medical ultrasound, is defined as the signals are filtered and sampled by two high resolution ADCs, phase alignment and summation of signals that are generated and the sampled signals are processed to extract the relevant from a common source but received at different times by a Doppler information. multielement ultrasound transducer. Beam forming has two functions: it imparts directivity to the transducer, enhancing its AD9271 LNA gm LNA gm SWITCH 8 × CHANNEL ARRAY AD8333 600nH LNA gm 2.5V 700Ω 600nH LNA gm 600nH 2.5V 700Ω 600nH AD8333 AD9271 600nH 2.5V 700Ω LNA gm 600nH LNA gm 600nH 2.5V 700Ω 600nH SWITCH ARRAY I 8 × CHANNEL 16-BIT ADC LNA gm LNA gm Q 1A6-DBCIT 06304-096 Figure 47. Typical CW Doppler System Using the AD9271 and AD8333 or AD8339 Rev. B | Page 24 of 60

AD9271 Crosspoint Switch The system gain is distributed as listed in Table 8. Each LNA is followed by a transconductance amp for V/I con- Table 8. Channel Gain Distribution version. Currents can be routed to one of six pairs of differential Section Nominal Gain (dB) outputs or to 12 single-ended outputs for summing. Each CWD LNA 14/15.6/18 output pin sinks 2.4 mA dc current, and the signal has a full-scale Attenuator 0 to −30 current of ±2 mA for each channel selected by the crosspoint VGA Amp 24 switch. For example, if four channels were to be summed on Filter 0 one CWD output, the output would sink 9.6 mA dc and have a ADC 0 full-scale current output of ±8 mA. The maximum number of Total 8.4 to 38.4/10 to 40/12.4 to 42.4 channels combined must be considered when setting the load impedance for I/V conversion to ensure that the full-scale swing and common-mode voltage are within the operating limits of The linear-in-dB gain (law conformance) range of the TGC path the AD9271. When interfacing to the AD8339, a common- is 30 dB, extending from 10 dB to 40 dB. The slope of the gain mode voltage of 2.5 V and a full-scale swing of 2.8 V p-p are control interface is 31.6 dB/V, and the gain control range is 0 V desired. This can be accomplished by connecting an inductor to 1 V as specified in Equation 3. Equation 4 is the expression between each CWD output and a 2.5 V supply, and then for channel gain. connecting either a single-ended or differential load resistance V (V)=(GAIN+)−(GAIN−)+0.5 (3) GAIN to the CWD± outputs. The value of resistance should be calculated based on the maximum number of channels that can Gain(dB)=31.6dBV +ICPT (4) V GAIN be combined. where ICPT is the intercept point of the TGC gain. CWD± outputs are required under full-scale swing to be greater In its default condition, the LNA has a gain of 15.6 dB (6×) and than 1.5 V and less than CWVDD (3.3 V supply). the VGA gain is −6 dB if the voltage on the GAIN± pins is 0 V. TGC OPERATION This gives rise to a total gain (or ICPT) of 10 dB through the The TGC signal path is fully differential throughout to maximize TGC path if the LNA input is unmatched, or of 4 dB if the LNA signal swing and reduce even-order distortion; however, the LNAs is matched to 50 Ω (R = 200 Ω). If the voltage on the GAIN± FB are designed to be driven from a single-ended signal source. Gain pins is 1 V, however, the VGA gain is 24 dB. This gives rise to a values are referenced from the single-ended LNA input to the total gain of 40 dB through the TGC path if the LNA input is differential ADC input. A simple exercise in understanding the unmatched, or of 34 dB if the LNA input is matched. maximum and minimum gain requirements is shown in Figure 48. Each LNA output is dc-coupled to a VGA input. The VGA consists of an attenuator with a range of 30 dB followed by an amplifier ADCFS(2Vp-p) with 24 dB of gain for a net gain range of −6 dB to +24 dB. The MINIMUM GAIN ~5dBMARGIN X-AMP gain-interpolation technique results in low gain error (0.333VLpN-pA S FES) 70dB ADC and uniform bandwidth, and differential signal paths minimize distortion. 87dB >8dBMARGIN At low gains, the VGA should limit the system noise perfor- LNA ADC NOISE FLOOR (224µVrms) mance (SNR); at high gains, the noise is defined by the source and MAXIMUM GAIN LNA. The maximum voltage swing is bound by the full-scale LNA INPUT-REFERRED NOISE FLOOR peak-to-peak ADC input voltage (2 V p-p). (5L.4NµAV+rmVsG)A @ NAOAISFEB=W1.=4n1V5M/ HHzz VMGAAX GCHAAINN RNAENL GGEA I>N 3 >0 d4B0dB 06304-097 Both the LNA and VGA have limitations within each section of Figure 48. Gain Requirements of TGC for a 12-Bit, 40 MSPS ADC the TGC path, depending on the voltage applied to the GAIN+ and GAIN− pins. The LNA has three limitations, or full-scale settings, In summary, the maximum gain required is determined by depending on the gain selection applied through the SPI interface. (ADC Noise Floor/VGA Input Noise Floor) + Margin = When a voltage of 0.2 V or less is applied to the GAIN± pins, the 20 log(224/5.4) + 8 dB = 40.3 dB LNA operates near the full-scale input range to maximize the The minimum gain required is determined by dynamic range of the ADC without clipping the signal. When more than 0.2 V is applied to the GAIN± pins, the input signal to (ADC Input FS/VGA Input FS) + Margin = the LNA must be lowered to keep it within the full-scale range 20 log(2/0.333) – 5 dB = 10.6 dB of the ADC (see Figure 49). Therefore, a 12-bit, 40 MSPS ADC with 15 MHz of bandwidth should suffice in achieving the dynamic range required for most of today’s ultrasound systems. Rev. B | Page 25 of 60

AD9271 0.450 slope is monotonic with respect to the control voltage and is LNA GAIN = 5x 0.400 stable with variations in process, temperature, and supply. p) 0.350 The X-AMP inputs are part of a 24 dB gain feedback amplifier p- that completes the VGA. Its bandwidth is about 70 MHz. The V 0.300 LNA E ( GAIN = 6x input stage is designed to reduce feedthrough to the output and L CA 0.250 to ensure excellent frequency response uniformity across the S LL- 0.200 LNA GAIN = 8x gain setting. U F T 0.150 Gain Control U P IN 0.100 The gain control interface, GAIN±, is a differential input. The VGA gain, V , is shown in Equation 3. V varies the gain 0.05000 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.006304-110 oinf paullt V sGtaAgess t hcGorAonINungehc ttehde tinot tehrpe oilnaptourt baytt seenleucattiGonArgI.N tThhee a pnpormopinriaalt e VGAIN (V) VGAIN range for 30 dB/V is 0 V to 1 V, with the best gain linearity Figure 49. LNA/VGA Full-Scale Limitations from about 0.1 V to 0.9 V, where the error is typically less than Variable Gain Amplifier ±0.5 dB. For VGAIN voltages greater than 0.9 V and less than 0.1 V, the error increases. The value of V can exceed the supply GAIN The differential X-AMP VGA provides precise input attenuation voltage by 1 V without gain foldover. and interpolation. It has a low input-referred noise of 4 nV/√Hz and excellent gain linearity. A simplified block diagram is shown Gain control response time is less than 750 ns to settle within 10% in Figure 50. of the final value for a change from minimum to maximum gain. There are two ways in which the GAIN+ and GAIN− pins can GAIN GAININTERPOLATOR be interfaced. Using a single-ended method, a Kelvin type of POSTAMP + connection to ground can be used as shown in Figure 51. For gm driving multiple devices, it is preferable to use a differential 3dB method, as shown in Figure 52. In either method, the GAIN+ VIP and GAIN− pins should be dc-coupled and driven to accom- modate a 1 V full-scale input. VIN AD9271 100Ω GAIN+ 0 TO 1V DC 0.01µF 50Ω – POSTAMP 06304-078 GAIN– 0.01µF CONKNELEVCITNION 06304-109 Figure 50. Simplified VGA Schematic Figure 51. Single-Ended GAIN± Pins Configuration The input of the VGA is a 12-stage differential resistor ladder with 499Ω AVDD 3.01 dB per tap. The resulting total gain range is 30 dB, which AD9271 ±0.25DC AT 26kΩ allows for range loss at the endpoints. The effective input resistance 100Ω 0.5V CM 499Ω GAIN+ ±0.5V DC per side is 180 Ω nominally for a total differential resistance of 0.01µF AD8138 0.5V CM 50Ω 360 Ω. The ladder is driven by a fully differential input signal from 100Ω 523Ω GAIN– ±0.25DC AT 10kΩ tcVhaGep aALcN iitsAo c.r osL.nN TtArho eol lcueodtpm bumyts aoannre -a mdmcop-dcloiefu iveporl lettdhag ateot uoafsv eothsid et h eaextt tseeanrmnuaaelt omdre icadonsudup ptlpihnleyg 0.01µF 0.5V CM 499Ω 06304-098 Figure 52. Differential GAIN± Pins Configuration voltage derived in the LNA, permitting dc coupling of the LNA VGA Noise to the VGA without introducing large offsets due to common- mode differences. However, any offset from the LNA will be In a typical application, a VGA compresses a wide dynamic amplified as the gain is increased, producing an exponentially range input signal to within the input span of an ADC. The increasing VGA output offset. input-referred noise of the LNA limits the minimum resolvable input signal, whereas the output-referred noise, which depends The input stages of the X-AMP are distributed along the ladder, primarily on the VGA, limits the maximum instantaneous and a biasing interpolator, controlled by the gain interface, dynamic range that can be processed at any one particular gain determines the input tap point. With overlapping bias currents, control voltage. This latter limit is set in accordance with the signals from successive taps merge to provide a smooth total noise floor of the ADC. attenuation range from 0 dB to −30 dB. This circuit technique results in linear-in-dB gain law conformance and low distortion Output-referred noise as a function of VGAIN is shown in Figure 24 levels—only deviating ±0.5 dB or less from the ideal. The gain and Figure 25 for the short-circuit input conditions. The input Rev. B | Page 26 of 60

AD9271 noise voltage is simply equal to the output noise divided by the The filter can be configured for dc coupling or to have a single measured gain at each point in the control range. pole for high-pass filtering at either 700 kHz or 350 kHz (programmed through the SPI). The high-pass pole, however, is The output-referred noise is a flat 63 nV/√Hz over most of the not tuned and can vary by ±30%. gain range, because it is dominated by the fixed output-referred noise of the VGA. At the high end of the gain control range, the A third-order Butterworth low-pass filter is used to reduce noise of the LNA and source prevail. The input-referred noise noise bandwidth and provide antialiasing for the ADC. The reaches its minimum value near the maximum gain control filter uses on-chip tuning to trim the capacitors and in turn set voltage, where the input-referred contribution of the VGA is the desired cutoff frequency and reduce variations. The default miniscule. −3 dB cutoff is 1/3 the ADC sample clock rate. The cutoff can be scaled to 0.7, 0.8, 0.9, 1, 1.1, 1.2, or 1.3 times this frequency At lower gains, the input-referred noise and, therefore, the noise through the SPI. The cutoff can be set from 8 MHz to 18 MHz. figure increases as the gain decreases. The instantaneous dynamic range of the system is not lost, however, because the input capacity Tuning is normally off to avoid changing the capacitor settings increases as the input-referred noise increases. The contribution during critical times. The tuning circuit is enabled and disabled of the ADC noise floor has the same dependence. The important through the SPI. Initializing the tuning of the filter must be relationship is the magnitude of the VGA output noise floor done after initial power-up and after reprogramming the filter relative to that of the ADC. cutoff scaling or ADC sample rate. Occasional retuning during an idle time is recommended to compensate for temperature drift. Gain control noise is a concern in very low noise applications. Thermal noise in the gain control interface can modulate the ADC channel gain. The resultant noise is proportional to the output The AD9271 architecture consists of a pipelined ADC divided signal level and is usually evident only when a large signal is into three sections: a 4-bit first stage followed by eight 1.5-bit present. The gain interface includes an on-chip noise filter, which stages and a 3-bit flash. Each stage provides sufficient overlap to significantly reduces this effect at frequencies above 5 MHz. Care correct for flash errors in the preceding stages. The quantized should be taken to minimize noise impinging at the GAIN± outputs from each stage are combined into a 12-bit result in the input. An external RC filter can be used to remove V source GAIN digital correction logic. The pipelined architecture permits the noise. The filter bandwidth should be sufficient to accommodate first stage to operate on a new input sample and the remaining the desired control bandwidth. stages to operate on preceding samples. Sampling occurs on the Antialiasing Filter rising edge of the clock. The filter that the signal reaches prior to the ADC is used to Each stage of the pipeline except for the last consists of a low reject dc signals and to band limit the signal for antialiasing. resolution flash ADC connected to a switched-capacitor DAC Figure 53 shows the architecture of the filter. and interstage residue amplifier (for example, a multiplying 4kΩ digital-to-analog converter (MDAC)). The residue amplifier magnifies the difference between the reconstructed DAC output 1C* and the flash input for the next stage in the pipeline. One bit of 56pF/112pF redundancy is used in each stage to facilitate digital correction 2kΩ 2kΩ 2kΩ of flash errors. The last stage consists of a flash ADC. 7.5C* 6.5C* The output staging block aligns the data, carries out error cor- 2kΩ 2kΩ 2kΩ rection, and passes the data to the output buffers. The data is then serialized and aligned to the frame and output clock. 56pF/112pF 1C* *C = 0.5pF TO 3.1pF 4kΩ 06304-099 Figure 53. Simplified Filter Schematic Rev. B | Page 27 of 60

AD9271 CLOCK INPUT CONSIDERATIONS In some applications, it is acceptable to drive the sample clock inputs with a single-ended CMOS signal. In such applications, For optimum performance, the AD9271 sample clock inputs CLK+ should be driven directly from a CMOS gate, and the (CLK+ and CLK−) should be clocked with a differential signal. CLK− pin should be bypassed to ground with a 0.1 μF capacitor This signal is typically ac-coupled into the CLK+ and CLK− pins in parallel with a 39 kΩ resistor (see Figure 57). Although the via a transformer or capacitors. These pins are biased internally CLK+ input circuit supply is AVDD (1.8 V), this input is and require no additional bias. designed to withstand input voltages of up to 3.3 V, making the Figure 54 shows the preferred method for clocking the AD9271. selection of the drive logic voltage very flexible. A low jitter clock source, such as the Valpey Fisher oscillator 3.3V VFAC3-BHL-50MHz, is converted from single-ended to AD951x FAMILY differential using an RF transformer. The back-to-back Schottky VFAC3 0.1µF OUT CLK diodes across the secondary transformer limit clock excursions EN 50Ω* OP1T0IO0ΩNAL0.1µF into the AD9271 to approximately 0.8 V p-p differential. This CMOS DRIVER CLK+ ADC helps prevent the large voltage swings of the clock from feeding CLK AD9271 through to other portions of the AD9271, and it preserves the 0.1µF CLK– fast rise and fall times of the signal, which are critical to low 0.1µF 39kΩ jitter performance. *50Ω RESISTOR IS OPTIONAL. 06304-053 3.3V Figure 57. Single-Ended 1.8 V CMOS Sample Clock MINI-CIRCUITS ADT1-1WT, 1:1Z 3.3V 0.1µF XFMR 0.1µF AD951x FAMILY ENOUT CLK+ 0.1µF 50Ω 100Ω ADC OUT CLK VFAC3 0.1µF AD9271 EN 50Ω* OP1T0IO0ΩNAL 0.1µF CLK– CMOS DRIVER CLK+ 0.1µF SHCDSHIOMOD2TE8T1SK2:Y 06304-050 VFAC3 0.1µF CLK 0.1µF ADA9D2C71 If a low jitteFri gculorec 5k4 .i sT raavnasfiolarmbleer,- Caonuoptlheedr D oifpfetrieonnti aisl Ctloo cakc -couple a *50Ω RESISTOR IS OPTIONAL. CLK– 06304-054 Figure 58. Single-Ended 3.3 V CMOS Sample Clock differential PECL signal to the sample clock input pins as shown in Figure 55. The AD951x family of clock drivers offers excellent Clock Duty Cycle Considerations jitter performance. Typical high speed ADCs use both clock edges to generate a variety of internal timing signals. As a result, these ADCs may 3.3V 50Ω* AD951x FAMILY be sensitive to the clock duty cycle. Commonly, a 5% tolerance is VFAC3 0.1µF 0.1µF OUT CLK CLK+ required on the clock duty cycle to maintain dynamic performance EN ADC characteristics. The AD9271 contains a duty cycle stabilizer (DCS) 0.1µF PECL DRIVER 100.01ΩµF AD9271 that retimes the nonsampling edge, providing an internal clock CLK CLK– signal with a nominal 50% duty cycle. This allows a wide range 240Ω 240Ω of clock input duty cycles without affecting the performance of *50Ω RESISTOR IS OPTIONAL. 06304-051 the AD9271. When the DCS is on, noise and distortion perfor- Figure 55. Differential PECL Sample Clock mance are nearly flat for a wide range of duty cycles. However, some applications may require the DCS function to be off. If so, 3.3V keep in mind that the dynamic range performance can be affected 50Ω* AD951x FAMILY VFAC3 0.1µF 0.1µF when operated in this mode. See the Memory Map section for OUT CLK CLK+ more details on using this feature. EN ADC LVDS DRIVER 100Ω AD9271 The duty cycle stabilizer uses a delay-locked loop (DLL) to 0.1µF 0.1µF CLK CLK– create the nonsampling edge. As a result, any changes to the sampling frequency require approximately eight clock cycles *50Ω RESISTOR IS OPTIONAL. 06304-052 tCol oalclkow Ji tthteer D CLoLn tsoi daecqrautirieo nansd lock to the new rate. Figure 56. Differential LVDS Sample Clock High speed, high resolution ADCs are sensitive to the quality of the clock input. The degradation in SNR at a given input frequency (f ) A due only to aperture jitter (t) can be calculated by J SNR Degradation = 20 × log 10[1/2 × π × f × t] A J Rev. B | Page 28 of 60

AD9271 In this equation, the rms aperture jitter represents the root mean 190 square of all jitter sources, including the clock input, analog input 180 signal, and ADC aperture jitter. IF undersampling applications 170 are particularly sensitive to jitter (see Figure 59). W) 50MSPS SPEED GRADE m 160 The clock input should be treated as an analog signal in cases L ( E where aperture jitter may affect the dynamic range of the AD9271. NN 150 A Power supplies for clock drivers should be separated from the CH 140 R/ 40MSPS SPEED GRADE ADC output driver supplies to avoid modulating the clock signal E W 130 with digital noise. Low jitter, crystal-controlled oscillators make O P the best clock sources, such as the Valpey Fisher VFAC3 series. 120 25MSPS SPEED GRADE Idfi vthidei nclgo,c okr ios tgheenre mraetethdo fdros)m, i ta nshoothueldr tbyep ree otifm soedu rbcye t(hbey gating, 110100 06304-031 original clock during the last step. 0 10 20 30 40 50 SAMPLING FREQUENCY (MSPS) Refer to the AN-501 Application Note and the AN-756 Figure 61. Power per Channel vs. fSAMPLE for fIN = 7.5 MHz Application Note for more in-depth information about how By asserting the PDWN pin high, the AD9271 is placed into jitter performance relates to ADCs (visit www.analog.com). power-down mode. In this state, the device typically dissipates 130 RMS CLOCK JITTER REQUIREMENT 2 mW. During power-down, the LVDS output drivers are placed 120 into a high impedance state. The AD9271 returns to normal 110 operating mode when the PDWN pin is pulled low. This pin is 100 16 BITS both 1.8 V and 3.3 V tolerant. B) 90 14 BITS By asserting the STBY pin high, the AD9271 is placed into a SNR (d 7800 12 BITS s6t5a nmdWby. Dmuordine.g I nst athnidsb syt,a tthe,e t ehnet direev picaer tt yisp ipcoawllye rdeids sdipoawtens except 10 BITS the internal references. The LVDS output drivers are placed into 60 0.125ps a high impedance state. This mode is well suited for applications 8 BITS 50 0.25ps that require power savings because it allows the device to be 0.5ps 40 1.0ps powered down when not in use and then quickly powered up. 2.0ps 30 The time to power the device back up is also greatly reduced. The 1 ANALO1G0 INPUT FREQUENC10Y0 (MHz) 1000 06304-038 Ais Dpu92ll7e1d rleotwu.r Tnsh tios pnionr mis ablo otphe 1r.a8t iVng a mndo d3e.3 w Vh etonl ethraen St.T BY pin Figure 59. Ideal SNR vs. Input Frequency and Jitter Power Dissipation and Power-Down Mode In power-down mode, low power dissipation is achieved by shutting down the reference, reference buffer, PLL, and biasing As shown in Figure 61, the power dissipated by the AD9271 is networks. The decoupling capacitors on REFT and REFB are proportional to its sample rate. The digital power dissipation discharged when entering power-down mode and must be does not vary much because it is determined primarily by the recharged when returning to normal operation. As a result, the DRVDD supply and bias current of the LVDS output drivers wake-up time is related to the time spent in the power-down (Figure 60). mode: shorter cycles result in proportionally shorter wake-up 800 times. To restore the device to full operation, approximately 700 IAVDD, 50MSPS SPEED GRADE 1 ms is required when using the recommended 0.1 μF and 4.7 μF decoupling capacitors on the REFT and REFB pins and the 600 IAVDD, 40MSPS SPEED GRADE 0.01 μF decoupling capacitors on the GAIN± pins. Most of this A) 500 time is dependent on the gain decoupling; higher value decoupling T (m IAVDD, 25MSPS SPEED GRADE capacitors on the GAIN± pins result in longer wake-up times. N 400 E R There are a number of other power-down options available R CU 300 when using the SPI port interface. The user can individually power down each channel or put the entire device into standby 200 mode. This allows the user to keep the internal PLL powered up 1000 IDRVDD 3206304-0 wslihgehntl fya dste wpeankde-eunpt otinm geasi nar. eT ore aqcuhirieevde. Ta h1e μ ws awkaek-eu-pu pti mtime ies 0 10 20 30 40 50 when the device is in standby mode, 0.5 V must be applied to SAMPLING FREQUENCY (MSPS) the GAIN± pins. See the Memory Map section for more details Figure 60. Supply Current vs. fSAMPLE for fIN = 7.5 MHz on using these features. Rev. B | Page 29 of 60

AD9271 Digital Outputs and Timing Additional SPI options allow the user to further increase the internal termination (and therefore increase the current) of all The AD9271 differential outputs conform to the ANSI-644 LVDS eight outputs in order to drive longer trace lengths (see Figure 65). standard on default power-up. This can be changed to a low power, Even though this produces sharper rise and fall times on the reduced signal option similar to the IEEE 1596.3 standard by using data edges, is less prone to bit errors, and improves frequency the SDIO pin or via the SPI. This LVDS standard can further distribution (see Figure 65), the power dissipation of the DRVDD reduce the overall power dissipation of the device by approximately supply increases when this option is used. 36 mW. See the SDIO Pin section or Table 15 for more information. In cases that require increased driver strength to the DCO± and FCO± outputs because of load mismatch, Register 0x15 allows The LVDS driver current is derived on chip and sets the output the user to double the drive strength. To do this, first set the current at each output equal to a nominal 3.5 mA. A 100 Ω differ- appropriate bit in Register 0x05. Note that this feature cannot ential termination resistor placed at the LVDS receiver inputs be used with Bit 4 and Bit 5 in Register 0x15 because these bits results in a nominal 350 mV swing at the receiver. take precedence over this feature. See the Memory Map section The AD9271 LVDS outputs facilitate interfacing with LVDS for more details. receivers in custom ASICs and FPGAs that have LVDS capability 600 for superior switching performance in noisy environments. EYE: ALL BITS ULS: 2398/2398 Single point-to-point net topologies are recommended with a 400 100 Ω termination resistor placed as close to the receiver as possible. No far-end receiver termination and poor differential E (V) 200 G trace routing may result in timing errors. It is recommended TA 100 L that the trace length be no longer than 24 inches and that the VO M 0 differential output traces be kept close together and at equal A R lengths. An example of the FCO, DCO, and data stream with AG –100 DI proper trace length and position can be found in Figure 62. E Y –200 E –400 –600 –1.5ns –1.0ns –0.5ns 0ns 0.5ns 1.0ns 1.5ns 25 s) 20 Hit M ( A R 15 G O 06304-034 R HIST 10 CH1 500mV/DIV Ω 5.0ns/DIV E CH2 500mV/DIV Ω TT CH3 500mV/DIV Ω JI E Figure 62. LVDS Output Timing Example in ANSI-644 Mode (Default) TI 5 A(dne feaxualtm) dplaet ao ef ythe ea nLdV Da tSi moue tipnutet ruvsailn egr rthoer (ATNIES)I -ji6t4te4r shtiasntodgarradm 0 06304-035 –200ps –100ps 0ps 100ps 200ps with trace lengths of less than 24 inches on regular FR-4 material Figure 63. Data Eye for LVDS Outputs in ANSI-644 Mode with Trace Lengths is shown in Figure 63. Figure 64 shows an example of the trace of Less Than 24 Inches on Standard FR-4 lengths exceeding 24 inches on regular FR-4 material. Notice that the TIE jitter histogram reflects the decrease of the data eye opening as the edge deviates from the ideal position; therefore, the user must determine if the waveforms meet the timing budget of the design when the trace lengths exceed 24 inches. Rev. B | Page 30 of 60

AD9271 400 600 EYE: ALL BITS ULS: 2399/2399 EYE: ALL BITS ULS: 2396/2396 300 400 E (V) 200 E (V) AG AG 200 OLT 100 OLT V V M 0 M 0 A A R R G G A –100 A DI DI –200 E E EY –200 EY –400 –300 –400 –600 –1.5ns –1.0ns –0.5ns 0ns 0.5ns 1.0ns 1.5ns –1.5ns –1.0ns –0.5ns 0ns 0.5ns 1.0ns 1.5ns 25 25 Hits) 20 Hits) 20 M ( M ( A A R 15 R 15 G G O O ST ST HI HI R 10 R 10 E E E JITT E JITT TI 5 TI 5 0 06304-036 0 06304-037 –200ps –100ps 0ps 100ps 200ps –200ps –100ps 0ps 100ps 200ps Figure 64. Data Eye for LVDS Outputs in ANSI-644 Mode with Trace Lengths Figure 65. Data Eye for LVDS Outputs in ANSI-644 Mode with 100 Ω of Greater Than 24 Inches on Standard FR-4 Termination On and Trace Lengths of Greater Than 24 Inches on Standard FR-4 Rev. B | Page 31 of 60

AD9271 The format of the output data is offset binary by default. An times the sample clock rate, with a maximum of 600 Mbps example of the output coding format can be found in Table 9. (12 bits × 50 MSPS = 600 Mbps). The lowest typical conversion To change the output data format to twos complement, see the rate is 10 MSPS, but the PLL can be set up for encode rates as Memory Map section. low as 5 MSPS via the SPI if lower sample rates are required for a specific application. See the Memory Map section for details Table 9. Digital Output Coding on enabling this feature. (VIN+) − (VIN−), Digital Output Offset Binary Code Input Span = 2 V p-p (V) (D11 ... D0) Two output clocks are provided to assist in capturing data from the AD9271. DCO± is used to clock the output data and is equal 4095 +1.00 1111 1111 1111 to six times the sampling clock rate. Data is clocked out of the 2048 0.00 1000 0000 0000 AD9271 and must be captured on the rising and falling edges of 2047 −0.000488 0111 1111 1111 the DCO± that supports double data rate (DDR) capturing. The 0 −1.00 0000 0000 0000 frame clock output (FCO±) is used to signal the start of a new Data from each ADC is serialized and provided on a separate output byte and is equal to the sampling clock rate. See the channel. The data rate for each serial stream is equal to 12 bits timing diagram shown in Figure 2 for more information. Table 10. Flexible Output Test Modes Output Test Mode Subject to Data Bit Sequence Pattern Name Digital Output Word 1 Digital Output Word 2 Format Select 0000 Off (default) N/A N/A N/A 0001 Midscale short 1000 0000 (8 bits) Same Yes 10 0000 0000 (10 bits) 1000 0000 0000 (12 bits) 10 0000 0000 0000 (14 bits) 0010 +Full-scale short 1111 1111 (8 bits) Same Yes 11 1111 1111 (10 bits) 1111 1111 1111 (12 bits) 11 1111 1111 1111 (14 bits) 0011 −Full-scale short 0000 0000 (8 bits) Same Yes 00 0000 0000 (10 bits) 0000 0000 0000 (12 bits) 00 0000 0000 0000 (14 bits) 0100 Checkerboard 1010 1010 (8 bits) 0101 0101 (8 bits) No 10 1010 1010 (10 bits) 01 0101 0101 (10 bits) 1010 1010 1010 (12 bits) 0101 0101 0101 (12 bits) 10 1010 1010 1010 (14 bits) 01 0101 0101 0101 (14 bits) 0101 PN sequence long1 N/A N/A Yes 0110 PN sequence short1 N/A N/A Yes 0111 One-/zero-word toggle 1111 1111 (8 bits) 0000 0000 (8 bits) No 11 1111 1111 (10 bits) 00 0000 0000 (10 bits) 1111 1111 1111 (12 bits) 0000 0000 0000 (12 bits) 11 1111 1111 1111 (14 bits) 00 0000 0000 0000 (14 bits) 1000 User input Register 0x19 and Register 0x1A Register 0x1B and Register 0x1C No 1001 1-/0-bit toggle 1010 1010 (8 bits) N/A No 10 1010 1010 (10 bits) 1010 1010 1010 (12 bits) 10 1010 1010 1010 (14 bits) 1010 1× sync 0000 1111 (8 bits) N/A No 00 0001 1111 (10 bits) 0000 0011 1111 (12 bits) 00 0000 0111 1111 (14 bits) 1011 One bit high 1000 0000 (8 bits) N/A No 10 0000 0000 (10 bits) 1000 0000 0000 (12 bits) 10 0000 0000 0000 (14 bits) 1100 Mixed bit frequency 1010 0011 (8 bits) N/A No 10 0110 0011 (10 bits) 1010 0011 0011 (12 bits) 10 1000 0110 0111 (14 bits) 1 All test mode options except PN sequence short and PN sequence long can support 8- to 14-bit word lengths in order to verify data capture to the receiver. Rev. B | Page 32 of 60