ICGOO在线商城 > 集成电路(IC) > 线性 - 放大器 - 视频放大器和频缓冲器 > AD829JN

- 型号: AD829JN

- 制造商: Analog

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

AD829JN产品简介:

ICGOO电子元器件商城为您提供AD829JN由Analog设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 AD829JN价格参考¥30.72-¥64.44。AnalogAD829JN封装/规格:线性 - 放大器 - 视频放大器和频缓冲器, Video Amp, 1 Voltage Feedback 8-PDIP。您可以下载AD829JN参考资料、Datasheet数据手册功能说明书,资料中有AD829JN 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| -3db带宽 | 120MHz |

| 3dB带宽 | 120 MHz |

| 产品目录 | 集成电路 (IC)半导体 |

| 描述 | IC VIDEO OPAMP LN HS 8-DIP视频放大器 IC HIGH Speed Low Noise |

| 产品分类 | |

| 品牌 | Analog Devices Inc |

| 产品手册 | |

| 产品图片 |

|

| rohs | 否不符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 放大器 IC,视频放大器,Analog Devices AD829JN- |

| 数据手册 | |

| 产品型号 | AD829JN |

| Pd-功率耗散 | 1.3 W |

| 产品 | Video Amplifiers |

| 产品种类 | 视频放大器 |

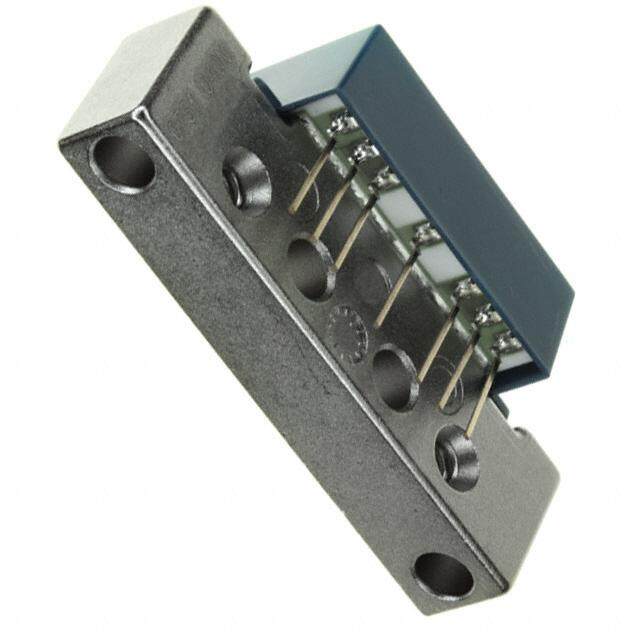

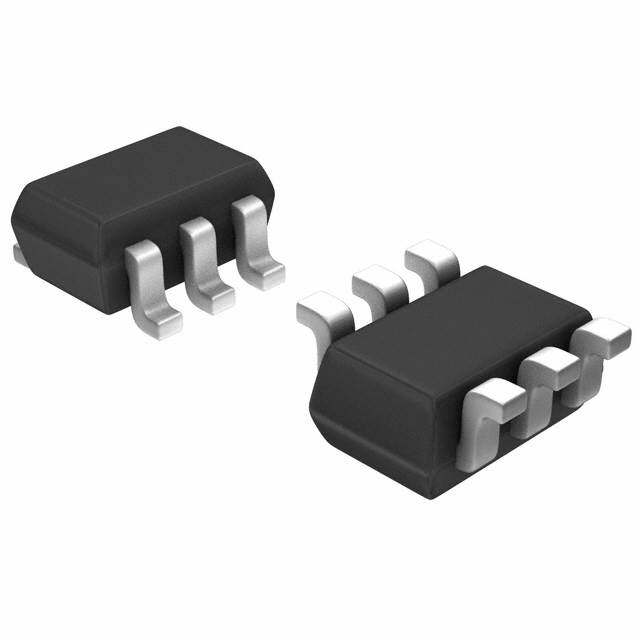

| 供应商器件封装 | 8-PDIP |

| 关闭 | No Shutdown |

| 包装 | 管件 |

| 压摆率 | 230 V/µs |

| 商标 | Analog Devices |

| 安装类型 | 通孔 |

| 安装风格 | Through Hole |

| 封装 | Tube |

| 封装/外壳 | 8-DIP(0.300",7.62mm) |

| 封装/箱体 | PDIP-8 |

| 工作温度范围 | 0 C to + 70 C |

| 工作电源电压 | 9 V to 36 V |

| 工厂包装数量 | 50 |

| 带宽 | 120 MHz |

| 应用 | 电压反馈 |

| 技术 | BiCOM |

| 放大器类型 | General Purpose Amplifier |

| 最大功率耗散 | 1.3 W |

| 最大双重电源电压 | +/- 18 V |

| 最大工作温度 | + 70 C |

| 最小双重电源电压 | +/- 4.5 V |

| 最小工作温度 | 0 C |

| 标准包装 | 50 |

| 电压-电源,单/双 (±) | ±4.5 V ~ 18 V |

| 电流-电源 | 5.3mA |

| 电流-输出/通道 | 32mA |

| 电源电压-最大 | 36 V |

| 电源电压-最小 | 9 V |

| 电源电流 | 5 mA |

| 电源类型 | Dual |

| 电路数 | 1 |

| 系列 | AD829 |

| 输入类型 | No |

| 输出类型 | - |

| 通道数量 | 1 Channel |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

High Speed, Low Noise Video Op Amp Data Sheet AD829 FEATURES CONNECTION DIAGRAM High speed OFFSET NULL 1 AD829 8 OFFSET NULL 120 MHz bandwidth, gain = −1 –IN 2 7 +VS 230 V/µs slew rate +IN 3 6 OUTPUT Ide9a0l nfosr s veitdtleinog a ptipmliec atoti o0n.1s% –VS 4 (NToOt Pto V SIEcaWle) 5 CCOMP 00880-001 0.02% differential gain Figure 1. 8-Lead PDIP (N), CERDIP (Q), and SOIC (R) 0.04° differential phase ET ET SL SL Low noise CFFULCFFULC NONNONN 1.7 nV/√Hz input voltage noise 3 2 1 20 19 1.5 pA/√Hz input current noise NC4 18NC Excellent dc precision –IN5 AD829 17+V NC6 TOP VIEW 16NC 1 mV maximum input offset voltage (over temperature) +IN7 (Not to Scale) 15OUTPUT 0.3 µV/°C input offset drift NC8 14NC Flexible operation 9 10 11 12 13 S±p3e Vc iofuietdp ufot rs ±w5in Vg t ion ±to1 5a V15 o0p Ωer laotaiodn NC = NO CONNCNE–VCTNCCCOMP NC 00880-002 Figure 2. 20-Terminal LCC External compensation for gains 1 to 20 5 mA supply current Operating as a traditional voltage feedback amplifier, the AD829 Available in tape and reel in accordance with EIA-481A standard provides many of the advantages that a transimpedance amplifier offer. A bandwidth >50 MHz can be maintained for a range of GENERAL DESCRIPTION gains through the replacement of the external compensation The(cid:1)(cid:34)(cid:37)(cid:25)(cid:19)(cid:26) is a low noise (1.7 nV/√Hz), high speed op amp with capacitor. The AD829 and the transimpedance amplifier are both custom compensation that provides the user with gains of 1 to 20 unity-gain stable and provide similar voltage noise performance while maintaining a bandwidth >50 MHz. Its 0.04° differential (1.7 nV/√Hz); however, the current noise of the AD829 phase and 0.02% differential gain performance at 3.58 MHz and (1.5 pA/√Hz) is less than 10% of the noise of transimpedance 4.43 MHz, driving reverse-terminated 50 Ω or 75 Ω cables, makes amplifiers. The inputs of the AD829 are symmetrical. it ideally suited for professional video applications. The AD829 PRODUCT HIGHLIGHTS achieves its 230 V/µs uncompensated slew rate and 750 MHz gain bandwidth while requiring only 5 mA of current from 1. The input voltage noise of 2 nV/√Hz, current noise of power supplies. 1.5 pA/√Hz, and 50 MHz bandwidth for gains of 1 to 20 make the AD829 an ideal preamp. The external compensation pin of the AD829 gives it 2. A differential phase error of 0.04 and a 0.02% differential exceptional versatility. For example, compensation can be gain error, at the 3.58 MHz NTSC, 4.43 MHz PAL, and selected to optimize the bandwidth for a given load and power SECAM color subcarrier frequencies, make the op amp an supply voltage. As a gain-of-2 line driver, the −3 dB bandwidth outstanding video performer for driving reverse-terminated can be increased to 95 MHz at the expense of 1 dB of peaking. 50 Ω and 75 Ω cables to ±1 V (at their terminated end). Its output can also be clamped at its external compensation pin. 3. The AD829 can drive heavy capacitive loads. The AD829 exhibits excellent dc performance. It offers a minimum 4. Performance is fully specified for operation from ±5 V open-loop gain of 30 V/mV into loads as low as 500 Ω, a low input to ±15 V supplies. voltage noise of 1.7 nV/√Hz, and a low input offset voltage of 1 mV 5. The AD829 is available in PDIP, CERDIP, and small outline maximum. Common-mode rejection and power supply rejection packages. Chips and MIL-STD-883B parts are also available. ratios are both 120 dB. The 8-lead SOIC is available for the extended temperature This op amp is also useful in multichannel, high speed data range (−40°C to +125°C). conversion where its fast (90 ns to 0.1%) settling time is important. In such applications, the AD829 serves as an input buffer for 8-bit to 10-bit ADCs and as an output I/V converter for high speed DACs. Rev. I Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Tel: 781.329.4700 www.analog.com Trademarks and registered trademarks are the property of their respective owners. Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

AD829 Data Sheet TABLE OF CONTENTS Features .............................................................................................. 1 Test Circuits ..................................................................................... 11 General Description ......................................................................... 1 Theory of Operation ...................................................................... 12 Connection Diagram ....................................................................... 1 Externally Compensating the AD829 ...................................... 12 Product Highlights ........................................................................... 1 Shunt Compensation ................................................................. 12 Revision History ............................................................................... 2 Current Feedback Compensation ............................................ 13 Specifications ..................................................................................... 3 Low Error Video Line Driver ................................................... 15 Absolute Maximum Ratings ............................................................ 5 High Gain Video Bandwidth, 3-Op-Amp Instrumentation Thermal Characteristics .............................................................. 5 Amplifier ..................................................................................... 16 Metallization Photo ...................................................................... 5 Outline Dimensions ....................................................................... 17 ESD Caution .................................................................................. 5 Ordering Guide .......................................................................... 19 Typical Performance Characteristics ............................................. 6 REVISION HISTORY 10/11—Rev. H to Rev. I 2/03—Rev. E to Rev. F Change to Table 2 ............................................................................. 5 Renumbered Figures ......................................................... Universal Changes to Product Highlights ....................................................... 1 4 /09—Rev. G to Rev. H Changes to Specifications ................................................................. 2 C hanges to Features .......................................................................... 1 Changes to Absolute Maximum Ratings ........................................ 4 C hanges to Quiescent Current Parameter, Table 1 ...................... 4 Changes to Ordering Guide ............................................................. 4 C hanges to Table 2 ............................................................................ 5 Updated Outline Dimensions ....................................................... 13 A dded Thermal Characteristics Section and Table 3 .................. 5 U pdated Outline Dimensions ....................................................... 17 C hanges to Ordering Guide .......................................................... 19 4 /04—Rev. F to Rev. G Added Figure 1; Renumbered Sequentially .................................. 4 C hanges to Ordering Guide ............................................................ 5 U pdated Table I ............................................................................... 11 U pdated Figure 15 .......................................................................... 12 U pdated Figure 16 .......................................................................... 13 U pdated Outline Dimensions ....................................................... 14 Rev. I | Page 2 of 20

Data Sheet AD829 SPECIFICATIONS T = 25°C and V = ±15 V dc, unless otherwise noted. A S Table 1. AD829JR AD829AR AD829AQ/AD829S Parameter Conditions V Min Typ Max Min Typ Max Min Typ Max Unit S INPUT OFFSET VOLTAGE tMIN to tMAX ±5 V, 0.2 1 0.2 1 0.1 0.5 mV ±15 V 1 1 0.5 mV Offset Voltage Drift ±5 V, 0.3 0.3 0.3 µV/°C ±15 V INPUT BIAS CURRENT ±5 V, 3.3 7 3.3 7 3.3 7 µA ±15 V t to t 8.2 9.5 9.5 µA MIN MAX INPUT OFFSET CURRENT ±5 V, 50 500 50 500 50 500 nA ±15 V t to t 500 500 500 nA MIN MAX Offset Current Drift ± 5 V, 0.5 0.5 0.5 nA/°C ±15 V OPEN-LOOP GAIN V = ±2.5 V, ±5 V 30 65 30 65 30 65 V/mV O R = 500 Ω L R = 150 Ω 40 40 40 V/mV L t to t 20 20 20 V/mV MIN MAX V = ±10 V, ±15 V 50 100 50 100 50 100 V/mV O R = 1 kΩ L R = 500 Ω 85 85 85 V/mV L t to t 20 20 20 V/mV MIN MAX DYNAMIC PERFORMANCE Gain Bandwidth Product ±5 V 600 600 600 MHz ±15 V 750 750 750 MHz Full Power Bandwidth1, 2 V = 2 V p-p, ±5 V 25 25 25 MHz O R = 500 Ω L V = 20 V p-p, ±15 V 3.6 3.6 3.6 MHz O R = 1 kΩ L Slew Rate2 R = 500 Ω ±5 V 150 150 150 V/µs L R = 1 kΩ ±15 V 230 230 230 V/µs L Settling Time to 0.1% A = –19 V −2.5 V to ±5 V 65 65 65 ns +2.5 V 10 V step ±15 V 90 90 90 ns Phase Margin2 C = 10 pF ±15 V L R = 1 kΩ 60 60 60 Degrees L DIFFERENTIAL GAIN ERROR3 R = 100 Ω, ±15 V 0.02 0.02 0.02 % L C = 30 pF COMP DIFFERENTIAL PHASE ERROR3 R = 100 Ω, ±15 V 0.04 0.04 0.04 Degrees L C = 30 pF COMP COMMON-MODE REJECTION V = ±2.5 V ±5 V 100 120 100 120 100 120 dB CM V = ±12 V ±15 V 100 120 100 120 100 120 dB CM t to t 96 96 96 dB MIN MAX POWER SUPPLY REJECTION V = ±4.5 V 98 120 98 120 98 120 dB S to ±18 V t to t 94 94 94 dB MIN MAX INPUT VOLTAGE NOISE f = 1 kHz ±15 V 1.7 2 1.7 2 1.7 2 nV/√Hz INPUT CURRENT NOISE f = 1 kHz ±15 V 1.5 1.5 1.5 pA/√Hz Rev. I | Page 3 of 20

AD829 Data Sheet AD829JR AD829AR AD829AQ/AD829S Parameter Conditions V Min Typ Max Min Typ Max Min Typ Max Unit S INPUT COMMON-MODE ±5 V +4.3 +4.3 +4.3 V VOLTAGE RANGE −3.8 −3.8 −3.8 V ±15 V +14.3 +14.3 +14.3 V −13.8 −13.8 −13.8 V OUTPUT VOLTAGE SWING R = 500 Ω ±5 V ±3.0 ±3.6 ±3.0 ±3.6 ±3.0 ±3.6 V L R = 150 Ω ±5 V ±2.5 ±3.0 ±2.5 ±3.0 ±2.5 ±3.0 V L R = 50 Ω ±5 V ±1.4 ±1.4 ±1.4 V L R = 1 kΩ ±15 V ±12 ±13.3 ±12 ±13.3 ±12 ±13.3 V L R = 500 Ω ±15 V ±10 ±12.2 ±10 ±12.2 ±10 ±12.2 V L Short-Circuit Current ±5 V, 32 32 32 mA ±15 V INPUT CHARACTERISTICS Input Resistance 13 13 13 kΩ (Differential) Input Capacitance 5 5 5 pF (Differential)4 Input Capacitance 1.5 1.5 1.5 pF (Common Mode) CLOSED-LOOP OUTPUT A = +1, 2 2 2 mΩ V RESISTANCE f = 1 kHz POWER SUPPLY Operating Range ±4.5 ±18 ±4.5 ±18 ±4.5 ±18 V Quiescent Current ±5 V 5 6.5 5 6.5 5 6.5 mA t to t 8.0 8.0 8.7 mA MIN MAX ±15 V 5.3 6.8 5.3 6.8 5.3 6.8 mA t to t 8.3 9.0 9.0 mA MIN MAX TRANSISTOR COUNT Number of 46 46 46 transistors 1 Full power bandwidth = slew rate/2 π VPEAK. 2 Tested at gain = 20, CCOMP = 0 pF. 3 3.58 MHz (NTSC) and 4.43 MHz (PAL and SECAM). 4 Differential input capacitance consists of 1.5 pF package capacitance plus 3.5 pF from the input differential pair. Rev. I | Page 4 of 20

Data Sheet AD829 ABSOLUTE MAXIMUM RATINGS METALLIZATION PHOTO Table 2. Parameter Rating OFFSET NULL OFFSET NULL 1 8 +VS Supply Voltage ±18 V 7 Internal Power Dissipation1 8-Lead PDIP (N) 1.3 W 8-Lead SOIC (R) 0.9 W –IN 2 8-Lead CERDIP (Q) 1.3 W OUTPUT 6 20-Terminal LCC (E) 0.8 W Differential Input Voltage2 ±6 V (01..03574) Output Short-Circuit Duration Indefinite CCOMP 5 Storage Temperature Range +IN 8-Lead CERDIP (Q) and 20-Terminal LCC (E) −65°C to +150°C 3 –VS 8-Lead PDIP (N) and 8-Lead SOIC (R) −65°C to +125°C 4 Operating Temperature Range AADD882299JA −0°4C0 °tCo 7to0 °+C1 25°C SUBSTRATE CONNEC0T.0E6D7 T(1O.7 +0)VS 00880-003 AD829S −55°C to +125°C Figure 3. Metallization Photo; Contact Factory for Latest Dimensions, Lead Temperature (Soldering, 60 sec) 300°C Dimensions Shown in Inches and (Millimeters) 2.5 1 Maximum internal power dissipation is specified so that TJ does not exceed 150°C at an ambient temperature of 25°C. 2 If the differential voltage exceeds 6 V, external series protection resistors W) should be added to limit the input current. N ( 2.0 PDIP O LCC TI Stresses above those listed under Absolute Maximum Ratings A P may cause permanent damage to the device. This is a stress SSI 1.5 DI rating only; functional operation of the device at these or any R E other conditions above those indicated in the operational W O 1.0 CERDIP P section of this specification is not implied. Exposure to absolute M U mdeavxicime ruemlia rbaitliintyg. conditions for extended periods may affect MAXIM 0.5 SOIC THERMAL CHARACTERISTICS 0 00880-004 –55–45–35–25–15 –5 5 15 25 35 45 55 65 75 85 95 105115125 Table 3. AMBIENT TEMPERATURE (°C) Package Type θJA Unit Figure 4. Maximum Power Dissipation vs. Temperature 8-Lead PDIP (N) 100 (derates at 8.7 mW/°C) °C/W 8-Lead CERDIP (Q) 110 (derates at 8.7 mW/°C) °C/W ESD CAUTION 20-Lead LCC (E) 77 °C/W 8-Lead SOIC (R) 125 (derates at 6 mW/°C) °C/W Rev. I | Page 5 of 20

AD829 Data Sheet TYPICAL PERFORMANCE CHARACTERISTICS 20 6.0 V) E RANGE ( 15 +VOUT ENT (mA) 5.5 D R O R MMON-M 10 –VOUT CENT CU 5.0 O S C E UT 5 QUI 4.5 P N I 0 00880-005 4.0 00880-008 0 5 10 15 20 0 5 10 15 20 SUPPLY VOLTAGE (±V) SUPPLY VOLTAGE (±V) Figure 5. Input Common-Mode Range vs. Supply Voltage Figure 8. Quiescent Current vs. Supply Voltage 20 –5 V) E ( G A UTPUT VOLT 15 +VOUT µRRENT (A) –4 F THE O 10 –VOUT BIAS CU VS =±5V,±15V UDE O 5 NPUT –3 T I NI G MA 0 RL = 1kΩ 00880-006 –2 00880-009 0 5 10 15 20 –60 –40 –20 0 20 40 60 80 100 120 140 SUPPLY VOLTAGE (±V) TEMPERATURE (°C) Figure 6. Output Voltage Swing vs. Supply Voltage Figure 9. Input Bias Current vs. Temperature 30 100 Ω) WING (V p-p) 2250 ±S1U5PVPLIES MPEDANCE ( 10 ACVC O=M 2P0 = 0pF E S UT I 1 G 15 P A T T U L O TPUT VO 10 D-LOOP 0.1 ACVC O=M 1P = 68pF U E O 05 ±S5UVPPLIES 00880-007 CLOS0.00.0011 00880-010 10 100 1k 10k 1k 10k 100k 1M 10M 100M LOAD RESISTANCE (Ω) FREQUENCY (Hz) Figure 7. Output Voltage Swing vs. Resistive Load Figure 10. Closed-Loop Output Impedance vs. Frequency Rev. I | Page 6 of 20

Data Sheet AD829 7 120 100 PHASE 100 80 QUIESCENT CURRENT (mA) 654 VS =±15VVS =±5V OPEN-LOOP GAIN (dB) 864000 G±S550UAV0PIΩNP LLOIEASD G±S11kUA5ΩPIVN PLLOIAEDS 642000 PHASE (Degrees) 20 0 3 00880-011 0 CCOMP = 0pF –20 00880-014 –60 –40 –20 0 20 40 60 80 100 120 140 100 1k 10k 100k 1M 10M 100M TEMPERATURE (°C) FREQUENCY (Hz) Figure 11. Quiescent Current vs. Temperature Figure 14. Open-Loop Gain and Phase vs. Frequency 40 105 NEGATIVE A) CURRENT LIMIT m 100 CURRENT LIMIT ( 3305 CURPROESNITTI VLEIMIT OP GAIN (dB) 9905 VS =±15V VS =±5V CIRCUIT 25 OPEN-LO 85 T- R O 20 H 80 S 15 VS = ±5V 00880-012 75 00880-015 –60 –40 –20 0 20 40 60 80 100 120 140 10 100 1k 10k AMBIENT TEMPERATURE (°C) LOAD RESISTANCE (Ω) Figure 12. Short-Circuit Current Limit vs. Ambient Temperature Figure 15. Open-Loop Gain vs. Resistive Load 65 120 VS = ±15V AV = +20 +SUPPLY CCOMP = 0pF 100 MHz) 60 –SUPPLY TH ( B) 80 D d WI 55 R ( D R N S BA P 60 B d 3 – 50 40 45 00880-013 20 CCOMP = 0pF 00880-016 –60 –40 –20 0 20 40 60 80 100 120 140 1k 10k 100k 1M 10M 100M TEMPERATURE (°C) FREQUENCY (Hz) Figure 13. –3 dB Bandwidth vs. Temperature Figure 16. Power Supply Rejection Ratio (PSRR) vs. Frequency Rev. I | Page 7 of 20

AD829 Data Sheet 120 –70 VIN = 3V RMS –75 AV = –1 100 –80 CCCL O=M 1P0 0=p 3F0pF –85 CMRR (dB) 6800 THD (dB) ––9950 RL = 500Ω –100 40 RL = 2kΩ 20 CCOMP = 0pF 00880-017 ––111005 00880-020 1k 10k 100k 1M 10M 100M 100 300 1k 3k 10k 30k 100k FREQUENCY (Hz) FREQUENCY (Hz) Figure 17. Common-Mode Rejection Ratio (CMRR) vs. Frequency Figure 20. Total Harmonic Distortion (THD) vs. Frequency 30 –20 p-p) 25 RVCASLVC O===M ±1+P1k2 5Ω=0V 0pF –30 VRACCIVLLCN O ====M 20–2P5p1. 02=FΩ5 3V0 pRFMS THIRD HARMONIC V 20 T VOLTAGE ( 15 RVSL == ±550V0Ω THD (dB) ––4500 UTPU 10 CAVC O=M +P2 =0 0pF SECOND HARMONIC O –60 5 0 00880-018 –70 00880-021 1 10 100 0 500k 1.0M 1.5M 2.0M INPUT FREQUENCY (MHz) FREQUENCY (Hz) Figure 18. Large Signal Frequency Response Figure 21. Second and Third THD vs. Frequency 10 5 8 V 6 Hz) 4 ±O V/ SWING FROM 0 T –2024 11%% 00..11%% EACRVC OR=MO–PR1 =9 0pF LTAGE NOISE (n 32 PUT –4 T VO T U U P O –6 IN 1 –1–08 00880-019 0 00880-022 0 20 40 60 80 100 120 140 160 10 100 1k 10k 100k 1M 10M SETTLING TIME (ns) FREQUENCY (Hz) Figure 19. Output Swing and Error vs. Settling Time Figure 22. Input Voltage Noise Spectral Density Rev. I | Page 8 of 20

Data Sheet AD829 400 AV = +20 20mV 20ns SLEW RATE 10%TO 90% 350 100% 90 s) 300 RISE µ V/ E ( VS = ±15V FALL AT 250 R W E RISE L S 200 FALL 10 150 0% 100 VS = ±5V 00880-023 00880-028 –60 –40 –20 0 20 40 60 80 100 120 140 TEMPERATURE (°C) Figure 23. Slew Rate vs. Temperature Figure 26. Gain-of-2 Follower Small Signal Pulse Response (See Figure 32) 0.03 2V 50ns es) 0.02 100% gre %) 90 E (De DIFFERENTIAL GAIN 0.01 AIN ( S G TIAL PHA 0.043° RENTIAL N E E0.05 F R F FFE DIFFERENTIAL PHASE DI 10 DI0.04 0% 0.03 00880-024 00880-030 ±5 ±10 ±15 SUPPLY VOLTAGE (V) Figure 24. Differential Phase and Gain vs. Supply Voltage Figure 27. Gain-of-20 Follower Large Signal Pulse Response (See Figure 33) 200mV 50ns 50mV 20ns 100% 90 90 10 10 0% 0% 00880-027 00880-031 Figure 25. Gain-to-2 Follower Large Signal Pulse Response (See Figure 32) Figure 28. Gain-of-20 Follower Small Signal Pulse Response (See Figure 33) Rev. I | Page 9 of 20

AD829 Data Sheet 200mV 50ns 20mV 20ns 100% 100% 90 90 10 10 0% 0% 00880-033 00880-034 Figure 29. Unity-Gain Inverter Large Signal Pulse Response (See Figure 34) Figure 30. Unity-Gain Inverter Small Signal Pulse Response (See Figure 34) Rev. I | Page 10 of 20

Data Sheet AD829 TEST CIRCUITS CCOMP (EXTERNAL) +VS 5 0.1µF 2 – 7 AD829 6 4 3 + 8 1 0.1µF Ω k 0 2 AONDFUFJUSLELSTT –VS 00880-025 Figure 31. Offset Null and External Shunt Compensation Connections +15V CCOMP 0.1µF 15pF 50Ω CABLE 7 5nsH RP8IS1E30 TAIME 3 + 5 50Ω CA50BΩLE TEKTRONIX 50Ω AD829 6 TPYRPEEA M7AP24 2 – 50Ω 4 5pF 300kΩ 0.1µF –15V 300kΩ 00880-026 Figure 32. Follower Connection, Gain = 2 +15V 50Ω 0.1µF CABLE 45Ω 100Ω HP8130A 2 – 7 FET 5ns RISE TIME PROBE 5Ω AD829 6 TEKTRONIX TYPE 7A24 3 + PREAMP 4 1pF 2kΩ 0.1µF –15V CCOMP = 0pF 105kΩ 00880-029 Figure 33. Follower Connection, Gain = 20 5pF 300Ω +15V 50Ω CABLE 300Ω 0.1µF 5nsH RP8IS1E30 TAIME 2 – 7 50Ω CA50BΩLE TEKTRONIX 50Ω AD829 6 TPYRPEEA M7AP24 3 + 5 CCOMP 50Ω 4 15pF –15V 0.1µF 00880-032 Figure 34. Unity-Gain Inverter Connection Rev. I | Page 11 of 20

AD829 Data Sheet THEORY OF OPERATION The AD829 is fabricated on the Analog Devices, Inc., proprietary An RC network in the output stage (see Figure 35) completely complementary bipolar (CB) process, which provides PNP and removes the effect of capacitive loading when the amplifier NPN transistors with similar f s of 600 MHz. As shown in compensates for closed-loop gains of 10 or higher. At low T Figure 35, the AD829 input stage consists of an NPN differential frequencies, and with low capacitive loads, the gain from the pair in which each transistor operates at a 600 µA collector current. compensation node to the output is very close to unity. In this case, This gives the input devices a high transconductance, which in C is bootstrapped and does not contribute to the compensation turn gives the AD829 a low noise figure of 2 nV/√Hz at 1 kHz. capacitance of the device. As the capacitive load increases, a pole forms with the output impedance of the output stage, which +VS reduces the gain, and subsequently, C is incompletely bootstrapped. Therefore, some fraction of C contributes to the compensation capacitance, and the unity-gain bandwidth falls. 15Ω As the load capacitance is further increased, the bandwidth OUTPUT C R continues to fall, and the amplifier remains stable. 12.5pF 500Ω 15Ω EXTERNALLY COMPENSATING THE AD829 +IN –IN The AD829 is stable with no external compensation for noise 1.2mA gains greater than 20. For lower gains, two different methods of frequency compensating the amplifier can be used to achieve –VS closed-loop stability: shunt and current feedback compensation. OFFSET NULL CCOMP 00880-035 SHUNT COMPENSATION Figure 35. Simplified Schematic Figure 36 and Figure 37 show that shunt compensation has an external compensation capacitor, C , connected between the The input stage drives a folded cascode that consists of a fast pair of COMP compensation pin and ground. This external capacitor is tied in PNP transistors. These PNPs drive a current mirror that provides a parallel with approximately 3 pF of internal capacitance at the differential-input-to-single-ended-output conversion. The high compensation node. In addition, a small capacitance, C , in speed PNPs are also used in the current-amplifying output stage, LEAD parallel with resistor R2, compensates for the capacitance at the which provides a high current gain of 40,000. Even under heavy inverting input of the amplifier. loading conditions, the high f s of the NPN and PNPs, produced T using the CB process, permit cascading two stages of emitter CLEAD followers while maintaining 60 phase margin at closed-loop R2 bandwidths greater than 50 MHz. 50Ω +VS COAX Two stages of complementary emitter followers also effectively CABLE R1 0.1µF VIN 2 – 7 buffer the high impedance compensation node (at the CCOMP pin) 50Ω AD829 6 VOUT from the output so that the AD829 can maintain a high dc open- 3 + 4 5 CCOMP 1kΩ loop gain, even into low load impedances (92 dB into a 150 Ω 0.1µF lboiaasdi nagn de n1s0u0r ed Blo win toof fas e1t kvΩol tlaogaed a).n Lda lsoewr torfimfsemt ivnoglt aanged dPrTifAt,T –VS 00880-036 Figure 36. Inverting Amplifier Connection Using External Shunt enabling the user to eliminate ac coupling in many applications. Compensation For added flexibility, the AD829 provides access to the internal +VS frequency compensation node. This allows users to customize the CA50BΩLE 0.1µF frequency response characteristics for a particular application. VIN 3 + 7 50Ω AD829 6 VOUT Unity-gain stability requires a compensation capacitance of 68 pF 2 – 5 R2 1kΩ (Pin 5 to ground), which yields a small signal bandwidth of 4 CCOMP 66 MHz and slew rate of 16 V/µs. The slew rate and gain 0.1µF CLEAD bandwidth product varies inversely with compensation –VS ccoapmapceitnasnactieo. nT acbaplea 4ci taanndc eF iagnudr et h3e7 rsehsouwlt itnhge solpetwim ruatme for R1 00880-037 Figure 37. Noninverting Amplifier Connection Using External Shunt a desired noise gain. Compensation For gains between 1 and 20, choose CCOMP to keep the small signal Table 4 gives the recommended CCOMP and CLEAD values, as well bandwidth relatively constant. The minimum gain that will still as the corresponding slew rates and bandwidth. The capacitor provide stability depends on the value of the external values were selected to provide a small signal frequency response compensation capacitance. with <1 dB of peaking and <10% overshoot. For Table 4, ±15 V Rev. I | Page 12 of 20

Data Sheet AD829 supply voltages should be used. Figure 38 is a graphical extension C is the compensation capacitance. COMP of Table 4, which shows the slew rate/gain trade-off for lower r is the inverse of the transconductance of the input transistors. e closed-loop gains, when using the shunt compensation scheme. kT/q approximately equals 26 mV at 27°C. 100 1k Because both f and slew rate are functions of the same variables, T the dynamic behavior of an amplifier is limited. Because 2I SlewRate= CCOMP SLEW RATE C s) COMP µ (pF)MP 10 100 ATE (V/ then O R SlewRate kT CC W =4π E L f q S T This shows that the slew rate is only 0.314 V/µs for every mega- 1 VS =±15V 10 00880-038 ihUnencrrfteoza rostfeu bnthaanete dflTwy, ,ia danntdh a.t mhTahpte li isof indeilryf f wiwciuathylt tbao e bicnaancurdseewa osiedf ptthhreo o csfel e1sws0 l irMmatHiet aizst i ctooann s . 1 10 100 NOISE GAIN only slew at 3.1 V/µs, which is barely enough to provide a full Figure 38. Value of CCOMP and Slew Rate vs. Noise Gain power bandwidth of 50 kHz. CURRENT FEEDBACK COMPENSATION The AD829 is especially suited to a form of current feedback Bipolar, nondegenerated, single-pole, and internally compensation that allows for the enhancement of both the full compensated amplifiers have their bandwidths defined as power bandwidth and the slew rate of the amplifier. The voltage gain from the inverting input pin to the compensation pin is 1 I f = = large; therefore, if a capacitance is inserted between these pins, T 2πr C kT e COMP 2π C the bandwidth of the amplifier becomes a function of its feed- q COMP back resistor and the capacitance. The slew rate of the amplifier where: is now a function of its internal bias (2I) and the compensation f is the unity-gain bandwidth of the amplifier. capacitance. T I is the collector current of the input transistor. Table 4. Component Selection for Shunt Compensation Follower Gain Inverter Gain R1 (Ω) R2 (Ω) C (pF) C (pF) Slew Rate (V/µs) −3 dB Small Signal Bandwidth (MHz) LEAD COMP 1 Open 100 0 68 16 66 2 −1 1 k 1 k 5 25 38 71 5 −4 511 2.0 k 1 7 90 76 10 −9 226 2.05 k 0 3 130 65 20 −19 105 2 k 0 0 230 55 25 −24 105 2.49 0 0 230 39 100 −99 20 2 k 0 0 230 7.5 Rev. I | Page 13 of 20

AD829 Data Sheet Because the closed-loop bandwidth is a function of R and Figure 42 is an oscilloscope photo of the pulse response of a unity- F C (see Figure 39), it is independent of the amplifier closed- gain inverter that has been configured to provide a small signal COMP loop gain, as shown in Figure 41. To preserve stability, the time bandwidth of 53 MHz and a subsequent slew rate of 180 V/µs; constant of R and C needs to provide a bandwidth of R = 3 kΩ and C = 1 pF. Figure 43 shows the excellent pulse F COMP F COMP <65 MHz. For example, with C = 15 pF and R = 1 kΩ, the response as a unity-gain inverter, this using component values COMP F small signal bandwidth of the AD829 is 10 MHz. Figure 40 of RF = 1 kΩ and CCOMP = 4 pF. shows that the slew rate is in excess of 60 V/µs. As shown in Figure 41, the closed-loop bandwidth is constant for gains of 5V 200ns −1 to −4; this is a property of the current feedback amplifiers. 100% 90 RF CCOMP 0.1µF +VS 50Ω COAX CABLE R1 7 VIN 2 – 5 C1* AD829 6 VOUT 50Ω IN4148 3 + 4 R1kLΩ 01%0 *RECOMMENDED VALUE CCOMP SHOULD N–EVVSER E0X.1CµEFED 00880-042 O<≥77Fpp CFFCOMP F01p5OpFRF C1 15pF FOR THIS CONNECTION 00880-039 FiCguurrere 4n2t. F Leaerdgbea Scigk nCaolm Puplesnes Raetsiopno,n CsCeO oMfP t=h e1 IpnFv,e RrFt i=n g3 AkΩm,p Rli1fi =er 3 U ksΩin g Figure 39. Inverting Amplifier Connection Using Current Feedback Compensation 10ns 100% 5V 200ns 90 100% 90 10 0% 01%0 20mV 00880-043 00880-040 Figure 43F.e Semdbaallc Ski gCnoaml pPeunlssea Rtieosnp, oCnCsOeM Po =f I 4n vpeFr,t RinFg = A 1m kpΩl,i fRie1d = U 1s iknΩg Current Figure 40. Large Signal Pulse Response of Inverting Amplifier Using Current Feedback Compensation, CCOMP = 15 pF, C1 = 15 pF RF = 1 kΩ, R1 = 1 kΩ 15 GAIN =–4 12 –3dB @ 8.2MHz 9 B) GAIN =–2 d 6 N ( –3dB @ 9.6MHz GAI 3 P GAIN =–1 O 0 O –3dB @ 10.2MHz L D- –3 E S CLO –6 VVISN ==±–1350VdBm –9 RL = 1kΩ ––1152 RCCFC1 O==M 11Pk5 Ω=p F15pF 00880-041 100k 1M 10M 100M FREQUENCY (Hz) Figure 41. Closed-Loop Gain vs. Frequency for the Circuit of Figure 38 Rev. I | Page 14 of 20

Data Sheet AD829 Figure 44 and Figure 45 show the closed-loop frequency +15V response of the AD829 for different closed-loop gains and 50Ω 0.1µF different supply voltages. CCAOBALXE 7 50Ω 15 VIN 3 + 50Ω CCAOBALXE GAIN =–4 50Ω AD829 6 VOUT 12 CCOMP = 2pF 2 – 5 50kΩ 9 4 N (dB) 6 GCCAOINM P= =– 23pF –01.15µVF 3CpCFOMP 2kΩ GAI 3 P GAIN =–1 ED-LOO –30 CCOMP = 4pF 2kΩ 00880-046 S Figure 46. Noninverting Amplifier Connection Using Current Feedback LO –6 Compensation C –9 VS =±15V RL = 1kΩ ––1152 RVIFN == 1–k3Ω0dBm 00880-044 0.1µF +15V 1 10 100 Figure 44. Closed-Loop FrequencFyR ERQesUpEoNnCsYe (fMorH tzh)e Inverting Amplifier Us ing VIN 3 +7 75Ω CCA5O0BAΩLXE Current Feedback Compensation 75Ω AD829 6 VOUT 2 – 4 75Ω 5 ––2107 CC3O0MpFP –15V 0.1µF 300Ω O2pPFT ITOON 7ApLF FLATNESS –23 TRIM L (dB) ––2296 ±5V±15V Figure 47. Video Line Driver with a Flatness o3v0e0rΩ Frequency Adjustm00880-047e nt VE LE –32 T LOW ERROR VIDEO LINE DRIVER U P –35 T OU –38 The buffer circuit shown in Figure 47 drives a back-terminated VIN =–20dBm 75 Ω video line to standard video levels (1 V p-p), with 0.1 dB –41 RL = 1kΩ ––4474 RGCFCA OI=NM 1 P=k Ω=– 14pF 00880-045 pTgahhianiss felle aavtnnedle s ogsf a tpione 3 ra0fto MtrhmHe az4n .a4cne3d, M wwhHitihcz h oP nAmlyLe e0ct.o0s l4to°hr ae sn urdeb q0cu.a0irr2re%ime rde finrffetesqr fueonertn iacly . 1 10 100 FREQUENCY (MHz) high definition video displays and test equipment, is achieved Figure 45. Closed-Loop Frequency Response vs. Supply for the Inverting using only 5 mA quiescent current. Amplifier Using Current Feedback Compensation When a noninverting amplifier configuration using a current feedback compensation is needed, the circuit shown in Figure 46 is recommended. This circuit provides a slew rate twice that of the shunt compensated noninverting amplifier of Figure 47 at the expense of gain flatness. Nonetheless, this circuit delivers 95 MHz bandwidth with 1 dB flatness into a back-terminated cable, with a differential gain error of only 0.01% and a differential phase error of only 0.015 at 4.43 MHz. Rev. I | Page 15 of 20

AD829 Data Sheet HIGH GAIN VIDEO BANDWIDTH, 3-OP-AMP The input amplifiers operate at a gain of 20, while the output INSTRUMENTATION AMPLIFIER op amp runs at a gain of 5. In this circuit, the main bandwidth limitation is the gain/bandwidth product of the output amplifier. Figure 48 shows a 3-op-amp instrumentation amplifier circuit Extra care should be taken while breadboarding this circuit that provides a gain of 100 at video bandwidths. At a circuit gain of because even a couple of extra picofarads of stray capacitance at the 100, the small signal bandwidth equals 18 MHz into a FET probe. compensation pins of A1 and A2 will degrade circuit bandwidth. Small signal bandwidth equals 6.6 MHz with a 50 Ω load. The 0.1% settling time is 300 ns. 3pF +VIN 3 5 (G = 20) SE2TpTFL TINOG 8 TpIFME A1 AC CMR ADJUST AD829 6 2 1kΩ 2kΩ 1pF 200Ω 2 21R0ΩG 1pF ADA8348 6 200Ω 3 2kΩ 5 (G = 5) INPUT 2kΩ FREQUENCY CMRR 3pF 100Hz 64.6dB 970Ω 1MHz 44.7dB 10MHz 23.9dB 2 DC CMR A2 ADJUST AD829 6 50Ω +15V +VS PIN 7 +VIN 3 5 (G = 20) 10µF 0.1µF 1µF 0.1µF COMM EACH 3pF AMPLIFIER CIRCUIT GAIN = 40R0G0Ω + 1 5 –15V 10µF 0.1µF –VS 1µF 0.1µFPIN 4 00880-048 Figure 48. High Gain Video Bandwidth, 3-Op-Amp In-Amp Circuit Rev. I | Page 16 of 20

Data Sheet AD829 OUTLINE DIMENSIONS 5.00(0.1968) 4.80(0.1890) 8 5 4.00(0.1574) 6.20(0.2441) 3.80(0.1497) 1 4 5.80(0.2284) 1.27(0.0500) 0.50(0.0196) BSC 1.75(0.0688) 0.25(0.0099) 45° 0.25(0.0098) 1.35(0.0532) 8° 0.10(0.0040) 0° COPLANARITY 0.51(0.0201) 1.27(0.0500) 0.10 SEATING 0.31(0.0122) 0.25(0.0098) 0.40(0.0157) PLANE 0.17(0.0067) COMPLIANTTOJEDECSTANDARDSMS-012-AA CONTROLLINGDIMENSIONSAREINMILLIMETERS;INCHDIMENSIONS A (RINEFPEARREENNCTEHEOSNELSY)AANRDEARROEUNNODTEDA-POPFRFOMPIRLLIAIMTEETFEORREUQSUEIVINALDEENSTIGSNF.OR 012407- Figure 49. 8-Lead Standard Small Outline Package [SOIC_N] Narrow Body (R-8) Dimensions shown in millimeters and (inches) 0.400 (10.16) 0.365 (9.27) 0.355 (9.02) 8 5 0.280 (7.11) 0.250 (6.35) 1 4 0.240 (6.10) 0.325 (8.26) 0.310 (7.87) 0.100 (2.54) 0.300 (7.62) BSC 0.060 (1.52) 0.195 (4.95) 0.210 (5.33) MAX 0.130 (3.30) MAX 0.115 (2.92) 0.015 0.150 (3.81) (0.38) 0.015 (0.38) 0.130 (3.30) MIN GAUGE 0.115 (2.92) SEATING PLANE 0.014 (0.36) PLANE 0.010 (0.25) 0.022 (0.56) 0.008 (0.20) 0.005 (0.13) 0.430 (10.92) 0.018 (0.46) MIN MAX 0.014 (0.36) 0.070 (1.78) 0.060 (1.52) 0.045 (1.14) COMPLIANTTO JEDEC STANDARDS MS-001 CONTROLLING DIMENSIONSARE IN INCHES; MILLIMETER DIMENSIONS RC(INEOFRPEANRREERENN LCTEEHA EODSNSEL MSY)AAAYNR BDEE AR CROOEU NNNFODIGETUDAR-POEPFDRFOA INSPC RWHIAH ETOEQL UFEIO VORAR LU EHSNAETL ISFN FLDOEEARSDIGSN.. 070606-A Figure 50. 8-Lead Plastic Dual In-Line Package [PDIP] Narrow Body (N-8) Dimensions shown in inches and (millimeters) Rev. I | Page 17 of 20

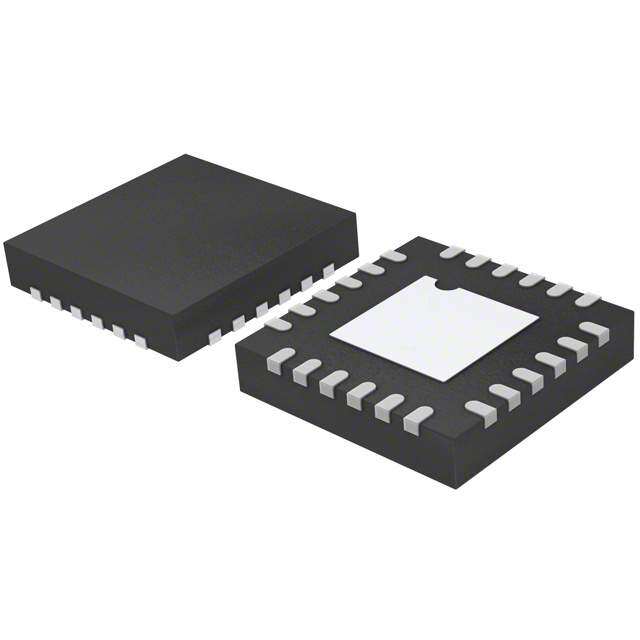

AD829 Data Sheet 0.005 (0.13) 0.055 (1.40) MIN MAX 8 5 0.310 (7.87) 0.220 (5.59) 1 4 0.100 (2.54) BSC 0.405 (10.29) MAX 0.320 (8.13) 0.290 (7.37) 0.200 (5.08) 0.060 (1.52) MAX 0.015 (0.38) 0.200 (5.08) 0.150 (3.81) MIN 0.125 (3.18) 0.015 (0.38) 00..002134 ((00..5386)) 0.070 (1.78) SPELAANTIENG 1 05°° 0.008 (0.20) 0.030 (0.76) CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN. Figure 51. 8-Lead Ceramic Dual In-Line [CERDIP] (Q-8) Dimensions shown in inches and (millimeters) 0.200 (5.08) 0.075 (1.91) REF 0.100 (2.54) REF 0.100 (2.54) REF 0.064 (1.63) 0.095 (2.41) 0.015 (0.38) 0.075 (1.90) MIN 19 3 18 20 4 0.028 (0.71) 0.358 (9.09) 0.358 1 0.342 (8.69) (9.09) 0.011 (0.28) BOTTOM 0.022 (0.56) SQ MSAQX 0.007 R(0 T.1Y8P) VIEW 0.050 (1.27) 0.075 (1.91) 14 8 BSC REF 13 9 45° TYP 0.088 (2.24) 0.055 (1.40) 0.150 (3.81) 0.054 (1.37) 0.045 (1.14) BSC C(RINOEFNPEATRRREOENNLCLTEIHN EOGSN EDLSIYM)AEANNRDSEI AORRNOESU NANORDEET DAIN-PO IPFNRFCO HINPECRSHI;A METEQIL UFLIOIVMRAE LUTEESNRET DISNI M FDOEERNSSIGIONN.S 022106-A Figure 52. 20-Terminal Ceramic Leadless Chip Carrier [LCC] (E-20-1) Dimensions shown in inches and (millimeters) Rev. I | Page 18 of 20

Data Sheet AD829 ORDERING GUIDE Model1 Temperature Range Package Description Package Option AD829AR −40°C to +125°C 8-Lead SOIC_N R-8 AD829AR-REEL −40°C to +125°C 8-Lead SOIC_N R-8 AD829AR-REEL7 −40°C to +125°C 8-Lead SOIC_N R-8 AD829ARZ −40°C to +125°C 8-Lead SOIC_N R-8 AD829ARZ-REEL −40°C to +125°C 8-Lead SOIC_N R-8 AD829ARZ-REEL7 −40°C to +125°C 8-Lead SOIC_N R-8 AD829JN 0°C to 70°C 8-Lead PDIP N-8 AD829JNZ 0°C to 70°C 8-Lead PDIP N-8 AD829JR 0°C to 70°C 8-Lead SOIC_N R-8 AD829JR-REEL 0°C to 70°C 8-Lead SOIC_N R-8 AD829JR-REEL7 0°C to 70°C 8-Lead SOIC_N R-8 AD829JRZ 0°C to 70°C 8-Lead SOIC_N R-8 AD829JRZ-REEL 0°C to 70°C 8-Lead SOIC_N R-8 AD829JRZ-REEL7 0°C to 70°C 8-Lead SOIC_N R-8 AD829AQ −40°C to +125°C 8-Lead CERDIP Q-8 AD829SQ −55°C to +125°C 8-Lead CERDIP Q-8 AD829SQ/883B −55°C to +125°C 8-Lead CERDIP Q-8 5962-9312901MPA −55°C to +125°C 8-Lead CERDIP Q-8 AD829SE/883B −55°C to +125°C 20-Lead LCC E-20-1 5962-9312901M2A −55°C to +125°C 20-Lead LCC E-20-1 AD829JCHIPS Die AD829SCHIPS Die AD829AR-EBZ Evaluation Board 1 Z = RoHS Compliant Part. Rev. I | Page 19 of 20

AD829 Data Sheet NOTES ©2011 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D00880-0-10/11(I) Rev. I | Page 20 of 20

Datasheet下载

Datasheet下载