ICGOO在线商城 > 集成电路(IC) > 线性 - 放大器 - 仪表,运算放大器,缓冲器放大器 > AD8004AR-14

- 型号: AD8004AR-14

- 制造商: Analog

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

AD8004AR-14产品简介:

ICGOO电子元器件商城为您提供AD8004AR-14由Analog设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 AD8004AR-14价格参考¥35.80-¥74.94。AnalogAD8004AR-14封装/规格:线性 - 放大器 - 仪表,运算放大器,缓冲器放大器, 电流反馈 放大器 4 电路 14-SOIC。您可以下载AD8004AR-14参考资料、Datasheet数据手册功能说明书,资料中有AD8004AR-14 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| -3db带宽 | 250MHz |

| 3dB带宽 | 185 MHz |

| 产品目录 | 集成电路 (IC)半导体 |

| 描述 | IC OPAMP CFA 250MHZ 14SOIC高速运算放大器 Quad 3000V/uS 35mW Current Feedback |

| 产品分类 | Linear - Amplifiers - Instrumentation, OP Amps, Buffer Amps集成电路 - IC |

| 品牌 | Analog Devices |

| 产品手册 | |

| 产品图片 |

|

| rohs | 否不符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 放大器 IC,高速运算放大器,Analog Devices AD8004AR-14- |

| 数据手册 | |

| 产品型号 | AD8004AR-14 |

| PCN过时产品 | |

| 产品 | Current Feedback Amplifier |

| 产品培训模块 | http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=30008http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=26202 |

| 产品种类 | |

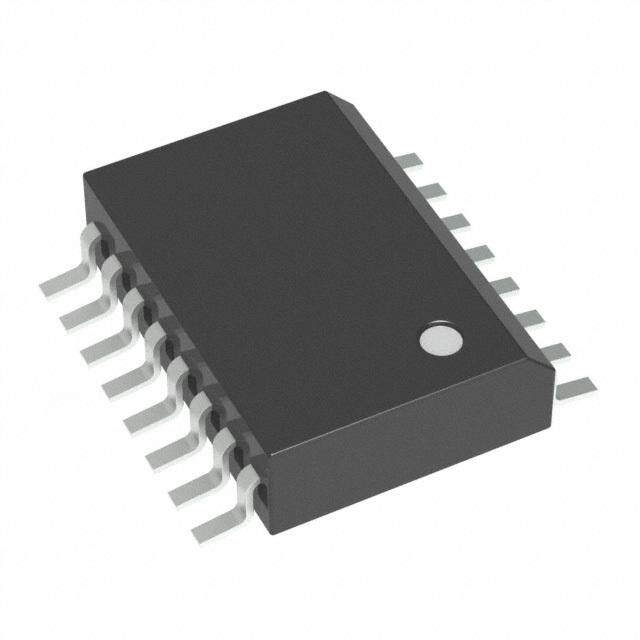

| 供应商器件封装 | 14-SOIC |

| 共模抑制比—最小值 | 52 dB |

| 关闭 | No Shutdown |

| 其它名称 | AD8004AR14 |

| 包装 | 管件 |

| 单电源电压 | 4 V to 12 V |

| 压摆率 | 3000 V/µs |

| 双重电源电压 | +/- 2 V to +/- 6 V |

| 商标 | Analog Devices |

| 增益带宽积 | - |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装 | Tube |

| 封装/外壳 | 14-SOIC(0.154",3.90mm 宽) |

| 封装/箱体 | SOIC-14 |

| 工作温度 | -40°C ~ 85°C |

| 工作电源电压 | +/- 2 V to +/- 6 V |

| 工厂包装数量 | 56 |

| 技术 | BiCOM |

| 拓扑结构 | Current Feedback |

| 放大器类型 | High Speed Amplifier |

| 最大工作温度 | + 85 C |

| 最小工作温度 | - 40 C |

| 标准包装 | 56 |

| 电压-电源,单/双 (±) | 4 V ~ 12 V, ±2 V ~ 6 V |

| 电压-输入失调 | 1mV |

| 电流-电源 | 14mA |

| 电流-输入偏置 | 40µA |

| 电流-输出/通道 | 50mA |

| 电源电压-最大 | 12 V |

| 电源电压-最小 | 4 V |

| 电源电流 | 3.5 mA |

| 电路数 | 4 |

| 稳定时间 | 21 ns |

| 系列 | AD8004 |

| 视频文件 | http://www.digikey.cn/classic/video.aspx?PlayerID=1364138032001&width=640&height=505&videoID=2245193153001http://www.digikey.cn/classic/video.aspx?PlayerID=1364138032001&width=640&height=505&videoID=2245193159001 |

| 转换速度 | 3000 V/us |

| 输入补偿电压 | 1 mV |

| 输出电流 | 50 mA |

| 输出类型 | - |

| 通道数量 | 4 Channel |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

a (cid:1) Quad 3000 V/ s, 35 mW Current Feedback Amplifier AD8004 FEATURES CONNECTION DIAGRAM High Speed SOIC (R) Package 250 MHz –3 dB Bandwidth (G = +1) 3000 V/(cid:1)s Slew Rate 21 ns Settling Time to 0.1% 1.8 ns Rise Time for 2 V Step OUTPUT 1 14 OUTPUT Low Power –IN 2 1 4 13 –IN 3.5 mA/Amp Power Supply Current (35 mW/Amp) +IN 3 12 +IN Single Supply Operation AD8004 Fully Specified for +5 V Supply +VS 4 (TOP VIEW) 11 –VS +IN 5 10 +IN Good Video Specifications (R = 150 (cid:2), G = +2) L –IN 6 2 3 9 –IN Gain Flatness 0.1 dB to 30 MHz OUTPUT 7 8 OUTPUT 0.04% Differential Gain Error 0.10(cid:3) Differential Phase Error Low Distortion –78 dBc THD at 5MHz 30MHz while offering differential gain and phase error of –61dBc THD at 20MHz 0.04% and 0.10∞. This makes the AD8004 suitable for video High Output Current of 50 mA electronics such as cameras and video switchers. Available in a 14-Lead SOIC The AD8004 offers low power of 3.5 mA/amplifier and can run on a single +4 V to +12 V power supply, while being capable of APPLICATIONS delivering up to 50 mA of load current. All this is offered in a Image Scanners small 14-lead SOIC package. These features make this Active Filters amplifier ideal for portable and battery powered applications Video Switchers where size and power are critical. Special Effects The outstanding bandwidth of 250 MHz along with 3000 V/ms GENERAL DESCRIPTION of slew rate make the AD8004 useful in many general-purpose, The AD8004 is a quad, low power, high speed amplifier designed high speed applications where dual power supplies of up to ±6V to operate onsingle or dual supplies. It utilizes a current feed- and single supplies from 4 V to 12 V are needed. The AD8004 back architecture and features high slew rate of 3000V/ms is available in the industrial temperature range of –40∞C to +85∞C in the R package. making the AD8004 ideal for handling large amplitude pulses. Additionally, the AD8004 provides gain flatness of 0.1dB to 1 0.04 G = +2 0 E – dB N – % 000...000321 VRRRI LFNP ==A= 11C50.K010m0A(cid:2)kGV(cid:2) Erms +5VS (cid:4)5VS ––21RESPONS DIFF GAI–––0000....00001230 R8RV0SLF I===R (cid:4)11E5.520V1(cid:2)k(cid:2) S – dB 0.10 ––43ENCY –0.04 1ST 2ND 3RD 4TH 5TH 6TH 7TH 8TH 9TH 10TH 11TH S U E Q s 0.12 D FLATN––00..12 +5VS (cid:4)5VS ––56ZED FRE – Degree 000...100086 ORMALIZE––00..34 ––78NORMALI FF PHASE –0000....00002420 R8RV0SLF I===R (cid:4)11E5.520V1(cid:2)k(cid:2) N–0.5 –9 DI–0.04 1 10 40 100 500 1ST 2ND 3RD 4TH 5TH 6TH 7TH 8TH 9TH 10TH 11TH FREQUENCY – MHz Figure 1.Frequency Response and Flatness, G = +2 Figure 2.Differential Gain/Differential Phase REV. D Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and Tel: 781/329-4700 www.analog.com registered trademarks are the property of their respective companies. Fax: 781/326-8703 © 2003-2015 Analog Devices, Inc. All rights reserved.

AD8004–SPECIFICATIONS (@ T = +25(cid:3)C, V = (cid:4)5 V, R = 100 (cid:2), unless otherwise noted.) A S L AD8004A AD8004S Parameter Test Conditions/Comments Min Typ Max Min Typ Max Unit DYNAMIC PERFORMANCE Bandwidth for 0.1 dB Flatness G = +2 30 30 MHz Slew Rate G = +2, VO = 4 V Step 3000 3000 V/µs G = –2, VO = 4 V Step 2000 2000 V/µs Settling Time to 0.1% G = +2, VO = 2 V Step 21 21 ns Rise and Fall Time (10% to 90%) G = +2, V = 2 V Step 1.8 1.8 ns O NOISE/HARMONIC PERFORMANCE Total Harmonic Distortion fC = 5 MHz, VO = 2 V p-p, RL = 1 kΩ –78 –78 dBc Crosstalk, R Package, Worst Case f = 5 MHz, G = +2, RL = 1 kΩ –69 dB Input Voltage Noise f = 10 kHz 1.5 1.5 nV/√Hz Input Current Noise f = 10 kHz, +In 38 38 pA/√Hz –In 38 38 pA/√Hz Differential Gain Error NTSC, G = +2, R = 150 Ω, R = 1.21kΩ 0.04 0.04 % L F Differential Phase Error NTSC, G = +2, R = 150 Ω, R = 1.21kΩ 0.10 0.10 Degree L F Differential Gain Error NTSC, G = +2, R = 1kΩ, R = 1.21 kΩ 0.01 0.01 % L F Differential Phase Error NTSC, G = +2, R = 1kΩ, R = 1.21kΩ 0.04 0.04 Degree L F DC PERFORMANCE Input Offset Voltage 1.0 3.5 1.0 3.5 mV T to T 1.5 5 1.5 6 mV MIN MAX Offset Drift 15 15 µV/°C –Input Bias Current ±35 ±90 ±35 ±90 µA T to T ±110 ±120 µA MIN MAX +Input Bias Current ±40 ±110 ±40 ±110 µA T to T ±120 ±130 µA MIN MAX Open-Loop Transresistance V = ±2.5 V 170 290 170 290 kΩ O T to T 220 220 kΩ MIN MAX INPUT CHARACTERISTICS Input Resistance +Input 2 2 MΩ –Input 50 50 Ω Input Capacitance +Input 1.5 1.5 pF Input Common-Mode Voltage Range 3.2 3.2 ±V Common-Mode Rejection Ratio Offset Voltage V = ±2.5 V 52 58 52 58 dB CM –Input Current V = ±2.5 V, T to T 1 1 µA/V CM MIN MAX +Input Current V = ±2.5 V, T to T 12 12 µA/V CM MIN MAX OUTPUT CHARACTERISTICS Output Voltage Swing R = 150 Ω 3.9 3.9 ±V L Output Current 50 50 mA Short Circuit Current 100 180 100 180 mA POWER SUPPLY Operating Range ±2.0 ±6.0 ±2.0 ±6.0 V Total Quiescent Current 14 17 14 17 mA T to T 16 20 16 23 mA MIN MAX Power Supply Rejection Ratio ∆V = ±2 V 56 62 56 62 dB S –Input Current T to T 0.5 0.5 µA/V MIN MAX +Input Current T to T 4 4 µA/V MIN MAX Specifications subject to change without notice. –2– REV. D

SPECIFICATIONS AD8004 (@ T = +25(cid:3)C, V = +5 V, R = 100 (cid:2), unless otherwise noted.) A S L AD8004A AD8004S Parameter Test Conditions/Comments Min Typ Max Min Typ Max Unit DYNAMIC PERFORMANCE Bandwidth for 0.1 dB Flatness G = +2 30 30 MHz Slew Rate G = +2, VO = 2 V Step 1100 1100 V/µs Settling Time to 0.1% G = +2, V = 2 V Step 24 24 ns O Rise and Fall Time (10% to 90%) G = +2, V = 2 V Step 2.3 2.3 ns O NOISE/HARMONIC PERFORMANCE Total Harmonic Distortion f = 5 MHz, V = 2 V p-p, R = 1 kΩ –65 –65 dBc C O L Crosstalk, R Package, Worst Case f = 5 MHz, G = +2, RL = 1kΩ –69 dB Input Voltage Noise f = 10 kHz 1.5 1.5 nV/√Hz Input Current Noise f = 10 kHz, +In 38 38 pA/√Hz –In 38 38 pA/√Hz Differential Gain Error NTSC, G = +2, R = 150 Ω, R = 1.21kΩ 0.06 0.06 % L F Differential Phase Error NTSC, G = +2, R = 150 Ω, R = 1.21kΩ 0.25 0.25 Degree L F Differential Gain Error NTSC, G = +2, R = 1kΩ, R = 1.21kΩ 0.01 0.01 % L F Differential Phase Error NTSC, G = +2, R = 1kΩ, R = 1.21kΩ 0.08 0.08 Degree L F DC PERFORMANCE Input Offset Voltage 1.0 2.5 1.0 2.5 mV T to T 1 3 1 4 mV MIN MAX Offset Drift 15 15 µV/°C –Input Bias Current ±20 ±80 ±20 ±80 µA T to T ±100 ±110 µA MIN MAX +Input Bias Current ±35 ±100 ±35 ±100 µA T to T ±115 ±125 µA MIN MAX Open Loop Transresistance V = +1.5Vto+3.5V 140 230 140 230 kΩ O T to T 170 170 kΩ MIN MAX INPUT CHARACTERISTICS Input Resistance +Input 2 2 MΩ –Input 50 50 Ω Input Capacitance +Input 1.5 1.5 pF Input Common-Mode Voltage Range 3.2 3.2 V Common-Mode Rejection Ratio Offset Voltage V =+1Vto+3V 52 57 52 57 dB CM –Input Current V = +1V to +3V, T to T 2 2 µA/V CM MIN MAX +Input Current V = +1V to +3V, T to T 15 15 µA/V CM MIN MAX OUTPUT CHARACTERISTICS Output Voltage Swing R = 150 Ω 0.9 to 4.1 0.9 to 4.1 V L Output Current 50 50 mA Short Circuit Current 95 95 mA POWER SUPPLY Operating Range 0, +4 +12 0, +4 +12 V Total Quiescent Current 13 14 13 14 mA T to T 14.5 15.5 14.5 17.5 mA MIN MAX Power Supply Rejection Ratio ∆V = +1 V, V = +2.5 V 56 62 56 62 dB S CM –Input Current T to T 1 1 µA/V MIN MAX +Input Current T to T 6 6 µA/V MIN MAX Specifications subject to change without notice. REV. D –3–

AD8004 ABSOLUTE MAXIMUM RATINGS1, 2 MAXIMUM POWER DISSIPATION SupplyVoltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12.6V The maximum power that can be safely dissipated by the Internal Power Dissipation . . . . . . . . . . . . . . . . . . . . . Note 2 AD8004 is limited by the associated rise in junction temperature. Input Voltage (Common Mode) . . . . . . . . . . . . . . . . . . . . ±V The maximum safe junction temperature for plastic encapsu- S DifferentialInputVoltage . . . . . . . . . . . . . . . . . . . . . . . ±2.5V lated devices is determined by the glass transition temperature Output Short Circuit Duration of the plastic, approximately +150°C. Exceeding this limit . . . . . . . . . . . . . . . . . . . . . . Observe Power Derating Curves temporarily may cause a shift in parametric performance due to Storage Temperature Range (R) . . . . –65°C to +125°C a change in the stresses exerted on the die by the package. Operating Temperature Range Exceeding a junction temperature of +175°C for an extended A Grade . . . . . . . . . . . . . . . . . . . . . . . . . . . .–40°C to +85°C period can result in device failure. S Grade . . . . . . . . . . . . . . . . . . . . . . . . . . .–55°C to +125°C While the AD8004 is internally short circuit protected, this may Lead Temperature Range (Soldering10sec) . . . . . . . . +300°C not be sufficient to guarantee that the maximum junction tem- NOTES perature is not exceeded under all conditions. To ensure proper 1Stresses above those listed under Absolute Maximum Ratings may cause perma- operation, it is necessary to observe the maximum power ratings. nent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. 2Specification is for device in free air: 14-Lead SOIC Package: θJA = 140°C/W, θJC = 30°C/W ORDERING GUIDE Temperature Package Package Model1 Range Description Option AD8004ARZ-14 –40°C to +85°C 14-Lead SOIC R-14 AD8004ARZ-14-REEL7 –40°C to +85°C 7" Tape and Reel R-14 AD8004AR-EBZ Evaluation Board 1 Z = RoHS Compliant Part. CAUTION ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD8004 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality. SCOPE SCOPE 604(cid:2) 604(cid:2) 50(cid:2) INPUT 249(cid:2) 499(cid:2) 50(cid:2) INPUT VIN 50(cid:2) 61.9(cid:2) 50(cid:2) VIN +VS +VS 50(cid:2) 0.1(cid:1)F 10(cid:1)F 0.1(cid:1)F 10(cid:1)F 0.1(cid:1)F 10(cid:1)F 0.1(cid:1)F 10(cid:1)F –VS –VS Figure 4.Test Circuit; Gain =–2 Figure 3.Test Circuit; Gain =–2 –4– REV. D

Typical Performance Characteristics–AD8004 TPC 1.1 100 mV Step Response; G = +2, VS = ±2.5 V or ±5 V TPC 4.1 100 mV Step Response; G = –2, VS = ±2.5 V or ±5 V TPC 2.1 Step Response; G = +2, VS = ±5 V TPC 5.1 Step Response; G = –2, VS = ±5 V 2 1 Y RESPONSE – dB––0211 RVVIILNN === 15500m0m(cid:2)VV ( G(G = = + +110,) R+ F2 ) =G 6 =9 8+(cid:2)1, CY RESPONSE – dB–––3210 VRVNRSIFL NP = ==A= 4 (cid:4)1C590K0590mVA(cid:2)(cid:2)GV Erms G = –2 G = –1 ENC–3 R F =G 6 =0 4+(cid:2)2, UEN–4 G = –10 U Q EQ–4 RE–5 R F D F–5 ED –6 ALIZE–6 R F G = =4 9+91(cid:2)0, MALIZ–7 M R OR–7 NO–8 N –8 –9 1 10 40 100 500 1 10 40 100 500 FREQUENCY – MHz FREQUENCY – MHz TPC 3.Frequency Response; G = +1, +2, +10; VS =±5 V TPC 6.2 Frequency Response; G = –1, –2, –10 1 VS = ±2.5 V operation is identical to VS = +5 V single-supply operation. 2 The N-14 package option is no longer available; the R-14 package performance may vary. REV. D –5–

AD8004 9 3 1V rms 6 0 3 –3 1V rms BV 0 BV –6 UT LEVEL – d –––639 UT LEVEL – d–––11925 OUTP–12 OUTP–18 G = +2 G = +2 –15 VS = (cid:4)5V –21 VS = +5V RF = 604(cid:2) RF = 604(cid:2) –18 –24 –21 –27 1 10 40 100 500 1 10 40 100 500 FREQUENCY – MHz FREQUENCY – MHz TPC 7.Large Signal Frequency Response; V = ±5.0 V, TPC 10.Large Signal Frequency Response; V = +5.0 V, S S G = +2, R = 604 Ω G = +2, R = 604 Ω F F –40 –40 G = +2 3RD –50 GVROF = == + 6229V8 p(cid:2)-p RL = 1530R(cid:2)D –50 VROF == 629V8 p(cid:2)-p RL 2=N 1D50(cid:2)RL = 150(cid:2) 2ND 3RD ORTION – dBc––6700 RL = 150(cid:2) ORTION – dBc––6700 RL = 1k(cid:2) DIST–80 DIST–80 2ND 2ND RL = 1k(cid:2) –90 RL = 1k(cid:2) –90 3RD RL = 1k(cid:2) –100 –100 1 10 20 1 10 20 FREQUENCY – MHz FREQUENCY – MHz TPC 8.Distortion vs. Frequency; VS = ±5 V TPC 11.Distortion vs. Frequency; VS = +5 V 1 –10 0 dB –15 604(cid:2) 604(cid:2) (cid:4)5VS SS – dB 0.01 RVGRRILF NP= == A=+ 11C250.K010m0A(cid:2)kGV(cid:2) Erms +5VS (cid:4)5VS ––––3214UENCY RESPONSE – RR – dB––––32230505 V5IN7.6(cid:2) 154(cid:2) 154(cid:2) 50(cid:2) VOUT +5VS E Q M FLATN––00..12 +5VS (cid:4)5VS ––56D FRE C––4405 ALIZED –0.3 –7MALIZE –50 +5VS ORM–0.4 –8NOR –55 (cid:4)5VS N–0.5 –9 –60 1 10 40 100 500 0.03 0.1 1 10 100 500 FREQUENCY – MHz FREQUENCY – MHz TPC 9.Frequency Response and Flatness, G = +2 TPC 12.CMRR vs. Frequency; VS = ±5 V or +5 V, V = 200 mV rms, Other Sides Are Equal, RTO IN –6– REV. D

AD8004 100 1000 0 G = +2 500 –10 (cid:4)RF5 V=S 1 Ok(cid:2)R (cid:4)2.5VS Hz Hz 100mV rms ON TOP SE – nV/ 230000 SE – pA/ B––3200 OF dc BIAS +PSRR OLTAGE NOI10 CU+R ORRE –N TIN NPOUITSE 1750000 URRENT NOI PSRR – d––5400 –PSRR V 40 C UT 30 UT –60 P P IN VOLTAGE NOISE 20 IN –70 1 10 –80 10 100 1k 10k 100k 1M 10k 100k 1M 10M 100M 500M FREQUENCY – Hz FREQUENCY – Hz TPC 13.Noise vs. Frequency, V = +5 V or ±5 V TPC 16.PSRR vs. Frequency S S –20 G = +2 100 –30 RF = 1.10k(cid:2) (cid:4)5VS RBT = 50(cid:2) –40 VIN = 200mV rms (cid:2)NCE – 10 RP(G2OF 2= W4= +m 6E2V9R8 r(cid:2)=m 0sd)Bm (cid:4)5VS OR +5VS LK – dB ––6500 RIRN LPP1AU =CT 1 KTkAO(cid:2)G SEIDE 1 OUSTIDPEU T4 = OUSTIDPEU T2 = MPEDA 1 +5VS RBT = 0 OSSTA ––7800 I CR –90 OUTPUT = SIDE 3 0.1 (cid:4)5VS –100 –110 0.01 –120 0.03 0.1 1 10 100 500 0.03 0.1 1 10 100 500 FREQUENCY – MHz FREQUENCY – MHz TPC 14.Output Impedance vs. Frequency TPC 17.Crosstalk (Output to Output) vs. Frequency 110 0 GAIN 60 100 GAIN 50 90 0 90 40 80 s SE – Degree–180 PHASE 3200 GAIN – dB (cid:2)AIN – dB 7600 PHASE –50 Degrees PHA–240 VIN = –40dBm 100 G 5400 –100ASE – VS = (cid:4)5V PH –10 30 –150 –360 20 10 –200 0.03 0.1 1 10 100 500 100k 1M 10M 100M 1G FREQUENCY – MHz FREQUENCY – Hz TPC 15.Open-Loop Voltage Gain and Phase TPC 18.Open-Loop Transimpedance Gain REV. D –7–

AD8004 9 G = +2 8 RF = 1.21k(cid:2) (cid:4)5VS 7 6 p p- V 5 – G N4 WI S3 +5VS 2 1 0 10 100 1000 10000 LOAD RESISTANCE – (cid:2) TPC 19.Short-Term Settling Time TPC 22.Output Voltage Swing vs. Load 10 9 G = +2 RF = 1.21k(cid:2) 8 f = 100kHz TPUTT – V 7 RL = 1k(cid:2) UN K-TO-PEAK OCLIPPING POI 654 RL = 100(cid:2) PEAAT 3 2 1 0 3 4 5 6 7 8 9 10 11 12 TOTAL SUPPLY VOLTAGE – V TPC 20.Long-Term Settling Time TPC 23.Output Swing vs. Supply 0.04 0.03 DIFF GAIN – %–––0000000.......00000001233210 R8RV0SLF I===R (cid:4)11E5.520V1(cid:2)k(cid:2) DIFF GAIN – %––00000.....0000012210 8RVR0SLF I===R (cid:4)11E.k52(cid:2)V1k(cid:2) –0.04 –0.03 1ST 2ND 3RD 4TH 5TH 6TH 7TH 8TH 9TH 10TH 11TH 1ST 2ND 3RD 4TH 5TH 6TH 7TH 8TH 9TH 10TH 11TH DIFF PHASE – Degrees––000000000.........001100000242086420 R8RV0SLF I===R (cid:4)11E5.520V1(cid:2)k(cid:2) DIFF PHASE – Degrees––––000000000.........000000000123443210 8RVR0SLF I===R (cid:4)11Ek.52(cid:2)V1k(cid:2) 1ST 2ND 3RD 4TH 5TH 6TH 7TH 8TH 9TH 10TH 11TH 1ST 2ND 3RD 4TH 5TH 6TH 7TH 8TH 9TH 10TH 11TH TPC 21.Differential Gain/Differential Phase TPC 24.Differential Gain/Phase, R = 1 kΩ L –8– REV. D

AD8004 THEORY OF OPERATION The more exact relationships that take into account open-loop The AD8004 is a member of a new family of high speed current- gain errors are: feedback (CF) amplifiers offering new levels of bandwidth, distortion, and signal-swing capability vs. power. Its wide dynamic A = G range capabilities are due to both a complementary high speed V 1−G R 1+ + F for inverting (G is negative) bipolar process and a new design architecture. The AD8004 is A (s) T (s) O O basically a two stage (Figure 30) rather than the conventional one stage design. Both stages feature the current-on-demand G property associated with current feedback amplifiers. This A = V G R gives an unprecedented ratio of quiescent current to dynamic 1+ + F for noninverting (G is positive) A (s) T (s) performance. The important properties of slew rate and full O O power bandwidth benefit from this performance. In addition In these equations the open-loop voltage gain (A (s)) is common the second gain stage buffers the effects of load impedance, O to both voltage and current-feedback amplifiers and is the ratio significantly reducing distortion. of output voltage to differential input voltage. The open-loop A full discussion of this new amplifier architecture is available on transimpedance gain (T (s)) is the ratio of output voltage to O the data sheet for the AD8011. This discussion only covers the inverting input current and is applicable to current-feedback basic principles of operation. amplifiers. The open-loop voltage gain and open-loop transim- pedance gain (T (s)) of the AD8004 are plotted vs. frequency O DC AND AC CHARACTERISTICS in TPCs 15 and 18. These plots and the basic relationships can As with traditional op amp circuits the dc closed-loop gain is be used to predict the first order performance of the AD8004 over defined as: frequency. At low closed-loop gains the term (R /T (s)) dominates F O the frequency response characteristics. This gives the result that A =G=1+ RF noninverting operation bandwidth is constant with gain, a familiar property of current V R feedback amplifiers. N An R of 1k(cid:1) has been chosen as the nominal value to give F A =G=− RF inverting operation optimum frequency response with acceptable peaking at gains of V RN +2/–1. As can be seen from the above relationships, at higher closed-loop gains reducing R has the effect of increasing closed- F loop bandwidth. Table I gives optimum values for R and R F G for a variety of gains. A1 CD IPP IPN IQ1 A2 CP1 Q3 CP2 ICQ + IO Q1 VP VN ZI VO´ A3 VO Q2 Z2 RF RL CL IE RG Q4 IQ1 A2 INP IPN CP1 A1 CD AD8004 Figure 5.Simplified Block Diagram REV. D –9–

AD8004 DRIVING CAPACITIVE LOADS In noninverting gains, the effect of extra capacitance on The AD8004 was designed primarily to drive nonreactive loads. summing junctions is far more pronounced than with inverting If driving loads with a capacitive component is desired, best gains. Figure 9 shows an example of this. Note that only 1 pF of settling response is obtained by the addition of a small series added junction capacitance causes about a 70% bandwidth resistance as shown in Figure 6. The accompanying graph shows extension and additional peaking on a gain = +2. For an inverting the optimum value for RSERIES vs. capacitive load. It is worth gain = –2, 5 pF of additional summing junction capacitance noting that the frequency response of the circuit when driving caused a small 10% bandwidth extension. large capacitive loads will be dominated by the passive roll-off of R and C . SERIES L Extra output capacitive loading also causes bandwidth exten- 1k(cid:1) sions and peaking. The effect is more pronounced with less resistive loading from the next stage. Figure 10 shows the effect RSERIES of direct output capacitive loads for gains of +2 and –2. For both 1k(cid:1) AD8004 gains C was set to 10 pF or 0 pF (no extra capacitive loading). LOAD 1kR(cid:1)L CL For each of the four traces in Figure 10 the resistive loads were 100 (cid:1). Figure 11 also shows capacitive loading effects with a lighter output resistive load. Note that even though bandwidth Figure 6.Driving Capacitive Load is extended 2¥, the flatness dramatically suffers. 40 2 RF = 698(cid:1) 1 G = +1 RF = 1.1k(cid:1) 0 RF = 909(cid:1) –1 30 +1 (cid:1)R – SERIES20 GAIN – dB, G = +2––1012 VVSIN G == = (cid:2)5 +50mV2V rms RF = 1.10k(cid:1) RF = 604(cid:1) ––––3245GAIN – dB, G = ZED –3 RRL P =A 1C0K0A(cid:1)GE –6 MALI–4 RF = 845(cid:1) –7 R O 100 5 10 15 20 25 N–51 10 40 100 500–8 CL – pF FREQUENCY – MHz Figure 7.Recommended RSERIES vs. Capacitive Load for Figure 8.RFEEDBACK vs. Frequency Response, G = +1/+2 £ 30 ns Settling to 0.1% 2 OPTIMIZING FLATNESS The fine scale gain flatness and –3 dB bandwidth is affected by G = +2 CJ = 1pF 0 +2 = WRFiEthED tBhAeC Kex sceelpectitoionn o af sg iasi nn o=r m+1al, othf ec uArDre8n0t 0f4ee cdabna cbke aamdjpulsitfeiedrs. –2 20 G = –2 CJ = 0 ––24 – dB, G for either maximal flatness with modest closed-loop bandwidth = N obchra nafondrgw emisd itluhdp.l yoF npig eguaarkieen d8 =- us h+po 1fwr aesqn tudhe egn eacfiyfne r c=ets po+fo2 nt.h sTree aweb ieltevh e Imn sluyh coshpw amsc etohdree RF GAIN – dB, G –––246 (cid:2)VRIL5N V ==S 15000m(cid:1)V rms CJ = 5.1pF –––6810MALIZED GAI recommended component values for achieving maximally flat D R frequency response as well as a faster slightly peaked-up fre- ZE –8 –12NO quency response. MALI–10 CJ = 0 –14 R O Printed circuit board parasitics and device lead frame parasitics N–12 also control fine scale gain flatness. In the printed circuit board –14 environment, parasitics such as extra capacitance caused by two 1 10 40 100 500 FREQUENCY – MHz parallel and vertical flat conductors on opposite PC board Figure 9.Frequency Response vs. Added Summing sides in the region of the summing junction will cause some Junction Capacitance bandwidth extension and/or increased peaking. –10– REV. D

AD8004 2 through R2. This current flows toward the summing junction G = +2, RF = 1.10k(cid:2) CL = 10pF 0 +2 and requires that the output be 2 V higher than the summing = junction or at 3.6 V. 2 G = –2, RF = 698(cid:2) CL = 0 –2 , G dB When the input is at 1 V, there is 1.2 mA flowing into the sum- = –2 0 –4 N – ming junction through R3 and 1.2 mA flowing out through R1. GAIN – dB, G –––246 V(cid:4)I5NV =S 50mV CL = 10pF –––8610MALIZED GAI TRin2hp.eu sTte oh cruu s1r .rt6eh neVt os. ubtapluant cise aatn tdh ele saavme en op octuernretinatl atos tflhoew i nthverortuinggh LIZED –8 RL = 100(cid:2) CL = 0 –12NOR Tonh ea nindp ouftf oaft tthhee AsaDm8p7li6n gh arsa tae .s eTriheiss MMOOSSFFEETT sisw citocnhn tehcatte dtu trons MA–10 –14 a hold capacitor internal to the device. The on impedance of the R NO–12 MOSFET is about 50 Ω, while the hold capacitor is about 5 pF. –14 In a worst case condition, the input voltage to the AD876 will 1 10 40 100 500 FREQUENCY – MHz change by a full-scale value (2 V) in one sampling cycle. When Figure 10.Frequency Response vs. Capacitive Loading, the input MOSFET turns on, the output of the op amp will be R = 100 Ω Output connected to the charged hold capacitor through the series L resistance of the MOSFET. Without any other series resistance, the instantaneous current that flows would be 40 mA. This 2 CL = 10pF would cause settling problems for the op amp. 0 The series 100 Ω resistor limits the current that flows instanta- B, G = 2 –2 (cid:4)RGL 5= V= +S 12k(cid:2) nreesoisutsolry caaftnenro tth be eM mOaSdFe EtoTo tluarrgnes oorn tthoe ahbioguht f r1e3q mueAn.c yT pheisrfor- – d –4 VIN = 50mV rms mance will be affected. GAIN –6 RF = 1.2k(cid:2) CL = 0 The sampling MOSFET of the AD876 is closed for only half of D each cycle or for 25 ns. Approximately seven time constants are E LIZ –8 required for settling to 10 bits. The series 100 Ω resistor along A M with the 50 Ω on resistance and the hold capacitor, create a NOR–10 750 ps time constant. These values leave a comfortable margin –12 for settling. Obtaining the same results with the op amp A/D combination as compared to driving with a signal generator –141 10 40 100 500 indicates that the op amp is settling fast enough. FREQUENCY – MHz Figure 11.Flatness with 10 pF Capacitive Load Overall the AD8004 provides adequate buffering for the AD876 A/D converter without introducing distortion greater than that DRIVING A SINGLE-SUPPLY A/D CONVERTER of the A/D converter by itself. New CMOS A/D converters are placing greater demands on the amplifiers that drive them. Higher resolutions, faster conversion +5V rates, and input switching irregularities require superior settling R3 R2 characteristics. In addition, these devices run off a single +5 V 1.65k(cid:2) 1k(cid:2) 0.1(cid:1)F 10(cid:1)F 3.6V supply and consume little power, so good single-supply operation 0.1(cid:1)F with low power consumption is very important. The AD8004 is +3.6V R1 well positioned for driving this new class of A/D converters. 1V VIN 499k(cid:2) REFT Figure 12 shows a circuit that uses an AD8004 to drive an 0V 50(cid:2) AD18/4004 100(cid:2) AD876 AD876, a single supply, 10-bit, 20 MSPS A/D converter that 3.6V requires only 140 mW. Using the AD8004 for level shifting and 0.1(cid:1)F 1.6V REFB driving, the A/D exhibits no degradation in performance com- +1.6V 1.6V pared to when it is driven from a signal generator. Figure 12.AD8004 Driving the AD876 The analog input of the AD876 spans 2 V centered at about 2.6 V. The resistor network and bias voltages provide the level LAYOUT CONSIDERATIONS shifting and gain required to convert the 0 V to 1 V input signal The specified high speed performance of the AD8004 requires to a 3.6 V to 1.6 V range that the AD876 wants to see. careful attention to board layout and component selection. Table I shows the recommended component values for the Biasing the noninverting input of the AD8004 at 1.6 V dc forces AD8004 and Figures 14–16 show the layout for the AD8004 the inverting input to be at 1.6 V dc for linear operation of the amplifier. When the input is at 0 V, there is 3.2 mA flowing out evaluation board (14-lead SOIC). Proper RF design techniques and low parasitic component selection are mandatory. of the summing junction via R1 (1.6 V/499 Ω). R3 has a current of 1.2 mA flowing into the summing junction (3.6 V – 1.6 V)/ 1.65kΩ. The difference of these two currents (2 mA) must flow REV. D –11–

AD8004 The PCB should have a ground plane covering all unused portions of the component side of the board to provide a low impedance RG RF RBT, 50(cid:2) VIN VOUT ground path. The ground plane should be removed from the RT area near the input pins to reduce stray capacitance. 1/4 +VS Chip capacitors should be used for supply bypassing (see C1 C3 0.1(cid:1)F 10(cid:1)F Figure 13). One end should be connected to the ground plane and the other within 1/8" of each power pin. An additional (4.7 µF to C0.21(cid:1)F C104(cid:1)F 10µF) tantalum electrolytic capacitor should be connected in –VS INVERTING CONFIGURATION parallel. The feedback resistor should be located close to the inverting RG RF RBT, 50(cid:2) VOUT input pin in order to keep the stray capacitance at this node to a minimum. Capacitance greater than 1 pF at the inverting input 1/4 will significantly affect high speed performance when operating VIN +VS at low noninverting gains. An example of extra inverting input RT C0.11(cid:1)F C103(cid:1)F capacitance can be seen on the plot of Figure 10. C2 C4 0.1(cid:1)F 10(cid:1)F Stripline design techniques should be used for long signal traces –VS NONINVERTING CONFIGURATION (greater than about 1"). These should be designed with the proper system characteristic impedance and be properly termi- Figure 13.Inverting and Noninverting Configurations nated at each end. Table I. Recommended Component Values1 and Typical Bandwidths Alternate Alternate Alternate Alternate Gain –10 –2 –2 –1 –1 +1 +1 +2 +2 +10 AD8004 (SOIC) PACKAGE TYPE R (Ω) 499 698 499 750 499 1.10 k 698 1.10 k 604 499 F R (Ω) 49.9 348 249 750 499 1.10 k 604 54.9 G R 2 (Ω) None 57.6 61.9 53.6 54.9 50 50 50 50 50 T Small Signal BW @ ±5 V (MHz) 155 130 190 125 195 150 225 110 175 135 S Peaking @ ±5 V < 0.7 dB < 0.1 dB 0.5 dB None 0.4 dB 1.3 dB 1.8 dB < 0.1 dB 0.5 dB < 0.2 dB S 0.1 dB Flatness @ ±5 V (MHz) 35 25 30 S Small Signal BW @ +5 V (MHz) 135 115 175 110 165 130 195 95 155 120 S NOTES 1Resistor values listed are standard 1% tolerance. 2R chosen for 50 Ω characteristic input impedance. T –12– REV. D

AD8004 Figure 14.1 Evaluation Board Silkscreen (Top) 1 The DIP package option is no longer available. REV. D –13–

AD8004 Figure 15Evaluation Board Layout (Top Side) Figure 16.1 Evaluation Board Layout (Bottom Side, Looking Through the Board) 1 The DIP package option is no longer available. –14– REV. D

AD8004 OUTLINE DIMENSIONS 14-Lead Standard Small Outline Package [SOIC] (R-14) Dimensions shown in millimeters and (inches) 8.75 (0.3445) 8.55 (0.3366) 4.00 (0.1575) 14 8 6.20 (0.2441) 3.80 (0.1496) 1 7 5.80 (0.2283) 1.27 (0.0500) 1.75 (0.0689) 0.50 (0.0197) 0.25 (0.0098) BSC 1.35 (0.0531) 0.25 (0.0098)(cid:5) 45(cid:3) 0.10 (0.0039) 8(cid:3) COPLANARITY 0.51 (0.0201) SEATING 0.25 (0.0098)0(cid:3) 1.27 (0.0500) 0.10 0.33 (0.0130) PLANE 0.19 (0.0075) 0.40 (0.0157) COMPLIANT TO JEDEC STANDARDS MS-012AB CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN REV. D –15–

AD8004 Revision History Location Page 12/15—Data Sheet changed from REV. C to REV. D. Deleted 14-Lead PDIP and 14-Lead CERDIP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Universal Changes to ORDERING GUIDE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 D) 5( 3/03—Data Sheet changed from REV. B to REV. C. 2/1 1 Updated format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Universal – 0 – 5 Added CERDIP (Q) Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 4 0 1 Added text to GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 0 D Changes to SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2 Changes to ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 Changes to ORDERING GUIDE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 Edited MAXIMUM POWER DISSIPATION section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 Deleted Figure 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 Edited Y axis of TPC 13 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 Edited OPTIMIZING FLATNESS section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Edits to Figure 13 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12 Changes to Table I . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12 Updated OUTLINE DIMENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15 A. S. U. N D I E T N RI P –16– REV. D

Datasheet下载

Datasheet下载