- 型号: AD5522JSVDZ

- 制造商: Analog

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

AD5522JSVDZ产品简介:

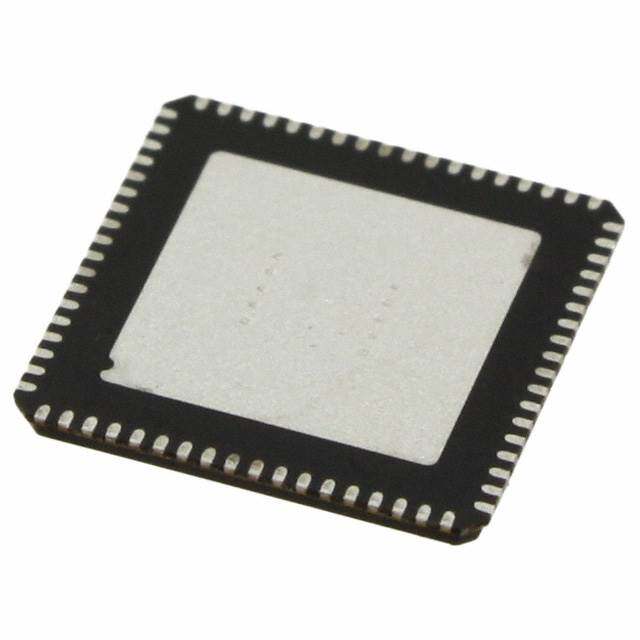

ICGOO电子元器件商城为您提供AD5522JSVDZ由Analog设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 AD5522JSVDZ价格参考。AnalogAD5522JSVDZ封装/规格:专用 IC, Per-Pin Parametric Measurement Unit (PPMU) IC Automatic Test Equipment 80-TQFP-EP (12x12)。您可以下载AD5522JSVDZ参考资料、Datasheet数据手册功能说明书,资料中有AD5522JSVDZ 详细功能的应用电路图电压和使用方法及教程。

AD5522JSVDZ是由Analog Devices Inc.(ADI公司)生产的一款专用集成电路(IC),具体型号为AD5522。该器件主要用于高精度、低噪声的模拟信号处理和控制应用,特别是在需要高分辨率电流输出的场合。 主要应用场景: 1. 工业自动化与过程控制: AD5522JSVDZ广泛应用于工业自动化领域,尤其是在需要精确控制和测量的场景中。例如,在工厂自动化系统中,它可以用作电流环路控制器,实现对电机、阀门等设备的精确控制。其高精度的电流输出特性使其非常适合用于4-20mA电流环路标准,确保数据传输的稳定性和准确性。 2. 精密仪器仪表: 在精密测量仪器中,AD5522JSVDZ可以用于提供稳定的电流源,确保测量结果的准确性和重复性。例如,在温度传感器、压力传感器等设备中,它能够提供精确的激励电流,从而提高传感器的线性和稳定性。 3. 医疗设备: 医疗设备对精度和可靠性要求极高,AD5522JSVDZ凭借其低噪声和高精度特性,适用于各种医疗监测设备,如心电图机、血压计等。它可以为传感器提供稳定的电流激励,确保信号采集的准确性,进而提升诊断的可靠性。 4. 通信系统: 在通信系统中,AD5522JSVDZ可用于生成精确的电流信号,用于调制或解调电路中。其低噪声特性有助于减少信号干扰,提高通信质量。此外,它还可以用于电源管理模块,确保系统的稳定运行。 5. 航空航天与国防: 由于其卓越的性能和可靠性,AD5522JSVDZ在航空航天和国防领域也有广泛应用。例如,在飞行控制系统中,它可以用于提供精确的电流输出,确保各个执行机构的稳定运行。此外,它还可以用于雷达系统中的信号处理部分,确保信号的高保真度。 总之,AD5522JSVDZ凭借其高精度、低噪声和稳定可靠的性能,适用于多种高要求的应用场景,尤其在工业自动化、精密仪器、医疗设备等领域表现出色。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC)半导体 |

| 描述 | IC PMU QUAD 16BIT DAC 80-TQFPPMIC 解决方案 Quad PPMU w/s and LVDS/SPI |

| 产品分类 | |

| 品牌 | Analog Devices Inc |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 电源管理 IC,PMIC 解决方案,Analog Devices AD5522JSVDZ- |

| 数据手册 | |

| 产品型号 | AD5522JSVDZ |

| PCN设计/规格 | |

| 产品 | PMU |

| 产品目录页面 | |

| 产品种类 | PMIC 解决方案 |

| 供应商器件封装 | 80-TQFP(12x12) |

| 包装 | 托盘 |

| 商标 | Analog Devices |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装 | Tray |

| 封装/外壳 | 80-TQFP 裸露焊盘 |

| 封装/箱体 | TQFP-80 |

| 工作温度范围 | - 25 C to + 90 C |

| 工厂包装数量 | 119 |

| 应用 | 自动测试设备 |

| 描述/功能 | Quad parametric measurement unit |

| 最大工作温度 | + 90 C |

| 最小工作温度 | - 25 C |

| 标准包装 | 1 |

| 电源电压 | 5 V to 28 V |

| 电源电流 | 26 mA |

| 类型 | 每引脚参数测量单元(PPMU) |

| 系列 | AD5522 |

| 设计资源 | |

| 输出端数量 | 4 |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

Quad Parametric Measurement Unit with Integrated 16-Bit Level Setting DACs Data Sheet AD5522 FEATURES APPLICATIONS Quad parametric measurement unit (PMU) Automated test equipment (ATE) FV, FI, FN (high-Z), MV, MI functions Per-pin parametric measurement unit 4 programmable current ranges (internal R ) Continuity and leakage testing SENSE ±5 μA, ±20 μA, ±200 μA, and ±2 mA Device power supply 1 programmable current range up to ±80 mA (external R ) Instrumentation SENSE 22.5 V FV range with asymmetrical operation Source measure unit (SMU) Integrated 16-bit DACs provide programmable levels Precision measurement Gain and offset correction on chip Low capacitance outputs suited to relayless systems On-chip comparators per channel FI voltage clamps and FV current clamps Guard drive amplifier System PMU connections Programmable temperature shutdown SPI- and LVDS-compatible interfaces Compact 80-lead TQFP with exposed pad (top or bottom) FUNCTIONAL BLOCK DIAGRAM AGND AVSS AVDD DVCC DGND CCOMP[0:3] SYS_FORCE SYS_SENSE ×4 EN EXTFOH[0:3] REFVGRNEDF 111666 CMX 1 RR REEEGGG×2 X2 ROEGFF×S2ET1 6DACCL1H6- BDIATC CLH SW3 CFF[0:3] 16 INTERNAL RANGE SELECT 16 ×6 – FIN SW1 (±5µA, ±20µA, ±200µA, ±2mA)60Ω 1kΩ 16 MX1 R REEGG X2 REG16F1IN6 -DBAITC + AGND F+ORCE FOH[0:3] C REG MEASVH AMPLIFIER ×6 (Hi-Z) – SW5RSENSE SW2 SW4 SW6 4kΩ 111666 CMX 1 RR REEEGGG×2 X2 REG×2 16CL16L- DBAITC SW10 IVC RMEANIDNTGTEOER CL+L +– 2kΩ SW7 SW8 EXTMEASIH[0:3] ER(CXSUETRNESRREENNATLS ×5 or ×10 EXTMEASIL[0:3] UPTO ±80mA) MEASOUT[0:3] SW12 MUMX×EA1A/N×S0DO. 2UGTAIN TEMP – +– 4kΩ SW9 SENSOR MEASURE AGND 111666 CMX 1 RR REEEGGG×6 X2 RE×G616CP1H6- BDIATC SW11 AGND + CINU-ARMRPENT +– SW13 SW16 MGGEUUAAASRRVDDH[I0[N0:[3:03]:]3]/ DUT 111666 CMX 1 RR REEEGGG×6 X2 RE×G616CP1L6 -DBAITC CPL– + C–PH+ ×1– MVOELATSAUGREE +– DUTGND SW14 GUSAWR1D5AMP DDUUTTGGNNDD[0:3] COMPARATOR IN-AMP 10kΩ AGND 16 1O D6FA-FBCSITET OATOUMTPAPLLUILF TI EDRASC MEMATUSOOXUT SETENMSOPR TMPALM 16 SERIAL CLAMPAND POWER-ON INTERFACE GUARD CGALM RESET ALARM RESETSDO SCLKSDI SYNC BUSY LOAD SLVPDI/S CSCPOLKL0/ CSDPOIH0/ CSYPNOCL1/ CSDPOOH1/ CCPPOOL02/ CCPPOOH12/ CCPPOOL23/ CCPPOOH33/ 06197-001 Figure 1. Rev. F Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Tel: 781.329.4700 ©2008–2018 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. Technical Support www.analog.com

AD5522 Data Sheet TABLE OF CONTENTS Features .............................................................................................. 1 Calibration................................................................................... 38 Applications ....................................................................................... 1 Additional Calibration ............................................................... 39 Functional Block Diagram .............................................................. 1 System Level Calibration ........................................................... 39 Revision History ............................................................................... 3 Circuit Operation ........................................................................... 40 General Description ......................................................................... 4 Force Voltage (FV) Mode .......................................................... 40 Specifications ..................................................................................... 6 Force Current (FI) Mode ........................................................... 41 Timing Characteristics .............................................................. 11 Serial Interface ................................................................................ 42 Absolute Maximum Ratings .......................................................... 15 SPI Interface ................................................................................ 42 Thermal Resistance .................................................................... 15 LVDS Interface............................................................................ 42 ESD Caution ................................................................................ 15 Serial Interface Write Mode ...................................................... 42 Pin Configurations and Function Descriptions ......................... 16 RESET Function ......................................................................... 42 Typical Performance Characteristics ........................................... 22 BUSY and LOAD Functions ..................................................... 42 Terminology .................................................................................... 29 Register Update Rates ................................................................ 44 Theory of Operation ...................................................................... 30 Register Selection ....................................................................... 44 Force Amplifier ........................................................................... 30 Write System Control Register ................................................. 46 Comparators ................................................................................ 30 Write PMU Register ................................................................... 48 Clamps ......................................................................................... 30 Write DAC Register ................................................................... 50 Current Range Selection ............................................................ 31 Read Registers ............................................................................. 53 High Current Ranges ................................................................. 31 Readback of System Control Register...................................... 54 Measure Current Gains.............................................................. 32 Readback of PMU Register ....................................................... 55 VMID Voltage ............................................................................. 32 Readback of Comparator Status Register ................................ 56 Choosing Power Supply Rails ................................................... 33 Readback of Alarm Status Register .......................................... 56 Measure Output (MEASOUTx Pins)....................................... 33 Readback of DAC Register ........................................................ 57 Device Under Test Ground (DUTGND)................................. 33 Applications Information .............................................................. 58 Guard Amplifier ......................................................................... 34 Power-On Default ...................................................................... 58 Compensation Capacitors ......................................................... 34 Setting Up the Device on Power-On ....................................... 58 System Force and Sense Switches ............................................. 35 Changing Modes ........................................................................ 59 Temperature Sensor ................................................................... 35 Required External Components ............................................... 59 DAC Levels ...................................................................................... 36 Power Supply Decoupling ......................................................... 60 Offset DAC .................................................................................. 36 Power Supply Sequencing ......................................................... 60 Gain and Offset Registers .......................................................... 36 Typical Application for the AD5522 ........................................ 60 Cached X2 Registers ................................................................... 37 Outline Dimensions ....................................................................... 62 Reference Voltage (VREF) ......................................................... 37 Ordering Guide .......................................................................... 63 Reference Selection .................................................................... 37 Rev. F | Page 2 of 64

Data Sheet AD5522 REVISION HISTORY 6/2018—Rev. E to Rev. F 10/2008—Rev. 0 to Rev. A Changes to Table 1 ............................................................................ 7 Changes to Table 1 ............................................................................ 6 Changes to Table 2 .......................................................................... 11 Change to 4 DAC X1 Parameter, Table 2 ..................................... 11 Changes to Figure 5 ......................................................................... 13 Changes to Table 3 .......................................................................... 12 Changes to Choosing Power Supply Rails Section and Note 2, Change to Reflow Soldering Parameter, Table 4 ......................... 15 Table 10 ............................................................................................. 33 Changes to Figure 18, Figure 19, Figure 20, and Figure 21 ....... 23 Moved Table 11 ................................................................................ 34 Changes to Figure 25 ...................................................................... 24 Changes to MV Transfer Function, Table 11 and Note 3, Changes to Force Amplifier Section ............................................. 29 Table 11 ............................................................................................. 34 Changes to Clamps Section ........................................................... 29 Changes to Table 39 ........................................................................ 60 Changes to High Current Ranges Section ................................... 30 Changes to Ordering Guide ........................................................... 63 Changes to Choosing Power Supply Rails Section ..................... 32 Changes to Compensation Capacitors Section ........................... 33 5/2012—Rev. D to Rev. E Added Table 14, Renumbered Tables Sequentially ..................... 36 Change to MV Transfer Function, Table 11 ................................ 33 Changes to Reference Selection Example .................................... 36 Changes to Table 15 and BUSYEE and LOADEE Functions 2/2011—Rev. C to Rev. D Section .............................................................................................. 40 Changes to Measure Current, Gain Error Tempco Parameter .... 6 Changes to Table 17 and Register Update Rates Section ........... 41 Changes to Force Current, Common Mode Error (Gain = 5) Added Table 38 ................................................................................ 57 and Common Mode Error (Gain = 10) Parameters ..................... 7 Changes to Ordering Guide ........................................................... 60 Changes to Figure 5 ......................................................................... 13 Changes to Figure 6 ......................................................................... 14 7/2008—Revision 0: Initial Version Changes to Figure 15 ...................................................................... 22 Changes to High Current Ranges Section ................................... 31 Changes to Gain and Offset Registers Section ............................ 36 Changes to Endnote 1 in Table 17 and Figure 56 ........................ 43 Changes to Register Update Rates and Figure 57 ....................... 44 Changes to Bit 15 to Bit 0 Description in Table 28 ..................... 50 5/2010—Rev. B to Rev. C Changes to Compensation Capacitors Section ........................... 34 Changes to Gain and Offset Registers Section ............................ 36 Changes to Table 14 and Reducing Zero-Scale Error Section .. 38 Changes to Serial Interface Write Mode Section and BUSYEE and LOADEE Functions Section ............................................................... 42 Changes to Table 17 ........................................................................ 43 Added Table 18; Renumbered Sequentially ................................. 43 Changes to Register Update Rates Section .................................. 44 Changes to Table 23 ........................................................................ 46 Changes to Table 31 ........................................................................ 54 10/2009—Rev. A to Rev. B Changes to Table 1 ............................................................................ 6 Changes to Table 2 .......................................................................... 11 Added Figure 13 and Figure 15; Renumbered Sequentially ...... 22 Added Figure 16 .............................................................................. 23 Changes to Figure 21 ...................................................................... 23 Changes to Clamps Section ........................................................... 30 Changes to Table 22, Bit 21 to Bit 18 Description ...................... 44 Changes to Table 25, Bit 9 Description ........................................ 47 Changes to Table 28 ........................................................................ 49 Changes to Figure 59 ...................................................................... 59 Rev. F | Page 3 of 64

AD5522 Data Sheet GENERAL DESCRIPTION The AD5522 is a high performance, highly integrated parametric The PMU functions are controlled via a simple 3-wire serial measurement unit consisting of four independent channels. Each interface compatible with SPI, QSPI™, MICROWIRE™, and DSP per-pin parametric measurement unit (PPMU) channel includes interface standards. Interface clocks of 50 MHz allow fast updating five 16-bit, voltage output DACs that set the programmable input of modes. The low voltage differential signaling (LVDS) interface levels for the force voltage inputs, clamp inputs, and comparator protocol at 83 MHz is also supported. Comparator outputs are inputs (high and low). Five programmable force and measure provided per channel for device go-no-go testing and character- current ranges are available, ranging from ±5 µA to ±80 mA. ization. Control registers allow the user to easily change force or Four of these ranges use on-chip sense resistors; one high current measure conditions, DAC levels, and selected current ranges. range up to ±80 mA is available per channel using off-chip sense The SDO (serial data output) pin allows the user to read back resistors. Currents in excess of ±80 mA require an external ampli- information for diagnostic purposes. fier. Low capacitance DUT connections (FOHx and EXTFOHx) ensure that the device is suited to relayless test systems. Rev. F | Page 4 of 64

Data Sheet AD5522 AGND AVSS AVDD DVCC DGND CCOMP0 CH0 EN EXTFOH0 REFVGRNEDF 111666 CMX 1 RR REEEGGG×2 X2 ROEGFF×S2ET1 6DACCL1H6- BDIATC CLH INTERSNWA3L RANGE CFF0 111666 MX1 R REEGG X2 RE×6G16F1IN6 -DBAITC +– AGFNIND SW1 F+ORCE (±5µA, ±20SµAEL, E±2C0T0µA, ±2mA) FOH0 C REG MEASVH AMPLIFIER ×6 (Hi-Z) – SW2 SSWW45RSENSESW6 4kΩ 111666 CMX 1 RR REEEGGG×2 X2 REG×2 16 CL16L- BDIATC SW10 IVC RMEANIDNT GTEOER CL+L +– 2kΩ SW7 SW8 EXTMEASIH0 ER(CXSUETRNESRREENNATLS ×5 OR ×10 EXTMEASIL0 UP TO ±80mA) MEASOUT0 MUMXE AANSDO UGTAIN – +– SW9 SW12 ×1/×0.2 TEMP 4kΩ SENSOR MEASURE AGND 111666 X1 REG×6 ×6 16 16-BIT SW11 CINU-ARMRPENT +– SW16 MEASVH0 CM RREEGG X2 REG CPH DAC AGND + SW13 GUARD0 DUT 111666 MX1 R REEGG×6 X2 RE×G616CP16L- BDIATC CPL– + C–PH+ ×1– MEASURE +–DUTGND SW14 GUARD AMP GDUUTAGRNDDIN00/ DUTGND C REG VOLTAGE SW15 COMPARATOR IN-AMP CPOL0/SCLK 10kΩ AGND CPOH0/SDI EXTFOH1 CFF1 CCOMP1 FOH1 MEASOUT1 CH1 EXTMEASIH1 CPOL1/SYNC EXTMEASIL1 CPOH1/SDO MEASVH1 AGND GUARD1 GUARDIN1/DUTGND1 MUX SYS_SENSE MUX SYS_FORCE EXTFOH2 CCOMP2 CFF2 MEASOUT2 FOH2 CPOL2/CPO0 CH2 EXTMEASIH2 CPOH2/CPO1 EXTMEASIL2 AGND MEASVH2 GUARD2 GUARDIN2/DUTGND2 CCOMP3 EN EXTFOH3 111666 CMX 1 RR REEEGGG×2 X2 ROEGFF×S2ET1 6DACCL1H6- BDIATC CH3 CLH INTESWR3NAL RANGE CFF3 111666 MX1 R REEGG X2 RE×G616F1IN6 -DBAITC +– AGFNIND SW1 F+ORCE (±5µA, ±20SµAEL, E±2C0T0µA, ±2mA) FOH3 C REG ×6 M(HEi-AZS)VH A–MPLIFIER SW5RSENSE SW2 SW6 4kΩ 111666 CMX 1 RR REEEGGG×2 X2 REG×2 16 CL16L- BDIATC SW10 IVC RMEANIDNT GTEOER CL+L S+–W4 2kΩ SW7 SW8 EXTMEASIH3 ER(CXSUETRNESRREENNATLS x5 or x10 EXTMEASIL3 UP TO ±80mA) MEASOUT3 MUMXE AANSDO UGTAIN – +– SW9 SW12 x1/x0.2 TEMP 4kΩ SENSOR MEASURE AGND 111666 X1 REG×6 ×6 16 16-BIT SW11 CINU-ARMRPENT +– MEASVH3 CM RREEGG X2 REG CPH DAC AGND + SW13 SW16 GUARD3 DUT 111666 CMX 1 RR REEEGGG×6 X2 RE×G616CP16L- BDIATC CPL– + C–PH+ x1– MVOELATSAUGREEDUTG+–ND SW14 GUSAWR1D5 AMP GDUUTAGRNDDIN33/ COMPARATOR IN-AMP 10kΩ AGND DUTGND 16 1O D6FA-FBCSITET TOAOUM TPAPLLUILFT IDEARCS SW15a MEMATUSOOXUT SETENMSOPR TMPALM PORWEESRE-TON 16 INTSEERRFIAALCE AGND 10kΩ CLGAAULMAAPRR AMDND CGALM 06197-002 RESET SDO SCLKSDI SYNC BUSY LOAD SPI/ CPOL3/ CPOH3/ LVDS CPO2 CPO3 Figure 2. Detailed Block Diagram Rev. F | Page 5 of 64

AD5522 Data Sheet SPECIFICATIONS AVDD ≥ 10 V; AVSS ≤ −5 V; |AVDD − AVSS| ≥ 20 V and ≤ 33 V; DVCC = 2.3 V to 5.25 V; VREF = 5 V; REFGND = DUTGND = AGND = 0 V; gain (M), offset (C), and DAC offset registers at default values; T = 25°C to 90°C, unless otherwise noted. (FV = force voltage, FI = force J current, MV = measure voltage, MI = measure current, FS = full scale, FSR = full-scale range, FSVR = full-scale voltage range, FSCR = full-scale current range.) Table 1. Parameter Min Typ1 Max Unit Test Conditions/Comments FORCE VOLTAGE FOHx Output Voltage Range2 AVSS + 4 AVDD − 4 V All current ranges from FOHx at full-scale current, includes ±1 V dropped across sense resistor EXTFOHx Output Voltage Range2 AVSS + 3 AVDD − 3 V External high current range at full-scale current, does not include ±1 V dropped across sense resistor Output Voltage Span 22.5 V Offset Error −50 +50 mV Measured at midscale code; prior to calibration Offset Error Tempco2 −10 µV/°C Standard deviation = 20 μV/°C Gain Error −0.5 +0.5 % FSR Prior to calibration Gain Error Tempco2 0.5 ppm/°C Standard deviation = 0.5 ppm/°C Linearity Error −0.01 +0.01 % FSR FSR = full-scale range (±10 V), gain and offset errors calibrated out Short-Circuit Current Limit2 −150 +150 mA ±80 mA range −10 +10 mA All other ranges Noise Spectral Density (NSD)2 320 nV/√Hz 1 kHz, at FOHx in FV mode MEASURE CURRENT Measure current = (IDUT × RSENSE × gain), amplifier gain = 5 or 10, unless otherwise noted Differential Input Voltage Range2 −1.125 +1.125 V Voltage across RSENSE; gain = 5 or 10 Output Voltage Span 22.5 V Measure current block with VREF = 5 V, MEASOUT scaling happens after Offset Error −0.5 +0.5 % FSCR V(RSENSE) = ±1 V, measured with zero current flowing Offset Error Tempco2 1 µV/°C Referred to MI input; standard deviation = 4 µV/°C Gain Error −1 +1 % FSCR Using internal current ranges −0.5 +0.5 % FSCR Measure current amplifier alone Gain Error Tempco2 −2 ppm/°C Standard deviation = 2 ppm/°C, measure current amplifier alone; internal sense resistor 25 ppm/°C Linearity Error (MEASOUTx Gain = 1) −0.015 +0.015 % FSR MI gain = 10 −0.01 +0.01 % FSR MI gain = 5 Linearity Error (MEASOUTx Gain = 0.2) −0.06 +0.06 % FSR MI gain = 10, AVDD = 28 V, AVSS = −5 V, offset DAC = 0x0 −0.11 +0.11 % FSR MI gain = 10, AVDD = 10 V, AVSS = −23 V, offset DAC = 0x0EDB7 −0.015 +0.015 % FSR MI gain = 10, AVDD = 15.25 V, AVSS = −15.25 V, offset DAC = 0xA492 −0.06 +0.06 % FSR MI gain = 5, AVDD = 28 V, AVSS = −5 V, offset DAC = 0x0 −0.01 +0.01 % FSR MI gain = 5, AVDD = 10 V, AVSS = −23 V, offset DAC = 0xEDB7 −0.01 +0.01 % FSR MI gain = 5, AVDD = 15.25 V, AVSS = −15.25 V, offset DAC = 0xA492 Common-Mode Voltage Range2 AVSS + 4 AVDD − 4 V Common-Mode Error (Gain = 5) −0.01 +0.01 % FSCR/V % of full-scale change at force output per V change in DUT voltage Common-Mode Error (Gain = 10) −0.005 +0.005 % FSCR/V % of full-scale change at force output per V change in DUT voltage Sense Resistors Sense resistors are trimmed to within 1% 200 kΩ ±5 µA range 50 kΩ ±20 µA range 5 kΩ ±200 µA range 0.5 kΩ ±2 mA range Rev. F | Page 6 of 64

Data Sheet AD5522 Parameter Min Typ1 Max Unit Test Conditions/Comments Measure Current Ranges2 Specified current ranges are achieved with VREF = 5 V and MI gain = 10, or with VREF = 2.5 V and MI gain = 5 ±5 µA Set using internal sense resistor ±20 µA Set using internal sense resistor ±200 µA Set using internal sense resistor ±2 mA Set using internal sense resistor ±80 mA Set using external sense resistor; internal amplifier can drive up to ±80 mA Noise Spectral Density (NSD)2 400 nV/√Hz 1 kHz, MI amplifier only, inputs grounded FORCE CURRENT Voltage Compliance, FOHx2 AVSS + 4 AVDD − 4 V Voltage Compliance, EXTFOHx2 AVSS + 3 AVDD − 3 V Supports 64 mA sink current and 80 mA source current AVSS + 6 AVDD − 3 V Supports 80 mA sink and source current Offset Error −0.5 +0.5 % FSCR Measured at midscale code, 0 V, prior to calibration Offset Error Tempco2 5 ppm FS/°C Standard deviation = 5 ppm/°C Gain Error −1.5 +1.5 % FSCR Prior to calibration Gain Error Tempco2 −6 ppm/°C Standard deviation = 5 ppm/°C Linearity Error −0.02 +0.02 % FSCR Common-Mode Error (Gain = 5) −0.01 +0.01 % FSCR/V % of full-scale change per V change in DUT voltage Common-Mode Error (Gain = 10) −0.006 +0.006 % FSCR/V % of full-scale change per V change in DUT voltage Force Current Ranges Specified current ranges achieved with VREF = 5 V and MI gain = 10, or with VREF = 2.5 V and MI gain = 5 V ±5 µA Set using internal sense resistor, 200 kΩ ±20 µA Set using internal sense resistor, 50 kΩ ±200 µA Set using internal sense resistor, 5 kΩ ±2 mA Set using internal sense resistor, 500 Ω ±64 ±80 mA Set using external sense resistor, internal amplifier can drive up to ±80 mA with increased compliance MEASURE VOLTAGE Measure Voltage Range2 AVSS + 4 AVDD − 4 V Offset Error −10 +10 mV Gain = 1, measured at 0 V −25 +25 mV Gain = 0.2, measured at 0 V Offset Error Tempco2 −1 µV/°C Standard deviation = 6 µV/°C Gain Error −0.25 +0.25 % FSR MEASOUTx gain = 1 −0.5 +0.5 % FSR MEASOUTx gain = 0.2 Gain Error Tempco2 1 ppm/°C Standard deviation = 4 ppm/°C Linearity Error (MEASOUTx Gain = 1) −0.01 +0.01 % FSR Linearity Error (MEASOUTx Gain = 0.2) −0.01 +0.01 % FSR AVDD = 15.25 V, AVSS = −15.25 V, offset DAC = 0xA492 −0.06 +0.06 % FSR AVDD = 28 V, AVSS = −5 V, offset DAC = 0x0 −0.1 +0.1 % FSR AVDD = −10 V, AVSS = −23 V, offset DAC = 0x3640 Noise Spectral Density (NSD)2 100 nV/√Hz 1 kHz; measure voltage amplifier only, inputs grounded OFFSET DAC Span Error ±30 mV COMPARATOR Comparator Span 22.5 V Offset Error −2 +1 +2 mV Measured directly at comparator; does not include measure block errors Offset Error Tempco2 1 µV/°C Standard deviation = 2 µV/°C Propagation Delay2 0.25 μs VOLTAGE CLAMPS Clamp Span 22.5 V Positive Clamp Accuracy 155 mV Negative Clamp Accuracy −155 mV CLL to CLH2 500 mV CLL < CLH and minimum voltage apart Recovery Time2 0.5 1.5 μs Activation Time2 1.5 3 μs Rev. F | Page 7 of 64

AD5522 Data Sheet Parameter Min Typ1 Max Unit Test Conditions/Comments CURRENT CLAMPS Clamp Accuracy Programmed Programmed % FSC MI gain = 10, clamp current scales with selected clamp value clamp value ± 10 range Programmed Programmed % FSC MI gain = 5, clamp current scales with selected range clamp value clamp value ± 20 CLL to CLH2 5 % of IRANGE CLL < CLH and minimum setting apart, MI gain = 10 10 % of IRANGE CLL < CLH and minimum setting apart, MI gain = 5 Recovery Time2 0.5 1.5 μs Activation Time2 1.5 3 μs FOHx, EXTFOHx, EXTMEASILx, EXTMEASIHx, CFFx PINS Pin Capacitance2 10 pF Leakage Current −3 +3 nA Individual pin on or off switch leakage, measured with ±11 V stress applied to pin, channel enabled, but tristate Leakage Current Tempco2 ±0.01 nA/°C MEASVHx PIN Pin Capacitance2 3 pF Leakage Current −3 +3 nA Measured with ±11 V stress applied to pin, channel enabled, but tristate Leakage Current Tempco2 ±0.01 nA/°C SYS_SENSE PIN SYS_SENSE connected, force amplifier inhibited Pin Capacitance2 3 pF Switch Impedance 1 1.3 kΩ Leakage Current −3 +3 nA Measured with ±11 V stress applied to pin, switch off Leakage Current Tempco2 ±0.01 nA/°C SYS_FORCE PIN SYS_FORCE connected, force amplifier inhibited Pin Capacitance2 6 pF Switch Impedance 60 80 Ω Leakage Current −3 +3 nA Measured with ±11 V stress applied to pin, switch off Leakage Current Tempco2 ±0.01 nA/°C COMBINED LEAKAGE AT DUT Includes FOHx, MEASVHx, SYS_SENSE, SYS_FORCE, EXTMEASILx, EXTMEASIHx, EXTFOHx, and CFFx, calculation of all the individual leakage contributors Leakage Current −15 +15 nA TJ = 25°C to 70°C −25 +25 nA TJ = 25°C to 90°C Leakage Current Tempco2 ±0.1 nA/°C DUTGNDx PIN Voltage Range −500 +500 mV Leakage Current −30 +30 nA MEASOUTx PIN With respect to AGND Output Voltage Span 22.5 V Software programmable output range Output Impedance 60 80 Ω Output Leakage Current −3 +3 nA With SW12 off Output Capacitance2 15 pF Maximum Load Capacitance2 0.5 μF Output Current Drive2 2 mA Short-Circuit Current −10 +10 mA Slew Rate2 2 V/μs Enable Time2 150 320 ns Closing SW12, measured from BUSY rising edge Disable Time2 400 1100 ns Opening SW12, measured from BUSY rising edge MI to MV Switching Time2 200 ns Measured from BUSY rising edge, does not include slewing or settling Rev. F | Page 8 of 64

Data Sheet AD5522 Parameter Min Typ1 Max Unit Test Conditions/Comments GUARDx PIN Output Voltage Span 22.5 V Output Offset −10 +10 mV Short-Circuit Current −15 +15 mA Maximum Load Capacitance2 100 nF Output Impedance 85 Ω Tristate Leakage Current2 −30 +30 nA When guard amplifier is disabled Slew Rate2 5 V/μs CLOAD = 10 pF Alarm Activation Time2 200 μs Alarm delayed to eliminate false alarms FORCE AMPLIFIER2 Slew Rate 0.4 V/μs CCOMPx = 100 pF, CFFx = 220 pF, CLOAD = 200 pF Gain Bandwidth 1.3 MHz CCOMPx = 100 pF, CFFx = 220 pF, CLOAD = 200 pF Max Stable Load Capacitance 10,000 pF CCOMPx = 100 pF, larger CLOAD requires larger CCOMP capacitor 100 nF CCOMPx = 1 nF, larger CLOAD requires larger CCOMP capacitor FV SETTLING TIME TO 0.05% OF FS2 Midscale to full-scale change; measured from SYNC rising edge, clamps on ±80 mA Range 22 40 µs CCOMPx = 100 pF, CFFx = 220 pF, CLOAD = 200 pF ±2 mA Range 24 40 µs CCOMPx = 100 pF, CFFx = 220 pF, CLOAD = 200 pF ±200 µA Range 40 80 µs CCOMPx = 100 pF, CFFx = 220 pF, CLOAD = 200 pF ±20 µA Range 300 µs CCOMPx = 100 pF, CFFx = 220 pF, CLOAD = 200 pF ±5 µA Range 1400 µs CCOMPx = 100 pF, CFFx = 220 pF, CLOAD = 200 pF MI SETTLING TIME TO 0.05% OF FS2 Midscale to full-scale change; driven from force amplifier in FV mode, so includes FV settling time, measured from SYNC rising edge, clamps on ±80 mA Range 22 40 µs CCOMPx = 100 pF, CFFx = 220 pF, CLOAD = 200 pF ±2 mA Range 24 40 µs CCOMPx = 100 pF, CFFx = 220 pF, CLOAD = 200 pF ±200 µA Range 60 100 µs CCOMPx = 100 pF, CFFx = 220 pF, CLOAD = 200 pF ±20 µA Range 462 µs CCOMPx = 100 pF, CFFx = 220 pF, CLOAD = 200 pF ±5 µA Range 1902 µs CCOMPx = 100 pF, CFFx = 220 pF, CLOAD = 200 pF FI SETTLING TIME TO 0.05% OF FS2 Midscale to full-scale change; measured from SYNC rising edge, clamps on ±80 mA Range 24 55 µs CCOMPx = 100 pF, CLOAD = 200 pF ±2 mA Range 24 60 µs CCOMPx = 100 pF, CLOAD = 200 pF ±200 µA Range 50 120 µs CCOMPx = 100 pF, CLOAD = 200 pF ±20 µA Range 450 µs CCOMPx = 100 pF, CLOAD = 200 pF ±5 µA Range 2700 µs CCOMPx = 100 pF, CLOAD = 200 pF MV SETTLING TIME TO 0.05% OF FS2 Midscale to full-scale change; driven from force amplifier in FV mode, so includes FV settling time, measured from SYNC rising edge, clamps on ±80 mA Range 24 55 µs CCOMPx = 100 pF, CLOAD = 200 pF ±2 mA Range 24 60 µs CCOMPx = 100 pF, CLOAD = 200 pF ±200 µA Range 50 120 µs CCOMPx = 100 pF, CLOAD = 200 pF ±20 µA Range 450 µs CCOMPx = 100 pF, CLOAD = 200 pF ±5 µA Range 2700 µs CCOMPx = 100 pF, CLOAD = 200 pF DAC SPECIFICATIONS Resolution 16 Bits Output Voltage Span2 22.5 V VREF = 5 V, within a range of −16.25 V to +22.5 V Differential Nonlinearity2 −1 +1 LSB Guaranteed monotonic by design over temperature COMPARATOR DAC DYNAMIC SPECIFICATIONS2 Output Voltage Settling Time 1 µs 500 mV change to ±½ LSB Slew Rate 5.5 V/µs Digital-to-Analog Glitch Energy 20 nV-sec Glitch Impulse Peak Amplitude 10 mV REFERENCE INPUT VREF DC Input Impedance 1 100 MΩ VREF Input Current −10 +0.03 +10 µA VREF Range2 2 5 V Rev. F | Page 9 of 64

AD5522 Data Sheet Parameter Min Typ1 Max Unit Test Conditions/Comments DIE TEMPERATURE SENSOR Accuracy2 ±7 °C Output Voltage at 25°C 1.5 V Output Scale Factor2 4.6 mV/°C Output Voltage Range2 0 3 V INTERACTION AND CROSSTALK2 DC Crosstalk (FOHx) 0.05 0.65 mV DC change resulting from a dc change in any DAC in the device, FV and FI modes, ±2 mA range, CLOAD = 200 pF, RLOAD = 5.6 kΩ DC Crosstalk (MEASOUTx) 0.05 0.65 mV DC change resulting from a dc change in any DAC in the device, MV and MI modes, ±2 mA range, CLOAD = 200 pF, RLOAD = 5.6 kΩ DC Crosstalk Within a Channel 0.05 mV All channels in FVMI mode, one channel at midscale, measure the current for one channel in the lowest current range for a change in comparator or clamp DAC levels for that PMU SPI INTERFACE LOGIC INPUTS Input High Voltage, VIH 1.7/2.0 V (2.3 V to 2.7 V)/(2.7 V to 5.25 V), JEDEC-compliant input levels Input Low Voltage, VIL 0.7/0.8 V (2.3 V to 2.7 V)/(2.7 V to 5.25 V), JEDEC-compliant input levels Input Current, IINH, IINL −1 +1 µA Input Capacitance, CIN2 10 pF CMOS LOGIC OUTPUTS SDO, CPOx Output High Voltage, VOH DVCC − 0.4 V Output Low Voltage, VOL 0.4 V IOL = 500 µA Tristate Leakage Current −2 +2 µA SDO, CPOH1/SDO −1 +1 µA All other output pins Output Capacitance2 10 pF OPEN-DRAIN LOGIC OUTPUTS BUSY, TMPALM, CGALM Output Low Voltage, VOL 0.4 V IOL = 500 µA, CLOAD = 50 pF, RPULLUP = 1 kΩ Output Capacitance2 10 pF LVDS INTERFACE LOGIC INPUTS REDUCED RANGE LINK2 Input Voltage Range 875 1575 mV Input Differential Threshold −100 +100 mV External Termination Resistance 80 100 120 Ω Differential Input Voltage 100 mV LVDS INTERFACE LOGIC OUTPUTS REDUCED RANGE LINK Output Offset Voltage 1200 mV Output Differential Voltage 400 mV POWER SUPPLIES AVDD 10 28 V |AVDD − AVSS| ≤ 33 V AVSS −23 −5 V DVCC 2.3 5.25 V AIDD 26 mA Internal ranges (±5 μA to ±2 mA), excluding load conditions; comparators and guard disabled AISS −26 mA Internal ranges (±5 μA to ±2 mA), excluding load conditions; comparators and guard disabled AIDD 28 mA Internal ranges (±5 μA to ±2 mA), excluding load conditions; comparators and guard enabled AISS −28 mA Internal ranges (±5 μA to ±2 mA), excluding load conditions; comparators and guard enabled AIDD 36 mA External range, excluding load conditions AISS −36 mA External range, excluding load conditions DICC 1.5 mA Maximum Power Dissipation2 7 W Maximum power that should be dissipated in this package under worst-case load conditions; careful consideration should be given to supply selection and thermal design Rev. F | Page 10 of 64

Data Sheet AD5522 Parameter Min Typ1 Max Unit Test Conditions/Comments Power Supply Sensitivity2 From dc to 1 kHz ΔForced Voltage/ΔAVDD −80 dB ΔForced Voltage/ΔAVSS −80 dB ΔMeasured Current/ΔAVDD −85 dB ΔMeasured Current/ΔAVSS −75 dB ΔForced Current/ΔAVDD −75 dB ΔForced Current/ΔAVSS −75 dB ΔMeasured Voltage/ΔAVDD −85 dB ΔMeasured Voltage/ΔAVSS −80 dB ΔForced Voltage/ΔDVCC −90 dB ΔMeasured Current/ΔDVCC −90 dB ΔForced Current/ΔDVCC −90 dB ΔMeasured Voltage/ΔDVCC −90 dB 1 Typical specifications are at 25°C and nominal supply, ±15.25 V, unless otherwise noted. 2 Guaranteed by design and characterization; not production tested. Tempco values are mean and standard deviation, unless otherwise noted. TIMING CHARACTERISTICS AVDD ≥ 10 V, AVSS ≤ −5 V, |AVDD − AVSS| ≥ 20 V and ≤ 33 V, DVCC = 2.3 V to 5.25 V, VREF = 5 V, T = 25°C to 90°C, unless J otherwise noted. Table 2. SPI Interface DVCC, Limit at T , T MIN MAX Parameter 1, 2, 3 2.3 V to 2.7 V 2.7 V to 3.6 V 4.5 V to 5.25 V Unit Description tWRITE4 1030 735 735 ns min Single channel update cycle time (X1 register write) 950 655 655 ns min Single channel update cycle time (any other register write) t 30 20 20 ns min SCLK cycle time 1 t 8 8 8 ns min SCLK high time 2 t 8 8 8 ns min SCLK low time 3 t4 10 10 10 ns min SYNC falling edge to SCLK falling edge setup time t54 150 150 150 ns min Minimum SYNC high time in write mode after X1 register write (one channel) 70 70 70 ns min Minimum SYNC high time in write mode after any other register write t6 10 5 5 ns min 29th SCLK falling edge to SYNC rising edge t 5 5 5 ns min Data setup time 7 t 9 7 4.5 ns min Data hold time 8 t9 120 75 55 ns max SYNC rising edge to BUSY falling edge t10 BUSY pulse width low for X1 and some PMU register writes; see Table 17 and Table 18 1 DAC X1 1.65 1.65 1.65 µs max 2 DAC X1 2.3 2.3 2.3 µs max 3 DAC X1 2.95 2.95 2.95 µs max 4 DAC X1 3.6 3.6 3.6 µs max Other Registers 270 270 270 ns max System control register/PMU registers t11 20 20 20 ns min 29th SCLK falling edge to LOAD falling edge t12 20 20 20 ns min LOAD pulse width low t13 150 150 150 ns min BUSY rising edge to FOHx output response time t14 0 0 0 ns min BUSY rising edge to LOAD falling edge t15 100 100 100 ns max LOAD falling edge to FOHx output response time t16A 4.0 4.0 4.0 µs min RESET pulse width low min t16B 4.0 4.0 4.0 µs max RESET low to BUSY low max t17 750 750 750 µs max RESET time indicated by BUSY low Rev. F | Page 11 of 64

AD5522 Data Sheet DVCC, Limit at T , T MIN MAX Parameter 1, 2, 3 2.3 V to 2.7 V 2.7 V to 3.6 V 4.5 V to 5.25 V Unit Description t18 400 400 400 ns min Minimum SYNC high time in readback mode t 5, 6 60 45 25 ns max SCLK rising edge to SDO valid; DVCC = 5 V to 5.25 V 19 1 Guaranteed by design and characterization; not production tested. 2 All input signals are specified with tR = tF = 2 ns (10% to 90% of DVCC) and timed from a voltage level of 1.2 V. 3 See Figure 5 and Figure 6. 4 Writes to more than one X1 register engages the calibration engine for longer times, shown by the BUSY low time, t10. Subsequent writes to one or more X1 registers should either be timed or should wait until BUSY returns high (see Figure 56). This is required to ensure that data is not lost or overwritten. 5 t19 is measured with the load circuit shown in Figure 4. 6 SDO output slows with lower DVCC supply and may require use of a slower SCLK. Table 3. LVDS Interface DVCC, Limit at T , T MIN MAX Parameter1, 2, 3 2.7 V to 3.6 V 4.5 V to 5.25 V Unit Description t 20 12 ns min SCLK cycle time 1 t 8 5 ns min SCLK pulse width high and low time 2 t3 3 3 ns min SYNC to SCLK setup time t 3 3 ns min Data setup time 4 t 5 3 ns min Data hold time 5 t6 3 3 ns min SCLK to SYNC hold time t4 45 25 ns min SCLK rising edge to SDO valid 7 t8 150 150 ns min Minimum SYNC high time in write mode after X1 register write 70 70 ns min Minimum SYNC high time in write mode after any other register write 400 400 ns min Minimum SYNC high time in readback mode 1 Guaranteed by design and characterization; not production tested. 2 All input signals are specified with tR = tF = 2 ns (10% to 90% of DVCC) and timed from a voltage level of 1.2 V. 3 See Figure 7. 4 SDO output slows with lower DVCC supply and may require use of slower SCLK. Rev. F | Page 12 of 64

Data Sheet AD5522 Circuit and Timing Diagrams DVCC 200µA IOL RLOAD 2.2kΩ TO OUTPUT VOH(MIN) – VOL(MAX) PIN 2 TO CLOAD OUTPPUINT CLOAD 50pF VOL 06197-003 50pF 200µA IOH 06197-004 Figure 3. Load Circuit for CGALM, TMPALM Figure 4. Load Circuit for SDO, BUSY Timing Diagram t1 SCLK 1 2 29 1 29 t3 t2 t4 t6 SYNC t5 t7 t8 DB28 DB0 DB28 DB0 SDI (N) (N) (N+1) (N + 1) t9 t10 BUSY t11 t12 LOAD1 FOHx1 t13 t14 t12 LOAD2 FOHx2 t15 t16A RESET BUSY t16B t17 21LLOOAADD AACCTTIIVVEE ADFUTREINRG B BUUSSYY.. 06197-00506197-005 Figure 5. SPI Write Timing (Write Word Contains 29 Bits) Rev. F | Page 13 of 64

AD5522 Data Sheet SCLK 29 58 t19 t18 SYNC SDI D(BN2)8 D(NB)0 (DDNBB +22 138)/ (ND B+ 01) INPUT WORD SPECIFIES NOP CONDITION REGISTER TO BE READ DB23/ DB0 SDO (DNB +2 18) (N + 1) UNDEFINED SELECCTLEOD CRKEEGDIS OTUETR DATA 06197-006 Figure 6. SPI Read Timing (Readback Word Contains 24 Bits and Can Be Clocked Out with a Minimum of 24 Clock Edges) t8 SYNC SYNC t3 t1 t6 SCLK SCLK SDI MDS28B t2 t4 D2M3S/DB28 LDS0B LSB D0 SDI t5 t7 SDO MSB LSB DB23/ DB0 SDO DB28 UNDEFINED SELECTED REGISTER DATA CLOCKED OUT 06197-007 Figure 7. LVDS Read and Write Timing (Readback Word Contains 24 Bits and Can Be Clocked Out with a Minimum of 24 Clock Edges) Rev. F | Page 14 of 64

Data Sheet AD5522 ABSOLUTE MAXIMUM RATINGS THERMAL RESISTANCE Table 4. Parameter Rating Thermal resistance values are specified for the worst-case Supply Voltage, AVDD to AVSS 34 V conditions, that is, a device soldered in a circuit board for AVDD to AGND −0.3 V to +34 V surface-mount packages. AVSS to AGND +0.3 V to −34 V Table 5. Thermal Resistance1 (JEDEC 4-Layer (1S2P) Board) VREF to AGND −0.3 V to +7 V Airflow DUTGND to AGND AVDD + 0.3 V to AVSS − 0.3 V Package Type (LFPM) θ θ Unit JA JC REFGND to AGND AVDD + 0.3 V to AVSS − 0.3 V TQFP Exposed Pad on Bottom 4.8 °C/W DVCC to DGND −0.3 V to +7 V No Heat Sink2 0 22.3 °C/W AGND to DGND −0.3 V to +0.3 V 200 17.2 °C/W Digital Inputs to DGND −0.3 V to DVCC + 0.3 V 500 15.1 °C/W Analog Inputs to AGND AVSS − 0.3 V to AVDD + 0.3 V With Cooling Plate at 45°C3 N/A4 5.4 4.8 °C/W Storage Temperature Range −65°C to +125°C TQFP Exposed Pad on Top 2 °C/W Operating Junction Temperature 25°C to 90°C No Heat Sink2 0 42.4 °C/W Range (J Version) 200 37.2 °C/W Reflow Soldering JEDEC Standard (J-STD-020) 500 35.7 °C/W Junction Temperature 150°C max With Cooling Plate at 45°C3 N/A4 3.0 2 °C/W 1 The information in this section is based on simulated thermal information. Stresses at or above those listed under Absolute Maximum 2 These values apply to the package with no heat sink attached. The actual Ratings may cause permanent damage to the product. This is a thermal performance of the package depends on the attached heat sink and environmental conditions. stress rating only; functional operation of the product at these 3 Natural convection at 55°C ambient. Assumes perfect thermal contact or any other conditions above those indicated in the operational between the cooling plate and the exposed paddle. 4 N/A means not applicable. section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability. ESD CAUTION Rev. F | Page 15 of 64

AD5522 Data Sheet PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS EXTFOH0 AVSS RESET TMPALM CGALM SPI/LVDS AVDD DUTGND VREF REFGND SYS_SENSE AGND SYS_FORCE AVSS MEASOUT0 MEASOUT1 MEASOUT2 MEASOUT3 AVSS EXTFOH1 80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 AVDD 1 60 AVDD CFF0 2 PIN1 59 CFF1 CCOMP0 3 58 CCOMP1 EXTMEASIH0 4 57 EXTMEASIH1 EXTMEASIL0 5 56 EXTMEASIL1 FOH0 6 55 FOH1 GUARD0 7 54 GUARD1 GUARDIN0/DUTGND0 8 53 GUARDIN1/DUTGND1 AD5522 MEASVH0 9 52 MEASVH1 TOP VIEW AGND 10 51 AGND EXPOSED PAD ON BOTTOM AGND 11 (Not to Scale) 50 AGND MEASVH2 12 49 MEASVH3 GUARDIN2/DUTGND2 13 48 GUARDIN3/DUTGND3 GUARD2 14 47 GUARD3 FOH2 15 46 FOH3 EXTMEASIL2 16 45 EXTMEASIL3 EXTMEASIH2 17 44 EXTMEASIH3 CCOMP2 18 43 CCOMP3 CFF2 19 42 CFF3 AVDD 20 41 AVDD 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 EXTFOH2 AVSS BUSY SCLK CPOL0/SCLK CPOH0/SDI SDI SYNC CPOL1/SYNC DGND CPOH1/SDO SDO LOAD DVCC CPOL2/CPO0 CPOH2/CPO1 CPOL3/CPO2 CPOH3/CPO3 AVSS EXTFOH3 06197-008 NOTES 1. THE EXPOSED PAD IS INTERNALLY ELECTRICALLY CONNECTED TO AVSS. FOR ENHANCED THERMAL, ELECTRICAL, AND BOARD LEVEL PERFORMANCE, THE EXPOSED PADDLE ON THE BOTTOM OF THE PACKAGE SHOULD BE SOLDERED TO A CORRESPONDING THERMAL LAND PADDLE ON THE PCB. Figure 8. Pin Configuration, Exposed Pad on Bottom Table 6. Pin Function Descriptions Pin No. Mnemonic Description Exposed pad The exposed pad is internally electrically connected to AVSS. For enhanced thermal, electrical, and board level performance, the exposed paddle on the bottom of the package should be soldered to a corresponding thermal land paddle on the PCB. 1, 20, 41, AVDD Positive Analog Supply Voltage. 60, 74 2 CFF0 External Capacitor for Channel 0. This pin optimizes the stability and settling time performance of the force amplifier when in force voltage mode. See the Compensation Capacitors section. 3 CCOMP0 Compensation Capacitor Input for Channel 0. See the Compensation Capacitors section. 4 EXTMEASIH0 Sense Input (High Sense) for High Current Range (Channel 0). 5 EXTMEASIL0 Sense Input (Low Sense) for High Current Range (Channel 0). 6 FOH0 Force Output for Internal Current Ranges (Channel 0). 7 GUARD0 Guard Output Drive for Channel 0. 8 GUARDIN0/ Guard Amplifier Input for Channel 0/DUTGND Input for Channel 0. This dual function pin is configured via the DUTGND0 serial interface. The default function at power-on is GUARDIN0. If this pin is configured as a DUTGND input for the channel, the input to the guard amplifier is internally connected to MEASVH0. For more information, see the Device Under Test Ground (DUTGND) section and the Guard Amplifier section. 9 MEASVH0 DUT Voltage Sense Input (High Sense) for Channel 0. 10, 11, 50, AGND Analog Ground. These pins are the reference points for the analog supplies and the measure circuitry. 51, 69 12 MEASVH2 DUT Voltage Sense Input (High Sense) for Channel 2. Rev. F | Page 16 of 64

Data Sheet AD5522 Pin No. Mnemonic Description 13 GUARDIN2/ Guard Amplifier Input for Channel 2/DUTGND Input for Channel 2. This dual function pin is configured via the DUTGND2 serial interface. The default function at power-on is GUARDIN2. If this pin is configured as a DUTGND input for the channel, the input to the guard amplifier is internally connected to MEASVH2. For more information, see the Device Under Test Ground (DUTGND) section and the Guard Amplifier section. 14 GUARD2 Guard Output Drive for Channel 2. 15 FOH2 Force Output for Internal Current Ranges (Channel 2). 16 EXTMEASIL2 Sense Input (Low Sense) for High Current Range (Channel 2). 17 EXTMEASIH2 Sense Input (High Sense) for High Current Range (Channel 2). 18 CCOMP2 Compensation Capacitor Input for Channel 2. See the Compensation Capacitors section. 19 CFF2 External Capacitor for Channel 2. This pin optimizes the stability and settling time performance of the force amplifier when in force voltage mode. See the Compensation Capacitors section. 21 EXTFOH2 Force Output for High Current Range (Channel 2). Use an external resistor at this pin for current ranges up to ±80 mA. For more information, see the Current Range Selection section. 22, 39, 62, AVSS Negative Analog Supply Voltage. 67, 79 23 BUSY Digital Input/Open-Drain Output. This pin indicates the status of the interface. See the BUSY and LOAD Functions section for more information. 24 SCLK Serial Clock Input, Active Falling Edge. Data is clocked into the shift register on the falling edge of SCLK. This pin operates at clock speeds up to 50 MHz. 25 CPOL0/SCLK Comparator Output Low (Channel 0) for SPI Interface/Differential Serial Clock Input (Complement) for LVDS Interface. 26 CPOH0/SDI Comparator Output High (Channel 0) for SPI Interface/Differential Serial Data Input (Complement) for LVDS Interface. 27 SDI Serial Data Input for SPI or LVDS Interface. 28 SYNC Active Low Frame Synchronization Input for SPI or LVDS Interface. 29 CPOL1/SYNC Comparator Output Low (Channel 1) for SPI Interface/Differential SYNC Input for LVDS Interface. 30 DGND Digital Ground Reference Point. 31 CPOH1/SDO Comparator Output High (Channel 1) for SPI Interface/Differential Serial Data Output (Complement) for LVDS Interface. 32 SDO Serial Data Output for SPI or LVDS Interface. This pin can be used for data readback and diagnostic purposes. 33 LOAD Logic Input (Active Low). This pin synchronizes updates within one device or across a group of devices. If synchronization is not required, LOAD can be tied low; in this case, DAC channels and PMU modes are updated immediately after BUSY goes high. See the BUSY and LOAD Functions section for more information. 34 DVCC Digital Supply Voltage. 35 CPOL2/CPO0 Comparator Output Low (Channel 2) for SPI Interface/Comparator Output Window (Channel 0) for LVDS Interface. 36 CPOH2/CPO1 Comparator Output High (Channel 2) for SPI Interface/Comparator Output Window (Channel 1) for LVDS Interface. 37 CPOL3/CPO2 Comparator Output Low (Channel 3) for SPI Interface/Comparator Output Window (Channel 2) for LVDS Interface. 38 CPOH3/CPO3 Comparator Output High (Channel 3) for SPI Interface/Comparator Output Window (Channel 3) for LVDS Interface. 40 EXTFOH3 Force Output for High Current Range (Channel 3). Use an external resistor at this pin for current ranges up to ±80 mA. For more information, see the Current Range Selection section. 42 CFF3 External Capacitor for Channel 3. This pin optimizes the stability and settling time performance of the force amplifier when in force voltage mode. See the Compensation Capacitors section. 43 CCOMP3 Compensation Capacitor Input for Channel 3. See the Compensation Capacitors section. 44 EXTMEASIH3 Sense Input (High Sense) for High Current Range (Channel 3). 45 EXTMEASIL3 Sense Input (Low Sense) for High Current Range (Channel 3). 46 FOH3 Force Output for Internal Current Ranges (Channel 3). 47 GUARD3 Guard Output Drive for Channel 3. 48 GUARDIN3/ Guard Amplifier Input for Channel 3/DUTGND Input for Channel 3. This dual function pin is configured via the DUTGND3 serial interface. The default function at power-on is GUARDIN3. If this pin is configured as a DUTGND input for the channel, the input to the guard amplifier is internally connected to MEASVH3. For more information, see the Device Under Test Ground (DUTGND) section and the Guard Amplifier section. Rev. F | Page 17 of 64

AD5522 Data Sheet Pin No. Mnemonic Description 49 MEASVH3 DUT Voltage Sense Input (High Sense) for Channel 3. 52 MEASVH1 DUT Voltage Sense Input (High Sense) for Channel 1. 53 GUARDIN1/ Guard Amplifier Input for Channel 1/DUTGND Input for Channel 1. This dual function pin is configured via the DUTGND1 serial interface. The default function at power-on is GUARDIN1. If this pin is configured as a DUTGND input for the channel, the input to the guard amplifier is internally connected to MEASVH1. For more information, see the Device Under Test Ground (DUTGND) section and the Guard Amplifier section. 54 GUARD1 Guard Output Drive for Channel 1. 55 FOH1 Force Output for Internal Current Ranges (Channel 1). 56 EXTMEASIL1 Sense Input (Low Sense) for High Current Range (Channel 1). 57 EXTMEASIH1 Sense Input (High Sense) for High Current Range (Channel 1). 58 CCOMP1 Compensation Capacitor Input for Channel 1. See the Compensation Capacitors section. 59 CFF1 External Capacitor for Channel 1. This pin optimizes the stability and settling time performance of the force amplifier when in force voltage mode. See the Compensation Capacitors section. 61 EXTFOH1 Force Output for High Current Range (Channel 1). Use an external resistor at this pin for current ranges up to ±80 mA. For more information, see the Current Range Selection section. 63 MEASOUT3 Multiplexed DUT Voltage, Current Sense Output, Temperature Sensor Voltage for Channel 3. This pin is referenced to AGND. 64 MEASOUT2 Multiplexed DUT Voltage, Current Sense Output, Temperature Sensor Voltage for Channel 2. This pin is referenced to AGND. 65 MEASOUT1 Multiplexed DUT Voltage, Current Sense Output, Temperature Sensor Voltage for Channel 1. This pin is referenced to AGND. 66 MEASOUT0 Multiplexed DUT Voltage, Current Sense Output, Temperature Sensor Voltage for Channel 0. This pin is referenced to AGND. 68 SYS_FORCE External Force Signal Input. This pin enables the connection of the system PMU. 70 SYS_SENSE External Sense Signal Output. This pin enables the connection of the system PMU. 71 REFGND Accurate Analog Reference Input Ground. 72 VREF Reference Input for DAC Channels (5 V for specified performance). 73 DUTGND DUT Voltage Sense Input (Low Sense). By default, this input is shared among all four PMU channels. If a DUTGND input is required for each channel, the user can configure the GUARDINx/DUTGNDx pins as DUTGND inputs for each PMU channel. 75 SPI/LVDS Interface Select Pin. Logic low selects SPI-compatible interface mode; logic high selects LVDS interface mode. This pin has a pull-down current source (~350 μA). In LVDS interface mode, the CPOHx and CPOLx pins default to differential interface pins. 76 CGALM Open-Drain Output for Guard and Clamp Alarms. This open-drain pin provides shared alarm information about the guard amplifier and clamp circuitry. By default, this output pin is disabled. The system control register allows the user to enable this function and to set the open-drain output as a latched output. The user can also choose to enable alarms for the guard amplifier, the clamp circuitry, or both. When this pin flags an alarm, the origins of the alarm can be determined by reading back the alarm status register. Two flags per channel in this word (one latched, one unlatched) indicate which function caused the alarm and whether the alarm is still present. 77 TMPALM Open-Drain Output for Temperature Alarm. This latched, active low, open-drain output flags a temperature alarm to indicate that the junction temperature has exceeded the default temperature setting (130°C) or the user programmed temperature setting. Two flags in the alarm status register (one latched, one unlatched) indicate whether the temperature has dropped below 130°C or remains above 130°C. User action is required to clear this latched alarm flag by writing to the clear bit (Bit 6) in any of the PMU registers. 78 RESET Digital Reset Input. This active low, level sensitive input resets all internal nodes on the device to their power- on reset values. 80 EXTFOH0 Force Output for High Current Range (Channel 0). Use an external resistor at this pin for current ranges up to ±80 mA. For more information, see the Current Range Selection section. Rev. F | Page 18 of 64

Data Sheet AD5522 0 2 D D N N G G T T AVDD CFF0 CCOMP0 EXTMEASIH0 EXTMEASIL0 FOH0 GUARD0 GUARDIN0/DU MEASVH0 AGND AGND MEASVH2 GUARDIN2/DU GUARD2 FOH2 EXTMEASIL2 EXTMEASIH2 CCOMP2 CFF2 AVDD 80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 EXTFOH0 1 60 EXTFOH2 AVSS 2 PIN1 59 AVSS RESET 3 58 BUSY TMPALM 4 57 SCLK CGALM 5 56 CPOL0/SCLK SPI/LVDS 6 55 CPOH0/SDI AVDD 7 54 SDI AD5522 DUTGND 8 53 SYNC TOPVIEW VREF 9 52 CPOL1/SYNC EXPOSEDPAD ON TOP REFGND 10 51 DGND (Notto Scale) SYS_SENSE 11 50 CPOH1/SDO AGND 12 49 SDO SYS_FORCE 13 48 LOAD AVSS 14 47 DVCC MEASOUT0 15 46 CPOL2/CPO0 MEASOUT1 16 45 CPOH2/CPO1 MEASOUT2 17 44 CPOL3/CPO2 MEASOUT3 18 43 CPOH3/CPO3 AVSS 19 42 AVSS EXTFOH1 20 41 EXTFOH3 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 AVDD CFF1 CCOMP1 EXTMEASIH1 EXTMEASIL1 FOH1 GUARD1 N1/DUTGND1 MEASVH1 AGND AGND MEASVH3 N3/DUTGND3 GUARD3 FOH3 EXTMEASIL3 EXTMEASIH3 CCOMP3 CFF3 AVDD DI DI R R A A U U N1.O TTHEES EXPOSED PAD IS ELECTRICALLY CONGNECTED TO AVSGS. 06197-009 Figure 9. Pin Configuration, Exposed Pad on Top Table 7. Pin Function Descriptions Pin No. Mnemonic Description Exposed pad The exposed pad is electrically connected to AVSS. 1 EXTFOH0 Force Output for High Current Range (Channel 0). Use an external resistor at this pin for current ranges up to ±80 mA. For more information, see the Current Range Selection section. 2, 14, 19, AVSS Negative Analog Supply Voltage. 42, 59 3 RESET Digital Reset Input. This active low, level sensitive input resets all internal nodes on the device to their power- on reset values. 4 TMPALM Open-Drain Output for Temperature Alarm. This latched, active low, open-drain output flags a temperature alarm to indicate that the junction temperature has exceeded the default temperature setting (130°C) or the user programmed temperature setting. Two flags in the alarm status register (one latched, one unlatched) indicate whether the temperature has dropped below 130°C or remains above 130°C. User action is required to clear this latched alarm flag by writing to the clear bit (Bit 6) in any of the PMU registers. 5 CGALM Open-Drain Output for Guard and Clamp Alarms. This open-drain pin provides shared alarm information about the guard amplifier and clamp circuitry. By default, this output pin is disabled. The system control register allows the user to enable this function and to set the open-drain output as a latched output. The user can also choose to enable alarms for the guard amplifier, the clamp circuitry, or both. When this pin flags an alarm, the origins of the alarm can be determined by reading back the alarm status register. Two flags per channel in this word (one latched, one unlatched) indicate which function caused the alarm and whether the alarm is still present. Rev. F | Page 19 of 64

AD5522 Data Sheet Pin No. Mnemonic Description 6 SPI/LVDS Interface Select Pin. Logic low selects SPI-compatible interface mode; logic high selects LVDS interface mode. This pin has a pull-down current source (~350 μA). In LVDS interface mode, the CPOHx and CPOLx pins default to differential interface pins. 7, 21, 40, AVDD Positive Analog Supply Voltage. 61, 80 8 DUTGND DUT Voltage Sense Input (Low Sense). By default, this input is shared among all four PMU channels. If a DUTGND input is required for each channel, the user can configure the GUARDINx/DUTGNDx pins as DUTGND inputs for each PMU channel. 9 VREF Reference Input for DAC Channels. 5 V for specified performance. 10 REFGND Accurate Analog Reference Input Ground. 11 SYS_SENSE External Sense Signal Output. This pin enables the connection of the system PMU. 12, 30, 31, AGND Analog Ground. These pins are the reference points for the analog supplies and the measure circuitry. 70, 71 13 SYS_FORCE External Force Signal Input. This pin enables the connection of the system PMU. 15 MEASOUT0 Multiplexed DUT Voltage, Current Sense Output, Temperature Sensor Voltage for Channel 0. This pin is referenced to AGND. 16 MEASOUT1 Multiplexed DUT Voltage, Current Sense Output, Temperature Sensor Voltage for Channel 1. This pin is referenced to AGND. 17 MEASOUT2 Multiplexed DUT Voltage, Current Sense Output, Temperature Sensor Voltage for Channel 2. This pin is referenced to AGND. 18 MEASOUT3 Multiplexed DUT Voltage, Current Sense Output, Temperature Sensor Voltage for Channel 3. This pin is referenced to AGND. 20 EXTFOH1 Force Output for High Current Range (Channel 1). Use an external resistor at this pin for current ranges up to ±80 mA. For more information, see the Current Range Selection section. 22 CFF1 External Capacitor for Channel 1. This pin optimizes the stability and settling time performance of the force amplifier when in force voltage mode. See the Compensation Capacitors section. 23 CCOMP1 Compensation Capacitor Input for Channel 1. See the Compensation Capacitors section. 24 EXTMEASIH1 Sense Input (High Sense) for High Current Range (Channel 1). 25 EXTMEASIL1 Sense Input (Low Sense) for High Current Range (Channel 1). 26 FOH1 Force Output for Internal Current Ranges (Channel 1). 27 GUARD1 Guard Output Drive for Channel 1. 28 GUARDIN1/ Guard Amplifier Input for Channel 1/DUTGND Input for Channel 1. This dual function pin is configured via the DUTGND1 serial interface. The default function at power-on is GUARDIN1. If this pin is configured as a DUTGND input for the channel, the input to the guard amplifier is internally connected to MEASVH1. For more information, see the Device Under Test Ground (DUTGND) section and the Guard Amplifier section. 29 MEASVH1 DUT Voltage Sense Input (High Sense) for Channel 1. 32 MEASVH3 DUT Voltage Sense Input (High Sense) for Channel 3. 33 GUARDIN3/ Guard Amplifier Input for Channel 3/DUTGND Input for Channel 3. This dual function pin is configured via the DUTGND3 serial interface. The default function at power-on is GUARDIN3. If this pin is configured as a DUTGND input for the channel, the input to the guard amplifier is internally connected to MEASVH3. For more information, see the Device Under Test Ground (DUTGND) section and the Guard Amplifier section. 34 GUARD3 Guard Output Drive for Channel 3. 35 FOH3 Force Output for Internal Current Ranges (Channel 3). 36 EXTMEASIL3 Sense Input (Low Sense) for High Current Range (Channel 3). 37 EXTMEASIH3 Sense Input (High Sense) for High Current Range (Channel 3). 38 CCOMP3 Compensation Capacitor Input for Channel 3. See the Compensation Capacitors section. 39 CFF3 External Capacitor for Channel 3. This pin optimizes the stability and settling time performance of the force amplifier when in force voltage mode. See the Compensation Capacitors section. 41 EXTFOH3 Force Output for High Current Range (Channel 3). Use an external resistor at this pin for current ranges up to ±80 mA. For more information, see the Current Range Selection section. 43 CPOH3/CPO3 Comparator Output High (Channel 3) for SPI Interface/Comparator Output Window (Channel 3) for LVDS Interface. 44 CPOL3/CPO2 Comparator Output Low (Channel 3) for SPI Interface/Comparator Output Window (Channel 2) for LVDS Interface. 45 CPOH2/CPO1 Comparator Output High (Channel 2) for SPI Interface/Comparator Output Window (Channel 1) for LVDS Interface. Rev. F | Page 20 of 64

Data Sheet AD5522 Pin No. Mnemonic Description 46 CPOL2/CPO0 Comparator Output Low (Channel 2) for SPI Interface/Comparator Output Window (Channel 0) for LVDS Interface. 47 DVCC Digital Supply Voltage. 48 LOAD Logic Input (Active Low). This pin synchronizes updates within one device or across a group of devices. If synchronization is not required, LOAD can be tied low; in this case, DAC channels and PMU modes are updated immediately after BUSY goes high. See the BUSY and LOAD Functions section for more information. 49 SDO Serial Data Output for SPI or LVDS Interface. This pin can be used for data readback and diagnostic purposes. 50 CPOH1/SDO Comparator Output High (Channel 1) for SPI Interface/Differential Serial Data Output (Complement) for LVDS Interface. 51 DGND Digital Ground Reference Point. 52 CPOL1/SYNC Comparator Output Low (Channel 1) for SPI Interface/Differential SYNC Input for LVDS Interface. 53 SYNC Active Low Frame Synchronization Input for SPI or LVDS Interface. 54 SDI Serial Data Input for SPI or LVDS Interface. 55 CPOH0/SDI Comparator Output High (Channel 0) for SPI Interface/Differential Serial Data Input (Complement) for LVDS Interface. 56 CPOL0/SCLK Comparator Output Low (Channel 0) for SPI Interface/Differential Serial Clock Input (Complement) for LVDS Interface. 57 SCLK Serial Clock Input, Active Falling Edge. Data is clocked into the shift register on the falling edge of SCLK. This pin operates at clock speeds up to 50 MHz. 58 BUSY Digital Input/Open-Drain Output. This pin indicates the status of the interface. See the BUSY and LOAD Functions section for more information. 60 EXTFOH2 Force Output for High Current Range (Channel 2). Use an external resistor at this pin for current ranges up to ±80 mA. For more information, see the Current Range Selection section. 62 CFF2 External Capacitor for Channel 2. This pin optimizes the stability and settling time performance of the force amplifier when in force voltage mode. See the Compensation Capacitors section. 63 CCOMP2 Compensation Capacitor Input for Channel 2. See the Compensation Capacitors section. 64 EXTMEASIH2 Sense Input (High Sense) for High Current Range (Channel 2). 65 EXTMEASIL2 Sense Input (Low Sense) for High Current Range (Channel 2). 66 FOH2 Force Output for Internal Current Ranges (Channel 2). 67 GUARD2 Guard Output Drive for Channel 2. 68 GUARDIN2/ Guard Amplifier Input for Channel 2/DUTGND Input for Channel 2. This dual function pin is configured via the DUTGND2 serial interface. The default function at power-on is GUARDIN2. If this pin is configured as a DUTGND input for the channel, the input to the guard amplifier is internally connected to MEASVH2. For more information, see the Device Under Test Ground (DUTGND) section and the Guard Amplifier section. 69 MEASVH2 DUT Voltage Sense Input (High Sense) for Channel 2. 72 MEASVH0 DUT Voltage Sense Input (High Sense) for Channel 0. 73 GUARDIN0/ Guard Amplifier Input for Channel 0/DUTGND Input for Channel 0. This dual function pin is configured via the DUTGND0 serial interface. The default function at power-on is GUARDIN0. If this pin is configured as a DUTGND input for the channel, the input to the guard amplifier is internally connected to MEASVH0. For more information, see the Device Under Test Ground (DUTGND) section and the Guard Amplifier section. 74 GUARD0 Guard Output Drive for Channel 0. 75 FOH0 Force Output for Internal Current Ranges (Channel 0). 76 EXTMEASIL0 Sense Input (Low Sense) for High Current Range (Channel 0). 77 EXTMEASIH0 Sense Input (High Sense) for High Current Range (Channel 0). 78 CCOMP0 Compensation Capacitor Input for Channel 0. See the Compensation Capacitors section. 79 CFF0 External Capacitor for Channel 0. This pin optimizes the stability and settling time performance of the force amplifier when in force voltage mode. See the Compensation Capacitors section. Rev. F | Page 21 of 64

AD5522 Data Sheet TYPICAL PERFORMANCE CHARACTERISTICS 1.0 0.0020 TA = 25°C 0.8 NOM: AVDD = +16.5V, AVSS = –16.6V, OFFSET DAC = 0XA492 0.6 0.0015 HIGH: AVDD = +28V, AVSS = –5V, OFFSET DAC = 0X0 ARITY (LSB) 00..420 RITY (% FSR) 0.0010 LOOFWFS:EATV DDDA C= =+ 100xVE,DABV7SS = –23V, NE –0.2 EA 0.0005 LI –0.4 LIN –0.6 0 ––01..800 10,DI0N0NL0L 20,000 30,0C0O0DE40,000 50,000 60,000 06197-010 –0.00050 10,000 20,000 30,C00O0DE40,000 50,000 60,000 06197-140 Figure 10. Force Voltage Linearity vs. Code, All Ranges, Figure 13. Measure Voltage Linearity vs. Code, All Ranges, 1 LSB = 0.0015% FSR (20 V FSR) MEASOUTx Gain = 0.2 2.0 5 TA = 25°C TA = 25°C 4 1.5 3 DNL INL 1.0 2 B) B) LS 0.5 LS 1 Y ( Y ( RIT 0 RIT 0 A A LINE –0.5 LINE –1 –2 –1.0 –3 ––12..50 DINNLL 06197-011 ––45 06197-013 0 10,000 20,000 30,000 40,000 50,000 60,000 0 10,000 20,000 30,000 40,000 50,000 60,000 CODE CODE Figure 11. Force Current Linearity vs. Code, All Ranges, Figure 14. Measure Current Linearity vs. Code, All Ranges, 1 LSB = 0.0015% FSR (20 V FSR) 1 LSB = 0.0015% FSR (20 V FSR), MI Gain = 10, MEASOUTx Gain = 1 2.0 0.035 TA = 25°C 1.5 0.030 AOVFDFSDE =T + D1A5.C5 V=, 0AxVAS4S9 2= –15.5V, AVDD = +28V,AVSS = –5V, 1.0 0.025 OFFSET DAC = 0x0 AVDD = +10V,AVSS = –23V, ARITY (LSB) 0.50 RITY (% FSR) 000...000112050 OFFSET DAC = 0xEDB7 E A LIN –0.5 LINE 0.005 –1.0 0 ––12..500 10,DI0N0NL0L 20,000 30,0C0O0DE40,000 50,000 60,000 06197-012 ––00..0000150 10,000 20,000 30,0C0O0DE40,000 50,000 60,000 06197-141 Figure 12. Measure Voltage Linearity vs. Code, All Ranges, Figure 15. Measure Current Linearity vs. Code, All Ranges, 1 LSB = 0.0015% FSR (20 V FSR), MEASOUTx Gain = 1 MEASOUTx Gain = 0.2, MI Gain = 10 Rev. F | Page 22 of 64

Data Sheet AD5522 0.005 0.2 AVDD = +15.5V, AVSS = –15.5V, 0.004 OFFSET DAC = 0xA492 0 AVDD = +28V,AVSS = –5V, % FSR) 00..000023 OAOVFFDFFDSSEE =TT + DD1AA0VCC, A== V00Sxx0ESD =8 –723V, RENT (nA)––00..24 Y ( 0.001 UR T C LINEARI 0 AKAGE –0.6 ECFOXFTFHFxxOHx E–0.8 EXTMEASIHx –0.001 L EXTMEASILx V = –12V MEASVHx ––00..0000320 10,000 20,000 30,0C0O0DE40,000 50,000 60,000 06197-142 ––11..0225 35GCOUAMRBDIN4IN5ExD/ DTLUEETMAGK5P5NAEDRGxAETUR65E (°C) 75 85 9506197-016 Figure 16. Measure Current Linearity vs. Code, All Ranges, Figure 19. Leakage Current vs. Temperature (Stress Voltage = −12 V) MEASOUTx Gain = 0.2, MI Gain = 5 1.0 0.15 V = 0V TA = 25°C EXTFOHx 0.10 0.8 CFFx nA) FEOXTHMxEASIHx nA) 0.05 T ( 0.6 EXTMEASILx T ( N N E MEASVHx E R R 0 R GUARDINx/DUTGNDx R CU 0.4 COMBINED LEAKAGE CU AGE AGE –0.05 ECXFTFFxOHx AK 0.2 AK FOHx LE LE–0.10 EXTMEASIHx EXTMEASILx –0.20 06197-014 ––00..1250 MGCOUEAMARSBVDINHINExxD/ DLUETAGKNADGxE 06197-017 25 35 45 55 65 75 85 95 –12 –10 –8 –6 –4 –2 0 2 4 6 8 10 12 TEMPERATURE (°C) STRESS VOLTAGE (V) Figure 17. Leakage Current vs. Temperature (Stress Voltage = 0 V) Figure 20. Leakage Current vs. Stress Voltage 2.0 0 V = 12V AVDD ACPSRR EXTFOHx AVSS ACPSRR CFFx –20 DVCC ACPSRR 1.5 A) FOHx n EXTMEASIHx T ( EXTMEASILx –40 RREN 1.0 MGUEAARSVDHINxx/DUTGNDx R (dB) CU COMBINED LEAKAGE SR–60 AGE 0.5 ACP AK –80 E L 0 –100 –0.525 35 45 TEM5P5ERATUR65E (°C) 75 85 9506197-015 –12010 100 1kFREQU1E0NkCY (Hz1)00k 1M 10M 06197-018 Figure 18. Leakage Current vs. Temperature (Stress Voltage = 12 V) Figure 21. ACPSRR at FOHx in Force Voltage Mode vs. Frequency Rev. F | Page 23 of 64

AD5522 Data Sheet 0 0 –10 –10 –20 VSS –20 VSS –30 –30 ACPSRR (dB)–––654000 VVCDCD ACPSRR (dB)––––76540000 VVCDCD –70 –80 –80 –90 –90 –100 –10010 100 FR1kEQUENCY 1(H0kz) 100k 1M 06197-019 –11010 100 FR1kEQUENCY 1(H0kz) 100k 1M 06197-120 Figure 22. ACPSRR at FOHx in Force Current Mode vs. Frequency Figure 25. ACPSRR at MEASOUTx in Measure Voltage Mode vs. Frequency (MI Gain = 10) (MEASOUT Gain = 0.2) 0 0 –10 –10 –20 VSS –20 VSS –30 VDD –30 VDD –40 B)–40 B) R (d–50 VCC R (d–50 VCC R R–60 PS–60 PS C C–70 A–70 A –80 –80 –90 –90 –100 –100 –110 –11010 100 FR1kEQUENCY 1(H0kz) 100k 1M 06197-119 –12010 100 FR1kEQUENCY 1(H0kz) 100k 1M 06197-021 Figure 23. ACPSRR at FOHx in Force Current Mode vs. Frequency Figure 26. ACPSRR at MEASOUTx in Measure Current Mode vs. Frequency (MI Gain = 5) (MI Gain = 10, MEASOUT Gain = 1) 0 0 –10 –10 –20 VSS –20 VSS –30 –30 B)–40 VDD B)–40 VDD RR (d––6500 VCC RR (d––6500 VCC S S CP–70 CP–70 A A –80 –80 –90 –90 –100 –100 –110 –110 –12010 100 FR1kEQUENCY 1(H0kz) 100k 1M 06197-020 –12010 100 FR1kEQUENCY 1(H0kz) 100k 1M 06197-121 Figure 24. ACPSRR at MEASOUTx in Measure Voltage Mode vs. Frequency Figure 27. ACPSRR at MEASOUTx in Measure Current Mode vs. Frequency (MEASOUT Gain = 1) (MI Gain = 5, MEASOUT Gain = 1) Rev. F | Page 24 of 64

Data Sheet AD5522 0 –10 TA = 25°C –20 –30 FOH0 –40 1 B) VSS d–50 R ( SR–60 VCC P C–70 A VDD MEASOUT0 –80 2 –90 LOAD –100 4 ––11210010 100 FR1kEQUENCY 1(H0kz) 100k 1M 06197-122 CH1 20.0mV BW CCHH24 150.000mVV BW MT 4 . 0 0 µ1s0.0000µs 06197-023 CH1 Pk-Pk 39.00mV CH2 Pk-Pk 325.8mV Figure 28. APCSRR at MEASOUTx in Measure Current Mode vs. Frequency Figure 31. AC Crosstalk, FVMI Mode, PMU 0, Full-Scale Transition on One CPH (MI Gain = 10, MEASOUT Gain = 0.2) DAC, MI Gain = 10, MEASOUT Gain = 1, ±2 mA Range, CLOAD = 200 pF 0 –10 TA = 25°C –20 –30 VDD FOH1 –40 1 dB)–50 VSS R ( VCC R–60 S P C–70 A MEASOUT1 –80 2 –90 LOAD –100 4 ––11210010 100 FR1kEQUENCY 1(H0kz) 100k 1M 06197-123 CH1 20.0mV BW CCHH24 150.000mVV BW MT 4 . 0 0 µ1s0.0000µs 06197-024 CH1 Pk-Pk 18.80mV CH2 Pk-Pk 140.0mV Figure 29. APCSRR at MEASOUTx in Measure Current Mode vs. Frequency Figure 32. AC Crosstalk, FVMI Mode, PMU 1, Full-Scale Transition on One CPH (MI Gain = 5, MEASOUT Gain = 0.2) DAC, MI Gain = 10, MEASOUT Gain = 1, ±2 mA Range, CLOAD = 200 pF 900 MEASURE CURRENT IN-AMP T MEASURE VOLTAGE IN-AMP 800 FORCE AMP ATT1A6C.7K0 FmRVO pM-p FIN1 700 FOH0 1 600 Hz) ATT1A0C.3K5 FmRVO pM-p FIN2 nV/ 500 1 FOH0 D ( 400 ATTACK FROM FIN3 NS 11.75mV p-p 300 FOH0 1 200 1000 06197-022 06197-025 10 100 1k 10k 100k 1M CH1 10mV BW M10µs FREQUENCY (Hz) T 30.0µs Figure 30. NSD vs. Frequency (Measured in FVMV and FVMI Mode) Figure 33. AC Crosstalk at FOH0 in FI Mode from FIN DAC of Each Other PMU (Full- Scale Transition), MI Gain = 10, MEASOUT Gain = 1, ±2 mA Range, CLOAD = 200 pF Rev. F | Page 25 of 64

AD5522 Data Sheet TA = 25°C SYNC 4 BUSY 3 1 FOHx VICTIM 2 MEASOUTx VICTIM FOH0 1 MEASOUTx 3 ATTACK 4 TRIGGER 06197-026 06197-129 CH1 10.0mV BW CH2 50.0mV BW M100µs CH1 50.0mV BWCH3 5.00V BW M800ns CH4 2.10V CHC3H 52. 0P0kV-Pk 14.38mCVH4 5.00V T 200.000µs CH45.00V BW T 2.40000µs Figure 34. Shorted DUT AC Crosstalk, Victim PMU in FVMI Mode Figure 37. Range Change, PMU0, ±2 mA to ±5 μA, CLOAD = 1 nF, (±200 μA Range) RLOAD = 620 kΩ, FV = 3 V 1.80 1.75 SYNC 4 V) 1.70 BUSY E ( 3 G A 1.65 T L O V 1.60 Tx FOH0 U SO 1.55 A E 1 M 1.50 NOMINAL SUPPLIES 11..445025 35 45 55 ±561 D55I.F25FVERE7N5T DEVIC8E5S 06197-127 CH1 20.0mV BWCH3 5.00V BW M20.0µs CH4 2.10V 06197-130 FORCED TEMPERATURE (°C) CH45.00V BW T 60.0000µs Figure 35. Temperature Sensor Voltage on MEASOUTx Figure 38. Range Change, PMU0, ±5 μA to ±2 mA, CLOAD = 100 nF, vs. Forced Temperature RLOAD = 620 kΩ, FV = 3 V SYNC SYNC 4 4 3 BUSY BUSY 3 FOH0 FOH0 11 1 06197-128 06197-131 CH1 100mV BW CH3 5.00V BW M2.00µs CH4 2.10V CH1 20.0mV BWCH3 5.00V BW M20.0µs CH4 2.10V CH45.00V BW T 6.0000µs CH45.00V BW T 60.0000µs Figure 36. Range Change, PMU0, ±5 μA to ±2 mA, CLOAD = 1 nF, Figure 39. Range Change, PMU0, ±2 mA to ±5 μA, CLOAD = 100 nF, RLOAD = 620 kΩ, FV = 3 V RLOAD = 620 kΩ, FV = 3 V Rev. F | Page 26 of 64

Data Sheet AD5522 SYNC 4 SYNC 4 BUSY 3 BUSY 3 MEASOUTx (MI) FOH0 2 1 FOHx 1 06197-132 06197-135 CH1 100.0mV BW CH3 5.00V BW M2.00µs CH4 2.10V CH1 2.00V CH2 2.00V M5.0µs CH1 3.84V CH45.00V BW T 6.00000µs CH3 5.00V CH45.00V Figure 40. Range Change, PMU0, ±20 μA to ±2 mA, CLOAD = 1 nF, Figure 43. FV Settling, 0 V to 5 V, ±2 mA Range, CLOAD = 220 pF, RLOAD = 150 kΩ, FV = 3 V CCOMPx = 100 pF, RLOAD = 5.6 kΩ SYNC 4 SYNC 4 BUSY 3 BUSY 3 MEASOUTx (MI) FOH0 2 FOHx 1 1 06197-133 06197-136 CH1 50.0mV BWCH3 5.00V BW M2.000µs CH4 2.10V CH1 2.00V CH2 10.00V M100µs CH1 3.20V CH45.00V BW T 6.00000µs CH3 5.00V CH45.00V Figure 41. Range Change, PMU0, ±2 mA to ±20 μA, CLOAD = 1 nF, Figure 44. FV Settling, 0 V to 5 V, ±5 μA Range, CLOAD = 220 pF, RLOAD = 150 kΩ, FV = 3 V CCOMPx = 100 pF, RLOAD = 1 MΩ SYNC SYNC 4 4 BUSY BUSY 3 3 MEASOUTx (MI) MEASOUTx (MI) 2 2 FOHx FOHx 1 1 06197-134 06197-137 CH1 2.00V CH2 2.00V M10.0µs CH1 3.84V CH1 2.00V CH2 10.0V M25.0µs CH1 3.20V CH3 5.00V CH45.00V CH3 5.00V CH45.00V Figure 42. FV Settling, 0 V to 5 V, ±2 mA Range, CLOAD = 220 pF, Figure 45. FV Settling, 0 V to 5 V, ±20 μA Range, CLOAD = 220 pF, CCOMPx = 1 nF, RLOAD = 5.6 kΩ CCOMPx = 100 pF, RLOAD = 270 kΩ Rev. F | Page 27 of 64

AD5522 Data Sheet SYNC 4 BUSY 3 MEASOUTx (MI) 2 FOHx 1 06197-138 CH1 2.00V CH2 10.0V M10.0µs CH1 3.20V CH3 5.00V CH45.00V Figure 46. FV Settling, 0 V to 5 V, ±200 μA Range, CLOAD = 220 pF, CCOMPx = 100 pF, RLOAD = 27 kΩ Rev. F | Page 28 of 64

Data Sheet AD5522 TERMINOLOGY Offset Error Pin Capacitance Offset error is a measure of the difference between the actual Pin capacitance is the capacitance measured at a pin when that voltage and the ideal voltage at midscale or at zero current function is off or high impedance. expressed in mV or % FSR. Slew Rate Gain Error The slew rate is the rate of change of the output voltage Gain error is the difference between full-scale error and zero- expressed in V/μs. scale error. It is expressed in % FSR. Output Voltage Settling Time Gain Error = Full-Scale Error − Zero-Scale Error Output voltage settling time is the amount of time it takes for the output of a DAC to settle to a specified level for a full-scale where: input change. Full-Scale Error is the difference between the actual voltage and the ideal voltage at full scale. Digital-to-Analog Glitch Energy Zero-Scale Error is the difference between the actual voltage and Digital-to-analog glitch energy is the amount of energy that is the ideal voltage at zero scale. injected into the analog output at the major code transition. It is specified as the area of the glitch in nV-sec. It is measured by Linearity Error toggling the DAC register data between 0x7FFF and 0x8000. Linearity error, or relative accuracy, is a measure of the maximum deviation from a straight line passing through the Digital Crosstalk endpoints of the full-scale range. It is measured after adjusting Digital crosstalk is defined as the glitch impulse transferred to for gain error and offset error and is expressed in % FSR. the output of one converter due to a change in the DAC register code of another converter. It is specified in nV-sec. Differential Nonlinearity (DNL) Differential nonlinearity is the difference between the measured AC Crosstalk change and the ideal 1 LSB change between any two adjacent AC crosstalk is defined as the glitch impulse transferred to the codes. A specified differential nonlinearity of ±1 LSB maximum output of one PMU due to a change in any of the DAC registers ensures monotonicity. in the package. Common-Mode (CM) Error ACPSRR Common-mode (CM) error is the error at the output of the ACPSRR is a measure of the ability of the device to avoid amplifier due to the common-mode input voltage. It is coupling noise and spurious signals that appear on the supply expressed in % of FSVR/V. voltage pin to the output of the switch. The dc voltage on the Leakage Current device is modulated by a sine wave of 0.2 V p-p. The ratio of the Leakage current is the current measured at an output pin when amplitude of the signal on the output to the amplitude of the that function is off or high impedance. modulation is the ACPSRR. Rev. F | Page 29 of 64