ICGOO在线商城 > 集成电路(IC) > 数据采集 - 数模转换器 > AD5441BCPZ-REEL7

- 型号: AD5441BCPZ-REEL7

- 制造商: Analog

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

AD5441BCPZ-REEL7产品简介:

ICGOO电子元器件商城为您提供AD5441BCPZ-REEL7由Analog设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 AD5441BCPZ-REEL7价格参考。AnalogAD5441BCPZ-REEL7封装/规格:数据采集 - 数模转换器, 12 位 数模转换器 1 8-LFCSP-WD(3x3)。您可以下载AD5441BCPZ-REEL7参考资料、Datasheet数据手册功能说明书,资料中有AD5441BCPZ-REEL7 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC) |

| 描述 | IC DAC 12BIT SERIAL IN 8LFCSP |

| 产品分类 | |

| 品牌 | Analog Devices Inc |

| 数据手册 | |

| 产品图片 |

|

| 产品型号 | AD5441BCPZ-REEL7 |

| rohs | 无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | - |

| 产品培训模块 | http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=19145http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=18614http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=26125http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=26140http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=26150http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=26147 |

| 产品目录页面 | |

| 位数 | 12 |

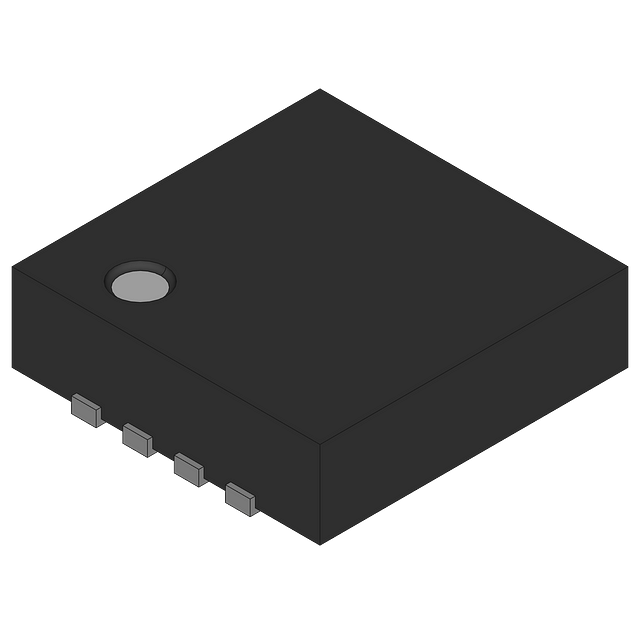

| 供应商器件封装 | 8-LFCSP-WD(3x3) |

| 其它名称 | AD5441BCPZ-REEL7DKR |

| 包装 | Digi-Reel® |

| 安装类型 | 表面贴装 |

| 封装/外壳 | 8-WDFN 裸露焊盘,CSP |

| 工作温度 | -40°C ~ 125°C |

| 建立时间 | 500ns |

| 数据接口 | 串行 |

| 标准包装 | 1 |

| 电压源 | 单电源 |

| 转换器数 | 1 |

| 输出数和类型 | 1 电流,单极1 电流,双极 |

| 配用 | /product-detail/zh/EVAL-AD5541%2F42EBZ/EVAL-AD5541%2F42EBZ-ND/1825562 |

| 采样率(每秒) | 5M |

PDF Datasheet 数据手册内容提取

12位串行输入 乘法DAC AD5441 产品特性 功能框图 2.5 V至5.5 V电源供电 AD5441 真12位精度 VDD RFB 采用5 V电源供电时,电流<1 μA VREF DAC IOUT 快速三线式串行输入 12 5 μs快速建立时间 LD DAC REG 1.9 MHz四象限乘法带宽 12 DAC8043和DAC8043A的升级产品 GND 标准和旋转式引脚排列 CSLRKI 12R-EBGITIS STHEIRFT 06492-001 应用 图1. 工业控制中PLC应用的理想选择 可编程放大器和衰减器 数字控制校准和滤波器 运动控制系统 概述 AD5441是一款改进型、高精度、12位乘法数模转换器 (DAC),采用节省空间的8引脚封装。该器件具有串行输 入、双缓冲和出色的模拟性能,非常适合小电路板空间的 应用。该器件还拥有更高的线性度和增益误差性能,无需 调整元件,从而减少了部件数量。输入时钟和负载DAC采 用分离式控制线路设计,使用户可以完全控制数据负载和 模拟输出。 电路由一个12位串行输入/并行输出移位寄存器、一个12位 DAC寄存器、一个12位CMOS DAC和控制逻辑构成。串行 数据在时钟脉冲的上升沿进入输入寄存器。当新的数据字 被输入时,会通过LD输入引脚载入DAC寄存器。DAC寄 存器中的数据由DAC转换成输出电流。 采用5 V单电源供电时,AD5441的功耗仅为1 μA,提供了一 种低功耗、小尺寸的高性能解决方案,能够解决诸多应用 问题。 AD5441的额定温度范围为−40°C至+125℃扩展工业温度范 围。该器件提供8引脚LFCSP和8引脚MSOP两种封装。 Rev. A Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Tel: 781.329.4700 www.analog.com Trademarks and registered trademarks are the property of their respective owners. Fax: 781.461.3113 ©2008–2011 Analog Devices, Inc. All rights reserved. ADI中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI不对翻译中存在的差异或由此产生的错误负责。如需确认任何词语的准确性,请参考ADI提供 的最新英文版数据手册。

AD5441 目录 产品特性...........................................................................................1 典型性能参数..................................................................................7 应用....................................................................................................1 术语..................................................................................................10 功能框图...........................................................................................1 参数定义.........................................................................................11 概述....................................................................................................1 一般电路信息...........................................................................11 修订历史...........................................................................................2 输出阻抗....................................................................................11 技术规格...........................................................................................3 应用信息....................................................................................11 电气特性......................................................................................3 单极性二象限乘法..................................................................11 时序特性......................................................................................4 双极性四象限乘法..................................................................12 绝对最大额定值..............................................................................5 接口逻辑信息...........................................................................12 热阻..............................................................................................5 数字部分....................................................................................12 ESD警告.......................................................................................5 外形尺寸.........................................................................................13 引脚配置和功能描述.....................................................................6 订购指南....................................................................................13 修订历史 2011年3月—修订版0至修订版A 删除图2.............................................................................................4 增加“时序图”部分..........................................................................4 新增图2、图3和图4;图号重新排序.........................................4 更改图5和表6..................................................................................6 更新“外形尺寸”.............................................................................13 更改“订购指南”.............................................................................13 2008年1月—版本0:初始版 Rev. A | Page 2 of 16

AD5441 技术规格 电气特性 除非另有说明,V = 5 V,V = 10 V,−40°C < T < +155°C。 DD REF A 表1. 参数 符号 最小值 典型值 最大值 单位 条件 静态性能 分辨率 N 12 位 相对精度 INL ±0.5 LSB 差分非线性 DNL ±0.5 LSB 所有等级均具有12位单调性 增益误差 G ±1 LSB 数据 = FFF FSE H 增益温度系数1 TCG ±5 ppm/°C 测量I 引脚 FS OUT 输出漏电流 I ±5 nA 数据 = 000 ,测量I 引脚 LKG H OUT ±25 nA T = –40°C,+125°C,数据= 000 ,测量I 引脚 A H OUT 零值误差 I ±0.03 LSB 数据 = 000 ZSE H ±0.15 LSB T = −40°C至+125°C,数据 = 000 A H 基准输入 输入电阻 R 7 15 kΩ 绝对温度系数小于50 ppm/°C REF 输入电容1 C 5 pF REF 模拟输出 输出电容1 C 1 pF 数据 = 000 OUT H 4 pF 数据 = FFF H 数字输入 数字输入低电平 V 0.8 V IL 数字输入高电平 V 2.4 V IH 输入漏电流 I 1 µA V = 0 V 至 5 V IL LOGIC 输入电容1 C 4.0 pF V = 0 V IL LOGIC 交流特性1 输出电流建立时间 t 5 µs 到满量程的±0.01%,外部运算放大器OP42 S 0.5 µs 到满量程的±0.01%,100 Ω端接于地 DAC毛刺 Q 40 nVs 数据 = 000 至FFF 至000 ,V = 0 V,OP42 H H H REF 1 nVs 数据 = 000 至FFF 至000 ,V = 0 V,100 Ω H H H REF 数字馈通 5 nV 使用外部运算放大器OP42 馈通(V /V ) FT 1.4 mV p-p V = 20 V p-p,数据 = 000 ,f = 10 kHz OUT REF REF H 总谐波失真 总谐波失真(THD) −85 dB V = 6 V rms,数据 = FFF ,f = 1 kHz REF H 输出噪声密度 e 17 nV/√Hz R 和I 之间为10 Hz至100 kHz n FB OUT 乘法带宽 带宽 1.9 MHz −3 dB,V /V ,V = 100 mV rms,数据 = FFF OUT REF REF H 电源特性1 电源电压范围 V 范围 2.5 5.5 V DD 正电源电流 I 10 µA V = 0 V 或 V DD LOGIC DD 功耗 P 2.5 5.5 µW V = 0 V 或 V DISS LOGIC DD 电源灵敏度 PSS 0.002 %/% ∆V = ±5% DD 1 通过设计保证这些参数,而这些参数未经生产测试。 Rev. A | Page 3 of 16

AD5441 时序特性 所有输入控制信号均指定t = t = 2 ns(10%至90%,V ),并从(V + V )/2电平起开始计时;V + 2.5 V至5.5 V, R F DD IL IH DD V = 10 V;温度范围 = −40°C至+125°C;除非另有说明,所有规格均相对于T 至T 而言。 REF MIN MAX 表2. 时序特性 参数 2.5 V 5.5 V 单位 条件/注释 t 10 5 ns(最小值) 数据建立 DS t 5 5 ns(最小值) 数据保持 DH t 15 10 ns(最小值) 时钟高电平脉宽 CH t 15 10 ns(最小值) 时钟低电平脉宽 CL t 20 10 ns(最小值) 负载脉冲宽度 LD t 0 0 ns(最小值) LD DAC高电平至MSB CLK高电平 LD1 t 0 0 ns(最小值) LSB CLK至LD DAC ASB 时序图 SRI D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 CLK tLD1 tASB LD DAC REGISTER LOAD 06492-102 图2. 完整数据传输 DATA LOADED MSB(D11) FIRST SRI Dxx tDS tDH CLK tCL tCH 06492-103 图3. 位数据传输 tLD LD FS ±1LSB VOUTZS ERROR BAND 06492-104 图4. 输出转换 表3. 控制逻辑真值表 CLK LD 串行移位寄存器功能 DAC寄存器功能 ↑1 H 移位寄存器数据前移一位 锁存 ↑ L 移位寄存器数据前移一位 透明 H 或 L L 不起作用 用电流移位寄存器内容更新 L ↑1 不起作用 锁存全部12位 1 ↑等于正逻辑转换。 Rev. A | Page 4 of 16

AD5441 绝对最大额定值 表4. 热阻 参数 额定值 V 至 GND −0.3 V, +8 V θ 针对最差条件,即器件焊接在电路板上以实现表贴封装。 DD JA V 至 GND ±18 V REF 表5. R 至 GND ±18 V FB 封装类型 θ θ 单位 逻辑输入至GND −0.3 V, V + 0.3 V JA JC DD 8引脚MSOP 142 44 °C/W I 至 GND −0.3 V, V + 0.3 V OUT DD 8引脚LFCSP1 75 18 °C/W 对地短路I 50 mA OUT 封装功耗 (T最大值 − T )/θ 1裸露焊盘焊接到接地层。 J A JA 最大结温(T ) 150°C JMAX ESD警告 工作温度范围 −40°C 至 +125°C 存储温度范围 −65°C 至 +150°C ESD(静电放电)敏感器件。 引脚温度(焊接,10秒) 300°C 带电器件和电路板可能会在没有察觉的情况下放电。 尽管本产品具有专利或专有保护电路,但在遇到高能 注意,超出上述绝对最大额定值可能会导致器件永久性损 量ESD时,器件可能会损坏。因此,应当采取适当的 坏。这只是额定最值,并不能以这些条件或者在任何其它 ESD防范措施,以避免器件性能下降或功能丧失。 超出本技术规范操作章节中所示规格的条件下,推断器件 能否正常工作。长期在绝对最大额定值条件下工作会影响 器件的可靠性。 Rev. A | Page 5 of 16

AD5441 引脚配置和功能描述 PIN 1 VREF 1 8 VDD REF1 VINDICATOR 8 VDD RFB 2 AD5441 7 CLK GONFUDBT234 (NRTIAoOtD Pto5 V 4SIE4caW1le) 765 SLCDRLKI GIONUDT 34 (NToOt Pto V SIEcWale) 65 SLDRI 06492-004 N1.O CTTHOEENS NEEXCPTOESDE DT OP ATDH ES HGORUOLUDN DB EPLANE. 06492-003 图5. 8引脚LFCSP的引脚配置 图6. 8引脚MSOP的引脚配置 表6. 引脚功能描述 引脚编号 引脚名称 描述 1 V DAC基准电压输入引脚。建立DAC满量程电压。恒定的输入电阻与代码。 REF 2 R 内部匹配的反馈电阻。连接到外部运算放大器输出。 FB 3 I DAC电流输出,满量程输出比基准输入电压−V 小1 LSB。 OUT REF 4 GND 模拟地和数字地。 5 LD 负载选通,电平敏感数字输入。移位寄存器数据在低电平有效时传输到DAC寄存器。 有关工作参数,参见表3。 6 SRI 12位串行寄存器输入。数据以MSB优先方式直接加载到移位寄存器。多余的前导位被忽略。 7 CLK 时钟输入。数据在正边沿输入移位寄存器中。 8 V 正电源输入。额定工作范围为5 V ± 10%。 DD EP 裸露焊盘。裸露焊盘必须连接到接地层。 Rev. A | Page 6 of 16

AD5441 典型性能参数 0.5 0.5 TA=25°C TA=25°C 0.4 VREF=10V 0.4 VREF=10V VDD=3V VDD= 5V 0.3 0.3 0.2 0.2 B) 0.1 B) 0.1 S S L (L 0 L (L 0 N N I –0.1 I –0.1 –0.2 –0.2 –0.3 –0.3 ––00..45 06492-039 ––00..45 06492-040 0 500 1000 1500 2000 2500 3000 3500 4000 0 500 1000 1500 2000 2500 3000 3500 4000 CODE CODE 图7. INL与代码的关系,3 V 图10. INL与代码的关系,5 V 0.5 0.5 TA=25°C TA=25°C 0.4 VREF=10V 0.4 VREF=10V VDD=3V VDD= 5V 0.3 0.3 0.2 0.2 B) 0.1 B) 0.1 S S L L L ( 0 L ( 0 N N D –0.1 D –0.1 –0.2 –0.2 –0.3 –0.3 ––00..45 06492-037 ––00..45 06492-038 0 500 1000 1500 2000 2500 3000 3500 4000 0 500 1000 1500 2000 2500 3000 3500 4000 CODE CODE 图8. DNL与代码的关系,3 V 图11. DNL与代码的关系,5 V 0.25 100 MAXINL 0.20 0.15 75 0.10 Y NL (LSB) 0.050 EQUENC 50 I R F –0.05 25 –0.10 MININL ––00..1250 TVADD==2 55°VC 06492-042 0 0 12 3REFE4RENC5E VOL6TAGE7 8 9 10 –1.0 T–O0.T5AL UNADJU0STED ERROR0 (.5LSB) 1.0 06492-048 图9. INL与基准电压的关系,5 V 图12. 总不可调整误差直方图 Rev. A | Page 7 of 16

AD5441 4 0.050 TA = 25°C TA = 25°C VREF = 10V 0.045 VDD = 5V OP42 0.040 2 0.035 A) L (LSB) 0 RENT (µ 00..003205 N R I CU 0.020 VDD = 3V 0.015 –2 VDD = 5V 0.010 –4 0.0050 06492-044 –2000 –1000OP AMP OFF0SET, VOS (µV)1000 2000 06492-049 –60 –40 –20 0TEM2P0ERAT4U0RE (°6C0) 80 100 120 图13. 积分非线性误差与外部运算放大器的关系 图16. 电源电流与温度的关系 1400 50 1200 40 1000 RENT (µA) 800 F55 QUENCY 30 UR 600 RE 20 C F 400 10 2000 FFF800 06492-035 0 10k 100k FREQU1EMNCY (Hz) 10M 100M 0 FULL-SCALE 1TEMPERATURE 2COEFFICIENT (pp3m/°C) 06492-046 图14. 电源电流与时钟频率的关系 图17. 满量程输出温度系数直方图 0.20 5.34 6 TA = 25°C LDAC 5 0.18 5.32 4 0.16 5.30 3 A) 0.14 GE (V) 55..2286 TVVARD ED=F =2= 55 1°VC0V 210 CURRENT (µ 000...110208 TPUT VOLTA 555...222420 7RFISFINTOG 8E0D0GE ––––1234 V (V)LOAD 0.06 OU –5 5.18 –6 0.04 5.16 –7 0.0200 0.5 1.0 1.5INP2U.0T VO2.L5TAG3E.0 (V)3.5 4.0 4.5 5.006492-043 55..1142–0.2 0 0.2 0.4 TIM0.E6 (µs)0.8 1.0 1.2 1.4 –––8910 06492-033 图15. 电源电流与逻辑输入电压的关系 图18. 中间值转换 Rev. A | Page 8 of 16

AD5441 4 100 ALL BIOTNS TVAR E=F 2=5 °1C0V –8 VDD = 5V 80 –20 B) d ON ( –32 dB) 60 ENUATI –44 PSRR ( 40 T T A –56 20 ––8608 TVVARD ED=F = 2= 55 °1VC00mV rms 0 06492-027 100 1k F1R0EkQUENCY1 (0H0zk) 1M 10M 06492-045 1k 10k FREQU1E00NkCY (Hz) 1M 10M 图19. 基准乘法带宽 图20. PSRR与频率的关系 Rev. A | Page 9 of 16

AD5441 术语 相对精度(INL) 数字馈通 相对精度或端点非线性度是指DAC输出与通过DAC传递函 当器件未被选择时,器件数字输入端的高频逻辑活动可以 数的两个端点的直线之间的最大偏差。它是在调整零值和满 穿越器件以容性方式耦合,在I 引脚上产生噪声。此噪 OUT 量程后进行测量,通常用LSB或满量程读数的百分比表示。 声会从器件的输出端耦合到后续电路。这种噪声就是数字 馈通。 差分非线性(DNL) DNL指任意两个相邻码之间所测得变化值与理想的1 LSB变 乘法馈通误差 化值之间的差异。整个工作温度范围内最大−1 LSB的额定差 这是由向DAC中载入全0时从DAC基准输入以容性方式馈 分非线性可确保单调性。 通到DAC I 1引脚而引起的误差。 OUT 增益误差 总谐波失真(THD) 增益误差或满量程误差衡量理想DAC和实际器件输出之间的 DAC由交流基准电压源驱动。总谐波失真是指DAC输出的 输出误差。对于这些DAC,理想的最大输出为V − 1 LSB。 谐波均方根和与基波值之比。通常仅包括较低阶的谐波, REF 这些DAC的增益误差可通过外部电阻调整为零。 例如二次到五次谐波。 零值误差 根据最差情况下的R 进行计算 REF IZSE(LSB) = (RREF × ILKG × 4096)/VREF. 顺从电压范围 输出漏电流 器件提供额定特征的(输出)端电压最大范围。 输出泄露电流是指DAC梯形开关断开时流入其中的电流。 输出噪声频谱密度 对于I 端,可以通过向DAC中载入全0并测量I 电流来 OUT OUT 计算公式为 进行测量。 e = √4KTRB n 输出电容 其中: 从I 1到AGND的电容。 OUT K表示波尔兹曼常数(J/°K)。 数模转换毛刺脉冲 R表示电阻(Ω)。 输入状态变化时从数字输入注入到模拟输出的电荷量。数 T表示电阻温度(°K)。 模转换毛刺脉冲通常规定为毛刺的面积,用pA-s或nV-s表 B表示1 Hz带宽。 示,具体取决于毛刺是作为电流信号还是作为电压信号来 测量的。 Rev. A | Page 10 of 16

AD5441 参数定义 一般电路信息 电阻梯形网络或R (例如输入检查)的任何测试期间, FEEDBACK AD5441是一款具有低温度系数的12位乘法DAC,包含一 V 必须存在,才能接通这些串联开关。 DD 个R-2R电阻梯形网络、数据输入和控制逻辑以及两个数据 输出阻抗 寄存器。 类似于输出电容的情形,AD5441的输出电阻因数字输入 数字电路构成一个接口,串行数据可以在微处理器控制下 代码而异。纵观I 引脚定义,此电阻的阻值可能介于10 kΩ OUT 通过该接口载入12位移位寄存器,然后以并行方式传输到 (所有数字输入均为低电平时则只有反馈电阻)和7.5 kΩ(任何 12位DAC寄存器。 单个位逻辑为高电平时则为反馈电阻与大约30 kΩ的R-2R梯 形网络电阻并联)。静态精度和动态性能会受到这些变化的 AD5441的模拟部分包含一个反相R-2R梯形网络,该网络 影响。 由高度稳定(50 ppm/°C)的薄膜硅铬电阻和12对NMOS电流导 引开关组成(见图21)。这些开关将二进制加权电流导引到 应用信息 I 或GND;这会在每个梯形支路上产生恒流,与数字输 大多数应用中,线性度取决于I 以及处于相同电位的 OUT OUT 入代码无关。此恒流会在V 产生阻值为R的恒定输入电 GND引脚的电势。DAC连接到外部精密运算放大器的反相 REF 阻。V 输入可以由绝对最大额定值所述限制内的任何基 输入端。外部放大器的同相输入端应直接连接到地,无需 REF 准交直流电压或电流驱动。 常用的偏置电流补偿电阻(见图22和图24)。选定的放大器 应具有低输入偏置电流和低温度漂移。放大器的输入失调 10kΩ 10kΩ 10kΩ VREF 电压应通过零点校准调整为小于200 mV(小于10%的1 LSB)。 20kΩ 20kΩ 20kΩ 20kΩ 20kΩ 所有接地引脚均应连接到单个公用接地点,以避免形成接 S1 S2 S3 S12 * 地环路。V 电源应具有充分的旁路,从而保持低噪声水 DD GND 平。AD5441最好采用模拟电源和模拟地。 10kΩ IOUT 单极性二象限乘法 * RFEEDBACK AD5441最直接的应用是图22所示的二象限乘法配置。如果 BIT 1 (MSB) BIT2 BIT3 BIT 12 (LSB) DIGITAL INPUTS 参考输入信号替换为固定的直流基准电压,DAC输出会根 *THESE SWITCHES PERMANENTLY ON. N1.O STWEISTCHES SHOWN FOR DIGITAL INPUTS HIGH. 06492-021 据传递公式提供成正比的直流电压输出 V = −D/4096 × V OUT REF 图21. DAC简化电路图 其中: 12个输出电流导引NMOS FET开关与每个R-2R电阻串联。 D表示载入DAC寄存器中的十进制数据。 为了进一步在整个温度范围内确保器件精度,始终接通的 V 表示外部提供的基准电压源。 REF MOS开关与R-2R梯形网络的反馈电阻和端接电阻串联。图 21显示了串联开关的位置。 VDD R2 VDD RFB C1 IOUT1 VREF VREF AD5441 A1 R1 GND VOUT = 0 TO –VREF LD CLK SRI AGND µCONTROLLER NOTES 21..CIRF11 A PA1HN IADSS RAE2 H CUIOGSMHE DPS EPONENSELADYT AIIFOM NGP AL(1IIFpNIF EA TRDO.J U2SpTFM) MEANTY IBSE R REEQQUUIRIREEDD. 06492-023 图22. 单极性(二象限)运算 Rev. A | Page 11 of 16

AD5441 双极性四象限乘法 数字部分 图24显示了实现四象限乘法运算的建议电路。求和放大 AD5441的数字输入(SRI、LD和CLK)为TTL兼容。输入电 器将V 乘以2,并通过基准电压使输出发生偏移,使得 平影响从电源吸取的电流量;数字输入(V )通过跃迁区时 OUT1 IN 中间值数字输入代码2048令V 为0 V。DAC载入全0时, 出现峰值电源电流。有关电源电流与逻辑输入电压的关系 OUT2 负满量程电压为V 。DAC载入全1时,正满量程输出为 图,请参见图15。保持数字输入电平尽可能接近电源V REF DD −(V − 1 LSB)。因此,数字编码为偏移二进制。各个输入 和GND,可使电源功耗降到最低。通过精心设计布局和内 REF 数据和基准(或信号)值的电压输出传递公式如下 置输入保护电路,AD5441的数字输入具有防静电能力。图 23显示了输入保护二极管和串联电阻;每个数字输入端均 V = (D/2048 − 1) − V OUT2 REF 具有相同的输入结构。施加于输入端的高压静电电荷通过 其中: 正偏二极管分流到电源和接地轨。这些保护二极管设计用 D表示载入DAC寄存器中的十进制数据。 于在静电放电期间将输入端箝位至远低于危险电平。 V 表示外部提供的基准电压源。 REF VDD 接口逻辑信息 AD5441专门针对简化运算而设计。图2中的时序图展示了 5kΩ LD, CLK, SRI 输入寄存器加载序列。请注意,最高有效位(MSB)优先载 入。12位输入寄存器存满之后,LD会被短暂拉低,从将数 GND 06492-020 据传输至DAC寄存器。 图23. 数字输入保护 R3 20kΩ VDD R2 R5 20kΩ VDD RFB C1 R4 V±1R0EVF VREF AD5441 IOUT1 A1 10kΩ R1 GND A2 VOUT = –VREF TO +VREF LD CLK SRI AGND µCONTROLLER NOTES 1.R1 AND R2 ARE USED ONLY IF GAIN ADJUSTMENT IS REQUIRED. ADJUST R1 FOR VOUT = 0V WITH CODE 10000000 LOADED TO DAC. 2.MATCHING AND TRACKING IS ESSENTIAL FOR RESISTOR PAIRS 3.RCIF31 A PA1HN/AAD2S R EIS4 .C AO HMIGPEHN SSPAETEIODN A (M1PpFL ITFOIE R2p.F) MAY BE REQUIRED 06492-024 图24. 双极性(四象限)运算 Rev. A | Page 12 of 16

AD5441 外形尺寸 0.35 3.00 0.30 0.65 BSC BSC SQ 0.25 5 8 PIN 1 IANRDEEAX *EXPPAODSED 11..7644 (BOTTOM VIEW) 0.50 1.49 0.40 0.30 4 1 PIN 1 INDICATOR TOP VIEW 2.48 (R 0.2) 2.38 0.80 MAX 0.80 0.55 NOM 2.23 0.75 0.05 MAX 0.70 0.02 NOM SEATING PLANE 0.20 REF *FOTOHFER T PHPIIRNSO CDPOAETNRAF C ISGOHUNERNEAETTC.ITOINO NA NODF FTUHNEC ETXIOPON SDEEDS CPRAIDP TPILOENASS SEE RCETFIOERN TO 022808-B 图25. 8引脚引线框芯片级封装[LFCSP_WD] 3 mm x 3 mm,超薄体,双列引脚 (CP-8-3) 图示尺寸单位:mm 3.20 3.00 2.80 8 5 5.15 3.20 4.90 3.00 4.65 2.80 1 4 PIN 1 0.65 BSC 0.95 0.85 1.10 MAX 0.75 0.80 0.15 0.38 0.23 8° 0.60 0.00 0.22 0.08 0° 0.40 COPLANARITY SEATING 0.10 PLANE COMPLIANT TO JEDEC STANDARDS MO-187-AA 图26. 8引脚超小型封装[MSOP] (RM-8) 图示尺寸单位:mm 订购指南 型号1 INL (LSB) 温度范围 封装描述 封装选项 标识 AD5441BCPZ-R2 ±0.5 −40°C至+125°C 8引脚LFCSP_WD CP-8-3 DBD AD5441BCPZ-REEL7 ±0.5 −40°C至+125°C 8引脚LFCSP_WD CP-8-3 DBD AD5441BRMZ ±0.5 −40°C至+125°C 8引脚MSOP RM-8 DBC AD5441BRMZ-REEL7 ±0.5 −40°C至+125°C 8引脚MSOP RM-8 DBC 1 Z = 符合RoHS标准的器件。 Rev. A | Page 13 of 16

AD5441 注释 Rev. A | Page 14 of 16

AD5441 注释 Rev. A | Page 15 of 16

AD5441 注释 ©2008–2011 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D06492sc-0-3/11(A) Rev. A | Page 16 of 16

Datasheet下载

Datasheet下载