ICGOO在线商城 > 集成电路(IC) > 数据采集 - ADCs/DAC - 专用型 > AD1833AASTZ

- 型号: AD1833AASTZ

- 制造商: Analog

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

AD1833AASTZ产品简介:

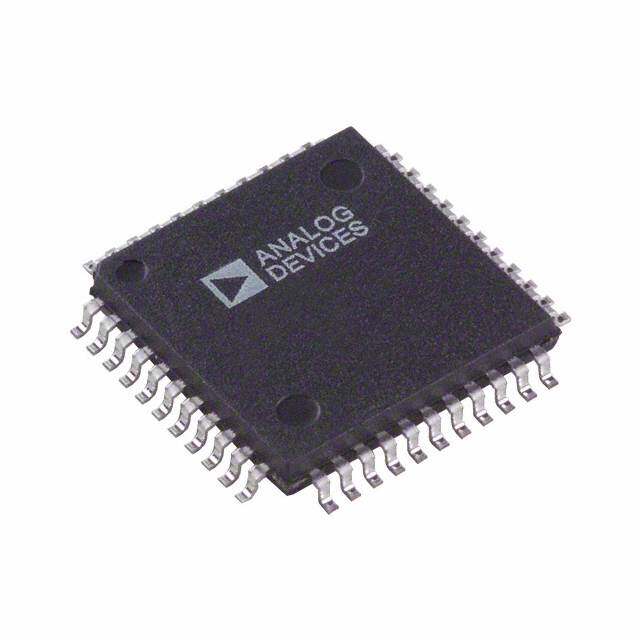

ICGOO电子元器件商城为您提供AD1833AASTZ由Analog设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 AD1833AASTZ价格参考。AnalogAD1833AASTZ封装/规格:数据采集 - ADCs/DAC - 专用型, DAC,音频 24 b 192k DSP,I²S 48-LQFP(7x7)。您可以下载AD1833AASTZ参考资料、Datasheet数据手册功能说明书,资料中有AD1833AASTZ 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC)半导体 |

| DAC输出端数量 | 6 |

| 描述 | IC DAC AUDIO 24BIT 6CH 48LQFP音频数/模转换器 IC 6 CH24 Bit 192 kHz Audio IC |

| 产品分类 | |

| 品牌 | Analog Devices |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 音频 IC,音频数/模转换器 IC,Analog Devices AD1833AASTZ- |

| 数据手册 | |

| 产品型号 | AD1833AASTZ |

| PCN过时产品 | |

| THD+噪声 | -95 dB |

| 产品培训模块 | http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=19145http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=18614http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=26125http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=26140http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=26150http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=26147 |

| 产品种类 | 音频数/模转换器 IC |

| 位数 | 24 |

| 供应商器件封装 | 48-LQFP(7x7) |

| 信噪比 | 120 dB |

| 分辨率 | 24 bit |

| 包装 | 托盘 |

| 商标 | Analog Devices |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装 | Tray |

| 封装/外壳 | 48-LQFP |

| 封装/箱体 | LQFP-48 |

| 工作温度 | -40°C ~ 85°C |

| 工作温度范围 | - 40 C to + 85 C |

| 工作电源电压 | 5 V |

| 工厂包装数量 | 250 |

| 建立时间 | - |

| 接口类型 | Serial |

| 数据接口 | DSP, I²S, 串行 |

| 标准包装 | 1 |

| 电压源 | 模拟和数字 |

| 电源电流 | 90 mA |

| 系列 | AD1833A |

| 转换器数 | 6 |

| 转换器数量 | 6 |

| 转换速率 | 192 kHz |

| 输出数和类型 | 12 电压,单极 |

| 通道数量 | 6 Channel |

| 采样率(每秒) | 96k |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

Multichannel, (cid:1) (cid:2) 24-Bit, 192 kHz, - DAC AD1833A FEATURES FUNCTIONAL BLOCK DIAGRAM 5 V Stereo Audio System with 3.3 V Tolerant Digital Interface DVDD1 DVDD2 ZERO FLAGS AVDD Supports 96 kHz Sample Rates on 6 Channels and 192 kHz on 2 Channels CDATA OUTLP1 Supports 16-/20-/24-Bit Word Lengths SPI INTERPOLATOR DAC OUTLN1 Multibit (cid:1)-(cid:2) Modulators with CLATCH PORT E CCLK OUTLP2 Perfect Differential Linearity Restoration for INTERPOLATOR DAC OUTLN2 Reduced Idle Tones and Noise Floor MCLK OUTLP3 Data Directed Scrambling DACs—Least Sensitive to RESET FILTTER INTERPOLATOR DAC OUTLN3 Jitter L/RCLK ENGINE OUTRP3 Differential Output for Optimum Performance BCLK INTERPOLATOR DAC OUTRN3 D–9A4C dsB S TigHnDa l+-t oN-—No6i-sCeh aannnde Dl yMnoadmeic Range:110 dB SSDDIINN12 PDOAETRAT INTERPOLATOR DAC OOUUTTRRPN22 –95 dB THD + N—2-Channel Mode SDIN3 INTERPOLATOR DAC OOUUTTRRPN11 On-Chip Volume Control per Channel with 1024-Step SOUT Linear Scale AD1833A Software Controllable Clickless Mute L FILTR FILTD Digital De-emphasis Processing DGND AGND Supports 256(cid:3) f , 512(cid:3) f , and 768(cid:3) f Master S S S Clock Modes O Power-Down Mode Plus Soft Power-Down Mode Flexible Serial Data Port with Right-Justified, Left-Justified, I2S Compatible, and DSP Serial Port Modes Supports Packed Data Mode and TDM Mode 48-Lead LQFP Plastic Package S The AD1833A is fully compatible with all known DVD formats, accommodating word lengths of up to 24 bits at sample rates of APPLICATIONS 48kHz and 96 kHz on all six channels while supporting a 192kHz DVD Video and Audio Players sample rate on two channels. It also provides the Redbook stan- Home Theater Systems B dard 50ms/15 ms digital de-emphasis filters at sample rates of Automotive Audio Systems 32kHz, 44.1kHz, and 48kHz. Set-Top Boxes The AD1833A has a very flexible serial data input port that Digital Audio Effects Processors allows glueless interconnection to a variety of ADCs, DSP chips, AES/EBU receivers, and sample rate converters. It can be con- O figured in right-justified, left-justified, I2S, or DSP serial port GENERAL DESCRIPTION compatible modes. The AD1833A accepts serial audio data in MSB The AD1833A is a complete, high performance, single-chip, first, twos complement format. The AD1833A can be operated multichannel, digital audio playback system. It features six audio from a single 5 V power supply; it also features a separate supply playback channels, each comprising a high performance digital pin for its digital interface that allows it to be interfaced to devices interpolation filter, a multibit S-D modulator featuring Analog using 3.3 V power supplies. Devices’ patented technology, and a continuous-time voltage-out analog DAC section. Other features include an on-chip clickless The AD1833A is fabricated on a single monolithic integrated attenuator and mute capability for each channel, programmed circuit and is housed in a 48-lead LQFP package for operation through an SPI compatible serial control port. from –40∞C to +85∞C. REV.0 Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. under any patent or patent rights of Analog Devices. Trademarks and Tel: 781/329-4700 www.analog.com registered trademarks are the property of their respective companies. Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

AD1833A–SPECIFICATIONS TEST CONDITIONS, UNLESS OTHERWISE NOTED* Supply Voltages (AV , DV ) 5 V DD DDX Ambient Temperature 25∞C Input Clock 12.288 MHz, (8(cid:3) Mode) Input Signal Nominally 1 kHz, 0 dBFS (Full-Scale) Input Sample Rate 48 kHz Measurement Bandwidth 20 Hz to 20 kHz Word Width 24 Bits Load Capacitance 100 pF Load Impedance 10 kW *Performance is identical for all channels (except for the Interchannel Gain E Mismatch and Interchannel Phase Deviation specifications). Parameter Min Typ Max Unit Test Conditions T ANALOG PERFORMANCE DIGITAL-TO-ANALOG CONVERTERS Dynamic Range (20 Hz to 20 kHz, –60 dBFS Input) with A-Weighted Filter E AD1833AA 106.5 110.0 dB AD1833AA 110.5 dB f = 96 kHz S AD1833AC 107.0 dB Total Harmonic Distortion + Noise –95 –89 dB Two channels active L –94 dB Six channels active –95 dB 96 kHz, two channels active –94 dB 96 kHz, six channels active SNR O110 dB Interchannel Isolation 108 dB DC Accuracy Gain Error ±3 % Interchannel Gain Mismatch 0.2 % Gain Drift S 80 ppm/∞C Interchannel Crosstalk (EIAJ Method) –120 dB Interchannel Phase Deviation ±0.1 Degrees Volume Control Step Size (1023 Linear Steps) 0.098 % Volume Control Range (Max Attenuation)B +63.5 (0.098) dB (%) Mute Attenuation –63.5 (0.098) dB (%) De-emphasis Gain Error ±0.1 dB Full-Scale Output Voltage at Each Pin (Single-Ended) 1 (2.8) V rms (V p-p) Output Resistance Measured DOifferentially 150 W Common-Mode Output Volts 2.2 V DAC INTERPOLATION FILTER—8(cid:1) Mode (48 kHz) Pass Band 21.768 kHz Pass-Band Ripple ±0.01 dB Stop Band 24 kHz Stop-Band Attenuation 70 dB Group Delay 510 ms DAC INTERPOLATION FILTER—4(cid:1) Mode (96 kHz) Pass Band 37.7 kHz Pass-Band Ripple ±0.03 dB Stop Band 55.034 kHz Stop-Band Attenuation 70 dB Group Delay 160 ms DAC INTERPOLATION FILTER—2(cid:1) Mode (192 kHz) Pass Band 89.954 kHz Pass-Band Ripple ±1 dB Stop Band 104.85 kHz Stop-Band Attenuation 70 dB Group Delay 140 ms REV. 0 –2–

AD1833A Parameter Min Typ Max Unit Test Conditions DIGITAL I/O Input Voltage HI 2.4 V Input Voltage LO 0.8 V Output Voltage HI DV –0.4 V DD2 Output Voltage LO 0.4 V POWER SUPPLIES Supply Voltage (AV and DV ) 4.5 5 5.5 V DD DD1 Supply Voltage (DV ) 3.3 DV V DD2 DD1 Supply Current I 38.5 42 mA ANALOG Supply Current I 42 48 mA Active DIGITAL E 2 mA Power-Down Power Supply Rejection Ratio 1 kHz 300 mV p-p Signal at Analog Supply Pins –60 dB 20 kHz 300 mV p-p Signal at Analog Supply Pins –50 dB T Specifications subject to change without notice. DIGITAL TIMING (Guaranteed over –40(cid:4)C to +85(cid:4)C, AV = DV = 5 V (cid:5) 10%) DD DD E Parameter Min Max Unit Comments MASTER CLOCK AND RESET t MCLK LO (All Modes)* 15 ns 24 MHz clock, clock doubler bypassed ML L t MCLK HI (All Modes)* 15 ns 24 MHz clock, clock doubler bypassed MH t PD/RST LO 20 ns PDR SPI PORT t CCLK HI Pulsewidth 20 O ns CCH t CCLK LO Pulsewidth 20 ns CCL t CCLK Period 80 ns CCP t CDATA Setup Time 10 ns To CCLK rising CDS t CDATA Hold Time 10 ns From CCLK rising CDH S t CLATCH Setup 10 ns To CCLK rising CLS t CLATCH Hold 10 ns From CCLK rising CLH DAC SERIAL PORT t BCLK HI B 15 ns DBH t BCLK LO 15 ns DBL t L/RCLK Setup 10 ns To BCLK rising DLS t L/RCLK Hold 10 ns From BCLK rising DLH t SDATA SetuOp 10 ns To BCLK rising DDS t SDATA Hold 15 ns From BCLK rising DDH TDM MODE MASTER t BCLKTDM Delay 20 ns From MCLK rising TMBD t FSTDM Delay 10 ns From BCLKTDM rising TMFSD t SDIN1 Setup 15 ns To BCLKTDM falling TMDDS t SDIN1 Hold 15 ns From BCLKTDM falling TMDDH TDM MODE SLAVE f BCLKTDM Frequency 256 (cid:1) f TSB S t BCLKTDM High 20 ns TSBCH t BCLKTDM Low 20 ns TSBCL t FSTDM Setup 10 ns To BCLKTDM falling TSFS t FSTDM Hold 10 ns From BCLKTDM falling TSFH t SDIN1 Setup 15 ns To BCLKTDM falling TSDDS t SDIN1 Hold 15 ns From BCLKTDM falling TSDDH AUXILIARY INTERFACE t L/RCLK Delay 10 ns From BCLK falling AXLRD t Data Delay 10 ns From BCLK falling AXDD t AUXBCLK Delay 20 ns From MCLK rising AXBD *MCLK symmetry must be better than 60:40 or 40:60. Specifications subject to change without notice. REV. 0 –3–

AD1833A tMH MCLK tML PD/RST tPDR Figure 1.MCLK and RESET Timing tCLS tCLH t t CCH CCL CLATCH tCCP E CCLK t t CDS CDH T CIN D15 D14 D9 D8 D0 Figure 2.SPI Port Timing E t DBH BCLK t L DBL tDLS tDLH L/RCLK O t DDS SDATA LEFT-JUSTIFIED MSB MSB-1 MODE t DDH S t DDS SDATA I2S MODE MSB t DDH B tDDS tDDS SDATA RIGHT-JUSTIFIED MSB LSB MODE t t DDH DDH Figure 3.Serial Port Timing O MCLK tTMBD tTSBCL tTSBCH BCLKTDM tTMFSD FSTDM tTSFS tTSFH tTMDDS tTMDDH SDIN1 MSB tTSDDS tTSDDH Figure 4.TDM Master and Slave Mode Timing –4– REV. 0

AD1833A MCLK tAXBD AUXBCLK tAXLRD AUXL/RCLK E tAXDD MSB AUX DATA T Figure 5.Auxiliary Interface Timing E ABSOLUTE MAXIMUM RATINGS* LQFLP, qJA Thermal Impedance . . . . . . . . . . . . . . . . . 91∞C/W (TA = 25∞C, unless otherwise noted.) Lead Temperature, Soldering AVDD, DVDDX to AGND, DGND . . . . . . . . –0.3 V to +6.5 V Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . . . 215∞C AGND to DGND . . . . . . . . . . . . . . . . . . . . –0.3 V to +0.3 V Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220∞C Digital I/O Voltage to DGND . . . . . –0.3 V to DV + 0.3 VO DD2 *Stresses above those listed under Absolute Maximum Ratings may cause perma- Analog I/O Voltage to AGND . . . . . . –0.3 V to AVDD + 0.3 V nent damage to the device. This is a stress rating only; functional operation of the Operating Temperature Range device at these or any other conditions above those listed in the operational Industrial (A Version) . . . . . . . . . . . . . . . –40∞C to +85∞C sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Only one absolute Storage Temperature Range . . . . . . . . . . . . –65S∞C to +150∞C maximum rating may be applied at any one time. Maximum Junction Temperature . . . . . . . . . . . . . . . . 150∞C ORDERING GUIDE B Model Temperature Range Package Description Package Option AD1833AAST –40∞C to +85∞C Low Profile Quad Flat Package ST-48 AD1833ACST –40∞C to +85∞C Low Profile Quad Flat Package ST-48 O EVAL-AD1833AEB Evaluation Board AD1833AAST-REEL –40∞C to +85∞C Low Profile Quad Flat Package ST-48 AD1833ACST-REEL –40∞C to +85∞C Low Profile Quad Flat Package ST-48 CAUTION ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD1833A features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality. REV. 0 –5–

AD1833A PIN CONFIGURATION OUTLN2 OUTLP2OUTLN3OUTLP3 AVDDFILTDFILTRAGNDOUTRP3OUTRN3 OUTRP2OUTRN2 48 47 46 45 44 43 42 41 40 39 38 37 OUTLP1 1 36 OUTRP1 PIN 1 OUTLN1 2 IDENTIFIER 35 OUTRN1 AVDD 3 34 AVDD AVDD 4 33 AVDD AGND 5 32 AGND AD1833A AGND 6 31 AGND AGND 7 (NToOt Pto V SIEcaWle) 30 AGND DGND 8 29 DGND E DVDD1 9 28 DVDD2 ZEROA 10 27 RESET ZERO3R 11 26 ZERO1L ZERO3L 12 25 ZERO1R T 13 14 15 16 17 18 19 20 21 22 23 24 RHA KK KK123 TL ZERO2CLATCCDAT CCLL/RCL BCLMCLSDINSDINSDIN SOUZERO2 E PIN FUNCTION DESCRIPTIONS Pin No. Mnemonic IN/OUT Description L 1 OUTLP1 O DAC 1 Left Channel Positive Output. 2 OUTLN1 O DAC 1 Left Channel Negative Output. 3, 4, 33, 34, 44 AV Analog Supply. DD O 5, 6, 7, 30, 31, 32, 41 AGND Analog Ground. 8, 29 DGND Digital Ground. 9 DV Digital Supply to Core Logic. DD1 10 ZEROA O Flag to Indicate Zero Input on All Channels. S 11 ZERO3R O Flag to Indicate Zero Input on Channel 3 Right. 12 ZERO3L O Flag to Indicate Zero Input on Channel 3 Left. 13 ZERO2R O Flag to Indicate Zero Input on Channel 2 Right. 14 CLATCH I B Latch Input for Control Data (SPI Port). 15 CDATA I Serial Control Data Input (SPI Port). 16 CCLK I Clock Input for Control Data (SPI Port). 17 L/RCLK I/O Left/Right Clock for DAC Data Input; FSTDM Input in TDM Slave Mode; O FSTDM Output in TDM Master Mode. 18 BCLK I/O Bit Clock for DAC Data Input; BCLKTDM Input in TDM Slave Mode; BCLKTDM Output in TDM Master Mode. 19 MCLK I Master Clock Input. 20 SDIN1 I Data Input for Channel 1 Left/Right (Data Stream Input in TDM and Packed Modes). 21 SDIN2 I/O Data Input for Channel 2 Left/Right (L/RCLK Output to Auxiliary DAC in TDM Mode). 22 SDIN3 I/O Data Input for Channel 3 Left/Right (BCLK Output to Auxiliary DAC in TDM Mode). 23 SOUT O Auxiliary I2S Output (Available in TDM Mode). 24 ZERO2L O Flag to Indicate Zero Input on Channel 2 Left. 25 ZERO1R O Flag to Indicate Zero Input on Channel 1 Right. 26 ZERO1L O Flag to Indicate Zero Input on Channel 1 Left. 27 RESET I Power-Down and Reset Control. 28 DV Power Supply to Output Interface Logic. DD2 35 OUTRN1 O DAC 1 Right Channel Negative Output. 36 OUTRP1 O DAC 1 Right Channel Positive Output. 37 OUTRN2 O DAC 2 Right Channel Negative Output. 38 OUTRP2 O DAC 2 Right Channel Positive Output. 39 OUTRN3 O DAC 3 Right Channel Negative Output. REV. 0 –6–

AD1833A PIN FUNCTION DESCRIPTIONS (continued) Pin No. Mnemonic IN/OUT Description 40 OUTRP3 O DAC 3 Right Channel Positive Output. 42 FILTR Reference/Filter Capacitor Connection. Recommend 0.1 mF/10 mF decouple to analog ground. 43 FILTD Filter Capacitor Connection. Recommend 0.1 mF/10 mF decouple to analog ground. 45 OUTLP3 O DAC 3 Left Channel Positive Output. 46 OUTLN3 O DAC 3 Left Channel Negative Output. 47 OUTLP2 O DAC 2 Left Channel Positive Output. 48 OUTLN2 O DAC 2 Left Channel Negative Output. E DEFINITION OF TERMS Gain Error Dynamic Range With a near full-scale input, the ratio of actual output to expected T The ratio of a full-scale input signal to the integrated input noise in output, expressed as a percentage. the pass band (20 Hz to 20 kHz), expressed in decibels. Dynamic Interchannel Gain Mismatch range is measured with a –60 dB input signal and is equal to With identical near full-scale inputs, the ratio of outputs of the (S/[THD + N]) +60 dB. Note that spurious harmonics are below two stereo chanEnels, expressed in decibels. the noise with a –60 dB input, so the noise level establishes the dynamic range. The dynamic range is specified with and without Gain Drift Change in response to a nearly full-scale input with a change in an A-Weight filter applied. Signal to (Total Harmonic Distortion + Noise) tempLerature, expressed as parts-per-million (ppm/∞C). Crosstalk (EIAJ Method) [S/(THD + N)] The ratio of the root-mean-square (rms) value of the fundamental Ratio of response on one channel with a grounded input to a input signal to the rms sum of all other spectral components in full-scale 1 kHz sine wave input on the other channel, expressed O the pass band, expressed in decibels. in decibels. Pass Band Power Supply Rejection The region of the frequency spectrum unaffected by the attenuation With no analog input, signal present at the output when a of the digital decimator’s filter. 300 mV p-p signal is applied to the power supply pins, expressed S in decibels of full scale. Pass-Band Ripple The peak-to-peak variation in amplitude response from equal- Group Delay amplitude input signal frequencies within the pass band, expressed Intuitively, the time interval required for an input pulse to appear in decibels. B at the converter’s output, expressed in ms. More precisely, the derivative of radian phase with respect to the radian frequency at Stop Band a given frequency. The region of the frequency spectrum attenuated by the digital decimator’s filter to the degree specified by stop-band attenuation. Group Delay Variation The difference in group delays at different input frequencies. O Specified as the difference between the largest and the smallest group delays in the pass band, expressed in ms. REV. 0 –7–

AD1833A–Typical Performance Characteristics 0.010 0.10 0.008 0.08 0.006 0.06 0.004 0.04 0.002 0.02 dB 0 dB 0 –0.002 –0.02 –0.004 –0.04 –0.006 –0.06 –0.008 –0.08 E –0.010 –0.10 0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 2.0 0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 Hz (cid:3)104 Hz (cid:3)104 TPC 1.Pass-Band Response, 8(cid:1) Mode TPC 4.Pass-BandT Response, 4(cid:1) Mode 10 0.5 E 0 0.4 –10 0.3 –20 L0.2 –30 0.1 –40 dB dB 0 –50 O –0.1 –60 –0.2 –70 –80 –0.3 –90 –0.4 S –100 –0.5 2.00 2.05 2.10 2.15 2.20 2.25 2.30 2.35 2.40 2.45 2.50 0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 Hz (cid:3)104 Hz (cid:3)104 TPC 2.Transition Band Response, 8(cid:1) Mode TPC 5.40 kHz Pass-Band Response, 4(cid:1) Mode B 10 0 0 O –20 –10 –40 –20 –30 –60 –40 B B d –80 d –50 –100 –60 –70 –120 –80 –140 –90 –160 –100 0 0.5 1.0 1.5 2.0 2.5 3.0 4.0 4.2 4.4 4.6 4.8 5.0 5.2 5.4 5.6 5.8 6.0 Hz (cid:3)105 Hz (cid:3)104 TPC 3.Complete Response, 8(cid:1) Mode TPC 6.Transition Band Response, 4(cid:1) Mode REV. 0 –8–

AD1833A 10 0 0 –20 –10 –40 –20 –30 –60 dB –80 dB –40 –50 –100 –60 –70 –120 –80 –140 E –90 –160 –100 0 0.5 1.0 1.5 2.0 2.5 3.0 0.80 0.85 0.90 0.95 1.00 1.05 1.10 1.15 1.20 Hz (cid:3)105 Hz (cid:3)105 TPC 7.Complete Response, 4(cid:1) Mode TPC 9.TransitioTn Band Response, 2(cid:1) Mode 2.0 E 0 1.5 –20 1.0 L–40 0.5 –60 dB 0 dB –80 O –0.5 –100 –1.0 –120 –1.5 –140 S –2.0 –160 0 1 2 3 4 5 6 7 8 0 0.5 1.0 1.5 2.0 Hz (cid:3)104 Hz (cid:3)105 TPC 8.80 kHz Pass-Band Response, 2(cid:1) Mode TPC 10.Complete Response, 2(cid:1) Mode B O REV. 0 –9–

AD1833A FUNCTIONAL DESCRIPTION rate, only one doubling stage is used. In each case, the input Device Architecture sample frequency is increased to 384 kHz (IMCLK/64). The The AD1833A is a six-channel audio DAC featuring multibit ZOH holds the interpolator samples for upsampling by the sigma-delta (S-D) technology. The AD1833A features three stereo modulator. This is done at a rate 16 times the interpolator converters (providing six channels); each stereo channel is con- output sample rate. trolled by a common bit-clock (BCLK) and synchronization Modulator signal (L/RCLK). The modulator is a 6-bit, second order implementation and uses General Overview data scrambling techniques to achieve perfect linearity. The modu- The AD1833A is designed to run with an internal MCLK lator samples the output of the interpolator stage(s) at arate of (IMCLK) of 24.576MHz and a modulator rate of 6.144MHz (IMCLK/4). (i.e., IMCLK/4). From this IMCLK frequency, sample rates of 48kHz and 96kHz can be achieved on six channels or 192kHz OPERATING FEATURES E can be achieved on two channels. The internal clock should never SPI Register Definitions be run at a higher frequency but may be reduced to achieve The SPI port allows flexible control of the device’s programmable lower sampling rates, i.e., for a sample rate of 44.1 kHz, the appro- functions. It is organized around nine registers: six individual channel priate internal MCLK is 22.5792 MHz. The modulator rate scales volume registers and three conTtrol registers. Each write operation in proportion with the MCLK scaling. to the AD1833A SPI control port requires 16 bits of serial data in MSB-first format. The four most significant bits are used to Interpolator select one of nine registers (seven register addresses are reserved), The interpolator consists of as many as three stages of sample and the bottom 10 bEits are written to that register. This allows a rate doubling and half-band filtering followed by a 16-sample write to one of the nine registers in a single 16-bit transaction. The zero order hold (ZOH). The sample rate doubling is achieved SPI CCLK signal is used to clock in the data. The incoming by zero stuffing the input samples, and a digital half-band filter data should change on the falling edge of this signal and remain is used to remove any images above the band of interest and to valid duriLng the rising edge. At the end of the 16CCLK periods, bring the zero samples to their correct values. the CLATCH signal should rise to latch the data internally into The interpolator output must always be at a rate of IMCLK/64. the AD1833A (see Figure 2). Depending on the interpolation rates selected, one, two, or all OThe serial interface format used on the control port uses a 16-bit three stages of doubling may be switched in. This allows for serial word, as shown in Table I. The 16-bit word is divided into three different sample rate inputs for any given IMCLK. For an several fields: Bits 15 through 12 define the register address, Bits11 IMCLK of 24.576 MHz, all three doubling stages are used with and 10 are reserved and must be programmed to 0, and Bits9 a 48 kHz input sample rate; with a 96 kHz input sample rate, only through 0 are the data field (which has specific definitions, two doubling stages are used; and with a 192 kHz inpuSt sample depending on the register selected). B Table I. Control Port Map Register Address Reserved1 Data Field 152 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 NOTES O 1Must be programmed to zero. 2Bit 15 = MSB. Bit 15 Bit 14 Bit 13 Bit 12 Register Function 0 0 0 0 DAC Control 1 0 0 0 1 DAC Control 2 0 0 1 0 DAC Volume 1 0 0 1 1 DAC Volume 2 0 1 0 0 DAC Volume 3 0 1 0 1 DAC Volume 4 0 1 1 0 DAC Volume 5 0 1 1 1 DAC Volume 6 1 0 0 0 DAC Control 3 1 0 0 1 Reserved 1 0 1 0 Reserved 1 0 1 1 Reserved 1 1 0 0 Reserved 1 1 0 1 Reserved 1 1 1 0 Reserved 1 1 1 1 Reserved REV. 0 –10–

AD1833A Table II. DAC Control Register 1 Function Data-Word Power-Down Interpolator Address Reserved1 De-emphasis Serial Mode Width RESET Mode 15–12 11 10 9–8 7–5 4–3 2 1–0 0000 0 0 00 = None 000 = I2S 00 = 24 Bits 0 = Normal 00 = 8(cid:1) (48 kHz)2 01 = 44.1 kHz 001 = RJ 01 = 20 Bits 1 = PWRDWN 01 = 2(cid:1) (192 kHz)2 10 = 32.0 kHz 010 = DSP 10 = 16 Bits 10 = 4(cid:1) (96 kHz)2 11 = 48.0 kHz 011 = LJ 11 = Reserved 11 = Reserved 100 = Pack Mode 1 (256) 101 = Pack Mode 2 (128) E 110 = TDM Mode 111 = Reserved NOTES T 1Must be programmed to zero. 2For IMCLK = 24.576 MHz. DAC CONTROL REGISTER 1 DAC Word WiEdth De-emphasis The AD1833A will accept input data in three separate word- The AD1833A has a built-in de-emphasis filter that can be used lengths—16 bits, 20 bits, and 24 bits. The word length may be to decode CDs that have been encoded with the standard selected by writing to Control Bits 4 and 3 in DAC Control Redbook 50 ms/15 ms emphasis response curve. Three curves are RegiLster 1 (see Table V). available, one each for 32 kHz, 44.1 kHz, and 48 kHz sampling rates. The filters may be selected by writing to Control Bits 9 Table V. Word Length Settings and 8 in DAC Control Register 1 (see Table III). O Bit 4 Bit 3 Word Length Table III. De-emphasis Settings 0 0 24 Bits 0 1 20 Bits Bit 9 Bit 8 De-emphasis 1 0 16 Bits 0 0 Disabled S 1 1 Reserved 0 1 44.1 kHz 1 0 32 kHz Power-Down Control 1 1 48 kHz The AD1833A can be powered down by writing to Control Bit 2 B in DAC Control Register 1 (see Table VI). Data Serial Interface Mode The AD1833A’s serial data interface is designed to accept data Table VI. Power-Down Control in a wide range of popular formats including I2S, right-justified Bit 2 Power-Down Setting (RJ), left-justified (LJ), and flexible DSP modes. The L/RCLK O pin acts as the word clock (or frame sync) to indicate sample 0 Normal Operation interval boundaries. The BCLK defines the serial data rate 1 Power-Down Mode while the data is input on the SDIN1–SDIN3 pins. The serial mode settings may be selected by writing to Control Bits 7 Interpolator Mode through 5 in the DAC Control Register 1 (see Table IV). The AD1833A’s DAC interpolators can be operated in one of three modes—8(cid:1), 4(cid:1), or 2(cid:1)— then correspond to 48 kHz, 96kHz, Table IV. Data Serial Interface Mode Settings and 192 kHz modes, respectively (for IMCLK = 24.576 MHz). The interpolator mode may be selected by writing to Control Bits 1 Bit 7 Bit 6 Bit 5 Serial Mode and 0 in DAC Control Register 1 (see Table VII). 0 0 0 I2S 0 0 1 Right Justify Table VII. Interpolator Mode Settings 0 1 0DSP Bit 1 Bit 0 Interpolator Mode 0 1 1 Left Justify 1 0 0 Packed Mode 1 (256) 0 0 8x (48 kHz)* 1 0 1 Packed Mode 2 (128) 0 1 2x (192 kHz)* 1 1 0TDM Mode 1 0 4x (96 kHz)* 1 1 1 Reserved 1 1 Reserved *For IMCLK = 24.576 MHz. REV. 0 –11–

AD1833A DAC CONTROL REGISTER 2 DAC CONTROL REGISTER 3 DAC Control Register 2 contains individual channel mute Stereo Replicate controls for each of the six DACs. Default operation (bit = 0) is The AD1833A allows the stereo information on Channel1 muting off. Bits 9 through 6 of Control Register 2 are reserved (SDIN1—Left 1 and Right 1) to be copied to Channels 2 and3 and should be programmed to zero (see Table VIII). (Left/Right 2 and Left/Right 3). These signals can be used in an external summing amplifier to increase potential signal SNR. Stereo replicate mode can be enabled by writing to control Bit5 (see TableXI). Note that replication is not reflected in the zero flag status. Table VIII. DAC Control Register 2 E Function Address Reserved* Reserved* Mute Control 15–12 11 10 9–6 5 4 3 2 T 1 0 0001 0 0 0 Channel 6 Channel 5 Channel 4 Channel 3 Channel 2 Channel 1 0 = Mute Off 0 = Mute Off 0 = Mute Off 0 = Mute Off 0 = Mute Off 0 = Mute Off 1 = Mute On 1 = Mute On 1 = Mute On 1 = Mute On 1 = Mute On 1 = Mute On E *Must be programmed to zero. Table IX. Muting Control L Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Muting X X X X X 1 Mute Channel 1 X X X X 1 O X Mute Channel 2 X X X 1 X X Mute Channel 3 X X 1 X X X Mute Channel 4 X 1 X X X X Mute Channel 5 1 X X X X X Mute Channel 6 S Table X. DAC Control Register 3 B Function Stereo Replicate Address Reserved* Reserved* (192 kHz) MCLK Select Zero Detect Reserved* TDM Mode 15–12 11 10 9–6 O 5 4–3 2 1 0 1000 0 0 0 0 = Normal 00 = IMCLK = MCLK (cid:1) 2 0 = Active High 0 0 = Master 1 = Replicate 01 = IMCLK = MCLK (cid:1) 1 1 = Active Low 1 = Slave 10 = IMCLK = MCLK (cid:1) 2/ 3 *Must be programmed to zero. Table XI. Stereo Replicate Bit 5 Stereo Mode 0 Normal 1 Channel 1 Data Replicated on Channels 2 and 3 REV. 0 –12–

AD1833A MCLK Select The AD1833A allows the matching of available external MCLK a global zero flag that indicates all channels contain zero data. frequencies to the required internal MCLK rate. The MCLK The polarity of the zero signal is programmable by writing to modification factor can be selected from 2, 1, or 2/ by writing to Control Bit 2 (see Table XIII). In right-justified mode, the six 3 Bit 4 and Bit 3 of Control Register 3. Internally, the AD1833A individual channel flags are best used as three stereo zero flags requires an MCLK of 24.576 MHz for sample rates of 48 kHz, by combining pairs of them through suitable logic gates. Then, 96 kHz, and 192 kHz. In the case of 48 kHz data with an when both the left and right inputs are zero for 1024 clock cycles, MCLK of 256 (cid:1) f , a clock doubler is used, whereas with an i.e., a stereo zero input for 1024 sample periods, the combined S MCLK of 768 (cid:1) f , a divide-by-3 block ((cid:2)3) is first implemented result of the two individual flags will become active, indicat- S followed by a clock doubler. With an MCLK of 512 (cid:1) f , the ing a stereo zero. S MCLK is passed through unmodified (see Table XII). Table XIII. Zero Detect E Table XII. MCLK Settings Bit 2 Channel Zero Status Bit 4 Bit 3 Modification Factor 0 Active High 0 0 MCLK (cid:1) 2 Internally 1 Active Low T 0 1 MCLK (cid:1) 1 Internally 1 0 MCLK (cid:1) 2/ Internally DAC Volume Control Registers 3 1 1 Reserved The AD1833A has six volume control registers, one for each of the six DAC chEannels. Volume control is exercised by writing to Channel Zero Status the relevant register associated with each DAC. This setting is The AD1833A provides individual logic output status indicators used to attenuate the DAC output. Full-scale setting (all 1s) is when zero data is sent to a channel for 1024 or more consecutive equivalent to zero attenuation (see Table XV). sample periods in all modes except right-justified. There is also L Table XIV. MCLK vs. Sample Rate Selection Sampling Rate Interpolator Mode Internal MCLK O Suitable External MCLK Frequencies (MHz) f (kHz) Required Required (MHz) MCLK (cid:3) 2 MCLK (cid:3) 1 MCLK (cid:3) 2/ S 3 32 8(cid:1) 64 4(cid:1) 16.384 8192 16.384 24.576 128 2(cid:1) S 44.1 8(cid:1) 88.2 4(cid:1) 22.5792 11.2896 22.5792 33.8688 176.4 2(cid:1) B 48 8(cid:1) 96 4(cid:1) 24.576 12.288 24.576 36.864 192 2(cid:1) O Table XV. Volume Control Registers Address Reserved* Volume Control 15–12 11 10 9–0 0 0 1 0 0 0 Channel 1 Volume Control (OUTL1) 0 0 1 1 Channel 2 Volume Control (OUTR1) 0 1 0 0 Channel 3 Volume Control (OUTL2) 0 1 0 1 Channel 4 Volume Control (OUTR2) 0 1 1 0 Channel 5 Volume Control (OUTL3) 0 1 1 1 Channel 6 Volume Control (OUTR3) *Must be programmed to zero. REV. 0 –13–

AD1833A I2S Timing to clock in the data. The first bit of data appears on the SDINx I2S timing uses an L/RCLK to define when the data being trans- lines when the L/RCLK toggles. The data is written MSB first mitted is for the left channel and when it is for the right channel. and is valid on the rising edge of the bit clock. The L/RCLK is low for the left channel and high for the right Right-Justified Timing channel. A bit clock running at 64 (cid:1) f is used to clock in the data. S Right-justified (RJ) timing uses an L/RCLK to define when the There is a delay of 1 bit clock from the time the L/RCLK signal data being transmitted is for the left channel and when it is for changes state to the first bit of data on the SDINx lines. The data the right channel. The L/RCLK is high for the left channel and is written MSB first and is valid on the rising edge of the bit clock. low for the right channel. A bit clock running at 64 (cid:1) f is used S Left-Justified Timing to clock in the data. The first bit of data appears on the SDINx Left-justified (LJ) timing uses an L/RCLK to define when the 8-bit clock periods (for 24-bit data) after L/RCLK toggles. In RJ data being transmitted is for the left channel and when it is for mode, the LSB of data is always clocked by the last bit clock the right channel. The L/RCLK is high for the left channel and before L/RCLK transitions. The data is wEritten MSB first and is low for the right channel. A bit clock running at 64 (cid:3) f is used valid on the rising edge of the bit clock. S T L/RCLK LEFT CHANNEL RIGHT CHANNEL INPUT BCLK E INPUT SIDNAPTUAT MSB M–S1B M–S2B L+S2B L+S1B LSB MSB M–S1B M–S2B L+S2B L+S1B LSB MSB L Figure 6.I2S Timing Diagram O L/RCLK INPUT LEFT CHANNEL RIGHT CHANNEL BCLK INPUT S SIDNAPTUAT MSB M–S1B M–S2B L+S2B L+S1B LSB MSB M–S1B M–S2B L+S2B L+S1B LSB MSB M–S1B Figure 7.Left-Justified Timing Diagram B L/RCLK LEFT CHANNEL INPUT RIGHT CHANNEL O BCLK INPUT SIDNAPUTAT LSB MSB M–S1B M–S2B L+S2B L+S1B LSB MSB M–S1B M–S2B L+S2B L+S1B LSB Figure 8.Right-Justified Timing Diagram REV. 0 –14–

AD1833A TDM Mode Timing—Interfacing to a SHARC® DACR0. The data is written on the rising edge of the bit clock In TDM mode, the AD1833A can be the master or slave, depend- and read by the AD1833A on the falling edge of the bit clock. ing on Bit 0 in Control Register 3. In master mode, it generates a The left and right data destined for the auxiliary DAC is sent in frame sync signal (FSTDM) on its L/RCLK pin and a bit clock standard I2S format in the next frame using the SDIN2, SDIN3, (BCLKTDM) on its BCLK pin, whereas in slave mode it expects and SOUT pins as the L/RCLK, BCLK, and SDATA pins, these signals to be provided. These signals are used to control respectively, for communicating with the auxiliary DAC. the data transmission from the SHARC. The bit clock must run DSP Mode Timing at a frequency of IMCLK/2 and the interpolation mode must be DSP mode timing uses the rising edge of the frame sync signal set to 8(cid:1), which limits TDM mode to frequencies of 48 kHz or on the L/RCLK pin to denote the start of the transmission of a less. In this mode, all data is written on the rising edge of the bit data-word. Note that for both left and right channels, a rising clock and read on the falling edge of the bit clock. The frame edge is used; therefore in this mode, there is no way to determine starts with a frame sync at the rising edge of the bit clock. The which data is intended for the left chaEnnel and which is intended SHARC then starts outputting data on the next rising edge of for the right. The DSP writes data on the rising edge of BCLK the bit clock. Each channel is given a 32-bit clock slot, and the and the AD1833A reads it on the falling edge. The DSP raises data is left-justified and uses 16, 20, or 24 of the 32 bits. An the frame sync signal on the rising edge of BCLK and then proceeds enlarged diagram detailing this is provided (see Figure 9). The to transmit data, MSB firsTt, on the next rising edge of BCLK. data is sent from the SHARC to the AD1833A on the SDIN1 The data length can be 16, 20, or 24 bits. The frame sync signal pin and provided in the following order: MSB first—Internal can be brought low any time at or after the MSB is transmitted, DACL0, Internal DACL1, Internal DACL2, AUX DACL0, but must be brought low at least one BCLK period before the Internal DACR0, Internal DACR1, Internal DACR2, and AUX start of the nextE channel transmission. FSTDM L BCLKTDM O INTERNAL INTERNAL INTERNAL AUXILIARY INTERNAL INTERNAL INTERNAL AUXILIARY DAC L0 DAC L1 DAC L2 DAC L0 DAC R0 DAC R1 DAC R2 DAC R0 S B BCLKTDM 24-BIT DATA MSB M–S1B M–S2B M–S3B M–S4B L+S8B L+S7B L+S6B L+S5B L+S4B L+S3B L+S2B L+S1B LSB O 20-BIT DATA MSB M–S1B M–S2B M–S3B M–S4B L+S4B L+S3B L+S2B L+S1B LSB 16-BIT DATA MSB M–S1B M–S2B M–S3B M–S4B LSB Figure 9.TDM Mode Timing L/RCLK BCLK SDATA MSB M–S1B M–S2B M–S3B M–S4B M–S5B M–S6B MSB M–S1B M–S2B M–S3B M–S4B M–S5B M–S6B MSB 32 BCLKs 32 BCLKs Figure 10.DSP Mode Timing REV. 0 –15–

AD1833A Packed Mode 128 Packed Mode 256 In Packed Mode 128, all six data channels are packed into one In Packed Mode 256, all six data channels are packed into one sample interval on one data pin. The BCLK runs at 128 (cid:1) f ; sample interval on one data pin. The BCLK runs at 256 (cid:1) f ; S S therefore, there are 128 BCLK periods in each sample interval. therefore, there are 256 BCLK periods in each sample interval, and Each sample interval is broken into eight time slots: six slots of each sample interval is broken into eight time slots of 32 BCLK 20 BCLK and two of 4 BCLK. In this mode, the data length is each. The data length can be 16, 20, or 24 bits. The three left restricted to a maximum of 20 bits. The three left channels are channels are written first, MSB first, and the data is written on the written first, MSB first, and the data is written on the falling falling edge of BCLK with a one BCLK period delay from the edge of BCLK. After the three left channels are written, there is start of the slot. After the three left channels are written, there is a space of four BCLK, and then the three right channels are writ- a space of 32 BCLK, and then the three right channels are written. ten. The L/RCLK defines the left and right data transmission; it The L/RCLK defines the left and right data transmission; it is is high for the three left channels and low for the three right channels. low for the three left channels and high for the three right channels. E L/RCLK T BCLK E DATA SLOT 1 SLOT 2 SLOT 3 BLANK SLOT SLOT 4 SLOT 5 SLOT 6 BLANK SLOT LEFT 0 LEFT 1 LEFT 2 4 SCLK RIGHT 0 RIGHT 1 RIGHT 2 4 SCLK L O BCLK 20-BIT DATA MSB M–S1B M–S2B M–S3B M–S4B L+S4B L+S3B L+S2B L+S1B LSB S 16-BIT DATA MSB M–S1B M–S2B M–S3B M–S4B LSB Figure 11.Packed Mode 128 B L/RCLK O BCLK SLOT 1 SLOT 2 SLOT 3 SLOT 4 SLOT 5 SLOT 6 DATA LEFT 0 LEFT 1 LEFT 2 RIGHT 0 RIGHT 1 RIGHT 2 BCLK 24-BIT DATA MSB M–S1B M–S2B M–S3B M–S4B L+S8B L+S7B L+S6B L+S5B L+S4B L+S3B L+S2B L+S1B LSB 20-BIT DATA MSB M–S1B M–S2B M–S3B M–S4B L+S4B L+S3B L+S2B L+S1B LSB 16-BIT DATA MSB M–S1B M–S2B M–S3B M–S4B LSB Figure 12.Packed Mode 256 REV. 0 –16–

AD1833A 0 68pF 11k(cid:6) NPO –20 VOUT– 11k(cid:6) 3.81k(cid:6) 270pF 6 –40 100pF NPO 7 604(cid:6) NPO OP275 VFILTOUT –60 5N6P0OpF 5 2N.P2OnF BR d 1.50k(cid:6) –80 VOUT+ 5.62k(cid:6) 5.62k(cid:6) 150pF –100 NPO –120 E –140 0 20 40 60 80 100 120 kHz Figure 13.Suggested Output Filter Schematic Figure 16.DynamicT Range for 37 kHz @ –60 dBFS, 110 dB, Triangular Dithered Input E 0 0 –20 –20 L –40 –40 –60 –60 R R B B d O d –80 –80 –100 –100 –120 –120 S –140 –140 0 2 4 6 8 10 12 14 16 18 20 0 20 40 60 80 100 120 kHz kHz Figure 14.Dynamic Range forB 1 kHz @ –60 dBFS, Figure 17.Input 0 dBFS @ 37 kHz, BW 20 Hz to 110 dB, Triangular Dithered Input 120 kHz, SR 96 kHz, THD + N –95 dBFS 0 O 0 –20 –20 –40 –40 –60 –60 BR BV –80 d d –80 –100 –100 –120 –120 –140 –140 –160 0 2 4 6 8 10 12 14 16 18 20 0 2 4 6 8 10 12 14 16 18 20 kHz kHz Figure 15.Input 0 dBFS @ 1 kHz, BW 20 Hz to Figure 18.Noise Floor for Zero Input, SR 48 kHz, 20kHz, SR 48 kHz, THD + N –95 dBFS SNR 110 dBFS A-Weighted REV. 0 –17–

AD1833A –60 –20 –30 –70 –40 –50 –80 –60 R R B –90 B –70 d d –80 –100 –90 –100 –110 E –110 –120 –120 –100 –90 –80 –70 –60 –50 –40 –30 –20 –10 0 –100 –90 –80 –70 –60 –50 –40 –30 –20 –10 0 dBFS dBFS Figure 19.THD + N Amplitude vs. Input Amplitude, Figure 20.THD + N RTatio vs. Input Amplitude, Input 1 kHz, SR 48 kHz, 24-Bit Input 1kHz, SR 48 kHz, 24-Bit E L O S B O REV. 0 –18–

AD1833A DVDD AVDD –INTF 5V 5V 10(cid:7)F + 10(cid:7)F 0.1(cid:7)F + 10(cid:7)F 0.1(cid:7)F + 10(cid:7)F 0.1(cid:7)F + 0.1(cid:7)F 10(cid:7)F 10(cid:7)F + + 10(cid:7)F DVDD 0.1(cid:7)F + 0.1(cid:7)F 0.1(cid:7)F E AVDD 0.1(cid:7)F 10(cid:7)F 9 28 433 33444 22 7 CCLADCTACCTLHAK 111456 CCCLDCAALTKTCAH DVDD1DVDD2 AVDD1AVDD2AVDDAVDDAVDDTOOOUUUTTTLLLNPP112 4127 LLL112+–+ 75RO 1100nnFF 109 RRXXPN VA+ VD+ SFSDMYSANCCTCAKK 21116129 PAL 11227801 LBS/DCRILCNKL1K AD1833EA OOOOUUUUTTTTRLLLNNPP2331 44438566 LLLR2331–+–+ 23 SDIN2 35 1k(cid:6) 20 FILT DIR-CS8414 MMMMCU0123 211114874 221239 SSMODCIULNKT3 L OOOOOUUUUUTTTTTRRRRRNNNPP12233 33438709 RRRRR23123++––– 47nF VCEERRBFFL 122585 GND1 GND2 ND ND ND ND NDNDND FFIILLTTRD 4423 D D G G G G GGG + + CO/EO 6 8 29 7 30 631 53241 0.1(cid:7)F 10(cid:7)F 0.1(cid:7)F 10(cid:7)F 21 AGND CA/E1 54 O CB/E2 8 3 DGND CC/F0 2 CD/F1 27 CE/F2 16 SEL CS12/FCK 13 S 5V L5 B 0.1(cid:7)F 10k(cid:6) 3 5 SHLD1 VDD 6 D SHLD1 OUT O U5 1 TORX173 2 SHLD1 4 SHLD1 Figure 21.Example Digital Interface REV. 0 –19–

AD1833A OUTLINE DIMENSIONS 48-Lead Low Profile Quad Flat Package [LQFP] 1.4 mm Thick (ST-48) Dimensions shown in millimeters 0) 3( 0 1.60 MAX 5/ PIN 1 – 0.75 INDICATOR –0 9.00 BSC 6 0.60 3 0.45 148 3736 E C023 SEATING 1.45 PLANE 1.40 0.20 TOP VIEW 7.00 0.09 (PINS DOWN) BSC 1.35 7(cid:4) VIEW A T 3.5(cid:4) 0.15 0(cid:4) 12 25 0.05 SEATING 0.08 MAX 13 24 PLANE COPLANARITY 0.50 0.27 VIEW A BSC E 0.22 ROTATED 90(cid:4) CCW 0.17 COMPLIANT TO JEDEC STANDARDS MS-026BBC L O S B O –20– REV. 0

Datasheet下载

Datasheet下载