ICGOO在线商城 > 集成电路(IC) > 逻辑 - 栅极和逆变器 - 多功能,可配置 > 74AUP1G97L6X

- 型号: 74AUP1G97L6X

- 制造商: Fairchild Semiconductor

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

74AUP1G97L6X产品简介:

ICGOO电子元器件商城为您提供74AUP1G97L6X由Fairchild Semiconductor设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 74AUP1G97L6X价格参考¥1.56-¥1.56。Fairchild Semiconductor74AUP1G97L6X封装/规格:逻辑 - 栅极和逆变器 - 多功能,可配置, 可配置多功能 Configurable 1 Circuit 3 Input 6-MicroPak。您可以下载74AUP1G97L6X参考资料、Datasheet数据手册功能说明书,资料中有74AUP1G97L6X 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC)半导体 |

| 描述 | IC GATE UNIV 2INPUT 6-MICROPAK逻辑门 2 Input, Low Power Config. Logic Gate |

| 产品分类 | |

| 品牌 | Fairchild Semiconductor |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 逻辑集成电路,逻辑门,Fairchild Semiconductor 74AUP1G97L6X74AUP |

| 数据手册 | |

| 产品型号 | 74AUP1G97L6X |

| PCN设计/规格 | |

| 产品 | Configurable |

| 产品种类 | 逻辑门 |

| 传播延迟时间 | 1.3 ns to 3.4 ns |

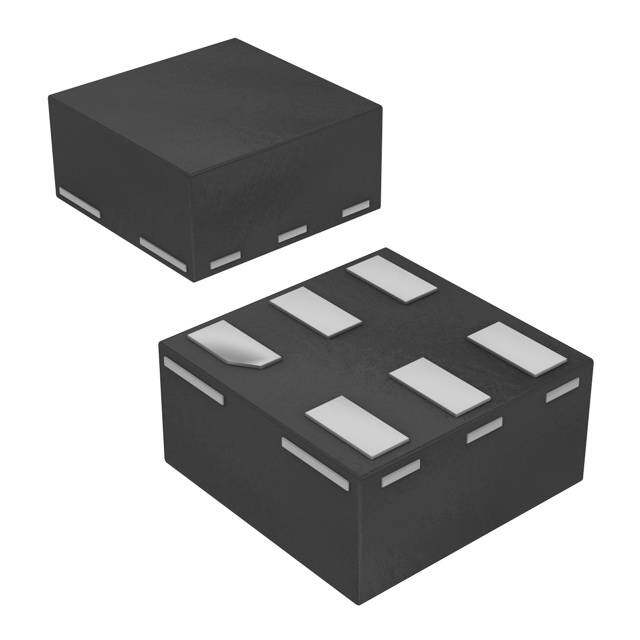

| 供应商器件封装 | 6-MicroPak |

| 其它名称 | 74AUP1G97L6XDKR |

| 包装 | Digi-Reel® |

| 单位重量 | 19.800 mg |

| 商标 | Fairchild Semiconductor |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装 | Reel |

| 封装/外壳 | 6-UFDFN |

| 封装/箱体 | Micropak-6 |

| 工作温度 | -40°C ~ 85°C |

| 工厂包装数量 | 5000 |

| 施密特触发器输入 | 是 |

| 最大工作温度 | + 85 C |

| 标准包装 | 1 |

| 电压-电源 | 0.8 V ~ 3.6 V |

| 电流-输出高,低 | 4mA,4mA |

| 电源电压-最大 | 3.6 V |

| 电源电压-最小 | 0.8 V |

| 电路数 | 1 |

| 系列 | 74AUP1G97 |

| 输入数 | 3 |

| 输出类型 | 单端 |

| 逻辑类型 | 可配置多功能 |

| 逻辑系列 | TinyLogic |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

Is Now Part of To learn more about ON Semiconductor, please visit our website at www.onsemi.com Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor’s system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (_), the underscore (_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at www.onsemi.com. Please email any questions regarding the system integration to Fairchild_questions@onsemi.com. ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor’s product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. “Typical” parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

7 4 A U P October 2010 1 G 9 7 — 74AUP1G97 T TinyLogic® Low Power Universal Configurable in y L Two-Input Logic Gate o g i c ® Features Description L o w (cid:131) 0.8V to 3.6V VCC Supply Operation Tlohgeic 7g4aAteU Pth1aGt 9p7r oivsi dae s uan ivheigrsha lp ecrofnofrimguarnacbele an2d-i nlpouwt P (cid:131) 3.6V Over-Voltage Tolerant I/Os at V o CC power solution ideal for battery-powered portable w from 0.8V to 3.6V applications. This product is designed for a wide low e (cid:131) High Speed tPD voltage operating range (0.8V to 3.6V) and guarantees r U very low static and dynamic power consumption across - 3.1ns: Typical at 3.3V n (cid:131) Power-Off High-Impedance Inputs and Outputs twhieth ehnytisrete rveoslitsa geto raanllgoew. Afollr insplouwtse ra rtera nimsiptiloenm einnpteudt ive (cid:131) Low Static Power Consumption signals and better switching noise immunity. rs a - ICC=0.9µA Maximum The 74AUP1G97 provides for multiple functions as l (cid:131) Low Dynamic Power Consumption determined by various configurations of the three C o inputs. The potential logic functions provided are MUX, - CPD=2.5pF Typical at 3.3V AND, OR, NAND, and NOR, inverter and buffer. Refer nf (cid:131) Ultra-Small MicroPak™ Packages to Figures 3 to 9. ig u r a b le T w Ordering Information o - I Part Number Top Mark Package Packing Method n p 5000 Units on u 74AUP1G97L6X AD 6-Lead MicroPak™, 1.0mm Wide t Tape & Reel L o 74AUP1G97FHX AD 6-Lead, MicroPak2™, 1x1mm Body, .35mm Pitch 5000 Units on g Tape & Reel i c G a t e © 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com 74AUP1G97 • 1.0.5

7 4 Logic Diagram A U P 1 G A 3 9 7 — 4 Y 1 B T i n y L 6 o C g i c Figure 1. Logic Diagram (Positive Logic) ® L o w P Pin Configurations o w e B 1 6 C r U n GND 2 5 VCC iv e r s A 3 4 Y a l C Figure 2. MicroPak™ (Top Through View) o n f i g u r a b l e Pin Definitions T w Pin # Name Description o - I n 1 B Data Input p u 2 GND Ground t L 3 A Data Input o g 4 Y Output i c 5 VCC Supply Voltage G a 6 C Data Input t e © 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com 74AUP1G97 • 1.0.5 2

7 4 Function Table A U P Inputs 74AUP1G97 1 G C B A Y=Output 9 7 L L L L — L L H L T i n L H L H y L L H H H o g H L L L i c H L H H ® L H H L L o w H H H H P o H = HIGH Logic Level w e L = LOW Logic Level r U n i v e Function Selection Table r s a l 2-Input Logic Function Connection Configuration C o 2-to-1 MUX Figure 3 n f i 2-Input AND Gate Figure 4 g u 2-Input OR Gate with One Inverted Input Figure 5 r a b 2-Input NAND Gate with One Inverted Input Figure 5 l e 2-Input AND Gate with One Inverted Input Figure 6 T w 2-Input NOR Gate with One Inverted Input Figure 6 o - 2-Input OR Gate Figure 7 I n p Inverter Figure 8 u t Buffer Figure 9 L o g i c G a t e © 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com 74AUP1G97 • 1.0.5 3

7 4 74AUP1G97 Logic Configurations A U Figure 3 through Figure 9 show the logical functions implementation is next to the board-level physical P 1 that can be implemented using the 74AUP1G97. The implementation of how the pins of the function should G diagrams show the DeMorgan’s equivalent logic duals be connected. 9 for a given two-input function. The logical 7 — T i V n CC y L C VCC o g B 1 6 C ic B ® Y 2 5 C 1 6 C L A AA 3 4 Y Y o A 2 5 w GND A 3 4 Y P o Note: GND w 1. When C is L, Y=B. e 2. When C is H, Y=A. r U Figure 3. 2-to-1 MUX Figure 4. 2-Input AND Gate n i v e r s V VCC a CC l C C Y C Y B on A B 1 6 C f 1 6 C C 2 5 ig C 2 5 B Y 3 4 Y ur Y A 3 4 Y a A b GND GND le T Figure 5. Input OR Gate with One Inverted Input Figure 6. 2-Input AND Gate with One Inverted Input w 2-Input NAND Gate with One Inverted Input 2-Input NOR Gate with One Inverted Input o - I n p u VCC t L V CC o g i c 1 6 C G C B 1 6 C C Y a Y 2 5 t B 2 5 e 3 4 Y 3 4 Y GND GND Figure 7. 2-Input OR Gate Figure 8. Inverter V CC B 1 6 B Y 2 5 33 4 Y GND Figure 9. Buffer © 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com 74AUP1G97 • 1.0.5 4

7 4 Absolute Maximum Ratings A U Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be P 1 operable above the recommended operating conditions and stressing the parts to these levels is not recommended. G In addition, extended exposure to stresses above the recommended operating conditions may affect device 9 reliability. The absolute maximum ratings are stress ratings only. 7 — Symbol Parameter Min. Max. Unit T VCC Supply Voltage -0.5 4.6 V in y VIN DC Input Voltage -0.5 4.6 V L o HIGH or LOW State(3) -0.5 VCC + 0.5 g VOUT DC Output Voltage V =0V -0.5 4.6 V ic CC ® IIK DC Input Diode Current VIN < 0V -50 mA L o VOUT < 0V -50 w I DC Output Diode Current mA OK VOUT > VCC +50 P o IOH / IOL DC Output Source / Sink Current ±50 mA w I Continuous Output Current ±20 mA e O r I or I DC V or Ground Current per Supply Pin ±50 mA U CC GND CC n TSTG Storage Temperature Range -65 +150 °C iv T Junction Temperature Under Bias +150 °C e J r s TL Junction Lead Temperature, Soldering 10s +260 °C a l MicroPak-6 130 C PD Power Dissipation at +85°C mW o MicroPak2-6 120 n f Human Body Model, JEDEC:JESD22-A114 5000+ i ESD V g Charged Device Model, JEDEC:JESD22-C101 1500 u r a Note: b 3. IO absolute maximum rating must be observed. le T Recommended Operating Conditions(4) w o - The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended In operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not p u recommend exceeding them or designing to Absolute Maximum Ratings. t L Symbol Parameter Conditions Min. Max. Unit o g VCC Supply Voltage 0.8 3.6 V ic V Input Voltage 0 3.6 V G IN a V =0V 0 3.6 t V Output Voltage CC V e OUT HIGH or LOW State 0 V CC V =3.0V to 3.6V ±4.0 CC V =2.3V to 2.7V ±3.1 CC V =1.65V to 1.95V ±1.9 mA CC I /I Output Current OH OL V =1.4V to 1.6V ±1.7 CC V =1.1V to 1.3V ±1.1 CC V =0.8V ±20.0 µA CC T Operating Temperature, Free Air -40 +85 °C A MicroPak-6 500 θ Thermal Resistance °C/W JA MicroPak2-6 560 Note: 4. Unused inputs must be held HIGH or LOW. They may not float. © 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com 74AUP1G97 • 1.0.5 5

7 4 DC Electrical Characteristics A U P T =+25°C T =-40 to +85°C A A 1 Symbol Parameter VCC Conditions Units G Min. Max. Min. Max. 9 7 0.80 0.30 0.60 0.30 0.60 — 1.10 0.53 0.90 0.53 0.90 T VP PVoosltiatigvee Threshold 11..4605 00..7941 11..1219 00..7941 11..1219 V iny L 2.30 1.37 1.77 1.37 1.77 o g 3.00 1.88 2.29 1.88 2.29 ic ® 0.80 0.10 0.60 0.10 0.60 L 1.10 0.26 0.65 0.26 0.65 o w VN NThergeasthivoeld Voltage 11..4605 00..3497 00..7854 00..3497 00..7854 V Po w 2.30 0.69 1.04 0.69 1.04 e r 3.00 0.88 1.24 0.88 1.24 U 0.80 0.07 0.50 0.07 0.50 n i v 1.10 0.08 0.46 0.08 0.46 e r 1.40 0.18 0.56 0.18 0.56 s VH Hysteresis Voltage 1.65 0.27 0.66 0.27 0.66 V al C 2.30 0.53 0.92 0.53 0.92 o n 3.00 0.79 1.31 0.79 1.31 f i g 0.80 ≤ VCC ≤ 3.60 IOH=-20µA VCC-0.1 VCC-0.1 u r 1.10 ≤ VCC ≤ 1.30 IOH=-1.1mA 0.75 x VCC 0.70 x VCC ab 1.40 ≤ VCC ≤ 1.60 IOH=-1.7mA 1.11 1.03 le VOH HVoIGltaHg Lee vel Output 1.65 ≤ VCC ≤ 1.95 IOH=-1.9mA 1.32 1.30 V Tw IOH=-2.3mA 2.05 1.97 o 2.30 ≤ VCC ≤ 2.70 IOH=-3.1mA 1.90 1.85 -In p IOH=-2.7mA 2.72 2.67 u 3.00 ≤ VCC ≤ 3.60 IOH=-4.0mA 2.60 2.55 t L o 0.80 ≤ VCC ≤ 3.60 IOL=20µA 0.10 0.10 g i 1.10 ≤ VCC ≤ 1.30 IOL=1.1mA 0.30 x VCC 0.30 x VCC c G 1.40 ≤ VCC ≤ 1.60 IOL=1.7mA 0.31 0.37 a t VOL LVOolWtag Lee vel Output 1.65 ≤ VCC ≤ 1.95 IOL=1.9mA 0.31 0.35 V e IOL=2.3mA 0.31 0.33 2.30 ≤ VCC ≤ 2.70 IOL=3.1mA 0.44 0.45 IOL=2.7mA 0.31 0.33 2.70 ≤ VCC ≤ 3.60 IOL=4.0mA 0.44 0.45 Input Leakage IIN Current 0V to 3.6V 0 ≤ VIN ≤ 3.6 ±0.1 ±0.5 µA Power Off Leakage IOFF Current 0V 0 ≤ (VIN,VO)≤ 3.6 0.2 0.6 µA Additional Power ΔIOFF Off Leakage 0V to 0.2V VtoI N3 o.6r VV O = 0V 0.2 0.6 µA Current ICC QCuurieresncte nt Supply 0.8V to 3.6V VGINN D- VCC or 0.5 0.9 µA VCC ≤ VIN ≤ 3.6 ±0.9 ΔICC IInncpruet ase in ICC per 3.3V VIN = VCC -0.6V 40.0 50.0 µA © 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com 74AUP1G97 • 1.0.5 6

7 4 A AC Electrical Characteristics U P T =-40 to 1 T =+25°C A G A +85°C Symbol Parameter V Conditions Units Figure 9 CC 7 Min. Typ. Max Min Max — 0.80 25.1 T i 1.10 ≤ VCC ≤ 1.30 2.8 8.6 12.6 2.5 13.0 n y 1.40 ≤ VCC ≤ 1.60 2.3 5.2 7.6 2.5 8.2 L 1.65 ≤ VCC ≤ 1.95 CL=5pF, RL=1MΩ 2.1 4.3 6.2 2.0 6.8 og i c 2.30 ≤ VCC ≤ 2.70 1.9 3.3 4.8 1.7 5.3 ® L 3.00 ≤ VCC ≤ 3.60 1.6 3.1 3.9 1.5 4.1 o w 0.80 29.4 P 1.10 ≤ VCC ≤ 1.30 3.2 9.4 14.3 2.9 14.9 o w 1.40 ≤ VCC ≤ 1.60 CL=10pF, 2.6 6.3 8.7 2.8 9.4 e 1.65 ≤ VCC ≤ 1.95 RL=1MΩ 2.2 4.9 7.0 2.1 7.8 r U 2.30 ≤ VCC ≤ 2.70 2.0 4.2 5.2 2.1 5.9 ni v 3.00 ≤ VCC ≤ 3.60 1.9 3.6 4.6 1.7 4.9 e tPHL, tPLH PDreolapya gation 0.80 31.3 ns FFiigguurree 1110 rsa l 1.10 ≤ VCC ≤ 1.30 3.6 9.6 16.0 3.2 16.7 C o 1.40 ≤ VCC ≤ 1.60 CL=15pF, 2.9 6.3 9.6 3.1 10.4 n 1.65 ≤ VCC ≤ 1.95 RL=1MΩ 2.4 5.4 7.8 2.3 8.7 fig u 2.30 ≤ VCC ≤ 2.70 2.3 4.7 5.8 2.1 6.5 r a 3.00 ≤ VCC ≤ 3.60 2.0 4.0 5.1 1.8 5.5 b l e 0.80 32.1 T w o 1.10 ≤ VCC ≤ 1.30 3.4 9.5 18.5 3.4 19.0 -I CL=30pF, n 1.40 ≤ VCC ≤ 1.60 RL=1MΩ 3.1 5.9 10.5 3.1 11.0 pu 1.65 ≤ VCC ≤ 1.95 1.8 4.8 8.7 1.8 9.5 t L 2.30 ≤ VCC ≤ 2.70 1.7 3.7 6.5 1.7 7.1 o g 3.00 ≤ VCC ≤ 3.60 1.3 3.1 5.6 1.3 6.3 ic Input G CIN Capacitance 0 2.1 pF a t Output e COUT Capacitance 0 3,0 pF 0.80 1.7 1.10 ≤ VCC ≤ 1.30 1.8 CPD PDCoiaswpsaeipcra ittaionnc e 11..4605 ≤≤ VVCCCC ≤≤ 11..6905 Vf=IN1=00MVH ozr VCC, 11..8814 pF 2.30 ≤ VCC ≤ 2.70 2.1 3.00 ≤ VCC ≤ 3.60 2.5 © 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com 74AUP1G97 • 1.0.5 7

7 4 AC Loadings and Waveforms A U P 1 G 9 7 — T i n y L o g i c ® L o w P Figure 10. AC Test Circuit o w e r U n i v e r s a l C o n f i g u r a b l e T Figure 11. AC Waveforms w o - I n p u t V L CC Symbol o g 3.3V ± 0.3V 2.5V ± 0.2V 1.8V ± 0.15V 1.5V ± 0.10V 1.2V ± 0.10V 0.8V i c Vmi VCC/2 VCC/2 VCC/2 VCC/2 VCC/2 VCC/2 G a Vmo VCC/2 VCC/2 VCC/2 VCC/2 VCC/2 VCC/2 te © 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com 74AUP1G97 • 1.0.5 8

7 4 Physical Dimensions A U 2X P 1 0.05 C 1.45 B G 2X (1) 9 0.05 C 7 — T (0.254) 1.00 (0.49) in 5X y L (0.75) o g i (0.52) c PIN 1 IDENTIFIER TOP VIEW A 1X ® L 5 o 0.55MAX (0.30) w PIN 1 6X P 0.05 C o 0.05 RECOMMENED w 0.00 LAND PATTERN e r 0.05 C U C 0.45 n 0.106X 0.35 iv 0.25 6X 0.00 e 0.15 r DETAIL A 1.0 s 0.10 C B A a 0.05 C 0.40 l 0.30 C o n 00..3255 5X fig u r a 00..4300 5X DETAIL A bl 0.075 X 45 PIN 1 TERMINAL e (0.05) 0.5 CHAMFER T (0.13) w 6X 4X o BOTTOM VIEW - Notes: In 1. CONFORMS TO JEDEC STANDARD M0-252 VARIATION UAAD p u 2. DIMENSIONS ARE IN MILLIMETERS t 3. DRAWING CONFORMS TO ASME Y14.5M-1994 L 4. FILENAME AND REVISION: MAC06AREV4 o 5. PIN ONE IDENTIFIER IS 2X LENGTH OF ANY g i OTHER LINE IN THE MARK CODE LAYOUT. c G Figure 12. 6-Lead, MicroPak™, 1.0mm Wide a t e Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products. Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/. Tape and Reel Specifications Please visit Fairchild Semiconductor’s online packaging area for the most recent tape and reel specifications: http://www.fairchildsemi.com/products/logic/pdf/micropak_tr.pdf. Package Designator Tape Section Cavity Number Cavity Status Cover Type Status Leader (Start End) 125 (Typical) Empty Sealed L6X Carrier 5000 Filled Sealed Trailer (Hub End) 75 (Typical) Empty Sealed © 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com 74AUP1G97 • 1.0.5 9

7 4 Physical Dimensions A U P 0.89 1 G 0.05 C 0.35 9 2X 1.00 B A 7 5X 0.40 — T PIN 1 0.66 in MIN 250uM y 1.00 L 1X 0.45 o g i c 6X 0.19 0.05 C ® TOP VIEW 2X RECOMMENDED LAND PATTERN L FOR SPACE CONSTRAINED PCB o w 0.90 P 0.05 C 0.35 o w e C 0.55MAX 5X0.52 r U n SIDE VIEW 0.73 iv e r (0.08) 4X 0.09 1X0.57 s DETAIL A 1 2 3 0.19 6X al C 0.20 6X o n ALTERNATIVE LAND PATTERN f i FOR UNIVERSAL APPLICATION g u r (0.05) 6X a b 5X0.35 le 0.25 0.60 T 6 5 4 0.10 C B A w 0.35 (04.0X8) .05 C 00..4300 o- BOTTOM VIEW In NOTES: p A. COMPLIES TO JEDEC MO-252 STANDARD u B. DIMENSIONS ARE IN MILLIMETERS. t C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994 0.075X45° L D. LANDPATTERN RECOMMENDATION IS BASED ON FSC CHAMFER DETAIL A o DESIGN. PIN 1 LEAD SCALE: 2X g E. DRAWING FILENAME AND REVISION: MGF06AREV3 ic Figure 13. 6-Lead, MicroPak2™, 1x1mm Body, .35mm Pitch G a t e Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products. Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/. Tape and Reel Specifications Please visit Fairchild Semiconductor’s online packaging area for the most recent tape and reel specifications: http://www.fairchildsemi.com/packaging/MicroPAK2_6L_tr.pdf. Package Designator Tape Section Cavity Number Cavity Status Cover Type Status Leader (Start End) 125 (Typical) Empty Sealed FHX Carrier 5000 Filled Sealed Trailer (Hub End) 75 (Typical) Empty Sealed © 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com 74AUP1G97 • 1.0.5 10

7 4 A U P 1 G 9 7 — T i n y L o g i c ® L o w P o w e r U n i v e r s a l C o n f i g u r a b l e T w o - I n p u t L o g i c G a t e © 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com 74AUP1G97 • 1.0.5 11

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor’s product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent−Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. “Typical” parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner. PUBLICATION ORDERING INFORMATION LITERATURE FULFILLMENT: N. American Technical Support: 800−282−9855 Toll Free ON Semiconductor Website: www.onsemi.com Literature Distribution Center for ON Semiconductor USA/Canada 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Europe, Middle East and Africa Technical Support: Order Literature: http://www.onsemi.com/orderlit Phone: 303−675−2175 or 800−344−3860 Toll Free USA/Canada Phone: 421 33 790 2910 Fax: 303−675−2176 or 800−344−3867 Toll Free USA/Canada Japan Customer Focus Center For additional information, please contact your local Email: orderlit@onsemi.com Phone: 81−3−5817−1050 Sales Representative © Semiconductor Components Industries, LLC www.onsemi.com www.onsemi.com 1

Datasheet下载

Datasheet下载