- 型号: 71V016SA15PHG

- 制造商: Integrated Device Technology

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

71V016SA15PHG产品简介:

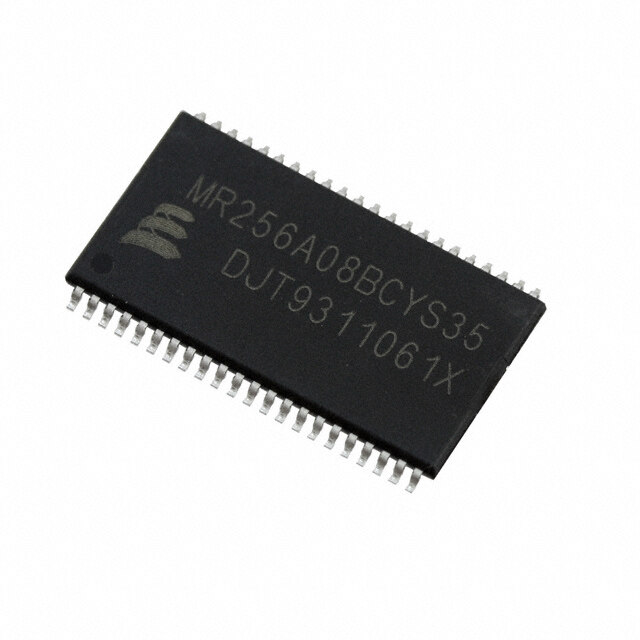

ICGOO电子元器件商城为您提供71V016SA15PHG由Integrated Device Technology设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 71V016SA15PHG价格参考。Integrated Device Technology71V016SA15PHG封装/规格:存储器, SRAM - 异步 存储器 IC 1Mb (64K x 16) 并联 15ns 44-TSOP II。您可以下载71V016SA15PHG参考资料、Datasheet数据手册功能说明书,资料中有71V016SA15PHG 详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 品牌 | IDT |

| 产品目录 | 半导体 |

| 描述 | 静态随机存取存储器 64Kx16 ASYNCHRONOUS 3.3V STATIC RAM |

| 产品分类 | 集成电路 - IC |

| 产品手册 | http://www.idt.com/document/dst/71v016sa-datasheet |

| 产品图片 |

|

| rohs | 符合RoHS |

| 产品系列 | 内存,静态随机存取存储器,IDT 71V016SA15PHG |

| 产品型号 | 71V016SA15PHG |

| 产品种类 | 静态随机存取存储器 |

| 商标 | IDT |

| 存储容量 | 1 Mbit |

| 存储类型 | SDR |

| 安装风格 | SMD/SMT |

| 封装 | Tray |

| 封装/箱体 | TSOP-44 |

| 工厂包装数量 | 26 |

| 接口 | Parallel |

| 最大工作温度 | + 70 C |

| 最大工作电流 | 130 mA |

| 最小工作温度 | 0 C |

| 电源电压-最大 | 3.6 V |

| 电源电压-最小 | 3 V |

| 类型 | Asynchronous |

| 系列 | 71V016 |

| 组织 | 64 k x 16 |

| 访问时间 | 15 ns |

| 零件号别名 | 71V016 IDT71V016SA15PHG |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

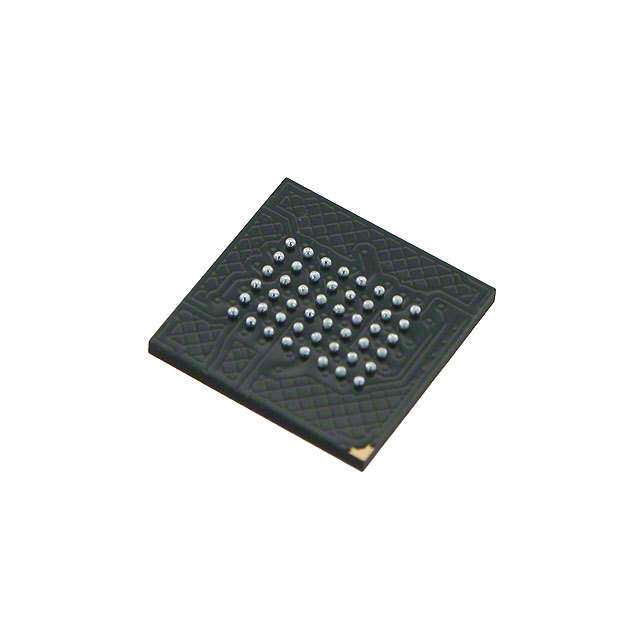

3.3V CMOS Static RAM 71V016SA 1 Meg (64K x 16-Bit) Features Description ◆◆◆◆◆ 64K x 16 advanced high-speed CMOS Static RAM The IDT71V016 is a 1,048,576-bit high-speed Static RAM organized ◆◆◆◆◆ Equal access and cycle times as 64K x 16. It is fabricated using high-performance, high-reliability CMOS — Commercial: 10/12/15/20ns technology. This state-of-the-art technology, combined with innovative — Industrial: 10/12/15/20ns circuit design techniques, provides a cost-effective solution for high-speed ◆◆◆◆◆ One Chip Select plus one Output Enable pin memory needs. ◆◆◆◆◆ Bidirectional data inputs and outputs directly The IDT71V016 has an output enable pin which operates as fast as LVTTL-compatible 5ns, with address access times as fast as 10ns. All bidirectional inputs and ◆◆◆◆◆ Low power consumption via chip deselect outputs of the IDT71V016 are LVTTL compatible and operation is from a ◆◆◆◆◆ Upper and Lower Byte Enable Pins single 3.3V supply. Fully static asynchronous circuitry is used, requiring ◆◆◆◆◆ Single 3.3V power supply no clocks or refresh for operation. ◆◆◆◆◆ Available in 44-pin Plastic SOJ, 44-pin TSOP, and The IDT71V016 is packaged in a JEDEC standard 44-pin Plastic SOJ, 48-Ball Plastic FBGA packages a 44-pin TSOP Type II, and a 48-ball plastic 7 x 7 mm FBGA. ◆◆◆◆◆ Industrial temperature range (–40°C to +85°C) is available for selected speeds ◆◆◆◆◆ Green parts available, see ordering information Functional Block Diagram Output OE Enable Buffer Address Row/Column A0–A15 Buffers Decoders I/O15 8 High 8 Chip Byte CS Enable I/O Buffer Buffer I/O8 Sense 64Kx16 16 Amps Memory and Array Write Write Drivers WE Enable I/O7 Buffer Low 8 Byte 8 I/O Buffer I/O0 BHE Byte Enable Buffers BLE 3834drw01 1 Jun.23.20

71V016SA, 3.3V CMOS Static RAM 1 Meg (64K x 16-Bit) Commercial and Industrial Temperature Ranges Pin Configurations - PBG44, PHG44(1) 1 2 3 4 5 6 A BLE OE A0 A1 A2 NC A4 1 44 A5 A3 2 43 A6 A2 3 42 A7 B I/O8 BHE A3 A4 CS I/O0 A1 4 41 OE A0 5 40 BHE C I/O9 I/O10 A5 A6 I/O1 I/O2 CS 6 39 BLE I/O0 7 38 I/O15 D VSS I/O11 NC A7 I/O3 VDD I/O1 8 37 I/O14 I/O2 9 7 1V016SA 36 I/O13 E VDD I/O12 NC NC I/O4 VSS I/O3 10 PBG44 35 I/O12 PHG44 VDD 11 34 VSS VSS 12 33 VDD F I/O14 I/O13 A14 A15 I/O5 I/O6 I/O4 13 32 I/O11 I/O5 14 31 I/O10 G I/O15 NC A12 A13 WE I/O7 I/O6 15 30 I/O9 I/O7 16 29 I/O8 H NC A8 A9 A10 A11 NC WE 17 28 NC A15 18 27 A8 FBGA (BF48, BFG48)(1) 3834 tbl 02a A14 19 26 A9 Top View A13 20 25 A10 NOTE: A12 21 24 A11 1. This text does not indicate orientation of actual part-marking. NC 22 23 NC Pin Description 3834 drw 02 A0 – A15 Address Inputs Input SOJ/TSOP CS Chip Select Input Top View WE Write Enable Input NOTE: OE Output Enable Input 1. This text does not indicate orientation of actual part-marking. BHE High Byte Enable Input BLE Low Byte Enable Input I/O0 – I/O15 Data Input/Output I/O VDD 3.3V Power Power VSS Ground Gnd Truth Table(1) 3834 tbl 01 CS OE WE BLE BHE I/O0-I/O7 I/O8-I/O15 Function H X X X X High-Z High-Z Deselected – Standby L L H L H DATAOUT High-Z Low Byte Read L L H H L High-Z DATAOUT High Byte Read L L H L L DATAOUT DATAOUT Word Read L X L L L DATAIN DATAIN Word Write L X L L H DATAIN High-Z Low Byte Write L X L H L High-Z DATAIN High Byte Write L H H X X High-Z High-Z Outputs Disabled L X X H H High-Z High-Z Outputs Disabled NOTE: 3834 tbl 02 1. H = VIH, L = VIL, X = Don't care. 2 Jun.23.20

71V016SA, 3.3V CMOS Static RAM 1 Meg (64K x 16-Bit) Commercial and Industrial Temperature Ranges Absolute Maximum Ratings(1) Recommended Operating Symbol Rating Value Unit Temperature and Supply Voltage VDD Supply Voltage Relative to VSS –0.5 to +4.6 V Grade Temperature VSS VDD VIN, VOUT Terminal Voltage Relative to VSS –0.5 to VDD+0.5 V Commercial 0°C to +70°C 0V See Below TBIAS Temperature Under Bias –55 to +125 oC Industrial -40°C to +85°C 0V See Below TSTG Storage Temperature –55 to +125 oC 3834 tbl 04 PT Power Dissipation 1.25 W IOUT DC Output Current 50 mA Recommended DC Operating Conditions NOTE: 3834 tbl 03 1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause Symbol Parameter Min. Typ. Max. Unit permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational VDD(1) Supply Voltage 3.15 3.3 3.6 V sections of this specification is not implied. Exposure to absolute maximum rating VDD(2) Supply Voltage 3.0 3.3 3.6 V conditions for extended periods may affect reliability. Vss Ground 0 0 0 V Capacitance VIH Input High Voltage 2.0 ____ VDD+0.3(3) V (TA = +25°C, f = 1.0MHz, SOJ package) VIL Input Low Voltage –0.3(4) ____ 0.8 V Symbol Parameter(1) Conditions Max. Unit 3834 tbl 05 CIN Input Capacitance VIN = 3dV 6 pF NOTES: 1. For 71V016SA10 only. CI/O I/O Capacitance VOUT = 3dV 7 pF 2. For all speed grades except 71V016SA10. 3. VIH (max.) = VDD+2V for pulse width less than 5ns, once per cycle. NOTE: 3834 tbl 06 4. VIL (min.) = –2V for pulse width less than 5ns, once per cycle. 1. This parameter is guaranteed by device characterization, but not production tested. DC Electrical Characteristics (VDD = Min. to Max., Commercial and Industrial Temperature Ranges) IDT71V016SA Symbol Parameter Test Condition Min. Max. Unit |ILI| Input Leakage Current VDD = Max., VIN = VSS to VDD ___ 5 µA |ILO| Output Leakage Current VDD = Max., CS = VIH, VOUT = VSS to VDD ___ 5 µA VOL Output Low Voltage IOL = 8mA, VDD = Min. ___ 0.4 V VOH Output High Voltage IOH = –4mA, VDD = Min. 2.4 ___ V 3834 tbl 07 DC Electrical Characteristics(1,2) (VDD = Min. to Max., VLC = 0.2V, VHC = VDD – 0.2V) 71V016SA10 71V016SA12 71V016SA15 71V016SA20 Symbol Parameter Com'l Ind'l Com'l Ind'l Com'l Ind'l Com'l Ind'l Unit ICC Dynamic Operating Current Max. 160 170 150 160 130 130 120 120 mA CS ≤ VLC, Outputs Open, VDD = Max., f = fMAX(3) Typ.(4) 65 -- 60 -- 55 -- 50 -- ISB Dynamic Standby Power Supply Current 45 50 40 45 35 35 30 30 mA CS ≥ VHC, Outputs Open, VDD = Max., f = fMAX(3) ISB1 Full Standby Power Supply Current (static) 10 10 10 10 10 10 10 10 mA CS ≥ VHC, Outputs Open, VDD = Max., f = 0(3) 3834 tbl 08 NOTES: 1. All values are maximum guaranteed values. 2. All inputs switch between 0.2V (Low) and VDD – 0.2V (High). 3. fMAX = 1/tRC (all address inputs are cycling at fMAX); f = 0 means no address input lines are changing . 4. Typical values are based on characterization data for H step only measured at 3.3V, 25°C and with equal read and write cycles. 3 Jun.23.20

71V016SA, 3.3V CMOS Static RAM 1 Meg (64K x 16-Bit) Commercial and Industrial Temperature Ranges AC Test Conditions Input Pulse Levels GND to 3.0V Input Rise/Fall Times 1.5ns Input Timing Reference Levels 1.5V Output Reference Levels 1.5V AC Test Load See Figure 1, 2 and 3 3834 tbl 09 AC Test Loads 3.3V +1.5V 320Ω 50Ω DATAOUT I/O Z0=50Ω 5pF* 350Ω 30pF 3834drw03 3834drw04 *Including jig and scope capacitance. Figure 1. AC Test Load Figure 2. AC Test Load (for tCLZ, tOLZ, tCHZ, tOHZ, tOW, and tWHZ) 7 • 6 ΔtAA,tACS (Typical,ns) 5 4 3 • • 2 • 1 • • (cid:129) 8 20 40 60 80 100 120140 160180 200 CAPACITANCE(pF) 3834drw05 Figure 3. Output Capacitive Derating 4 Jun.23.20

71V016SA, 3.3V CMOS Static RAM 1 Meg (64K x 16-Bit) Commercial and Industrial Temperature Ranges AC Electrical Characteristics (VDD = Min. to Max., Commercial and Industrial Temperature Ranges) 71V016SA10 71V016SA12 71V016SA15 71V016SA20 Symbol Parameter Min. Max. Min. Max. Min. Max. Min. Max. Unit READ CYCLE tRC Read Cycle Time 10 ____ 12 ____ 15 ____ 20 ____ ns tAA Address Access Time ____ 10 ____ 12 ____ 15 ____ 20 ns tACS Chip Select Access Time ____ 10 ____ 12 ____ 15 ____ 20 ns tCLZ(1) Chip Select Low to Output in Low-Z 4 ____ 4 ____ 5 ____ 5 ____ ns tCHZ(1) Chip Select High to Output in High-Z ____ 5 ____ 6 ____ 6 ____ 8 ns tOE Output Enable Low to Output Valid ____ 5 ____ 6 ____ 7 ____ 8 ns tOLZ(1) Output Enable Low to Output in Low-Z 0 ____ 0 ____ 0 ____ 0 ____ ns tOHZ(1) Output Enable High to Output in High-Z ____ 5 ____ 6 ____ 6 ____ 8 ns tOH Output Hold from Address Change 4 — 4 — 4 — 4 — ns tBE Byte Enable Low to Output Valid — 5 — 6 — 7 ____ 8 ns tBLZ(1) Byte Enable Low to Output in Low-Z 0 ____ 0 ____ 0 ____ 0 ____ ns tBHZ(1) Byte Enable High to Output in High-Z ____ 5 ____ 6 ____ 6 ____ 8 ns WRITE CYCLE tWC Write Cycle Time 10 ____ 12 ____ 15 ____ 20 ____ ns tAW Address Valid to End of Write 7 ____ 8 ____ 10 ____ 12 ____ ns tCW Chip Select Low to End of Write 7 ____ 8 ____ 10 ____ 12 ____ ns tBW Byte Enable Low to End of Write 7 ____ 8 ____ 10 ____ 12 ____ ns tAS Address Set-up Time 0 ____ 0 ____ 0 ____ 0 ____ ns tWR Address Hold from End of Write 0 ____ 0 ____ 0 ____ 0 ____ ns tWP Write Pulse Width 7 ____ 8 ____ 10 ____ 12 ____ ns tDW Data Valid to End of Write 5 ____ 6 ____ 7 ____ 9 ____ ns tDH Data Hold Time 0 ____ 0 ____ 0 ____ 0 ____ ns tOW(1) Write Enable High to Output in Low-Z 3 ____ 3 ____ 3 ____ 3 ____ ns tWHZ(1) Write Enable Low to Output in High-Z ____ 5 ____ 6 ____ 6 ____ 8 ns NOTE: 3834 tbl 10 1. This parameter is guaranteed with the AC Load (Figure 2) by device characterization, but is not production tested. Timing Waveform of Read Cycle No. 1(1,2,3) tRC ADDRESS tAA tOH tOH DATAOUT PREVIOUSDATAOUTVALID DATAOUTVALID NOTES: 3834drw06 1. WE is HIGH for Read Cycle. 2. Device is continuously selected, CS is LOW. 3. OE, BHE, and BLE are LOW. 5 Jun.23.20

71V016SA, 3.3V CMOS Static RAM 1 Meg (64K x 16-Bit) Commercial and Industrial Temperature Ranges Timing Waveform of Read Cycle No. 2(1) tRC ADDRESS tAA tOH OE (3) tOE tOHZ (3) tOLZ CS tCLZ(3) tACS(2) tCHZ(3) BHE,BLE tBE(2) tBHZ(3) (3) tBLZ DATAOUT DATAOUTVALID 3834drw07 NOTES: 1. WE is HIGH for Read Cycle. 2. Address must be valid prior to or coincident with the later of CS, BHE, or BLE transition LOW; otherwise tAA is the limiting parameter. 3. Transition is measured ±200mV from steady state. Timing Waveform of Write Cycle No. 1 (WE Controlled Timing)(1,2,4) tWC ADDRESS tAW CS tCW(2) tCHZ(5) tBW BHE,BLE tWR tBHZ (5) tWP WE tAS (5) tWHZ (5) tOW DATAOUT PREVIOUSDATAVALID (3) DATAVALID tDW tDH DATAIN DATAINVALID 3834drw08 NOTES: 1. A write occurs during the overlap of a LOW CS, LOW BHE or BLE, and a LOW WE. 2. OE is continuously HIGH. If during a WE controlled write cycle OE is LOW, tWP must be greater than or equal to tWHZ + tDW to allow the I/O drivers to turn off and data to be placed on the bus for the required tDW. If OE is HIGH during a WE controlled write cycle, this requirement does not apply and the minimum write pulse is as short as the specified tWP. 3. During this period, I/O pins are in the output state, and input signals must not be applied. 4. If the CS LOW or BHE and BLE LOW transition occurs simultaneously with or after the WE LOW transition, the outputs remain in a high-impedance state. 5. Transition is measured ±200mV from steady state. 6 Jun.23.20

71V016SA, 3.3V CMOS Static RAM 1 Meg (64K x 16-Bit) Commercial and Industrial Temperature Ranges Timing Waveform of Write Cycle No. 2 (CS Controlled Timing)(1,4) tWC ADDRESS tAW CS tAS tCW(2) tBW BHE,BLE tWP tWR WE DATAOUT tDH tDW DATAIN DATAINVALID 3834drw09 Timing Waveform of Write Cycle No. 3 (BHE, BLE Controlled Timing)(1,4) tWC ADDRESS tAW CS (2) tCW tAS tBW BHE,BLE tWP tWR WE DATAOUT tDW tDH DATAIN DATAINVALID 3834drw10 NOTES: 1. A write occurs during the overlap of a LOW CS, LOW BHE or BLE, and a LOW WE. 2. OE is continuously HIGH. If during a WE controlled write cycle OE is LOW, tWP must be greater than or equal to tWHZ + tDW to allow the I/O drivers to turn off and data to be placed on the bus for the required tDW. If OE is HIGH during a WE controlled write cycle, this requirement does not apply and the minimum write pulse is as short as the specified tWP. 3. During this period, I/O pins are in the output state, and input signals must not be applied. 4. If the CS LOW or BHE and BLE LOW transition occurs simultaneously with or after the WE LOW transition, the outputs remain in a high-impedance state. 5. Transition is measured ±200mV from steady state. 7 Jun.23.20

71V016SA, 3.3V CMOS Static RAM 1 Meg (64K x 16-Bit) Commercial and Industrial Temperature Ranges Ordering Information 71V016 SA XX XXX X X X Process/ Device Power Speed Package Temperature Type Range Blank Tube or Tray 8 Tape and Reel Blank Commercial (0°C to +70°C) I(1) Industrial (-40°C to +85°C) G(2) Green Y 400-mil SOJ (PBG44) PH 400-mil TSOP Type II (PHG44) BF 7.0 x 7.0 mm FBGA (BF48, BFG48) 10 12 Speed in nanoseconds 15 20 3834 drw 11 NOTE: 1. Contact your local sales office for industrial temp. range for other speeds, packages and powers. 2. Green parts available. For specific speeds, packages and powers contact your local sales office. Note that information regarding recently obsoleted parts are included in this datasheet for customer convenience. 8 Jun.23.20

IDT71V016SA, 3.3V CMOS Static RAM 1 Meg (64K x 16-bit) Commercial and Industrial Temperature Ranges Orderable Part Information Speed Pkg. Pkg. Temp. Speed Pkg. Pkg. Temp. Orderable Part ID Orderable Part ID (ns) Code Type Grade (ns) Code Type Grade 10 71V016SA10BF BF48 CABGA C 15 71V016SA15BF BF48 CABGA C 71V016SA10BF8 BF48 CABGA C 71V016SA15BF8 BF48 CABGA C 71V016SA10BFG BFG48 CABGA C 71V016SA15BFG BFG48 CABGA C 71V016SA10BFG8 BFG48 CABGA C 71V016SA15BFG8 BFG48 CABGA C 71V016SA10BFGI BFG48 CABGA I 71V016SA15BFGI BFG48 CABGA I 71V016SA10BFGI8 BFG48 CABGA I 71V016SA15BFGI8 BFG48 CABGA I 71V016SA10PHG PHG44 TSOP C 71V016SA15BFI BF48 CABGA I 71V016SA10PHG8 PHG44 TSOP C 71V016SA15BFI8 BF48 CABGA I 71V016SA10PHGI PHG44 TSOP I 71V016SA15PHG PHG44 TSOP C 71V016SA10PHGI8 PHG44 TSOP I 71V016SA15PHG8 PHG44 TSOP C 71V016SA10YG PBG44 SOJ C 71V016SA15PHGI PHG44 TSOP I 71V016SA10YG8 PBG44 SOJ C 71V016SA15PHGI8 PHG44 TSOP I 12 71V016SA12BF BF48 CABGA C 71V016SA15YG PBG44 SOJ C 71V016SA12BF8 BF48 CABGA C 71V016SA15YG8 PBG44 SOJ C 71V016SA12BFG BFG48 CABGA C 71V016SA15YGI PBG44 SOJ I 71V016SA12BFG8 BFG48 CABGA C 71V016SA15YGI8 PBG44 SOJ I 71V016SA12BFGI BFG48 CABGA I 20 71V016SA20BF BF48 CABGA C 71V016SA12BFGI8 BFG48 CABGA I 71V016SA20BF8 BF48 CABGA C 71V016SA12BFI BF48 CABGA I 71V016SA20BFG BFG48 CABGA C 71V016SA12BFI8 BF48 CABGA I 71V016SA20BFG8 BFG48 CABGA C 71V016SA12PHG PHG44 TSOP C 71V016SA20BFGI BFG48 CABGA I 71V016SA12PHG8 PHG44 TSOP C 71V016SA20BFGI8 BFG48 CABGA I 71V016SA12PHGI PHG44 TSOP I 71V016SA20BFI BF48 CABGA I 71V016SA12PHGI8 PHG44 TSOP I 71V016SA20BFI8 BF48 CABGA I 71V016SA12YG PBG44 SOJ C 71V016SA20PHG PHG44 TSOP C 71V016SA12YG8 PBG44 SOJ C 71V016SA20PHG8 PHG44 TSOP C 71V016SA12YGI PBG44 SOJ I 71V016SA20PHGI PHG44 TSOP I 71V016SA12YGI8 PBG44 SOJ I 71V016SA20PHGI8 PHG44 TSOP I 71V016SA20YG PBG44 SOJ C 71V016SA20YG8 PBG44 SOJ C 71V016SA20YGI PBG44 SOJ I 71V016SA20YGI8 PBG44 SOJ I 9 Jun.15.20

71V016SA, 3.3V CMOS Static RAM 1 Meg (64K x 16-Bit) Commercial and Industrial Temperature Ranges Datasheet Document History 01/07/00 Updated to new format Pg. 1, 3, 5, 8 Added Industrial Temperature range offerings Pg. 2 Numbered I/Os and address pins on FBGA Top View Pg. 6 Revised footnotes on Write Cycle No. 1 diagram Pg. 7 Revised footnotes on Write Cycle No. 2 and No. 3 diagrams Pg. 9 Added Datasheet Document History 08/30/00 Pg. 3 Tighten ICC and ISB. Pg. 5 Tighten tCLZ, tCHZ, tOHZ, tBHZ and tWHZ 08/22/01 Pg. 8 Removed footnote "available in 15ns and 20ns only" 06/20/02 Pg. 8 Added tape and reel field to ordering information 01/30/04 Pg. 8 Added "Restricted hazardous substance device" to ordering information. 09/27/06 Pg. 8 Corrected ordering information, changed position of I and G. 02/14/07 Pg.8 Added H step generation to data sheet ordering information. 06/26/07 Pg.3 Changed typical parameters for ICC, DC electrical characteristics table. 10/13/08 Pg.8 Removed "IDT" from orderable part number 10/11/11 Pg.1,8 Updated datasheet with removal of Obsolete HSA part number. 08/13/13 Pg.1,3,5,8 Added 10ns for Industrial Temperature range offerings. 06/23/20 Pg.1 - 9 Rebranded as Renesas datasheet Pg.1 & 8 Updated Industrial temp and Green availability Pg.2 & 8 Updated package codes Pg.9 Added Orderable Part Information tables 10 Jun.23.20

IMPORTANT NOTICE AND DISCLAIMER RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES (“RENESAS”) PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS. These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products. (Rev.1.0 Mar 2020) Corporate Headquarters Contact Information TOYOSU FORESIA, 3-2-24 Toyosu, For further information on a product, technology, the most Koto-ku, Tokyo 135-0061, Japan up-to-date version of a document, or your nearest sales www.renesas.com office, please visit: www.renesas.com/contact/ Trademarks Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners. © 2020 Renesas Electronics Corporation. All rights reserved.

Datasheet下载

Datasheet下载