ICGOO在线商城 > 511MAA-CAAG

- 型号: 511MAA-CAAG

- 制造商: Silicon Laboratories

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

511MAA-CAAG产品简介:

ICGOO电子元器件商城为您提供511MAA-CAAG由Silicon Laboratories设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 提供511MAA-CAAG价格参考以及Silicon Laboratories511MAA-CAAG封装/规格参数等产品信息。 你可以下载511MAA-CAAG参考资料、Datasheet数据手册功能说明书, 资料中有511MAA-CAAG详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 晶体和振荡器 |

| 描述 | OSC PROG 3.3V CMOS 50PPM 5X7MM |

| 产品分类 | |

| 品牌 | Silicon Laboratories Inc |

| 数据手册 | |

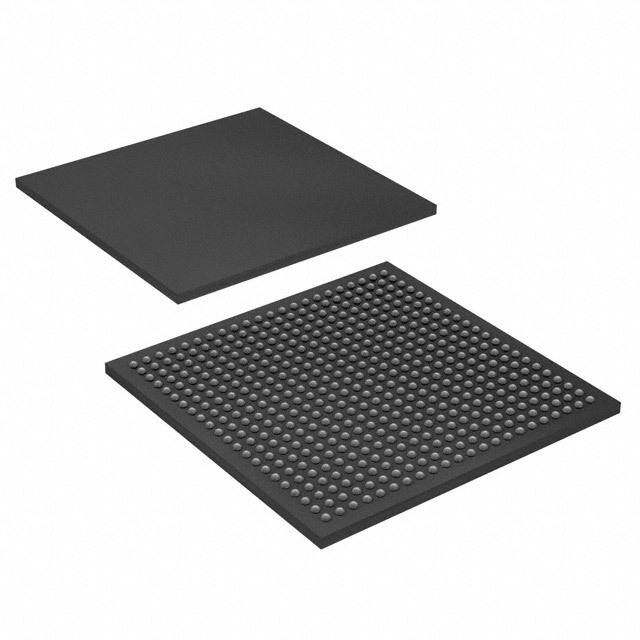

| 产品图片 |

|

| 产品型号 | 511MAA-CAAG |

| rohs | 无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | Si511 |

| 产品培训模块 | http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=30227 |

| 功能 | 三态(输出启用) |

| 包装 | 托盘 |

| 可用频率范围 | 170MHz ~ 250MHz |

| 大小/尺寸 | 0.276" 长 x 0.197" 宽(7.00mm x 5.00mm) |

| 安装类型 | 表面贴装 |

| 封装/外壳 | 6-SMD,无引线(DFN,LCC) |

| 工作温度 | -40°C ~ 85°C |

| 扩频带宽 | - |

| 标准包装 | 1 |

| 特色产品 | http://www.digikey.cn/product-highlights/cn/zh/silicon-laboratories-si510-511/3785 |

| 电压-电源 | 3.3V |

| 电流-电源(最大值) | 26mA |

| 电流-电源(禁用)(最大值) | 18mA |

| 类型 | 由 Digi-Key 编程(请在网站订购单中输入您需要的频率) |

| 输出 | CMOS,双通道(同步) |

| 频率稳定度 | ±50ppm |

| 高度 | 0.071"(1.80mm) |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

Si510/511 CRYSTAL OSCILLATOR (XO) 100 kHZ TO 250 MHZ Features Supports any frequency from 3.3, 2.5, or 1.8V operation Si5602 100kHz to 250MHz Differential (LVPECL, LVDS, Low jitter operation HCSL) or CMOS output options 2 to 4 week lead times Optional integrated 1:2 CMOS Total stability includes 10-year fanout buffer aging Runt suppression on OE and Comprehensive production test power on coverage includes crystal ESR and Industry standard 5x7, 3.2x5, 2.5x3.2mm DLD and 2.5x3.2mm packages On-chip LDO regulator for power Pb-free, RoHS compliant supply noise filtering –40 to 85oC operation 5x7mm and 3.2x5mm Ordering Information: Applications See page14. SONET/SDH/OTN 3G-SDI/HD-SDI/SDI Gigabit Ethernet Telecom Pin Assignments: Fibre Channel/SAS/SATA Switches/routers PCI Express FPGA/ASIC clock generation See page12. Description The Si510/511 XO utilizes Silicon Laboratories' advanced DSPLL technology OE 1 4 VDD to provide any frequency from 100kHz to 250MHz. Unlike a traditional XO where a different crystal is required for each output frequency, the Si510/511 uses one fixed crystal and Silicon Labs’ proprietary DSPLL synthesizer to generate any frequency across this range. This IC-based approach allows GND 2 3 CLK the crystal resonator to provide enhanced reliability, improved mechanical robustness, and excellent stability. In addition, this solution provides superior supply noise rejection, simplifying low jitter clock generation in noisy Si510 (CMOS) environments. Crystal ESR and DLD are individually production-tested to guarantee performance and enhance reliability. The Si510/511 is factory- NC 1 6 VDD configurable for a wide variety of user specifications, including frequency, supply voltage, output format, output enable polarity, and stability. Specific OE 2 5 CLK– configurations are factory-programmed at time of shipment, eliminating long lead times and non-recurring engineering charges associated with custom frequency oscillators. GND 3 4 CLK+ Functional Block Diagram Si510(LVDS/LVPECL/HCSL/ Dual CMOS) V DD OE Low Noise Regulator OOEE 11 66 VVDDDD Fixed Any-Frequency CLK+ NNCC 22 55 CCLLKK–– Frequency 0.1 to 250 MHz Oscillator DSPLL® Synthesis CLK– GGNNDD 33 44 CCLLKK++ Si511(LVDS/LVPECL/HCSL/ GND Dual CMOS) Rev. 1.4 6/18 Copyright © 2018 by Silicon Laboratories Si510/511

Si510/511 TABLE OF CONTENTS Section Page 1. Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3 2. Solder Reflow and Rework Requirements for 2.5x3.2 mm Packages . . . . . . . . . . . . . .11 3. Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12 3.1 Dual CMOS Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13 4. Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 5. Si510/511 Mark Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15 6. Package Outline Diagram: 5 x 7 mm, 4-pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16 7. PCB Land Pattern: 5 x 7 mm, 4-pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17 8. Package Outline Diagram: 5 x 7 mm, 6-pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18 9. PCB Land Pattern: 5 x 7 mm, 6-pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19 10. Package Outline Diagram: 3.2 x 5 mm, 4-pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20 11. PCB Land Pattern: 3.2 x 5 mm, 4-pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21 12. Package Outline Diagram: 3.2 x 5 mm, 6-Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22 13. PCB Land Pattern: 3.2 x 5.0 mm, 6-pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23 14. Package Outline Diagram: 2.5 x 3.2 mm, 4-pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24 15. PCB Land Pattern: 2.5 x 3.2 mm, 4-pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 16. Package Outline Diagram: 2.5 x 3.2 mm, 6-pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27 17. PCB Land Pattern: 2.5 x 3.2 mm, 6-pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 Document Change List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30 2 Rev. 1.4

Si510/511 1. Electrical Specifications Table 1. Operating Specifications V = 1.8V ±5%, 2.5 or 3.3V ±10%, T = –40 to +85oC DD A Parameter Symbol Test Condition Min Typ Max Unit Supply Voltage V 3.3V option 2.97 3.3 3.63 V DD 2.5V option 2.25 2.5 2.75 V 1.8V option 1.71 1.8 1.89 V Supply Current I CMOS, 100MHz, — 21 26 mA DD single-ended LVDS — 19 23 mA (output enabled) LVPECL — 39 43 mA (output enabled) HCSL — 41 44 mA (output enabled) Tristate — — 18 mA (output disabled) OE "1" Setting V See Note 0.80xV — — V IH DD OE "0" Setting V See Note — — 0.20xV V IL DD OE Internal Pull-Up/Pull- R — 45 — k I Down Resistor* Operating Temperature T –40 — 85 oC A *Note: Active high and active low polarity OE options available. Active high option includes an internal pull-up. Active low option includes an internal pull-down. See ordering information on page14. Rev. 1.4 3

Si510/511 Table 2. Output Clock Frequency Characteristics V = 1.8V ±5%, 2.5 or 3.3V ±10%, T = –40 to +85oC DD A Parameter Symbol Test Condition Min Typ Max Unit Nominal Frequency F CMOS, Dual CMOS 0.1 — 212.5 MHz O F LVDS/LVPECL/HCSL 0.1 — 250 MHz O Total Stability* Frequency Stability Grade C –30 — +30 ppm Frequency Stability Grade B –50 — +50 ppm Frequency Stability Grade A –100 — +100 ppm Temperature Stability Frequency Stability Grade C –20 — +20 ppm Frequency Stability Grade B –25 — +25 ppm Frequency Stability Grade A –50 — +50 ppm Startup Time T Minimum V until output — — 10 ms SU DD frequency (F ) within specification O Disable Time T F 10MHz — — 5 µs D O F <10MHz — — 40 µs O Enable Time T F 10MHz — — 20 µs E O F <10MHz — — 60 µs O *Note: Total stability includes initial accuracy, operating temperature, supply voltage change, load change, shock and vibration (not under operation), and 10 years aging at 40oC. 4 Rev. 1.4

Si510/511 Table 3. Output Clock Levels and Symmetry V = 1.8V ±5%, 2.5 or 3.3V ±10%, T = –40 to +85oC DD A Parameter Symbol Test Condition Min Typ Max Unit CMOS Output Logic V 0.85xV — — V OH DD High CMOS Output Logic V — — 0.15xV V OL DD Low CMOS Output Logic I 3.3V –8 — — mA OH High Drive 2.5V –6 — — mA 1.8V –4 — — mA CMOS Output Logic I 3.3V 8 — — mA OL Low Drive 2.5V 6 — — mA 1.8V 4 — — mA CMOS Output Rise/Fall T /T 0.1 to 212.5MHz, 0.45 0.8 1.2 ns R F Time C = 15pF L (20 to 80% V ) DD 0.1 to 212.5MHz, 0.3 0.6 0.9 ns C = no load L LVPECL Output T /T 100 — 565 ps R F Rise/Fall Time (20 to 80% VDD) HCSL Output Rise/Fall T /T 100 — 470 ps R F Time (20 to 80% VDD) LVDS Output Rise/Fall T /T 350 — 800 ps R F Time (20 to 80% VDD) LVPECL Output V 50 to V – 2V, — V – — V OC DD DD Common Mode single-ended 1.4V LVPECL Output Swing V 50 to V – 2V, 0.55 0.8 0.90 V O DD PPSE single-ended LVDS Output Common V 100 line-line 1.13 1.23 1.33 V OC Mode V =3.3/2.5V DD 100 line-line, V =1.8V 0.83 0.92 1.00 V DD LVDS Output Swing V Single-ended, 100differential 0.25 0.35 0.45 V O PPSE termination HCSL Output Common V 50to ground 0.35 0.38 0.42 V OC Mode HCSL Output Swing V Single-ended 0.58 0.73 0.85 V O PPSE Duty Cycle DC All formats 48 50 52 % Rev. 1.4 5

Si510/511 Table 4. Output Clock Jitter and Phase Noise (LVPECL) V = 2.5 or 3.3V ±10%, T = –40 to +85oC; Output Format = LVPECL DD A Parameter Symbol Test Condition Min Typ Max Unit Period Jitter JPRMS 10k samples1 — — 1.3 ps (RMS) Period Jitter JPPKPK 10k samples1 — — 11 ps (Pk-Pk) Phase Jitter φJ 1.875MHz to 20MHz integration — 0.31 0.5 ps (RMS) bandwidth2 (brickwall) 12kHz to 20MHz integration band- — 0.8 1.0 ps width2 (brickwall) Phase Noise, φN 100Hz — –86 — dBc/Hz 156.25MHz 1kHz — –109 — dBc/Hz 10kHz — –116 — dBc/Hz 100kHz — –123 — dBc/Hz 1MHz — –136 — dBc/Hz Additive RMS JPSR 10kHz sinusoidal noise — 3.0 — ps Jitter Due to External Power 100kHz sinusoidal noise — 3.5 — ps Supply Noise3 500kHz sinusoidal noise — 3.5 — ps 1MHz sinusoidal noise — 3.5 — ps Spurious SPR LVPECL output, 156.25MHz, — –75 — dBc offset>10kHz Notes: 1. Applies to output frequencies: 74.17582, 74.25, 75, 77.76, 100, 106.25, 125, 148.35165, 148.5, 150, 155.52, 156.25, 212.5, 250MHz. 2. Applies to output frequencies: 100, 106.25, 125, 148.35165, 148.5, 150, 155.52, 156.25, 212.5 and 250 MHz. 3. 156.25MHz. Increase in jitter on output clock due to sinewave noise added to VDD (2.5/3.3 V = 100mVPP). 6 Rev. 1.4

Si510/511 Table 5. Output Clock Jitter and Phase Noise (LVDS) V = 1.8V ±5%, 2.5 or 3.3V ±10%, T = –40 to +85oC; Output Format=LVDS DD A Parameter Symbol Test Condition Min Typ Max Unit Period Jitter JPRMS 10k samples1 — — 2.1 ps (RMS) Period Jitter JPPKPK 10k samples1 — — 18 ps (Pk-Pk) Phase Jitter φJ 1.875MHz to 20MHz integration — 0.25 0.55 ps (RMS) bandwidth2 (brickwall) 12kHz to 20MHz integration band- — 0.8 1.0 ps width2 (brickwall) Phase Noise, φN 100Hz — –86 — dBc/Hz 156.25MHz 1kHz — –109 — dBc/Hz 10kHz — –116 — dBc/Hz 100kHz — –123 — dBc/Hz 1MHz — –136 — dBc/Hz Spurious SPR LVPECL output, 156.25MHz, — –75 — dBc offset>10kHz Notes: 1. Applies to output frequencies: 74.17582, 74.25, 75, 77.76, 100, 106.25, 125, 148.35165, 148.5, 150, 155.52, 156.25, 212.5, 250MHz. 2. Applies to output frequencies: 100, 106.25, 125, 148.35165, 148.5, 150, 155.52, 156.25, 212.5 and 250 MHz. Rev. 1.4 7

Si510/511 Table 6. Output Clock Jitter and Phase Noise (HCSL) V = 1.8V ±5%, 2.5 or 3.3V ±10%, T = –40 to +85oC; Output Format=HCSL DD A Parameter Symbol Test Condition Min Typ Max Unit Period Jitter JPRMS 10k samples* — — 1.2 ps (RMS) Period Jitter JPPKPK 10k samples* — — 11 ps (Pk-Pk) Phase Jitter φJ 1.875MHz to 20MHz integration — 0.25 0.30 ps (RMS) bandwidth*(brickwall) 12kHz to 20MHz integration band- — 0.8 1.0 ps width* (brickwall) Phase Noise, φN 100Hz — –90 — dBc/Hz 156.25MHz 1kHz — –112 — dBc/Hz 10kHz — –120 — dBc/Hz 100kHz — –127 — dBc/Hz 1MHz — –140 — dBc/Hz Spurious SPR LVPECL output, 156.25MHz, — –75 — dBc offset>10kHz *Note: Applies to an output frequency of 100MHz. 8 Rev. 1.4

Si510/511 Table 7. Output Clock Jitter and Phase Noise (CMOS, Dual CMOS (Complementary)) V = 1.8V ±5%, 2.5 or 3.3V ±10%, T = –40 to +85oC; Output Format=CMOS, Dual CMOS (Complementary) DD A Parameter Symbol Test Condition Min Typ Max Unit Phase Jitter φJ 1.875MHz to 20MHz integration — 0.25 0.35 ps (RMS) bandwidth2 (brickwall) 12kHz to 20MHz integration band- — 0.8 1.0 ps width2 (brickwall) Phase Noise, φN 100Hz — –86 — dBc/Hz 156.25MHz 1kHz — –108 — dBc/Hz 10kHz — –115 — dBc/Hz 100kHz — –123 — dBc/Hz 1MHz — –136 — dBc/Hz Spurious SPR LVPECL output, 156.25MHz, — –75 — dBc offset>10kHz Notes: 1. Applies to output frequencies: 74.17582, 74.25, 75, 77.76, 100, 106.25, 125, 148.35165, 148.5, 150, 155.52, 156.25, 212.5MHz. 2. Applies to output frequencies: 100, 106.25, 125, 148.35165, 148.5, 150, 155.52, 156.25, 212.5MHz. Table 8. Environmental Compliance and Package Information Parameter Conditions/Test Method Mechanical Shock MIL-STD-883, Method 2002 Mechanical Vibration MIL-STD-883, Method 2007 Solderability MIL-STD-883, Method 2003 Gross and Fine Leak MIL-STD-883, Method 1014 Resistance to Solder Heat MIL-STD-883, Method 2036 Contact Pads Gold over Nickel Rev. 1.4 9

Si510/511 Table 9. Thermal Characteristics Parameter Symbol Test Condition Value Unit CLCC, Thermal Resistance Junction to Ambient Still air 110 °C/W JA 2.5x3.2mm, Thermal Resistance Junction to Ambient Still air 164 °C/W JA Table 10. Absolute Maximum Ratings1 Parameter Symbol Rating Unit Maximum Operating Temperature T 85 oC AMAX Storage Temperature T –55 to +125 oC S Supply Voltage V –0.5 to +3.8 V DD Input Voltage (any input pin) V –0.5 to V + 0.3 V I DD ESD Sensitivity (HBM, per JESD22-A114) HBM 2 kV Soldering Temperature (Pb-free profile)2 T 260 oC PEAK Soldering Temperature Time at TPEAK (Pb-free profile)2 TP 20–40 sec Notes: 1. Stresses beyond those listed in this table may cause permanent damage to the device. Functional operation or specification compliance is not implied at these conditions. Exposure to maximum rating conditions for extended periods may affect device reliability. 2. The device is compliant with JEDEC J-STD-020E. 10 Rev. 1.4

Si510/511 2. Solder Reflow and Rework Requirements for 2.5x3.2 mm Packages Reflow of Silicon Labs' components should be done in a manner consistent with the IPC/JEDEC J-STD-20E standard. The temperature of the package is not to exceed the classification Temperature provided in the standard. The part should not be within -5°C of the classification or peak reflow temperature (T ) for longer than 30 PEAK seconds. Key to maintaining the integrity of the component is providing uniform heating and cooling of the part during reflow and rework. Uniform heating is achieved through having a preheat soak and controlling the temperature ramps in the process. J-STD-20E provides minimum and maximum temperatures and times for the preheat/Soak step that need to be followed, even for rework. The entire assembly area should be heated during rework. Hot air should be flowed from both the bottom of the board and the top of the component. Heating from the top only will cause un-even heating of component and can lead to part integrity issues. Temperature Ramp-up rate are not to exceed 3°C/second. Temperature ramp-down rates from peak to final temperature are not to exceed 6°C/second. Time from 25°C to peak temperature is not to exceed 8 min for Pb-free solders. Rev. 1.4 11

Si510/511 3. Pin Descriptions OE 1 4 VDD NC 1 6 VDD OE 1 6 VDD OE 2 5 CLK–* NC 2 5 CLK–* GND 2 3 CLK GND 3 4 CLK+ GND 3 4 CLK+ Si510 (CMOS) Si510 (LVDS/LVPECL/HCSL/Dual CMOS*) Si511 (LVDS/LVPECL/HCSL/DualCMOS)*) *Supports integrated 1:2 CMOS buffer. See ordering information and section 2.1“Dual CMOS Buffer”. Table 11. Si510 Pin Descriptions (CMOS) Pin Name CMOS Function 1 OE Output Enable. Includes internal pull-up for OE active high. Includes internal pull-down for OE active low. See ordering information. 2 GND Electrical and Case Ground. 3 CLK Clock Output. 4 V Power Supply Voltage. DD Table 12. Si510 Pin Descriptions (LVPECL/LVDS/HCSL, Dual CMOS, OE Pin 2) Pin Name LVPECL/LVDS/HCSL Function 1 NC No connect. Make no external connection to this pin. 2 OE Output Enable. Includes internal pull-up for OE active high. Includes internal pull-down for OE active low. See ordering information. 3 GND Electrical and Case Ground. 4 CLK+ Clock Output. 5 CLK– Complementary Clock Output. 6 V Power Supply Voltage. DD Table 13. Si511 Pin Descriptions (LVPECL/LVDS/HCSL, Dual CMOS, OE Pin 1) Pin Name LVPECL/LVDS/HCSL Function 1 OE Output Enable. Includes internal pull-up for OE active high. Includes internal pull-down for OE active low. See ordering information. 2 NC No connect. Make no external connection to this pin. 3 GND Electrical and Case Ground. 4 CLK+ Clock Output. 5 CLK– Complementary Clock Output. 6 V Power Supply Voltage. DD 12 Rev. 1.4

Si510/511 3.1. Dual CMOS Buffer Dual CMOS output format ordering options support either complementary or in-phase output signals. This feature enables replacement of multiple XOs with a single Si510/11 device. ~ Complementary Outputs ~ In-Phase Outputs Figure 1. Integrated 1:2 CMOS Buffer Supports Complementary or In-Phase Outputs Rev. 1.4 13

Si510/511 4. Ordering Information The Si510/511 supports a wide variety of options including frequency, stability, output format, and V . Specific DD device configurations are programmed into the Si510/511 at time of shipment. Configurations can be specified using the Part Number Configuration chart below. Silicon Labs provides a web browser-based part number configuration utility to simplify this process. To access this tool refer to www.silabs.com/oscillators and click “Customize” in the product table. The Si510/511 XO series is supplied in industry-standard, RoHS compliant, lead- free, 2.5x3.2 mm, 3.2x5.0mm, and 5x7mm packages. Tape and reel packaging is an ordering option. Series Output Format OE Pin Package A = Revision: A 510 CMOS OE on pin 1 4-pin G = Temp Range: -40°C to 85°C(cid:3) 510 LVPECL, LVDS, HCSL, Dual CMOS OE on pin 2 6-pin R = Tape & Reel; Blank = (cid:38)(cid:82)(cid:76)(cid:79)(cid:3)(cid:55)(cid:68)(cid:83)(cid:72) 511 LVPECL, LVDS, HCSL, Dual CMOS OE on pin 1 6-pin 1stOption Code: Output Format 5511XX XX XX XX XXXXXXMMXXXXXX XX AAGGRR VVDDDD OOuuttppuutt FFoorrmmaatt A 3.3V LVPECL B 3.3V LVDS C 3.3V CMOS DD 33.33VV HHCCSSLL 3rdOption Code: E 2.5V LVPECL Output Enable Package Option F 2.5V LVDS OE Polarity Dimensions G 2.5V CMOS AA OOEE AAccttiivvee HHiigghh AA 55 xx 77 mmmm HH 22.55VV HHCCSSLL B OE Active Low B 3.2 x 5 mm J 1.8V LVDS (cid:38) (cid:21)(cid:17)(cid:24)(cid:3)(cid:91)(cid:3)(cid:22)(cid:17)(cid:21)(cid:3)(cid:80)(cid:80) K 1.8V CMOS Frequency Code L 1.8V HCSL 2ndOption Code: MM 33.33VV DDuall CCMMOOSS ((IIn-phhase)) FFrreeqquueennccyy SSttaabbiilliittyy FFrequency DDescriipttiion N 3.3V Dual CMOS (Complementary) Total Temperature Mxxxxxx f < 1MHz OUT P 2.5V Dual CMOS (In-phase) A ±100ppm ±50ppm xMxxxxx 1MHz (cid:148) fOUT< 10 MHz Q 2.5V Dual CMOS (Complementary) xxMxxxx 10 MHz (cid:148) fOUT< 100 MHz B ±5500ppppm ±255ppppm R 1.8V Dual CMOS (In-phase) xxxMxxx 100 MHz (cid:148) fOUT< 250 MHz S 1.8V Dual CMOS (Complementary) C ±30ppm ±20ppm xxxxxx Code if frequency requires >6 digit resolution Figure 2. Part Number Syntax Example orderable part number: 510ECB156M250AAG supports 2.5V LVPECL, ±30ppm total stability, OE active low in 5x7mm package across –40oC to 85oC temperature range. The output frequency is 156.25MHz. Note: CMOS and Dual CMOS maximum frequency is 212.5MHz. 14 Rev. 1.4

Si510/511 5. Si510/511 Mark Specification Figure3 illustrates the mark specification for the Si510/511. Use the part number configuration utility located at: www.silabs.com/VCXOpartnumber to cross-reference the mark code to a specific device configuration. 0 C C C C C T T T T T T Y Y WW 0 = Si510, 1 = Si511 CCCCC = mark code TTTTTT = assembly manufacturing code YY = year WW = work week Figure 3. Top Mark Rev. 1.4 15

Si510/511 6. Package Outline Diagram: 5 x 7 mm, 4-pin Figure4 illustrates the package details for the 5x7mm Si510/511. Table14 lists the values for the dimensions shown in the illustration. Figure 4. Si510/511 Outline Diagram Table 14. Package Diagram Dimensions (mm) Dimension Min Nom Max A 1.50 1.65 1.80 b 1.30 1.40 1.50 c 0.50 0.60 0.70 D 5.00 BSC D1 4.30 4.40 4.50 e 5.08 BSC f 0.50 TYP E 7.00 BSC E1 6.10 6.20 6.30 H 0.55 0.65 0.75 L 1.17 1.27 1.37 L1 0.05 0.10 0.15 p 2.50 2.60 2.70 aaa 0.15 bbb 0.15 ccc 0.10 ddd 0.10 eee 0.05 Notes: 1. All dimensions shown are in millimeters (mm) unless otherwise noted. 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994. 16 Rev. 1.4

Si510/511 7. PCB Land Pattern: 5 x 7 mm, 4-pin Figure5 illustrates the 5x7mm PCB land pattern for the 5x7mm Si510/511. Table15 lists the values for the dimensions shown in the illustration. Figure 5. Si510/511 PCB Land Pattern Table 15. PCB Land Pattern Dimensions (mm) Dimension (mm) C1 4.20 E 5.08 X1 1.55 Y1 1.95 Notes: General 1. All dimensions shown are in millimeters (mm) unless otherwise noted. 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification. 3. This Land Pattern Design is based on the IPC-7351 guidelines. 4. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05mm. Solder Mask Design 5. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60µm minimum, all the way around the pad. Stencil Design 6. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release. 7. The stencil thickness should be 0.125mm (5 mils). 8. The ratio of stencil aperture to land pad size should be 1:1. Card Assembly 9. A No-Clean, Type-3 solder paste is recommended. 10. The recommended card reflow profile is per the JEDEC/IPC J-STD-020D specification for Small Body Components. Rev. 1.4 17

Si510/511 8. Package Outline Diagram: 5 x 7 mm, 6-pin Figure6 illustrates the package details for the Si510/511. Table16 lists the values for the dimensions shown in the illustration. Figure 6. Si510/511 Outline Diagram Table 16. Package Diagram Dimensions (mm) Dimension Min Nom Max A 1.50 1.65 1.80 b 1.30 1.40 1.50 c 0.50 0.60 0.70 D 5.00 BSC D1 4.30 4.40 4.50 e 2.54 BSC E 7.00 BSC E1 6.10 6.20 6.30 H 0.55 0.65 0.75 L 1.17 1.27 1.37 L1 0.05 0.10 0.15 p 1.80 — 2.60 R 0.70 REF aaa 0.15 bbb 0.15 ccc 0.10 ddd 0.10 eee 0.05 Notes: 1. All dimensions shown are in millimeters (mm) unless otherwise noted. 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994. 18 Rev. 1.4

Si510/511 9. PCB Land Pattern: 5 x 7 mm, 6-pin Figure7 illustrates the 5x7mm PCB land pattern for the Si510/511. Table17 lists the values for the dimensions shown in the illustration. Figure 7. Si510/511 PCB Land Pattern Table 17. PCB Land Pattern Dimensions (mm) Dimension (mm) C1 4.20 E 2.54 X1 1.55 Y1 1.95 Notes: General 1. All dimensions shown are in millimeters (mm) unless otherwise noted. 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification. 3. This Land Pattern Design is based on the IPC-7351 guidelines. 4. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05mm. Solder Mask Design 5. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad. Stencil Design 6. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release. 7. The stencil thickness should be 0.125mm (5 mils). 8. The ratio of stencil aperture to land pad size should be 1:1. Card Assembly 9. A No-Clean, Type-3 solder paste is recommended. 10. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components. Rev. 1.4 19

Si510/511 10. Package Outline Diagram: 3.2 x 5 mm, 4-pin Figure8 illustrates the package details for the 3.2x5mm Si510/511. Table18 lists the values for the dimensions shown in the illustration. Figure 8. Si510/511 Outline Diagram Table 18. Package Diagram Dimensions (mm) Dimension Min Nom Max A 1.06 1.17 1.28 b 1.10 1.20 1.30 c 0.70 0.80 0.90 D 3.20 BSC D1 2.55 2.60 2.65 e 2.54 BSC f 0.40 TYP E 5.00 BSC E1 4.35 4.40 4.45 H 0.40 0.50 0.60 L 0.90 1.00 1.10 L1 0.05 0.10 0.15 p 1.17 1.27 1.37 aaa 0.15 bbb 0.15 ccc 0.10 ddd 0.10 eee 0.05 Notes: 1. All dimensions shown are in millimeters (mm) unless otherwise noted. 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994. 20 Rev. 1.4

Si510/511 11. PCB Land Pattern: 3.2 x 5 mm, 4-pin Figure9 illustrates the 3.2x5mm PCB land pattern for the Si510/511. Table19 lists the values for the dimensions shown in the illustration. Figure 9. Si510/511 PCB Land Pattern Table 19. PCB Land Pattern Dimensions (mm) Dimension (mm) C1 2.60 E 2.54 X1 1.35 Y1 1.70 Notes: General 1. All dimensions shown are in millimeters (mm) unless otherwise noted. 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification. 3. This Land Pattern Design is based on the IPC-7351 guidelines. 4. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05mm. Solder Mask Design 5. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad. Stencil Design 6. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release. 7. The stencil thickness should be 0.125mm (5 mils). 8. The ratio of stencil aperture to land pad size should be 1:1. Card Assembly 9. A No-Clean, Type-3 solder paste is recommended. 10. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components. Rev. 1.4 21

Si510/511 12. Package Outline Diagram: 3.2 x 5 mm, 6-Pin Figure10 illustrates the package details for the 3.2x5mm Si510/511. Table20 lists the values for the dimensions shown in the illustration. Figure 10. Si510/511 Outline Diagram Table 20. Package Diagram Dimensions (mm) Dimension Min Nom Max A 1.06 1.17 1.33 b 0.54 0.64 0.74 c 0.35 0.45 0.55 D 3.20 BSC D1 2.55 2.60 2.65 e 1.27 BSC E 5.00 BSC E1 4.35 4.40 4.45 H 0.45 0.55 0.65 L 0.80 0.90 1.00 L1 0.05 0.10 0.15 p 1.17 1.27 1.37 R 0.32 REF aaa 0.15 bbb 0.15 ccc 0.10 ddd 0.10 eee 0.05 Notes: 1. All dimensions shown are in millimeters (mm) unless otherwise noted. 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994. 22 Rev. 1.4

Si510/511 13. PCB Land Pattern: 3.2 x 5.0 mm, 6-pin Figure11 illustrates the 3.2x5.0mm PCB land pattern for the Si510/511. Table21 lists the values for the dimensions shown in the illustration. Figure 11. Si510/511 Recommended PCB Land Pattern Table 21. PCB Land Pattern Dimensions (mm) Dimension (mm) C1 2.60 E 1.27 X1 0.80 Y1 1.70 Notes: General 1. All dimensions shown are in millimeters (mm) unless otherwise noted. 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification. 3. This Land Pattern Design is based on the IPC-7351 guidelines. 4. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05mm. Solder Mask Design 5. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60µm minimum, all the way around the pad. Stencil Design 6. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release. 7. The stencil thickness should be 0.125mm (5 mils). 8. The ratio of stencil aperture to land pad size should be 1:1. Card Assembly 9. A No-Clean, Type-3 solder paste is recommended. 10. The recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components. Rev. 1.4 23

Si510/511 14. Package Outline Diagram: 2.5 x 3.2 mm, 4-pin Figure12 illustrates the package details for the 2.5x3.2mm Si510/511. Table22 lists the values for the dimensions shown in the illustration. Figure 12. Si510/511 Outline Diagram 24 Rev. 1.4

Si510/511 Table 22. Package Diagram Dimensions (mm) Dimension Min Nom Max A — — 1.1 A1 0.26 REF A2 0.7 REF W 0.65 0.7 0.75 D 3.20 BSC e 2.10 BSC E 2.50 BSC L 0.85 0.9 0.95 E1 1.65 BSC SE 0.825 BSC aaa 0.1 bbb 0.2 ddd 0.08 Notes: 1. All dimensions shown are in millimeters (mm) unless otherwise noted. 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994. Rev. 1.4 25

Si510/511 15. PCB Land Pattern: 2.5 x 3.2 mm, 4-pin Figure illustrates the 2.5x3.2mm PCB land pattern for the Si510/511. Table23 lists the values for the dimensions shown in the illustration. Figure 13. Si510/511 Recommended PCB Land Pattern Table 23. PCB Land Pattern Dimensions (mm) Dimension (mm) C1 2.0 E 2.10 X1 0.95 Y1 1.15 Notes: General 1. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05mm. 2. This Land Pattern Design is based on the IPC-7351 guidelines. Solder Mask Design 3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60µm minimum, all the way around the pad. Stencil Design 4. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release. 5. The stencil thickness should be 0.125mm (5 mils). 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pins. Card Assembly 7. A No-Clean, Type-3 solder paste is recommended. 8. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components. 26 Rev. 1.4

Si510/511 16. Package Outline Diagram: 2.5 x 3.2 mm, 6-pin Figure14 illustrates the package details for the 2.5x3.2mm Si510/511. Table24 lists the values for the dimensions shown in the illustration. Figure 14. Si510/511 Outline Diagram Rev. 1.4 27

Si510/511 Table 24. Package Diagram Dimensions (mm) Dimension Min Nom Max A — — 1.1 A1 0.26 REF A2 0.7 REF W 0.65 0.7 0.75 D 3.20 BSC e 1.25 BSC E 2.50 BSC M 0.30 BSC L 0.45 0.5 0.55 D1 2.5 BSC E1 1.65 BSC SE 0.825 BSC aaa 0.1 bbb 0.2 ddd 0.08 Notes: 1. All dimensions shown are in millimeters (mm) unless otherwise noted. 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994. 28 Rev. 1.4

Si510/511 17. PCB Land Pattern: 2.5 x 3.2 mm, 6-pin Figure15 illustrates the 2.5x3.2mm PCB land pattern for the Si510/511. Table25 lists the values for the dimensions shown in the illustration. Figure 15. Si510/511 Recommended PCB Land Pattern Table 25. PCB Land Pattern Dimensions (mm) Dimension (mm) C1 1.9 E 2.50 X1 0.70 Y1 1.05 Notes: General 3. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05mm. 4. This Land Pattern Design is based on the IPC-7351 guidelines. Solder Mask Design 5. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60µm minimum, all the way around the pad. Stencil Design 6. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release. 7. The stencil thickness should be 0.125mm (5 mils). 8. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pins. Card Assembly 9. A No-Clean, Type-3 solder paste is recommended. 10. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components. Rev. 1.4 29

Si510/511 REVISION HISTORY Revision 1.4 June, 2018 Changed “Trays” to “Coil Tape” in the Ordering Guide. Revision 1.3 December, 2017 Added new 2.5x3.2mm package options. Revision 1.2 Updated Table3. Separated LVPECL and HCSL output Rise/Fall time specs. Min Rise/Fall times added. Revision 1.1 Updated Table3. CMOS Output Rise/Fall Time Test Condition updated. Revision 1.0 Updated Table1 on page3. Updates to supply current typical and maximum values for CMOS, LVDS, LVPECL and HCSL. CMOS frequency test condition corrected to 100MHz. Updates to OE VIH minimum and VIL maximum values. Updated Table2 on page4. Dual CMOS nominal frequency maximum added. Total stability footnotes clarified for 10 year aging at 40°C. Disable time maximum values updated. Enable time parameter added. Updated Table3 on page5. CMOS output rise / fall time typical and maximum values updated. LVPECL/HCSL output rise / fall time maximum value updated. LVPECL output swing maximum value updated. LVDS output common mode typical and maximum values updated. HCSL output swing maximum value updated. Duty cycle minimum and maximum values tightened to 48/52%. Updated Table4 on page6. Phase jitter test condition and maximum value updated. Phase noise typical values updated. Additive RMS jitter due to external power supply noise typical values updated. Footnote 3 updated limiting the VDD to 2.5/3.3V Added Tables 5, 6, 7 for LVDS, HCSL, CMOS, and Dual CMOS operations. Moved Absolute Maximum Ratings table. Added note to Figure2 clarifying CMOS and Dual CMOS maximum frequency. Updated Figure10 outline diagram to correct pinout. 30 Rev. 1.4

ClockBuilder Pro One-click access to Timing tools, documentation, software, source code libraries & more. Available for Windows and iOS (CBGo only). www.silabs.com/CBPro Timing Portfolio SW/HW Quality Support and Community www.silabs.com/timing www.silabs.com/CBPro www.silabs.com/quality community.silabs.com Disclaimer Silicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice to the product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Without prior notification, Silicon Labs may update product firmware during the manufacturing process for security or reliability reasons. Such changes will not alter the specifications or the performance of the product. Silicon Labs shall have no liability for the consequences of use of the information supplied in this document. This document does not imply or expressly grant any license to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any FDA Class III devices, applications for which FDA premarket approval is required or Life Support Systems without the specific written consent of Silicon Labs. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons. Silicon Labs disclaims all express and implied warranties and shall not be responsible or liable for any injuries or damages related to use of a Silicon Labs product in such unauthorized applications. Trademark Information Silicon Laboratories Inc.® , Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga Logo®, ClockBuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world’s most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadioPRO®, Gecko®, Gecko OS, Gecko OS Studio, ISOmodem®, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress® , Zentri, the Zentri logo and Zentri DMS, Z-Wave®, and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. Wi-Fi is a registered trademark of the Wi-Fi Alliance. All other products or brand names mentioned herein are trademarks of their respective holders. Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA http://www.silabs.com

Datasheet下载

Datasheet下载