DDR

词条创建时间:2021-07-08浏览次数:1560

DDR(Double Data Rate) SDRAM就是双倍数据传输率的SDRAM。DDR内存是更先进的SDRAM。SDRAM只在时钟周期的上升沿传输指令、地址和数据。而DDR内存的数据线有特殊的电路,可以让它在时钟的上、下沿都传输数据。

DDRSDRAM的简介

DDR内存是更先进的SDRAM。SDRAM只在时钟周期的上升沿传输指令、地址和数据。而DDR内存的数据线有特殊的电路,可以让它在时钟的上、下沿都传输数据。所以DDR在每个时钟周期可以传输两个数据,而SDRAM只能传输一个数据。举例来说,DDR266能提供266 MHz×2×4 B=2.1 GB/s的内存带宽。另外,由于它是基于SDRAM的设计制造技术,因此厂房、流水线等设备的更新成本可降到最低。这就使得DDR SDRAM的价格比普通的SDRAM贵不了多少(10%)。因此,DDR SDRAM在当前得到了非常广泛的应用。

DDRSDRAM的时序介绍

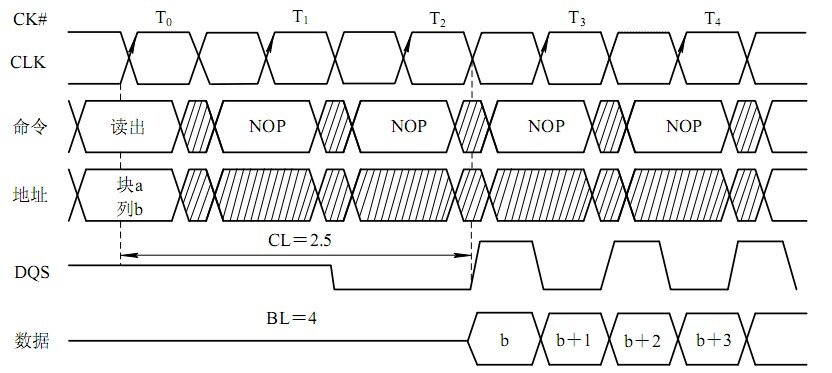

(1) 读出。DDR SDRAM的读出时序关系与SDRAM很相似,如图所示。

(2) 写入。突发写入的时序如图所示。

在图中表示的是突发写入的过程,突发长度为4。由图我们注意到,在写入第一个数据前有一段写入延时tDQSS。

同样,DDR SDRAM是每个时钟周期写入两个数据。

最后要说明的是,为了使用户用好DDR SDRAM,厂家为我们开发了有关的控制器芯片,在将来连接使用时注意去选用。在PC机中,厂家开发出支持DDR SDRAM的北桥芯片,该芯片能提供DDR SDRAM工作所要求的信号,这为用户提供了很大的方便。

DDRDDR SDRAM与SDRAM的区别

DDR SDRAM与SDRAM的不同主要体现在以下几个方面:

(1) 初始化。SDRAM在开始使用前要进行初始化,这项工作主要是对模式寄存器进行设置,即MRS。DDR SDRAM与SDRAM一样,在开机时也要进行MRS,不过由于操作功能的增多,DDR SDRAM在MRS之前还增加了一个扩展模式寄存器设置(EMRS)过程。这个扩展模式寄存器对DLL的有效与禁止、输出驱动强度等功能实施控制。

(2) 时钟。前面介绍SDRAM时已经看到,SDRAM的读/写采用单一时钟。在DDR SDRAM工作中要用差分时钟,也就是两个时钟,一个是CLK,另一个是与之反相的CK#。

CK#并不能被理解为第二个触发时钟(可以在讲述DDR原理时简单地这么比喻),它能起到触发时钟校准的作用。由于数据是在CLK的上下沿触发的,造成传输周期缩短了一半,因此必须要保证传输周期的稳定以确保数据的正确传输,这就要求对CLK的上下沿间距要有精确的控制。但因为温度、电阻性能的改变等原因,CLK上下沿间距可能发生变化,此时与其反相的CK#就起到纠正的作用(CLK上升快下降慢,CK#则是上升慢下降快)。而由于上下沿触发的原因,也使CL=1.5或2.5成为可能,并容易实现。

(3) 数据选取(DQS)脉冲。DQS是DDR SDRAM中的重要信号,其功能主要用来在一个时钟周期内准确地区分出每个传输周期,并使数据得以准确接收。每一块DDR SDRAM芯片都有一个双向的DQS信号线。在写入时,它用来传送由北桥发来的DQS信号;在读取时,则由芯片生成DQS向北桥发送。可以说,DQS就是数据的同步信号。

(4) 写入延时。在写入时,与SDRAM的0延时不一样,DDRSDRAM的写入延迟已经不是0了。在发出写入命令后,DQS与写入数据要等一段时间才会送达。这个周期被称为DQS相对于写入命令的延迟时间。

为什么会有这样的延迟呢?原因也在于同步,毕竟在一个时钟周期内进行两次传送需要很高的控制精度,它必须要等接收方做好充分的准备才行。tDQSS是DDR内存写入操作的一个重要参数,太短的话恐怕接收有误,太长则会造成总线空闲。tDQSS最短不能小于0.75个时钟周期,最长不能超过1.25个时钟周期。

(5) 突发长度与写入掩码。在DDR SDRAM中,突发长度只有2、4、8三种选择,没有了SDRAM的随机存取的操作(突发长度为1)和全页式突发方式。同时,突发长度的定义也与SDRAM的不一样了,它不再指所连续寻址的存储单元数量,而是指连续的传输周期数。

对于突发写入,如果其中有不想存入的数据,仍可以运用DM信号进行屏蔽。DM信号和数据信号同时发出,接收方在DQS的上升沿与下降沿来判断DM的状态,如果DM为高电平,那么之前从DQS脉冲中部选取的数据就被屏蔽了。

(6)延迟锁定回路(DLL)。DDR SDRAM对时钟的精确性有着很高的要求,而DDR SDRAM有两个时钟,一个是外部的总线时钟,一个是内部的工作时钟。在理论上,DDRSDRAM的这两个时钟应该是同步的,但由于种种原因,如温度、电压波动而产生延迟使两者很难同步,更何况时钟频率本身也有不稳定的情况。这就需要根据外部时钟动态修正内部时钟的延迟来实现内部时钟与外部时钟的同步,为此专门设置了DLL。利用这种电路,可使内部时钟与外部时钟保持同步。

DDRSDRAM的结构与接口定义

VDD、VDDQ:电源供电

CLK、/CLK:差分时钟

CKE:时钟使能

/CS:片选信号

BA0-BA1:块选择(决定哪个块进行读、写、刷新、预充电等操作)

/RAS:行地址选取

/CAS:列地址选取

A0-A11:地址

DQ0-DQ15:双向数据

DQS:数据选通信号,控制I/O buffer,数据真正的同步信号

/WE :读/写信号,高电平为读命令,低电平为写命令

DM、/DM:数据标志位,标示当前数据是否为有效数据

DDR规格

SDRAM在一个时钟周期内只传输一次数据,它是在时钟上升期进行数据传输;而DDR则是一个时钟周期内可传输两次数据,也就是在时钟的上升期和下降期各传输一次数据。

ddr芯片和模块

注意:上面列出的数据都是由JEDEC JESD79F指定。所有RAM的上市规格的数据率不一定是JEDEC规范,往往是制造商自行最优化,使用更严格的公差或overvolted芯片。

DDR SDRAM 之间有很大的设计上的差异,设计不同的时钟频率,例如,PC-1600被设计运行在100 MHz,至于PC-2100被设计运行在133 MHz。

DDR SDRAM 的模块用于台式机,被称为DIMMs,有184只引脚(而不是168针SDRAM,或240针脚的DDR2 SDRAM),并可以从不同notches数目来辨别(DDR SDRAM,有一个,SDRAM,SDRAM DIMMs的有两个)。笔记本计算机上的DDR SDRAM 的SO-DIMMs有200只引脚,引脚相同数量的DDR2的SO-DIMMs。这两种规格的缺口也非常相似,如果不能确定正确的匹配,必须小心插入。

ddr记忆芯片

ddr芯片模块

为了要增加内存的容量和带宽,芯片会利用模块结合。例如,有关 DIMMs 的64位bus需要8个 8位的芯片并发处理。与常见的地址线(address lines)的多个芯片被称为memory rank。这个术语被引入,是要避免与芯片内部row和bank的混乱。

DDR公式

利用下列公式,就可以计算出DDR SDRAM时钟频率。

DDRI/II存储器运作时钟频率:实际时钟频率*2。 (由于两笔数据同时传输,200MHz存储器的时钟频率会以400MHz运作。)

存储器带宽=存储器速度*8Byte

标准公式:存储器除频系数=时钟频率/200→*速算法:外频*(除频频率/同步频率) (使用此公式将会导致4%的误差)

DDR高密度比低密度

PC3200是使用带宽 3200 MB / s的DDR - 400芯片设计,在200 MHz的DDR SDRAM 由于 PC3200内存的上升和下降时钟边沿的数据传输,其有效的时钟速率为 400 MHz。

DDR替换

(DDR1)已被DDR2 SDRAM取代,其中有一些修改,以允许更高的时钟频率。与DDR2的竞争是Rambus 公司的XDR DRAM 。DDR3 SDRAM是一个新的标准,提供更高的性能和新功能。

DDR 预取缓冲器(prefetch buffer)深度为2比特,而DDR2采用4位。虽然DDR2的时钟速率高于DDR,但整体性能并没有提升,主要是由于DDR2高延迟(high latency)。直到2004年DDR2才有明显的提升。

购物指南

购物指南 消费保障

消费保障 关于我们

关于我们