Cmos

词条创建时间:2023-04-06浏览次数:5264

CMOS(本意是指互补金属氧化物半导体存储器,是一种大规模应用于集成电路芯片制造的原料)是微机主板上的一块可读写的RAM芯片,主要用来保存当前系统的硬件配置和操作人员对某些参数的设定。CMOS RAM芯片由系统通过一块后备电池供电,因此无论是在关机状态中,还是遇到系统掉电情况,CMOS信息都不会丢失。

Cmos简介

早期的CMOS是一块单独的芯片MC146818A(DIP封装),共有64个字节存放系统信息。386以后的微机一般将 MC146818A芯片集成到其它的IC芯片中(如82C206,PQFP封装),586以后主板上更是将CMOS与系统实时时钟和后备电池集成到一块叫做DALLDA DS1287的芯片中。随着微机的发展、可设置参数的增多,现在的CMOS RAM一般都有128字节及至256字节的容量。为保持兼容性,各BIOS厂商都将自己的BIOS中关于CMOS RAM的前64字节内容的设置统一与MC146818A的CMOS RAM格式一致,而在扩展出来的部分加入自己的特殊设置,所以不同厂家的BIOS芯片一般不能互换,即使是能互换的,互换后也要对CMOS信息重新设置以确保系统正常运行。

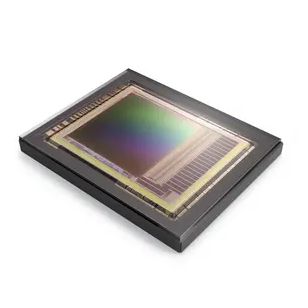

在今日,CMOS制造工艺也被应用于制作数码影像器材的感光元件,尤其是片幅规格较大的单眼数码相机。虽然在用途上与过去CMOS电路主要作为固件或计算工具的用途非常不同,但基本上它仍然是采取CMOS的工艺,只是将纯粹逻辑运算的功能转变成接收外界光线后转化为电能,再透过芯片上的数码─类比转换器(ADC)将获得的影像讯号转变为数码讯号输出。

CMOS(本意是指互补金属氧化物半导体存储器,是一种大规模应用于集成电路芯片制造的原料)是微机主板上的一块可读写的RAM芯片,主要用来保存当前系统的硬件配置和操作人员对某些参数的设定。CMOS RAM芯片由系统通过一块后备电池供电,因此无论是在关机状态中,还是遇到系统掉电情况,CMOS信息都不会丢失。

由于CMOS RAM芯片本身只是一块存储器,只具有保存数据的功能,所以对CMOS中各项参数的设定要通过专门的程序。早期的CMOS设置程序驻留在软盘上的(如IBM的PC/AT机型),使用很不方便。现在多数厂家将CMOS设置程序做到了 BIOS芯片中,在开机时通过按下某个特定键就可进入CMOS设置程序而非常方便地对系统进行设置,因此这种CMOS设置又通常被叫做BIOS设置。

Cmos特点

功耗低

CMOS集成电路采用场效应管,且都是互补结构,工作时两个串联的场效应管总是处于一个管导通,另一个管截止的状态,电路静态功耗理论上为零。实际上,由于存在漏电流,CMOS电路尚有微量静态功耗。单个门电路的功耗典型值仅为20mW,动态功耗(在1MHz工作频率时)也仅为几mW。

工作电压范围宽

CMOS集成电路供电简单,供电电源体积小,基本上不需稳压。国产CC4000系列的集成电路,可在3~18V电压下正常工作。

逻辑摆幅大

CMOS集成电路的逻辑高电平“1”、逻辑低电平“0”分别接近于电源高电位VDD及电影低电位VSS。当VDD=15V,VSS=0V时,输出逻辑摆幅近似15V。因此,CMOS集成电路的电压电压利用系数在各类集成电路中指标是较高的。

抗干扰能力强

CMOS集成电路的电压噪声容限的典型值为电源电压的45%,保证值为电源电压的30%。随着电源电压的增加,噪声容限电压的绝对值将成比例增加。对于VDD=15V的供电电压(当VSS=0V时),电路将有7V左右的噪声容限。

输入阻抗高

CMOS集成电路的输入端一般都是由保护二极管和串联电阻构成的保护网络,故比一般场效应管的输入电阻稍小,但在正常工作电压范围内,这些保护二极管均处于反向偏置状态,直流输入阻抗取决于这些二极管的泄露电流,通常情况下,等效输入阻抗高达103~1011Ω,因此CMOS集成电路几乎不消耗驱动电路的功率。

温度稳定性能好

由于CMOS集成电路的功耗很低,内部发热量少,而且,CMOS电路线路结构和电气参数都具有对称性,在温度环境发生变化时,某些参数能起到自动补偿作用,因而CMOS集成电路的温度特性非常好。一般陶瓷金属封装的电路,工作温度为-55 ~ +125℃;塑料封装的电路工作温度范围为-45 ~ +85℃。

扇出能力强

扇出能力是用电路输出端所能带动的输入端数来表示的。由于CMOS集成电路的输入阻抗极高,因此电路的输出能力受输入电容的限制,但是,当CMOS集成电路用来驱动同类型,如不考虑速度,一般可以驱动50个以上的输入端。

抗辐射能力强

CMOS集成电路中的基本器件是MOS晶体管,属于多数载流子导电器件。各种射线、辐射对其导电性能的影响都有限,因而特别适用于制作航天及核实验设备。

可控性好

CMOS集成电路输出波形的上升和下降时间可以控制,其输出的上升和下降时间的典型值为电路传输延迟时间的125%~140%。

接口方便

因为CMOS集成电路的输入阻抗高和输出摆幅大,所以易于被其他电路所驱动,也容易驱动其他类型的电路或器件。

Cmos设置内容

大致都包含如下可设置的内容:

1.Standard CMOS Setup:标准参数设置,包括日期,时间和软、硬盘参数等。

2.BIOS Features Setup:设置一些系统选项。

3.Chipset Features Setup:主板芯片参数设置。

4.Power Management Setup:电源管理设置。

5.PnP/PCI Configuration Setup:即插即用及PCI插件参数设置。

6.Integrated Peripherals:整合外设的设置。

7.其他:硬盘自动检测,系统口令,加载缺省设置,退出等。

Cmos注意事项

使用CMOS电路时,除了要认真阅读产品说明书或有关资料,了解其引脚分布情况及极限参数之外,还应注意以下问题:

(1)在安装电路、改变电路连接、插拔CMOS器件时,必须切断电源,否则CMOS器件很容易受到极大的感应或电冲击而损坏。

(2)电源问题。CMOS集成电路的工作电源电压一般在3~18V之间,但当系统中有门电路的模拟应用(如脉冲振荡、线性放大)时,最低工作电压则不应低于4.5V。由于工作电压范围宽,故使用不稳压的电源电路也可以工作。CMOS有微功耗的特点,所以特别适用于电池做电源或备用电源,其电路如图1所示。正常工作时,VD1导通,VD2截止,由VA供电。一旦VA不供电,则VD2迅速导通,由VB进行供电。国产C000系列CMOS电路的电源电压允许在7~15V范围内选择。工作在不同电源电压下的器件,其输出阻抗、工作速度和功耗也会不同,在使用中应注意。

(3)驱动能力问题。CMOS电路的驱动能力,除选用驱动能力较强的大缓冲器来提高之外,还可以将同一个芯片几个同类电路并接起来提高,这时驱动能力提高到N倍(N为并联门电路的数量)。

(4)多余输入端的处理。CMOS电路的输入端不允许悬空,因为悬空会使电位不定,破坏正常的逻辑关系。另外,悬空时输入阻抗高,易受外界噪声干扰,使电路产生误动作,而且也极易使栅极感应静电造成击穿。所以,对于“与”门,“与非”门的多余端接高电平,对于“或”门、“或非”门的多余端接低电平。如果电路的工作速度不高,功耗也不需要特别考虑,则可采用多余的输入端和使用端并用的方法加以解决。

(5)输入端的电流不能超过1mA(极限值为10mA),如果不能保证这一点,必须在输入端加适当的电阻进行限流保护。

(6)输入信号不可大于VDD或小于VSS,否则输入保护二极管会因正向偏置而引起大电流。基于这一点,在工作或测试时,必须按照先接通电源后由加入信号,先撤除信号后再关闭电源顺序进行操作。

(7)输入信号的上升或下降时间不宜过长,否则一方面容易造成虚假触发而导致器件失去正常功能,另一方面还会造成大的损耗。对4000B系列,上升或下降时间限于15μs以内;对于74HC系列限于0.5μs以内。如果不满足这个要求,必须使用史密特触发器件输入整形。

(8)输入端接长线时的保护问题。在CMOS电路的输入端与机械接点连接以及其它特殊应用情况下,输入端往往需要接入长线,长输入线必然有较大的分布电容和分布电感,很容易形成LC振荡。特别当输入端一旦发生负电压,容易破坏CMOS中的保护二极管。其保护方法是在输入端串接一个电阻R2,如图2所示,R2=VDD/1mA。

(9)CMOS的接口电路问题。当和运放接口时,如果运放采用双电源,CMOS采用的是独立的另一组电源,则要采用如图3所示的连接方式。在电路中,VD1、VD2作箝位保护,使CMOS输入电压处在10V与地之间。15kΩ的电阻既作为CMOS的限流电阻,又对二极管进行限流保护。如果运放使用单电源,且与CMOS使用的电源一样,则可直接连接。

总之,集成电路在使用过程中,常常涉及到CMOS电路和TTL等其它电路之间的连接问题。由于这些电路相互之间的电源电压和输入、输出电平及电流不相同,因此它们之间的连接必须通过电平转换或电流转换电路,使前级器件的输出电流大于后级器件对输入电流的要求,前级器件输出的逻辑电平满足后级器件对输入电平的要求,并不得对器件造成损坏。逻辑器件的接口电路主要应注意电平匹配和输出能力两个问题,要和器件的电源电压结合起来考虑。

(10)CMOS电路具有很高的输入阻抗,致使器件易受外界干扰、冲击和静电击穿,所以在其内部输入端接有二极管保护电路,如图4所示。其中R约为1.5~2.5kΩ。输入保护网络的引入,使器件的输入阻抗有一定的下降,但仍达到108Ω以上。由于保护电路吸收的瞬变能量有限,太大的瞬变信号和过高的静电电压将使保护电路失去作用。在焊接CMOS管时,电烙铁必须可靠接地,以防电烙铁漏电击穿器件输入端。一般可利用电烙铁断电后的余热焊接,并先焊接其接地脚。

(11)防止用大电阻串入VDD和VSS端,以免在电路开关期间由于电阻上的压降引起保护二极管瞬时导通,而损坏器件。

(12)CMOS器件输出端不允许直接和VDD或VSS连接,否则将导致器件损坏。除三态输出器件外,不允许两个器件并接成逻辑状态,因为不同的器件参数不一致,有可能导致NMOS和PMOS器件同时导通,形成大电流。但为了增加电路的驱动能力,允许把同一芯片上的同类电路并联使用。

(13)对于CMOS电路,如果输入电路中没有一定的抗静电措施,很容易造成电路的毁灭性破坏。虽然各种CMOS输入端有抗静电的保护措施,但仍须小心对待在包装、储存、运输等环节中可能产生的静电问题,可采取多种措施,诸如工作台面有良好的导电性,并且可靠接地。应放在抗静电的材料中储存和运输CMOS集成电路。工作人员不宜穿尼龙、化纤衣服,不穿硬塑料底的鞋子,手或工具在接触集成块前最好先接一下地。对器件引线矫直、弯曲或人工焊接时,使用的设备必须接地。

购物指南

购物指南 消费保障

消费保障 关于我们

关于我们